(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년12월22일

(11) 등록번호 10-1096900

(24) 등록일자 2011년12월14일

(51) Int. Cl.

H01G 4/33 (2006.01) H05K 1/18 (2006.01)

H05K 3/46 (2006.01)

(21) 출원번호 10-2010-7001113

(22) 출원일자(국제출원일자) 2008년06월17일

심사청구일자 2010년01월18일

(85) 번역문제출일자 2010년01월18일

(65) 공개번호 10-2010-0021002

(43) 공개일자 2010년02월23일

(86) 국제출원번호 PCT/US2008/067177

(87) 국제공개번호 WO 2008/157524

국제공개일자 2008년12월24일

(30) 우선권주장

11/765,113 2007년06월19일 미국(US)

(56) 선행기술조사문헌

KR1020060071329 A\*

KR1020070043667 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

이 아이 듀폰 디 네모아 앤드 캄파니

미합중국 테라웨이주 (우편번호 19898) 월밍تون시

마아켓트 스트리йт 1007

(72) 발명자

블랜드, 윌리암

미국 27517 노쓰 캐롤라이나주 채플 힐 옥스포드

셔 레인 312

아메이, 다니엘, 아이.

미국 27705 노쓰 캐롤라이나주 더햄 미들스보로우

코트 6

(뒷면에 계속)

(74) 대리인

양영준, 양영환, 김영

전체 청구항 수 : 총 15 항

심사관 : 이우식

(54) 박막 커패시터를 인쇄 배선 기판의 빌드업층에 포함시키는 방법

**(57) 요약**

본 명세서에는 공지의 양호한 박막 포일상 소성된 커패시터로 제조된 개별화 커패시터를 포함하는 인쇄 배선 기판을 포함하는 소자가 제공된다. 임피던스를 최소화하기 위해 인쇄 배선 기판의 빌드업층 내에 개별화 커패시터를 포함시키는 방법이 제공된다. 개별화 커패시터는 IC의 각각의 전원 및 접지 단자가 그 자신의 개별화 커패시터의 전원 및 접지 전극에 각각 직접 접속될 수 있게 하는 피치를 갖는다. 공지의 양호한 포일상 소성된 커패시터의 공급 재료를 사용하여 PWB 수율의 향상을 가능하게 한다.

**대 표 도 - 도1**

(종래 기술)

(72) 발명자

디에츠, 칼, 에이치.

미국 27613 노쓰 캐롤라이나주 랠레이 블로썸 헬

코트 4304

팔란두즈, 센기즈, 아흐멧

미국 27705 노쓰 캐롤라이나주 더햄 널 로드 4125

에릭슨, 스탠, 제이.

미국 27518 노쓰 캐롤라이나주 캐리 호크 트리 레

인 5216

## 특허청구의 범위

### 청구항 1

인쇄 배선 기판을 포함하는 소자로서,

인쇄 배선 기판은 집적 회로를 지지하고 있으며,

집적 회로는 영역, 복수의 능동 전원 및 접지 단자, 및 복수의 신호 단자를 가지며,

인쇄 배선 기판은 복수의 공지의 양호한 개별화 커패시터를 포함하며,

복수의 공지의 양호한 개별화 커패시터의 각각은 전원 전극 및 접지 전극을 갖고 단일의 공지의 양호한 박막 포일상 소성된 커패시터로 형성되며,

공지의 양호한 박막 포일상 소성된 커패시터는 제1 및 제2 전극을 포함하고,

제2 전극은 풋프린트를 가지며,

복수의 공지의 양호한 개별화 커패시터의 각각은 상기 공지의 양호한 박막 포일상 소성된 커패시터의 제2 전극의 풋프린트 내에 형성되고 인쇄 배선 기판의 빌드업층 내에 매립되고,

복수의 공지의 양호한 개별화 커패시터의 각각은 복수의 개별화 커패시터가 집적 회로의 영역 바로 아래에 그리고 그 영역 내에 있도록 하는 크기 및 피치를 가지며,

집적 회로의 각각의 능동 전원 및 접지 단자는 상기 복수의 공지의 양호한 개별화 커패시터 중 하나의 대응하는 전원 및 접지 전극에 각각 직접 접속되고,

집적 회로의 각각의 신호 단자는 복수의 공지의 양호한 개별화 커패시터로부터 절연된 신호 패드에 직접 접속되지만, 복수의 공지의 개별화 커패시터가 형성될 때 공지의 양호한 박막 포일상 소성된 커패시터로 형성되는,

인쇄 배선 기판을 포함하는 소자.

### 청구항 2

제1항에 있어서, 복수의 공지의 양호한 개별화 커패시터의 각각의 유전체층은 벌크 유전 상수(bulk dielectric constant)가 500을 초과하고, BaTiO<sub>3</sub>; BaSrTiO<sub>3</sub>; PbTiO<sub>3</sub>; CaTiO<sub>3</sub>; PbZrO<sub>3</sub>; BaZrO<sub>3</sub> 및 SrZrO<sub>3</sub> 또는 그 혼합물의 군으로부터 선택된 일반식 AB<sub>0</sub><sub>3</sub>을 포함하는 물질들로부터 선택된 박막 세라믹인, 인쇄 배선 기판을 포함하는 소자.

### 청구항 3

제1항에 있어서, 공지의 양호한 박막 포일상 소성된 커패시터의 포일은 니켈, 니켈 합금, 구리, 구리 합금, 구리-인바-구리, 인바, 니켈-코팅된 구리 및 이들의 임의의 조합으로 이루어진 군으로부터 선택되는, 인쇄 배선 기판을 포함하는 소자.

### 청구항 4

제1항에 있어서, 인쇄 배선 기판은 공지의 양호한 포일상 소성된 커패시터들을 포함하는 포일로부터 다이싱된 적어도 하나의 공지의 양호한 부품으로 형성된 개별화 커패시터들을 포함하고, 공지의 양호한 부품은 적어도 하나의 공지의 양호한 포일상 소성된 커패시터를 포함하는, 인쇄 배선 기판을 포함하는 소자.

### 청구항 5

제4항에 있어서, 공지의 양호한 부품은 픽 앤 플레이스 기법에 의해 인쇄 배선 기판의 빌드업층에 배치되는, 인쇄 배선 기판을 포함하는 소자.

### 청구항 6

제1항에 있어서, 공지의 양호한 박막 포일상 소성된 커패시터의 제2 전극 위에 존재하는, 공지의 양호한 박막 포일상 소성된 커패시터에 적용되는 캐리어 막을 추가로 포함하는, 인쇄 배선 기판을 포함하는 소자.

**청구항 7**

제1항에 있어서, 복수의 개별화 커패시터는

100 마이크로미터 미만의 길이 및 20 피코hen리 미만의 인덕턴스를 갖는 비아에 의해 접적 회로의 단자에 접속되어 있는 PWB의 적어도 하나의 빌드업층 내에 매립되는, 인쇄 배선 기판을 포함하는 소자.

**청구항 8**

인쇄 배선 기판을 포함하는 소자를 제조하는 방법으로서,

2개의 면을 갖고 공지의 양호한 박막 포일상 소성된 커패시터-상기 커패시터는 유전체층 및 풋프린트를 갖는 제2 전극을 포함함-를 포함하는 적어도 하나의 포일 구조체를 제공하는 단계와;

제2 전극을 포함하는 포일 구조체의 면에 금속을 적용하는 단계와;

제2 전극을 포함하지 않는 포일 구조체의 면을 패턴화함으로써 복수의 개별화 커패시터 제1 전극을 형성하는 단계와;

포일 구조체의 패턴화된 면을 인쇄 배선 기판의 빌드업층에 라미네이팅하는 단계와;

포일상 소성된 커패시터의 제2 전극을 포함하는 포일 구조체의 면을 패턴화함으로써, 공지의 양호한 박막 포일상 소성된 커패시터의 제2 전극의 풋프린트 내에 복수의 개별화 커패시터 제2 전극을 형성하는 단계를 포함하여,

복수의 개별화 커패시터 제1 전극 및 복수의 개별화 커패시터 제2 전극을 형성하는 단계는 상기 공지의 양호한 박막 포일상 소성된 커패시터로 복수의 개별화 커패시터를 형성하는 것이고, 상기 복수의 개별화 커패시터는 각각의 개별화 커패시터 전극이 접적 회로의 단자에 직접 부착될 수 있도록 일정 크기 및 피치를 갖고,

복수의 개별화 커패시터는 상기 공지의 양호한 포일상 소성된 커패시터의 제2 전극의 풋프린트 내에 형성되고, 접적 회로의 영역 바로 아래에 그리고 그 영역 내에 있는,

인쇄 배선 기판을 포함하는 소자를 제조하는 방법.

**청구항 9**

인쇄 배선 기판을 포함하는 소자를 제조하는 방법으로서,

2개의 면을 갖고 적어도 하나의 공지의 양호한 박막 포일상 소성된 커패시터-상기 커패시터는 유전체층 및 풋프린트를 갖는 제2 전극을 포함함-를 포함하는 적어도 하나의 포일 구조체를 제공하는 단계와;

제2 전극을 포함하는 포일 구조체의 면에 금속을 적용하는 단계와;

제2 전극을 포함하지 않는 포일 구조체의 면을 패턴화함으로써 복수의 개별화 커패시터 제1 전극을 형성하는 단계와;

포일 구조체를 다이싱하여 복수의 다이싱된 부품들을 형성하고, 복수의 다이싱된 부품들 중 하나는 상기 적어도 하나의 공지의 양호한 박막 포일상 소성된 커패시터를 포함하는 단계와;

상기 적어도 하나의 공지의 양호한 박막 포일상 소성된 커패시터를 포함하는 상기 적어도 하나의 다이싱된 부품의 패턴화된 면이 인쇄 배선 기판의 빌드업층과 접촉하도록 상기 적어도 하나의 다이싱된 부품을 빌드업층에 핀 앤 플레이스하는 단계와;

상기 적어도 하나의 공지의 양호한 박막 포일상 소성된 커패시터를 포함하는 상기 적어도 하나의 다이싱된 부품을 빌드업층에 라미네이팅하는 단계와;

공지의 양호한 박막 포일상 소성된 커패시터의 제2 전극을 포함하는 포일 구조체의 면을 패턴화함으로써, 제2 전극의 풋프린트 내에 복수의 개별화 커패시터 제2 전극을 형성하는 단계를 포함하여,

복수의 개별화 커패시터 제1 전극 및 복수의 개별화 커패시터 제2 전극을 형성하는 단계는, 상기 적어도 하나의 공지의 양호한 박막 포일상 소성된 커패시터로 복수의 개별화 커패시터를 형성하는 것이고, 상기 복수의 개별화 커패시터는 각각의 개별화 전극이 접적 회로의 단자에 직접 부착될 수 있도록 일정 크기 및 피치를 갖고,

복수의 개별화 커패시터는 상기 적어도 하나의 공지의 양호한 포일상 소성된 커패시터의 제2 전극의 풋프린트 내에 형성되고, 접적 회로의 영역 바로 아래에 그리고 그 영역 내에 있는, 인쇄 배선 기판을 포함하는 소자를 제조하는 방법.

#### 청구항 10

제8항에 있어서, 유전체층의 전체 영역이 지지되는, 인쇄 배선 기판을 포함하는 소자를 제조하는 방법.

#### 청구항 11

제8항에 있어서, 공지의 양호한 박막 포일상 소성된 커패시터를 포함하는 포일 구조체가 다른 PWB 층들에 라미네이팅되고, 그에 의해 다수의 층들이 일제히 서로 라미네이팅되는 단일 라미네이션 단계에서 또는 각각의 층이 개별적으로 라미네이팅되는 다수의 라미네이션 단계들에서 무코어 다층 구조체를 생성하는, 인쇄 배선 기판을 포함하는 소자를 제조하는 방법.

#### 청구항 12

제8항에 있어서,

커패시턴스 허용오차, 다른 전기적 특성, 또는 이들 둘 다에 의해 공지의 양호한 품질을 갖는지를 판정하기 위해 포일상 소성된 커패시터를 테스트하는 단계를 추가로 포함하는, 인쇄 배선 기판을 포함하는 소자를 제조하는 방법.

#### 청구항 13

제9항에 있어서,

커패시턴스 허용오차, 다른 전기적 특성, 또는 이들 둘 다에 의해 공지의 양호한 품질을 갖는지를 판정하기 위해 포일상 소성된 커패시터를 테스트하는 단계를 추가로 포함하는, 인쇄 배선 기판을 포함하는 소자를 제조하는 방법.

#### 청구항 14

제12항에 있어서,

공지의 불량인 포일상 소성된 커패시터를 식별하는 단계와;

공지의 불량인 포일상 소성된 커패시터를 포함하는 인쇄 배선 기판에 부품들을 조립하는 것을 방지하는 단계를 추가로 포함하는, 인쇄 배선 기판을 포함하는 소자를 제조하는 방법.

#### 청구항 15

제9항에 있어서,

패턴화하기 전에, 캐리어 막을 커패시터를 포함하는 포일 구조체의 면에 적용하는 단계를 추가로 포함하는, 인쇄 배선 기판을 포함하는 소자를 제조하는 방법.

#### 청구항 16

삭제

#### 청구항 17

삭제

#### 청구항 18

삭제

#### 청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

## 명세서

### 기술분야

[0001]

본 발명은 낮은 인덕턴스 전력을 반도체 소자에 제공하기 위해 높은 커패시턴스를 갖는 소자들을 인쇄 배선 기판의 빌드업층에 포함시키는 방법에 관한 것이다.

### 배경기술

[0002]

집적 회로(IC)를 비롯한 반도체 소자는 점점 더 높은 주파수 및 데이터 전송속도로 그리고 더 낮은 전압에서 작동한다. 더 높은 작동 주파수, 즉 더 높은 IC 스위칭 속도는 IC에 대한 전압 응답 시간이 더 빨라야만 한다는 것을 의미한다. 더 낮은 작동 전압은 허용가능한 전압 변동(리플(ripple)) 및 노이즈가 더 작아질 것을 필요로 한다.

[0003]

예를 들어, 마이크로프로세서 IC가 스위칭되어 작동을 시작함에 따라, 그것은 스위칭 회로를 지원하기 위한 전력을 필요로 한다. 전압원의 응답 시간이 너무 느린 경우, 마이크로프로세서는 허용가능한 리플 전압 및 노이즈 여유(noise margin)를 초과할 전압 강하 또는 전력 저하(power droop)를 겪을 것이고, IC가 오작동하게 될 것이다. 더욱이, IC에 전원이 공급될 때, 느린 응답 시간은 전력 오버슈트(power overshoot)로 이어질 것이다.

[0004]

그 결과, 전원선 및 접지(복귀)선에서의 노이즈 생성 및 더 빠른 회로 스위칭에 대응하기 위한 충분한 전류의 공급 필요성은 반도체 소자에서 점점 더 중요한 문제가 된다.

[0005] 허용 가능한 한계 내로 전력 저하 및 오버슈트를 제어함으로써 IC로의 전력 전송을 안정화시키는 것은 적절한 응답 시간 내에 전력을 제공 또는 흡수하기 위해 IC에 충분히 가깝게 배치된 커패시터를 사용함으로써 달성된다. 전력 분배 시스템에서 노이즈를 저감시키는 것은 임피던스를 저감시킴으로써 달성된다.

[0006] 종래의 회로에서, 임피던스는 병렬로 상호접속되어 IC 주변에 모여 있는 부가의 표면 실장 커패시터를 사용함으로써 감소된다. 대용량 커패시터(large value capacitor)는 전원 공급 장치 부근에 배치되고, 중용량 커패시터(mid-range value capacitor)는 IC와 전원 공급 장치 사이의 지점에 배치되고, 소용량 커패시터(small value capacitor)는 IC에 아주 가깝게 배치된다. 이러한 커패시터 분포는 전력이 전원 공급 장치로부터 IC로 이동할 때 전압 응답 시간을 줄이도록 설계된다. 주파수가 상승되고 작동 전압이 계속 강하됨에 따라, 증가된 전력이 더 빠른 속도로 공급되어야 하며, 이는 점점 더 낮은 인더턴스 및 임피던스 레벨을 필요로 한다.

## 발명의 내용

### 과제의 해결 수단

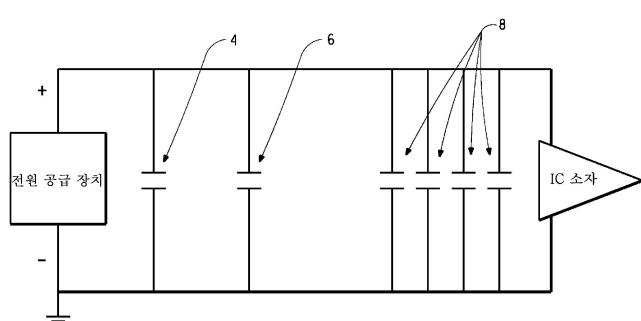

[0007] 도 1은 IC 소자 및 전원 공급 장치에 대한 커패시터들의 배치의 전기 개략도이다. 전원 공급 장치, IC 소자 및 커패시터들(4, 6, 8)이 도시되어 있으며, 이들 커패시터는 각각 대용량, 중용량 및 소용량 커패시터들을 나타내며, 상기한 바와 같이 임피던스 감소와 전력 저하 최소화와 오버슈트 감소에 사용된다.

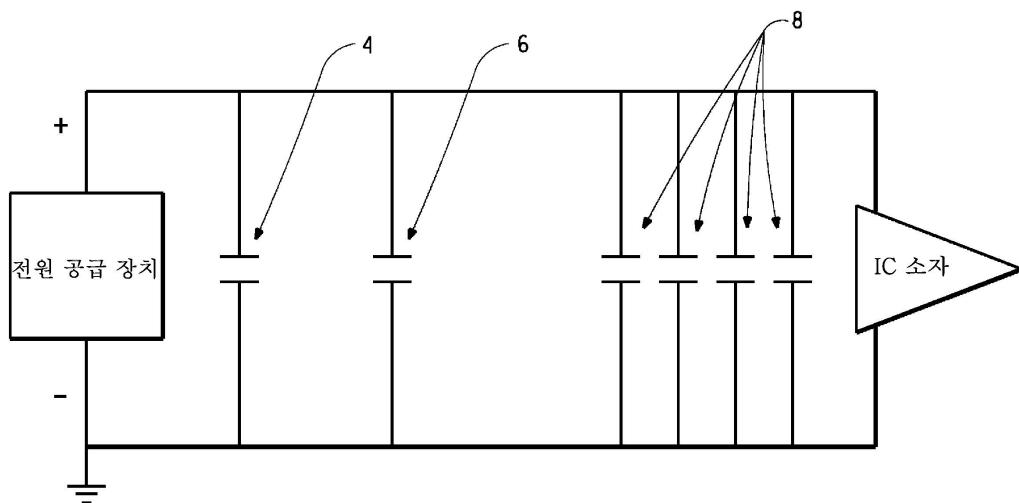

[0008] 도 2는 도 1에 나타낸 전기 개략도에 따른 PWB의 대표적인 정단면도이며, PWB의 기판의 전원 및 접지 평면으로의 표면 실장 기술(SMT) 커패시터(50, 60)(도 1에 8로 나타낸 커패시터) 및 IC 소자(40)의 종래 기술의 접속을 도시한다. IC 소자(40)는 땜납 필렛(solder fillet)(44)에 의해 랜드(land)(41)에 접속된다. 랜드(41)는 회로 라인(circuit line)(72, 73)에 의해 비아(90, 100)의 패드를 거쳐 도금된 도통 홀(plated through hole)에 접속된다. 비아 패드는 총칭적으로 82로 도시되어 있다. 비아(90)는 도체 평면(120)에 전기적으로 접속되어 있고 비아(100)는 도체 평면(122)에 접속되어 있다. 도체 평면(120, 122)은 전원 공급 장치의 전력 또는 전압측에 접속되고 전원 공급 장치의 접지 또는 복귀측에 접속되어 있다. 소용량 커패시터(50, 60)는 유사하게도 IC 소자(40)에 전기적으로 병렬 접속되는 방식으로 비아 및 도체 평면(120, 122)에 전기적으로 접속되어 있다. 모듈, 인터포저(interposer) 또는 패키지에 배치된 IC 소자들의 경우에, 그 모듈, 인터포저 또는 패키지가 부착되는 인쇄 배선 마더보드(printed wiring motherboard) 상에 대용량 및 중용량 커패시터가 존재할 수 있다.

[0009] 종래에 실시되는 것으로 도 1에 도시된 종래의 관행인, 다수의 커패시터를 병렬로 상호접속시키는 것은 전력 시스템 임피던스를 감소시키지만 또한 복잡한 전기 경로 설정을 필요로 한다. 이는 회로 루프 인더턴스의 증가는 바람직하지 않은 결과를 갖고, 이는 차례로 임피던스를 증가시키고 전류 흐름을 제약하며 부분적으로 표면 실장형 커패시터 사용의 이점을 감소시킨다. 주파수가 상승되고 작동 전압이 계속 강하함에 따라, 증가된 전력이 더 빠른 속도로 공급되어야 하고 이는 점점 더 낮은 인더턴스 및 임피던스 레벨을 필요로 한다.

[0010] 임피던스를 최소화하기 위해 상당한 노력이 있어 왔다. 하워드(Howard) 등의 미국 특허 제5,161,086호는 커패시터 라미네이트(평면 커패시터)가 기판의 다수 층들 내에 배치된 용량성 인쇄 회로 기판을 개시하고 있으며, 이 기판 상에 접적 회로와 같은 다수의 소자들이 배치되어 있다. 이들 소자는 커패시터 라미네이트(들)와 작동 식으로 결합되어 있다. 하워드 등의 특허에서는 차용 또는 공유 커패시턴스를 이용하여 용량성 기능의 증대를 제공한다. 그러나, 이러한 커패시터 배치에 대한 방안은 높은 커패시턴스를 제공하지 않으면 전압 응답을 반드시 향상시키지는 않는다. 커패시터 라미네이트를 단순히 IC에 더 근접하게 배치시키는 것은 높은 커패시턴스를 제공하는 만족스러운 기술적 해결책이 아닌데, 이는 이용 가능한 총 커패시턴스가 임피던스를 적절히 최소화시키는 데 불충분할 수 있기 때문이다.

[0011] 차크라보티(Chakravorty)의 미국 특허 제6,611,419호는 접적 회로 다이의 전원 공급 단자가 다층 세라믹 기판의 적어도 하나의 매립된 커패시터의 각자의 단자에 결합될 수 있다는 것을 개시하고 있다.

[0012] 아메이(Amey) 등의 미국 특허 출원 공개 제2006-0138591호는 높은 커패시턴스 커패시터들을 인쇄 배선 기판의 코어에 포함시키는 방법을 개시하고 있으며, 이들이 빌드업층에 배치될 수 있다는 것을 단지 제안하고 있을 뿐이다. 그러나, 아메이 등의 출원은 테스트된 공지의 양호한 커패시터를 빌드업층 내에 배치하는 방법을 개시하거나 제안하고 있지는 않다. 또한, 아메이 등의 커패시터 형성 방법은 포일 레벨(foil level)에서 커패시터를 테스트하는 것을 교시하거나 고려하고 있지 않은데, 이는 아메이 출원에서의 커패시터들은 포일 레벨에서 단락 되기 때문이다. 더욱이, 아메이 등의 출원은 커패시터 수율이 나쁜 포일 전체 또는 테스트 결과가 불량인 개개의 커패시터를 폐기함으로써 최종 PWB 제품의 수율에 어떻게 영향을 미칠 수 있는지에 대해 개시하고 있지

않다.

[0013] 문헌[Development of Novel Thin Material for Decoupling Capacitors Embedded in PWBs", Proceedings of the Technical Conference, IPC Printed Circuits Expo, Los Angeles, 2007]에서 히라타(Hirata) 등은 금속/ 절연체/금속(MIM) 라미네이트 구조체를 형성하고 상부 금속층을 패턴화 및 에칭하여 전극을 형성하며 이 구조체를 개개의 개별화 커패시터(크기가 1 mm<sup>2</sup> 내지 100 mm<sup>2</sup>임)로 절단하는 것에 대해 개시하고 있다. 이들 커패시터는 테스트될 수 있고, 공지의 양호한 커패시터가 접착제를 사용하여 인쇄 배선 기판에 부착될 수 있다. 커패시터 크기 및 설계는 많은 전원 및 접지 단자를 갖는 마이크로프로세서 등의 IC에 전력을 전달하는 데 적합하지 않다. 히라타 등은 본 명세서에 기술된 기술적 해결 방안을 제안하지 못하고 있다.

[0014] 따라서, 현재의 문제점은 복수의 커패시터를 PWB의 빌드업층 내에 포함시키는, 즉 배치하는 방법을 개발하는 것이며, 각각의 커패시터는 "공지의 양호한(know good)" 것이고, 각각의 배치된 커패시터가 IC 바로 아래에 위치하고 IC의 치수 내에 들어가며 마이크로프로세서와 같은 IC의 각각의 전원 및 접지 단자가 고유의 배치된 커패시터의 전원 및 접지 단자에 각각 직접 접속될 수 있도록 하는 크기 및 피치를 갖는다.

[0015] 본 명세서에 기술된 방법은 공지의 양호한 커패시터만을 사용하여, 모든 커패시터가 IC의 바로 아래에 있고 IC의 치수 내에 들어갈 수 있게 하는 매우 작은 크기 및 미세 피치를 갖는 복수의 배치된 커패시터를 형성함으로써 이러한 문제점을 해결한다. 하워드 등과, 차크라보티와, 아메이 등과, 히라타 등의 문헌 또는 다른 참조문헌들의 어떤 조합도 본 해결 방안을 제안하거나 예측가능한 결과를 구성하지 않는다. 이들 3가지 특징—"공지의 양호한" 품질, 크기 및 피치-을 갖는 커패시터를 제조하는 것에 의해, IC가 갖는 전원 및 접지 단자와 동일한 개수의 공지의 양호한 개별화 커패시터를 IC의 바로 아래에 그리고 IC의 치수 내에 포함시키는 것이 가능하게 된다. 이는 낮은 임피던스에서 IC에 전력을 제공하고 적격으로 신뢰성있는 PWB 제품을 제조하는 유효 결과를 가져온다.

#### 발명의 개요

[0017] 청구된 발명은, 영역과 복수의 전원, 접지 및 신호 단자를 갖는 접적 회로를 지지하는 인쇄 배선 기판을 포함하는 소자에 관한 것으로서,

#### 인쇄 배선 기판은

[0019] 복수의 공지의 양호한 개별화 커패시터를 포함하며, 각각의 커패시터는 전원 전극 및 접지 전극을 갖고, 제1 전극과 풋프린트를 갖는 제2 전극을 구비한 공지의 양호한 포일상 소성된 커패시터(fired-on-foil capacitor)로 형성된다. 공지의 양호한 개별화 커패시터 각각은 (1) 공지의 양호한 포일상 소성된 커패시터의 제2 전극의 풋프린트 내에 형성되고 인쇄 배선 기판의 빌드업층들 내에 매립되고, (2) 복수의 개별화 커패시터가 IC의 영역 바로 아래에 그리고 IC의 영역 내에 있도록 하는 크기 및 피치를 갖는다. 소자에서, IC의 각각의 능동 전원 및 접지 전극은 공지의 양호한 개별화 커패시터의 대응하는 전원 및 접지 전극에 각각 직접 접속된다. 소자에서, IC의 각각의 신호 단자는 개별화 커패시터로부터 절연된 신호 패드에 직접 접속되지만 그와 동시에 공지의 양호한 포일상 소성된 커패시터로 형성된다.

[0020] 이를 소자를 제조하는 방법으로서,

[0021] 2개의 면과 공지의 양호한 박막 포일상 소성된 커패시터-상기 커패시터는 유전체층과 풋프린트를 갖는 제2 전극 층을 포함함-를 갖는 적어도 하나의 포일 구조체를 제공하는 단계와;

[0022] 제2 전극을 포함하는 포일 구조체의 제2 면을 금속으로 스퍼터링 및 도금하는 단계와;

[0023] 제2 전극을 포함하지 않는 포일 구조체의 면을 패턴화함으로써 복수의 제1 전극을 형성하는 단계와;

[0024] 포일 구조체의 패턴화된 면을 인쇄 배선 기판의 빌드업층에 라미네이팅하는 단계와;

[0025] 포일상 소성된 커패시터의 제2 전극을 포함하는 포일 구조체의 면을 패턴화함으로써 제2 전극층의 풋프린트 내에 복수의 제2 전극을 형성하는 단계를 포함하는 방법이 제공된다.

[0026] 이를 방법 모두에서, 제1 및 제2 전극을 형성하는 단계는 각각의 전극이 IC의 능동 단자에 직접 부착될 수 있도록 일정 크기 및 피치를 갖는 복수의 개별화 커패시터를 형성한다. 또한, 복수의 개별화 커패시터는 접적 회로에 근접해 있다.

[0027] 또한, 일부 방법에서, 유전체층의 전체 영역이 지지된다.

[0028] 더욱이, 일부 방법에서, 포일 구조체가 다이싱(dicing)되어 적어도 하나의 포일상 소성된 커패시터를 포함하는 공지의 양호한 부품들을 형성할 수 있다. 이들 부품은 퍽 앤 플레이스(pick and place) 기법에 의해 PWB의 빌드업층에 배치된 다음에 그에 라미네이팅될 수 있다.

[0029] 또한, 이들 방법 중 일부에서, 코어 구조체가 PWB에 라미네이팅된다. 대안적으로, 다른 방법에서, 코어 구조체가 사용되지 않는다. 오히려, 본 방법으로 무코어(coreless) 구조체가 얻어지고, 포일상 소성된 커패시터를 포함하지 않는 포일 구조체의 예칭된 면이 다른 PWB 층에 라미네이팅된다. 이는 다수의 층이 일제히 함께 라미네이팅되는 단일 라미네이션 단계에서 또는 각각의 층이 개별적으로 라미네이팅되는 다수의 라미네이션 단계들에서 무코어 다층 구조체를 생성한다.

### 도면의 간단한 설명

[0030] 상세한 설명은 다음의 도면들을 참조할 것이며, 여기서 동일한 도면 부호는 동일한 요소를 가리킨다.

도 1은 임피던스 감소 및 전력 저하 최소화 또는 오버슈트 감쇠를 위한 전형적인 커패시터 배치의 전기 개략도.

도 2는 임피던스 감소 및 전력 저하 최소화 또는 오버슈트 감쇠에 사용되는 종래의 표면 실장 기술 커패시터를 갖는 도 1의 전기 개략도에 따른 종래 기술의 인쇄 배선 기판의 정면 단면도.

도 3a 내지 도 3h는 포일이 공지의 양호한 커패시터 전극의 풋프린트 내에 앤티패드(antipad)를 생성하기 위해 패턴화되는 박막 포일상 소성된 커패시터를 제조하는 방법을 도시하는 도면.

도 4a 내지 도 4d는 공지의 양호한 커패시터로부터 도출된 복수의 박막 포일상 소성된 개별화 커패시터를 인쇄 배선 기판의 빌드업층 내에 포함시키는 방법을 나타낸 도면.

도 5a 내지 도 5g는 공지의 양호한 커패시터로부터 도출된 복수의 박막 포일상 소성된 개별화 커패시터를 인쇄 배선 기판의 빌드업층에 포함시키는 대안적인 방법을 나타낸 도면.

도 6은 본 명세서에 기술된 방법들에 의해 박막 커패시터가 포함되고 플립칩 IC의 범프에 직접 접속되고 납땜 접합에 의해 인쇄 배선 마더 보드에 접속된 PWB를 도시하는 단면도.

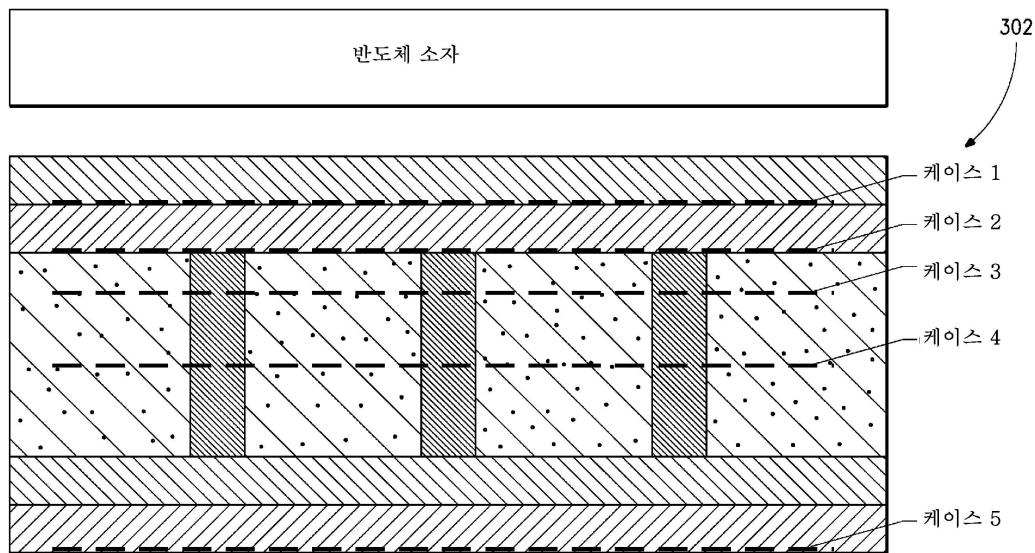

도 7은 본 명세서에 기술된 방법들에 의해 PWB의 코어 및 빌드업층에 포함된 5개의 커패시터의 위치들을 나타낸 단면도.

도 8은 도 7에 도시된 5개의 커패시터 위치들에 대한 임피던스 대 주파수 응답의 전기 시뮬레이션 결과를 도시하는 도면.

도 9는 도 7에 도시된 5개의 커패시터 위치들에 대한 공진 주파수 대 반도체 소자로부터의 거리를 나타낸 그래프.

### 발명을 실시하기 위한 구체적인 내용

[0031] 상세한 설명은 이하의 정의된 용어들과 관련하여 청구의 범위에 언급된 발명에 대해 논의한다.

[0032] 본 명세서에서 사용되는 바와 같이, 용어 "포함시키는" 또는 "포함시키는 것"은 커패시터를 인쇄 배선 기판 내에 매립하는 것을 말하며, 커패시터를 인쇄 배선 기판 내에 배치, 위치 또는 통합시키는 것의 개념들을 포함한다.

[0033] 본 명세서에 사용되는 바와 같이, 용어 "포일상 소성된 박막 커패시터"는 (1) 유전 상수가 높은 박막을 형성하는 유전체를 결정화하고 소결시키기 위하여 금속 포일 상에 증착된 유전층을 승온에서 소성하고, (2) 유전체를 소성하기 전에 또는 그 후에 상부 전극을 증착함으로써 형성되는 커패시터를 말한다.

[0034] 본 명세서에서 사용되는 바와 같이, 용어 "어닐링" 및 "소성"은 바꾸어 사용될 수 있으며 승온 공정을 말한다.

[0035] 본 명세서에 사용되는 바와 같이, "높은 유전 상수" 또는 "높은 K의 박막 커패시터 유전 재료"라는 용어는 별크 유전 상수(bulk dielectric constant)가 500을 초과하고 일반식  $ABO_3$ 의 페로브스카이트형(perovskite-type) 강 유전성 조성물을 포함할 수 있는 재료를 말한다. 이러한 조성물의 예로는  $BaTiO_3$ ;  $BaSrTiO_3$ ;  $PbTiO_3$ ;  $CaTiO_3$ ;  $PbZrO_3$ ;  $BaZrO_3$  및  $SrZrO_3$  또는 그 혼합물을 말한다.  $Pb(Mg_{1/3}Nb_{2/3})O_3$  및  $Pb(Zn_{1/3}Nb_{2/3})O_3$ 와 같이 대안적인 원소를 A 및/또는 B 위치에 치환함으로써 다른 조성물들도 또한 가능하다. 조성물의 혼합 금속 변형(version)도 또

한 적합하다.

- [0036] 본 명세서에 사용되는 바와 같이, "인쇄 배선 기판" 또는 "인쇄 배선 기판 소자" [PWB]라는 용어는 인터포저, 멀티칩 모듈, 에어리어 어레이 패키지(area array package), 반도체 패키지, 시스템 온 패키지(system-on package), 시스템 인 패키지(system-in package) 등, 또는 그와 같이 사용되는 소자를 말한다.

- [0037] 본 명세서에서 사용되는 바와 같이, "PWB 코어" 또는 "PWB 라미네이팅된 코어"라는 용어는 하나의 라미네이션 단계에서 다수의 내부층 PWB 패널들로 형성되는 인쇄 배선 기판 구조체를 말한다. PWB 코어는 전형적으로 코어에 형성되거나 순차적으로 추가되는 추가적인 금속/유전체층들에 대한 베이스(base)로서 사용된다.

- [0038] 본 명세서에서 사용되는 바와 같이, "빌드업" 또는 "빌드업층"이라는 용어는 유기 유전체 및 패턴화된 구리층을 PWB 라미네이팅된 코어의 한쪽 또는 양쪽에 추가함으로써 형성되는 인쇄 배선 기판의 층들을 말한다.

- [0039] 본 명세서에 사용되는 바와 같이, "인쇄 배선 마더보드" 또는 "PWB 마더보드"라는 용어는 위에서 정의한 인쇄 배선 기판이 일반적으로 그 상에 배치되어 그에 상호 연결되는 큰 인쇄 배선 기판을 말한다.

- [0040] 본 명세서에 사용되는 바와 같이, "포일"이라는 용어는 일반 금속층, 도금된 금속, 스퍼터링된 금속 또는 당업자에게 공지된 임의의 방식으로 형성 또는 중착된 금속층을 말한다.

- [0041] 본 명세서에서 사용되는 바와 같이, "양호한" 또는 "공지의 양호한 커패시터"라는 용어는 테스트된 커패시터를 말하며 미리 정해진 규격 내에서 기능을 하는 것으로 알려져 있다.

- [0042] 본 명세서에서 사용되는 바와 같이, "공지의 양호한 커패시터 전극"이라는 용어는 공지의 양호한 커패시터의 전극을 말한다.

- [0043] 본 명세서에서 사용되는 바와 같이, "개별화 커패시터"라는 용어는 단일의 큰 공지의 양호한 포일상 소성된 커패시터를 분할하여 형성되는 복수의 커패시터들 중 하나를 말한다. 단일의 큰 포일상 소성된 커패시터는 이미 테스트되었고 공지의 양호한 것으로 판정되었다. 임의의 개별화 커패시터는 동일한 큰 포일상 소성된 커패시터로 제조된 다른 개별화 커패시터들과 공통인 하나 또는 2개의 (상부 또는 하부) 전극을 갖거나 갖지 않을 수 있다.

- [0044] 본 명세서에서 사용되는 바와 같이, 공통 전극은 2개 이상의 개별화 커패시터에 대한 2개 이상의 전극으로서 기능을 하는 연속하는 커패시터 전극을 말한다.

- [0045] 본 명세서에서 사용되는 바와 같이, "다이싱"이라는 용어는 다수의 큰 테스트된 포일상 소성된 커패시터를 포함하는 포일 구조체를 특정의 치수로 절단하여 하나 이상의 큰 커패시터를 포함하는 유닛을 형성하는 것을 말한다. 다이싱은 보통 다이아몬드 톱으로 달성되며, 포일은 하나 이상의 큰 커패시터(들)의 커패시터 유전체 영역보다 크게 절단된다.

- [0046] 본 명세서에서 사용되는 바와 같이, "공지의 양호한 부품"은 다이싱된 포일 구조체를 말하며, 각각의 유닛은 하나 이상의 큰 공지의 양호한 커패시터(들)를 포함하고 있다.

- [0047] 본 명세서에서 사용되는 바와 같이, "전극 웃프린트"라는 용어는 스퍼터링된 커패시터 전극의 위치 및 영역을 말한다.

- [0048] 본 명세서에서 사용되는 바와 같이, "양호한" 또는 "공지의 양호한 인쇄 배선 기판 또는 PWB"라는 용어는 테스트된 인쇄 배선 기판을 말하며, 모든 매립된 커패시터 및 회로는 미리 정해진 규격 내에서 기능을 하는 것으로 알려져 있다.

- [0049] 본 명세서에서 사용되는 바와 같이, "미세 피치"라는 용어는 기술 용어로서, 25 밀(mil) 이하의 간격을 갖는 커패시터를 말한다.

- [0050] 본 명세서에서 사용되는 바와 같이, "픽 앤 플레이스"라는 용어는 기술 용어로서 회로의 조립 파일에 따라 부품이 선택되어 특정의 위치에 배치되는 조립 공정을 말한다.

- [0051] 본 명세서에서 사용되는 바와 같이, "제1 및 제2 전극의 공통 영역"이라는 용어는 제1 및 제2 전극 둘 모두의 일부분을 포함하는 커패시터 내의 중첩 영역을 말하며, 이하의 식으로부터 커패시턴스를 계산하는 데 사용된다.

- [0052]  $C = 0.885 K A/t$ ,

- [0053] 여기서

- [0054] C는 단위가 나노 페럿인 커패시턴스이고,

- [0055] 0.885는 상수이며,

- [0056] K는 유전 상수이고,

- [0057] t는 단위가 마이크로미터(미크론)인 유전체층의 두께이며, A는 단위가 ~~㎟~~인 제1 및 제2 전극의 공통 면적이다.

- [0058] 본 명세서에서 사용되는 바와 같이, "집적 회로(IC)"라는 용어는 반도체 칩, 예를 들어, 마이크로프로세서, 트랜지스터 세트, 논리 소자 등을 말한다.

- [0059] 본 명세서에서 사용되는 바와 같이, "직접 접속된"이라는 용어는 수평 평면에 있는 도체 트레이스보다는 비아에 의한 2개의 특징부의 상호접속을 말한다.

- [0060] 본 명세서에서 사용되는 바와 같이, "근접"이라는 용어는 커패시터들이 집적 회로의 영역 바로 아래에 그리고 IC의 영역, 즉 길이 및 폭 치수 내에 배치되어 있다는 사실을 말한다.

- [0061] 본 명세서에서 사용되는 바와 같이, "하나"라는 용어는 적어도 하나를 의미한다.

- [0062] 본 명세서에서 사용되는 바와 같이, "복수"라는 용어는 하나 초과를 의미한다.

- [0063] 본 발명은 공지의 양호한 포일상 소성된 커패시터의 공급 재료를 사용하여 인쇄 배선 기판(PWB)을 포함하는 소자를 형성하는 방법에 관한 것이다. 본 명세서에 기술된 방법들은 단일의 큰 공지의 양호한 커패시터로 형성되는 복수의 개별화 커패시터들이 PWB의 빌드업층 내에 포함(다시 말하면, 배치 또는 위치)되어 있는 인쇄 배선 기판을 제조한다. 이들 방법은 공지의 양호한 개별화 커패시터를 복수개 형성하기 위하여 이전에 테스트되어 양호한 것으로 판정된 큰 포일상 소성된 커패시터의 제1 및 제2 전극을 복수의 전극으로 분할한다. 개별화 커패시터가, 일반적으로 라미네이션에 의해, 인쇄 배선 기판의 빌드업층에 부착된다. PWB를 형성하는 데 공지의 양호한 커패시터만이 사용되기 때문에, 공지의 양호한 PWB만이 생산된다. 따라서, 본 발명에 의해 양호한 PWB의 수율이 향상된다.

- [0064] 구체적으로, 큰 포일상 소성된 커패시터가 포일 레벨에서 "공지의 양호한" 커패시터로서 판정된다. 이들로 형성된 복수의 개별화 커패시터는 (1) 모든 개별화 커패시터가 IC의 바로 아래에 그리고 IC의 치수 내에 배치되고 (2) 마이크로프로세서와 같은 IC의 각각의 능동(즉, 작동) 전원 및 접지 단자가 그 자신의 개별화 커패시터의 전원 및 접지 전극에 직접 접속될 수 있도록 하는 크기 및 피치를 갖는다. 커패시터 및 PWB 회로는 또한 매립 공정에서 부가의 지점들에서 테스트될 수 있다. 테스트는 포일상 소성된 커패시터의 공지의 양호한 품질은 물론 그로부터 제조된 개별화 커패시터의 공지의 양호한 품질을 확실히 입증한다. 따라서, 개별화 커패시터들이 매립되어 있는 PWB도 또한 공지의 양호한 것으로 확인된다. 그 결과, PWB 내로의 매립 이전에 커패시터를 테스트하는 것은 IC 및 부품을 공지의 양호한 인쇄 배선 기판에만 실장하는 것을 촉진시키고, 이는 최종 제품의 생산 수율을 향상시킨다.

- [0065] 매립된 개별화 커패시터를 형성하는 2가지 일반적인 방법

- [0066] 궁극적으로, 본 발명의 바탕이 되는 메커니즘은 IC의 각각의 능동 전원 및 접지 단자가 비아를 사용하여 그 자신의 개별화 커패시터의 전원 및 접지 전극에 각각 직접 접속될 수 있도록 하는 크기 및 피치의 개별화 커패시터를 형성하는 것이다. 임피던스를 최소화하기 위해, 모든 개별화 커패시터가 IC의 바로 아래에 그리고 IC의 치수 내에 배치된다. 그렇게 배치되도록 충분히 작은 크기 및 미세 피치를 갖고 공지의 양호한 품질을 갖는 개별화 커패시터를 생성하는 것은 지금까지 커패시터를 PWB에 배치하는 현재의 그리고 종래의 기술을 넘어서는 것이었다. 따라서, 본 명세서에 설명된 방법은 이러한 기술로부터 예측가능한 결과가 아니다.

- [0067] 개별화 커패시터의 작은 크기 및 미세 피치는 IC에 있는 전원 및 접지 단자와 동일한 개수의 이들 커패시터를 빌드업층 내에 포함시키는 것을 촉진시키며, 그에 의해 각각의 IC 전원 및 접지 단자를 다른 특유의 개별화 커패시터의 전원 및 접지 전극에 직접 접속시키는 것을 가능하게 한다. 각각의 개별화 커패시터의 공지의 양호한 품질은 IC 단자로의 커패시턴스 전달이 신뢰성있도록 보장해준다. 다수의 커패시터를 PWB의 빌드업층 내에 배치하면 커패시터로부터 IC까지의 거리를 최소화함으로써 임피던스를 감소시킨다. 일정 크기 및 피치의 많은 공지의 양호한 개별화 커패시터를 생성하고 IC의 능동 단자의 개수에 대응하는 일정 수율 요건을 갖는 것에 의존하여, 본 명세서에 기술된 방법들은 임피던스를 최소화하고 지금까지 실시되지 않은 제품 수율을 향상시키는 방식으로 커패시터를 PWB에 포함시켜 PWB를 형성한다.

- [0068] PWB에 매립될 개별화 커패시터가 도출되는 포일상 소성된 커패시터는 금속 포일 상에 형성된 높은 유전 상수("

높은 K")를 갖는 세라믹 유전체 및 금속 전극을 포함하는 다양한 재료의 박막 기법들에 의해 제조된다.

[0069] 이하는 복수의 개별화 커패시터를 형성하고 매립하는 한 방식이다. 먼저, 포일상 소성된 큰 커패시터가 테스트되고 양호한 커패시터가 "공지의 양호한" 것으로 지정된다. 공지의 양호한 커패시터를 식별하는 것은 또한 불량 포일상 소성된 커패시터를 식별한다. 이러한 식별은 IC 및 임의의 SMT 부품을 갖는 최종 조립체가 불량 포일상 소성된 커패시터를 갖는 PWB에 대해 제거될 수 있게 한다.

[0070] 부가의 금속이 이제 포일의 커패시터측의 전체에 추가되어 금속 포일/유전체/금속 샌드위치 구조체를 생성한다. 포일상 소성된 큰 커패시터의 제1 전극을 형성하는 포일이 이제 예칭에 의해 패턴화되어, 각각의 제1 전극으로부터 복수의 제1 전극이 생성된다. 그 다음, 패턴화된 포일은 라미네이션에 의해 인쇄 배선 기판의 빌드업층에 부착된다. 그 후, 포일상 소성된 커패시터의 제2 전극을 포함하는 포일이 예칭에 의해 패턴화되어, 포일 내에 포함되어 있는 각각의 제2 전극으로부터 복수의 제2 전극을 형성한다. 포일상 소성된 큰 커패시터의 제1 및 제2 전극의 패턴화는 복수의 개별화 커패시터를 형성한다. 예칭은 개별화 커패시터를 배치하는 것에 비해 고도로 정확한 패턴화 공정이며, 한 면이 75 마이크로미터 이하와 같이 아주 작은 크기의 커패시터 전극을 생성할 수 있으며, 각각의 개별화 커패시터는 75 마이크로미터 이하만큼 분리되어 있다. 이러한 작은 크기, 미세 피치 및 정확한 전극 패턴화는 차례로 각각의 개별화 커패시터의 전원 및 접지 전극과 IC의 개개의 전원 및 접지 단자 사이의 정확하고 특유의 미세 피치 접속을 촉진시킨다.

[0071] 샌드블라스팅, 레이저 제거 또는 다른 방법들과 같은 다른 기술들이 포일상 소성된 공지의 양호한 커패시터의 전극을 패턴화하여 개별화 커패시터를 형성하는 데 이용될 수 있다.

[0072] 복수의 개별화 커패시터를 형성 및 매립하는 다른 방법은 포일상 소성된 큰 커패시터를 포함하는 포일을 다이싱 하는 단계를 포함한다. 이전의 방법에서와 같이, 포일상 소성된 큰 커패시터가 테스트되고, 양호한 커패시터가 "공지의 양호한" 것으로 지정되며, 부가의 금속이 포일의 커패시터측에 추가되고, 포일상 소성된 큰 커패시터의 제1 전극을 형성하는 포일이 예칭에 의해 패턴화되어 각각의 제1 전극으로부터 복수의 제1 전극을 형성한다. 그 다음, (패턴화된 제1 전극을 갖는) 포일상 소성된 큰 커패시터를 포함하는 포일이 다이싱되어, 즉 절단되어 부품들을 형성한다. 불량의 큰 커패시터를 포함하는 부품들이 버려지고 공지의 양호한 부품들만 남는다.

[0073] 부품들은 하나의 공지의 양호한 큰 커패시터 또는 그의 어레이를 포함하며, 각각의 커패시터는 패턴화된 제1 전극을 갖는다. 이 때, 공지의 양호한 포일상 소성된 큰 커패시터로부터 도출되기 때문에 모든 부품들은 이제 공지의 양호한 것이다. 공지의 양호한 부품은 픽 앤 플레이스 기법에 의해 PWB의 빌드업층의 특정 위치에 배치될 수 있고 패턴화된 전극측의 라미네이션에 의해 빌드업층에 부착될 수 있다. 부품들이 상당히 크기 때문에(예를 들어, 1.5 cm × 1.5 cm), 픽 앤 플레이트 기법은 부품들을 쉽게 다룰 수 있고 배치 정밀도가 매우 높다.

[0074] 그 다음, 포일상 소성된 커패시터의 제2 전극을 포함하는 포일이 예칭에 의해 패턴화되어 포일 내에 포함된 각각의 제2 전극으로부터 복수의 제2 전극을 형성한다. 이는 복수의 개별화 커패시터를 형성하는 제1 및 제2 전극의 패턴화이다.

[0075] 다이싱 방법은 몇 가지 이점을 갖는다. 공지의 양호한 부품들로 다이싱하는 것은, 20 cm × 20 cm(8인치 × 8인치) 기판과 같은 큰 인쇄 배선 기판이 예를 들어 단지 하나 또는 몇 개의 IC를 갖고 하나 또는 몇 개의 특정 위치에 복수의 매립된 높은 커패시턴스 커패시터를 필요로 할 때, 특히 유용하다.

[0076] 다른 이점은 불량 커패시터를 포함하는 다이싱된 부품이 빌드업층에 배치되기 전에 버려질 수 있다는 것이다. 따라서, 공지의 양호한 부품만이 빌드업층에 배치되고 이어서 IC 단자에 접속되는 개별화 커패시터의 모든 전극이 공지의 양호한 커패시터로부터 도출된다.

[0077] 더욱이, 테스트는 포일상 소성된 커패시터의 "공지의 양호한" 품질뿐만 아니라 그의 품질의 척도인 커패시턴스 허용오차 또는 선택적으로 다른 전기적 특성도 판정한다. 이는 각각의 다이싱된 부품의 커패시턴스 허용오차도 알게 된다는 것을 의미한다. 따라서, 다이싱 방법은, 다이싱된 부품들을 빌드업층에 배치하기 전에, 다이싱된 부품이 목표값으로부터 예를 들어, 5%, 10% 또는 20%와 같은 커패시턴스 허용오차에 따라 분류될 수 있게 한다. 이는 일정 허용오차를 갖는 다이싱된 부품들을 빌드업층 내의 특정 위치에 정확하게 배치하는 것을 가능하게 하고, 이는 특정 위치 또는 특정 응용에 대한 커패시턴스를 맞춘다.

#### 개별화 커패시터를 PWB의 빌드업층에 포함

[0079] 이하는 정확하게 배치된 개별화 커패시터가 다수의 능동 전원 및 접지 단자를 갖는 IC의 요구에 따라 미세 피치를 가지면서 크기가 작게 되는 것을 용이하게 하는 방법을 사용하여 공지의 양호한 박막 포일상 소성된 큰 커패

시터로부터 도출된 복수의 개별화 커패시터를 PWB의 빌드업층에 포함시키는 것에 대한 설명이다.

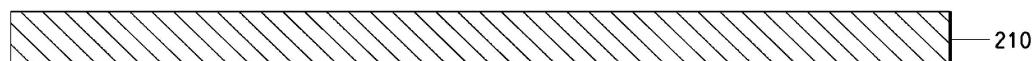

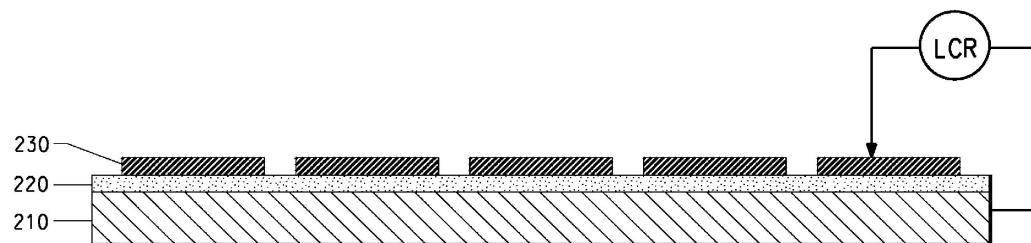

[0080] 도 3a는 개별화 커패시터를 인쇄 배선 기판의 빌드업층에 매립시키는 제1 단계의 측면도이다. 도 3a에서, 금 속 포일(210)이 제공된다. 포일(210)은 포일상 소성된 커패시터의 제1 전극이 될 것이다. 포일(210)은 본 산업 분야에서 일반적으로 입수가능한 유형일 수 있다. 예를 들어, 포일(210)은 구리 또는 그의 합금, 구리-인바-구리, 인바, 니켈, 니켈-코팅된 구리, 또는 박막 유전체의 소성 온도를 초과하는 용점을 갖는 다른 금속일 수 있다. 양호한 포일은 구리 또는 니켈을 주로 포함하는 포일을 포함한다. 포일(210)의 두께는, 예를 들어 1 내지 100 마이크로미터, 양호하게는 3 내지 75 마이크로미터, 가장 양호하게는 12 내지 36 마이크로미터의 범위에 있을 수 있다. 적합한 구리 포일의 예는 오크-미즈이(Oak-Mitsui)로부터 입수가능한 PLSP 등급 28.35 g(1 온스)(36 마이크로미터 두께) 구리 포일이다. 적합한 니켈 포일의 일례는 올포일즈(Allfoils)로부터 얻을 수 있는 니켈 포일 201이다.

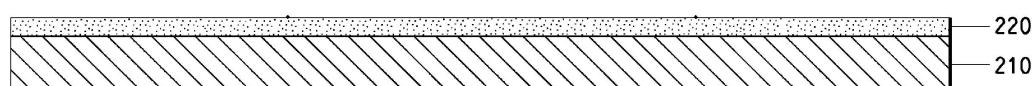

[0081] 도 3b에서, 커패시터 유전체 물질이 포일(210)에 중착되어 커패시터 유전체층(220)을 형성한다. 커패시터 유전체 물질은, 예를 들어 적절히 높은 유전 상수의 물질의 화학 용액으로 포일을 코팅함으로써 중착될 수 있다. 유전체 물질은 신뢰성 및 다른 원하는 특성을 달성하기 위해 도핑될 수 있다. 미국 특허 출원 제11/157894호 및 미국 특허 출원 공개 제2006-0287188-A1호가 본 명세서에 참고로 포함된다. 유전체를 중착하는 다른 방법은 스퍼터링 또는 화학 기상 증착 또는 이들의 조합을 포함한다.

[0082] 그 다음, 커패시터 유전체층(220)이 소성된다. 소성 온도는 하부 금속 포일의 용융점 및 원하는 미세구조 성장에 의존한다. 소성 온도의 범위는 유전체가 결정화하기 시작하는 온도 바로 위의 온도와 하부 금속 포일의 용융 온도 바로 아래의 온도 사이일 수 있다. 예를 들어, 유전체는 500 내지 700°C의 온도 범위에서 소성 동안에 결정화한다. 추가의 가열은 유전체를 고밀도화시켜 입자 성장을 촉진시킨다. 구리에 대한 적합한 상부 소성 온도는 대략 1050°C이고 니켈에 대해서는 1400°C일 수 있으며, 이는 각각의 용융점에 따른다. 따라서, 소성 온도의 범위는 대체로 700°C 내지 1400°C인 것이 적합하지만, 상기한 파라미터에 따라 이를 한계 밖으로 확장될 수 있다.

[0083] 금속 포일을 산화로부터 보호하기 위해 산소가 충분히 낮은 보호 또는 환원 분위기 하에서 소성이 행해진다. 특정 분위기가 온도 및 하부 금속 포일에 의존할 것이며, 공개 문헌[" F. D. Richardson and J.H.E. Jeffes, J. Iron Steel Inst., 160, 261 (1948)"]에 개시된 바와 같이 온도 계산 또는 다이어그램의 함수로서 산화물 형성의 표준 자유 에너지로부터 열역학적으로 도출될 수 있다. 예를 들어, 하부 금속 포일로서 구리를 사용하여, 700°C, 900°C 및 1050°C에서 소성하는 것은 각각 구리를 산화로부터 보호하기 위해 대략  $4 \times 10^{-11}$ ,  $3.7 \times 10^{-8}$ , 및  $1.6 \times 10^{-6}$  기압보다 작은 산소 분압(P02)을 필요로 할 것이다.

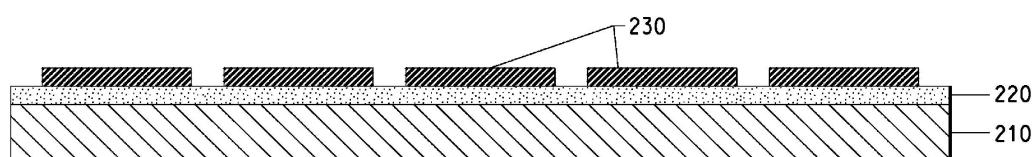

[0084] 도 3c에서, 예를 들어 스퍼터링 또는 다른 방법에 의해 제2 전극(230)이 소성된 유전체층(220) 상에 형성되어 포일상 소성된 커패시터(즉, 큰 커패시터)를 형성한다. 통상적으로 스퍼터링된 제2 전극은 대략 IC-제2 전극이 IC용으로 설계됨-와 동일한 크기, 예를 들어 변이 1.0 내지 3 cm이고 두께가 1 마이크로미터 미만일 것이며, 그의 금속은 구리일 것이지만, 어떠한 금속도 사용될 수 있다.

[0085] 큰 단일의 커패시터의 크기가 매립될 PWB의 크기와 근사할 때, 제2 전극층(230)의 면적은 일반적으로 인쇄 배선 기판의 면적보다 약간 작게 된다. 이는 부정확한 유전체 증착 또는 스퍼터링으로 인해 포일 유전체층과 전극층 사이의 임의의 어떠한 오정렬도 수용한다. 예를 들어, 인쇄 배선 기판이 20 mm × 20 mm인 경우, 제2 전극층(230)은 19 mm × 19 mm와 같이 약간 더 작을 수 있다.

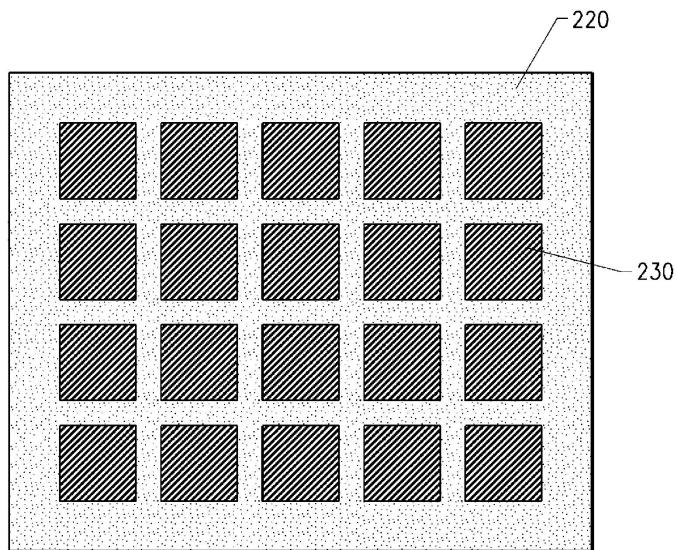

[0086] 도 3d는 도 3c의 단면도에 도시된 포일상 소성된 큰 커패시터의 평면도이다. 20개의 큰 커패시터가 도시되어 있고, 각각이 포일(210) 상의 유전체층(220) 상에 제2 전극(230)을 갖는다(포일은 100% 유전체로 덮여 있어서 도시되어 있지 않음). 커패시터 크기, 인쇄 배선 기판 치수 및 기판마다의 커패시터 위치에 따라, 임의 개수의 큰 커패시터가 포일(210) 상에 다양한 패턴으로 형성될 수 있으며, 이는 본 기술분야의 일반적인 기술이다.

[0087] 도 3e를 참조하면, 이 단계에서, 포일상 소성된 큰 커패시터가 커패시턴스를 위해 LCR 미터로 테스트될 수 있다. 테스트는 공지의 양호한 큰 커패시터의 위치를 식별한다. 예를 들어, 각각의 포일은 서브부품(subpart)의 그리드로 분할될 수 있고, 각각의 서브부품은 고유의 주소를 가져서, 각각의 큰 커패시터의 위치를 고유하게 식별한다. 테스트된 큰 커패시터가 단락되거나 달리 결함이 있는 경우, 그의 위치를 알고 있기 때문에, IC 및 SMT 부품을 갖는 최종 조립체가 제거될 수 있다. 포일 상의 큰 커패시터의 수율이 낮은 경우, 포일상 소성된 큰 커패시터를 포함하는 포일이 버려질 수 있다. 이는 최종 제품의 높은 수율을 가능하게 한다.

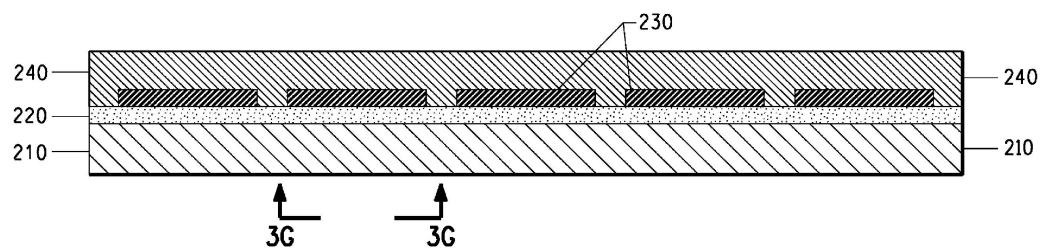

- [0088] 도 3f에서, 부가의 금속이 포일상 소성된 큰 커패시터 및 제2 전극(230)을 포함하는 포일의 면에 추가되어 금속 층(240)을 형성한다. 이는 시드(seed) 금속층(일반적으로, 구리)을 스퍼터링하고 그 다음에 원하는 두께로 추가의 구리로 도금함으로써 달성을 수 있다. 부가의 금속을 추가하여 층(240)을 형성하는 다른 방법들이 또한 실시될 수 있다. 금속층(240)은 차후의 처리를 수용하기 위해 부가된 강도를 구조체에 제공하도록 설계되어 있다. 층(240)의 두께는 15 내지 35 마이크로미터 또는 4 내지 10 마이크로미터 또는 4 내지 30 마이크로미터일 수 있다. 명확함을 위해, 도면들이 제2 전극(230)을 계속 도시하고 있지만, 실제로는 제2 전극(230)은 이제 층(240)에 포함되어 있다.

- [0089] 포토레지스트가 이제 포일(210)에 도포된다. 캐리어 막(carrier film)도 또한 층(240)에 도포될 수 있다. 캐리어 막은 포일에 부가의 강도를 제공하며 층(240)을 차후의 취급 및 처리로부터 보호하고, 또한 에칭 레지스트(etch resist)로서 역할을 할 것이다. 포일(210)에 도포된 포토레지스트는 이미지 형성되어 현상되고 포일(210)이 에칭되며, 나머지 포토레지스트는 박리된다. 캐리어 막에 의해 보호되어, 층(240)은 에칭되지 않은 채로 있다.

- [0090] 도 3g는 도 3f의 에칭된 물품의 한 부분을 확대하여 나타낸 것으로서, 공지의 양호한 커패시터의 단지 하나의 큰 전극(230)이 도시되어 있다. 에칭은 포일(210)을 패턴화하고 다수의 개별화 커패시터의 다수의 접지 (제1) 전극으로서 역할을 할 공통의 제1 전극(211)을 생성한다. 에칭은 또한 제2 (상부) 전극 및 상부 신호 패드에 비아 접속을 위해 제1 전극(211)에 안티패드(또는 홀)(245)를 생성한다. 각각의 공지의 양호한 큰 커패시터는 원래의 제2 전극(230)의 풋프린트 (또는 영역) 내에 그리고 제1 전극(211) 내에 IC마다 요구된 개수의 안티패드(245)를 갖는다. 제1 전극(211)은 제2 전극(230)보다 약간 더 크게 제조될 수 있지만, 공지의 양호한 커패시터 전극의 공통 영역이 제2 전극(230)에 의해 한정된다.

- [0091] 도 3h는 도 3g의 패턴화된 포일(210)의 하부면의 평면도를 도시한다. 공지의 양호한 커패시터 제2 전극(230)의 원래 풋프린트 내에 그리고 제1 전극(211) 내에 제조된 6개의 안티패드(245)가 여기에 도시되어 있다. 제2 전극(230)의 치수 내에 그리고 공지의 양호한 큰 커패시터의 전극(211) 내에 특징부(245)를 제조함으로써 공지의 양호한 개별화 커패시터가 얻어질 것이 보장된다. 여기서, 전극(211)은 3개의 개별화 커패시터에 대한 3개의 접지 전극으로서 기능을 하는 공통 전극이지만, 개개의 (분리된) 접지 전극도 또한 생성될 수 있다.

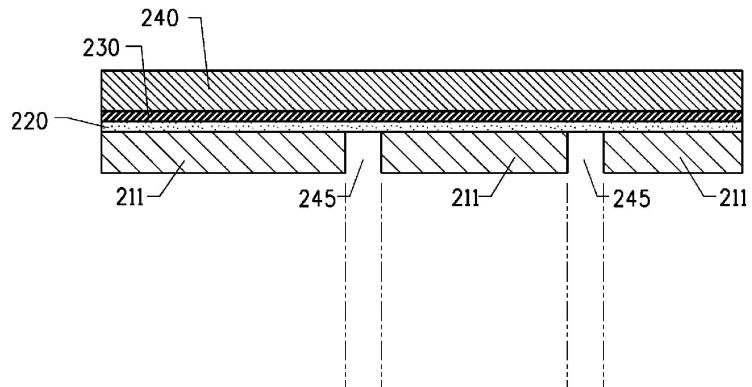

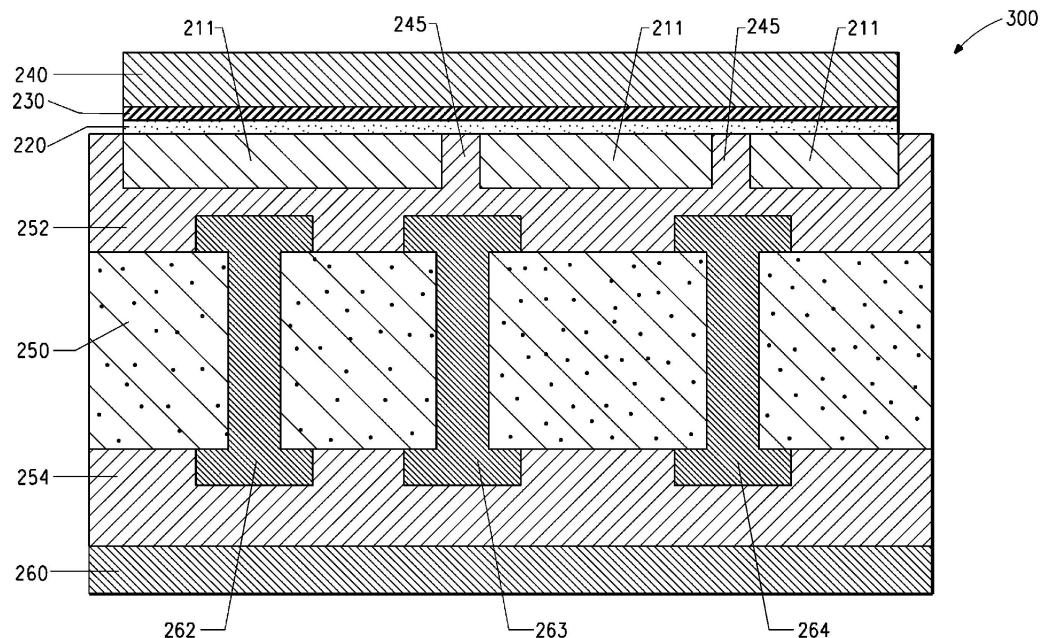

- [0092] 도 4a는 안티패드(245)를 갖는 제1 공통 접지 전극(211)이 인쇄 배선 기판의 빌드업층(252)에 라미네이팅되어 구조체(300)를 형성하는 것을 단면도로 도시한다. 구조체(300)는 관통 홀 비아(262, 263, 264)를 포함하는 코어 라미네이트(250) 및 라미네이트(250)의 양 면에 있는 적어도 하나의 빌드업층(252, 254)을 포함한다. 구리 포일(260)은 또한 전형적으로 대칭을 제공함으로써 구조체를 더 균형있게 하는 빌드업층(254)에 라미네이팅되어 있다. 포일(260)은, 커패시터를 포함하지 않고 커패시터를 포함하려고 하지 않는 포일일 수 있다. 이전에 층(240)에 도포되었을 수 있는 어떠한 캐리어 막도 제거된다. 명확함을 위해, 구조체(300)가 층(240) 내에 공지의 양호한 커패시터 제2 전극(230)의 위치를 보여줌으로써, 층(240)의 차후의 패턴화가 어떻게 제2 전극(230)의 풋프린트 내에 존재하는 특징부를 형성하는지를 관찰할 수 있다. 완성된 인쇄 회로 기판의 크기는 제1 전극(211)의 영역보다 약간 또는 상당히 더 클 수 있다.

- [0093] 빌드업층은 대칭으로 배열될 수 있거나 또는 라미네이트 코어 둘레에 배열되지 않을 수 있다. 임의 개수의 빌드업층이 적용될 수 있고, 커패시터를 포함하는 임의 개수의 포일이 빌드업층 내에 포함될 수 있다. 빌드업층은 유전체막으로서 라미네이팅될 수 있거나, 액체로서 스핀 코팅 또는 커튼 코팅될 수 있거나, 금속층 (예를 들어, 구리 포일) 상에 코팅된 수지로서 또는 강화 프리프레그(reinforced prepreg), 예를 들어 B-단계 수지로서 도포될 수 있다.

- [0094] 적합한 라미네이션 조건은 94.82 kPa(28 inHg)까지 배기된 진공 챔버에서 1시간 동안 1434.1 kPa(208 psig)에서 185°C 일 수 있다. 실리콘 러버 프레스 패드 및 평탄한 PTFE 충전된 유리 릴리스 시트는 빌드업층으로부터의 에폭시가 라미네이션 플레이트를 서로 접합하지 못하도록 포일(240, 260)과 접촉할 수 있다. 생성된 구조체(300)가 일면 상의 포일(240) 및 다른 면 상의 포일(260)로 싸여 있다.

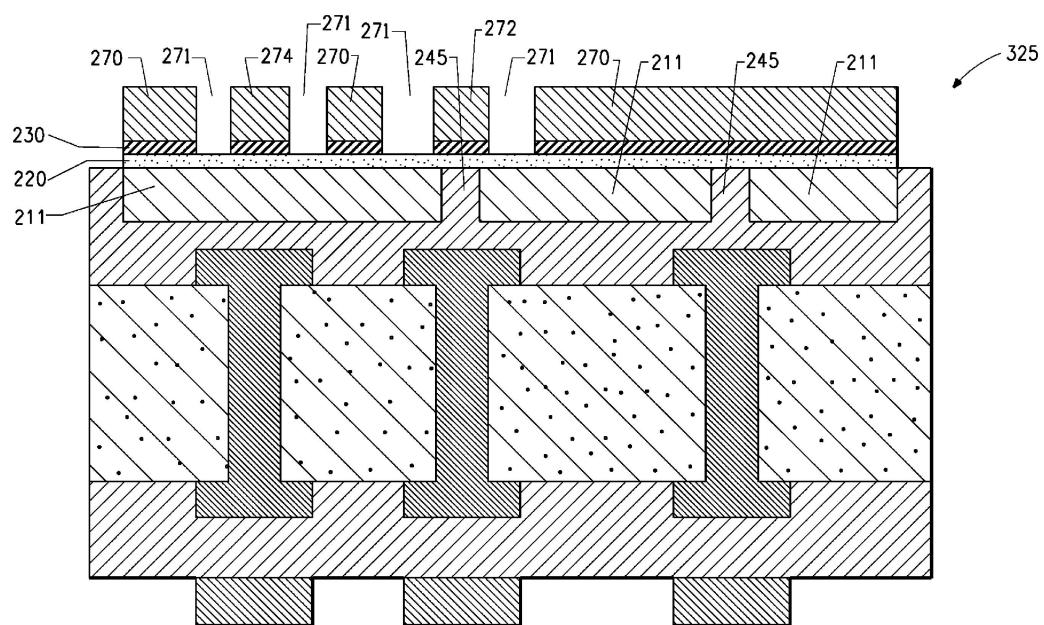

- [0095] 라미네이션 후에, 포토레지스트가 제2 전극(230)을 포함하는 포일(240) 및 포일(260)에 도포된다. 포토레지스트는 이미지화 및 현상되고, 금속 포일이 에칭된다. 포토레지스트가 표준 인쇄 배선 기판 처리 조건을 사용하여 박리되어 도 4b의 물품(325)을 형성한다. 에칭은 포일(240)을 패턴화하고 포일에 복수의 원형 트렌치(271)를 형성한다. 에칭은 또한 다수의 개별화 커패시터의 다수의 전원 전극으로서 기능을 하는 공통의 제2 전극(270)을 형성한다. 에칭은 또한 신호 접속을 위한 구리 패드(272) 및 하부 전극에 비아 접속을 위한 패드(274)를 생성한다. 특징부(270, 271, 272, 274)는 공지의 양호한 포일상 소성된 큰 커패시터의 원래의 제2 전극

(230)의 풋프린트 내에 있으며, 그에 의해 모든 개별화 커패시터가 공지의 양호한 큰 커패시터로 형성되는 것을 보장한다. 예청에 의해 포일(240)을 패턴화하여 복수의 개별화 커패시터의 형성을 완료한다.

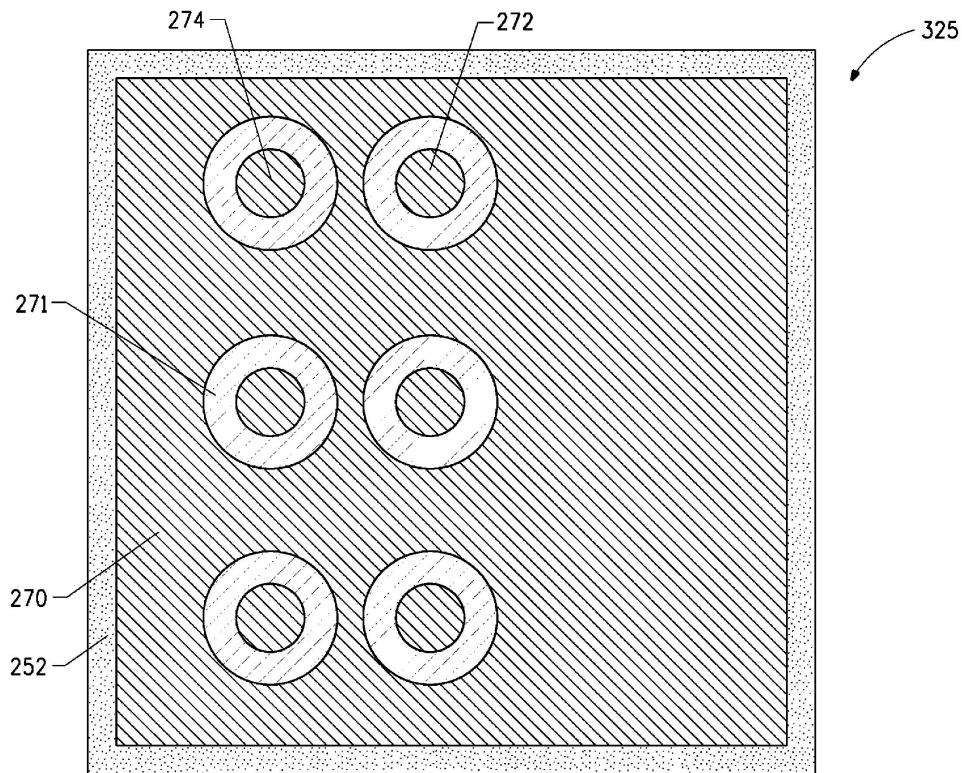

[0096] 도 4c는 도 3h에 도시된 패턴화된 포일(210)의 설계와 일치하는 6개의 원형 트렌치를 갖는 구조체(325)의 상부 평면도를 도시한다. 여기에 도시된 원형 트렌치의 개수는 예시적인 것이며, IC가 도시된 것보다 더 많은 개별화 커패시터를 필요로 하는 경우, 포일(210)은 더 많은 앤티패드로 패턴화될 수 있고, 일치하는 개수의 원형 트렌치가 포일(240)에서 원래의 제2 전극(230)의 풋프린트 내에 형성될 수 있다. 여기서, 전극(270)은 3개의 개별화 커패시터에 대한 3개의 전원 전극으로서 기능을 하는 공통 전극이다. 그러나, 개개의 (분리된) 전원 전극은 포일(240)로부터 패턴화될 수 있다.

[0097] 도 4d는 도 4b의 물품(325)을 확대한 것으로서, 상부 부분만이 도시되어 있다. 미세 비아(microvia)(280, 285)가 각각 전극(270) 및 패드(274)를 통해 형성되고 상부 전극(270) 및 하부 전극(211)을 라미네이팅된 코어의 관통 홀 비아(264, 262)에 각각 상호접속시키도록 도금된다. 미세 비아(290)가 또한 전극(270, 211)과 절연되어 있는 패드(272)를 통해 형성되고, 신호 패드(272)를 라미네이팅된 코어의 관통 홀 비아(263)에 상호접속시키기 위해 도금된다. 여기에 도시된 바와 같은 설계는 지지되지 않은 유전체층(220)을 갖지 않으며 구조적 이유로 바람직하지만 다른 설계들도 사용될 수 있다. 미세 비아(280, 285, 290)는 레이저 천공에 의해, 포토리소그래피에 의해, 또는 제어된 깊이의 기계적 천공에 의해 형성될 수 있다. 미세 비아 홀-벽의 초기 금속화는 표면에 증착된 촉매, 예를 들어 팔라듐으로 활성화될 수 있는 금속 시드층, 예를 들어 무전해 동을 증착함으로써 달성된다. 개별화 커패시터를 PWB 내에 더 깊이 포함시키기 위해 부가의 빌드업층이 적용될 수 있고, 마지막으로 외부 회로가 또한, 예를 들어 니켈 및 금으로 도금되어 PWB를 완성할 수 있다.

[0098] 도 3 및 4에 도시된 단계들의 순서가 불변은 아니며 조정될 수 있다. 예를 들어, 미세 비아(280, 285, 290)는 포일(240)을 패턴화하기 전에 형성될 수 있다.

#### 공지의 양호한 부품을 형성하는 다이싱

[0100] 도 5a 내지 도 5g는 공지의 양호한 큰 커패시터로부터 도출된 복수의 박막 개별화 커패시터를 인쇄 배선 기판의 빌드업층에 포함시키는 대안적인 방법을 나타낸다. 본질적으로, 이 방법은 포일상 소성된 커패시터를 포함하는 포일을 하나 이상의 큰 커패시터를 포함하는 부품들로 다이싱하고 공지의 양호한 포일상 소성된 큰 커패시터만을 PWB의 빌드업층에 부착한다. 그 다음, 제2 전극이 예청에 의해 복수의 전극으로 패턴화되고 그에 의해 복수의 개별화 커패시터를 형성한다.

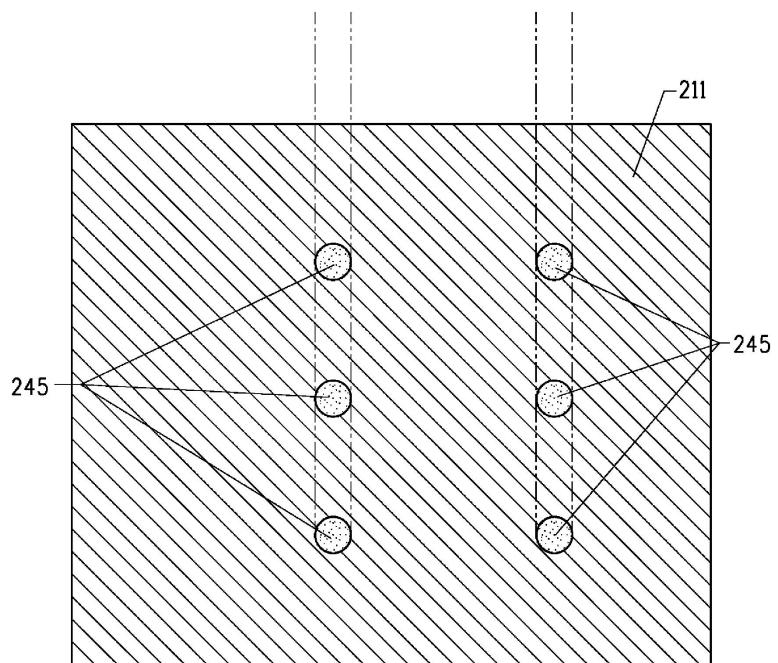

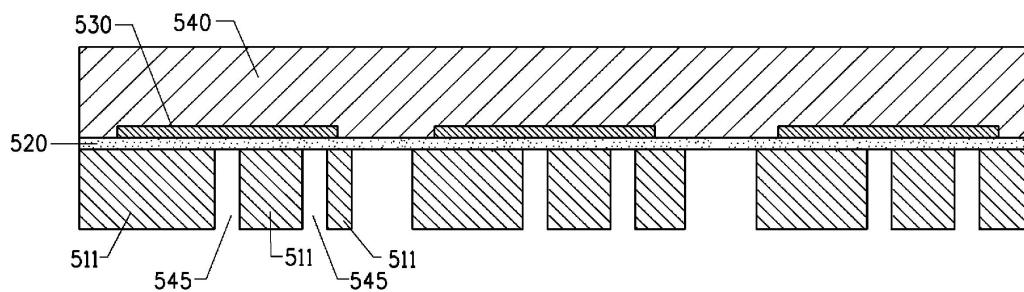

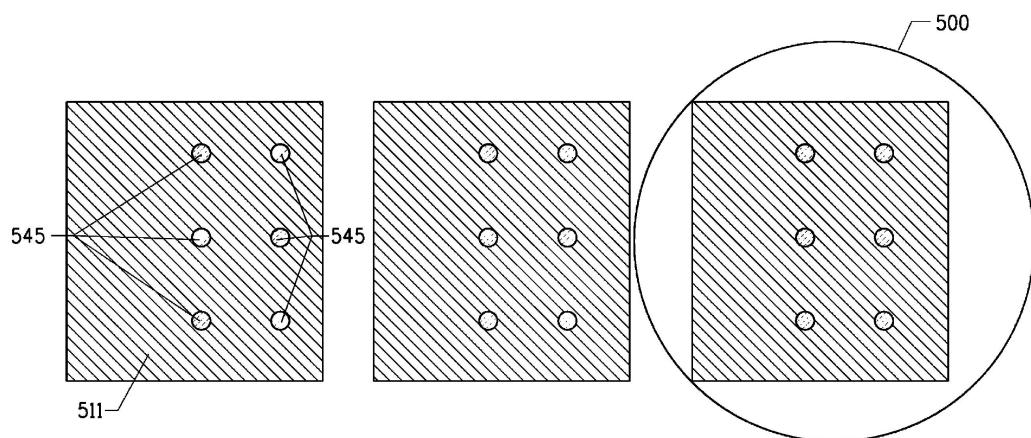

[0101] 도 5a는 구리 포일 상에 형성된 유전체층(520) 상의 금속층(540) 내에 3개의 포일상 소성된 제2 전극(530)을 갖는 것을 제외하고는 도 3g의 물품을 나타낸 것이다. 포일은 패턴화되어 제1 전극(511) 및 앤티패드(545)를 형성하였다.

[0102] 도 5a의 구조체를 다이싱하여 도 5b의 측면도 및 도 5c의 평면도에 도시된 바와 같이 개개의 다이싱된 부품(500)을 생성한다. 도 5b는 하나의 포일상 소성된 큰 커패시터를 갖는 부품(500)을 형성하는 다이싱을 도시하지만, 대안적인 방법이 포일을 하나 초파의 커패시터를 포함하는 부품들로 다이싱할 수 있다. 이러한 대안의 방법은 하나 초파의 IC가 PWB에 부착될 때 유용하고, 각각의 큰 커패시터는 하나의 IC에 도움을 제공할 것이다. 다이싱은 전형적으로 다이어몬드 톱으로 수행되지만, 임의의 적합한 소자 또는 방법이 채용될 수 있다.

[0103] 다이싱 후에, 양호하지 않은 것으로 테스트된 커패시터를 포함하는 이들 부품이 식별되고 폐기된다. 공지의 양호한 큰 커패시터를 포함하는 이들 부품은 그들의 이전의 테스트된 커패시턴스 데이터에 따라 그들 각각의 커패시터 허용오차 내로 분류될 수 있다.

[0104] 도 5c는 제1 전극(511)에 형성된 단지 6개의 앤티패드(545)만을 도시하고 있지만, IC 커패시터 요구에 따라, 임의 개수의 이들 특징부가 제1 전극(511) 내에 그리고 원래의 제2 전극(530)의 풋프린트 내에 형성될 수 있다(도 5a). 도 5b 및 도 5c는 3개의 다이싱된 부품들만을 도시하고 있지만, 포일 상의 포일상 소성된 커패시터의 개수 및 부품마다의 원하는 커패시터의 개수에 따라 포일상 소성된 큰 커패시터를 포함하는 포일 구조체가 임의 개수의 부품으로 다이싱될 수 있다.

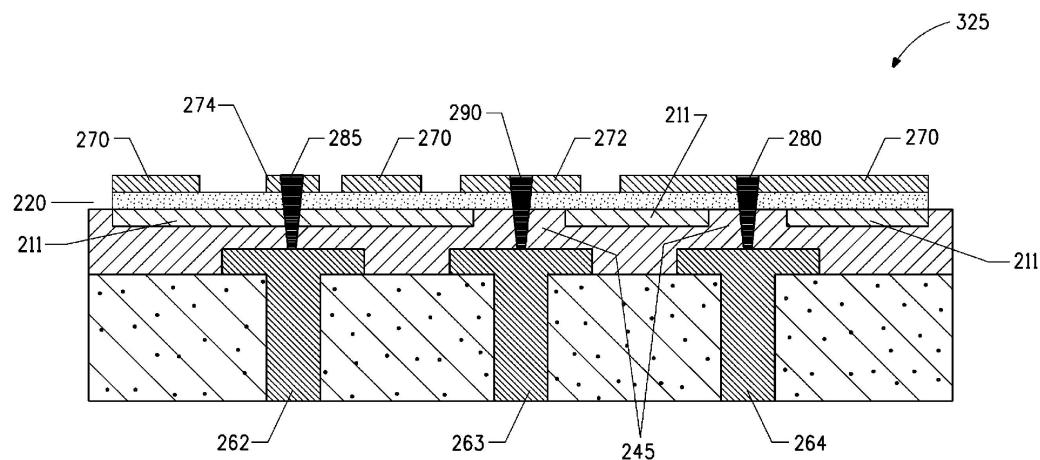

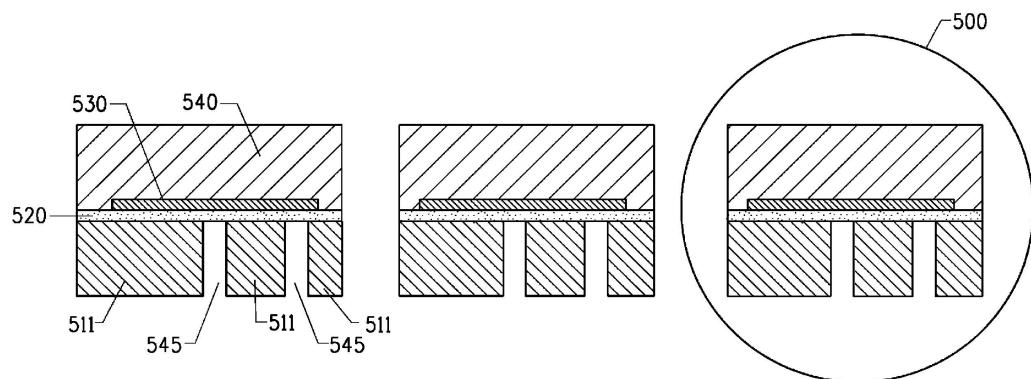

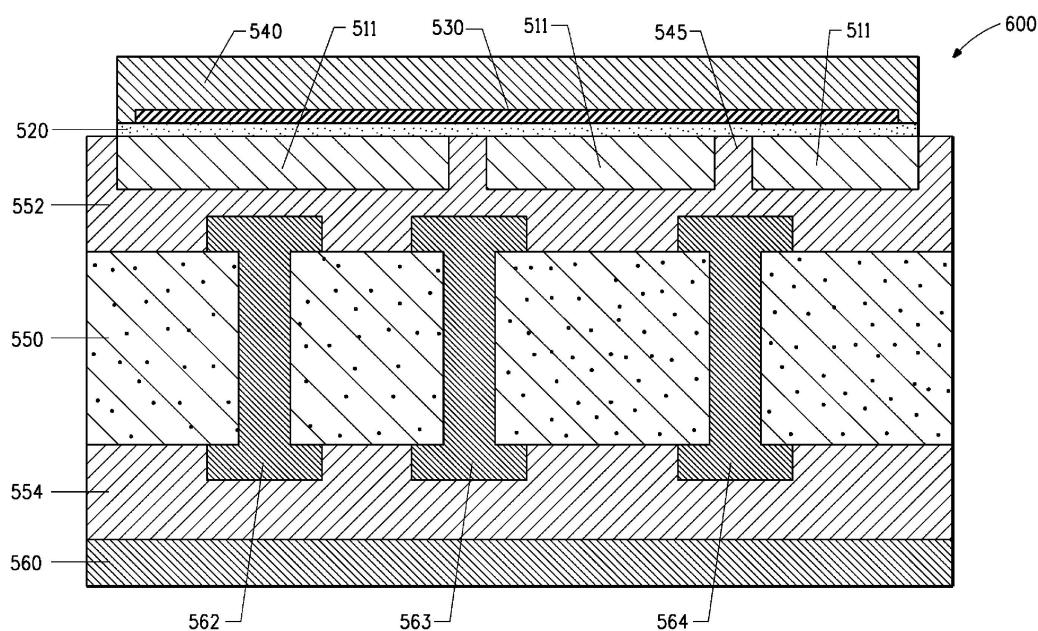

[0105] 도 5d는 PWB의 빌드업층(552) 내에 포함된 공지의 양호한 부품(500)(도 5c)을 도시한다. 이는 원하는 위치에 꽂 앤 플레이스 기법으로 그리고 그 다음에 부품을 그의 패턴화된 제1 전극으로부터 빌드업층으로 라미네이팅하여 구조체(600)를 생성함으로써 수행된다. 앞서 설명한 바와 같이 라미네이션의 일어난다. 인쇄 배선 기판 구조체(600)는 관통 홀 비아(562, 563, 564)를 포함하는 코어 라미네이트(550) 및 코어 라미네이트(550)의 어느

한 면에 있는 적어도 하나의 빌드업층(552, 554)을 포함한다.

[0106] 통상적으로, 대칭을 제공함으로써 구조체를 더 균형있게 하기 위해 구리 포일(560)이 또한 빌드업층(554)에 라미네이팅된다. 이전에 층(540)에 적용되었을 수 있는 캐리어 막이 또한 제거된다. 도 5d가 552 상에 배치되고 인쇄 배선 기판 내에 포함된 단지 하나의 개별화 커패시터를 도시하고 있지만, 인쇄 배선 기판의 회로 설계 요구 및 크기에 따라 임의 개수의 부품들이 인쇄 배선 기판의 빌드업층(552) 상의 임의의 특정 위치에 배치될 수 있다.

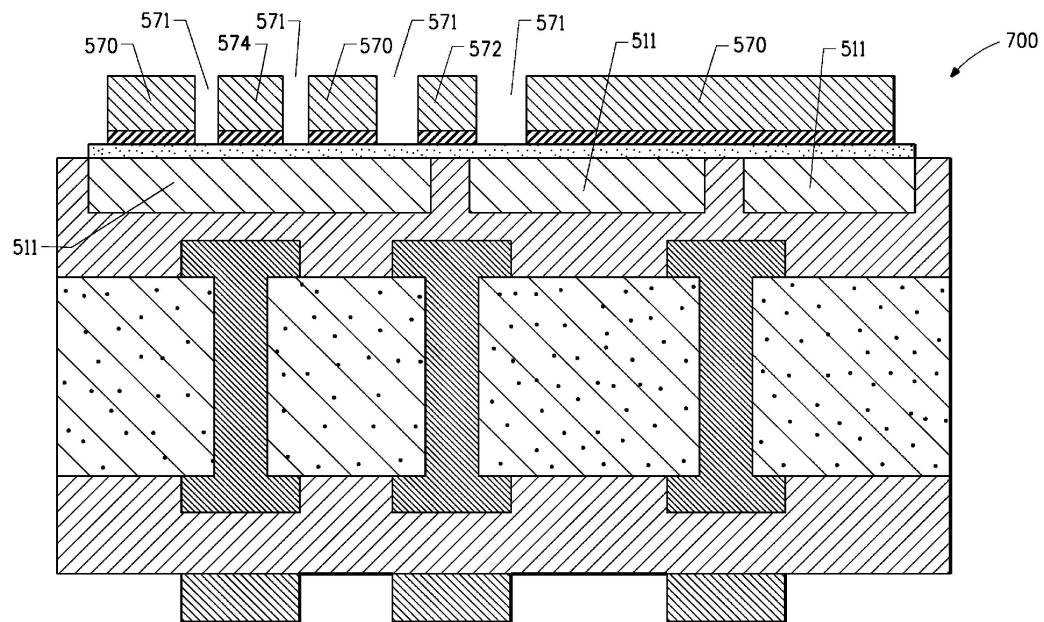

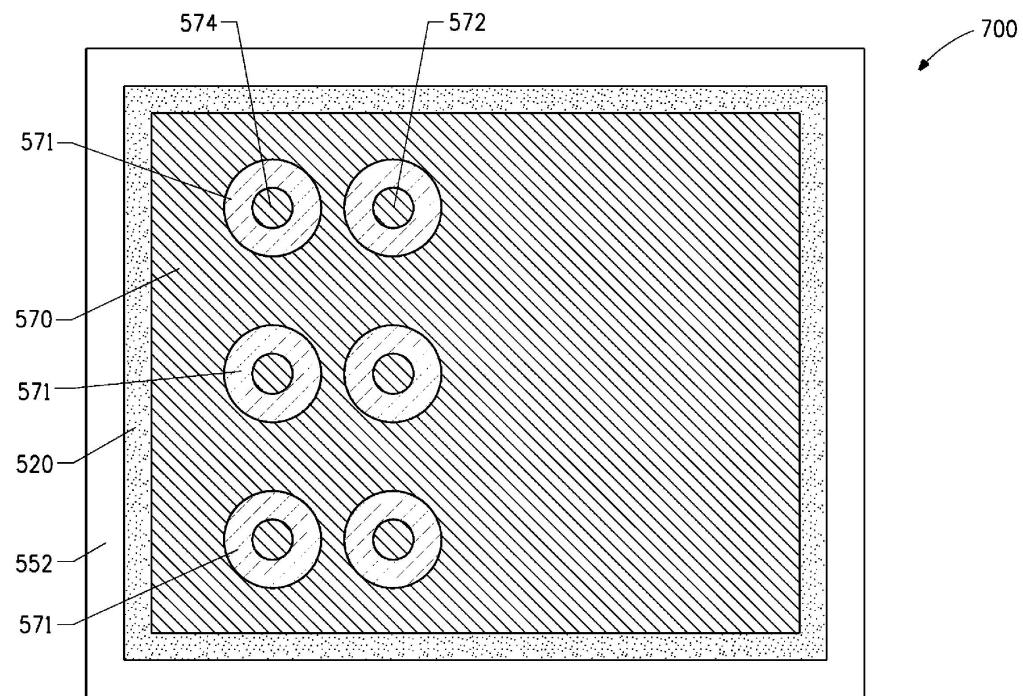

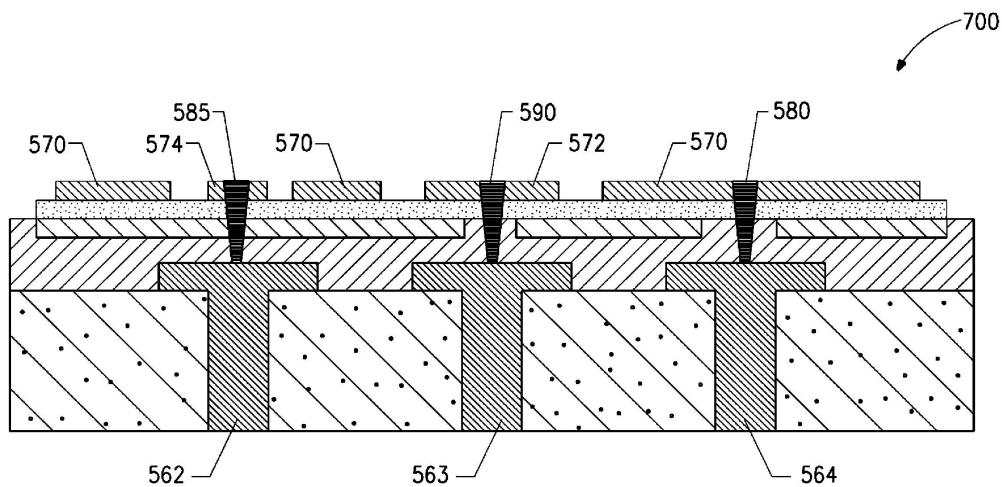

[0107] 라미네이션 후에, 포토레지스트가 포일(540, 560)에 도포된다. 포토레지스트는 이미지화 및 현상되고, 금속 포일이 에칭된다. 포토레지스트가 표준 인쇄 배선 처리 조건을 사용하여 박리되어 도 5e의 물품(700)을 형성한다. 에칭은 포일을 패턴화하고 복수의 원형 트렌치(571), 상부 공통 (제2) 전극(570), 구리 신호 패드(572) 및 하부 전극에 접속하기 위한 구리 패드(574)를 형성한다. 특징부(570, 571, 572, 574)는, 공지의 양호한 부품으로부터 도출된 모든 개별화 커패시터가 양호한 것을 확실하게 하기 위해, 공지의 양호한 부품의 원래의 제2 전극(530)(도 5d)의 풋프린트 내에 있다. 포일(540)(도 5d)의 패턴화로 복수의 개별화 커패시터의 형성이 완료된다. 도 5f는 6개의 원형 트렌치를 갖는 구조체(700)의 상부 평면도를 도시하는 것으로서, 이 개수는 도 5c에 도시된 패턴화된 포일의 설계와 일치한다. 그러나, IC가 더 많은 개별화 커패시터를 필요로 하는 경우, 원래의 제2 전극(530)의 풋프린트 내에 더 많은 안티패드 및 원형 트렌치가 있도록 포일이 패턴화될 수 있다. 도시된 바와 같이, 전극(570)은 3개의 개별화 커패시터에 대한 3개의 전원 전극으로서 기능을 하는 공통 전극이지만, 개개의 (분리된) 전원 전극이 생성될 수 있다.

[0108] 도 5g는 도 5e의 상부 부분을 확대하여 도시한 것이다. 미세 비아(580, 585)가 형성되고 상부 및 하부 전극을 각각 라미네이팅된 코어의 적절한 관통 홀 비아(564, 562)에 상호접속시키기 위해 도금된다. 미세 비아(590)가 또한 형성되고 신호 패드(572)를 라미네이팅된 코어의 적절한 관통 홀(563)에 상호접속시키기 위해 도금된다. 이전의 예에서와 같이, 이러한 설계에서는 지지되지 않는 유전체가 존재하지 않는다. 미세 비아(580, 585, 590)는 레이저 천공에 의해, 포토리소그래피에 의해, 또는 제어된 깊이의 기계적 천공에 의해 형성될 수 있다. 미세 비아 홀-벽의 초기 금속화는 금속 시드 층, 예를 들어 무전해 동을 증착함으로써 달성된다. 시드층 증착은 표면 상에 증착된 촉매에 의해 활성화될 수 있으며, 예를 들어 일 실시 형태에서, 팔라듐이 사용될 수 있다. 외부 회로가 또한, 예를 들어 나켈 및 금으로 이 때 도금되어 물품을 완성할 수 있다. 앞서 설명한 바와 같이, 미세 비아(580, 585, 590)를 형성하는 공정이 포일(540)을 패턴화하는 단계보다 선행할 수 있다.

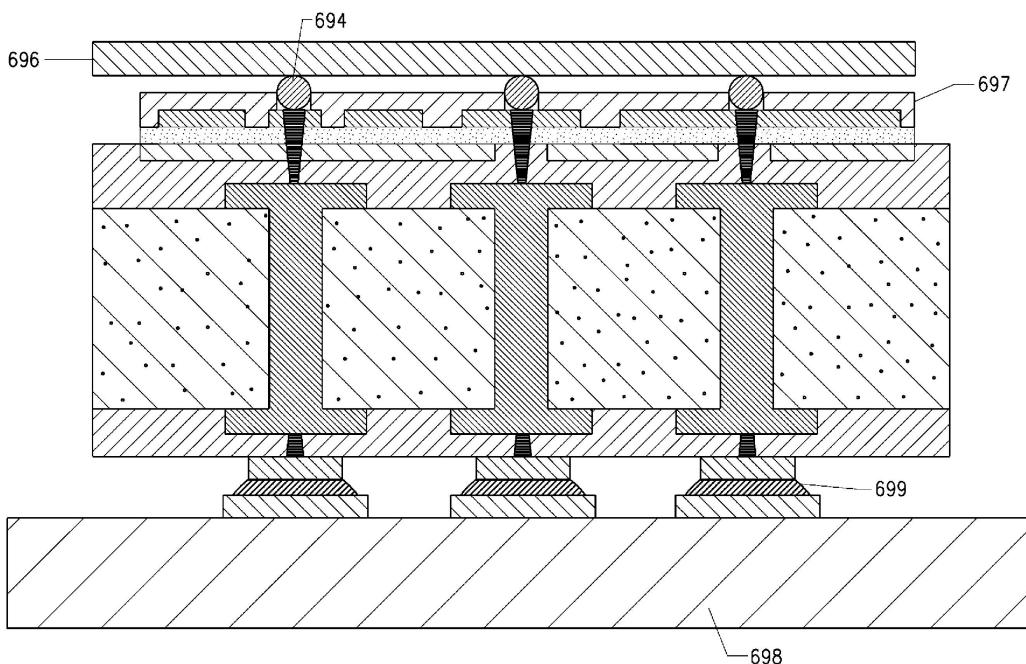

[0109] 도 4d 및 도 5g의 인쇄 회로 기판은 플립칩 IC의 범프에 접속될 수 있고 인쇄 배선 마더보드에 접속될 수 있다. 도 6은 박막 커패시터가 플립칩 IC에 접속된 빌드업층에 매립된 인쇄 회로 기판의 단면도를 나타낸 것이다. 도 4d 및 도 5g의 인쇄 회로 기판은 PWB의 외부 금속 표면을 보호하고 범프(694)의 접속 영역을 한정하기 위해 유기 커버 코팅(697)으로 마무리될 수 있다. 인쇄 배선 기판은 대략 IC와 동일한 크기이며, 그에 의해 모든 개별화 커패시터가 IC의 치수 내에 있다. IC의 신호 단자가 코어에 상호접속되어 있는 절연된 패드에 접속되어 있다. 반도체의 전원 단자는 개별화 커패시터의 전극에 직접 접속되고, 플립칩 IC의 접지 단자는 다른 전극에 직접 접속되어 있다. 플립칩 IC(696)의 범프(694)를 PWB에 접속시키는 것은 일반적으로 고온 납땜 단계에서 달성된다. 그 다음, PWB는 저온 납땜 단계에서 납땜 접합(699)을 통해 인쇄 배선 마더보드(698)에 접속된다.

#### 무코어 변형

[0111] 더욱이, 이들 방법은, 코어 구조체가 생성되지 않는, 도 3, 도 4 및 도 5에 도시된 단계들의 변형을 포함한다. 구체적으로, 빌드업층(들)이라고도 하는 외부층(들)에 박막 커패시터를 포함하는 구조체는 둘레에 외부층들이 순차적으로 추가되어 있는 코어로서 구성될 필요가 없다. 오히려, 이는 "무코어" 구조체로서 형성될 수 있으며, 이는 동시에 또는 공동으로 개개의 층들을 별별로 회로화함으로써 제조될 수 있다. 다시 말하면, 개개의 층들을 단일 라미네이션 단계에서 다층 구조체 내에 라미네이팅함으로써 또는 순차적인 단계들에서 하나의 빌드업층을 이전의 빌드업층의 상부에 배치함으로써 무코어 구조체가 형성될 수 있다.

[0112] 별별로 형성된 "무코어" 구조체의 한 가지 이러한 예가 ALIVH(Any Layer Interstitial Via Hole) 공정(마쓰시다(Matsushita)를 통해 이용가능함)이다. ALIVH 공정은 또한 박막 평면 커패시터를 포함시킬 수 있다. 별별로 형성된 "무코어" 구조체의 다른 예들은 NMBI(Neo Manhattan Bump Interconnection) (노스 코포레이션(North Corp.)) 및 PALAP(Patterned Prepreg Lay-up Process)(덴소 코포레이션(Denso Corp.))를 포함한다. 순차적으로 형성된 무코어 구조체의 예는 B<sup>2</sup>잇(it) ⑧ 공정(도시바 코포레이션(Toshiba Corporation)을 통해

이용가능함) 및 FVSS 공정(이비덴 코포레이션(Ibiden Corp.)), 즉 "자유 비아 스택업 구조체(free via stacked-up structure)"를 포함하며, 여기서 평면 커판시터가 유사한 방식으로 포함될 수 있다.

[0113] "무코어 구조체"의 이점은 모든 층에 미세 비아가 존재한다는 것이다. 이는 엇갈려서 적층된 미세 비아들의 조합을 사용하여 최단 가능 경로에 의해 서로 상이한 층 상의 2개의 점 사이에 배선(즉, 상호접속)을 가능하게 한다. 이와 달리, 코어 구조체는 코어 내의 금속층들을 접속시키는 도금 관통 홀(PTH)을 갖는다. PTH는 미세 비아보다 큰 직경의 홀을 가지며 주어진 상호접속에 대해 미세 비아보다 더 많은 공간을 필요로 한다. 따라서, 이들은 미세 비아의 높은 배선 밀도를 달성할 수 없다. 더욱이, 예를 들어 4개의 금속층을 갖는 코어 구조체에서, 금속층 1과 2 사이의 접속은 PTH가 4개의 층 모두를 통해 전공되어야 할 필요가 있으며, 이는 접속되지 않은 층들의 실면적을 낭비한다. 더욱이, 층 3 및 4에 대한 불필요한 금속 접속, 소위 "비아 스터브(via stub)"가 바람직하지 않은 기생 전기 효과를 생성한다.

[0114] 막막 커판시터를 갖는 인쇄 배선 기판이 반도체 소자보다 면적이 더 큰 경우, 저항과 같은 부가의 수동 부품이 인쇄 배선 기판의 표면에 추가되어 매립된 커판시터에 의해 제공되지 않는 기능들을 제공할 수 있다.

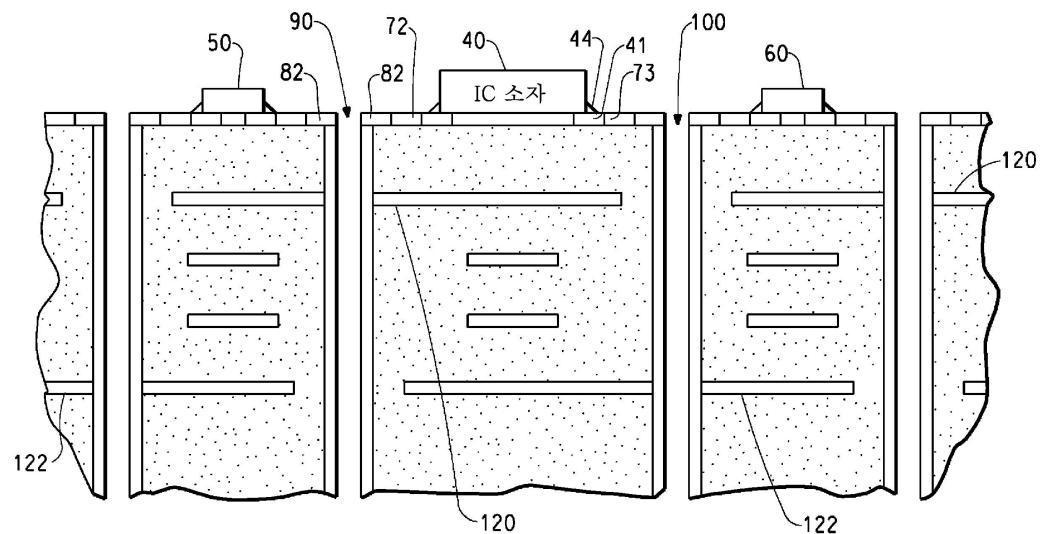

#### 실시예 1

[0116] 표 1은 도 7의 빌드업 반도체 인쇄 배선 기판 구조체 내의 상이한 위치에 배치된 5개의 커판시터에 대한 비아 길이(단위: 마이크로미터)의 함수로서 관찰되는 비아 인덕턴스 데이터를 나타낸다. 비아 길이는 각각의 커판시터와 IC의 단자들 사이의 접속 길이이고 마이크로미터로 측정된다. 층 비아 인덕턴스는 피코헨리[pH]로 측정하였다. PWB에 5개의 상이한 위치에 배치된 2 평방㎟ 커판시터를 갖는 테스트 비이클(test vehicle) 상의 회로 측정으로부터 인덕턴스 데이터를 얻었다.

#### 표 1

| 비아 길이의 함수인 비아 인덕턴스 |                       |                |

|--------------------|-----------------------|----------------|

| 케이스 번호             | 비아 길이 - $\mu\text{m}$ | 총 비아 인덕턴스 - pH |

| 1                  | 38                    | 6              |

| 2                  | 76                    | 19.74          |

| 3                  | 171                   | 70.6           |

| 4                  | 376                   | 123.56         |

| 5                  | 752                   | 319.48         |

[0117]

[0118] 도 7의 구조체는 통상 2/4/2 구성이라고 하는 코어층 및 양면 빌드업층을 갖는다. 이는 커판시터의 위치를 명확히 나타내기에는 불완전한 (미세 비아, 범프 등이 없음) 것으로 도시되어 있다. 5개의 커판시터 각각의 위치가 케이스 1 내지 5로 지정되어 있다. 케이스 1에서, 커판시터는 반도체 소자에 가장 가까운 상부 2개의 빌드업층 사이에 배치되고, 케이스 2에서 커판시터는 코어 라미네이트의 상부에 배치되며, 케이스 3에서 커판시터는 코어 BT 라미네이트 내부  $100 \mu\text{m}$ 로 배치되고, 케이스 4에서 커판시터는 코어 라미네이트의 중간에 배치되며, 케이스 5에서 커판시터는 하부 빌드업층 상의 구조체의 하부에 배치된다. 모든 케이스에서, 미세 비아의 직경은  $100 \mu\text{m}$ 였고, 이들 사이의 간격은  $300 \mu\text{m}$ 였다.

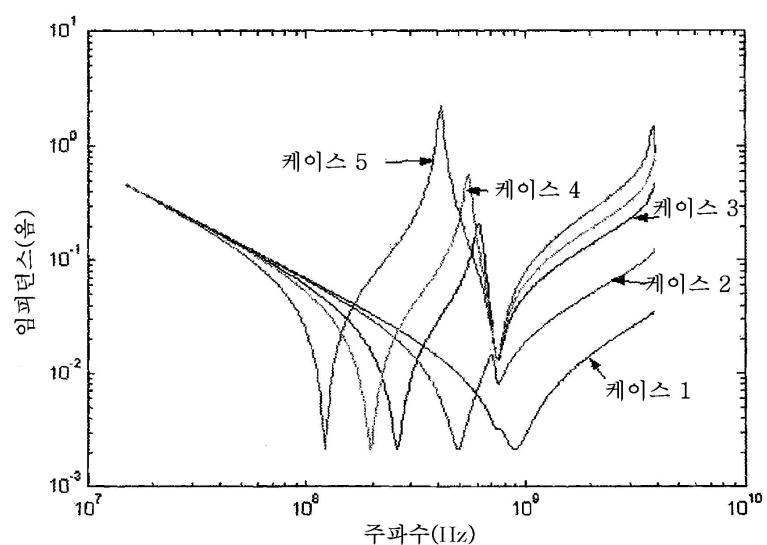

[0119] 이들 인덕턴스 값 및 길이를 사용하여, 임피던스 감소와 다이로부터의 커판시터 거리 사이의 관계를 보여주기 위해 시뮬레이션을 수행하였다. 이 시뮬레이션은 5개의 케이스에 대해 다이 바로 아래에 배치된 2개의 2 평방㎟의 커판시터에 기초하였다. 시뮬레이션에 사용된 커판시터 특성들은 커판시턴스가  $5.31 \text{ pF}$ (피코페러드)였고, 등가 직렬 저항이  $8.59 \text{ 밀리옴}$ 이었으며, 커판시터의 등가 직렬 인덕턴스가  $27.11 \text{ pH}$ (피코헨리)였다.

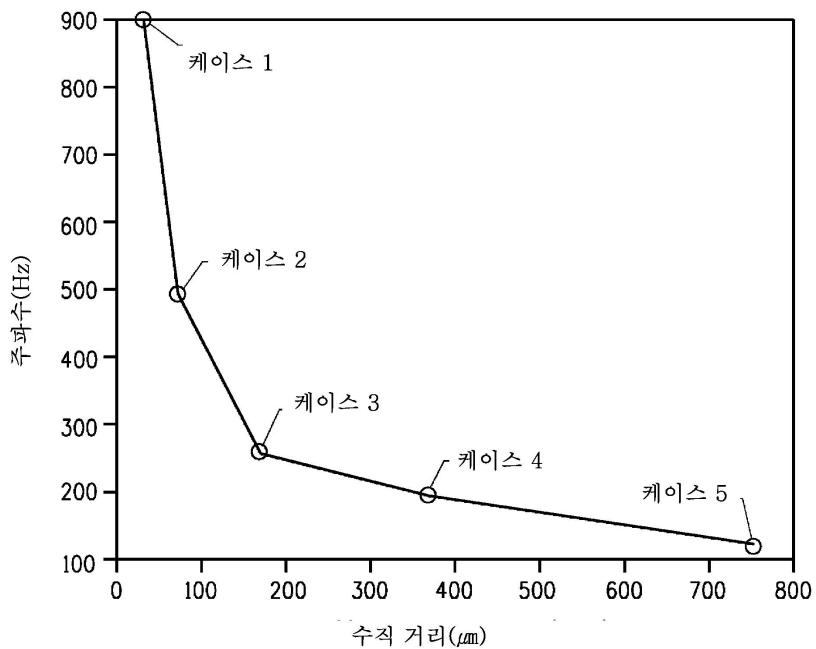

[0120] 도 8은 이들 시뮬레이션에 대한 임피던스 대 주파수 데이터를 나타낸 것이며, 커판시터 배치로부터 얻어지는 커판시터의 공진 주파수를 보여주고 있다. 알 수 있는 바와 같이, 케이스 1의 공진 주파수는  $10^9 \text{ 헤르츠}(1 \text{ GHz})$ 에

가깝다. 다른 케이스들에 대한 공진 주파수는 이 주파수보다 사실상 낮다.

[0121] 도 9는 각각의 케이스에 대한 MHz 단위의 공진 주파수 대 IC로부터의 거리를 나타낸 것으로서, 커패시터를 IC에 가깝게 배치한 결과로서 공진 주파수가 증가한다는 것을 나타내고 있다. 공진 주파수가 높을수록, 커패시터(들)가 IC에 더 효과적으로 전하를 제공한다.

[0122] 인덕턴스의 증가는 커패시터로부터 반도체 IC 소자로의 전압 응답을 느리게 한다는 것은 잘 알려져 있다. 커패시터와 반도체 사이의 거리를 짧게 하면 인덕턴스를 저하시키는 것으로 나타나며, 그에 의해 커패시터로부터의 더 빠른 전압 응답을 가능하게 한다.

[0123] 커패시터와 반도체 사이의 거리를 단축시키는 것은 또한 커패시터의 공진 주파수도 상승시켜, 그에 의해 높은 주파수에서 낮은 임피던스를 제공한다. 이는 높은 작동 주파수에서 낮은 노이즈의 결과를 가져온다.

[0124] 이상의 예는 반도체 소자에 가까운 인쇄 배선 기판의 빌드업층 내에 높은 커패시턴스의 박막 커패시터를 배치하는 본 명세서에서 설명된 방법들의 가치를 보여준다.

## 도면

### 도면1

(종래 기술)

도면2

(종래 기술)

도면3a

도면3b

도면3c

도면3d

도면3e

도면3f

도면3g

도면3h

도면4a

도면4b

도면4c

도면4d

도면5a

도면5b

도면5c

도면5d

도면5e

도면5f

도면5g

도면6

도면7

도면8

도면9