**【特許請求の範囲】****【請求項 1】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数個近接して形成する工程と、該溝で挟まれた半導体領域を除去し、前記半導体装置にトレンチを形成する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 2】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数個近接して形成する工程と、該溝で挟まれた半導体領域を完全に酸化膜に変質するまで酸化する工程と、該酸化された前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有することを特徴とする半導体装置の製造方法。

10

**【請求項 3】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数本ループ状に形成する工程と、該溝で挟まれた半導体領域を除去し、半導体基板にトレンチを形成する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 4】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数本ループ状に形成する工程と、該溝で挟まれた半導体領域を完全に酸化膜に変質するまで酸化する工程と、酸化膜に変質した前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有することを特徴とする半導体装置の製造方法。

20

**【請求項 5】**

半導体基板の表面層にアスペクト比が 1 以上の、半導体領域を囲む第 1 溝と、該第 1 溝で囲まれる半導体領域に、前記第 1 溝と開口部の幅と溝深さが同じ第 2 溝を同時に形成する工程と、前記溝に挟まれた前記半導体領域を除去し、半導体基板にトレンチ溝を形成する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 6】**

半導体基板の表面層にアスペクト比が 1 以上の、半導体領域を囲む第 1 溝と、該第 1 溝で囲まれる半導体領域に、前記第 1 溝と開口部の幅と溝深さが同じ第 2 溝を同時に形成する工程と、前記溝に挟まれた前記半導体領域を完全に酸化膜に変質するまで酸化する工程と、酸化膜に変質した前記半導体領域を除去し、半導体基板にトレンチを形成する工程とを有することを特徴とする半導体装置の製造方法。

30

**【請求項 7】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数個近接して形成する工程と、該溝で挟まれた半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない半導体領域を除去する工程と、酸化膜に変質した前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 8】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数本ループ状に形成する工程と、該溝で挟まれた半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない半導体領域を除去する工程と、酸化膜に変質した前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有することを特徴とする半導体装置の製造方法。

40

**【請求項 9】**

半導体基板の表面層にアスペクト比が 1 以上の、半導体領域を囲む第 1 溝と、該第 1 溝で囲まれる半導体領域に、前記第 1 溝と開口部の幅と溝深さが同じ第 2 溝を同時に形成する工程と、前記前記溝に挟まれた前記半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない前記半導体領域を除去する工程と、酸化膜に変質した前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 10】**

前記トレンチを形成する工程に続いて、該トレンチ内に絶縁膜を充填する工程を有することを特徴とする請求項 1 ~ 9 のいずれか一項に記載の半導体装置の製造方法。

50

**【請求項 1 1】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数本ループ状に形成する工程と、該溝で挟まれた半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない半導体領域を除去する工程と、該除去された半導体領域の箇所と前記溝に絶縁膜を充填する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 1 2】**

半導体基板の表面層にアスペクト比が 1 以上の、半導体領域を囲む第 1 溝と、該第 1 溝で囲まれる半導体領域に、前記第 1 溝と開口部の幅と溝深さが同じ第 2 溝を同時に形成する工程と、前記溝に挟まれた前記半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない半導体領域を除去する工程と、該除去された半導体領域の箇所と前記溝に絶縁膜を充填する工程とを有することを特徴とする半導体装置の製造方法。 10

**【請求項 1 3】**

前記トレンチを形成する工程に続いて、該トレンチ内壁と接するドリフト領域となる拡散層を形成する工程と、該トレンチ内に絶縁膜を充填する工程とを有することを特徴とする請求項 1 ~ 9 のいずれか一項に記載の半導体装置の製造方法。

**【請求項 1 4】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数個近接して形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を完全に酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、前記溝を絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。 20

**【請求項 1 5】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数本ループ状に形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を完全に酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、前記溝を絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 1 6】**

半導体基板の表面層にアスペクト比が 1 以上の、半導体領域を囲む第 1 溝と、該第 1 溝で囲まれる半導体領域に、前記第 1 溝と開口部の幅と溝深さが同じ第 2 溝を同時に形成する工程と、該第 1 溝および第 2 溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と前記溝で挟まれた半導体領域を完全に酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、前記溝を絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。 30

**【請求項 1 7】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数個近接して形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。 40

**【請求項 1 8】**

半導体基板の表面層にアスペクト比が 1 以上の溝を複数個近接して形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多 50

結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。

【請求項 19】

半導体基板の表面層にアスペクト比が 1 以上の溝を複数本ループ状に形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。

【請求項 20】

半導体基板の表面層にアスペクト比が 1 以上の溝を複数本ループ状に形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。

【請求項 21】

半導体基板の表面層にアスペクト比が 1 以上の、半導体領域を囲む第 1 溝と、該第 1 溝で囲まれる半導体領域に、前記第 1 溝と開口部の幅と溝深さが同じ第 2 溝を同時に形成する工程と、該第 1 溝と第 2 溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。

【請求項 22】

半導体基板の表面層にアスペクト比が 1 以上の半導体領域を囲む第 1 溝と、該第 1 溝で囲まれる半導体領域に、前記第 1 溝と開口部の幅と溝深さが同じ第 2 溝を同時に形成する工程と、該第 1 溝と第 2 溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。

【請求項 23】

前記溝の内壁に多結晶シリコン層を形成する工程を、イオン注入層を形成する工程に置き換えることを特徴とする請求項 14 ~ 22 のいずれか一項に記載の半導体装置の製造方法。

【請求項 24】

前記溝の内壁に多結晶シリコン層を形成する工程を、イオン注入層を形成した後、熱処理する工程に置き換えることを特徴とする 14 ~ 22 のいずれか一項に記載の半導体装置の製造方法。

10

20

30

40

50

**【請求項 25】**

前記第2溝の両端が前記第1溝と接し、前記第2溝の平面形状がストライプ状をしていることを特徴とする請求項5、6、9、13、15、16、21～24のいずれか一項に記載の半導体装置の製造方法。

**【請求項 26】**

前記第2溝の平面形状が格子状であり、該格子の外周端が前記第1溝と接することを特徴とする請求項5、6、9、13、15、16、21～24のいずれか一項に記載の半導体装置の製造方法。

**【請求項 27】**

前記溝で挟まれた前記半導体領域および酸化膜に変質した前記半導体領域を除去する方法が、等方性エッティング法であることを特徴とする請求項1～24のいずれか一項に記載の半導体装置の製造方法。 10

**【請求項 28】**

半導体基板の表面層にトレンチを形成する工程と、該トレンチの内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層を完全に酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、トレンチと接する半導体基板にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、前記トレンチを絶縁膜で充填する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 29】**

前記ドリフト領域を形成する工程に続いて、前記半導体基板上にゲート電極を形成する工程と、該ドリフト領域を挟んで前記半導体基板の表面層にソース領域およびドレイン領域を形成する工程とを有することを特徴とする請求項13～28のいずれか一項に記載の半導体装置の製造方法。 20

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

この発明は、トレンチを有する高耐圧MOSFETなどの半導体装置の製造方法であり、特に、トレンチと、このトレンチを充填する絶縁膜およびこのトレンチを囲むドリフト領域などの製造方法に関する。

**【0002】****【従来の技術】**

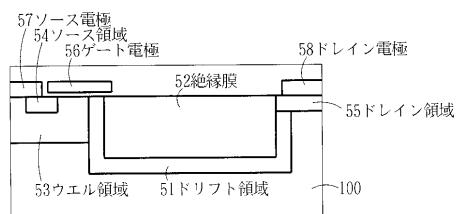

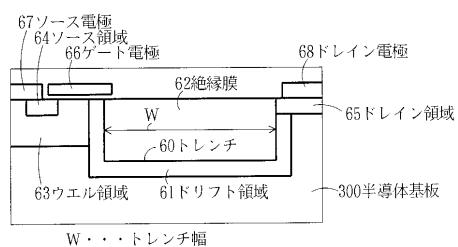

トレンチ技術は、DRAM等のメモリのキャパシタンスを作成する技術、素子分離のSOI技術、またMOSデバイスのトレンチゲートに既に使用されているが、近年パワーICへの適用が検討され、図43に示すような横型高耐圧MOSFETへの応用も提案されている（特許文献1）。

この横型高耐圧MOSFETの構造について説明する。半導体基板300にトレンチ60を形成し、このトレンチ60に沿ってドリフト領域61を形成し、トレンチ60を絶縁膜62で充填し、半導体基板300の表面層にウエル領域63を形成する。ウエル領域63の表面層にドリフト領域61と離してソース領域64を形成し、ソース領域64とドリフト領域61に挟まれたウエル領域63上に図示しないゲート絶縁膜を介してゲート電極66が形成され、半導体基板300の表面層にドリフト領域61と接してドレイン領域65を形成する。ソース領域64上とドレイン領域65上にソース電極67とドレイン電極68をそれぞれ形成する。前記したドリフト領域61は、トレンチ内壁に高濃度にドープされた多結晶シリコン膜を形成し、熱処理して、この多結晶シリコン層を拡散源として、トレンチに沿うように、半導体基板300に拡散層を形成することで形成される。 40

**【0003】**

トレンチ幅Wが広く、トレンチ開口率（トレンチの開口部面積のウエハ面積に占める割合）の大きなデバイスを製作する場合、幅広トレンチ内にブラックシリコンと呼ばれる柱状の突起物が形成される（特許文献2）。

このブラックシリコンの発生メカニズムはつきのように推測される。一回で幅の広いトレ 50

ンチを形成する場合、そのエッティングする面積が大面積となり、シリコンのエッティングにより発生した反応生成物であるSiOなどが被エッティング面に堆積し、それがマスクとして作用することによってSiOの下のシリコンがエッティングされずにエッティングが進み、結果としてトレンチ内に柱状のシリコンが残りブラックシリコンとなる。

#### 【0004】

##### 【特許文献1】

U S P 5 8 4 4 2 7 5 号公報

##### 【特許文献2】

特開2002-64089号公報

#### 【0005】

##### 【発明が解決しようとする課題】

このようにブラックシリコンが発生すると、トレンチ内に充填した絶縁膜の膜質が低下し、もれ電流が増大する。またシリコンの突起部で電界集中を生じて、耐圧不良を引起す。また、後工程においてこの柱状の突起物が折れてパーティクル発生の原因や拡散炉の汚染原因になり、製造良品率を低下させる。

また、前記のように、大面積をエッティングするとウェハの反りが発生する。開口率（ウェハ面積に対するエッティング面積の比率）が大きくなるほどウェハの反りも大きくなり、この結果、フォトリソグラフィ工程時にウェハに形成されるパターンの精度が低下し、トレンチ形状の精度よい制御が困難になる。また、ウェハの反りが大きくなると、半導体製造装置でウェハの移載などが行えなくなるといった不具合が生じる。

#### 【0006】

また、開口部が大きく、開口部の幅と同程度の深さのトレンチの内部を酸化膜などの絶縁膜で埋め込む場合、減圧CVD (Chemical Vapour Deposition) 法を用いた場合には、少なくともトレンチの開口部の幅(トレンチ幅)の半分以上の厚い膜を形成しなければならない。例えば、トレンチ幅及びトレンチの深さが20μmの場合には、10μmもの厚い膜を形成しなければならず、非常に時間のかかる膜形成工程となるために製造コストが増大する。

また、図43の半導体装置を製造する場合に、拡散源となる高濃度にドープした多結晶シリコン層を付けたままで、トレンチ内に絶縁膜を充填する工程や、ウエル領域、ソース・ドレイン領域などを形成する工程を実施すると、熱処理により、ドリフト領域の不純物濃度が所定値から変化したり、拡散源の不純物が前記領域に拡散して、所定の特性が得られなくなったり、信頼性の低下を招いたりする。

#### 【0007】

また、トレンチ内を充填する絶縁膜を酸化膜とした場合、この酸化膜を形成するための熱酸化工程で多結晶シリコン層が酸化膜に変質する。しかし、この変質した酸化膜の膜質は必ずしも良質でなく、また、この変質した酸化膜と熱酸化膜との間で歪みが発生し、耐圧特性などの信頼性が低下する。

この発明は、前記の課題を解決して、トレンチ底面に発生するブラックシリコンを抑制し、ウェハの反りを抑制し、トレンチを囲むように形成されるドリフト領域の不純物濃度を所定値に確保し、トレンチ内を充填する絶縁膜の信頼性を確保できる半導体装置の製造方法を提供することにある。

#### 【0008】

##### 【課題を解決するための手段】

前記の目的を達成するために、(1)半導体基板の表面層にアスペクト比が1以上の溝を複数個近接して形成する工程と、該溝で挟まれた半導体領域を除去し、前記半導体装置にトレンチを形成する工程とを有する製造方法とする。

(2)半導体基板の表面層にアスペクト比が1以上の溝を複数個近接して形成する工程と、該溝で挟まれた半導体領域を完全に酸化膜に変質するまで酸化する工程と、該酸化された前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有する製造方法とする。

10

20

30

40

50

(3) 半導体基板の表面層にアスペクト比が1以上の溝を複数本ループ状に形成する工程と、該溝で挟まれた半導体領域を除去し、半導体基板にトレンチを形成する工程とを有する製造方法とする。

(4) 半導体基板の表面層にアスペクト比が1以上の溝を複数本ループ状に形成する工程と、該溝で挟まれた半導体領域を完全に酸化膜に変質するまで酸化する工程と、酸化膜に変質した前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有する製造方法とする。

(5) 半導体基板の表面層にアスペクト比が1以上の半導体領域を囲む第1溝と、該第1溝で囲まれる半導体領域に、前記第1溝と開口部の幅と溝深さが同じ第2溝を同時に形成する工程と、前記溝に挟まれた前記半導体領域を除去し、半導体基板にトレンチ溝を形成する工程とを有する製造方法とする。

10

(6) 半導体基板の表面層にアスペクト比が1以上の半導体領域を囲む第1溝と、該第1溝で囲まれる半導体領域に、前記第1溝と開口部の幅と溝深さが同じ第2溝を同時に形成する工程と、前記溝に挟まれた前記半導体領域を完全に酸化膜に変質するまで酸化する工程と、酸化膜に変質した前記半導体領域を除去し、半導体基板にトレンチを形成する工程とを有する製造方法とする。

(7) 半導体基板の表面層にアスペクト比が1以上の溝を複数個近接して形成する工程と、該溝で挟まれた半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない半導体領域を除去する工程と、酸化膜に変質した前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有する製造方法とする。

20

#### 【0009】

(8) 半導体基板の表面層にアスペクト比が1以上の溝を複数本ループ状に形成する工程と、該溝で挟まれた半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない半導体領域を除去する工程と、酸化膜に変質した前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有する製造方法とする。

(9) 半導体基板の表面層にアスペクト比が1以上の半導体領域を囲む第1溝と、該第1溝で囲まれる半導体領域に、前記第1溝と開口部の幅と溝深さが同じ第2溝を同時に形成する工程と、前記溝に挟まれた前記半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない前記半導体領域を除去する工程と、酸化膜に変質した前記半導体領域を除去し、前記半導体基板にトレンチを形成する工程とを有する製造方法とする。

30

(10) (1)～(9)の製造方法において、前記トレンチを形成する工程に続いて、該トレンチ内に絶縁膜を充填する工程を有する製造方法とする。

(11) 半導体基板の表面層にアスペクト比が1以上の溝を複数本ループ状に形成する工程と、該溝で挟まれた半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない半導体領域を除去する工程と、該除去された半導体領域の箇所と前記溝に絶縁膜を充填する工程とを有する製造方法とする。

(12) 半導体基板の表面層にアスペクト比が1以上の半導体領域を囲む第1溝と、該第1溝で囲まれる半導体領域に、前記第1溝と開口部の幅と溝深さが同じ第2溝を同時に形成する工程と、前記溝に挟まれた前記半導体領域を酸化膜に変質する工程と、該溝で挟まれ酸化膜に変質しない半導体領域を除去する工程と、該除去された半導体領域の箇所と前記溝に絶縁膜を充填する工程とを有する製造方法とする。

40

(13) (1)から(9)の製造方法において、前記トレンチを形成する工程に続いて、該トレンチ内壁と接するドリフト領域となる拡散層を形成する工程と、該トレンチ内に絶縁膜を充填する工程とを有する製造方法とする。

(14) 半導体基板の表面層にアスペクト比が1以上の溝を複数個近接して形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を完全に酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、前記溝を絶縁膜で充填する工程とを有する製造方法とする。

50

## 【0010】

(15) 半導体基板の表面層にアスペクト比が1以上の溝を複数本ループ状に形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を完全に酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、前記溝を絶縁膜で充填する工程とを有する製造方法とする。

(16) 半導体基板の表面層にアスペクト比が1以上の半導体領域を囲む第1溝と、該第1溝で囲まれる半導体領域に、前記第1溝と開口部の幅と溝深さが同じ第2溝を同時に形成する工程と、該第1溝および第2溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と前記溝で挟まれた半導体領域を完全に酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、前記溝を絶縁膜で充填する工程とを有する製造方法とする。

10

(17) 半導体基板の表面層にアスペクト比が1以上の溝を複数個近接して形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有する製造方法とする。

20

## 【0011】

(18) 半導体基板の表面層にアスペクト比が1以上の溝を複数個近接して形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有する製造方法とする。

30

(19) 半導体基板の表面層にアスペクト比が1以上の溝を複数本ループ状に形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有する製造方法とする。

(20) 半導体基板の表面層にアスペクト比が1以上の溝を複数本ループ状に形成する工程と、該溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有する製造方法とする。

40

## 【0012】

(21) 半導体基板の表面層にアスペクト比が1以上の半導体領域を囲む第1溝と、該第1溝で囲まれる半導体領域に、前記第1溝と開口部の幅と溝深さが同じ第2溝を同時に形成する工程と、該第1溝と第2溝の内壁に不純物をドープした多結晶シリコン層を形成す

50

る工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有する製造方法とする。

(22) 半導体基板の表面層にアスペクト比が1以上の半導体領域を囲む第1溝と、該第1溝で囲まれる半導体領域に、前記第1溝と開口部の幅と溝深さが同じ第2溝を同時に形成する工程と、該第1溝と第2溝の内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層と溝で挟まれた半導体領域を酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、前記多結晶シリコン層を拡散源として溝近傍の半導体領域にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、酸化膜に変質しない前記半導体領域を除去し、該除去箇所に前記拡散層と接するドリフト層の一部となる拡散層を形成する工程と、前記溝と除去された前記半導体領域の箇所を絶縁膜で充填する工程とを有する製造方法とする。

10

#### 【0013】

(23) (14)～(22)の半導体装置の製造方法において、前記溝の内壁に多結晶シリコン層を形成する工程を、イオン注入層を形成する工程に置き換えるてもよい。

(24) (14)～(22)の半導体装置の製造方法において、前記溝の内壁に多結晶シリコン層を形成する工程を、イオン注入層を形成した後、熱処理する工程に置き換えるてもよい。

20

(25) (5)、(6)、(9)、(13)、(15)、(16)、(21)～(24)の半導体装置の製造方法において、前記第2溝の両端が前記第1溝と接し、前記第2溝の平面形状がストライプ状をしているとよい。

(26) (5)、(6)、(9)、(13)、(15)、(16)、(21)～(24)の半導体装置の製造方法において、前記第2溝の平面形状が格子状であり、該格子の外周端が前記第1溝と接するとよい。

(27) (1)～(24)の半導体装置の製造方法において、前記溝で挟まれた前記半導体領域および酸化膜に変質した前記半導体領域を除去する方法が、等方性エッチング法であるとよい。

30

(28) 半導体基板の表面層にトレンチを形成する工程と、該トレンチの内壁に不純物をドープした多結晶シリコン層を形成する工程と、該多結晶シリコン層を完全に酸化膜に変質するまで熱酸化処理し、該熱酸化処理で、トレンチと接する半導体基板にドリフト領域となる拡散層を形成する工程と、酸化膜に変質した前記多結晶シリコン層を除去する工程と、前記トレンチを絶縁膜で充填する工程とを有する製造方法とする。

(29) (13)～(28)の半導体装置の製造方法において、前記ドリフト領域を形成する工程に続いて、前記半導体基板上にゲート電極を形成する工程と、該ドリフト領域を挟んで前記半導体基板の表面層にソース領域およびドレイン領域を形成する工程とを有する製造方法とする。

#### 〔作用〕

トレンチを形成する領域にアスペクト比が1以上の微小な溝を近接して多数形成することで、溝底部にブラックシリコンが形成されることを防止できる。

40

#### 【0014】

また、溝で挟まれるシリコン柱の幅を広くして、熱酸化によりシリコン柱が熱酸化膜に変質した箇所を残し、変質しない箇所のシリコンを除去することで、幅広のトレンチ内に熱酸化膜に変質したシリコン柱を残すことで、その後の工程でウエハが反ることを防止できる。

また、ドレイン領域を形成した後で、拡散源のドープされたポリシリコン層を除去することで、後工程の熱処理で、ドレイン領域の不純物濃度が変わることを防止できる。また、ドレイン領域以外の拡散層に拡散源の不純物が拡散することを防止できる。

50

## 【0015】

## 【発明の実施の形態】

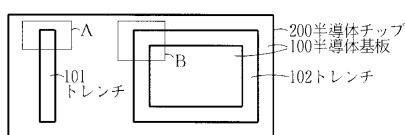

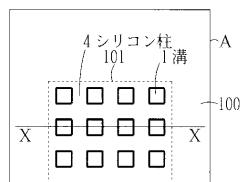

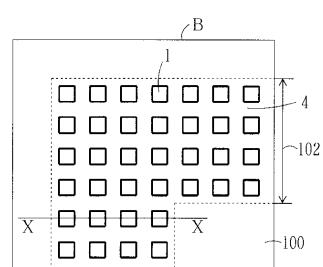

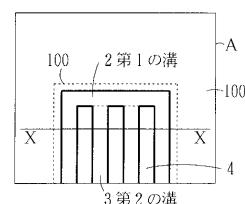

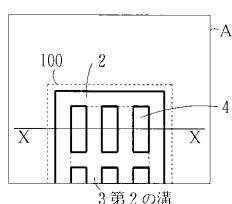

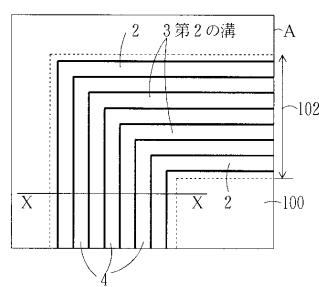

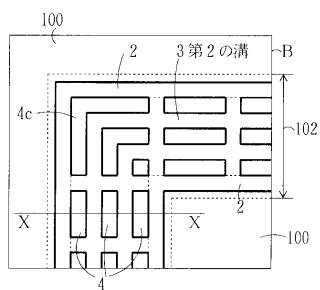

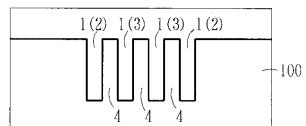

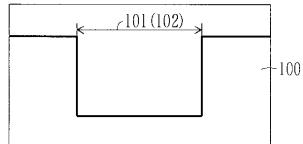

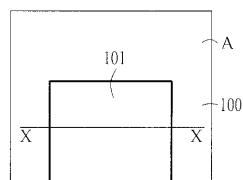

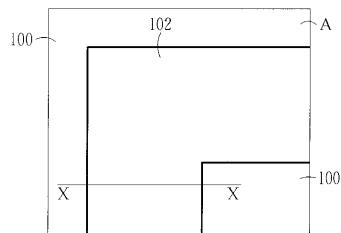

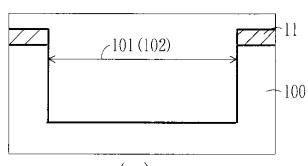

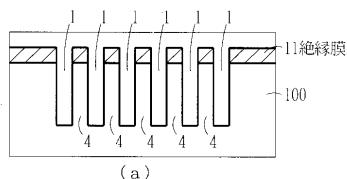

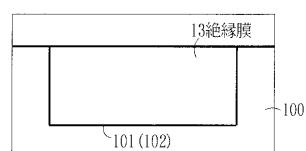

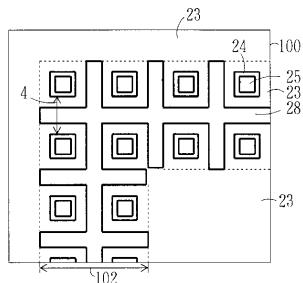

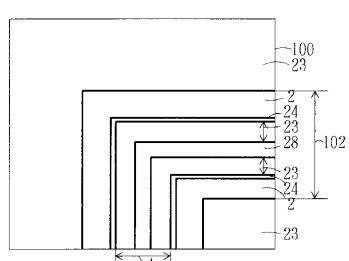

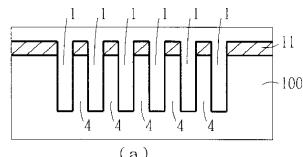

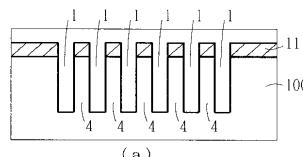

図1から図11は、本発明の半導体装置の製造方法の内、トレンチを形成する方法の概要を説明する図である。図1は、半導体基板にトレンチを形成した平面図であり、図2から図7は微小の溝を形成した平面図であり、図8は図2から図7の断面図であり、図9はトレンチの断面図であり、図10、図11はトレンチの平面図である。

図1は、半導体基板にトレンチを形成した平面図である。トレンチ101はストライプ状のものであり、トレンチ102はリング状をしたものである。図示しないが、トレンチ101、102に絶縁膜が充填されて、誘電体分離領域が形成されたり、このトレンチに沿うように横型高耐圧MOSFETなどのドリフト領域が形成される。

10

## 【0016】

図2、図3は、図1のA部およびB部の拡大図である。このトレンチ101、102内には、微小な独立した平面が正方形の溝1が近接して形成されている。この溝のアスペクト比は1以上である。また溝1で囲まれた(挟まれた)半導体基板100は格子状をしたシリコン柱4となる。

図4は、図1のA部の拡大図である。これは図2とは異なった例である。トレンチ101は微小な第1の溝2で枠取りされており、この枠取りされた内側に、複数本のストライプ状の第2の溝3が第1の溝2にその両端が接するように、しかも互いが近接するように、第1の溝2と同時に形成される。この第1および第2の溝2、3のアスペクト比は1以上である。第1の溝2に囲まれた箇所(挟まれた箇所)がストライプ状のシリコン柱4となる。

20

## 【0017】

図5は、図4の変形例であり、図4の複数本のシリコン柱4が途中で切断され、格子状の溝となつた場合である。図4ではシリコン柱4の平面形状は長方形となっているが、互いに近接した正方形の場合もある。

図6は、図1のB部の拡大図である。これは、図3と異なった例である。トレンチ102の外周端と内周端に微小な第1の溝2が形成されており、この第1の溝2で挟まれた領域に、複数本のリング状の第2の溝3が近接して、第1の溝2と同時に形成される。この第1および第2の溝2、3のアスペクト比は1以上である。第1の溝2、第2の溝3および第2の溝3で挟まれた箇所がリング状のシリコン柱4となる。

30

## 【0018】

図7は、図6の変形例であり、図6の複数本のシリコン柱4が途中で切断され、格子状の溝となり、コーナー部のシリコン柱4の平面形状は鉤状となっているが、円弧状の場合もある。また、全域で微小な正方形の場合もある。

図8は、図2から図7のX-X線で切断した要部断面図である。図中の1は図2、図3の溝であり、(2)で示した溝は、図4から図7の第1の溝2であり、(3)で示した溝は、図4から図7の第2の溝3である。これらの溝に挟まれた箇所がシリコン柱4となる。

図9は、最終的に形成されるトレンチの断面形状であり、図10、図11はその平面図である。図9は、図10、図11のX-X線で切断した断面図である。図8で示すアスペクト比が1以上の溝で挟まれたシリコン柱4を除去することで、幅広のトレンチが形成できる。

40

## 【0019】

多数の微小な溝1、2、3を形成することで、幅広のトレンチを一回のエッチングで形成する場合と比べて、エッチングによる反応生成物(SiOなど)を少なくして、この反応生成物で発生する微小なブラックシリコンも、その後のシリコン柱4を除去する工程で除去されるために、ブラックシリコンの発生を抑えることができる。

そのため、例えば、20μm幅で20μm深さの幅広で深いトレンチを形成する場合、2μm幅で20μm深さの微小な溝を多数形成し、その後、シリコン柱を除去して20μm幅で20μm深さのトレンチを形成することで、ブラックシリコンの発生を抑制できる。つまり、微小な溝の幅は深さより小さくするほどブラックシリコンの発生は抑制できるこ

50

とになる。そのため、本発明では、微小さな溝のアスペクト比を1以上とした。アスペクト比とは溝の深さを幅で割った値であり、アスペクト比が1以上ということは、溝の深さが溝の幅以上に深いということを意味する。

#### 【0020】

つぎに、具体的な実施例について説明する。ここでは、図2、図3の場合を例として挙げたが、図4から図7の場合も同様である。

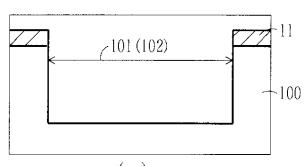

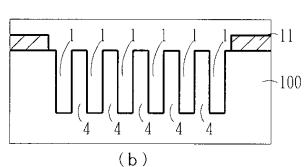

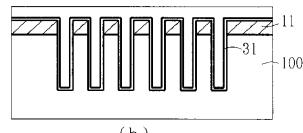

図12は、この発明の第1実施例の半導体装置の製造方法であり、同図(a)から同図(c)は工程順に示した要部製造工程断面図である。

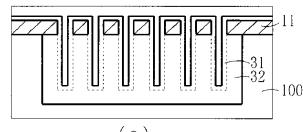

半導体基板100を、絶縁膜11をマスクとして、アスペクト1以上の溝1を近接して形成する。この溝1に挟まれた箇所がシリコン柱4となる。溝1およびシリコン注4の幅は1μm程度である。溝1の形成は、絶縁膜11をマスクとしてRIE(Reactive Ion Etching)法などの異方性ドライエッチングを行う。また、絶縁膜11は、酸化膜や窒化膜である(同図(a))。

#### 【0021】

つぎに、図示しないレジストをマスクとして、シリコン柱4上の絶縁膜11を除去する。絶縁膜11が酸化膜の場合はフッ酸溶液などで容易に除去できる(同図(b))。

つぎに、CDE(Chemical Dry Etching)法等の等方性ドライエッチングによりシリコン柱4を除去することで、トレンチ101、102が形成される(同図(c))。

前記の溝1幅を狭くすることで、ブラックシリコンの発生は抑制される。

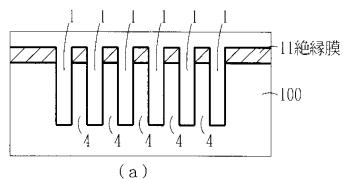

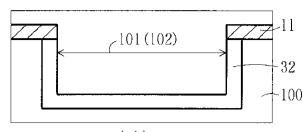

図13は、この発明の第2実施例の半導体装置の製造方法であり、同図(a)から同図(d)は工程順に示した要部製造工程断面図である。

#### 【0022】

図12との違いは、シリコン柱4を熱酸化により、シリコン柱4全体を熱酸化膜12に変質させ(同図(b))、その後、フッ酸溶液などでこの熱酸化膜12を除去することで、トレンチを形成する(同図(c))点である。図12と比べると、熱酸化膜12に変質したシリコン柱を容易に除去できる。

つぎに、このトレンチ101、102に絶縁膜を充填して誘電体分離領域などを形成する場合について説明する。

図14は、この発明の第3実施例の半導体装置の製造工程断面図である。この工程断面図は、前記したトレンチ101、102に絶縁膜を充填した図である。

#### 【0023】

これは、図11、図12の工程に続いて、絶縁膜13をトレンチ101、102の深さより、高くなるように全面に形成した後、CMP(Chemical Mechanical Polishing)法で半導体基板100より高い余分な絶縁膜13および絶縁膜11を除去して平坦化し、トレンチ101、102内の絶縁膜13の表面高さを半導体基板100の表面高さと同じ高さになるようする。

このように、トレンチ101、102に絶縁膜13を充填することで、図1のBのようなリング状のトレンチの場合には、誘電体分離領域とすることができます。

#### 【0024】

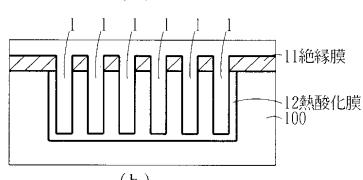

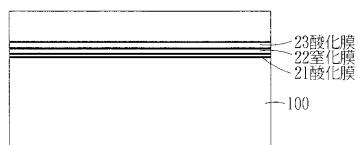

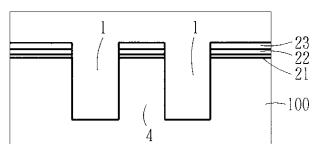

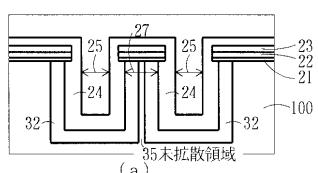

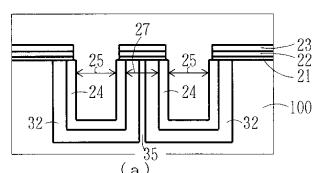

図15から図20は、この発明の第3実施例の半導体装置の製造方法であり、工程順に示した要部製造工程断面図である。

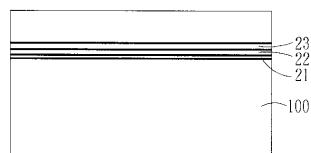

半導体基板100上に30nm厚さの酸化膜21(熱酸化膜)、100nm厚さの窒化膜22(CVD(Chemical Vapor Deposition)法で形成)、1μm厚さの酸化膜23(減圧CVD法で形成)を形成する。これら3層の絶縁膜は微小さな溝を形成する場合のマスクとして用いられる。また、熱酸化するときのマスクの働きもある(図15)。

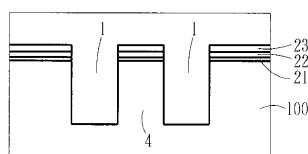

つぎに、半導体基板100に、微小さな溝1の互いの間隔を2μmにして形成する。溝1の幅は2μm、深さは20μmでアスペクト比が10である。このアスペクト比が50を超すと後工程での洗浄でシリコン柱4が根元から折れて、エッティング不良やパーティクルの

10

20

30

40

50

原因となる。また、シリコン柱4の幅は2μm程度とする(図16)。

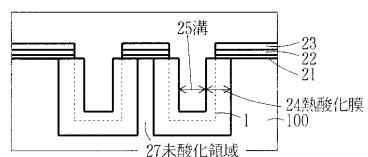

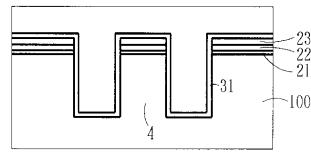

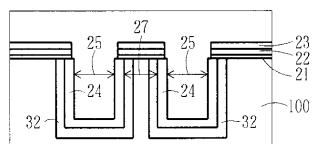

【0025】

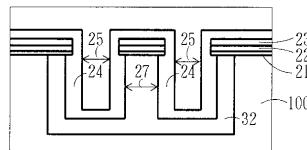

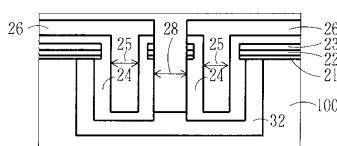

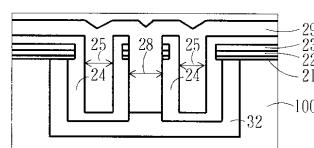

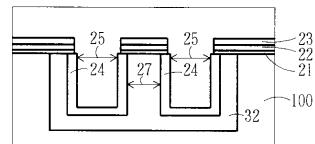

つぎに、溝1の周囲に熱酸化膜24を形成する。シリコン柱4の幅が2μm程度と広いために、この熱酸化ではシリコン柱4を完全には熱酸化膜24に変質させることができず、未酸化領域27が発生する。また、この熱酸化膜24で囲まれ、溝1より浅い溝25が形成される(図17)。

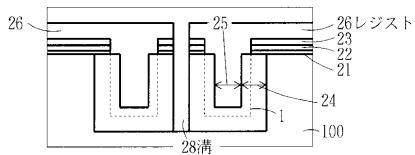

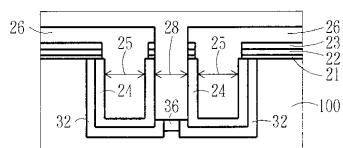

つぎに、未酸化領域27上を開口したレジスト26を形成し、このレジスト26をマスクに未酸化領域27をRIE法で異方性ドライエッティングして除去する(図18)。

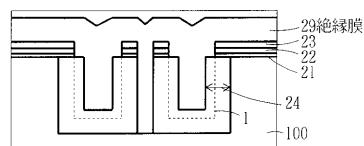

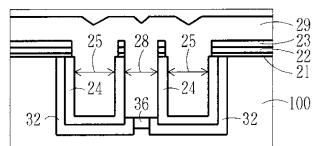

つぎに、レジスト26を除去し、絶縁膜29を溝25、28を覆うように全面に形成する(図19)。

10

【0026】

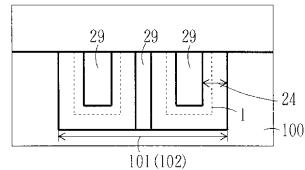

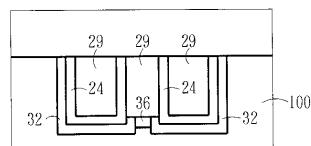

つぎに、CMP法で絶縁膜29、酸化膜21、窒化膜22、酸化膜23を、半導体基板100の表面高さまで除去する(図20)。

このように、シリコン柱4の幅を広くして、未酸化領域27を除去することで、幅20μm程度のトレンチ101、102を形成することができる。

また、広いトレンチ幅でも、熱酸化膜24に変質したシリコン柱を残すことで、ウエハ裏面の図示しない酸化膜とのバランスがとれるため、ウエハの反りを抑制できる。さらに、熱酸化膜24に変質したシリコンはしら残すと、前記第1、第2実施例と比べ絶縁膜29の溝内への形成時間を短縮することができる。また、複数解に分け、1回のエッティング開口率を低くして、トレンチを掘ることによっても、プロセス途中でのウエハの反りを抑制できる。また、溝1を微小とすることで、ブラックシリコンの発生を防止できる。

20

【0027】

【表1】

|        | 開口率(%) |    |    |    |    |    |    |

|--------|--------|----|----|----|----|----|----|

|        | 10     | 20 | 30 | 40 | 50 | 60 | 70 |

| 本発明の場合 | ○      | ○  | ○  | ○  | ○  | ○  | ○  |

| 従来の場合  | ○      | ○  | ○  | ×  | ×  | ×  | ×  |

○は搬送エラーなし ×は搬送エラーあり

30

表1は、ウエハの反りと開口率の関係を示す。従来の場合はトレンチ(平面形状が正方形)の幅が20μm、トレンチの深さは20μmのものをウエハに多数形成し、本発明の場合は、トレンチエッティングを2回に分け、1回のエッティングにおいてトレンチを形成するための微小な溝1(平面形状が正方形)の幅は2μm、深さ20μm、間隔2μmであり、本発明のトレンチも平面形状が正方形でその幅は20μmである。この本発明のトレンチもウエハに多数個形成する。開口率とは、従来の場合も本発明の場合も、ウエハ面積に占めるエッティング開口部全部の面積の割合である。この開口率を10~70%とした場合にウエハの反りにより半導体製造装置で搬送エラーが起きた場合を×とし、起きない場合を○で示した。

40

【0028】

本発明の場合は、トレンチ101、102内に熱酸化膜24に変質したシリコン柱が存在するため、ウエハの反りが小さく、開口率が70%でも搬送エラーが起きなかつた。一方、従来の場合は開口率40%で搬送エラーが起こつた。

【0029】

【表2】

|       | 溝幅 ( $\mu\text{m}$ ) |   |   |   |    |    |    |    |    |    |

|-------|----------------------|---|---|---|----|----|----|----|----|----|

|       | 2                    | 4 | 6 | 8 | 10 | 12 | 14 | 16 | 18 | 20 |

| 発生の有無 | 無                    | 無 | 無 | 無 | 無  | 有  | 有  | 有  | 有  | 有  |

表2は、ブラックシリコンの発生の有無と溝幅との関係を示す。溝の平面形状は正方形の場合である。また溝の開口率が35%、溝の深さが20 $\mu\text{m}$ であり、溝の幅は2 $\mu\text{m}$ から20 $\mu\text{m}$ まで実験した。

10

溝の幅が10 $\mu\text{m}$ まではブラックシリコンは発生しないが、12 $\mu\text{m}$ 以上ではブラックシリコンは発生するようになる。表2に示さないが、開口率70%とすると、溝幅が4 $\mu\text{m}$ まではブラックシリコンが発生しない。

### 【0030】

このブラックシリコンの発生は、前記したように、シリコンのエッチングにより発生した反応生成物が被エッチング面に付着して起こるため、溝幅（溝の開口部の大きさ）が大きくなると発生し易くなり、また、溝の総数（開口率）が大きくなると発生し易くなる。よって、1回のエッチングの開口率を35%以下として、トレンチ幅10 $\mu\text{m}$ 以下とすればよい。

20

図21、図22は、図18の段階での平面図である。図21は、図3に相当する平面図で、図22は、図6に相当する平面図である。これらの平面図から溝28の平面形状が分かる。

### 【0031】

つぎに、横型高耐圧MOSFETなどのドリフト領域を形成して、トレンチを絶縁膜で充填する場合の製造方法について説明する。以下の説明ではドリフト領域となる拡散層32の導電形を示さないが、nチャネルMOSFETを形成する場合はn形であり、pチャネルMOSFETを形成する場合はp形である。

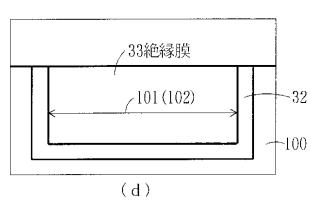

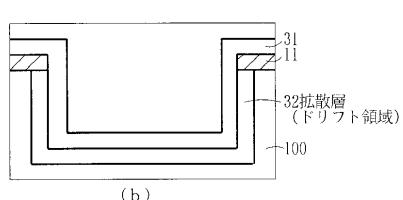

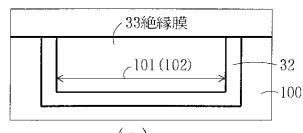

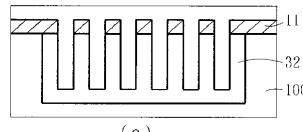

図23は、この発明の第4実施例の半導体装置の製造方法であり、同図(a)から同図(d)は、工程順に示した要部製造工程断面図である。

30

図12、図13の工程に続いて、全面にドープしたポリシリコン層31を形成する（同図(a)）。

### 【0032】

つぎに、熱処理して、ドリフト領域となる拡散層32を形成する（同図(b)）。

つぎに、ポリシリコン層31を除去する（同図(c)）。

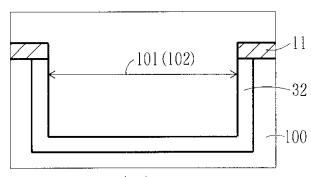

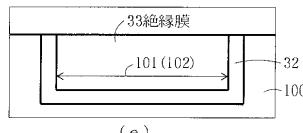

つぎに、トレンチ101、102が埋まるように全面に絶縁膜33を形成し、半導体基板100の表面が露出するまで、CMP法で絶縁膜33と絶縁膜11を研削除去し、平坦化する（同図(d)）。

拡散源となるポリシリコン層31を除去することで、後工程での熱処理で、ドリフト領域の不純物濃度が変化することを防止して、所定の不純物濃度を得ることができる。

40

### 【0033】

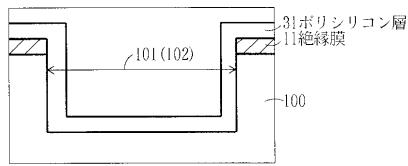

図24は、この発明の第5実施例の半導体装置の製造方法であり、同図(a)から同図(e)は、工程順に示した要部製造工程断面図である。

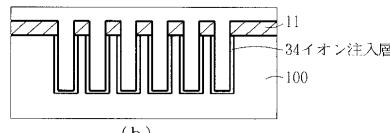

半導体基板100を、絶縁膜11をマスクとして、アスペクト比1以上（例えばアスペクト比10程度）の溝1を近接して形成する。

つぎに、全面に、ドープしたポリシリコン層31（例えば、厚さが30nm程度）を減圧CVD法で形成する（同図(b)）。

つぎに、ポリシリコン層31を拡散源として、シリコン柱4の底部で拡散層が繋がるまで、例えば、1150、120分の熱処理を行い、ドリフト領域となる拡散層32を、例えば、ピーク濃度 $1 \times 10^{16} \text{ cm}^{-3}$ で幅3 $\mu\text{m}$ となるように形成する（同図(c)）

50

。

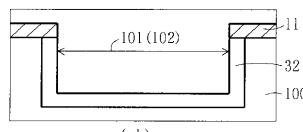

### 【 0 0 3 4 】

つぎに、ポリシリコン層 3 1 とシリコン柱 4 を除去して、トレンチ 1 0 1 、 1 0 2 を形成する。この場合、ポリシリコン層 3 1 とシリコン柱 4 を熱酸化膜に変質した後、これらを除去しても構わない（同図（ d ））。

つぎに、トレンチ 1 0 1 、 1 0 2 が埋まるように全面に絶縁膜 3 3 を形成し、半導体基板 1 0 0 の表面が露出するまで、 C M P 法で絶縁膜 3 3 と絶縁膜 1 1 を研削除去し、平坦化する（同図（ e ））。

図 2 5 は、この発明の第 6 実施例の半導体装置の製造方法であり、同図（ a ）から同図（ e ）は、工程順に示した要部製造工程断面図である。

10

### 【 0 0 3 5 】

半導体基板 1 0 0 を、絶縁膜 1 1 をマスクとして、アスペクト比 1 以上（例えば、アスペクト比 1 0 程度）の溝 1 を近接して形成する。

つぎに、全面にイオン注入層 3 4 を形成する（同図（ b ））。

つぎに、イオン注入層 3 4 を拡散源として、シリコン柱 4 の底部で拡散層が繋がるまで熱処理し、ドリフト領域となる拡散層 3 2 （ピーク濃度  $1 \times 1 0^{16} \text{ cm}^{-3}$  で幅 3  $\mu\text{m}$  ）を形成する（同図（ c ））。

つぎに、シリコン柱 4 を除去して、トレンチ 1 0 1 、 1 0 2 を形成する。この場合、シリコン柱 4 を熱酸化膜に変質した後、これらを除去しても構わない（同図（ d ））。

20

### 【 0 0 3 6 】

つぎに、トレンチ 1 0 1 、 1 0 2 が埋まるように全面に絶縁膜 3 3 を形成し、半導体基板 1 0 0 の表面が露出するまで、 C M P 法で絶縁膜 3 3 と絶縁膜 1 1 を研削除去し、平坦化する（同図（ e ））。

つぎに、シリコン柱の幅が広く、シリコン柱全域が熱酸化膜に変質できない場合について説明する。

図 2 6 から図 3 2 は、この発明の第 7 実施例の半導体装置の製造方法であり、工程順に示した要部製造工程断面図である。

半導体基板 1 0 0 上に 3 0 nm 厚さの酸化膜 2 1 （熱酸化膜）、 1 0 0 nm 厚さの窒化膜 2 2 （ C V D （ C hemical V apor D eposition ）法で形成）、 1  $\mu\text{m}$  厚さの酸化膜 2 3 （減圧 C V D 法で形成）を形成する。これら 3 層の絶縁膜は微小な溝を形成する場合のマスクとして用いられる。また、熱酸化するときのマスクの働きもする（図 2 6 ）。

30

### 【 0 0 3 7 】

つぎに、半導体基板 1 0 0 に、微小な溝 1 の互いの間隔を 2  $\mu\text{m}$  にして形成する。溝 1 の幅は 2  $\mu\text{m}$  、深さは 2 0  $\mu\text{m}$  でアスペクト比が 1 0 である。この溝 1 は R I E 法による異方性ドライエッティングで形成される（図 2 7 ）。

つぎに、全面に、ドープしたポリシリコン層 3 1 （例えば、厚さが 3 0 nm 程度）を減圧 C V D 法で形成する（図 2 8 ）。

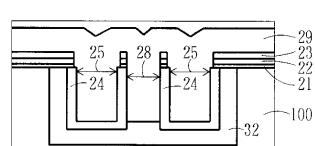

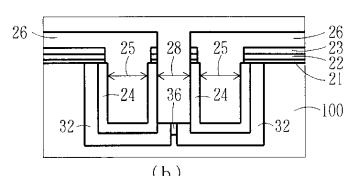

つぎに、ポリシリコン層 3 1 を拡散源として、シリコン柱 4 の底部で拡散層が繋がるまで、例えば、 1 1 5 0 、 1 2 0 分の熱処理を行い、ドリフト領域となる拡散層 3 2 を、例えば、ピーク濃度  $1 \times 1 0^{16} \text{ cm}^{-3}$  で幅 3  $\mu\text{m}$  となるように形成する。その後、熱酸化して、ポリシリコン層 3 1 と拡散層 3 2 の表面層を熱酸化膜 2 4 に変質させる。シリコン柱 4 の幅が広いために、この熱酸化ではシリコン柱 4 を完全には熱酸化膜 2 4 に変質させることができず、未酸化領域 2 7 が発生する。また、この熱酸化膜 2 4 で囲まれ、溝 1 より浅い溝 2 5 が形成される（図 2 9 ）。

40

### 【 0 0 3 8 】

つぎに、未酸化領域 2 7 上を開口したレジスト 2 6 を形成し、未酸化領域を除去する（図 3 0 ）。

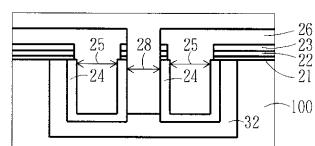

つぎに、レジスト 2 6 を除去し、絶縁膜 2 9 を溝 2 5 、 2 8 を覆うように全面に形成する（図 3 1 ）。

50

つぎに、C M P 法で絶縁膜 2 9、酸化膜 2 1、窒化膜 2 2、酸化膜 2 3 を、半導体基板 1 0 0 の表面高さまで除去し平坦化する。このとき、窒化膜 2 2 をストップとして C M P 法で第 1 次の平坦化を図り、その後、窒化膜 2 2 と酸化膜 2 3 および絶縁膜 2 9 をエッティングによって最終的に平坦化しても構わない(図 3 2)。

#### 【 0 0 3 9 】

前記したように、シリコン柱 4 の幅を広くし、未拡散領域 2 7 を除去することで、トレンチの幅を広くすることができる。

また、広いトレンチ幅でも、熱酸化膜 2 4 に変質したシリコン柱を残すことで、ウエハの反りを防止でき、また、溝 1 を微小とすることで、ブラックシリコンの発生を防止できる。

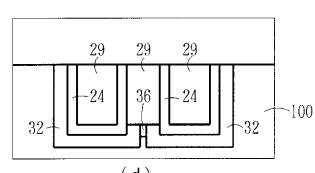

図 3 3 は、この発明の第 8 実施例の半導体装置の製造方法であり、同図 (a) から同図 (d) は工程順に示した要部製造工程断面図である。

図 2 8 の工程に続いて、ポリシリコン層 3 1 を拡散源として、シリコン柱 4 の底部で拡散層が繋がるまで熱処理し、ドリフト領域となる拡散層 3 2 を形成する。その後、この拡散源となるポリシリコン層 3 1 を除去し、その後で熱酸化して、拡散層 3 2 の表面層を熱酸化膜 2 4 に変質させる。ポリシリコン層 3 1 の除去は熱酸化膜に変質させた後に希フッ酸溶液などで行っても構わない。シリコン柱 4 の幅が広いために、この熱酸化ではシリコン柱 4 を完全には熱酸化膜 2 4 に変質させることができず、未酸化領域 2 7 が発生する。また、この熱酸化膜 2 4 で囲まれ、溝 1 より浅い溝 2 5 が形成される(同図 (a))。

#### 【 0 0 4 0 】

つぎに、未酸化領域 2 7 上を開口したレジスト 2 6 を形成し、未酸化領域を除去する(同図 (b))。

つぎに、レジスト 2 6 を除去し、絶縁膜 2 9 を溝 2 5、2 8 を覆うように全面に形成する(同図 (c))。

つぎに、C M P 法で絶縁膜 2 9、酸化膜 2 1、窒化膜 2 2、酸化膜 2 3 を、半導体基板 1 0 0 の表面高さまで除去し平坦化する(同図 (d))。

このように、拡散源となるポリシリコン層 3 1 を除去することで、後工程での熱処理で、ドリフト領域の不純物濃度が変化することを防止して、所定の不純物濃度を得ることができる。

#### 【 0 0 4 1 】

また、前記したように、未拡散領域 2 7 を除去することで、シリコン柱 4 の幅を広くすることができて、トレンチの幅を広くすることができる。

また、広いトレンチ幅でも、熱酸化膜 2 4 に変質したシリコン柱を残すことで、ウエハの反りを防止でき、また、溝 1 を微小とすることで、ブラックシリコンの発生を防止できる。

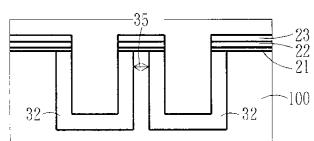

図 3 4 は、この発明の第 9 実施例の半導体装置の製造方法であり、同図 (a) から同図 (d) は工程順に示した要部製造工程断面図である。

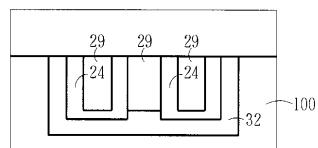

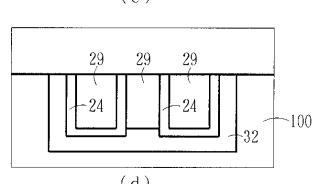

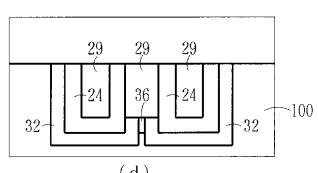

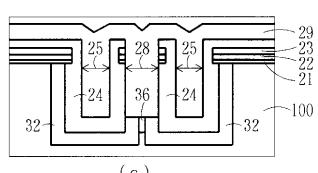

図 2 8 の工程に続いて、ポリシリコン層 3 1 を拡散源として、熱処理して、ドリフト領域となる拡散層 3 2 を形成する。この熱処理では、シリコン柱 4 の底部で直接的に拡散層が繋がらず未拡散領域 3 5 が残る。その後、熱酸化して、ポリシリコン層 3 1 と拡散層 3 2 の表面層を熱酸化膜 2 4 に変質させる。この熱酸化では拡散層 3 2 の表面層が熱酸化膜に変質するために、未酸化領域 2 7 が発生する。また、この熱酸化膜 2 4 で囲まれ、溝 1 より浅い溝 2 5 が形成される(同図 (a))。

#### 【 0 0 4 2 】

つぎに、未酸化領域 2 7 上を開口したレジスト 2 6 を形成し、溝 2 5 で挟まれた未酸化領域 2 7 を除去し、溝 2 8 を形成する。その後で、この溝 2 8 の底の半導体基板 1 0 0 にドリフト領域となる拡散層 3 6 を拡散層 3 2 と接するように形成する(同図 (b))。

つぎに、レジスト 2 6 を除去し、絶縁膜 2 9 を溝 2 5、2 8 を覆うように全面に形成する(同図 (c))。

つぎに、C M P 法で絶縁膜 2 9、酸化膜 2 1、窒化膜 2 2、酸化膜 2 3 を、半導体基板 1

10

20

30

40

50

00の表面高さまで除去し、平坦化する(同図(d))。

**【0043】**

第7実施例と同様の効果が得られるが、第7実施例よりさらに、シリコン柱4の幅を広げて、トレンチの幅を広げることができる。

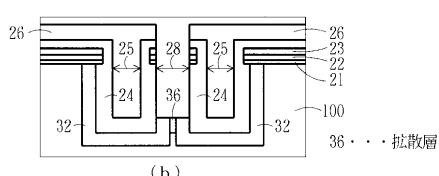

図35は、この発明の第10実施例の半導体装置の製造方法であり、同図(a)から同図(d)は工程順に示した要部製造工程断面図である。

図28の工程に続いて、ポリシリコン層31を拡散源として、熱処理して、ドリフト領域となる拡散層32を形成する。この熱処理では、シリコン柱4の底部で直接的に拡散層が繋がらず未拡散領域35が残る。その後、この拡散源となるポリシリコン層31を除去し、その後で熱酸化して、拡散層32の表面層を熱酸化膜24に変質させる。シリコン柱4の幅が広いために、この熱酸化ではシリコン柱4を完全には熱酸化膜24に変質させることができず、未酸化領域27が発生する。また、この熱酸化膜24で囲まれ、溝1より浅い溝25が形成される(同図(a))。

**【0044】**

つぎに、未酸化領域27上を開口したレジスト26を形成し、溝25で挟まれた未酸化領域27を除去し、溝28を形成する。その後で、この溝28の底の半導体基板100にドリフト領域となる拡散層36を拡散層32と接するように形成する(同図(b))。

つぎに、レジスト26を除去し、絶縁膜29を溝25、28を覆うように全面に形成する(同図(c))。

つぎに、CMP法で絶縁膜29、酸化膜21、窒化膜22、酸化膜23を、半導体基板100の表面高さまで除去し、平坦化する(同図(d))。

**【0045】**

第8実施例と同様の効果が得られるが、第8実施例よりさらに、シリコン柱4の幅が広い場合に有効となる。

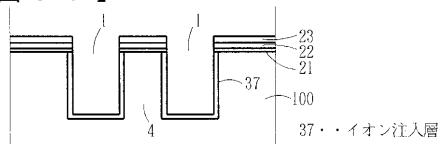

図36から図42は、この発明の第11実施例の半導体装置の製造方法であり、工程順に示した要部製造工程断面図である。

図27の工程に続いて、溝1の内壁に接する半導体基板100にイオン注入層37を形成する(図36)。

つぎに、熱処理し、ドリフト領域となる拡散層32を形成する。この熱処理では、シリコン柱4の底部で直接的に拡散層が繋がらず未拡散領域35が残る(図37)。

**【0046】**

つぎに、熱酸化して、拡散層32の表面層を熱酸化膜24に変質させる。この熱酸化では拡散層32を完全には熱酸化膜24に変質させることができず、未酸化領域27が発生する。また、この熱酸化膜24で囲まれ、図示しない溝1より浅い溝25が形成される(図38)。

つぎに、未酸化領域27上を開口したレジスト26を形成し、溝25で挟まれた未酸化領域27を除去し、溝28を形成する。その後で、この溝28の底の半導体基板100にドリフト領域となる拡散層36を拡散層32と接するように形成する(図39)。

**【0047】**

つぎに、レジスト26を除去し、絶縁膜29を溝25、28を覆うように全面に形成する(図40)。

つぎに、CMP法で絶縁膜29、酸化膜21、窒化膜22、酸化膜23を、半導体基板100の表面高さまで除去し、平坦化する(図41)。

前記した実施例と同様の効果が得られる。

つぎに、前記した実施例を用いて横型高耐圧MOSFETの製造方法について説明する。

図42は、この発明の第12実施例の半導体装置の要部製造工程断面図である。

**【0048】**

図23(d)、図24(e)、図25(e)、図32、図33(d)、図34(d)、図35(d)および図41の工程に続いて、ドリフト領域51に接するウエル領域53を半導体基板100の表面層に形成し、このウエル領域53の表面層にソース領域54を形成

する。また、ドリフト領域 5 1 と接するドレイン領域を半導体基板 1 0 0 の表面層に形成する。ソース領域 5 4 とドリフト領域 5 1 に挟まれた半導体基板 1 0 0 上に図示しないゲート絶縁膜を介してゲート電極 5 6 を形成する。ソース領域 5 4 上とドレイン領域 5 5 上にソース電極 5 7 とドレイン電極 5 8 をそれぞれ形成して、トレンチに沿うドリフト領域 5 1 を有する横型高耐圧 M O S F E T が製作される。

#### 【 0 0 4 9 】

尚、ドリフト領域 5 1 は、前記した各図の拡散層 3 2 、 3 6 である。また、絶縁膜 5 2 は、前記した各図の 2 4 、 2 9 、 3 3 である。

このようにして製作された高耐圧横型 M O S F E T は、その耐圧は数 1 0 0 V であり、また、微小な溝を形成した後でトレンチを形成するため、ブラックシリコンの発生が抑制され、トレンチ部での耐圧特性を向上できる。また、トレンチに沿うドレイン領域のため、ソース・ドレインの平面距離を短くできて、単位面積当たりのオン抵抗を低減できる。10

また、ドレイン領域を形成した後、拡散源を除去することで、後工程でのドリフト領域の不純物濃度の変調や他領域への汚染（拡散源からの拡散）を防止できる。また、トレンチ内に熱酸化したシリコン柱を残留させることで、幅広のトレンチ幅でもウエハの反りを抑制でき、半導体製造装置での搬送エラーの発生を防止できる。

#### 【 0 0 5 0 】

##### 【 発明の効果 】

この発明によれば、微小な溝を多数形成し、その後、この微小な溝で挟まれた多数の微小な半導体柱（シリコン柱）を除去してトレンチを形成することで、トレンチ底面に発生するブラックシリコンを抑制することができる。20

このブラックシリコンの発生を抑制することで、素子の電気的特性の向上と信頼性の向上を図ることができる。

また、微小な半導体柱が熱酸化膜に変質した箇所をトレンチ内で残留させることで、ウエハ裏面の酸化膜とのバランスがとれて、ウエハの反りを抑制することができる。また、徐々にトレンチを掘ることで、プロセス途中でのウエハの反りを防止できる。

#### 【 0 0 5 1 】

また、微小な溝内に、ドープされたポリシリコン層を形成し、熱処理でドリフト領域となる拡散層を形成した後、ポリシリコン層を除去することで、後工程での熱処理で、ドリフト領域の不純物濃度の変調や他領域への不純物拡散を防止できる。30

##### 【 図面の簡単な説明 】

【 図 1 】 半導体基板にトレンチを形成した平面図

【 図 2 】 図 1 の A 部の拡大図

【 図 3 】 図 1 の B 部の拡大図

【 図 4 】 図 1 の A 部の別の拡大図

【 図 5 】 図 4 の変形例の図

【 図 6 】 図 1 の B 部の別の拡大図

【 図 7 】 図 6 の変形例の図

【 図 8 】 図 2 から図 7 の X - X 線で切断した要部断面図

【 図 9 】 最終的に形成されるトレンチの断面形状であり、図 1 0 、図 1 1 の X - X 線で切断した断面図40

【 図 1 0 】 図 9 の平面図

【 図 1 1 】 図 9 の別の平面図

【 図 1 2 】 この発明の第 1 実施例の半導体装置の製造方法であり、( a ) から ( c ) は工程順に示した要部製造工程断面図

【 図 1 3 】 この発明の第 2 実施例の半導体装置の製造方法であり、( a ) から ( d ) は工程順に示した要部製造工程断面図

【 図 1 4 】 この発明の第 3 実施例の半導体装置の製造工程断面図

【 図 1 5 】 この発明の第 3 実施例の半導体装置の要部製造工程断面図

【 図 1 6 】 図 1 5 に続く、この発明の第 3 実施例の半導体装置の要部製造工程断面図50

【図17】図16に続く、この発明の第3実施例の半導体装置の要部製造工程断面図

【図18】図17に続く、この発明の第3実施例の半導体装置の要部製造工程断面図

【図19】図18に続く、この発明の第3実施例の半導体装置の要部製造工程断面図

【図20】図19に続く、この発明の第3実施例の半導体装置の要部製造工程断面図

【図21】図18の平面図

【図22】図18の別の平面図

【図23】この発明の第4実施例の半導体装置の製造方法であり、(a)から(d)は、工程順に示した要部製造工程断面図

【図24】この発明の第5実施例の半導体装置の製造方法であり、(a)から(e)は、工程順に示した要部製造工程断面図

【図25】この発明の第6実施例の半導体装置の製造方法であり、(a)から(e)は、工程順に示した要部製造工程断面図

【図26】この発明の第7実施例の半導体装置の要部製造工程断面図

【図27】図26に続く、この発明の第7実施例の半導体装置の要部製造工程断面図

【図28】図27に続く、この発明の第7実施例の半導体装置の要部製造工程断面図

【図29】図28に続く、この発明の第7実施例の半導体装置の要部製造工程断面図

【図30】図29に続く、この発明の第7実施例の半導体装置の要部製造工程断面図

【図31】図30に続く、この発明の第7実施例の半導体装置の要部製造工程断面図

【図32】図31に続く、この発明の第7実施例の半導体装置の要部製造工程断面図

【図33】この発明の第8実施例の半導体装置の製造方法であり、(a)から(d)は工程順に示した要部製造工程断面図

【図34】この発明の第8実施例の半導体装置の製造方法であり、(a)から(d)は工程順に示した要部製造工程断面図

【図35】この発明の第10実施例の半導体装置の製造方法であり、(a)から(d)は工程順に示した要部製造工程断面図

【図36】この発明の第11実施例の半導体装置の要部製造工程断面図

【図37】図36に続く、この発明の第11実施例の半導体装置の要部製造工程断面図

【図38】図37に続く、この発明の第11実施例の半導体装置の要部製造工程断面図

【図39】図38に続く、この発明の第11実施例の半導体装置の要部製造工程断面図

【図40】図39に続く、この発明の第11実施例の半導体装置の要部製造工程断面図

【図41】図40に続く、この発明の第11実施例の半導体装置の要部製造工程断面図

【図42】図41に続く、この発明の第11実施例の半導体装置の要部製造工程断面図

【図43】従来の横型高耐圧MOSFETの要部断面図

#### 【符号の説明】

1、28 溝

2 第1の溝

3 第2の溝

4 シリコン柱

11、13、29、33、52 絶縁膜

12、24 熱酸化膜

21 酸化膜

22 室化膜

23 酸化膜

25 溝

26 レジスト

27 未酸化領域

31 ポリシリコン層

32 拡散層(ドリフト領域)

34、37 イオン注入層

35 未拡散領域

10

20

30

40

50

3 6 拡散層

5 1 ドリフト領域

5 3 ウエル領域

5 4 ソース領域

5 5 ドレイン領域

5 6 ゲート電極

5 7 ソース電極

5 8 ドレイン電極

1 0 0 半導体基板

1 0 1、1 0 2 トレンチ

2 0 0 半導体チップ

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

(a)

(b)

(c)

(d)

(e)

【図25】

(a)

(b)

(c)

(d)

(e)

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図3-2】

【図3-3】

【図3-4】

【図3-5】

【図3 6】

【図3 7】

【図3 8】

【図3 9】

【図4 0】

【図4 1】

【図4 2】

【図4 3】

---

フロントページの続き

(72)発明者 脇本 節子

神奈川県川崎市川崎区田辺新田1番1号 富士電機株式会社内

(72)発明者 須ヶ原 紀之

神奈川県川崎市川崎区田辺新田1番1号 富士電機株式会社内

F ターム(参考) 5F032 AA35 AA44 AA67 AA77 BA02 CA17 CA24 DA02 DA23 DA25

DA53 DA78

5F140 AA25 AC21 BA01 BH05 BH07 BH14 BH30 BH41 BH45 BK09

BK13 BK16 BK21 CE07