(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5729947号

(P5729947)

(45) 発行日 平成27年6月3日(2015.6.3)

(24) 登録日 平成27年4月17日(2015.4.17)

(51) Int.Cl.

G02B 7/34 (2006.01)

H04N 5/232 (2006.01)

F 1

G02B 7/34

H04N 5/232

A

請求項の数 11 (全 20 頁)

(21) 出願番号 特願2010-191315 (P2010-191315)

(22) 出願日 平成22年8月27日 (2010.8.27)

(65) 公開番号 特開2012-48064 (P2012-48064A)

(43) 公開日 平成24年3月8日 (2012.3.8)

審査請求日 平成25年8月26日 (2013.8.26)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 斎藤 和宏

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 井上 大介

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置、焦点検出装置、および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の光電変換部と、

第2の光電変換部と、

前記第1および第2の光電変換部の各々の電荷を電圧に変換する浮遊拡散部と、

前記浮遊拡散部に接続され、前記浮遊拡散部の電位と対応した電位となる入力ノードを備えるとともに、前記入力ノードの電位に基づく信号を出力する画素出力部と、

前記第1の光電変換部で生成された電荷を前記浮遊拡散部に転送する第1の転送部と、

前記第2の光電変換部で生成された電荷を前記浮遊拡散部に転送する第2の転送部と、を各々が有する複数の単位画素と、前記第2の転送部を導通させることにより前記第2の光電変換部で生成された電荷が転送された前記浮遊拡散部の電位に対応して前記画素出力部が出力する信号に基づいて、前記第1の光電変換部の電荷蓄積期間の長さを制御するモニタ部と、

を有することを特徴とする光電変換装置。

## 【請求項 2】

前記モニタ部は、複数の前記単位画素から出力される信号の最大値と最小値との差分に基づいて前記第1の光電変換部の電荷蓄積動作を制御することを特徴とする請求項1に記載の光電変換装置。

## 【請求項 3】

前記単位画素の各々は、前記画素出力部から出力された信号を増幅する信号出力部をさ

10

20

らに有することを特徴とする請求項 1 または 2 に記載の光電変換装置。

**【請求項 4】**

前記信号出力部の各々は、前記画素出力部で生じるノイズを低減するノイズ低減回路をさらに有することを特徴とする請求項 3 に記載の光電変換装置。

**【請求項 5】**

前記第 1 の光電変換部は、前記第 2 の光電変換部よりも受光面積が大きいことを特徴とする請求項 1 ないし 4 のいずれかに記載の光電変換装置。

**【請求項 6】**

前記モニタ部は、前記第 1 の転送部が非導通である期間に前記第 2 の転送部が導通することによって前記画素出力部から出力される、前記第 2 の光電変換部で生成された電荷に基づく信号に基づいて前記第 1 の光電変換部の電荷蓄積期間の長さを制御し、10

前記第 1 の光電変換部の前記電荷蓄積期間後であって前記第 2 の転送部が非導通である期間に、前記第 1 の転送部が導通することによって、前記第 1 の光電変換部が前記電荷蓄積期間に蓄積した電荷が前記浮遊拡散部に転送されることを特徴とする請求項 1 ないし 5 のいずれかに記載の光電変換装置。

**【請求項 7】**

前記モニタ部が、前記第 2 の転送部が導通している期間の長さを、前記第 2 の光電変換部で生成された電荷に基づく前記画素出力部から出力された信号に基づいて制御することを特徴とする請求項 1 ないし 5 のいずれかに記載の光電変換装置。20

**【請求項 8】**

前記浮遊拡散部に接続され、前記浮遊拡散部の電位をリセットするリセット部をさらに有し、

前記電荷蓄積期間に先立つ期間である第 1 の期間に、前記リセット部が前記浮遊拡散部の電位をリセットするとともに、前記前記第 1 の転送部と前記第 2 の転送部の各々が導通することによって前記第 1 の光電変換部と前記第 2 の光電変換部の各々の電荷がリセットされ、

前記第 1 の期間の後に前記第 1 の転送部が導通から非導通に切り替わることで前記第 1 の光電変換部のリセットが解除されるとともに、前記電荷蓄積期間の終了まで前記第 1 の転送部は非導通のままであって、前記第 2 の転送部が導通したまま、前記浮遊拡散部のリセットを解除することで前記第 2 の光電変換部のリセットが解除され、前記第 2 の転送部が前記電荷蓄積期間まで導通を維持することによって、前記第 1 の期間から前記電荷蓄積期間の終了までにおいて、前記第 2 の転送部が導通している期間の長さが、前記第 1 の転送部が導通している期間の長さよりも長いことを特徴とする請求項 1 ないし 7 のいずれかに記載の光電変換装置。30

**【請求項 9】**

請求項 1 ないし 8 のいずれかに記載の光電変換装置を有する焦点検出装置。

**【請求項 10】**

請求項 9 に記載の焦点検出装置と、被写体の光学像に基づく画像信号を生成する撮像装置とを備える撮像システム。

**【請求項 11】**

第 1 の光電変換部と、40

第 2 の光電変換部と、

前記第 1 および第 2 の光電変換部の各々の電荷を電圧に変換する浮遊拡散部と、

前記浮遊拡散部に接続され、前記浮遊拡散部の電位と対応した電位となる入力ノードを備えるとともに、前記入力ノードの電位に基づく信号を出力する画素出力部と、

を各々が有する複数の単位画素を有する光電変換装置の駆動方法であって、

前記第 2 の光電変換部で生成された電荷を、前記第 1 の光電変換部の電荷を前記浮遊拡散部に転送しない期間に前記浮遊拡散部に転送することによって前記画素出力部が出力する信号に基づいて、前記第 1 の光電変換部の電荷蓄積期間の長さを制御し、

前記第 1 の光電変換部の前記電荷蓄積期間後に、前記第 1 の光電変換部の電荷を、前記50

第2の光電変換部の電荷を前記浮遊拡散部に転送しない期間に前記浮遊拡散部に転送することを特徴とする光電変換装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は光電変換装置に関し、特に、位相差検出型オートフォーカス(Auto Focusing; AF)を行う光電変換装置に関する。

【背景技術】

【0002】

オートフォーカス(Auto Focusing; 以下、AFとする)用のセンサとして、被写体の位置情報を検出するための受光部に加えて、受光部の蓄積時間を制御するために光量を検出するモニタ用センサを備えるものが知られている。特許文献1には、位置情報検出用の受光部からの信号を伝達する経路と、モニタ用センサからの信号を伝達する経路とが互いに異なる構成を取っている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009-239788号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1に開示された構成では、位置情報検出用の受光部とモニタ用センサとで、出力される信号が互いに異なる検出回路で処理されるため、検出回路間の誤差がAFの特性に悪影響を及ぼす恐れがある。さらに、検出回路の数が増大することに起因して、装置の大型化や消費電力の増大をもたらす恐れもあった。

【0005】

本発明は、上述の問題を鑑みて、光電変換装置における信号検出の精度を向上し、かつ、装置の大型化および消費電力の増大を抑制することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するための本発明は、第1の光電変換部と、第2の光電変換部と、前記第1および第2の光電変換部の各々の電荷を電圧に変換する浮遊拡散部と、前記浮遊拡散部に接続され、前記浮遊拡散部の電位と対応した電位となる入力ノードを備えるとともに、前記入力ノードの電位に基づく信号を出力する画素出力部と、前記第1の光電変換部で生成された電荷を前記浮遊拡散部に転送する第1の転送部と、前記第2の光電変換部で生成された電荷を前記浮遊拡散部に転送する第2の転送部と、を各々が有する複数の単位画素と、前記第2の転送部を導通させることにより前記第2の光電変換部で生成された電荷が転送された前記浮遊拡散部の電位に対応して前記画素出力部が出力する信号に基づいて、前記第1の光電変換部の電荷蓄積期間の長さを制御するモニタ部と、を有することを特徴とする光電変換装置である。

【発明の効果】

【0007】

本発明によれば、光電変換装置における信号検出の精度を向上し、かつ、装置の大型化および消費電力の増大を抑制することができる。

【図面の簡単な説明】

【0008】

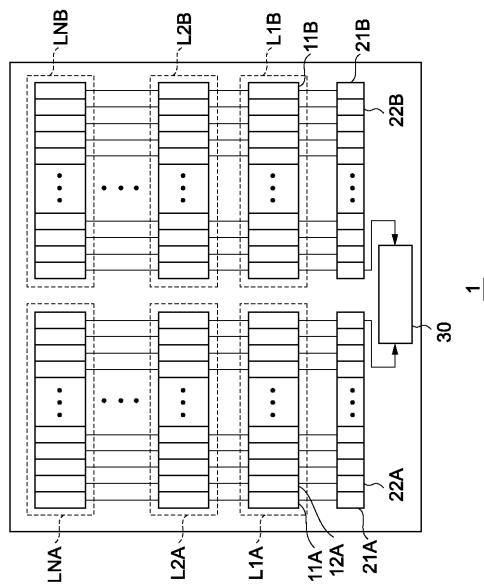

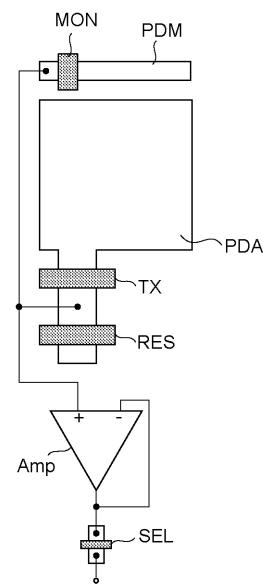

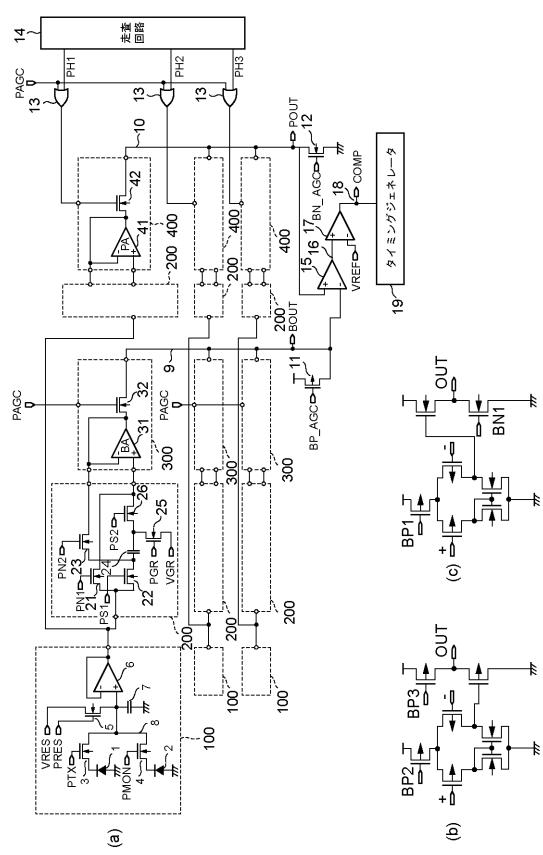

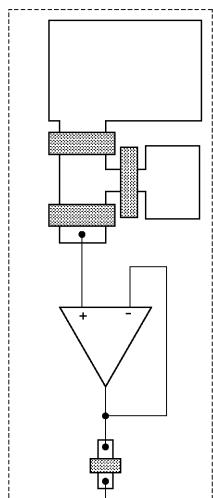

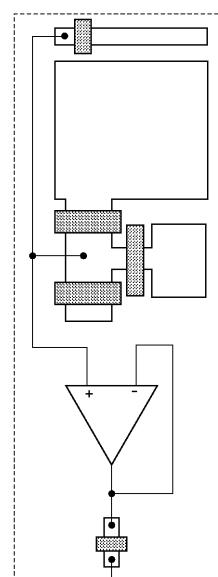

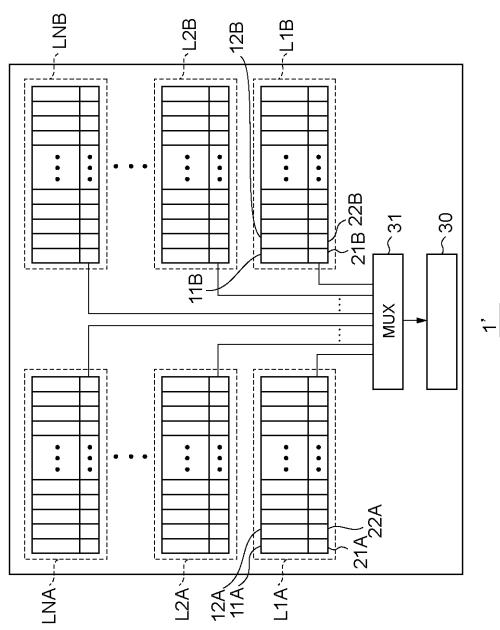

【図1】本発明に係るAF用の光電変換装置の主要な構成を示す図

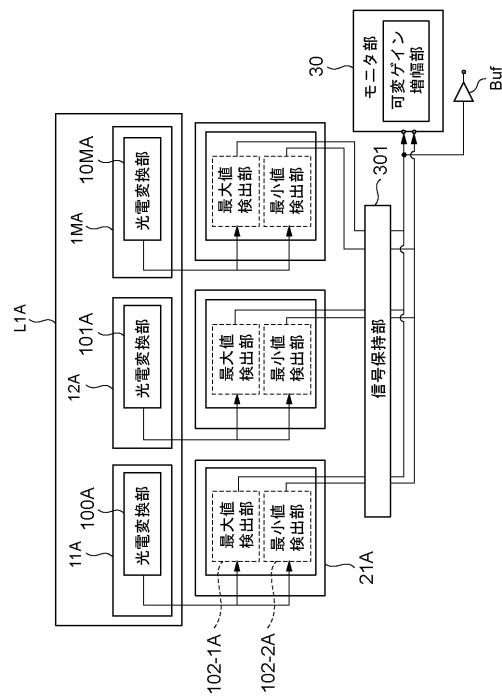

【図2】本発明に係るラインセンサ部の主要な構成を示す図

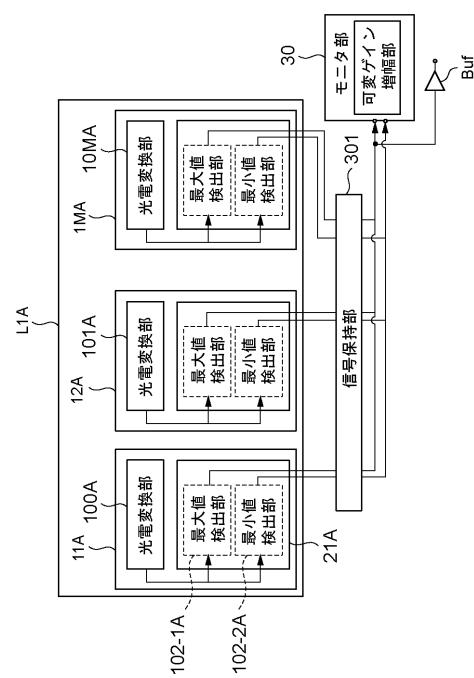

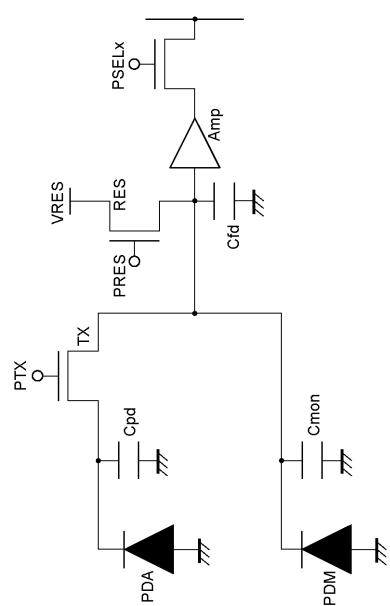

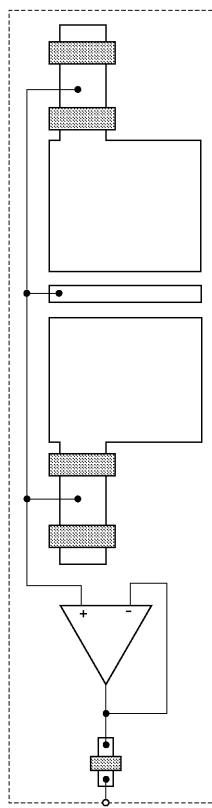

【図3】実施例1に係る単位画素の等価回路図

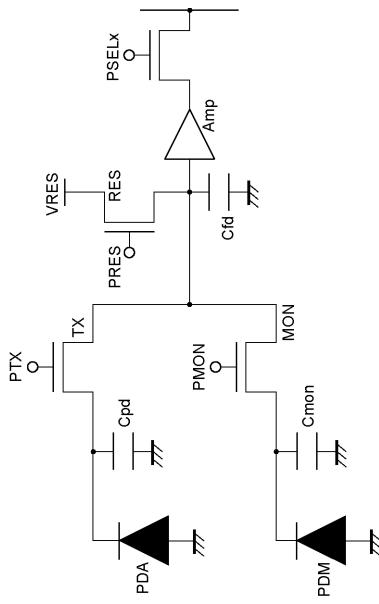

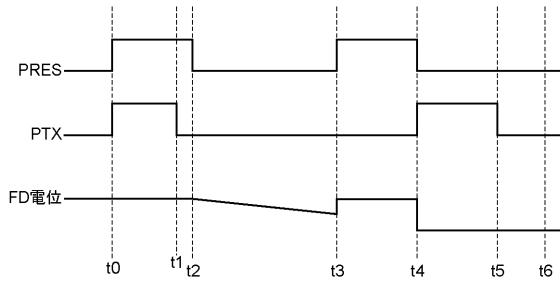

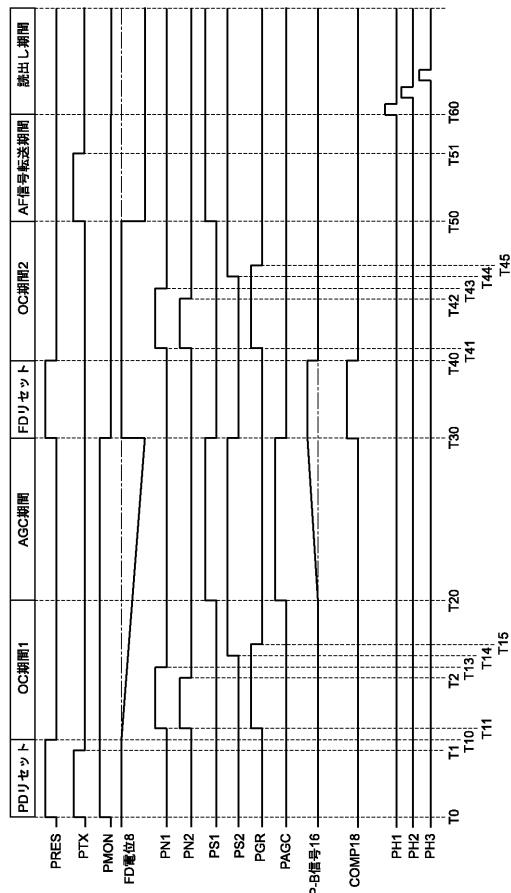

【図4】実施例1に係るタイミング図

10

20

30

40

50

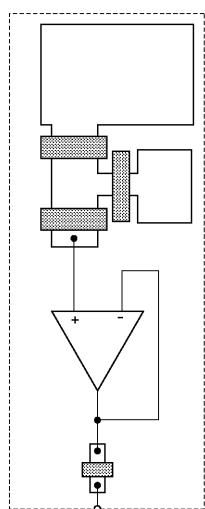

【図5】実施例1に係る単位画素の平面レイアウト図

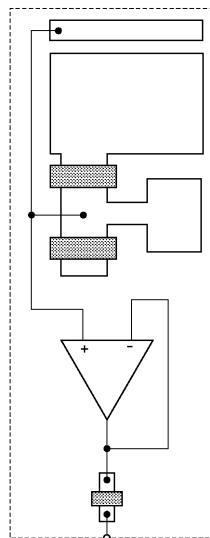

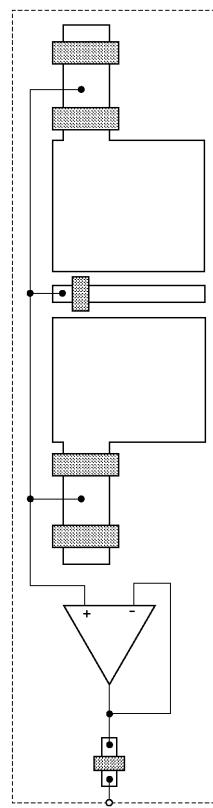

【図6】実施例2に係る単位画素の等価回路図

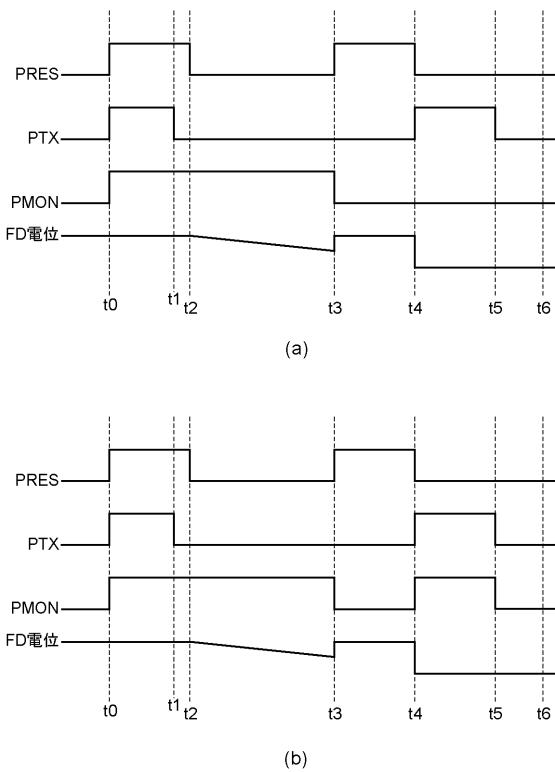

【図7】実施例2に係るタイミング図

【図8】実施例2に係る単位画素の平面レイアウト図

【図9】実施例3に係るラインセンサ部の主要な構成を示す図

【図10】実施例3に係るタイミング図

【図11】実施例4に係る単位画素の平面レイアウト図

【図12】実施例5に係る単位画素の平面レイアウト図

【図13】実施例6に係る単位画素の平面レイアウト図

【図14】実施例7に係る単位画素の平面レイアウト図

10

【図15】実施例8に係る単位画素の平面レイアウト図

【図16】実施例9に係る単位画素の平面レイアウト図

【図17】実施例10に係るAF用の光電変換装置の主要な構成を示す図

【図18】実施例10に係るラインセンサ部の主要な構成を示す図

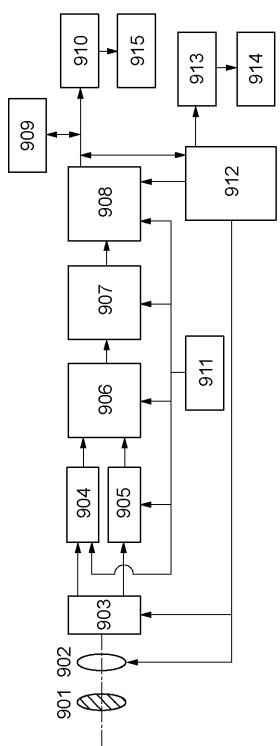

【図19】実施例11に係る撮像システムの構成を示すブロック図

【発明を実施するための形態】

【0009】

(実施例1)

本発明に係る第1の実施例を以下に説明する。第1の実施例は、位相差方式の焦点検出(Auto Focusing; 以下AFとする)用の光電変換装置に適用した例を示す。

20

【0010】

図1は、位相差AF用の光電変換装置の主要な構成を模式的に示した図である。光電変換装置1は、対となるラインセンサ部L1AとL1B、L2AとL2B、…LN AとLN Bを有する。一对のラインセンサ部は撮像面のある領域における被写体のデフォーカス量を測定するために用いられ、このラインセンサ部の対を複数配列することで測距点を複数設け、AFの精度の向上を図るものである。各ラインセンサ部は、それぞれが位相差情報を検出するためのAF用光電変換部と、光量を検出するためのモニタ用光電変換部と、を有する単位画素11A、12A、…を含んでいる。複数のラインセンサ部L1A、L2A、…、LN AおよびL1B、L2B、…、LN Bの単位画素同士は、画素毎に共通の信号出力部21A、22A、…および21B、22B、…を介して信号を例えばモニタ部30に出力する。

30

【0011】

図2は、ラインセンサ部L1Aに係る部分をより詳細に示した図である。単位画素11Aは、光電変換部100A、信号出力部21Aとを含み、信号出力部21Aは最大値検出部102-1Aと最小値検出部102-2Aとを含んで成る。光電変換部から出力された信号は最大値検出部102-1Aと最小値検出部102-2Aとに供給される。最大値検出部102-1Aおよび最小値検出部102-2Aは例えばソースフォロワアンプである。このほか、信号検出の精度を向上させるために、ノイズ除去回路を含んでも良い。他の単位画素は単位画素11Aと同じ構成である。ラインセンサ部L2A、L3A、…、L1B、L2B、…もラインセンサ部L1Aと同様の構成なので、説明を省略する。

40

【0012】

各単位画素の最大値検出部及び最小値検出部の出力は信号保持部301を介してモニタ部30へと導かれる。信号保持部301は、最大値検出部から出力された信号を一時的に保持する保持部を有するとともに、最大値検出部及び最小値検出部の信号を保持することなくモニタ部30に伝達する経路を有する。後述するモニタ動作を行う期間には、信号を一次保持することなくモニタ部30に信号を伝達することでリアルタイムな光量のモニタリングを実現する。そして、各単位画素からの信号を読み出す場合には、ラインセンサ部内で蓄積時間を揃えるために一時的に信号を信号保持部301で保持し、保持された信号を不図示の走査回路によって順次、出力バッファBufへと伝達する。

50

## 【0013】

各単位画素の最大値検出部の出力端子同士、並びに最小値検出部の出力端子同士は、信号保持部301の後段でそれぞれ共通に接続されており、モニタ部へと入力される。この構成により、ラインセンサ部L1Aの信号出力の最大値と最小値とがモニタ部でリアルタイムに検出され、最大値と最小値の差分信号（以下、P-B信号）が予め定められた閾値を超えると、モニタ部30から光電変換部の電荷蓄積動作を終了させる信号が出力される。上記の閾値とは、使用条件によって変更されるものである。また、モニタ部30は可変ゲイン増幅部を含み、P-B信号が十分なコントラストを得られないときに信号に対する増幅率を増大させる。

## 【0014】

ここでは各単位画素からの信号を個別に読み出すために最大値検出部を用いているが、最大値検出部に換えて最小値検出部を用いても良い。

## 【0015】

図3は、光電変換検出部101に係る部分をより詳細に示した等価回路図である。

## 【0016】

図3において、PDAは位相差情報を検出するためのフォトダイオード、PDMは光量を検出するためのモニタ用のフォトダイオードである。フォトダイオードのPDAのアノードは転送トランジスタTXを、フォトダイオードPDMのアノードは転送トランジスタMONを介してアンプAMPの入力ノードに接続される。CpdはフォトダイオードPDAと転送トランジスタTXとの寄生容量を、そしてCmonはフォトダイオードPDMと転送トランジスタMONとの寄生容量を意味している。アンプAMPの入力ノードには、浮遊拡散部の容量としてのFD容量Cfdと、リセットトランジスタRESとが接続される。信号PTXがハイレベルになると転送トランジスタTXが導通し、容量Cpdに蓄積された電荷がFD容量Cfdに転送される。また、信号PMONがハイレベルになると転送トランジスタMONが導通し、容量Cmonに蓄積された電荷がFD容量Cfdに転送される。信号PRESがハイレベルになるとリセットトランジスタRESが導通し、アンプAMPの入力ノードを電源電圧VRESに応じてリセットする。信号PTX、PMON、PRES、PSELxは、例えば不図示のタイミング生成部から与えられる。ここでPDAは第1の光電変換部、PDMは第2の光電変換部、TXは第1の転送部、MONは第2の転送部、アンプAMPが画素出力部、リセットトランジスタRESがリセット部に、それぞれ対応する。

## 【0017】

次に、フォトダイオードPDAとPDMと電源電圧VRESとの関係を説明する。

## 【0018】

位相差情報検出用のフォトダイオードPDA及びモニタ用のフォトダイオードPDMは、ともにリセットトランジスタRESによって逆バイアス状態にリセットされる。ここで、リセットトランジスタRESによってリセットされたときに、フォトダイオードPDAは空乏化し、フォトダイオードPDMは空乏化しないようにする。これにより、フォトダイオードPDAの容量Cpdの容量値はほぼ無視できる値になる。一方、容量Cmonの容量値は、空乏化していない受光部の寄生容量が支配的となる。また、FD部の容量Cfdは、転送スイッチTX、MON、リセットスイッチRES、アンプAMPの入力ノード、ならびに付随する配線による配線容量が寄与する。典型的には、容量値の大きさはCmon > Cfd > Cpdとなる。

## 【0019】

次に、本実施例に係る光電変換装置の動作を、図4(a)を参照しながら説明する。この動作は、被写体の輝度が低い条件で有効なものである。図4は、信号RES、PTX、PMONに加えて、アンプAMPの入力ノードの電位(FD電位と表記)を示している。図4(a)には示していないが、信号PSELxはこの期間内で常時ハイレベルにあるものとする。また、対となっているラインセンサ部は同時に動作するように制御されている。

10

20

30

40

50

**【 0 0 2 0 】**

まず、時刻  $t_0$  に信号 P R E S、P T X、P M O N がハイレベルになると、これに対応してリセットトランジスタ R E S、転送トランジスタ T X および M O N が導通する。これにより、フォトダイオード P D A、P D M、アンプ A m p の入力ノードが電源電圧 V R E S によってリセットされる。

**【 0 0 2 1 】**

時刻  $t_1$  に信号 P T X がローレベルになると転送トランジスタ T X がオフすることで、フォトダイオード P D A が電荷を蓄積する状態になる。この時点ではリセットトランジスタ R E S が導通しているので、F D 電位は変化しない。

**【 0 0 2 2 】**

時刻  $t_2$  に信号 P R E S がローレベルになるとリセットトランジスタ R E S がオフし、フォトダイオード P D M のリセット状態が解除される。この時点から、フォトダイオード P D M で発生した電荷によって F D 電位が変化する。

**【 0 0 2 3 】**

時刻  $t_2$  から時間が経過し、モニタ部 3 0 で検出される P - B 信号が予め定められた閾値を超えると（時刻  $t_3$ ）、信号 P R E S がハイレベルになるとともに信号 P M O N がローレベルになる。これによりフォトダイオード P D M とアンプ A m p の入力ノードとの接続が遮断され、F D 電位が電源電圧 V R E S によってリセットされる。

**【 0 0 2 4 】**

時刻  $t_4$  から時刻  $t_5$  の期間に信号 P T X がハイレベルになり、位相差情報検出用のフォトダイオード P D A に蓄積された電荷が F D 容量 C f d に転送される。以上をもって位相差情報検出用のフォトダイオード P D A の蓄積時間の制御が終了する。

**【 0 0 2 5 】**

時刻  $t_6$  から、各最大値検出部からの出力を、不図示の走査回路によって出力バッファ B u f に順次伝達することで、単位画素毎の個別信号を得る。

**【 0 0 2 6 】**

以上で説明した動作によれば、時刻  $t_3$  に転送トランジスタ M O N をオフした後に、フォトダイオード P D A に蓄積された電荷を F D 容量 C f d に転送している。そのため、位相差情報を検出する際にアンプ A m p の入力ノードに付随する容量は F D 容量 C f d のみとなり、電荷電圧変換係数が大きくなる。言い換えると、フォトダイオード P D A で発生する電荷量が少ない場合でも、電圧信号として検出することができる範囲を広げることが可能となるので、被写体が低輝度である場合でも合焦させることが容易となる。

**【 0 0 2 7 】**

次に、本実施例に係る光電変換装置の動作を、図 4 ( b ) を参照しながら説明する。この動作は、被写体の輝度が高い条件で有効なものである。図 4 ( a ) に示した動作との相違点は、時刻  $t_4$  ~  $t_5$  の間に信号 P M O N がハイレベルになり、モニタ用のフォトダイオード P D M が F D 部と導通する点である。

**【 0 0 2 8 】**

この動作によれば、フォトダイオード P D A に蓄積された電荷を F D 容量 C f d に転送する時にアンプ A m p の入力ノードに付随する容量は F D 容量 C f d にフォトダイオード P D M の容量 C m o n が加わったものとなる。そのため、電荷変換係数が小さくなるので、被写体が高輝度であったとしても、飽和せずに電圧信号として検出できる範囲を広げることが可能となる。

**【 0 0 2 9 】**

本実施例によれば、リセット時にフォトダイオード P D A は空乏化し、フォトダイオード P D M は完全空乏化しない。このため、低輝度条件では小さい容量値の C p d により電荷電圧変換係数を大きくすることができ、高輝度条件では大きな容量値の C m o n を加えることで電荷電圧変換係数を小さくすることができ、広範な輝度条件に対応することを可能とする。特に低輝度条件ではフォトダイオード P D A の容量値が小さいことから感度の向上も実現できる。

10

20

30

40

50

**【0030】**

図4(a)の動作を第1のモード、図4(b)の動作を第2のモードとして、被写体の輝度に応じて第1と第2のモードを切り換えることで、精度良く検出できる輝度条件の範囲、すなわちダイナミックレンジを拡大することが可能となる。

**【0031】**

次に、モニタ部30で判定する、単位画素の電荷蓄積動作を終了させるレベルについて説明を行う。

**【0032】**

単位画素から出力された信号に対して、モニタ部30に入力されるまでにかかるゲインをGとして、低輝度時、すなわち高ゲイン時にモニタ部30に入力される信号をVhigh、高輝度時、すなわち低ゲイン時にモニタ部30に入力される信号をVlowとする、それぞれ以下のように表される。ここで、QpdはフォトダイオードPDAで発生した電荷量、QmonはフォトダイオードPDMで発生した電荷量を意味する。

**【0033】****【数1】**

低輝度時：

$$V_{high} = G \times \frac{Q_{pd}}{C_{fd} + C_{pd}} \quad (1)$$

**【0034】****【数2】**

高輝度時：

$$V_{low} = G \times \frac{Q_{pd} + Q_{mon}}{C_{mon} + C_{fd} + C_{pd}} \quad (2)$$

**【0035】**

式(1)、(2)から明らかなように、低輝度時と高輝度時とでは信号の振幅が異なる。しかし、モニタ部30に入力される信号の振幅は被写体の条件によらずある振幅レンジ内に入ることが望ましい。その所望の値をVtargetとすると、ある時刻tにモニタ部30に入力される信号をVagc(t)として、以下の関係にあることが求められる。

**【0036】****【数3】**

低輝度時：

$$V_{target} \times \frac{V_{high}}{V_{agc}} = \frac{Q_{pd}}{Q_{mon}} \times \frac{C_{mon} + C_{fd}}{C_{fd} + C_{pd}} \quad (3)$$

**【0037】****【数4】**

高輝度時：

$$V_{target} \times \frac{V_{low}}{V_{agc}} = \frac{Q_{pd} + Q_{mon}}{Q_{mon}} \times \frac{C_{mon} + C_{fd}}{C_{mon} + C_{fd} + C_{pd}} \quad (4)$$

**【0038】**

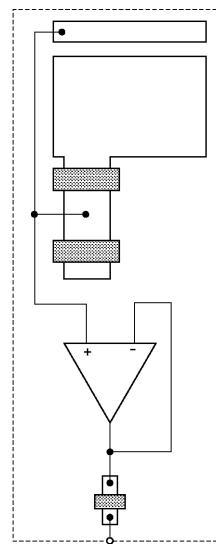

次に、本実施例に係る単位画素を半導体基板上に作成する場合の平面レイアウト例を図5に示す。ここでは、アンプAmpとして演算増幅器を用いた電圧フォロワとした場合を例示している。

**【0039】**

図5から明らかなように、単位画素11A、12A、…が配列される繰り返し方向を第1の方向として、フォトダイオードPDAとフォトダイオードPDMとは、第1の方向に対して直交する第2の方向に沿って配列されている。AF用の光電変換装置において、単位画素のフォトダイオードPDAとフォトダイオードPDMとが第1の方向に沿って配列されていると、画素ピッチの狭小化への対応が困難となる。さらに、同一の単位画素でありながら、第1の方向に異なる位置からの入射光を用いてモニタ動作を行うためにモニタ動作の精度が十分でなくなる恐れがある。

10

20

30

40

50

**【 0 0 4 0 】**

これに対して、図5に示したようなレイアウトにすることで、第1の方向としては同じ位置からの入射光を用いてモニタ動作を行うことが可能となる。これにより画素ピッチの狭小化に対応できるだけでなく、モニタ動作の精度を向上させることができる。

**【 0 0 4 1 】**

また、フォトダイオードPDAは、フォトダイオードPDMよりも受光面積が大きくなるように設計される。これは、位相差情報として用いるフォトダイオードPDAで生成される電荷量を多くする目的である。

**【 0 0 4 2 】**

(実施例2) 10

本発明にかかる第2の実施例を以下に説明する。第2の実施例は、位相差方式の焦点検出用の光電変換装置に適用した例を示す。第1の実施例との相違点は、モニタ用のフォトダイオードPDMとFD部との間に転送スイッチMONがない点である。電源電圧VRESによるリセット時に、フォトダイオードPDAは空乏化し、フォトダイオードPDMは完全に空乏化しない点は実施例1と同じである。

**【 0 0 4 3 】**

図6は、本実施例に係る等価回路図である。図3と同じ構成には同じ符号を付している。図7は、本実施例に係る動作を説明するためのタイミング図である。図7には示していないが、信号PSELxはこの期間内で常時ハイレベルにあるものとする。また、対となっているラインセンサ部は同時に動作するように制御されている。

**【 0 0 4 4 】**

時刻t0に信号PRESおよびPTXがハイレベルになると、これに対応してリセットトランジスタRESおよび転送トランジスタTXがオンする。これにより、フォトダイオードPDA、PDM、アンプAmpの入力ノードが電源電圧VRESによってリセットされる。

**【 0 0 4 5 】**

時刻t1に信号PTXがローレベルになると、これに対応してリセットトランジスタRESがオフし、フォトダイオードPDAが電荷を蓄積する状態になる。この時点においてはリセットトランジスタRESがオンしているので、FD電位およびモニタ用のフォトダイオードPDMの電位は変化しない。

**【 0 0 4 6 】**

時刻t2に信号PRESがローレベルになるとリセットトランジスタRESがオフし、フォトダイオードPDMのリセット状態が解除される。この時点から、フォトダイオードPDMで発生した電荷によってFD電位が変化する。

**【 0 0 4 7 】**

時刻t2から時間が経過し、モニタ部30で検出されるP-B信号が予め定められた閾値を超えると(時刻t3)、信号PRESがハイになり、アンプAmpの入力ノードおよびフォトダイオードPDMが電源電圧VRESによってリセットされる。

**【 0 0 4 8 】**

時刻t4に信号PRESがローレベルに遷移すると入れ替わりに、信号PTX時刻t5までの期間にハイレベルになる。これにより、位相差情報検出用のフォトダイオードPDAに蓄積された電荷がFD容量Cfdに転送される。以上をもって位相差情報検出用のフォトダイオードPDAの蓄積時間が終了する。

**【 0 0 4 9 】**

時刻t6から、各最大値検出部からの出力を、不図示の走査回路によって出力バッファに順次伝達することで、単位画素毎の個別信号を得る。

**【 0 0 5 0 】**

本実施例では、FD部とフォトダイオードPDMとが常に電気的に接続されているために容量Cfdに加えて容量Cmonを含めて電荷電圧変換を行うことになる。

**【 0 0 5 1 】**

10

20

30

40

50

このように、位相差情報検出用のフォトダイオード P D A は、蓄積期間中に転送トランジスタによって F D 容量から電気的に切断されているために蓄積期間中に F D 容量で生じる暗電流の影響を受けない。これにより、高精度に情報を読み出すことが可能となる。さらに、転送スイッチ M O N が省略されたことにより受光部の面積をより大きくすることが可能となり、感度の向上に寄与する。また、単位画素の制御が容易になるという利点もある。

#### 【 0 0 5 2 】

本実施例に係る単位画素を半導体基板上に作成する場合の平面レイアウトを図 8 に示す。

#### 【 0 0 5 3 】

図 8 から明らかなように、単位画素 1 1 A、1 2 A、・・・が配列される繰り返し方向を第 1 の方向として、フォトダイオード P D A とフォトダイオード P D M とは、第 1 の方向に対して直交する第 2 の方向に沿って配列されている。このようなレイアウトにすることで、第 1 の方向としては同じ位置からの入射光を用いてモニタ動作を行うことが可能となる。これにより画素ピッチの狭小化に対応できるだけでなく、モニタ動作の精度を向上させることができる。

#### 【 0 0 5 4 】

##### ( 実施例 3 )

次に、本発明にかかる第 3 の実施例を説明する。

#### 【 0 0 5 5 】

本実施例は、第 1 の実施例で説明した構成に対して、ノイズ低減回路としてのオフセットキャンセル回路をさらに設けたものである。図 9 ( a ) は、ラインセンサ部 L 1 A のうちの 1 画素を抜き出した模式的な回路図である。説明を簡単にするために、図 3 に示した単位画素の構成から、選択スイッチ S E L を省略している。また、タイミングジェネレータ 1 5 は信号 P T X 、 P M O N 、 P R E S 、 P S E L 、 P A G C 、などを出力して、光電変換装置の動作を制御する。

#### 【 0 0 5 6 】

図 9 ( a ) の O C 1 は最小値検出部用のオフセットキャンセル回路であって、 O C 2 は最大値検出部用のオフセットキャンセル回路である。

#### 【 0 0 5 7 】

最小値検出部は差動アンプ B A とスイッチとを含んで成り、差動アンプ B A の出力がオフセットキャンセル回路 O C 1 にフィードバックされる構成となっている。複数の最小値検出部の出力は信号線 9 に共通に接続されており、端子 B O U T に出力された信号がモニタ部 3 0 に与えられる。また、複数の最小値検出部のスイッチは共通の信号 P A G C によって制御される。

#### 【 0 0 5 8 】

最小値検出部の差動アンプ B A の構成例を図 9 ( b ) に示す。差動アンプ B A は、差動增幅アンプと、ソースフォロワ出力段とを含む。信号 B P 2 は外部から与えられる信号であって、差動入力段に流れる電流を制御するためのものである。また、信号 B P 3 はソースフォロワ出力段の定電流源を制御するためのものである。

#### 【 0 0 5 9 】

信号線 9 に接続されたトランジスタ 1 1 は、最小値検出部のスイッチが信号 P A G C によってオンした際にソースフォロワ出力段の定電流源として機能する。

#### 【 0 0 6 0 】

最大値検出部の差動アンプ P A の構成例を図 9 ( c ) に示す。差動アンプ B A との違いは、ソースフォロワ出力段の極性が逆である点である。

#### 【 0 0 6 1 】

最大値検出部は差動アンプ P A とスイッチとを含んで成り、差動アンプ P A の出力がオフセットキャンセル回路 O C 2 にフィードバックされる構成となっている。複数の最大値検出部の出力は信号線 1 0 に共通に接続されており、端子 P O U T に出力された信号がモ

10

20

30

40

50

ニタ部 30 に与えられる。信号 P A G C は外部から与えられる信号であって、差動入力段に流れる電流を制御するためのものである。また、信号 P H 1 はソースフォロワ出力段の定電流源を制御するためのものである。

#### 【 0 0 6 2 】

複数の最大値検出部のスイッチは、共通の信号 P A G C によって制御される一方で、走査回路から出力される信号 P H 1 、 P H 2 、 ··· によっても制御することが可能であるため、単位画素から出力された信号を個別に読み出すことが可能となる。

#### 【 0 0 6 3 】

信号線 10 に接続されたトランジスタ 12 は、最大値検出部のスイッチが信号 P A G C によってオンした際にソースフォロワ出力段の定電流源として機能する。

10

#### 【 0 0 6 4 】

モニタ部 30 は、差動アンプ 13 と、比較器 14 を含む。差動アンプ 13 は反転入力端子に信号線 9 が、非反転入力端子に信号線 10 が接続される。つまり、信号 P A G C によって最小値検出部と最大値検出部がそれぞれの信号線に同時に接続されると、ラインセンサ部 L 1 A の最大値と最小値の差分、すなわち P - B 信号を出力する。この P - B 信号と参照信号 V R E F との比較結果が反転したタイミングで、タイミングジェネレータ 15 は各単位画素の電荷蓄積動作を終了させる。

#### 【 0 0 6 5 】

次に、図 10 を参照しながら本実施例に係る光電変換装置の動作を説明する。実施例 1 で説明した動作と共に通する部分は省略する。

20

#### 【 0 0 6 6 】

時刻 T 0 ~ T 10 までの P D リセット期間で行われるフォトダイオードのリセット動作は実施例 1 の動作と同じである。この期間では、オフセットキャンセル回路 O C 1 、 O C 2 に係る信号 P N 1 、 P N 2 、 P S 1 、 P S 2 、 P G R 、 P A G C はローレベルである。

#### 【 0 0 6 7 】

オフセットキャンセル ( O f f s e t C a n c e l ; O C ) 期間 1 は、位相差情報検出用のフォトダイオード P D A が電荷を蓄積する期間に含まれる。時刻 T 11 に信号 P N 1 、 P N 2 、 P G R がハイレベルになると、スイッチ 21 、 23 、 25 がオンする。これにより、単位画素から出力される信号がスイッチ 21 を介して差動アンプ B A に与えられ、差動アンプ B A から出力される信号がスイッチ 23 を介してクランプ容量 24 の一方の端子に与えられる。この信号には、差動アンプ B A のオフセットが含まれる。

30

#### 【 0 0 6 8 】

時刻 T 12 から信号 P N 2 と P N 1 が順次ローレベルになり、スイッチ 23 と 21 とがそれぞれオフする。

#### 【 0 0 6 9 】

時刻 T 14 に信号 P S 2 がハイレベルになるとスイッチ 28 がオンして差動アンプ B A の非反転入力端子のノードがクランプ電圧 V G P によってリセットされる。

#### 【 0 0 7 0 】

時刻 T 15 に信号 P G R がローレベルになると、クランプ容量 24 の他方の端子、すなわち差動アンプ B A の非反転入力端子のノードが電気的に浮遊状態になる。これにより、クランプ容量には単位画素からの信号に差動アンプ B A のオフセットが加わった電圧とクランプ電圧との間の電位差が保持される。

40

#### 【 0 0 7 1 】

時刻 T 20 から開始する A G C 期間では、信号 P S 1 と P A G C とがハイレベルになる。このとき、単位画素から出力された信号はスイッチ 22 を介してクランプ容量 24 の一方の端子に与えられる。つまり、時刻 T 15 にクランプされたレベルからの電位変動分だけが差動アンプ B A に伝達される。そして、再び差動アンプ B A を経由することで、差動アンプ B A から出力される信号には、差動アンプ B A のオフセットが含まれない。

#### 【 0 0 7 2 】

時刻 T 20 から時間が経過し、モニタ部 30 から出力される信号 C O M P 18 の論理レ

50

ベルが時刻 T 3 0 に反転すると、A G C 期間が終了する。そして、時刻 T 3 0 からの F D リセット期間において、モニタ部 3 0 は信号 C O M P 1 8 が反転したことに応じて信号 P R E S をハイレベルにして、F D 容量 C f d をリセットするとともに、信号 P M O N をローレベルにしてモニタ用のフォトダイオード P D M を F D 容量 C f d から電気的に切断する。このほか、信号 P S 1 、 P S 2 、 P A G C をローレベルにする。

#### 【 0 0 7 3 】

時刻 T 4 0 に、信号 P R E S がローレベルになり、アンプ A m p の入力ノードのリセット状態が解除される。時刻 T 4 0 から時刻 T 5 0 までの O C 期間 2 で行われる動作は、信号 P M O N がローレベルとなっている点を除いては O C 期間 1 で行われる動作と同じである。すなわち、この期間では、モニタ用のフォトダイオード P D M がアンプ A m p の入力ノードから電気的に切断された状態でオフセットキャンセル動作が行われるものである。10

#### 【 0 0 7 4 】

時刻 T 5 0 から A F 信号転送期間が開始し、信号 P T X がハイレベルになる。これにより、位相差情報検出用のフォトダイオード P D A に蓄積された電荷が F D 容量 C f d に転送される。そして、信号 P S 1 および P S 2 がハイレベルであるので、単位画素で発生したノイズと、差動アンプ B A のオフセットが低減された信号が差動アンプ B A から出力される。オフセットキャンセル回路 O C 2 および最大値検出部についても同様である。

#### 【 0 0 7 5 】

時刻 T 6 0 から読み出し期間では、走査回路から信号 P H 1 、 P H 2 、 P H 3 、 . . . が順次出力され、位相差情報検出用のフォトダイオード P D A で蓄積された信号に基づく信号が出力端子 P O U T から順次出力される。20

#### 【 0 0 7 6 】

本実施例によれば、実施例 1 の構成で得られる効果に加えて、単位画素で生じるノイズと最大値検出部および最小値検出部で生じるオフセットとを低減できるので、信号をより精度よく検出できる。

#### 【 0 0 7 7 】

##### ( 実施例 4 )

次に、本実施例に係る単位画素を半導体基板上に作成する場合の平面レイアウト例を図 1 1 に示す。

#### 【 0 0 7 8 】

本実施例では、モニタ用のフォトダイオード P D M が、F D 部と直接接続されている。図 9 との違いは、モニタ用のフォトダイオードが、より F D 部に近い位置に設けられている点である。30

#### 【 0 0 7 9 】

ここでは、フォトダイオード P D M と F D 部とが、連続した拡散層で接続されているが、互いに異なる拡散層に形成し、配線で接続させてもよい。このような構成では図 9 に示したレイアウトよりも配線の長さを短縮できるため、F D 部に付随する容量値を低減することが可能となり、感度の向上が得られる。

#### 【 0 0 8 0 】

##### ( 実施例 5 )

次に、本実施例に係る単位画素を半導体基板上に作成する場合の平面レイアウト例を図 1 2 に示す。

#### 【 0 0 8 1 】

本実施例では、モニタ用のフォトダイオード P D M A と P D M B とが、F D 部と直接接続されている。

#### 【 0 0 8 2 】

図 9 や図 1 1 に示した構成では、第 2 の方向に沿ってフォトダイオード P D A に対して一方の側にしかモニタ用のフォトダイオードが設けられていなかった。本実施例によれば、第 2 の方向に沿ってフォトダイオード P D A を挟むようにモニタ用のフォトダイオードの光電変換領域が設けられるため、第 2 の方向に被写体の輝度分布がある場合でも、精度4050

よくモニタ動作を行い、蓄積時間を制御することができる。

【0083】

(実施例6)

本発明の第6の実施例に係る単位画素を半導体上に形成する場合の平面レイアウト例を図13に示す。

【0084】

本実施例では、図6で示したレイアウトと比較して、フォトダイオードPDMがFD部に近接して設けられるので、フォトダイオードPDMとFD部とを接続する配線を短縮できる。これにより、アンプAMPの入力ノードに接続される容量値が低減できるので、感度の向上が得られる。

10

【0085】

(実施例7)

続いて、本発明の第7の実施例に係る単位画素を半導体基板上に形成する場合の平面レイアウト例を図14に示す。

【0086】

本実施例では、図12に示した構成と同様に、モニタ用のフォトダイオードの光電変換領域が2つ、第2の方向にフォトダイオードPDAを挟むように設けられている。

20

【0087】

実施例5と同様に、第2の方向に輝度分布がある場合でも精度よく蓄積時間を制御できることに加えて、モニタ用のフォトダイオードがそれぞれスイッチを介してFD部と接続されているため、実施例1と同じく被写体の輝度に応じて電荷電圧変換係数を切り替えることができる。

【0088】

(実施例8)

本発明の第8の実施例に係る単位画素を半導体基板上に形成する場合の平面レイアウト例を図15に示す。

【0089】

本実施例では、位相差情報検出用のフォトダイオードがPDA1とPDA2として2つの光電変換領域が設けられており、その間にモニタ用のフォトダイオードPDMが設けられている。この配置によれば、フォトダイオードがPDA1とPDA2との間で被写体の輝度が大きく異なっていても、両者の中間にモニタ用のフォトダイオードにより、精度よく蓄積時間の制御を行える。

30

【0090】

(実施例9)

本発明の第9の実施例に係る単位画素を半導体基板上に形成する場合の平面レイアウト例を図16に示す。

【0091】

本実施例では、位相差情報検出用のフォトダイオードがPDA1とPDA2として2つの光電変換領域が設けられており、その間にモニタ用のフォトダイオードPDMが設けられている。この配置によれば、フォトダイオードがPDA1とPDA2との間で被写体の輝度が大きく異なっていても、両者の中間にモニタ用のフォトダイオードにより、精度よく蓄積時間の制御を行える。

40

【0092】

(実施例10)

図17は、本発明の実施例10に係る位相差AF用の光電変換装置の主要な構成を模式的に示した図である。実施例1で示した光電変換装置との相違点を中心に説明する。

【0093】

光電変換装置1'は、対となるラインセンサ部L1AとL1B、L2AとL2B、…・LN AとLN Bを有する。一对のラインセンサ部は撮像面のある領域における被写体のデフォーカス量を測定するために用いられ、このラインセンサ部の対を複数配列すること

50

で測距点を複数設け、A F の精度の向上を図るものである。各ラインセンサ部は、それぞれが位相差情報を検出するための A F 用光電変換部と、光量を検出するためのモニタ用光電変換部と、を有する単位画素 1 1 A、1 2 A、・・・を含んでいる。複数のラインセンサ部 L 1 A、L 2 A、・・・、L N A および L 1 B、L 2 B、・・・、L N B の単位画素は、それぞれ信号出力部 2 1 A、2 2 A、・・・および 2 1 B、2 2 B を備え、2 1 A、2 2 A、・・・および 2 1 B、2 2 B を介して信号を例えれば MUX 3 1 に出力し、MUX 3 1 で選択された信号がモニタ部 3 0 に出力する。

#### 【 0 0 9 4 】

図 1 8 は、ラインセンサ部 L 1 A に係る部分をより詳細に示した図である。単位画素 1 1 A は、光電変換部 1 0 0 A を含み、信号出力部 2 1 A は最大値検出部 1 0 2 - 1 A と最小値検出部 1 0 2 - 2 A とを含んで成る。光電変換部から出力された信号は信号保持部を介して、最大値検出部 1 0 2 - 1 A と最小値検出部 1 0 2 - 2 A とに供給される。最大値検出部 1 0 2 - 1 A および最小値検出部 1 0 2 - 2 A は例えばソースフォロワアンプである。このほか、信号検出の精度を向上させるために、ノイズ除去回路を含んでも良い。他の単位画素は単位画素 1 1 A と同じ構成である。ラインセンサ部 L 2 A、L 3 A、・・・、L 1 B、L 2 B、・・・もラインセンサ部 L 1 A と同様の構成なので、説明を省略する。

#### 【 0 0 9 5 】

以上で説明した本実施例に係る光電変換装置の構成でも、上述した各実施例の構成を適用することで同じ効果を得ることができる。

#### 【 0 0 9 6 】

##### ( 実施例 1 1 )

図 1 9 は、本発明の実施例 1 1 を示す撮像システムの構成例を示すブロック図である。

#### 【 0 0 9 7 】

9 0 1 は後述するレンズのプロテクトを行うバリア、9 0 2 は被写体の光学像を固体撮像装置 9 0 4 に結像するレンズ、9 0 3 はレンズを通過した光量を調整するための絞りである。9 0 4 はレンズで結像された被写体の光学像を画像信号として取得する固体撮像装置である。9 0 5 は先述の各実施例で説明した光電変換装置を用いた A F センサである。

#### 【 0 0 9 8 】

9 0 6 は固体撮像装置 9 0 4 や A F センサ 9 0 5 から出力される信号を処理するアナログ信号処理装置、9 0 7 は信号処理装置 9 0 6 から出力された信号をアナログデジタル変換する A / D 変換器である。9 0 8 は A / D 変換器 9 0 7 より出力された画像データに対して各種の補正や、データを圧縮するデジタル信号処理部である。

#### 【 0 0 9 9 】

9 0 9 は画像データを一時記憶するためのメモリ部、9 1 0 は外部コンピュータなどと通信するための外部 I / F 回路、9 1 1 はデジタル信号処理部 9 0 8 などに各種タイミング信号を出力するタイミング発生部である。9 1 2 は各種演算とカメラ全体を制御する全体制御・演算部、9 1 3 は記録媒体制御 I / F 部、9 1 4 は取得した画像データを記録、又は読み出しを行うための半導体メモリなどの着脱可能な記録媒体、9 1 5 は外部コンピュータである。

#### 【 0 1 0 0 】

次に、上記の撮像システムの撮影時の動作について説明する。

バリア 9 0 1 がオープンされ、A F センサ 9 0 5 から出力された信号をもとに、全体制御・演算部 9 1 2 は前記したような位相差検出により被写体までの距離を演算する。その後、演算結果に基づいてレンズ 9 0 2 を駆動し、再び合焦しているか否かを判断し、合焦していないと判断したときには、再びレンズ 9 0 2 を駆動するオートフォーカス制御を行う。次いで、合焦が確認された後に固体撮像装置 9 0 4 による電荷蓄積動作が始まる。固体撮像装置 9 0 4 の電荷蓄積動作が終了すると、固体撮像装置 9 0 4 から出力された画像信号は A / D 変換器 9 0 7 でアナログデジタル変換され、デジタル信号処理部 9 0 8 を通り全体制御・演算によりメモリ部 9 0 9 に書き込まれる。その後、メモリ部 9 0 9 に蓄積さ

10

20

40

50

れたデータは全体制御・演算部 912 の制御により記録媒体制御 I/F 部 910 を介して記録媒体 914 に記録される。また、外部 I/F 部 910 を通り直接コンピュータなどに入力してもよい。

#### 【符号の説明】

##### 【0101】

11A 単位画素

21A 信号出力部

30 モニタ部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(72)発明者 黒田 享裕

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 衣笠 友壽

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 前田 康次

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 井龜 諭

(56)参考文献 特開2000-059688(JP,A)

特開平05-034588(JP,A)

特開平11-355662(JP,A)

特開平05-207376(JP,A)

特開2002-325204(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 04 N        5 / 232

G 02 B        7 / 34