US 20080265362A1

# (19) United States

# (12) Patent Application Publication Tigelaar

(10) **Pub. No.: US 2008/0265362 A1**(43) **Pub. Date: Oct. 30, 2008**

# (54) BUILDING FULLY-DEPLETED AND BULK TRANSISTORS ON SAME CHIP

(75) Inventor: **Howard Lee Tigelaar**, Allen, TX

Correspondence Address: TEXAS INSTRUMENTS INCORPORATED P O BOX 655474, M/S 3999 DALLAS, TX 75265

(73) Assignee: **TEXAS INSTRUMENTS INCORPORATED**, Dallas, TX

(US)

(21) Appl. No.: 12/169,997

(22) Filed: Jul. 9, 2008

### Related U.S. Application Data

(62) Division of application No. 11/091,078, filed on Mar. 28, 2005, now Pat. No. 7,410,840.

#### **Publication Classification**

(51) **Int. Cl.** *H01L 27/12* (2006.01)

(52) **U.S. Cl.** ...... **257/504**; 257/E27.112

(57) ABSTRACT

An integrated circuit having fully-depleted silicon-on-insulator (FD-SOI) transistors and bulk transistors on a semiconductor substrate is disclosed.

# BUILDING FULLY-DEPLETED AND BULK TRANSISTORS ON SAME CHIP

#### FIELD OF INVENTION

[0001] The present invention relates generally to semiconductor devices and more particularly to fabricating fully-depleted and bulk SOI devices in an integrated circuit fabrication process.

#### BACKGROUND OF THE INVENTION

[0002] Semiconductor device geometries have dramatically decreased in size since such devices were first introduced several decades ago. The desire for higher performance circuits has driven the development of high-speed sub-100 nanometer (nm) silicon-on-insulator (SOI) complementary metal-oxide-semiconductor (CMOS) technology. In SOI technology, metal-oxide semiconductor field-effect transistors (MOSFETs) are formed on a thin layer of silicon overlying a layer of insulating material such as silicon oxide. Devices formed on SOI offer many advantages over their bulk counterparts. For example, SOI devices generally have a reduced junction capacitance, little to no reverse body effect, soft-error immunity, full dielectric isolation, and little to no latch-up. SOI technology therefore enables higher speed performance, higher packing density, and reduced power consumption, among other things, as compared to conventional transistors that are formed on a semiconductor bulk material (e.g., silicon) and not over a layer of insulating material.

[0003] One type of SOI device is a fully-depleted (FD-SOI) device. In a FD-SOI device the thin layer of silicon has a thickness that is less than the maximum depletion layer width in the silicon during device operation. Consequently, during operation, the FD-SOI experiences a "full" depletion thereof. FD-SOI devices have an additional advantage over traditional or bulk transistors in that they can be scaled to shorter gate lengths and do not suffer from body effects due to the fact that the body is fully-depleted during device operation. FD-SOI devices are also believed to provide lower off-state leakage currents, higher speeds, fewer soft errors, lower operating voltages and lower gate delay than regular non-SOI transistors.

[0004] However, since FD-SOI devices are formed on a thin layer of silicon overlying a layer of insulating material, they can be said to lack a "body tie", or rather a connection to the underlying semiconductor substrate. This makes it very difficult to produce different types of transistors on the same chip and/or the same or similar types of transistors that have different operating characteristics from being produced on the same chip. For example, multiple transistors having different threshold voltages (Vt's) and/or operating speeds would be difficult to be produced at the same time. Likewise, it would be difficult to produce high voltage I/O transistors while low voltage I/O transistors are also produced. Bulk transistors, on the other hand, do allow such different transistors to be made at the same time. More particularly, since these more traditional transistors are formed on bulk semiconductor material (e.g., silicon) that does not overlie a layer of insulating material, they can be said to have a "body tie". Essentially, the thicker substrate that the transistors are formed on can accommodate different types of processing, such as different doping concentrations, for example, that enable different devices to be formed on the same chip.

[0005] Consequently, it would be desirable to be able to reliably form both FD-SOI and bulk transistors in a single fabrication process so that either of the devices can be employed based on circuit application requirements.

#### SUMMARY OF THE INVENTION

[0006] The following presents a simplified summary of the invention in order to provide a basic understanding of some aspects of the invention. This summary is not an extensive overview of the invention. It is intended neither to identify key or critical elements of the invention nor to delineate the scope of the invention. Rather, its primary purpose is merely to present one or more concepts of the invention in a simplified form as a prelude to the more detailed description that is presented later.

[0007] The present invention relates to forming fully-depleted silicon-on-insulator (FD-SOI) and bulk transistor devices in an integrated circuit fabrication process. Forming the different types of transistors on the same semiconductor substrate allows different circuit application requirements to be met. For example, FD-SOI transistors can be used where speed and low threshold voltages (Vt's) are important. Likewise, bulk transistors can be used where high voltage I/O, low voltage I/O and/or multiple transistors having different Vt's are needed. Capacitors can also be built from a layer of polysilicon and the substrate. Similarly, resistors can be built in the substrate and bipolar transistors can also be fabricated. [0008] According to one or more aspects of the present invention, a method of forming a fully-depleted silicon-oninsulator (FD-SOI) transistor and a bulk transistor as part of an integrated circuit fabrication process is disclosed. The method includes providing a silicon-on-insulator (SOI) substrate which comprises a layer of silicon material formed over a layer of insulating material which is in turn formed over a semiconductor substrate. A layer of oxide material is formed over the layer of silicon material and a layer of nitride material is formed over the layer of oxide material. The layer of nitride material, the layer of oxide material, the layer of silicon material and at least some of the layer of insulating material are patterned to establish bulk regions wherein bulk transistors can be formed, and where the bulk regions separate the layer of silicon into silicon regions wherein fully depleted transistors can be formed. The layer of nitride material is removed and an epitaxial material is grown in the bulk regions. The layer of oxide material is removed and the silicon regions are thinned by growing a layer of oxide material which consumes silicon as part of the growth process. The grown layer of oxide material is removed to reveal the thinned silicon regions. A fully depleted transistor is then formed in a thinned silicon region and a bulk transistor is formed in a bulk region.

[0009] According to one or more other aspects of the present invention, an integrated circuit is disclosed that includes a fully depleted transistor and a bulk transistor formed on a single semiconductor substrate. The fully depleted and bulk transistors are formed as part of an integrated circuit fabrication process, where the fully depleted transistor is formed within a silicon-on-insulator (SOI) region of the semiconductor substrate and the bulk transistor is formed within a bulk region of the semiconductor substrate.

[0010] To the accomplishment of the foregoing and related ends, the following description and annexed drawings set forth in detail certain illustrative aspects and implementations of the invention. These are indicative of but a few of the

various ways in which one or more aspects of the present invention may be employed. Other aspects, advantages and novel features of the invention will become apparent from the following detailed description of the invention when considered in conjunction with the annexed drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

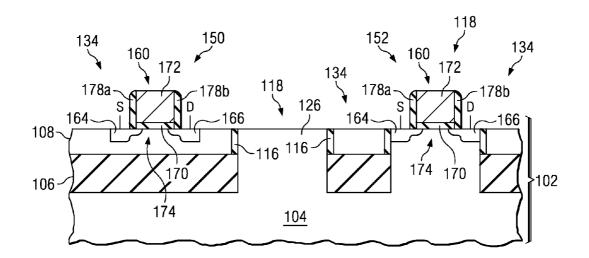

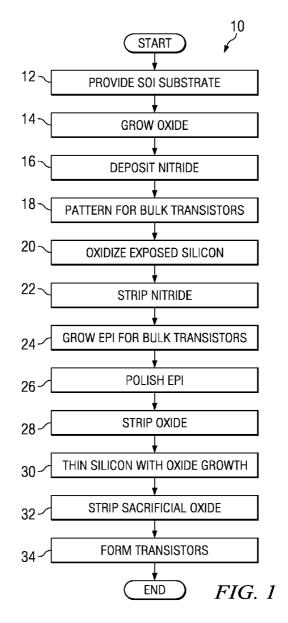

[0011] FIG. 1 is a flow diagram illustrating an exemplary method for forming fully-depleted silicon-on-insulator (FD-SOI) and bulk transistor devices in an integrated circuit fabrication process according to one or more aspects of the present invention.

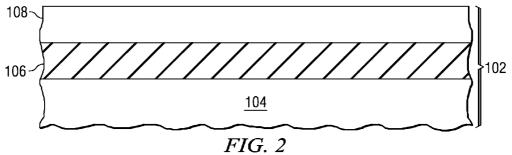

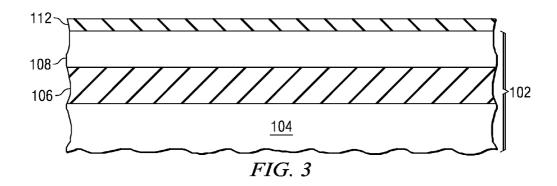

[0012] FIGS. 2-11 are fragmentary cross sectional diagrams illustrating the formation of exemplary fully-depleted silicon-on-insulator (FD-SOI) and bulk transistor devices in an integrated circuit fabrication process according to one or more aspects of the present invention, such as the methodology set forth in FIG. 1.

# DETAILED DESCRIPTION OF THE INVENTION

[0013] One or more aspects of the present invention are described with reference to the drawings, wherein like reference numerals are generally utilized to refer to like elements throughout, and wherein the various structures are not necessarily drawn to scale. It will be appreciated that where like acts, events, elements, layers, structures, etc. are reproduced, subsequent (redundant) discussions of the same may be omitted for the sake of brevity. In the following description, for purposes of explanation, numerous specific details are set forth in order to provide a thorough understanding of one or more aspects of the present invention. It may be evident, however, to one of ordinary skill in the art that one or more aspects of the present invention may be practiced with a lesser degree of these specific details. In other instances, known structures are shown in diagrammatic form in order to facilitate describing one or more aspects of the present invention. [0014] Turning to FIG. 1, an exemplary methodology 10 is illustrated for forming fully-depleted silicon-on-insulator (FD-SOI) and bulk transistor devices in an integrated circuit fabrication process according to one or more aspects of the present invention. Although the methodology 10 is illustrated and described hereinafter as a series of acts or events, it will be appreciated that the present invention is not limited by the illustrated ordering of such acts or events. For example, some acts may occur in different orders and/or concurrently with other acts or events apart from those illustrated and/or described herein. In addition, not all illustrated steps may be required to implement a methodology in accordance with one or more aspects of the present invention. Further, one or more of the acts may be carried out in one or more separate acts or phases. It will be appreciated that a methodology carried out according to one or more aspects of the present invention may be implemented in association with the formation and/or processing of structures illustrated and described herein as well as in association with other structures not illustrated or described herein

[0015] The method 10 begins at 12, wherein a SOI starting material 102 is provided (FIG. 2). The SOI starting material comprises a semiconductor substrate 104 over which a layer of nonconductive insulating material 106 is formed, and having a thin layer of silicon 108 formed over the layer of insulating material 106 (FIG. 2). The layer of insulating material 106 may comprise a buried oxide layer (BOX), for example.

Similarly, the semiconductor substrate 104 may comprise any type of semiconductor body (e.g., formed of silicon or SiGe) such as a semiconductor wafer or one or more die on a wafer, as well as any other type of semiconductor layers associated therewith. By way of example, the layer of silicon 108 can have a thickness of between around 800 Angstroms and around 1200 Angstroms.

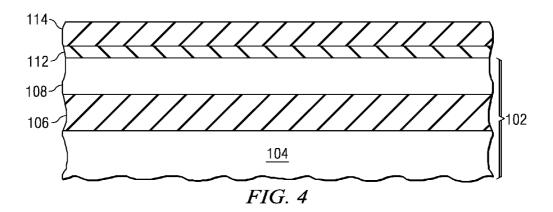

[0016] At 14, a thin layer of oxide based material 112 is grown over the layer of silicon 108 (FIG. 3). The layer of oxide material 112 can be formed to a thickness of around 50 to 200 Angstroms, for example. A layer of nitride based material 114 is then deposited over the layer oxide 112 at 16 (FIG. 4). The layer of nitride material 114 can be formed to thickness of between around 700 Angstroms and around 1200 Angstroms, for example.

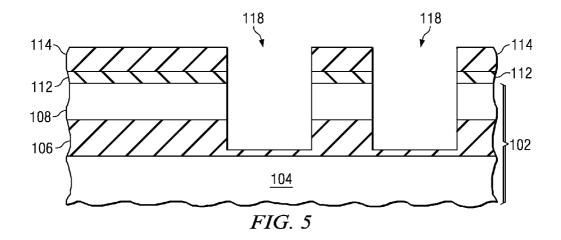

[0017] The layer of nitride material 114, layer of oxide material 112, layer of silicon 108 and layer of insulating material 106 are then patterned at 18 to establish regions 118 where bulk transistors can be formed in the bulk silicon substrate 104 (FIG. 5). The patterning can be performed in any suitable manner, such as with lithographic techniques, for example, where lithography broadly refers to processes for transferring one or more patterns between various media. In lithography, a light sensitive resist coating (not shown) is formed over one or more layers to which a pattern is to be transferred (e.g., layers 114, 112, 108 and 106). The resist coating is then patterned by exposing it to one or more types of radiation or light which (selectively) passes through an intervening lithography mask containing the pattern. The light causes the exposed or unexposed portions of the resist coating to become more or less soluble, depending on the type of resist used. A developer is then used to remove the more soluble areas leaving the patterned resist. The patterned resist can then serve as a mask for the underlying layer or layers which can be selectively treated (e.g., etched) to transfer the pattern thereto. After regions 118 are formed, the resist pattern is removed.

[0018] An oxidation activity is then performed at 20 to form an oxide 116 on exposed portions of the layer of silicon 108 on the sidewalls of the regions 118 (FIG. 6). It will be appreciated that the exposed portions of the layer of silicon 108 may be slightly recessed prior to the oxidation at 20, such as by an isotropic gas etch and/or a wet etch, for example. It will also be appreciated that while in the example illustrated, a small amount 120 of the layer of insulating material 106 remains on the surface of the substrate 104 within the regions 118 after the patterning at 18, that all of the layer of insulating material 106 may be removed from the surface of the substrate 104 within the regions 118 during the patterning at 18. In such a situation, a small amount of oxide 120 may grow on the exposed portions of the substrate 104 within the regions 118 during the oxidation at 20.

[0019] In any event, the oxidation at 20 may be performed, for example, by placing the layers in an oxidizing furnace and/or depositing oxide, followed by an optional etch to remove residual and/or unwanted amounts of oxide. In addition to removing excess oxide built up on the sidewalls of the regions 118, such an etch may also remove, for example, some of the oxide 120 on the substrate 104 within the regions 118—regardless of whether the oxide 120 is a remnant of layer 106 or is formed during the oxidation at 20. Nevertheless, some oxide is allowed to remain on the exposed portions of the layer of silicon 108 on the sidewalls of the regions 118 as well as on the exposed surface portions of the substrate 104

within the regions 118 so that these areas are protected by the oxide 116, 120 during a subsequent removal of the layer of nitride material 114.

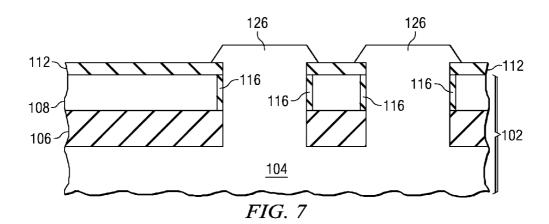

[0020] Accordingly, the layer of nitride material 114 is then removed at 22, such as with a hot phosphoric acid solution, for example (FIG. 7). The remaining oxide protects the silicon, for example, which would otherwise be attacked by such a hot phosphoric solution. The nitride removal at 22 may be carefully controlled to also remove the oxide 120 on the substrate 104 within regions 118. Alternatively, the oxide 120 on the substrate 104 within regions 118 (but not on the sidewalls thereof) may be removed by a subsequent etching process (not shown). Once the substrate 104 within regions 118 is exposed, an epitaxial growth process is performed at 24 to fill the regions 118 with an epitaxially grown semiconductor material 126 (FIG. 7). It can be appreciated that growing the oxide at 20 on the sidewall of the regions 118 seals off the layer of silicon 108 to mitigate nucleation of epi growth. This epitaxially grown material 126 provides areas wherein bulk transistors can be formed (e.g., that have a "body tie" to the bulk semiconductor substrate 104). In addition to facilitating the epitaxial growth process, it can be appreciated that removing the oxide 120 from the substrate 104 also removes a barrier that would otherwise prevent transistors formed therein from being "tied" to the body of the semiconductor substrate 104.

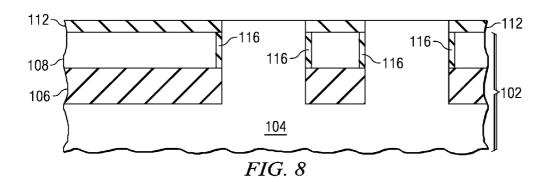

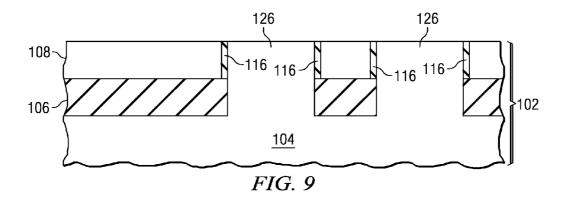

[0021] As illustrated in the example presented in FIG. 7, it can be appreciated that some of the epitaxially grown semi-conductor material 126 may "mushroom" up out of the regions 118, depending upon the technology used to grow the material 126. As such, an optional polishing activity is performed at 26, such as a chemical mechanical polishing (CMP), for example, to remove any such facets, bumps or other types of discontinuities (FIG. 8). This planarization process makes the epi material 126 in the regions 118 substantially flush with the surrounding layer of oxide material 112. The remaining oxide material 112 is then stripped at 28 so that both the layer of silicon 108 and epi material 126 are revealed (FIG. 9).

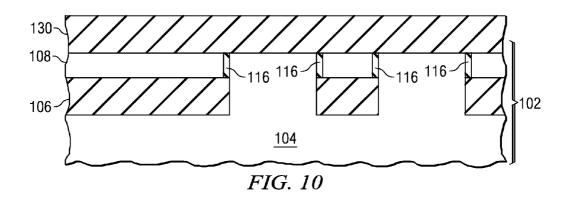

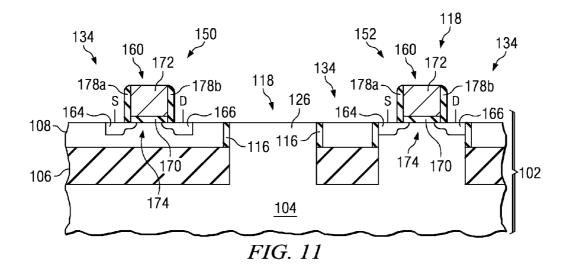

[0022] At 30, the layer of silicon 108 is thinned by an oxide growth process which consumes silicon as the layer of oxide 130 is grown (FIG. 10). Incidentally, some of the epi material 126 is also consumed as part of this growth process. This does not, however, adversely affect bulk transistors since the epi material 126 can be said to extend very far or be very thick as it is tied to the semiconductor substrate 104. The grown oxide 130 is then removed at 32, such as by stripping it with a hydrogen fluoride (HF) based agent, for example (FIG. 11). Removing the oxide 130 reveals the thinned layer of silicon 108 wherein the fully depleted transistors can be formed. Since the epi material 126 is also consumed by the grown oxide 130, stripping this oxide leaves the epi material 126 substantially flush with the surrounding thinned layer of silicon 108. By way of example, the layer of silicon 108 can be thinned so that it has a thickness of between around 20 Angstroms and around 40 Angstroms.

[0023] At 34, the different transistors can be formed in the different regions (FIG. 11). More particularly, fully-depleted silicon-on-insulator (FD-SOI) transistors can be formed in the regions 134 comprising the thinned silicon 108, while bulk transistors can be formed in the regions 118 comprising the epi material 126. It will be appreciated that while three thinned silicon regions 134 and two epi regions 118 are depicted in the example illustrated, that any suitable number

of such regions can be fashioned upon a semiconductor substrate. Similarly, while in the example presented only one FD-SOI transistor 150 is illustrated in a thinned silicon region 134 and only one bulk transistor 152 is illustrated in an epi region 118, any suitable number of transistors can be in the formed in the different regions. The different transistors can be formed by slightly varying certain fabrication processes and/or selectively exposing different parts of the regions to different processes. For example, certain parts of the epi regions 118 can be selectively masked off to receive more or less of one or more types of dopant materials to establish high performance CMOS transistors and/or analog transistors. Further, it can be seen that the oxide formations 116 grown at 20 may serve to electrically isolate the different regions 118 and 134 (and the devices formed therein) from one another.

[0024] Generally speaking, to establish any of the different transistors, a gate structure 160 and source and drain regions 164, 166 are formed (FIG. 11), after which silicide, metallization, and/or other back-end processing (not shown) can be performed. To form the gate structure 160, a thin gate oxide 170 is formed over the upper surface of the silicon and epi regions 134, 118. The gate oxide 170 can be formed by any suitable material formation process, such as thermal oxidation processing, for example. By way of example, the oxide layer 170 can, for example, be formed to a thickness of between about 100 Angstroms and about 500 Angstroms at a temperature of between about 600 degrees Celsius and about 1000 degrees Celsius in the presence of O2. This layer of oxide material 170 can serve as a gate oxide in a high voltage CMOS bulk transistor device, for example. Alternatively, a layer of oxide material 170 having a thickness of about 70 Angstroms or less can be formed to serve as a gate oxide in a low voltage CMOS bulk transistor device, for example.

[0025] A gate polysilicon layer 172 is then deposited over the layer of gate oxide material 170. The polysilicon layer 172 can, for example, for formed to between about 800 to about 5000 Angstroms, and may include a dopant, such as a p-type dopant (Boron) or n-type dopant (e.g., Phosphorus), depending upon the type(s) of transistors to be formed. The dopant can be in the polysilicon 172 as originally applied, or may be subsequently added thereto (e.g., via a doping process). The gate oxide 170 and gate polysilicon 172 layers are then patterned to form the gate structure 160, which comprises a gate dielectric and a gate electrode, and which is situated over a channel region 174 in the epi and silicon regions 118, 134.

[0026] With the patterned gate structure formed, LDD, MDD, or other extension implants (not shown) can be performed, for example, depending upon the type(s) of transistors to be formed, and left and right sidewall spacers 178a, 178b can be formed along left and right lateral sidewalls of the patterned gate structure 160. Implants to form the source (S) region 164 and the drain (D) region 166 are then performed, wherein any suitable masks and implantation processes may be used in forming the source and drain regions 164, 166 to achieve desired transistor types. For example, a PMOS well mask can be utilized to define n-type wells for the bulk PMOS transistor areas and a PMOS source/drain mask may be utilized to define one or more openings through which a p-type source/drain implant (e.g., Boron (B and/or BF<sub>2</sub>)) is performed to form p-type source and drain regions for PMOS bulk transistor devices. Similarly, an NMOS well mask can be utilized to define p-type wells for the bulk NMOS transistor areas and an NMOS source/drain mask may be employed to define one or more openings through which an n-type source/ drain implant (e.g., Phosphorous (P) and/or Arsenic (As)) is performed to form n-type source and drain regions for NMOS bulk transistor devices. Depending upon the types of masking techniques employed, such implants may also selectively dope the poly-silicon 172 of the gate structure 160 of certain transistors, as desired. It will be appreciated that the channel region 174 is thus defined between the source and drain regions 164, 166 in the different transistors.

[0027] Accordingly, forming transistors according to one or more aspects of the present invention allows fully-depleted silicon-on-insulator (FD-SOI) and bulk transistor devices to be fabricated in a single integrated circuit fabrication process. Forming the different types of transistors on the same semiconductor substrate allows their respective advantages to be integrated to satisfy different circuit application requirements. For example, FD-SOI transistors can be used where speed and low threshold voltages (Vt's) are important. NMOS and/or PMOS transistors can, for example, be formed in the fully depleted areas 134 for high speed CMOS applications. Likewise, transistors having a high threshold voltage (Vt), transistors having a low threshold voltage, high performance CMOS transistors, transistors that are to be used for memory applications and/or transistors that are to be used for analog applications can formed in the bulk or epi regions 118. Additionally, forming transistors as disclosed herein also allows capacitors to be formed as part of the fabrication process. For example, a capacitor can be fashioned from the layer of gate polysilicon material 172, the layer of gate oxide material 170 and the substrate 104, for example. Similarly, resistors can be built in the substrate 104, and bipolar transistors can also be fabricated as part of the process.

[0028] It will be appreciated that while reference is made throughout this document to exemplary structures in discussing aspects of methodologies described herein (e.g., those structures presented in FIGS. 2-11 while discussing the methodology set forth in FIG. 1), that those methodologies are not to be limited by the corresponding structures presented. Rather, the methodologies (and structures) are to be considered independent of one another and able to stand alone and be practiced without regard to any of the particular aspects depicted in the Figs.

[0029] It is also to be appreciated that layers and/or elements depicted herein are illustrated with particular dimensions relative to one another (e.g., layer to layer dimensions and/or orientations) for purposes of simplicity and ease of understanding, and that actual dimensions of the elements may differ substantially from that illustrated herein. Addi-

tionally, unless stated otherwise and/or specified to the contrary, any one or more of the layers set forth herein can be formed in any number of suitable ways, such as with spin-on techniques, sputtering techniques (e.g., magnetron and/or ion beam sputtering), (thermal) growth techniques and/or deposition techniques such as chemical vapor deposition (CVD), physical vapor deposition (PVD) and/or plasma enhanced chemical vapor deposition (PECVD), or atomic layer deposition (ALD), for example, and can be patterned in any suitable manner (unless specifically indicated otherwise), such as via etching and/or lithographic techniques, for example. Further, the term "exemplary" as used herein merely meant to mean an example, rather than the best.

[0030] Although one or more aspects of the invention has been shown and described with respect to one or more implementations, equivalent alterations and modifications will occur to others skilled in the art based upon a reading and understanding of this specification and the annexed drawings. The invention includes all such modifications and alterations and is limited only by the scope of the following claims. In addition, while a particular feature or aspect of the invention may have been disclosed with respect to only one of several implementations, such feature or aspect may be combined with one or more other features or aspects of the other implementations as may be desired and/or advantageous for any given or particular application. Furthermore, to the extent that the terms "includes", "having", "has", "with", or variants thereof are used in either the detailed description or the claims, such terms are intended to be inclusive in a manner similar to the term "comprising."

What is claimed is:

- 1. An integrated circuit, comprising:

- a fully depleted transistor and a bulk transistor formed on a single semiconductor substrate, where the fully depleted and bulk transistors are formed as part of an integrated circuit fabrication process, and where the fully depleted transistor is formed within a silicon-on-insulator (SOI) region of the semiconductor substrate and where the bulk transistor is formed within a bulk region of the semiconductor substrate.

- 2. The circuit of claim 1, where in the fully depleted transistor is formed within a thinned layer of silicon within the SOI region of the semiconductor substrate.

- 3. The circuit of claim 2, where the thinned layer of silicon has a thickness of between around 20 Angstroms and around 40 Angstroms.

\* \* \* \* \*