(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5996828号

(P5996828)

(45) 発行日 平成28年9月21日(2016.9.21)

(24) 登録日 平成28年9月2日(2016.9.2)

(51) Int.Cl.

G06F 12/08 (2016.01)

F 1

G06F 12/08 531B

G06F 12/08 519Z

請求項の数 20 (全 22 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-507630 (P2016-507630)  |

| (86) (22) 出願日 | 平成26年4月9日(2014.4.9)           |

| (65) 公表番号     | 特表2016-514882 (P2016-514882A) |

| (43) 公表日      | 平成28年5月23日(2016.5.23)         |

| (86) 國際出願番号   | PCT/US2014/033474             |

| (87) 國際公開番号   | W02014/169025                 |

| (87) 國際公開日    | 平成26年10月16日(2014.10.16)       |

| 審査請求日         | 平成28年6月1日(2016.6.1)           |

| (31) 優先権主張番号  | 61/810,889                    |

| (32) 優先日      | 平成25年4月11日(2013.4.11)         |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 13/933,337                    |

| (32) 優先日      | 平成25年7月2日(2013.7.2)           |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

最終頁に続く

|           |                                                                                       |

|-----------|---------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サンディエゴ モアハウス ドラ<br>イブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                |

| (72) 発明者  | トマス・フィリップ・スパイアー<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ドラ<br>イブ・5775              |

(54) 【発明の名称】コヒーレントバスを介したセマフォ管理シーケンスのパフォーマンスを改善するための方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

マルチプロセッサにおけるコヒーレントバスを介したセマフォ管理のための方法であつて、

第1のプロセッサから発行されたロード排他命令に応答して、前記第1のプロセッサに対してローカルな第1のキャッシュがターゲットアドレスにおいてミスしたと判断するステップと、

前記コヒーレントバス上で前記第1のキャッシュから第2のプロセッサに対してローカルな第2のキャッシュに読み取り優先排他コマンドを発行するステップと、

前記読み取り優先排他コマンドに応答して、前記第2のキャッシュ内の予約グラニュールが前記ターゲットアドレスに関してタグ付けされた状態ないと判断するステップと、

前記第2のキャッシュ内の前記予約グラニュールは前記ターゲットアドレスに関してタグ付けされた状態ないと判断したことにより、前記第2のキャッシュ内の前記ターゲットアドレスでキャッシュラインを無効化するステップとを含む方法。

## 【請求項 2】

前記コヒーレントバスから前記第2のキャッシュによってスヌープされた前記読み取り優先排他コマンドに応答して、前記ターゲットアドレスにおいて要求されたデータを前記第1のキャッシュに提供するステップをさらに含む、請求項1に記載の方法。

## 【請求項 3】

10

20

前記コヒーレントバスをスヌープすることによって検出された前記読取り優先排他コマンドに応答して、メモリ階層内の前記第1のキャッシュの上の次のレベルのメモリから前記ターゲットアドレスにおいて要求されたデータを前記第1のキャッシュに提供するステップをさらに含む、請求項1に記載の方法。

【請求項4】

前記読取り優先排他コマンドが実行を完了した後に、前記第1のキャッシュ内の予約グラニュールが前記ターゲットアドレスにタグ付けされる、請求項1に記載の方法。

【請求項5】

前記読取り優先排他コマンドが、前記キャッシュラインが共有データを含むものとしてタグ付けされている場合に前記キャッシュラインを放棄するために、前記マルチプロセッサ内の他のキャッシュに対するヒントとして動作する、請求項1に記載の方法。10

【請求項6】

前記第2のプロセッサ内の前記キャッシュラインの状態を判断するステップと、

前記第2のプロセッサ内の前記キャッシュラインの状態が共有または排他状態であることに応答して、前記第1のプロセッサにおいて受信された前記キャッシュラインの前記状態を排他状態に変更するステップと

をさらに含む、請求項1に記載の方法。

【請求項7】

前記第2のプロセッサ内の前記キャッシュラインの状態を判断するステップと、

前記第2のプロセッサ内の前記キャッシュラインの状態が所有または変更状態であることに応答して、前記第1のプロセッサにおいて受信された前記キャッシュラインの前記状態を変更状態に変更するステップと

をさらに含む、請求項1に記載の方法。20

【請求項8】

マルチプロセッシングシステムにおけるセマフォ管理のための装置であって、

第1のキャッシュがロード排他命令によって提供されたターゲットアドレスにおいてデータをミスしたことに応答して、コヒーレントバス上で前記第1のキャッシュから第2のキャッシュに読取り優先排他コマンドを発行するように構成された第1のキャッシュコントローラであって、前記第1のキャッシュはロード排他命令を発行した第1の処理エージェントに結合され、前記第2のキャッシュは第2の処理エージェントに結合される、第1のキャッシュコントローラと。30

前記コヒーレントバスをスヌープし、前記第2のキャッシュ内のスヌープされた読取り優先排他コマンドおよび予約グラニュールが前記ターゲットアドレスに対してタグ付けされたことに応答して、前記第2のキャッシュ内のキャッシュラインの状態を前記ターゲットアドレスで有効状態および共有状態において終了させるように構成された第2のキャッシュコントローラと、

を備える、装置。

【請求項9】

前記ターゲットアドレスにおける前記データが、前記コヒーレントバスから前記第2のキャッシュコントローラによってスヌープされた前記読取り優先排他コマンドに応答して、前記第1のキャッシュに提供される、請求項8に記載の装置。40

【請求項10】

前記ターゲットアドレスにおける前記データが、前記コヒーレントバスをスヌープすることによって検出された前記読取り優先排他コマンドに応答して、メモリ階層内の前記第1のキャッシュの上の次のレベルのメモリから前記第1のキャッシュに提供される、請求項8に記載の装置。

【請求項11】

前記第1のキャッシュコントローラはさらに、前記スヌープされた読取り優先排他コマンドが実行を完了した後に、前記第1のキャッシュ内の予約グラニュールを前記ターゲットアドレスにタグ付けするように構成された、請求項8に記載の装置。50

**【請求項 12】**

前記読み取り優先排他コマンドが、前記キャッシュラインが共有データを含むものとしてタグ付けされている場合に前記キャッシュラインを放棄するために、前記マルチプロセッsingシステム内の他のキャッシュに対するヒントとして動作する、請求項8に記載の装置。

**【請求項 13】**

前記第1の処理エージェントが、前記第2のキャッシュコントローラによって提供される前記データを受信し、前記第1の処理エージェントのキャッシュラインの状態を共有状態に変更する、請求項8に記載の装置。

**【請求項 14】**

マルチプロセッサにおけるコヒーレントバスを介したセマフォ管理のための方法であつて、

第1のプロセッサから発行されたロード排他命令に応答して、前記第1のプロセッサに対してローカルな第1のキャッシュがターゲットアドレスにおいてヒットしたと判断するステップであつて、アクセスされた第1のキャッシュラインが共有または所有状態である、ステップと、

前記コヒーレントバス上で前記第1のキャッシュから第2のプロセッサに対してローカルな第2のキャッシュにアップグレード優先排他コマンドを発行するステップと、

前記アップグレード優先排他コマンドに応答して、前記第2のキャッシュが前記ターゲットアドレスにおいてヒットしたと判断するステップであつて、アクセスされた第2のキャッシュラインの予約グラニュールがタグ付けされない、ステップと、

前記第1のプロセッサによって要求された前記第1のキャッシュラインを、前記第2のキャッシュラインが共有状態であることに応答して、排他状態にアップグレードするステップと

を含む方法。

**【請求項 15】**

前記第2のキャッシュラインが最初に前記共有状態であることに応答して、前記第2のキャッシュ内の前記第2のキャッシュラインを無効化するステップをさらに含む、請求項14に記載の方法。

**【請求項 16】**

前記第2のキャッシュラインが所有状態であることに応答して、前記第1のプロセッサによって要求された前記第1のキャッシュラインを変更状態にアップグレードするステップをさらに含む、請求項14に記載の方法。

**【請求項 17】**

前記アップグレード優先排他コマンドに応答して、前記第2のキャッシュが前記ターゲットアドレスにおいてヒットし、前記ヒットした第2のキャッシュラインの前記予約グラニュールが前記第1のプロセッサによって要求された前記第1のキャッシュラインと同じターゲットアドレスにタグ付けされていると判断するステップと、

前記第1のキャッシュおよび前記第2のキャッシュのキャッシュラインの状態を変更することなく、さらなるコヒーレントバスコマンドの監視に戻るステップとをさらに含む、請求項14に記載の方法。

**【請求項 18】**

前記アップグレード優先排他コマンドが、前記第2のキャッシュ用のキャッシュコントローラ内のスヌープユニットによって識別される、請求項14に記載の方法。

**【請求項 19】**

コンピュータ可読プログラムデータおよびコードで符号化されたコンピュータ可読記録媒体であつて、実行されると、前記プログラムデータおよびコードが、

第1のプロセッサから発行されたロード排他命令に応答して、前記第1のプロセッサに対してローカルな第1のキャッシュがターゲットアドレスにおいてミスしたと判断し、

コヒーレントバス上で前記第1のキャッシュから第2のプロセッサに対してローカルな第

10

20

30

40

50

2のキャッシュに読み取り優先排他コマンドを発行し、

前記ターゲットアドレスに関する前記第2のキャッシュ内の予約グラニュールがタグ付けされた状態にないことに応答して、前記第2のキャッシュ内の前記ターゲットアドレスでキャッシュラインを無効化する

ように動作可能である、コンピュータ可読記録媒体。

【請求項 20】

マルチプロセッシングシステムにおけるセマフォ管理のための装置であって、

第1のキャッシュがロード排他命令によって提供されたターゲットアドレスにおいてデータをミスしたことに応答して、コヒーレントバス上で前記第1のキャッシュから第2のキャッシュに読み取り優先排他コマンドを発行するための手段であって、前記第1のキャッシュが前記ロード排他命令を発行した第1の処理エージェントに結合され、前記第2のキャッシュが第2の処理エージェントに結合される、手段と、10

前記コヒーレントバスをスヌープし、前記第2のキャッシュ内のスヌープされた読み取り優先排他コマンドおよび予約グラニュールが前記ターゲットアドレスに対してタグ付けされたことに応答して、前記第2のキャッシュ内のキャッシュラインの状態を前記ターゲットアドレスで有効状態および共有状態において終了させるための手段と

を備える装置。

【発明の詳細な説明】

【技術分野】

【0001】

20

優先権出願

本出願は、「METHODS AND APPARATUS FOR IMPROVING PERFORMANCE OF SEMAPHORE MANAGEMENT SEQUENCES ACROSS A COHERENT BUS」という名称の2013年7月2日に出願された米国特許出願第13/933,337号の優先権を主張し、この米国特許出願は、「METHODS AND APPARATUS FOR IMPROVING PERFORMANCE OF SEMAPHORE MANAGEMENT SEQUENCES ACROSS A COHERENT BUS」という名称の2013年4月11日に出願された米国仮特許出願第61/810,889号の優先権をさらに主張し、その両方の出願の全体が参照により本明細書に組み込まれる。

【0002】

本発明の実施形態は一般にセマフォ管理の態様に関し、より詳細には、コヒーレントバスを介したセマフォ管理に関する。30

【背景技術】

【0003】

セルフオン、ラップトップコンピュータ、携帯情報端末(PDA)などの多くのポータブル製品は、通信プログラムおよびマルチメディアプログラムなどのプログラムを実行する処理システムを利用している。そのような製品用の処理システムは、マルチプロセッサと、マルチレベルのキャッシュと命令およびデータを記憶するためのメモリとを含む複合メモリシステムと、コントローラと、通信インターフェースなどの周辺デバイスと、たとえば单一チップ上に構成された固定関数論理ブロックとを含み得る。

【0004】

デュアルプロセッサまたはクワッドプロセッサなどのマルチプロセッサ(MP)は一般に、マルチレベルメモリ階層を利用する共有メモリシステムとして設計されている。そのような共有メモリMPでは、データはプライベートデータおよび共有データとして編成され得る。プライベートデータは、MPにおける各プロセッサによってローカルに使用するためにさらに編成される。共有データは、プロセッサ間でデータを効率的に通信し、プロセッサ間でデータのコヒーレンスを効率的に維持する機構を必要とする。プロセッサ間でデータを効率的に通信する1つの機構は、マルチレベルメモリ階層内でコヒーレントバスを使用することであり、コヒーレントバスは、共有されるデータがプロセッサの各々の間で一貫していることを保証するコヒーレントプロトコルをサポートする。40

【0005】

50

たとえば、バスは、共有メモリ階層内のレベル2キャッシュ位置においてなど、共有データのコヒーレンスを必要とするキャッシュレベルにおいて使用され得る。コヒーレントバスは、MPにおける各プロセッサに関連付けられた各レベル2キャッシュ間で利用される。変更-所有-排他-共有-無効(MOESI: Modified Owned Exclusive Shared Invalid)プロトコルなど、共有されるデータの一貫性を維持するための様々なプロトコルが開発されてきた。MOESIプロトコルでは、各キャッシュラインは、キャッシュラインが現在のキャッシュのみに存在し、ダーティである(変更(modified))か、キャッシュラインが現在のキャッシュのみに存在し、クリーンである(排他(exclusive))か、キャッシュラインがMPにおける他のキャッシュに記憶される可能性があり、現在のキャッシュにおいてダーティである(所有(owned))か、キャッシュラインがMPにおける他のキャッシュに記憶される可能性があり、現在のキャッシュにおいてクリーンである(共有(shared))か、キャッシュラインが現在のキャッシュにおいて無効である(無効(invalid))かを示すようにタグ付けされる。キャッシュラインが書き込まれるたびに、その書き込みが複数のキャッシュにおいて共有される対応するデータに及ぼす影響を判断するために、MOESI状態がチェックされる。

#### 【 0 0 0 6 】

マルチプロセッサでは、セマフォ管理のために各処理エージェントによって特殊命令が使用される。セマフォ管理はしばしば、メモリロケーションを読み取り、予約グラニュール(reservation granule)を設定し、予約グラニュールの状態に基づいて条件付きでメモリロケーションを書き込むための1組の特殊ロード/ストア命令を伴う。バスを介してキャッシュコヒーレンスを維持するシステムでは、2つ以上のプロセッサが同じセマフォを求めて競合している場合、これらのセマフォ管理命令がライロックまたは悪いパフォーマンスをもたらす可能性がある。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【 0 0 0 7 】

そのいくつかの態様の中で、本開示は、コヒーレントバスを介したセマフォ管理のためのより効率的な方法および装置を提供することが望ましいことを認識する。そのために、本発明の一実施形態は、マルチプロセッサにおけるコヒーレントバスを介したセマフォ管理のための方法を対象とする。第1のプロセッサに対してローカルな第1のキャッシュは、第1のプロセッサから発行されたロード排他(load exclusive)命令に応答して、ターゲットアドレスにおいてミスしたと判断される。読み取り優先排他コマンド(read prefer exclusive command)は、コヒーレントバス上で第1のキャッシュから第2のプロセッサに対してローカルな第2のキャッシュに発行される。読み取り優先排他コマンドに応答して、第2のキャッシュ内の予約グラニュールはタグ付けされていない状態であると判断される。第2のキャッシュ内のキャッシュラインは、このアドレスに対する第2のキャッシュ内の予約グラニュールはタグ付けされていない状態であるという判断に応答して、無効化される。

#### 【 0 0 0 8 】

別の実施形態は、マルチプロセッシングシステムにおけるコヒーレントバスを介したセマフォ管理のための装置を対象とする。第1のキャッシュコントローラは、第1のキャッシュがロード排他命令によって提供されたターゲットアドレスにおいてデータをミスしたことに応答して、コヒーレントバス上で第1のキャッシュから第2のキャッシュに読み取り優先排他コマンドを発行するように構成され、第1のキャッシュがロード排他命令を発行した第1の処理エージェントに結合され、第2のキャッシュが第2の処理エージェントに結合される。第2のキャッシュコントローラは、コヒーレントバスをスヌープし、第2のキャッシュ内のスヌープされた読み取り優先排他コマンドおよび予約グラニュールがこのターゲットアドレスに対してタグ付けされたことに応答して、第2のキャッシュ内のラインの状態が有効および共有状態であることを保証するように構成される。

#### 【 0 0 0 9 】

別の実施形態は、マルチプロセッサにおけるコヒーレントバスを介したセマフォ管理の

10

20

30

40

50

ための方法を対象とする。第1のプロセッサに対してローカルな第1のキャッシュは、第1のプロセッサから発行されたロード排他命令に応答して、ターゲットアドレスにおいてヒットしたと判断され、アクセスされた第1のキャッシュラインは共有または所有状態である。アップグレード優先排他コマンド(upgrade prefer exclusive command)は、コヒーレントバス上で第1のキャッシュから第2のプロセッサに対してローカルな第2のキャッシュに発行される。第2のキャッシュは、アップグレード優先排他コマンドに応答して、ターゲットアドレスにおいてヒットしたと判断され、アクセスされた第2のキャッシュラインの予約グラニュールは、タグ付けされていない状態である。第1のプロセッサによって要求されたラインは、第2のキャッシュラインが共有状態であることに応答して、排他状態にアップグレードされる。

10

#### 【0010】

別の実施形態は、コンピュータ可読プログラムデータおよびコードで符号化されたコンピュータ可読非一時的媒体を対象とする。第1のプロセッサに対してローカルな第1のキャッシュは、第1のプロセッサから発行されたロード排他命令に応答して、ターゲットアドレスにおいてミスしたと判断される。読み取り優先排他コマンドは、コヒーレントバス上で第1のキャッシュから第2のプロセッサに対してローカルな第2のキャッシュに発行される。第2のキャッシュ内のキャッシュラインは、このアドレスに対する第2のキャッシュ内の予約グラニュールがタグ付けされていない状態であることに応答して、無効化される。

#### 【0011】

さらなる実施形態は、マルチプロセッシングシステムにおけるコヒーレントバスを介したセマフォ管理のための装置を対象とする。第1のキャッシュがロード排他命令によって提供されたターゲットアドレスにおいてデータをミスしたことに応答して、コヒーレントバス上で第1のキャッシュから第2のキャッシュに読み取り優先排他コマンドを発行する手段であって、第1のキャッシュがロード排他命令を発行した第1の処理エージェントに結合され、第2のキャッシュが第2の処理エージェントに結合される、手段が利用される。コヒーレントバスをスヌープし、第2のキャッシュ内のスヌープされた読み取り優先排他コマンドおよび予約グラニュールがこのターゲットアドレスに対してタグ付けされたことに応答して、第2のキャッシュ内のラインの状態が有効および共有状態であることを保証する手段が利用される。

20

#### 【0012】

本発明の他の実施形態が、本発明の様々な実施形態が例として図示および説明されている以下の詳細な説明から、当業者には容易に明らかになることを理解されたい。了解されるように、本発明は、他の実施形態および異なる実施形態が可能であり、そのいくつかの詳細は、すべてが本発明の趣旨および範囲から逸脱することなく、様々な他の点において変更が可能である。したがって、図面および詳細な説明は、限定的なものではなく、本質的に例示的なものとして見なされるべきである。

30

#### 【0013】

本発明の様々な態様を、限定ではなく例として、添付の図面に示す。

#### 【図面の簡単な説明】

#### 【0014】

40

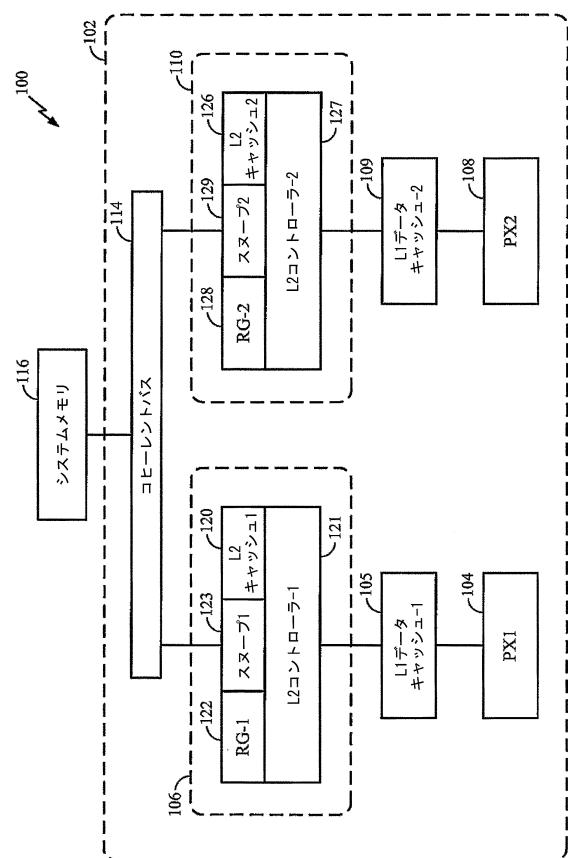

【図1】デュアルコアマルチプロセッサ(MP)システムを示す図である。

【図2A】2つの処理エージェント間のセマフォ管理の基本的な例を示す図である。

【図2B】コヒーレントバスを介したセマフォ管理の第1のシナリオを示す図である。

【図2C】コヒーレントバスを介したセマフォ管理の第2のシナリオを示す図である。

【図2D】ライブロック状況を示す、コヒーレントバスを介したセマフォ管理の第3のシナリオを示す図である。

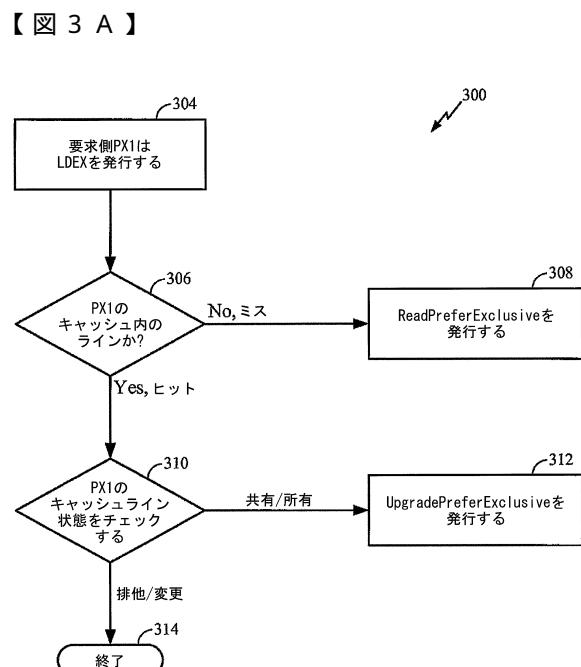

【図3A】効率的なライブロック回避のためのサポートを有するセマフォ管理プロセスを示す図である。

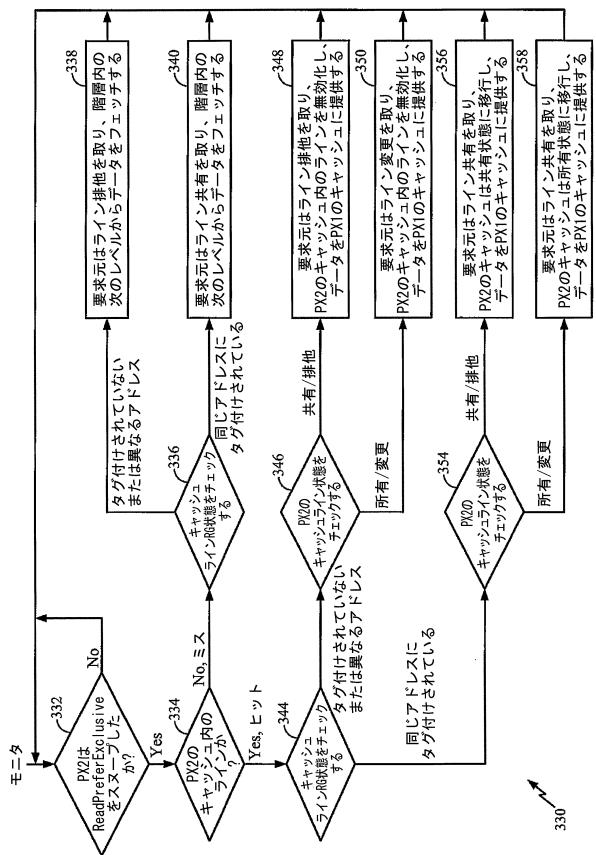

【図3B】読み取り優先排他セマフォ管理プロセスを示す図である。

【図3C】アップグレード優先排他セマフォ管理プロセスを示す図である。

50

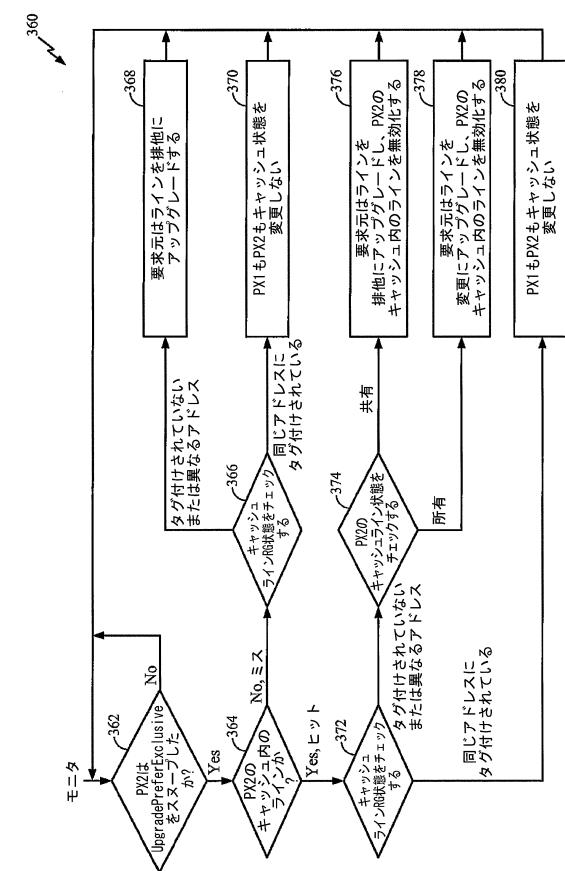

【図4A】読み取り優先排他バスコマンドを使用した、例示的な第1のセマフォ管理技法を示す図である。

【図4B】読み取り優先排他バスコマンドを使用した、例示的な第2のセマフォ管理技法を示す図である。

【図4C】アップグレード優先排他バスコマンドを使用した、例示的な第3のセマフォ管理技法を示す図である。

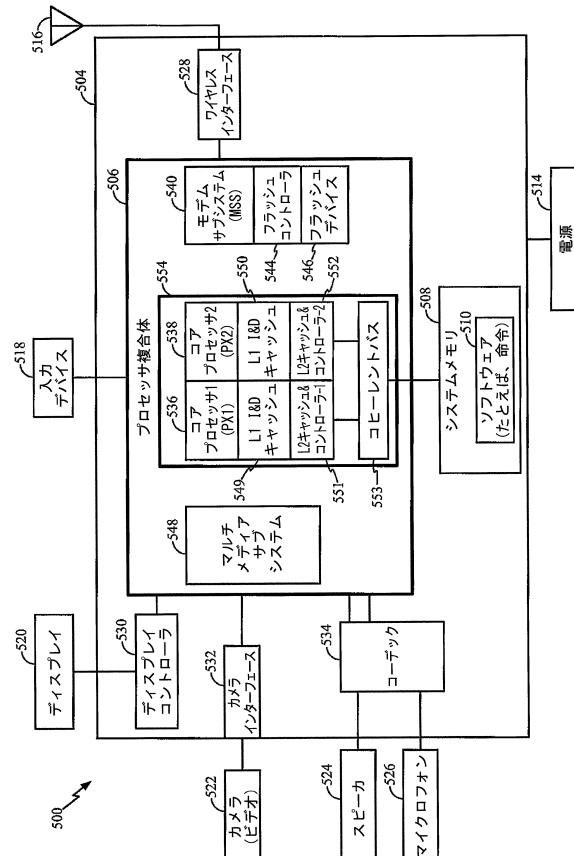

【図5】本発明の実施形態による効率的なライロック回避を伴う例示的なセマフォ管理を利用するポータブルデバイスの特定の実施形態を示す図である。

#### 【発明を実施するための形態】

##### 【0015】

10

添付の図面に関して以下に記載する詳細な説明は、本発明の様々な例示的な実施形態の説明として意図されており、本発明が実施され得る実施形態のみを表すことを意図されているわけではない。詳細な説明は、本発明の完全な理解をもたらす目的で、具体的な詳細を含んでいる。しかしながら、本発明がこれらの具体的な詳細なしに実施され得ることが、当業者には明らかであろう。場合によっては、本発明の概念を曖昧にするのを回避するために、よく知られている構造および構成要素がブロック図の形態で示されている。

##### 【0016】

図1は、マルチプロセッサ(MP)システム100を示す。MPシステム100は、第1のコアプロセッサなどの第1の処理エージェント(PX1)104と、レベル1データキャッシュ-1(L1 Dcache-1) 105と、L2キャッシュおよびコントローラ-1 106と、第2のコアプロセッサなどの第2の処理エージェント(PX2)108と、レベル1データキャッシュ-2(L1 Dcache-2) 109と、L2キャッシュおよびコントローラ-2 110と、コヒーレントバス114とを有するデュアルコアシステム102と、メインメモリ116とを備える。L2キャッシュおよびコントローラ-1 106は、L2キャッシュ1 120と、L2コントローラ-1 121と、予約グラニュール-1(RG-1) 122と、スヌープ1ユニット123とを含む。L2キャッシュおよびコントローラ-2 110は、L2キャッシュ2 126と、L2コントローラ-2 127と、予約グラニュール-2(RG-2) 128と、スヌープ2ユニット129とを含む。コヒーレントバスは、本明細書で説明する技法と同様の技法を使用して、メモリ階層内の他のレベルにおけるキャッシュ間でも使用され得る。異種マシン編成におけるプロセッサまたはハードウェアアクセラレータなどの他のタイプの処理エージェントはセマフォ管理のための特殊命令を実行し得るので、システム100は同種マシンに限定されないことに留意されたい。RG-1 122およびRG-2 128などの予約グラニュール(RG)は、有効ビットなどの有効表示と、アドレスを記憶するためのタグフィールドとを有するプログラムアクセス可能な記憶ロケーションを備える。RG-1 122およびRG-2 128は関連するL2キャッシュコントローラ内に示されているが、予約グラニュールのロケーションはそのように限定されず、デュアルコアシステム102内の他の場所、たとえば、異なるレベルのメモリ階層用のコントローラなどに配置され得る。

20

##### 【0017】

30

デュアルコアMPシステム100では、セマフォ管理のために、PX1 104およびPX2 108などの各処理エージェントによって特殊命令が使用される。セマフォ管理はしばしば、メモリロケーションを読み取り、予約グラニュールを設定し、予約グラニュールの状態に基づいて条件付きでメモリロケーションを書き込むための1組の特殊ロード/ストア命令を伴う。これらの特殊命令は、ロード排他(LDEX)およびストア排他(STEX)と呼ばれる。予約グラニュール(RG)は、LDEXに対して返されたデータ値が、LDEXの実行とSTEXの実行との間に、別の処理エージェントによって変更されたかどうかを判断するために使用される。言い換えれば、RGは、2つの個別の命令が別々に実行されていても、それらの命令がアトミックであるかのように一緒に振る舞うことを可能にするために使用される。読み取り優先排他コマンドおよびアップグレード優先排他コマンドを含む、効率的なセマフォ管理のための特殊コマンドについても、図3A～図3Cおよび図4A～図4Cに関してさらに詳細に説明する。

40

##### 【0018】

MPシステム100は、コヒーレントバス114を介したセマフォ管理を提供する。L2キャッシュ

50

ユおよびコントローラ-1 106などの、第1のキャッシュがロード排他命令によって提供されたターゲットアドレスにおいてデータをミスしたことに応答して、コヒーレントバス上で第1のキャッシュから第2のキャッシュに読み取り優先排他コマンドを発行する手段であって、第1のキャッシュがロード排他命令を発行した第1の処理エージェントに結合され、第2のキャッシュが第2の処理エージェントに結合される、手段が利用される。L2キャッシュおよびコントローラ-2 110などの、コヒーレントバスをスヌープし、ターゲットアドレスにおいてデータを第1のキャッシュに提供することによって、スヌープされた読み取り優先排他コマンドに応答する手段が利用される。第2のキャッシュ内の予約グラニュールがこのターゲットアドレスに対してタグ付けされたことに応答して、第2のキャッシュ内のラインの状態が有効状態になる。

10

#### 【0019】

たとえば、ロード排他(LDEX)またはストア排他(STEX)を実行する第1の処理エージェント(PX1)104に関連付けられたL2キャッシュおよびコントローラ-1 106は、コヒーレントバス114上でコマンドを識別するためのデコーダによって構成され得る。また、L2キャッシュおよびコントローラ-1 106は、アクセスされたキャッシュラインの状態を識別するためのハードウェア、および現在のキャッシュライン状態または現在の予約グラニュール(RG)状態が対応する以前の状態から変わったかどうかを判断するための比較器によって構成される。L2キャッシュ1 120内のアクセスされたキャッシュラインの状態などのキャッシュライン状態、およびRG-1 122の状態は、記憶された状態値に並行してアクセスする別個の機構によって判断される。次いで、判断された状態値は、バスコマンドを発行する必要があるかどうかを識別する論理手段によって結合される。バスコマンドを発行する必要がある場合、発行すべき適切なバスコマンドが選択される。キャッシュ状態およびRG状態を連続的にチェックすることができるが、そのような手法はこれらの状態を並行してチェックすることほど効率的ではない場合がある。たとえば、スヌープ1 123およびスヌープ2 129などのスヌーパは、コヒーレントバス114上のバスコマンドを復号することによって、別個に並行して動作する。バスコマンドを検出し選択した特定の動作は、図3A～図3Cおよび図4A～図4Cに示す動作に続き、これらの動作は、キャッシュラインの状態を変更すること、RG状態を変更すること、およびコヒーレントバス114上にコマンドを生じさせるLDEXまたはSTEXを実行する処理エージェントへの応答を提供することを含む。LDEXを実行する処理エージェントへのさらなる応答は、たとえば、図3Bのブロック348、350、356、および358に関して以下に示すものなどのデータを提供することを含み得る。

20

#### 【0020】

図2Aは、2つの処理エージェント、PX1 202とPX2 203との間のセマフォ管理200の基本的な例を示す。第1の動作204では、PX1は、PX1に関連付けられた予約グラニュール(RG)をLDEXのメモリアドレスAとタグ付けさせるLDEX Aを実行する。第2の動作205では、PX1は何のアクションも取らず、PX2はやはり、PX2に関連付けられたRGをメモリアドレスAとタグ付けすることになるLDEX Aを実行する。マルチプロセッサ(MP)環境では、ある処理エージェントからのSTEXは、STEXアドレスにタグ付けされている場合、別の処理エージェントのRGをタグ解除することを必要とする。したがって、第3の動作206では、PX1は、PX1のRGがタグ付けされ、PX2のRGからタグを外すためのバスコマンドが発行されているので実行を完了するSTEX Aを実行する。バスコマンドに応答して、PX2のRGがタグ解除される。第4の動作207では、PX2は、PX2のRGがもはやタグ付けされていないので失敗するSTEXを実行しようと試みる。異なるシナリオでは、PX1がSTEXを実行する前にPX2がPX1のRGによってアドレス指定されたメモリを更新し、PX1のRG内のタグがクリアされた場合、RGがもはやタグ付けされていないので、PX1のSTEXはメモリを更新しない。タグをクリアすることは、PX1に、そのLDEXが返した値は今では古く、有効ではないことを示す。

30

#### 【0021】

バスを介してキャッシュコヒーレンスを維持するシステムでは、これらのセマフォ管理命令がライブロックまたは悪いパフォーマンスをもたらす可能性がある。最良のパフォーマンスは、セマフォ管理命令を実行するプロセッサに関連付けられたキャッシュが、STEX

40

50

が実行されるときの変更状態または排他状態のいずれかにおいてキャッシュラインを含むときに生じる。STEXによってアドレス指定されるキャッシュラインが任意の他の状態である場合、STEXを完了することが可能になる前に、変更状態または排他状態においてラインを取得するためのバス要求が行われなければならない。

#### 【 0 0 2 2 】

図2Bは、コヒーレントバスを介したセマフォ管理220の第1のシナリオを示す。この第1のシナリオの場合、処理エージェントPX1\_202および処理エージェントPX2\_203は同じセマフォに同時にアクセスしようとしておらず、PX2がアドレスAにおいてデータを含むキャッシュラインを保持する。また、PX2のRGはタグ付けされていない。第1の動作224では、PX1はLDEX\_Aを実行し、共有状態においてラインを取得する。次いで、PX1のRGはアドレスAにタグ付けされる。ラインは共有状態であるので、PX1のラインを排他状態に変更するために、PX2のラインのコピーが無効化されなければならない。第2の動作225では、PX1は、PX2のラインを無効化するためのバスコマンドを発行させるSTEX\_Aを発行する。アドレスAとのPX2のラインを無効化するために発行されたコマンドは、PX1がセマフォを得ようとしているときに、追加の待ち時間を生じさせる。10

#### 【 0 0 2 3 】

図2Cは、コヒーレントバスを介したセマフォ管理240の第2のシナリオを示す。この第2のシナリオの場合、PX1\_202、PX2\_203、およびコヒーレントバスは、LDEXの実行時にライン排他を取得するように構成される。PX2は、アドレスAにおいてデータを含むキャッシュラインを保持する。また、PX2のRGは、PX1のLDEX\_Aが発行される前にタグ付けされていない。第1の動作244では、PX1は、読み取り排他バスコマンドを発行させるLDEX\_Aを実行し、排他状態においてラインを取得する。ラインが排他状態であるので、PX2のラインのコピーが無効化され、次いでPX1のRGがアドレスAにタグ付けされる。第2の動作245では、PX1は、PX1のRGがタグ付けされているので実行を完了し、PX1のLDEXが排他状態においてラインAをすでに取得したのでバスコマンドを発行する必要がないSTEX\_Aを発行する。このセマフォ管理技法240は、PX1のSTEX\_Aが実行を完了する前に追加のバスコマンドを作成することを必要としないことによってパフォーマンスを助けるが、図2Dに関して説明したライロック状況を引き起こす可能性がある。20

#### 【 0 0 2 4 】

図2Dは、ライロック状況を示す、コヒーレントバスを介したセマフォ管理260の第3のシナリオを示す。この第3のシナリオの場合、PX1\_202、PX2\_203、およびコヒーレントバスは、LDEXの実行時にライン排他を取得するように構成される。PX1とPX2は両方とも、アドレスAにおいてデータを含むキャッシュラインのコピーを保持する。第1の動作264では、PX1は、読み取り排他バスコマンドを発行させるLDEX\_Aを実行し、排他状態においてラインを取得する。ラインが排他状態であるので、PX2のラインのコピーが無効化され、次いでPX1のRGがアドレスAにタグ付けされる。PX2のRGがタグ付けされている場合、PX2のRGはタグ解除される。第2の動作265では、PX2は、読み取り排他バスコマンドを発行させるLDEX\_Aを実行し、排他状態においてラインを取得する。ラインが排他状態であるので、PX1のラインのコピーが無効化され、PX1のRGがタグ解除され、次いでPX2のRGがアドレスAにタグ付けされる。第3の動作266では、PX1は、そのRGがもはやタグ付けされていないので失敗し、LDEX/STEXプロセスを繰り返させるSTEXを発行する。第4の動作267では、PX1は、読み取り排他バスコマンドを発行させるLDEX\_Aを実行し、PX1は、排他状態においてラインを取得する。ラインが排他状態であるので、PX2のラインのコピーが無効化され、次いでPX1のRGがアドレスAにタグ付けされ、PX2のRGがタグ解除される。第5の動作268では、PX2は、そのRGがもはやタグ付けされていないので失敗し、LDEX/STEXプロセスを繰り返させるSTEXを発行する。第6の動作269および継続する動作では、ライロック状況により、PX1とPX2の両方におけるLDEX/STEXプロセスが繰り返される。3040

#### 【 0 0 2 5 】

ライロック状況が生じないことを保証するために、LDEX動作が常にSTEX動作に先行し、したがって、LDEXは、STEXが実行されることを見越して、変更状態または排他状態にお50

いてラインを取得するためのヒントとして使用され得ることに留意されたい。しかしながら、図2Cおよび図2Dの動作によって示されるように、一実装形態は、LDEXの実行時に変更状態または排他状態においてラインを要求することができない。そのような手法は、図2Dに示すように、2つのプロセッサが同じセマフォを求めて競合していた場合、ライプロックを引き起こす可能性がある。このライプロック状況を回避するために、以前の実装形態では、すべての他のキャッシュがラインを無効にしていた場合、LDEXが排他状態においてラインを取得することを可能にしているが、任意の他のキャッシュがラインを無効以外の状態にしていた場合、ラインを共有して取ることを必要とする。LDEXを実行する処理エンジニアによってラインが共有して取られる場合、STEXは、図2Bに示すように、他のキャッシュのラインの共有コピーを無効化するための追加のバス要求を行わなければならず、このことはパフォーマンスのロスを引き起こす。

#### 【0026】

デュアルコアシステム102は、システムメモリ116に関連付けられるような非一時的コンピュータ可読媒体に記憶され、第1の処理エンジニア(PX1)104および第2の処理エンジニア(PX2)108などのコンピュータに図3A～図3Cおよび図4A～図4Cに示すように動作するプログラムを実行せしめるように実行可能である、ソフトウェア命令を実行するように構成される。PX1 104およびPX2 108は、異なるレベルのキャッシュメモリ105、120、109、および126ならびにシステムメモリ116からアクセスされるソフトウェア命令を実行するように構成される。

#### 【0027】

図3Aは、効率的なライプロック回避のためのサポートを有するセマフォ管理プロセス300を示す。ライプロックおよび関連するパフォーマンスのロスを回避するために、コヒーレントバスプロトコルは新しいコマンドを含むように変更され、これらのコマンドは、たとえば、ブロック308において読み取り優先排他コマンドを発行させ、ブロック312においてアップグレード優先排他コマンドを発行させるために発行される。ブロック308およびブロック312におけるコマンドは、ブロック306に関連付けられたキャッシュアクセスと、ブロック310に関連付けられたキャッシュライン状態と、L2キャッシュおよびコントローラ-1 106ならびにL2キャッシュおよびコントローラ-2 110などのキャッシュコントローラ内に作成された予約グラニュール(RG)の状態とに応答して動作する。

#### 【0028】

プロセス300は、PX1 104などの要求側コア処理エンジニアがLDEX A命令を発行するブロック304で始まる。ブロック306において、要求側PX1に関連付けられた、図1のL2キャッシュ1 120などのキャッシュは、アドレスAにおいてデータを有するラインがキャッシュ内にあるかどうかを判断する。ラインがキャッシュ内に存在しない場合、プロセス300はブロック308に進む。ブロック308において、PX1に関連付けられたL2キャッシュコントローラ-1 121などのコヒーレントバスコントローラは、コヒーレントバス114上で読み取り優先排他コマンドを発行する。ブロック306に戻り、キャッシュ内のヒットによって示されるように、ラインがキャッシュ内に存在する場合、プロセス300はブロック310に進む。ブロック310において、PX1のキャッシュライン状態が共有を示すか、所有を示すか、排他を示すか、または変更を示すかの判断が行われる。状態が共有または所有である場合、プロセス300はブロック312に進む。ブロック312において、PX1に関連付けられたL2キャッシュコントローラ-1 121などのコヒーレントバスコントローラは、コヒーレントバス114上でアップグレード優先排他コマンドを発行する。ブロック310に戻り、状態が排他または変更である場合、プロセス300はブロック314に進み、PX1のLDEX A命令の発行に関連付けられたプロセスが完了する。

#### 【0029】

図3Bは、読み取り優先排他セマフォ管理プロセス330を示す。RGは、LDEX命令に応答して、ターゲットキャッシュラインアドレスにタグ付けされる。STEX命令が実行のために発行されたときに、STEXを実行する処理エンジニア用のRGがタグ付けされている場合、STEX命令はメモリを更新するだけである。読み取り優先排他動作は、要求側マスタがキャッシュ

10

20

30

40

50

ラインに記憶する可能性があり、可能な場合、要求側マスタが排他状態に移行するのを可能にするために、その他のキャッシュの各々がラインを無効化するべきであるという、MP内の他のキャッシュに対するヒントとして使用される。たいていの場合、これにより、その他のマスタがラインを無効化する(このことは、ラインを放棄すると呼ばれることがある)ことになり、要求側マスタがライン排他を取ることになる。キャッシュラインは、そのライン内のデータが第2のキャッシュ内で消失している場合でも、共有としてマークされ得ることに留意されたい。第2のキャッシュが依然としてそのRGをターゲットアドレスにタグ付けしているので、第1のキャッシュ内のキャッシュラインは共有としてマークされる。第2のキャッシュはそのキャッシュ内でラインを有効にしないが、第2のキャッシュのRGは依然として有効であり、第1のキャッシュは、第2のキャッシュ内にタグ付けされたRGがあることを記憶しておくために、ライン共有を取る。第2のキャッシュがそのキャッシュ内でラインを有効にしなくても、第2のキャッシュ内のRGをタグ解除するために、依然としてSTEX命令をプロードキャストしなければならない。

10

#### 【0030】

別のキャッシュがラインを放棄することができない唯一の時は、その別のキャッシュがそれ自体でセマフォ管理シーケンスを実行しており、その別のキャッシュのRGが同じアドレスにタグ付けされているときであり、このことがライブロックをもたらす可能性があるからである。たいていの場合、マルチプロセッサは同じアドレスに対するセマフォ管理シーケンスを同時に実行していない。その結果、この実施形態は、要求側マスタのLDEXが排他状態においてラインを取ることができる回数を著しく増加させることができ、このことは、MPの各プロセッサにおけるパフォーマンスを高める。

20

#### 【0031】

プロセス330は、読み取り優先排他コマンドがコヒーレントバス上で検出されたかどうかを判断するモニタから、ブロック332で始まる。PX2用に動作するスヌーパによってコヒーレントバス114からコマンドが検出される(スヌープされるとも呼ばれる)と、プロセス330はブロック334に進む。ブロック334において、ブロック304において発行されたLDEX命令に関連付けられたラインがPX2のキャッシュ内にあるかどうかの判断が行われる。キャッシュ内のミスによって示されるように、ラインがPX2のキャッシュ内にないという判断である場合、プロセス330はブロック336に進む。ブロック336において、PX2に関連付けられたキャッシュライン予約グラニュール(RG)がLDEX命令の同じアドレスAにタグ付けされているか、またはタグ付けされていないか、またはアドレスAとは異なるアドレスにタグ付けされているかの判断が行われる。ラインがタグ付けされていないか、またはAとは異なるアドレスにタグ付けされている場合、プロセス330はブロック338に進む。ブロック338において、要求元、この場合はPX1は、ライン排他を取り、データは、L3キャッシュからなど、メモリ階層内の次のレベルからフェッチされる。次いで、プロセス330はブロック332に戻る。ブロック336に戻り、ラインが同じアドレスにタグ付けされている場合、プロセス330はブロック340に進む。ブロック340において、要求元、この場合はPX1は、ライン共有を取り、データはメモリ階層内の次のレベルからフェッチされる。次いで、プロセス330はブロック332に戻る。

30

#### 【0032】

ブロック334に戻り、キャッシュ内のヒットによって示されるように、ラインがPX2のキャッシュ内にあるという判断である場合、プロセス330はブロック344に進む。ブロック344において、PX2に関連付けられたキャッシュライン予約グラニュール(RG)がLDEX命令の同じアドレスAにタグ付けされているか、またはタグ付けされていないか、またはアドレスAとは異なるアドレスにタグ付けされているかの判断が行われる。ラインがタグ付けされていないか、またはAとは異なるアドレスにタグ付けされている場合、プロセス330はブロック346に進む。ブロック346において、PX2キャッシュライン状態が共有もしくは排他であるか、またはPX2キャッシュライン状態が所有もしくは変更であるかの判断が行われる。PX2キャッシュライン状態が共有または排他である場合、プロセス330はブロック348に進む。ブロック348において、要求元PX1はライン排他を取り、PX2のキャッシュ内のラインを

40

50

無効化し、アクセスされたデータをPX1のキャッシュに提供する。次いで、プロセス330はブロック332に戻る。ブロック346に戻り、PX2キャッシュライン状態が所有または変更である場合、プロセス330はブロック350に進む。ブロック350において、要求元PX1はライン変更を取り、PX2のキャッシュ内のラインを無効化し、アクセスされたデータをPX1のキャッシュに提供する。次いで、プロセス330はブロック332に戻る。

#### 【0033】

ブロック344に戻り、ラインが同じアドレスにタグ付けされている場合、プロセス330はブロック354に進む。ブロック354において、PX2キャッシュライン状態が共有もしくは排他であるか、またはPX2キャッシュライン状態が所有もしくは変更であるかの判断が行われる。PX2キャッシュライン状態が共有または排他である場合、プロセス330はブロック356に進む。ブロック356において、要求元PX1はライン共有を取り、PX2のキャッシュは、排他状態である場合は共有状態に移行し、共有状態である場合は共有状態にとどまり、アクセスされたデータをPX1のキャッシュに提供する。次いで、プロセス330はブロック332に戻る。ブロック354に戻り、PX2キャッシュライン状態が所有または変更である場合、プロセス330はブロック358に進む。ブロック358において、要求元PX1はライン共有を取り、PX2のキャッシュは、変更状態である場合は所有状態に移行し、所有状態である場合は所有状態にとどまり、アクセスされたデータをPX1のキャッシュに提供する。次いで、プロセス330はブロック332に戻る。

#### 【0034】

図3Cは、アップグレード優先排他セマフォ管理プロセス360を示す。プロセス360は、アップグレード優先排他コマンドがコヒーレントバス上で検出されたかどうかを判断するモニタから、ブロック362で始まる。PX2用に動作するスヌープユニットまたはスヌーパによってコヒーレントバス114からコマンドが検出される(スヌープされるとも呼ばれる)と、プロセス360はブロック364に進む。ブロック364において、ブロック304において発行されたLDEX命令に関連付けられたラインがPX2のキャッシュ内にあるかどうかの判断が行われる。キャッシュ内ミスによって示されるように、ラインがPX2のキャッシュ内にないという判断である場合、プロセス360はブロック366に進む。ブロック366において、PX2に関連付けられたキャッシュライン予約グラニュール(RG)がLDEX命令の同じアドレスAにタグ付けされているか、またはタグ付けされていないか、またはアドレスAとは異なるアドレスにタグ付けされているかの判断が行われる。ラインがタグ付けされていないか、またはAとは異なるアドレスにタグ付けされている場合、プロセス360はブロック368に進む。ブロック368において、要求元、この場合はPX1は、ライン状態を排他にアップグレードする。次いで、プロセス330はブロック332に戻る。ブロック366に戻り、ラインが同じアドレスにタグ付けされている場合、プロセス360はブロック370に進む。ブロック370において、何のアクションも取られず、PX1もPX2もキャッシュ状態を変更しない。次いで、プロセス330はブロック332に戻る。

#### 【0035】

ブロック364に戻り、キャッシュ内ヒットによって示されるように、ラインがPX2のキャッシュ内にあるという判断である場合、プロセス360はブロック372に進む。ブロック372において、PX2に関連付けられたキャッシュライン予約グラニュール(RG)がLDEX命令の同じアドレスAにタグ付けされているか、またはタグ付けされていないか、またはアドレスAとは異なるアドレスにタグ付けされているかの判断が行われる。ラインがタグ付けされていないか、またはAとは異なるアドレスにタグ付けされている場合、プロセス360はブロック374に進む。ブロック374において、PX2キャッシュライン状態が共有であるか、またはPX2キャッシュライン状態が所有であるかの判断が行われる。PX2キャッシュライン状態が共有である場合、プロセス360はブロック376に進む。ブロック376において、要求元PX1はラインを排他状態にアップグレードし、PX2のキャッシュ内のラインを無効化する。次いで、プロセス360はブロック362に戻る。ブロック374に戻り、PX2キャッシュライン状態が所有である場合、プロセス360はブロック378に進む。ブロック378において、要求元PX1はラインを変更状態にアップグレードし、PX2のキャッシュ内のラインを無効化する。次い

10

20

30

40

50

で、プロセス360はブロック362に戻る。

**【0036】**

ブロック372に戻り、ラインが同じアドレスにタグ付けされている場合、プロセス360はブロック380に進む。ブロック380において、何のアクションも取られず、PX1もPX2もキャッシュ状態を変更しない。次いで、プロセス360はブロック362に戻る。

**【0037】**

代替実施形態では、読み取り優先排他コマンドおよびアップグレード優先排他コマンドは、既存のバスコマンドに適切な属性を含むことによって判断され得る。たとえば、読み取り優先排他コマンドの機能を提供するために、要求側プロセッサがライン排他を必要とする可能性があることを示す属性が読み取りコマンドに追加され得る。たいていの場合、他の処理エージェントは、要求側エージェントがライン排他を取ることを可能にする属性に応答して、キャッシュラインを解放する。要求側プロセッサが排他状態においてラインを必要とする可能性があることを示すように設定された属性を有する読み取りコマンドは、読み取り優先排他コマンドと呼ばれることもあることに留意されたい。また、アップグレード優先排他コマンドの機能は、アップグレードコマンドに、要求側プロセッサがライン排他を必要とする可能性があることを示す属性を含むことによって、実装され得る。

10

**【0038】**

図4Aは、読み取り優先排他バスコマンドを使用した、例示的な第1のセマフォ管理技法400を示す。この第1の技法の場合、PX1 402、PX2 403、およびコヒーレントバスは、LDEXがそれ自体でライン排他を要求することができないとき、LDEXの実行時にライン排他を機会主義的に取得するように構成される。PX2は、アドレスAにおいてデータを含むキャッシュラインを保持する。また、PX2のRGは、PX1のLDEX Aが発行される前にタグ付けされていない。第1の動作404では、PX1は、読み取り優先排他バスコマンドを発行させるLDEX Aを実行し、排他状態においてラインを取得する。ラインが排他状態であるので、PX2のラインのコピーが無効化され、次いでPX1のRGがアドレスAにタグ付けされる。第2の動作405では、PX1は、PX1のRGがタグ付けされているので実行を完了するSTEX Aを発行し、追加のバスコマンドは発行されない。さらなるアクションはPX2によって必要とされない。セマフォ管理技法400は、PX1のSTEX Aが実行を完了する前に追加のバスコマンドを作成することを必要としないことによってパフォーマンスを助ける。

20

**【0039】**

30

図4Bは、読み取り優先排他バスコマンドを使用した、例示的な第2のセマフォ管理技法420を示す。この第2のセマフォ管理技法420の場合、PX1 402、PX2 403、およびコヒーレントバスは、LDEXの実行時にライン排他を取得するように構成される。PX1とPX2は両方とも、アドレスAにおいてデータを含む、それに関連するキャッシュ内で、キャッシュラインのコピーを保持する。PX2のRGは、PX1がLDEX Aを発行する前にタグ付けされていない。第1の動作424では、PX1は、読み取り優先排他バスコマンドを発行させるLDEX Aを実行し、排他状態においてラインを取得する。ラインが排他状態であるので、PX2のラインのコピーが無効化され、次いでPX1のRGがアドレスAにタグ付けされる。第2の動作425では、PX2は、読み取り優先排他バスコマンドを発行させるLDEX Aを実行し、共有状態においてラインを取得する。ラインが共有状態であるので、PX1のラインのコピーは共有状態に変更され、PX1のRGはアドレスAにタグ付けされたままであり、PX2のRGはアドレスAにタグ付けされる。第3の動作426では、PX1は、PX2のラインを無効化し、PX2のRGをタグ解除するための追加のバスコマンドを発行させるSTEX Aを発行する。PX2のラインが無効化され、PX1のRGがタグ付けされているので、STEXは実行を完了する。AとのPX2のラインを無効化するために発行されたコマンドは、PX1がセマフォを得ようとしているときに、追加の待ち時間を生じさせる。しかしながら、ライブロックはない。追加のバスコマンドは、2つの処理工エージェントが同じセマフォを同時に取得しようとする比較的まれな場合にのみ、必要とされる。

40

**【0040】**

図4Cは、アップグレード優先排他バスコマンドを使用した、例示的な第3のセマフォ管

50

理技法440を示す。この第3の技法の場合、PX1 402、PX2 403、およびコヒーレントバスは、LDEXがそれ自体でライン排他を要求することができないとき、LDEXの実行時にライン排他を機会主義的に取得するように構成される。PX2は、アドレスAにおいてデータを含むキャッシュラインを保持する。また、PX2のRGは、PX1のLDEX Aが発行される前にタグ付けされていない。第1の動作444では、PX1は、そのL2キャッシュ内でヒットし、アップグレード優先排他バスコマンドを発行させるLDEX Aを実行し、排他状態においてラインを取得する。ラインが排他状態であるので、PX2のラインのコピーが無効化され、次いでPX1のRGがアドレスAにタグ付けされる。第2の動作445では、PX1は、PX1が排他状態においてラインを保持し、PX1のRGがタグ付けされているので、実行を完了するSTEX Aを発行する。さらなるアクションはPX2によって必要とされない。セマフォ管理技法440は、PX1のSTE X Aが実行を完了する前に追加のバスコマンドを作成することを必要としないことによってパフォーマンスを助ける。10

#### 【0041】

代替実施形態では、ブロック348、350、356、および358の場合、PX2に関連付けられたレベル2キャッシュによってデータを提供させるのではなく、データはメモリ階層内の次のレベルのキャッシュによってまたはメインシステムメモリから提供され得る。そのような場合、ブロック348および350において示されるキャッシュライン無効化は、データがどこから来たかに関係なく生じる。

#### 【0042】

図1は2つの処理エージェント、PX1 104およびPX2 108を有するシステムを示しているが、本明細書で説明する実施形態は、3つ以上の処理エージェントを有するシステムにも適用可能である。このさらなる実施形態では、各追加のL2キャッシュおよびコントローラは、複数のキャッシュコントローラ間のコヒーレントバスをスヌープし、バスコマンドを検出すると、図3A～図3Cおよび図4A～図4Cに関して説明した方法で別々に応答する。たとえば、3つの処理エージェントPX1、PX2、およびPX3を有するシステムでは、PX1が図3Aのブロック304などにおいてLDEXを発行し、また、ブロック306などにおいてPX1のキャッシュにおいてミスしており、L2キャッシュおよびコントローラ-1 106は、コヒーレントバス上で読み取り優先排他コマンドを発行する。PX2サブシステムおよびPX3サブシステムは両方とも、コヒーレントバスをスヌープし、読み取り優先排他コマンドを識別し、要求されたラインがPX2のキャッシュとPX3のキャッシュの両方にある場合、PX2のL2キャッシュおよびコントローラとPX3のL2キャッシュおよびコントローラは両方とも、関連する予約グラニュールの状態をチェックし、RGおよびキャッシュライン状態の判断された状態値に基づいて、適切なブロック348、350、356、または358に進む。各キャッシュコントローラがPX1サブシステムに提供するべきデータを有する、そのような場合、PX2用のコントローラがデータをPX1サブシステムに提供するか、またはPX3用のコントローラがデータをPX1サブシステムに提供するかを選ぶための適切な手段がコヒーレントバス上のプロトコルによって提供される。2030

#### 【0043】

図5は、本発明の実施形態による効率的なライブロック回避を伴う例示的なセマフォ管理を利用するポータブルデバイス500の特定の実施形態を示す。ポータブルデバイス500はワイヤレス電子デバイスであってもよく、ソフトウェア命令510を有するシステムメモリ508に結合されたプロセッサ複合体506を含むシステムコア504を含み得る。ポータブルデバイス500は、電源514と、アンテナ516と、キーボードなどの入力デバイス518と、液晶ディスプレイLCDなどのディスプレイ520と、ビデオ機能を有する1つまたは2つのカメラ522と、スピーカ524と、マイクロフォン526とを備える。システムコア504はまた、ワイヤレスインターフェース528と、ディスプレイコントローラ530と、カーラインインターフェース532と、コーデック534とを含む。プロセッサ複合体506は、2つのコア処理ユニット、ローカルレベル1命令およびデータ(L1 I&D)キャッシュ549を有するPX1 536と、ローカルレベル1命令およびデータ(L1 I&D)キャッシュ550を有するPX2 538とを含む、マルチプロセッサ(MP)システム554を含み得る。MPシステム554は、図1のデュアルコアシステム102に対4050

応し得る。プロセッサ複合体506はまた、モデムサブシステム540と、フラッシュコントローラ544と、フラッシュデバイス546と、マルチメディアサブシステム548と、レベル2キャッシュ0およびコントローラ0 551と、レベル2キャッシュ1およびコントローラ1 552と、コヒーレントバス553とを含み得る。フラッシュデバイス546は、リムーバブルフラッシュメモリを含んでもよく、または組込みメモリであってもよい。

#### 【0044】

例示的な例では、システムコア504は、図1、図3A～図3C、および図4A～図4Cに示すまたは図1、図3A～図3C、および図4A～図4Cに関連付けられた実施形態のいずれかに従って動作する。たとえば、図5に示すように、MPシステム554のデュアルコアプロセッサは、図3A～図3Cに示す動作を提供するために、それに関連するデュアルコアプロセッサのL1 I&Dキャッシュ549および550、L2キャッシュ551および552のメモリに、ならびにシステムメモリ508に記憶されたデータまたはプログラム命令にアクセスするように構成される。10

#### 【0045】

ワイヤレスインターフェース528は、アンテナ516およびワイヤレスインターフェース528を介して受信されたワイヤレスデータがMSS540に提供され、MPシステム554と共有され得るように、プロセッサ複合体506およびワイヤレスアンテナ516に結合され得る。カメラインターフェース532はプロセッサ複合体506に結合され、ビデオ機能を有するカメラ522などの1つまたは複数のカメラにも結合される。ディスプレイコントローラ530はプロセッサ複合体506およびディスプレイデバイス520に結合される。コーダ/デコーダ(コーデック)534もプロセッサ複合体506に結合される。1組のステレオスピーカを備え得るスピーカ524およびマイクロフォン526はコーデック534に結合される。周辺デバイスおよびそれに関連するインターフェースは例示的なものであり、量または能力において限定されない。たとえば、入力デバイス518は、特定のデバイスに別々にまたは異なるデバイスに組み合わせて実装され得る、ユニバーサルシリアルバス(USB)インターフェースなど、QWERTY式キーボード、英数字キーボード、数字パッドを含み得る。20

#### 【0046】

MPシステム554のデュアルプロセッサは、システムメモリ508に関連付けられるような非一時的コンピュータ可読媒体に記憶され、デュアルコアプロセッサ536および538などのコンピュータに、図3A～図3Cおよび図4A～図4Cに示す動作を提供するためのプログラムを実行させるように実行可能である、ソフトウェア命令510を実行するように構成される。PX1

536およびPX2 538は、異なるレベルのキャッシュメモリおよびシステムメモリ508からアクセスされるソフトウェア命令510を実行するように構成される。30

#### 【0047】

特定の実施形態では、システムコア504は、システムインパッケージデバイス内またはシステムオンチップデバイス上で物理的に編成される。特定の実施形態では、システムオンチップデバイスとして編成されたシステムコア504は、図5に示すように、電源514、ワイヤレスアンテナ516、入力デバイス518、ディスプレイデバイス520、1つまたは複数のカメラ522、スピーカ524、マイクロフォン526に物理的に結合され、リムーバブルフラッシュデバイス546に結合され得る。40

#### 【0048】

本明細書で説明する実施形態によるポータブルデバイス500は、セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定ロケーションデータユニット、モバイルロケーションデータユニット、携帯電話、セルラーフォン、コンピュータ、ポータブルコンピュータ、タブレット、モニタ、コンピュータモニタ、テレビジョン、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、ビデオプレーヤ、デジタルビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタルビデオプレーヤ、データまたはコンピュータ命令を記憶するまたは取り出す任意の他のデバイス、またはそれらの任意の組合せなどの様々な電子デバイスに組み込まれてもよい。

#### 【0049】

10

20

30

40

50

本明細書で開示する実施形態に関して説明する様々な例示的な論理ブロック、モジュール、回路、要素、または構成要素は、汎用プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理構成要素、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書で説明する機能を実行するように設計されたそれらの任意の組合せで実装または実行され得る。汎用プロセッサはマイクロプロセッサであり得るが、代替として、プロセッサは任意の従来のプロセッサ、コントローラ、マイクロコントローラ、または状態機械であり得る。プロセッサはまた、コンピューティング構成要素の組合せ、たとえば、DSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと連携する1つもしくは複数のマイクロプロセッサ、または所望のアプリケーションに適した任意の他のそのような構成として実装され得る。

#### 【0050】

図5のデュアルコアプロセッサ536および538は、プログラムの制御下でリアルタイムタスクをサービスする命令を実行するように構成され得る。コンピュータ可読非一時的記憶媒体上に記憶されたプログラムは、命令およびデータキャッシュ549～552を介して利用可能であり得るようにプロセッサ複合体506とローカルに直接関連付けられるか、または特定の入力デバイス518もしくはワイヤレスインターフェース528を介してアクセス可能である。入力デバイス518またはワイヤレスインターフェース528は、たとえば、プロセッサローカルデータキャッシュなどのプロセッサにローカルに直接関連付けられた、またはシステムメモリ508からアクセス可能である、メモリデバイスに常駐するデータにアクセスすることもできる。本明細書で開示する様々な実施形態に関して説明する方法は、直接ハードウェアで具現化されるか、プロセッサによって実行される1つまたは複数のプログラムを有するソフトウェアモジュールで具現化されるか、またはその2つの組合せで具現化され得る。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、ダイナミックランダムアクセスメモリ(DRAM)、同期型ダイナミックランダムアクセスメモリ(SDRAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、消去可能プログラマブル読み取り専用メモリ(EPRO M)、電気消去可能プログラマブル読み取り専用メモリ(EEPROM)、ハードディスク、リムーバブルディスク、コンパクトディスク(CD)-ROM、デジタルビデオディスク(DVD)または当技術分野で知られている任意の他の形態の非一時的記憶媒体に常駐し得る。非一時的記憶媒体は、プロセッサが記憶媒体から情報を読み取り、かつ記憶媒体に情報を書き込むことができるよう、プロセッサに結合され得る。代替として、記憶媒体はプロセッサと一緒に得る。

#### 【0051】

本発明はプロセッサシステムにおいて使用するための例示的な実施形態の文脈において開示されているが、上記の説明および下記の特許請求の範囲に一致する多種多様な実装形態が当業者によって使用され得ることが認識されよう。たとえば、固定機能実装形態も、本発明の様々な実施形態を利用することができます。

#### 【符号の説明】

#### 【0052】

- 100 マルチプロセッサ(MP)システム、MPシステム、システム、デュアルコアMPシステム

- 102 デュアルコアシステム

- 104 第1の処理エージェント(PX1)、PX1

- 105 レベル1データキャッシュ-1(L1 Dcache-1)、キャッシュメモリ

- 106 L2キャッシュおよびコントローラ-1

- 108 第2の処理エージェント(PX2)、PX2

- 109 レベル1データキャッシュ-2(L1 Dcache-2)、キャッシュメモリ

- 110 L2キャッシュおよびコントローラ-2

- 114 コヒーレントバス

- 116 メインメモリ、システムメモリ

10

20

30

40

50

|     |                            |    |

|-----|----------------------------|----|

| 120 | L2キヤッシュ1、キヤッシュメモリ          |    |

| 121 | L2コントローラ-1                 |    |

| 122 | 予約グラニュール-1(RG-1)、RG-1      |    |

| 123 | スヌープ1ユニット、スヌープ1            |    |

| 126 | L2キヤッシュ2、キヤッシュメモリ          |    |

| 127 | L2コントローラ-2                 |    |

| 128 | 予約グラニュール-2(RG-2)、RG-2      |    |

| 129 | スヌープ2ユニット、スヌープ2            |    |

| 200 | セマフォ管理                     |    |

| 202 | 処理工エージェントPX1、PX1           | 10 |

| 203 | 処理工エージェントPX2、PX2           |    |

| 204 | 第1の動作                      |    |

| 205 | 第2の動作                      |    |

| 206 | 第3の動作                      |    |

| 207 | 第4の動作                      |    |

| 220 | コヒーレントバスを介したセマフォ管理         |    |

| 224 | 第1の動作                      |    |

| 225 | 第2の動作                      |    |

| 240 | コヒーレントバスを介したセマフォ管理         |    |

| 244 | 第1の動作                      | 20 |

| 245 | 第2の動作                      |    |

| 260 | コヒーレントバスを介したセマフォ管理         |    |

| 264 | 第1の動作                      |    |

| 265 | 第2の動作                      |    |

| 266 | 第3の動作                      |    |

| 267 | 第4の動作                      |    |

| 268 | 第5の動作                      |    |

| 269 | 第6の動作                      |    |

| 300 | セマフォ管理プロセス、プロセス            |    |

| 330 | 読み取り優先排他セマフォ管理プロセス、プロセス    | 30 |

| 360 | アップグレード優先排他セマフォ管理プロセス、プロセス |    |

| 400 | 第1のセマフォ管理技法、セマフォ管理技法       |    |

| 402 | PX1                        |    |

| 403 | PX2                        |    |

| 404 | 第1の動作                      |    |

| 405 | 第2の動作                      |    |

| 420 | 第2のセマフォ管理技法                |    |

| 424 | 第1の動作                      |    |

| 425 | 第2の動作                      |    |

| 426 | 第3の動作                      | 40 |

| 440 | 第3のセマフォ管理技法、セマフォ管理技法       |    |

| 444 | 第1の動作                      |    |

| 445 | 第2の動作                      |    |

| 500 | ポータブルデバイス                  |    |

| 504 | システムコア                     |    |

| 506 | プロセッサ複合体                   |    |

| 508 | システムメモリ                    |    |

| 510 | ソフトウェア命令                   |    |

| 514 | 電源                         |    |

| 516 | アンテナ                       | 50 |

- 518 入力デバイス

520 ディスプレイ

522 カメラ

524 スピーカ

526マイクロフォン

528 ワイヤレスインターフェース

530 ディスプレイコントローラ

532 カメラインターフェース

534 コーデック

536 PX1

538 PX2

540 モデムサブシステム、MSS

544 フラッシュコントローラ

546 フラッシュデバイス

548 マルチメディアサブシステム

549 ローカルレベル1命令およびデータ(L1 I&D)キャッシュ

550 ローカルレベル1命令およびデータ(L1 I&D)キャッシュ

551 レベル2キャッシュ0およびコントローラ0

552 レベル2キャッシュ1およびコントローラ1

553 コヒーレントバス

554 MPシステム

【 义 1 】

【図2A】

|      |   |                                 |                                                                   |                                                |

|------|---|---------------------------------|-------------------------------------------------------------------|------------------------------------------------|

|      |   | 処理エンジンPX1                       | 処理エンジンPX2                                                         |                                                |

| 204~ | 1 | LDEX A<br>- PX1のRGをアドレスAIにタグ付ける |                                                                   |                                                |

| 205~ | 2 |                                 | LDEX A<br>- PX2のRGをアドレスAIにタグ付ける<br>- アクションなし                      |                                                |

| 206~ | 3 |                                 | STEX A<br>- PX1のRGがタグ付けされているので実行する<br>- PX2のRGをタグ解除するために発行されるコマンド | - PX2のRGをタグ解除する                                |

| 207~ | 4 |                                 |                                                                   | STEX A<br>- RGもはやタグ付けされていないので失敗する<br>- アクションなし |

【図2B】

| 処理エージェントPX1 |                                                                           | 処理エージェントPX2                                                     |  |

|-------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|--|

| 264~<br>1   | LDEX A<br>-読み取り排他バスコマンドを生じさせる<br>-排他状態においてラインを取得する<br>-PX1のRGをアドレスAにタグ付ける | -PX2のラインのコピーを無効化する<br>-PX2はRGをアドレスAからタグ解除する                     |  |

| 265~<br>2   | LDEX A<br>-PX1のラインのコピーを無効化する<br>-PX1はRGをアドレスAからタグ解除する                     | -読み取り排他バスコマンドを生じさせる<br>-排他状態においてラインを取得する<br>-PX2のRGをアドレスAにタグ付ける |  |

| 266~<br>3   | STEX A<br>-RGもはやタグ付けされていないので失敗する                                          | -アクションなし                                                        |  |

| 処理エージェントPX1 |                                                                           | 処理エージェントPX2                                 |  |

|-------------|---------------------------------------------------------------------------|---------------------------------------------|--|

| 267~<br>4   | LDEX A<br>-読み取り排他バスコマンドを生じさせる<br>-排他状態においてラインを取得する<br>-PX1のRGをアドレスAにタグ付ける | -PX2のラインのコピーを無効化する<br>-PX2はRGをアドレスAからタグ解除する |  |

| 268~<br>5   | STEX A<br>-RGもはやタグ付けされていないので失敗する                                          | -アクションなし                                    |  |

| 269~        | …ライロックにより繰り返す                                                             | …ライロックにより繰り返す                               |  |

【図2C】

| 処理エージェントPX1 |                                                          | 処理エージェントPX2                                                          |  |

|-------------|----------------------------------------------------------|----------------------------------------------------------------------|--|

| 224~<br>1   | LDEX A<br>-共有状態においてラインを取得する<br>-PX1のRGをアドレスAIにタグ付ける      | -PX2のキャッシュはアドレスAラインを保持する<br>-PX2のRGはタグ付けされていない<br>-PX2はキャッシュ状態を変更しない |  |

| 225~<br>2   | STEX A<br>-PX1のRGがタグ付けされているので実行する<br>-PX2のアドレスAラインを無効化する | -PX2のキャッシュ内のラインAを無効化する<br>-PX2のRGがタグ付けされたために発行されるコマンド無効化するために発行される   |  |

| 処理エージェントPX1 |                                                                            | 処理エージェントPX2                                                  |  |

|-------------|----------------------------------------------------------------------------|--------------------------------------------------------------|--|

| 244~<br>1   | LDEX A<br>-読み取り排他バスコマンドを生じさせる<br>-排他状態においてラインを取得する<br>-PX1のRGをアドレスAIにタグ付ける | -PX2のRGはPX1のLDEX Aが発行される前にタグ付けされていない<br>-PX2のアドレスAラインは無効化される |  |

| 245~<br>2   | STEX A<br>-PXのRGがタグ付けされているので実行する<br>-ハスコマンドは発行されない                         | -アクションなし                                                     |  |

【図2D】

| 処理エージェントPX1 |                          | 処理エージェントPX2 |   |

|-------------|--------------------------|-------------|---|

| 202         | 要求側PX1はLDEXを発行する         | 203         |   |

| 260         | ↓                        | 220         |   |

| 202         | ↓                        | 202         | ↓ |

| 264~<br>1   | PX1のキャッシュ内にラインがあるか？      | 202         | ↓ |

| 265~<br>2   | Yes, ヒット                 | 202         | ↓ |

| 266~<br>3   | No, ミス                   | 308         | ↓ |

| 267~<br>4   | ReadPreferExclusiveを発行する | 300         | ↓ |

| 268~<br>5   | ↓                        | 304         | ↓ |

| 269~        | …ライロックにより繰り返す            | 306         | ↓ |

【図3B】

【図3C】

【 図 4 A 】

|        |      |                                                                                                                                                  |                                                                                                                                                              |                                                                                                                          |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

|        | 402  | 処理エージェントPX1                                                                                                                                      | 403                                                                                                                                                          | 処理エージェントPX2                                                                                                              |

| LDEX A | 404へ | <ul style="list-style-type: none"> <li>- Read/PreferExclusiveバスコマンドを生じさせる</li> <li>- 排他状態においてラインを取得する</li> <li>- PX1のORGをアドレスAIにタグ付ける</li> </ul> | <ul style="list-style-type: none"> <li>"PX2のキャッシュはアドレスAラインを保持する</li> <li>- PX2のORGはPX1のORGが、<br/>実行される前にタグ付けされていない</li> <li>- PX2のアドレスAラインは無効化される</li> </ul> | <ul style="list-style-type: none"> <li>- アクションなし</li> </ul>                                                              |

| STEX A | 405へ |                                                                                                                                                  |                                                                                                                                                              | <ul style="list-style-type: none"> <li>- PX1ORGがタグ付けされているので実行し、<br/>排他状態においてラインを保持する</li> <li>- バスコマンドは発行されない</li> </ul> |

【 図 4 B 】

| 402  |        | 処理エージェントPX1                                                                                                                                       | 処理エージェントPK2                                                                                                                                               |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 424～ | LDEX A | <ul style="list-style-type: none"> <li>- ReadPrefExcluiveBusCommandを生じさせる</li> <li>- 排他状態においてラインを取り得する</li> <li>- PX1のORGをアドレスAIにタグ付ける</li> </ul> | <ul style="list-style-type: none"> <li>- PX2のキャッシュはアドレスラインを保持する</li> <li>- PX2のORGはPX1のLDEX Aが発行される前にタグ付けされていない</li> <li>- PX2のアドレスAラインは無効化される</li> </ul> |

| 425～ | LDEX A | <ul style="list-style-type: none"> <li>- PX1のラインのコピーを共有状態に変更する</li> <li>- PX1のORGはアドレスAIにタグ付けされたままである</li> </ul>                                  | <ul style="list-style-type: none"> <li>- ReadPrefExcluiveBusCommandを生じさせる</li> <li>- 共有状態においてラインを取得する</li> <li>- PX2のORGをアドレスAIにタグ付けする</li> </ul>         |

| 426～ | STEX A | <ul style="list-style-type: none"> <li>- PX1のORGがタグ付けされているのでバスする</li> <li>- PX2のアドレスAラインを無効化するために発行されるコマンド</li> </ul>                             | <ul style="list-style-type: none"> <li>- PX2のキャッシュ内のラインAを無効化する</li> <li>- PX2のORGをタグ解除する</li> </ul>                                                       |

【図4C】

|       | 402                                                                                                                  | 403                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

|       | 処理エンジンPX1                                                                                                            | 処理エンジンPX2                                                                                     |

| 444~1 | LDEX Aはその2キャッシュ内でヒットする<br>- UpgradePreferringExclusive<br>バスコマンドを生じさせる<br>- 排他状態においてラインを取得する<br>- PXのRQをアドレスAIにタグ付ける | - PX2のキャッシュはアドレスAラインを保持する<br>- PX2のRIGHTDEX Aが、<br>発行される前にタグ付けされていない<br>- PX2のアドレスAラインは無効化される |

| 445~2 | STEX A<br>- PXのRQがタグ付けされているので実行し、<br>排他状態においてラインを保持する                                                                | - アクションなし                                                                                     |

【図5】

---

フロントページの続き

(72)発明者 エリック・エフ・ロビンソン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 ジャヤ・プラカシュ・スプラマニアム・ガナサン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 トーマス・アンドリュー・サルトリウス

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 ジェームズ・ノリス・ディーフェンダーファー

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 滝谷 亮一

(56)参考文献 特開2004-185610(JP,A)

特開平11-328023(JP,A)

特開2000-250881(JP,A)

特開2000-250882(JP,A)

国際公開第02/15021(WO,A1)

(58)調査した分野(Int.Cl., DB名)

G06F 12/08