등록특허 10-2271159

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년07월01일

(11) 등록번호 10-2271159

(24) 등록일자 2021년06월24일

- (51) 국제특허분류 (Int. Cl.)

*H01L 33/12* (2010.01) *H01L 33/20* (2010.01)

*H01L 33/22* (2010.01) *F21Y 101/00* (2016.01)

- (52) CPC특허분류

*H01L 33/12* (2013.01)

*H01L 33/20* (2013.01)

- (21) 출원번호 10-2018-7013813

- (22) 출원일자(국제) 2016년10월14일

심사청구일자 2019년10월02일

- (85) 번역문제출일자 2018년05월15일

- (65) 공개번호 10-2018-0061373

- (43) 공개일자 2018년06월07일

- (86) 국제출원번호 PCT/KR2016/011576

- (87) 국제공개번호 WO 2017/065566

국제공개일자 2017년04월20일

- (30) 우선권주장

1020150144060 2015년10월15일 대한민국(KR)

- (56) 선행기술조사문헌

JP2013539922 A\*

US09153741 B1\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 5 항

심사관 : 김동우

(54) 발명의 명칭 반도체 소자, 반도체 소자 패키지, 및 이를 포함하는 조명 시스템

**(57) 요 약**

실시예에 따른 반도체 소자는 기판과, 상기 기판 상에 배치되는 버퍼층과, 상기 버퍼층 상에 배치되며 제1 도전형 반도체층, 제2 도전형 반도체층 및 상기 제1 도전형 반도체층과 상기 제2 도전형 반도체층 사이에 배치되어 자외선 광을 방출하는 활성층을 발광 구조물과, 상기 버퍼층 내에 배치되는 복수의 에어 보이드를 포함하고, 상기 에어 보이드는 2개 이상의 경사면을 가지도록 형성될 수 있다.

(52) CPC특허분류

*H01L 33/22* (2013.01)

*F21Y 2101/00* (2013.01)

*H01L 2924/12041* (2013.01)

(72) 발명자

**최낙준**

서울특별시 중구 한강대로 416번지 서울스퀘어

**김병조**

서울특별시 중구 한강대로 416번지 서울스퀘어

## 명세서

### 청구범위

#### 청구항 1

요철을 갖는 상면을 포함하는 기판;

상기 기판의 상면 상에 배치되며 제1 도전형 반도체층, 제2 도전형 반도체층 및 상기 제1 도전형 반도체층과 상기 제2 도전형 반도체층 사이에 배치되는 활성층을 포함하는 발광 구조물;

상기 제1 도전형 반도체층은 상기 기판의 상면과 상기 활성층 사이에 배치되는 베퍼층;

상기 제1 도전형 반도체층 상에 배치되며 상기 제1 도전형 반도체층과 전기적으로 연결되는 제1 전극; 및

상기 제2 도전형 반도체층 상에 배치되며 상기 제2 도전형 반도체층과 전기적으로 연결되는 제2 전극을 포함하고,

상기 베퍼층은 상기 기판 상면의 일부와 수직으로 중첩되는 복수의 에어캡을 포함하고,

상기 복수의 에어캡 각각은 상기 활성층에 가장 가까운 지점에서 상기 기판의 상면을 향하여 연장되는 복수의 경사면을 더 포함하고,

상기 복수의 경사면의 최상부는 상기 제1 도전형 반도체층과 인접하게 배치되고,

상기 에어캡의 복수의 경사면에 대응되는 상기 베퍼층의 경사면은 격자 방향이 서로 다른 2 개 이상의 격자 방향을 포함하고,

상기 에어캡의 폭은 상기 요철의 일부의 폭의 절반 이하이고,

상기 에어캡은 상기 기판의 요철과 이격되며, 상기 에어캡의 최하단은 상기 요철의 최상부보다 상기 제1 도전형 반도체층과 인접한 상부에 배치되는 발광 소자.

#### 청구항 2

제1항에 있어서,

상기 기판과 상기 에어캡 사이의 이격 거리는 200nm 내지 300nm를 포함하는 발광 소자.

#### 청구항 3

제1항에 있어서,

상기 요철의 높이는 1.2μm이고, 상기 요철의 요의 폭은 0.5μm이고, 상기 요철의 철의 폭은 1.2μm이며, 상기 에어캡의 높이는 3μm인 발광 소자.

#### 청구항 4

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 기판에 대향하여 배치된 서브 마운트;

상기 발광 구조물과 상기 서브 마운트 사이에 배치된 적어도 하나의 범프;

상기 적어도 하나의 범프와 상기 발광 구조물 사이에 배치된 적어도 하나의 콘택층; 및

상기 적어도 하나의 콘택층과 상기 적어도 하나의 범프 사이에 배치된 적어도 하나의 스프레드층;을 더 포함하는 발광 소자.

#### 청구항 5

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 에어캡은 서로 다른 높이와 폭을 가지는 크기로 형성되며, 상기 에어 캡은 동일한 선상에서의 단면적 전체

면적의 ±30% 범위 내의 크기인 발광 소자.

청구항 6

삭제

청구항 7

삭제

청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

### 발명의 설명

#### 기술 분야

[0001] 실시예는 반도체 소자, 반도체 소자 패키지, 및 이를 포함하는 조명시스템에 관한 것이다.

#### 배경 기술

[0002] 반도체 소자, 예컨대 발광소자(light emitting diode)는 전기에너지가 빛에너지로 변환되는 특성의 p-n 접합 다이오드로서, 주기율표상에서 III족과 V족 등의 화합물 반도체로 생성될 수 있고, 화합물 반도체의 조성비를 조

절함으로써 다양한 색상구현이 가능하다.

[0003] 발광소자는 순방향전압 인가 시 n층의 전자와 p층의 정공이 결합하여 전도대(conduction band)와 가전대(valance band)의 에너지 갭에 해당하는 만큼의 에너지를 발산하고, 상기 에너지가 빛으로 발산되면 발광소자가 된다.

[0004] 질화물 반도체는 높은 열적 안정성과 폭넓은 밴드갭 에너지에 의해 광소자 및 고출력 전자소자 개발 분야에서 큰 관심을 받고 있다. 특히, 질화물 반도체를 이용한 청색(blue) 발광소자, 녹색(green) 발광소자, 및 자외선(UV) 발광소자는 상용화되어 널리 사용되고 있다.

[0005] 자외선 발광소자(UV LED)는 200nm~400nm 파장대의 빛을 발광하는 발광소자이다. 자외선 발광소자는 용도에 따라 단파장 및 장파장으로 구성된다. 단파장은 살균 또는 정화등에 사용되고, 장파장은 노광기 또는 경화기 등에 사용될 수 있다.

[0006] 한편, 자외선 발광소자는 베퍼층과 사파이어 기판 사이의 계면에서 전반사로 인해 광추출 효율이 저하되는 문제가 있고, 광추출 효율을 개선하기 위해 에어 보이드를 형성하려는 시도가 있으나, 에어 보이드의 제어가 어려운 문제가 있다.

### 발명의 내용

#### 해결하려는 과제

[0007] 실시예는 요철의 상부에 균일한 형상과 크기의 보이드를 배치하는 반도체 소자, 반도체 소자 패키지 및 조명시스템을 제공하고자 한다.

#### 과제의 해결 수단

[0008] 실시예에 따른 자외선 반도체 소자는 기판과, 상기 기판 상에 배치되는 베퍼층과, 상기 베퍼층 상에 배치되며 제1 도전형 반도체층, 제2 도전형 반도체층 및 상기 제1 도전형 반도체층과 상기 제2 도전형 반도체층 사이에 배치되어 자외선 광을 방출하는 활성층을 발광 구조물과, 상기 베퍼층 내에 배치되는 복수의 에어 보이드를 포함하고, 상기 에어 보이드는 2개 이상의 경사면을 가지도록 형성될 수 있다.

[0009] 또한, 실시예에 따른 반도체 소자는 기판과, 상기 기판의 일측에 배치된 베퍼층과, 상기 베퍼층 내에 배치되며, 2개 이상의 경사면을 가지는 보이드와, 상기 베퍼층의 일측에 배치되며, 제1 도전형 반도체층, 활성층 및 제2 도전형 반도체층을 포함하는 발광 구조물과, 상기 기판에 대향하여 배치된 서브 마운트와, 상기 발광 구조물과 상기 서브 마운트 사이에 배치된 적어도 하나의 범프와, 상기 적어도 하나의 범프와 상기 발광 구조물 사이에 배치된 적어도 하나의 콘택층과, 상기 적어도 하나의 콘택층과 상기 적어도 하나의 범프 사이에 배치된 적어도 하나의 스프레드층과, 상기 발광 구조물과 상기 스프레드층 사이에 상기 적어도 하나의 콘택층을 전기적으로 이격된 복수 개로 분리하도록 배치된 적어도 하나의 콘택 분리층을 포함할 수 있다.

#### 발명의 효과

[0010] 실시예는 요철의 상부에 보이드를 배치하여 관통 전위를 차단하여 발광 소자의 에피 성장의 질을 향상시킬 수 있다.

[0011] 실시예는 요철의 상부에 균일한 형상과 크기의 다수개의 보이드를 배치하여 광산란을 유도하여 광추출 효율을 향상시킬 수 있다.

[0012] 실시예는 요철의 상부에 소정의 기울기를 가진 경사면을 가진 보이드를 배치하여 지향각을 개선할 수 있다.

[0013] 실시예는 보이드의 높이를 조절함으로써, 플립 칩 본딩 구조의 발광 소자의 광 효율을 향상시킬 수 있다.

#### 도면의 간단한 설명

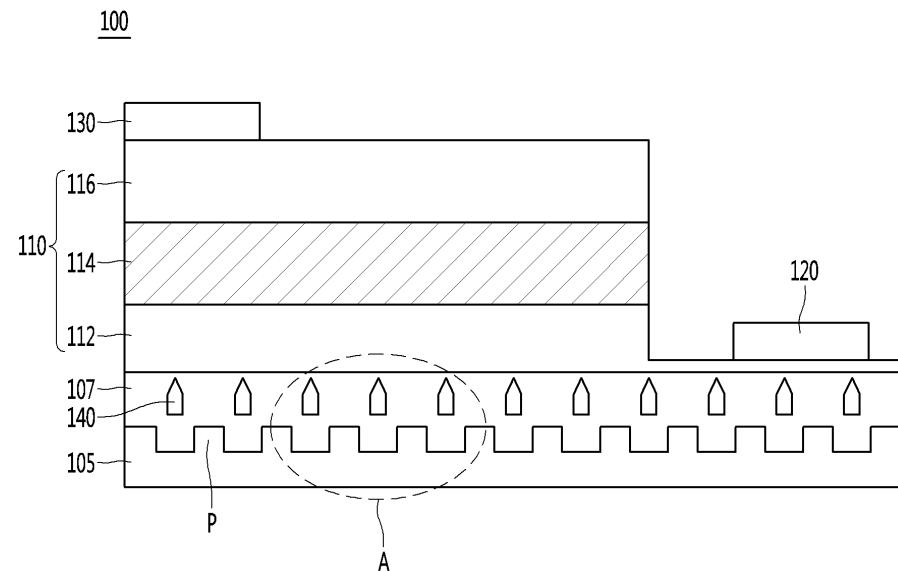

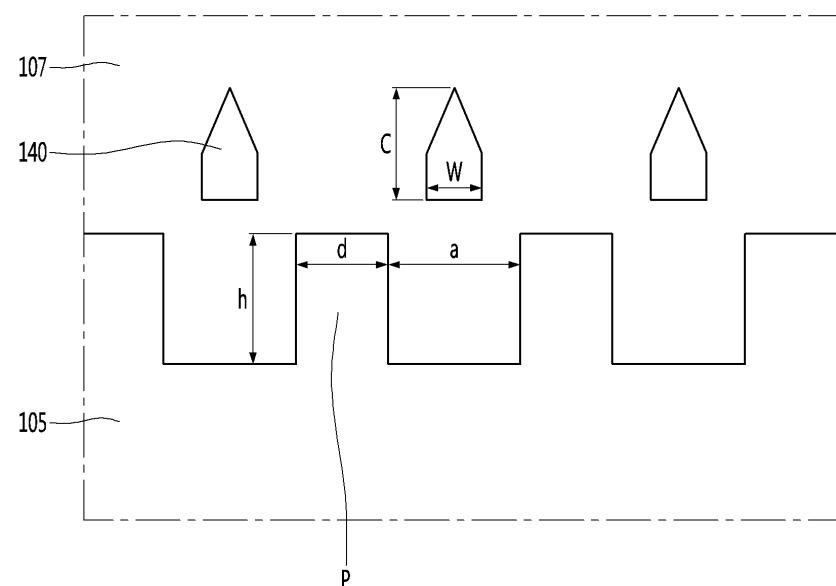

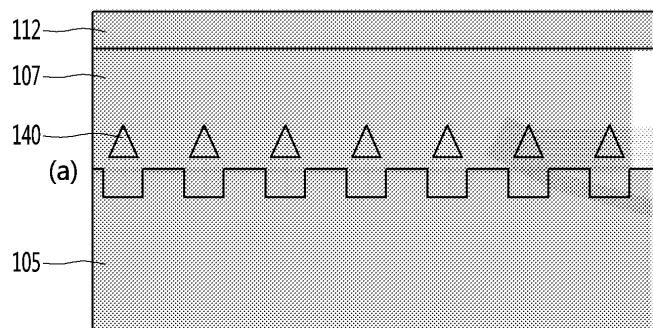

[0014] 도 1은 제1 실시예에 따른 반도체 소자의 단면도이다.

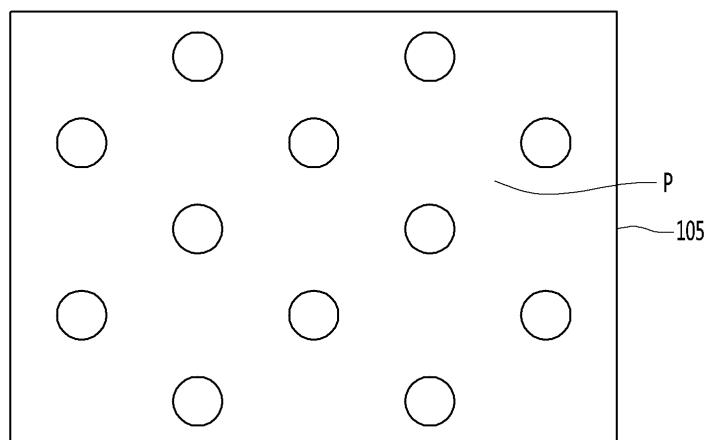

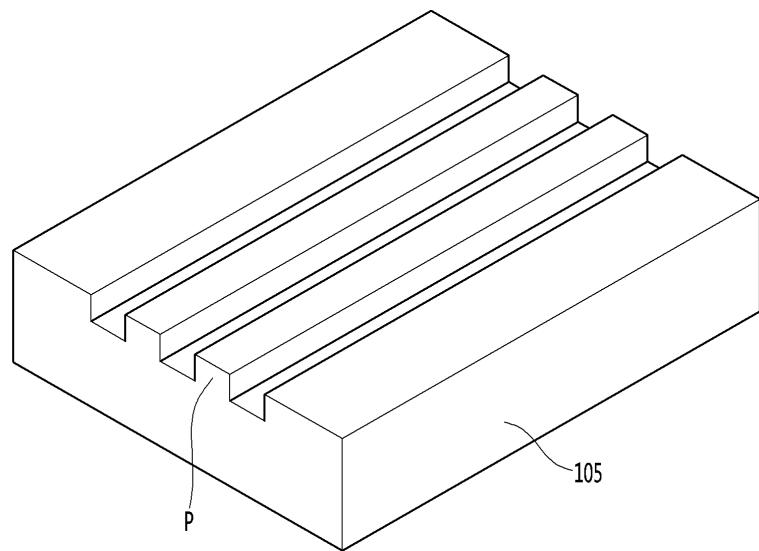

도 2 및 도 3은 제1 실시예에 따른 기판의 다양한 형상을 나타낸 평면도 및 사시도이다.

도 4는 제1 실시예에 따른 반도체 소자의 부분 확대도이다.

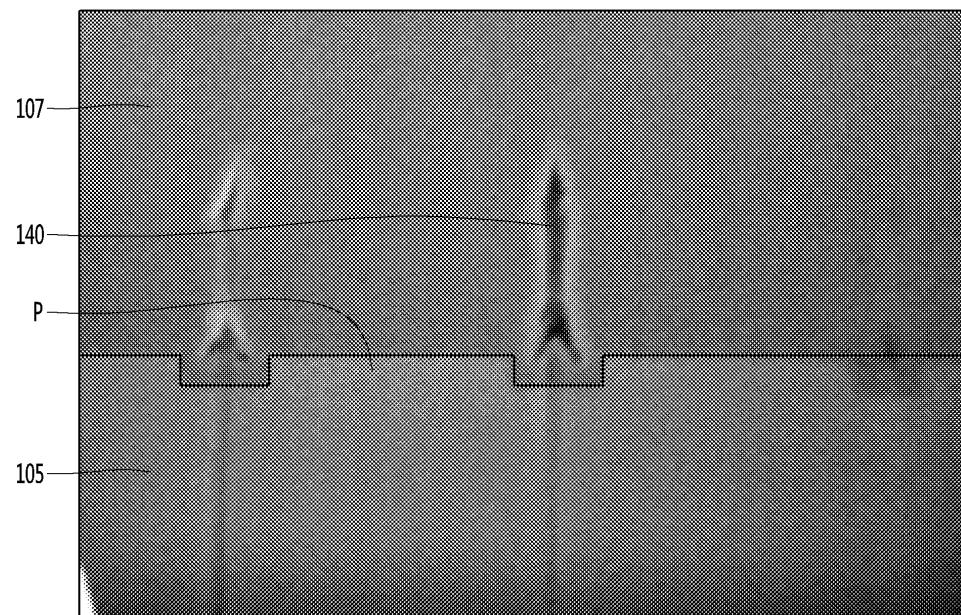

도 5는 제1 실시예에 따른 반도체 소자의 SEM 단면도이다.

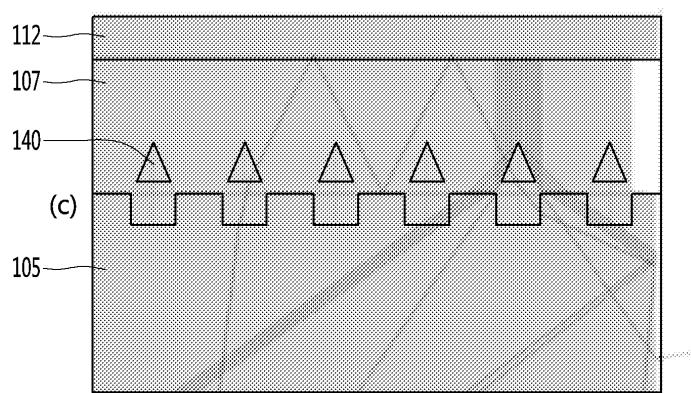

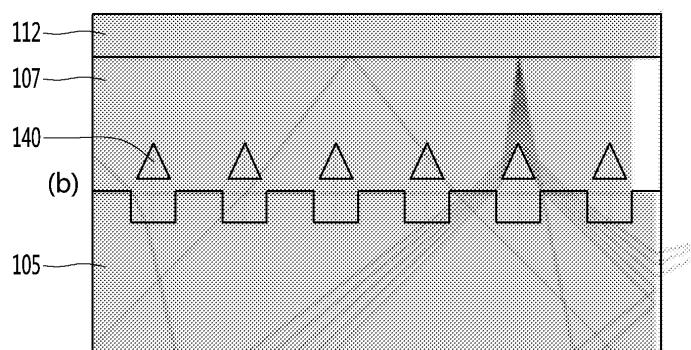

도 6과 도 7은 다른 실시예에 따른 반도체 소자의 부분확대도이다.

도 8은 제1 실시예에 따른 반도체 소자의 지향각을 나타내는 도면이다.

도 9는 제2 실시예에 따른 반도체 소자의 단면도이다.

도 10은 도 7에 도시된 반도체 소자의 평면도이다.

도 11은 제2 실시예에 따른 반도체 소자의 부분 확대도이다.

도 12는 제2 실시예에 따른 반도체 소자의 SEM 단면도이다.

도 13은 제2 실시예에 따른 반도체 소자 패키지의 단면도이다.

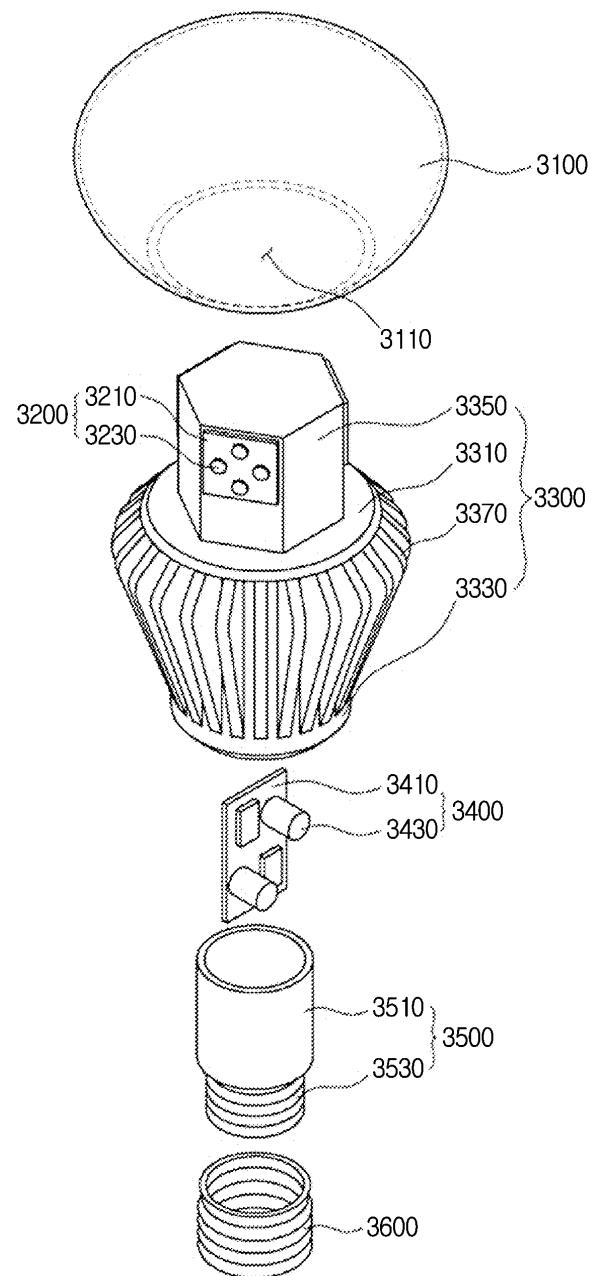

도 14 및 도 15는 실시예에 따른 반도체 소자를 포함하는 조명 시스템의 실시예들을 나타낸 분해 사시도이다.

### 발명을 실시하기 위한 구체적인 내용

[0015]

실시 예의 설명에 있어서, 각 층(막), 영역, 패턴 또는 구조물들이 기판, 각 층(막), 영역, 패드 또는 패턴들의 "상/위(on/over)"에 또는 "아래(under)"에 형성되는 것으로 기재되는 경우에 있어, "상/위(on/over)"와 "아래(under)"는 "직접(directly)" 또는 "다른 층을 개재하여 (indirectly)" 형성되는 것을 모두 포함한다. 또한 각 층의 상/위 또는 아래에 대한 기준은 도면을 기준으로 설명한다.

[0016]

도면에서 각층의 두께나 크기는 설명의 편의 및 명확성을 위하여 과장되거나 생략되거나 또는 개략적으로 도시되었다. 또한 각 구성요소의 크기는 실제크기를 전적으로 반영하는 것은 아니다.

[0017]

이하에서 설명하는 실시예들의 구성 요소들은 서로 조합이 가능할 수 있다. 제1 실시예에 따른 반도체 소자의 구성은 제2 실시예에 따른 반도체 소자의 구성에 채용될 수 있다. 반대로, 제2 실시예에 따른 반도체 소자의 구성은 제1 실시예에 따른 반도체 소자의 구성에 채용될 수 있다.

[0018]

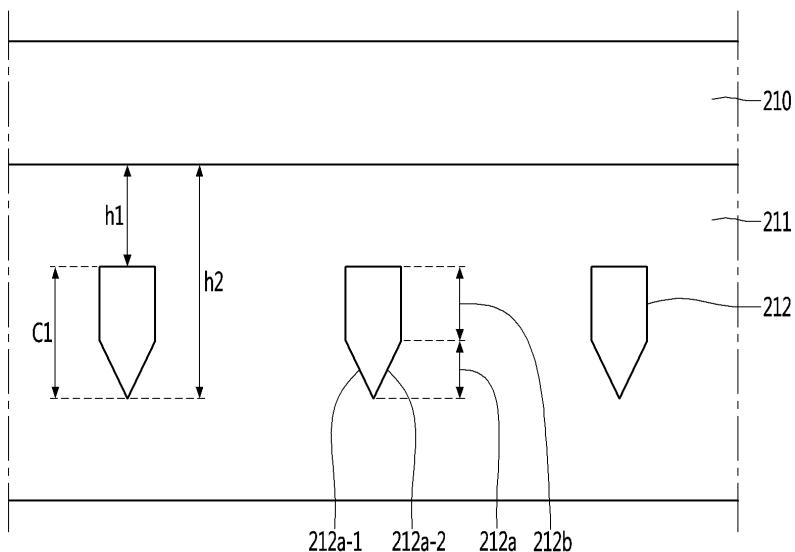

도 1은 실시예에 따른 반도체 소자의 단면도이고, 도 2 및 도 3은 제1 실시예에 따른 기판의 다양한 형상을 나타낸 평면도 및 사시도이다. 이하에서는 반도체 소자로서 자외선 발광소자를 사용한 경우를 실시예로 설명하기로 한다. 따라서, 이하 실시예에서는 반도체 소자는 편의상 자외선 발광소자로 지칭하기로 한다.

[0019]

도 1을 참조하면, 실시예에 따른 자외선 발광소자(100)는 요철(P)을 포함하는 기판(105), 기판(105) 상에 보이드(140)를 포함하는 벼페층(107), 벼페층(107) 상에 제1 도전형 반도체층(112), 제1 도전형 반도체층(112) 상에 활성층(114), 활성층(114) 상에 제2 도전형 반도체층(116), 제1 도전형 반도체층(140) 상에 제1 전극(120)과 제2 도전형 반도체층(116) 상에 제2 전극(130)을 포함할 수 있다.

[0020]

보이드(140)는 공기(air)를 포함할 수 있고, 기판(105) 상에 배치되는 요철(P)의 상부에 보이드(140)가 배치될 수 있다. 보이드(140)는 상기 요철(P)의 요의 상부에 배치될 수 있다. 보이드(140)의 폭은 상기 요철(P)의 요의 폭의 절반 이하일 수 있으나 이에 대해 한정하는 것은 아니다. 즉, 보이드(140)의 폭은 상기 요의 폭에 대응될 수 있다.

[0021]

보이드(140)의 단면은 삼각형, 오각형, 또는 육각형 중 적어도 하나인 다각형의 형상일 수 있으나 이에 대해 한정하는 것은 아니다. 보이드(140)는 소정의 기울기를 가진 경사면을 포함할 수 있고, 상기 경사면의 최상부는 제1 도전형 반도체층(112)과 인접하여 배치될 수 있다.

[0022]

즉, 실시예는 요철의 상부에 균일한 형상과 크기의 보이드를 배치하고, 상기 보이드는 소정의 기울기를 가진 경사면을 포함하여, 관통 전위를 차단하여 발광 소자의 에피 성장의 질을 향상시킬 수 있고, 광산란을 유도하여 광추출 효율을 향상시킬 수 있으며, 지향각을 개선할 수 있다.

[0023]

기판(105)은 열전도성이 뛰어난 물질로 형성될 수 있으며, 전도성 기판 또는 절연성 기판일 수 있다. 예컨대, 기판(105)은 사파이어( $Al_2O_3$ ), SiC, Si, GaAs, GaN, ZnO, GaP, InP, Ge, and  $Ga_2O_3$  중 적어도 하나를 사용할 수 있다. 기판(105) 위에는 요철 구조가 형성될 수 있고, 상기 요철 구조의 단면은 원형, 타원형 또는 다각형일 수 있으며, 이에 대해 한정하지는 않는다.

[0024]

기판(105)은 상기 요철 중 요의 폭은  $0.5\mu m$ 이고, 철의 폭은  $1.2\mu m$ 일 수 있고, 상기 요철의 높이는  $1.2\mu m$ 이고, 상기 보이드의 높이는  $3\mu m$ 일 수 있으나 이에 대해 한정하는 것은 아니다.

- [0025] 도 2에 도시된 바와 같이, 기판은 다수의 원형의 요를 형성하여 요철(P)을 형성할 수 있다. 이와 다르게, 도 3에 도시된 바와 같이, 기판은 일방향으로 연장된 스프라이프 패턴으로 요철(P)을 형성할 수 있다.

- [0026] 이때, 기판(105) 위에는 베퍼층(107)이 형성될 수 있다. 베퍼층(107)은 기판(105)과 제1 도전형 반도체층(112) 사이에 배치될 수 있다. 베퍼층(107)은 이후 형성되는 발광구조물의 재료와 기판(105)의 격자 부정합을 완화시켜 줄 수 있으며, 베퍼층의 재료는 3족-5족 화합물 반도체 예컨대, GaN, InN, AlN, InGaN, AlGaN, InAlGaN, AlInN 중 적어도 하나로 형성될 수 있다. 즉, 기판(105)의 상기 요철과 베퍼층(107)은 직접 접촉되어 배치될 수 있다.

- [0027] 제1 도전형 반도체층(112)은 베퍼층(107) 상에 배치될 수 있다. 제1 도전형 반도체층(112)은 베퍼층(107)과 활성층(114) 사이에 배치될 수 있다. 제1 도전형 반도체층(112)은 제1 도전형 도편트가 도핑된 III족-V족 화합물 반도체로 구현되며, 제1 도전형 반도체층(112)은  $In_xAl_yGa_{1-x-y}N$  ( $0 \leq x \leq 1$ ,  $0 \leq y \leq 1$ ,  $0 \leq x+y \leq 1$ )의 조성식을 포함한다. 제1 도전형 반도체층(112)은 예컨대, GaN, InN, AlN, InGaN, AlGaN, InAlGaN, AlInN, AlGaAs, GaP, GaAs, GaAsP, AlGaInP와 같은 화합물 반도체 중 적어도 하나를 포함하는 층들의 적층 구조를 포함할 수 있다. 제1 도전형 반도체층(112)은 n형 반도체층이며, 상기 제1 도전형 도편트는 n형 도편트로서, Si, Ge, Sn, Se, Te를 포함한다. 제1 도전형 반도체층(112) 상에는 전극이 더 배치될 수 있다.

- [0028] 활성층(114)은 제1 도전형 반도체층(112) 상에 배치될 수 있다. 활성층(114)은 제1 도전형 반도체층(112)과 제2 도전형 반도체층(116) 사이에 배치될 수 있다. 활성층(114)은 제1 도전형 반도체층(112)을 통해서 주입되는 전자(또는 정공)와 제2 도전형 반도체층(116)을 통해서 주입되는 정공(또는 전자)이 서로 만나서, 활성층(114)의 형성 물질에 따른 에너지 밴드(Energy Band)의 밴드갭(Band Gap) 차이에 의해서 빛을 방출하는 층이다. 활성층(114)은 단일 우물 구조, 다중 우물 구조, 양자점 구조 또는 양자선 구조 중 어느 하나로 형성될 수 있으나, 이에 한정되는 것은 아니다.

- [0029] 제2 도전형 반도체층(116)은 활성층(114)과 제2 전극(130) 사이에 배치될 수 있다. 제2 도전형 반도체층(116)은 제2 도전형 도편트가 도핑된 반도체 예컨대,  $In_xAl_yGa_{1-x-y}N$  ( $0 \leq x \leq 1$ ,  $0 \leq y \leq 1$ ,  $0 \leq x+y \leq 1$ )의 조성식을 포함한다. 제2 도전형 반도체층(116)은, GaN, InN, AlN, InGaN, AlGaN, InAlGaN, AlInN, AlGaAs, GaP, GaAs, GaAsP, AlGaInP와 같은 화합물 반도체 중 어느 하나로 이루어질 수 있다. 제2 도전형 반도체층(116)이 p형 반도체층이고, 상기 제2 도전형 도편트는 p형 도편트로서, Mg, Zn, Ca, Sr, Ba을 포함할 수 있다.

- [0030] 제2 도전형 반도체층(116)은 초격자 구조를 포함할 수 있으며, 상기 초격자 구조는 InGaN/GaN 초격자 구조 또는 AlGaN/GaN 초격자 구조를 포함할 수 있다. 제2 도전형 반도체층(116)의 초격자 구조는 비 정상적으로 전압에 포함된 전류를 확산시켜 주어, 활성층을 보호할 수 있다.

- [0031] 제1 전극(120)은 제1 도전형 반도체층(112) 상에 배치될 수 있다. 제1 전극(120)은 Cr, V, W, Ti, Zn, Ni, Cu, Al, Au, Mo, Ti/Au/Ti/Pt/Au, Ni/Au/Ti/Pt/Au, Cr/Al/Ni/Cu/Ni/Au 등에서 선택된 적어도 어느 하나를 포함할 수 있다.

- [0032] 제2 전극(130)은 제2 도전형 반도체층(116) 상에 배치될 수 있고, 외부 전원에 연결되어 발광구조물(110)에 전원을 제공할 수 있다. 제2 전극(130)은 Cr, V, W, Ti, Zn, Ni, Cu, Al, Au, Mo, Ti/Au/Ti/Pt/Au, Ni/Au/Ti/Pt/Au, Cr/Al/Ni/Cu/Ni/Au 등에서 선택된 적어도 어느 하나를 포함할 수 있다.

- [0033] 자외선 발광소자(100)는 315nm 내지 400nm 범위의 파장을 가진 UV-A, 280nm 내지 315nm 범위의 파장을 가진 UV-B, 100nm 내지 280nm 범위의 파장을 가진 UV-C로 나눌 수 있으며, 본 발명의 실시예에 따른 자외선 발광소자(100)는 상기 UV-C의 100nm 내지 280nm 범위 내의 파장을 방출할 수 있으나 이에 대해 한정하는 것은 아니다.

- [0034] 도 4는 실시예에 따른 반도체 소자의 부분 확대도이다.

- [0035] 도 1과 도 4를 참조하면, 보이드(140)는 베퍼층(107) 내에 배치되고, 기판(105)의 상부에 배치되는 요철 중 요의 상부에 배치될 수 있다.

- [0036] 보이드(140)의 폭(W)은 상기 요의 폭(a)의 절반 이하일 수 있으나, 이에 대해 한정하는 것은 아니다. 보이드(140)의 폭(W)은 0.25μm 이하이고, 보이드(140)의 높이는 3μm일 수 있고, 상기 요의 폭(a)은 0.5μm 일 수 있으며, 상기 철의 폭(d)은 1.2μm 일 수 있고, 상기 요철의 높이는 1.2μm일 수 있으나 이에 대해 한정하는 것은 아니다. 즉, 상기 철의 폭(d)은 상기 요의 폭(a)보다 2배 이상일 수 있다.

- [0037] 즉, 실시예는 요철의 상부에 균일한 형상과 크기의 보이드를 배치하고, 상기 보이드는 소정의 기울기를 가진 경

사면을 포함하여, 관통 전위를 차단하여 발광 소자의 에피 성장의 질을 향상시킬 수 있고, 광산란을 유도하여 광추출 효율을 향상시킬 수 있으며, 지향각을 개선할 수 있다.

[0038] 보이드(140)는 2개 이상의 경사면(facet)을 가지도록 형성될 수 있다. 도면에서는 2개의 경사면이 형성된 구조가 개시되어 있으나, 사각 뿐 형상인 경우 4개의 경사면을 가질 수 있다. 따라서, 다면체의 구조에 따라 3개 이상의 경사면이 형성될 수 있다.

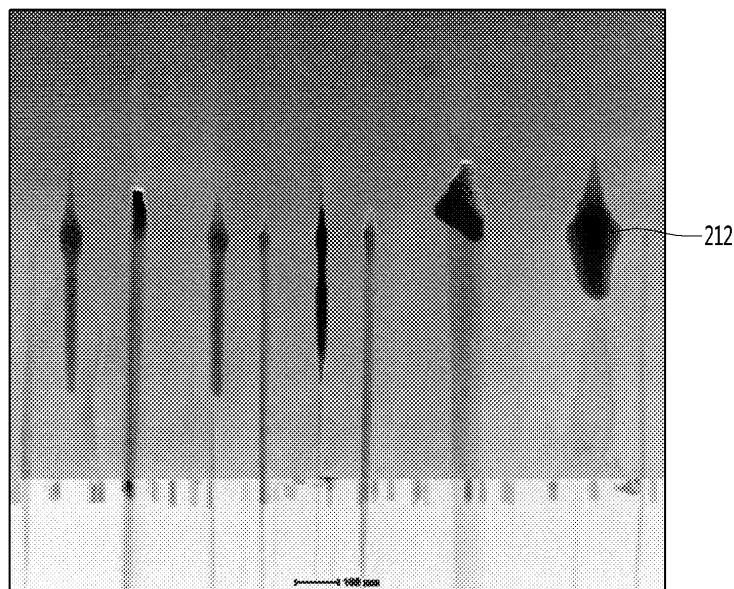

[0039] 도 5는 제1 실시예에 따른 반도체 소자의 SEM 단면도이다.

[0040] 도 5를 참조하면, 보이드(140)는 베퍼층(107) 내에 배치되고, 기판(105)의 상부에 배치되는 요철 중 요의 상부에 배치될 수 있다. 실시예에서, 보이드(140)는 공기(air)를 포함할 수 있고, 보이드(140)의 단면은 삼각형, 오각형, 또는 육각형 중 적어도 하나인 다각형의 형상일 수 있으나 이에 대해 한정하는 것은 아니다.

[0041] 보이드(140)는 소정의 기울기를 가진 경사면을 포함할 수 있고, 상기 경사면의 최상부는 제1 도전형 반도체층(112)과 인접하여 배치될 수 있다.

[0042] 보이드(140)는 성장 조건에 따라 형상 및 크기가 달라질 수 있으며, 기판(105)의 요철 중 요의 상부에 균일한 형상과 크기가 배치되는 특징을 가진다.

[0043] 즉, 실시예는 요철의 상부에 균일한 형상과 크기의 보이드를 배치하고, 상기 보이드는 소정의 기울기를 가진 경사면을 포함하여, 관통 전위를 차단하여 발광 소자의 에피 성장의 질을 향상시킬 수 있고, 광산란을 유도하여 광추출 효율을 향상시킬 수 있으며, 지향각을 개선할 수 있다.

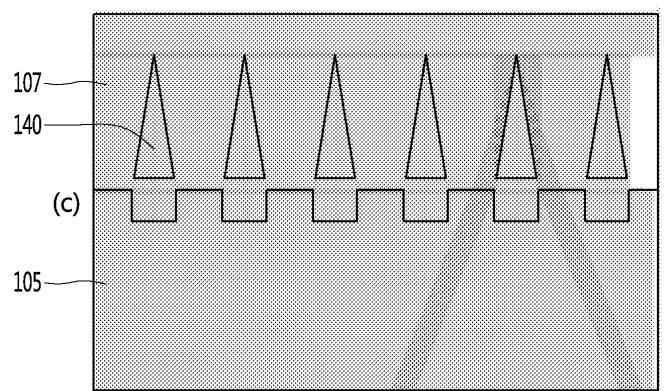

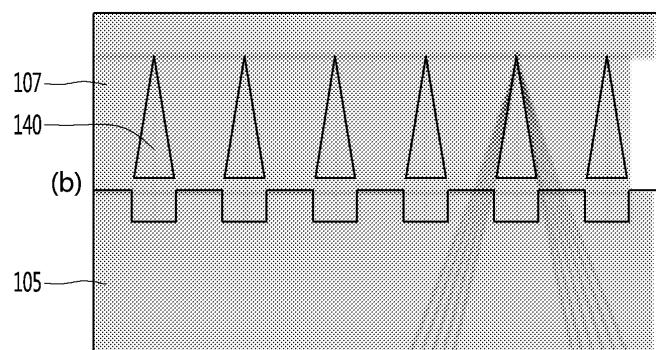

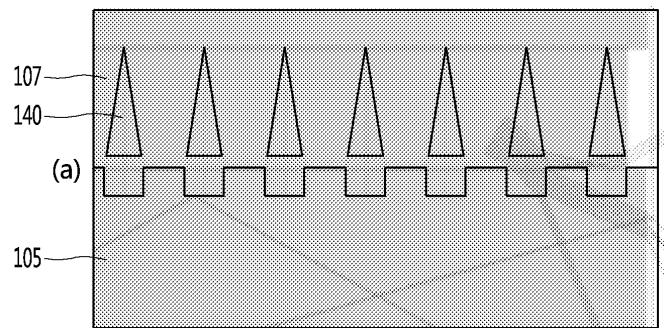

[0044] 도 6과 도 7은 다른 실시예에 따른 반도체 소자의 부분 확대도이다.

[0045] 도 6과 도 7을 참조하면, 도 6은 보이드(140)의 높이가 1.2 $\mu$ m 일 때의 광 추출 패턴을 나타내고, 도 7은 보이드(140)의 높이가 3 $\mu$ m 일 때의 광 추출 패턴을 나타내는 도면이다.

[0046] 도 6(a)와 도 7(a)는 활성층으로부터 광이 보이드(140)에 수평으로 입사하는 경우이고, 보이드(140)의 높이가 3 $\mu$ m인 도 5의 실시예가 보이드(140)의 높이가 1.2 $\mu$ m인 도 4의 실시예보다 광의 산란이 개선되는 것을 알 수 있다.

[0047] 도 6(b)와 도 7(b)는 활성층으로부터 광이 보이드(140)에 비스듬하게 입사하는 경우이고, 보이드(140)의 높이가 3 $\mu$ m인 도 5의 실시예가 보이드(140)의 높이가 1.2 $\mu$ m인 도 4의 실시예보다 광이 수직 방향으로 집중되어 방출되는 것을 알 수 있다.

[0048] 도 6(c)와 도 7(c)는 활성층으로부터 광이 보이드(140)에 수직으로 입사하는 경우이고, 보이드(140)의 높이가 3 $\mu$ m인 도 5의 실시예가 보이드(140)의 높이가 1.2 $\mu$ m인 도 4의 실시예보다 광이 수직 방향으로 집중되어 방출되는 것을 알 수 있다.

[0049] 즉, 보이드(140)의 높이가 클수록 광이 수직 방향으로 집중되어 방출될 수 있고, 보이드(140)의 높이를 조절하여 수직 방향으로 광의 집중도를 조절할 수 있으며, 이는 종래기술의 자외선 발광소자에서 수직방향으로 광을 집중하지 못하는 문제를 개선할 수 있다.

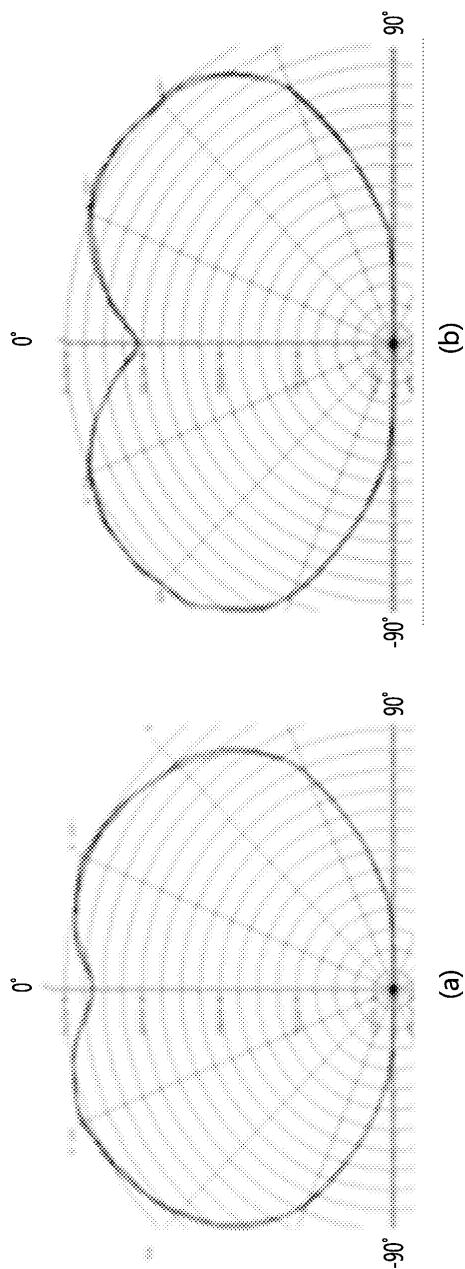

[0050] 도 8은 실시예에 따른 반도체 소자의 지향각을 나타내는 도면이다.

[0051] 도 8을 참조하면, 도 8(a)는 실시예에 따른 자외선 발광소자의 지향각을 나타내는 도면이고, 도 8(b)는 요철과 보이드를 포함하지 않는 자외선 발광소자의 지향각을 나타내는 도면이다.

[0052] 도 8(a)의 실시예에 따른 발광소자는 도 8(b)의 요철과 보이드를 포함하지 않는 자외선 발광소자보다 각도 0도 방향, 즉 수직방향으로 광을 집중시킬 수 있어 광추출 효율이 향상될 수 있다. 예컨대, 도 8(a)의 실시예에 따른 발광소자의 집중도는 89.3%이고, 도 8(b)의 자외선 발광소자의 집중도는 68.4%로 20.9%가 개선됨을 알 수 있다.

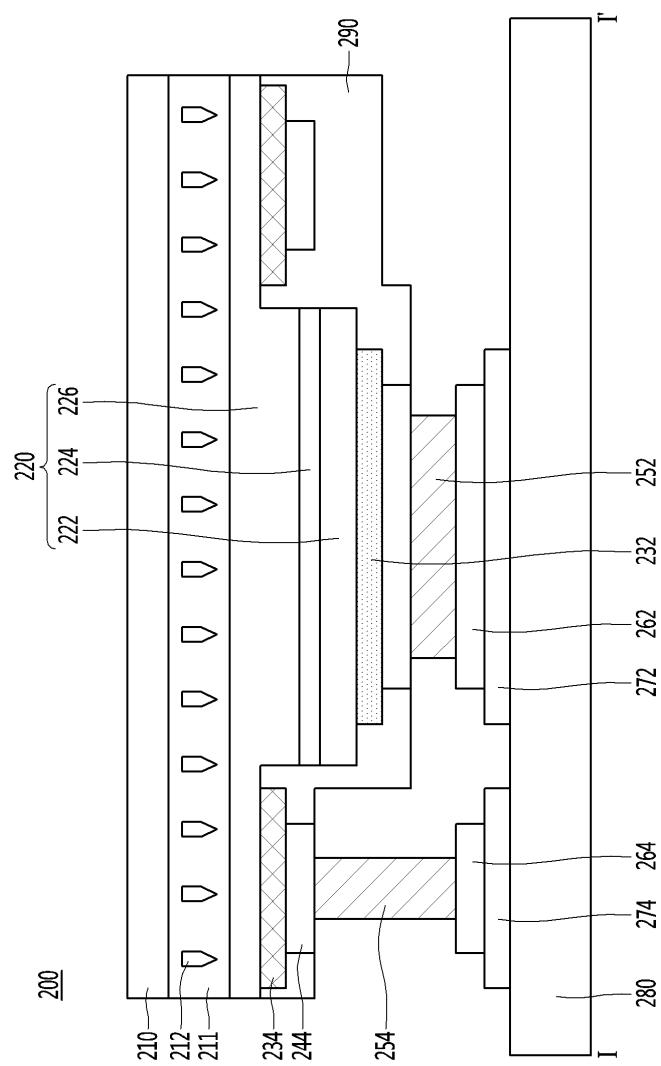

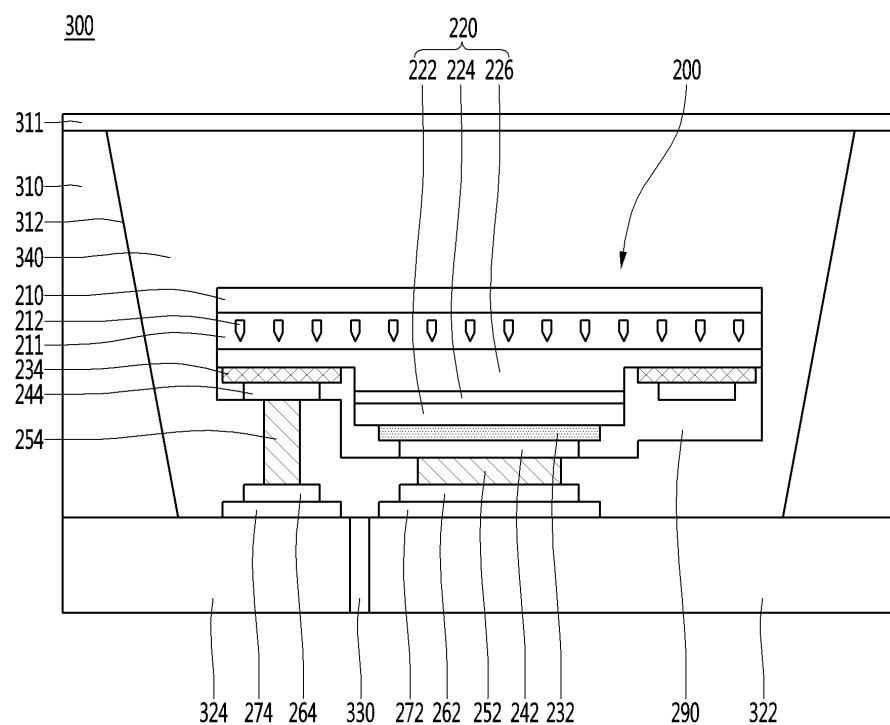

[0053] 도 9는 제2 실시예에 따른 반도체 소자의 단면도이고, 도 10은 도 9에 도시된 반도체 소자의 평면도이고, 도 11은 제2 실시예에 따른 반도체 소자의 부분 확대도이고, 도 12는 제2 실시예에 따른 반도체 소자의 SEM 단면도이다.

[0054] 도 9를 참조하면, 제2 실시예에 따른 자외선 발광소자(200)는 기판(210), 베퍼층(211), 발광 구조물(220), 제1 및 제2 콘택층(또는, 전극)(234, 232), 제1 및 제2 스프레드(spread)층(244, 242), 제1 범프(254), 제2 범프

(252), 제1 및 제2 금속 패드(264, 262), 제1 및 제2 절연층(274, 272), 서브 마운트(280)를 포함할 수 있다.

[0055] 발광 구조물(220)은 기판(210) 아래에 배치된다. 즉, 발광 구조물(220)은 기판(210)과 서브 마운트(280) 사이에 배치될 수 있다. 발광 구조물(220)은 제1 도전형 반도체층(226)과, 제2 도전형 반도체층(222)과, 제1 도전형 반도체층(226)과 제2 도전형 반도체층(222) 사이의 활성층(224)을 포함할 수 있다.

[0056] 기판(210)과 발광 구조물(220) 간의 열 팽창 계수(CTE:Coefficient of Thermal Expansion)의 차이 및 격자 부정합을 개선하기 위해, 이들(110, 120) 사이에 베퍼층(211)이 배치될 수 있다. 베퍼층(211)은 기판(210)과 제1 도전형 반도체층(226) 사이에 배치될 수 있다. 베퍼층(211)의 내부에는 보이드(212)가 형성될 수 있다.

[0057] 도 11에 도시된 바와 같이, 보이드(212)는 제1 도전형 반도체층(112)에 인접하는 제1 영역(212a)과, 기판(210)에 인접하는 제2 영역(212b)을 포함할 수 있다.

[0058] 제1 영역(212a)은 2개 이상의 경사면(facet, 212a-1, 212a-2)을 포함하는 영역이다. 예컨대, 제1 영역(212a)은 단면이 삼각 형상으로 형성될 수 있다. 제1 영역(212a)의 형상이 삼각 뿐일 경우, 경사면은 3개로 형성될 수 있으며, 제1 영역(212a)의 형상이 사각 뿐일 경우, 경사면은 4개로 형성될 수 있다. 즉, 제1 영역(212a)은 각각 뿐 형상에 의해 2개 이상의 경사면으로 이루어진 영역으로 지칭할 수 있다.

[0059] 제2 영역(212b)은 경사면을 포함하지 않는 영역일 수 있다. 제2 영역(212b)은 기판(210)에 인접하는 영역일 수 있다. 예컨대, 제2 영역(212b)은 단면이 사각 형상으로 형성될 수 있다.

[0060] 보이드(212)는 기판(210)으로부터 제1 이격거리(h1)로 이격 배치될 수 있다. 예컨대, 보이드(212)의 제2 영역(212b)의 상면과 기판(210)의 하부면 사이의 제1 이격거리(h1)는 200nm 내지 300nm일 수 있다. 제1 이격거리(h1)가 200nm 미만일 경우 보이드(212)와 기판(210)의 거리가 너무 가깝게 되어 베퍼층(211)을 형성할 때 결정성이 저하될 수 있다. 또한, 보이드(212)에서 산란되는 광이 넓게 확산되기에는 이격거리(h1)가 너무 가깝기 때문에 반도체 소자의 광 추출 효율 및 지향각 특성이 저하될 수 있다.

[0061] 제1 이격거리(h1)가 300nm를 초과할 경우, 베퍼층(211)이 두껍게 형성되어야 하기 때문에 베퍼층(211) 상부에 인가되는 응력이 커져 활성층의 파장을 변화시키고, 반도체 소자의 발광 효율(WPE)이 저하될 수 있다.

[0062] 기판(210)의 일면과 보이드(212)의 제1 영역(212a)의 끝단까지의 제2 이격거리(h2)는 500nm 내지 1200nm일 수 있다. 보이드(212)의 높이(C1)는 500nm 내지 900nm일 수 있다. 보이드(212)의 높이(C1)가 500nm 보다 작을 경우 보이드(212)의 제1 영역(212a)의 경사면에서 제1 도전형 반도체층(226)이 수평 방향으로 너무 급격하게 병합되기 때문에 발광 구조물(220)의 결정성이 저하될 수 있고, 900nm 보다 클 경우 너무 두꺼운 베퍼층(211)으로 인하여 발광 구조물(220)에 인가되는 응력이 커져 활성층(224)에서 발광하는 광의 파장을 변화시키고, 반도체 소자의 발광 효율이 저하될 수 있다.

[0063] 제2 실시예에 따른 발광 소자는 플립 칩 본딩 구조이기 때문에 기판 방향으로 광이 추출되는 구조이기 때문에 기판과 보이드 간의 이격 거리 및 보이드의 크기는 제1 실시예에 따른 발광 소자에 형성된 보이드의 이격 거리와는 상이할 수 있다. 즉, 제2 실시예에 따른 발광 소자는 기판의 하부면과 보이드의 상부면 사이의 거리가 200nm 내지 300nm의 거리로 이격될 경우가 플립 칩 본딩 구조의 발광 소자에서 광 추출 효율이 가장 효과적이다.

[0064] 다시 말해, 플립 칩 본딩 구조에 따른 발광 소자는 활성층에서 발생된 광을 기판을 향해 출사시키는 동시에 활성층에서 발생된 광이 활성층 아래의 반사층에 의해 반사되어 기판을 향해 출사되기 때문에, 기판을 향해 반사되는 광은 보이드와 기판이 가지는 굴절률 차이 및 보이드의 계면에서의 광 산란으로 인해 광 추출 효과가 향상될 수 있다.

[0065] 보이드(212)는 서로 다른 크기로 형성될 수 있다. 보이드(212)는 동일 선상에서의 단면적의 ±30% 범위 내에서 높이, 폭이 서로 다른 크기로 형성될 수 있다. 상기 동일 선상에서의 단면적은 보이드(212)의 중심 영역의 단면적 뿐만 아니라 측정을 위해 설정한 단면적도 포함할 수 있다.

[0066] 도 12에 도시된 바와 같이, 실제 보이드(212)의 형상을 보게 되면, 보이드(212)는 2개 이상의 경사면을 가지는 다양한 형상을 가짐을 알 수 있으며, 그 크기도 서로 다르게 형성되어 배치됨을 알 수 있다.

[0067] 앞서 설명한 바와 같이, 보이드(212)는 기판으로부터 200nm 내지 300nm 이격되어 각 상기 동일 선상에서의 단면적의 30% 범위 내의 크기로 다양한 형상으로 배치되고 있음을 알 수 있다.

[0068] 도 9로 돌아가서, 발광 구조물(220)은 제1 도전형 반도체층(226), 활성층(224) 및 제2 도전형 반도체층(222)을

포함할 수 있다. 제1 도전형 반도체층(226)은 베퍼층(211)과 활성층(224) 사이에 배치될 수 있다. 활성층(224)은 제1도전형 반도체층(226)과 제2도전형 반도체층(222) 사이에 배치될 수 있다. 제1 도전형 반도체층(226)이 N형이면, 제2 도전형 반도체층(222)은 P형일 수 있다. 이와 다르게, 제1 도전형 반도체층(226)이 P형이면, 제2 도전형 반도체층(222)은 N형일 수 있다.

[0069] 제2 실시예에 따른 발광소자는 플립 칩 본딩(flip chip bonding) 구조이기 때문에 활성층(224)에서 방출된 광은 제1 콘택층(234), 제1 도전형 반도체층(226) 및 기판(110)을 통해 출사될 수 있다. 이를 위해, 제1 콘택층(234), 제1 도전형 반도체층(226) 및 기판(210)은 광 투과성을 갖는 물질로 이루어질 수 있다. 이때, 제2 도전형 반도체층(222)과 제2 콘택층(232)은 광 투과성이나 비투과성을 갖는 물질 또는 반사성을 갖는 물질로 이루어질 수 있으나, 실시 예는 특정한 물질에 국한되지 않을 수 있다.

[0070] 서브 마운트(280)는 기판(210)을 대향하여 배치될 수 있다. 즉, 서브 마운트(280)는 기판(210) 아래에 배치될 수 있다. 서브 마운트(280)는 예를 들어 AlN, BN, 탄화규소(SiC), GaN, GaAs, Si 등의 반도체 기판으로 이루어질 수 있으며, 이에 국한되지 않고 열전도도가 우수한 반도체 물질로 이루어질 수도 있다. 또한, 서브 마운트(280) 내에 제너 다이오드 형태의 정전기(ESD:Electro Static Discharge) 방지를 위한 소자가 포함될 수도 있다.

[0071] 제1 및 제2 금속 패드(264, 262)는 서브 마운트(280) 위에 배치되며, 서로 전기적으로 이격될 수 있다. 제1 및 제2 금속 패드(264, 262) 각각은 전기적 전도성을 갖는 금속 물질로 이루어질 수 있다.

[0072] 제1 및 제2 절연층(274, 272)은 제1 및 제2 금속 패드(264, 262)와 서브 마운트(280) 사이에 각각 배치된다. 제1 및 제2 절연층(274, 272)은 보이드와 인접한 활성층의 타측에 배치될 수 있다. 만일, 서브 마운트(280)가 Si와 같이 전기적 전도성을 갖는 물질로 이루어질 경우, 제1 및 제2 금속 패드(264, 262)와 서브 마운트(280)를 전기적으로 절연시키기 위해 제1 및 제2 절연층(274, 272)이 배치될 수 있다. 여기서, 제1 및 제2 절연층(274, 272)은 전기적인 절연성을 갖는 물질을 포함할 수 있다.

[0073] 또한, 제1 및 제2 절연층(274, 272)은 전기적인 절연성을 가질 뿐만 아니라 광 반사 특성을 함께 갖는 물질로 이루어질 수도 있다. 이로 인해, 제1 및 제2 절연층(274, 272)은 반사층일 수 있다. 예를 들어, 제1 및 제2 절연층(274, 272) 각각은 분산 브래그 반사층(DBR:Distributed Bragg Reflector)을 포함할 수 있다. 이 경우, 분산 브래그 반사층은 절연 기능을 수행할 수도 있고, 반사 기능을 수행할 수도 있다. 분산 브래그 반사층은 굴절률이 서로 다른 제1 층 및 제2 층이 교대로 적어도 1회 이상 적층된 구조일 수 있다. 분산 브래그 반사층 각각은 전기 절연 물질일 수 있다. 예컨대, 제1 층은  $TiO_2$ 와 같은 제1 유전체층이고, 제2 층은  $SiO_2$ 와 같은 제2 유전체층을 포함할 수 있다. 예컨대, 분산 브래그 반사층은  $TiO_2/SiO_2$ 층이 적어도 1회 이상 적층된 구조일 수 있다. 제1 층 및 제2 층 각각의 두께는  $\lambda/4$ 이고,  $\lambda$ 는 발광 셀에서 발생하는 광의 파장일 수 있다.

[0074] 또한, 제1 및 제2 절연층(274, 272) 각각은  $SiO_2$ ,  $TiO_2$ ,  $ZrO_2$ ,  $Si_3N_4$ ,  $Al_2O_3$ , 또는  $MgF_2$  중 적어도 하나를 포함할 수 있으나, 실시 예는 이에 국한되지 않는다.

[0075] 발광 구조물(220)과 서브 마운트(280) 사이에 적어도 하나의 범프가 배치될 수 있다. 즉, 발광 구조물(220)과 서브 마운트(280) 사이에 제1 및 제2 범프(254, 252)가 배치될 수 있다.

[0076] 제1 범프(254)는 제1 금속 패드(264)와 제1 스프레드층(244) 사이에 배치될 수 있다. 제1 범프(254)의 개수는 하나 또는 하나 이상의 복수 개일 수 있다.

[0077] 제2 범프(252)는 제2 금속 패드(262)와 제2 스프레드층(242) 사이에 배치될 수 있다.

[0078] 적어도 하나 이상의 범프와 발광 구조물(220) 사이에 적어도 하나 이상의 콘택층이 배치될 수 있다. 예를 들어, 발광 구조물(220)과 제1 및 제2 범프(254, 252) 사이에 제1 및 제2 콘택층(234, 232)이 각각 배치될 수 있다.

[0079] 제2 콘택층(232)은 제2 스프레드층(242)을 경유하여 제2 범프(252)와 발광 구조물(220) 사이에 배치될 수 있다. 즉, 제2 콘택층(232)은 제2 스프레드층(242)과 제2 도전형 반도체층(222) 사이에 배치될 수 있다. 제2 콘택층(232)은 제2 스프레드층(242)과 제2 도전형 반도체층(222)을 전기적으로 서로 연결시킬 수 있다. 이를 위해, 도시된 바와 같이 제2 콘택층(232)은 제2 도전형 반도체층(222)과 접촉할 수 있다.

[0080] 제1 콘택층(234)은 메사 식각(Mesa etching)에 의해 노출된 제1 도전형 반도체층(226) 아래에 배치되며, 제1 스프레드층(244)을 경유하여 제1 범프(254)와 발광 구조물(320)의 제1 도전형 반도체층(226) 사이에 배치될 수 있다. 제1 콘택층(234)은 제1 스프레드층(244)과 제1 도전형 반도체층(226)을 전기적으로 서로 연결시킬 수 있다.

제1 콘택층(234)은 오믹 접촉하는 물질을 포함하여 오믹 역할을 수행할 수 있고, 제1 도전형 반도체층(226)과 전기적으로 연결될 수 있으며, 별도의 오믹층이 제1 콘택층(234) 위 또는 아래에 배치될 수도 있다.

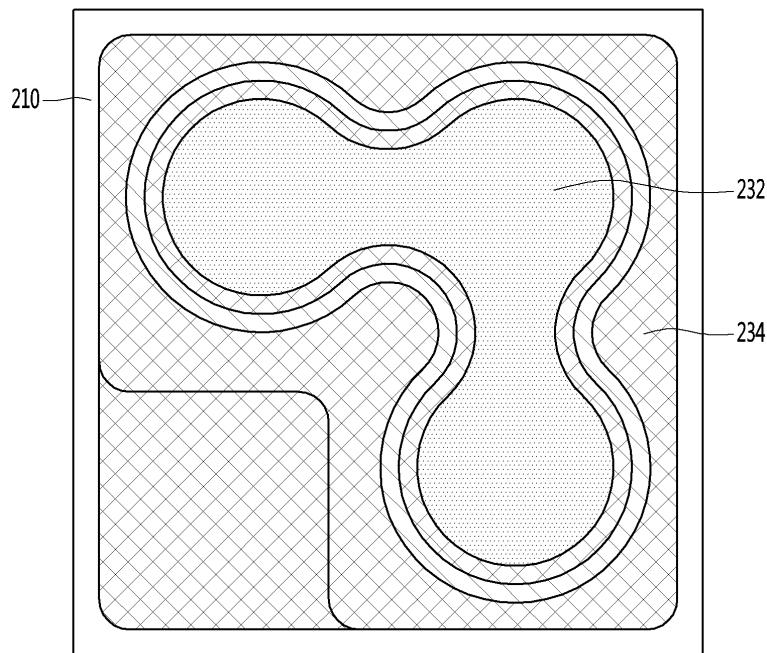

[0081] 도 10은 도 9에 도시된 발광 소자(200)를 서브 마운트(280)로부터 발광 구조물(220) 방향으로 바라본 평면도에 해당한다. 도 9에 도시된 제1 및 제2 스프레드층(244, 242), 제1 및 제2 범프(254, 252), 제1 및 제2 금속 패드(264, 262), 제1 및 제2 절연층(274, 272) 및 서브 마운트(280)의 도시는 생략되었다.

[0082] 도 10에 도시된 바와 같이, 제2 콘택층(232)은 꼭지점이 없는 소정 형상을 가지는 복수의 전극 패턴이 서로 연결된 구조로 이루어질 수 있다. 예컨대, 제2 콘택층(232)은 일정 개수의 소정 형상의 전극 패턴이 삼각 구조를 이루도록 서로 연결될 수 있다. 전극 패턴이 꼭지점을 가지지 않는 형상을 가지는 이유는 꼭지점에서 발생될 수 있는 전기장(E-field)의 집중을 방지하여 소자의 신뢰성을 개선하기 위함이다.

[0083] 또한, 전극 패턴을 증가시킬 경우, 범프에 접촉될 수 있는 면적을 고려해야 되기 때문에 일정 개수 이상 형성하는 것은 어렵게 된다. 따라서, 전극 패턴의 개수는 소자 면적 및 범프의 면적에 따라 적절하게 설계할 수 있다.

[0084] 제2 콘택층(232)의 면적은 전체 소자 면적의 30% 내지 50%를 포함할 수 있다. 전극 패턴은 제2 콘택층(232) 면적의 25% 내지 35%로 형성될 수 있다. 제2 콘택층(232)의 면적이 너무 좁으면 전류 주입 효율이 저하되어 전기적인 특성이 저하되고, 반면, 제2 콘택층(232)의 면적이 너무 넓으면 제1 콘택층(234)이 배치될 수 있는 면적이 좁아져 전기적, 광학적 특성이 저하될 수 있다.

[0085] 제1 콘택층(234)의 면적은 전체 소자 면적의 40% 내지 60%를 포함할 수 있다. 제1 콘택층(234)의 면적이 너무 좁으면 전류 주입 효율이 저하되어 전기적, 광학적 특성이 저하될 수 있다. 반면, 제1 콘택층(234)의 면적이 너무 넓으면 제거되는 활성층(224)의 면적이 커져 광학적 특성이 저하될 수 있다.

[0086] 이러한 점을 고려하여 제2 콘택층(232)의 면적은 제1 콘택층(234)의 면적보다 작게 형성될 수 있으며, 제2 콘택층(232)의 면적과 제1 콘택층(234)의 면적의 비는 1:1.3 내지 1:2로 형성될 수 있다. 즉, 제2 콘택층(232)의 면적과 제1 콘택층(234)의 면적비가 1:1.3 미만이거나, 1:2를 초과하게 되면 전기적 특성 및 광학적 특성이 저하되는 문제점이 발생될 수 있다.

[0087] 제1 및 제2 콘택층(234, 232) 각각은 제1 및 제2 도전형 반도체층(226, 222) 상에 양질로 성장될 수 있는 어느 물질로 형성될 수 있다. 예를 들어, 제1 및 제2 콘택층(232, 234) 각각은 금속으로 형성될 수 있으며, Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, Au, Hf 및 이들의 선택적인 조합으로 이루어질 수 있다.

[0088] 특히, 제2 콘택층(232)은 반사 물질을 포함할 수 있다. 예를 들어, 제2 콘택층(232)은 투명 전극(미도시) 및 반사층(미도시)을 포함할 수 있다. 반사층은 은(Ag)과 같은 반사 물질로 이루어질 수 있다.

[0089] 제2 콘택층(232)은 오믹 특성을 가질 수 있으며, 제2 도전형 반도체층(222)과 오믹 접촉하는 물질을 포함할 수 있다. 만일, 제2 콘택층(232)이 오믹 역할을 수행할 경우, 별도의 오믹층(미도시)은 형성되지 않을 수 있다.

[0090] 적어도 하나의 콘택층과 적어도 하나의 범프 사이에 적어도 하나의 스프레드층이 배치될 수 있다.

[0091] 제2 스프레드층(242)은 제2 콘택층(232)과 제2 범프(252) 사이에 배치될 수 있다. 제1 스프레드층(244)은 제1 콘택층(234)과 제1 범프(254) 사이에 배치될 수 있다. 제1 및 제2 스프레드층(244, 242)은 발광 구조물(220)에서 발생하는 열에 의해 발광 구조물(220)의 저항이 증가하여 전기적인 특성이 악화될 수 있기 때문에 이를 방지하는 역할을 수행할 수 있다. 이를 위해, 제1 및 제2 스프레드층(244, 242) 각각은 전기 전도성이 우수한 물질로 이루어질 수 있다.

[0092] 제2 스프레드층(242)과 제1 스프레드층(244)을 제외한 영역에는 발광구조물(220)의 상부를 덮도록 보호층(290)이 형성될 수 있다. 보호층(290)은 제2 스프레드층(242)의 일부 만을 노출시키도록 구성될 수 있다. 보호층(290)은 절연층을 포함할 수 있다.

[0093] 도 13은 제2 실시예에 따른 반도체 소자 패키지의 단면도이다.

[0094] 도 13을 참조하면, 발광 소자 패키지(300)는 발광 소자(200), 패키지 몸체(310), 제1 및 제2 리드 프레임(322, 324), 제3 절연층(330), 제1 및 제2 와이어(352, 354)를 포함할 수 있다. 여기서, 발광 소자(200)는 도 9 내지 도 12에 도시된 발광 소자(200)에 해당될 수 있다.

[0095] 도 13에 도시된 패키지 몸체(310)는 캐비티(340:Cavity)를 형성할 수 있다. 캐비티(340)에는 에어가 포함될 수 있다. 예를 들어, 패키지 몸체(310)는 제1 및 제2 리드 프레임(322, 324)과 함께 캐비티(340)를 형성할 수

있다. 즉, 캐비티(340)는 패키지 몸체(310)의 측면(312)과 제1 및 제2 리드 프레임(322, 324)의 각 상부면에 의해 정의될 수 있다. 그러나, 실시 예는 이에 국한되지 않는다.

[0096] 다른 실시 예에 의하면, 도 13에 도시된 바와 달리, 패키지 몸체(310)만으로 캐비티(340)를 형성할 수도 있다. 또는, 상부면이 평평한 패키지 몸체(310) 위에 격벽(barrier wall)(미도시)이 배치되고, 격벽과 패키지 몸체(310)의 상부면에 의해 캐비티가 정의될 수도 있다. 패키지 몸체(310)는 EMC(Epoxy Molding Compound) 등으로 구현될 수 있으나, 실시 예는 패키지 몸체(310)의 재질에 국한되지 않는다. 발광 소자(100A)는 캐비티(340)의 내부에 배치될 수 있다.

[0097] 패키지 몸체(310)의 상부에는 캐비티(340)는 덮을 수 있도록 유리 재질의 덮개(311)가 배치되어 캐비티(340)의 공간을 확보할 수 있다.

[0098] 제1 및 제2 리드 프레임(322, 324)은 수평 방향으로 서로 이격되어 배치될 수 있다. 제1 및 제2 리드 프레임(322, 324) 각각은 도전형 물질 예를 들면 금속으로 이루어질 수 있으며, 실시 예는 제1 및 제2 리드 프레임(322, 324) 각각의 물질의 종류에 국한되지 않는다. 제1 및 제2 리드 프레임(322, 324)을 전기적으로 분리시키기 위해, 제1 및 제2 리드 프레임(322, 324) 사이에는 제3 절연층(330)이 배치될 수도 있다.

[0099] 또한, 패키지 몸체(310)가 도전형 물질 예를 들면 금속 물질로 이루어질 경우, 제1 및 제2 리드 프레임(322, 324)은 패키지 몸체(310)의 일부일 수도 있다. 이 경우에도, 제1 및 제2 리드 프레임(322, 324)을 형성하는 패키지 몸체(310)는 제3 절연층(330)에 의해 서로 전기적으로 분리될 수 있다.

[0100] 또한, 제1 및 제2 도전형 반도체층(226, 222)과 제1 및 제2 범프(252A, 254)를 통해 각각 연결된 제1 및 제2 금속 패드(272, 274)는 제1 및 제2 와이어(352, 354)를 통해 제1 및 제2 리드 프레임(322, 324)에 각각 전기적으로 연결될 수 있다.

[0101] 실시 예에 따른 발광 소자 패키지는 복수 개가 기판 상에 어레이될 수 있고, 발광 소자 패키지의 광 경로 상에 광학 부재인 도광판, 프리즘 시트, 확산 시트 등이 배치될 수 있다. 이러한 발광 소자 패키지, 기판, 광학 부재는 조명 시스템 또는 차량용 램프의 기능할 수 있다.

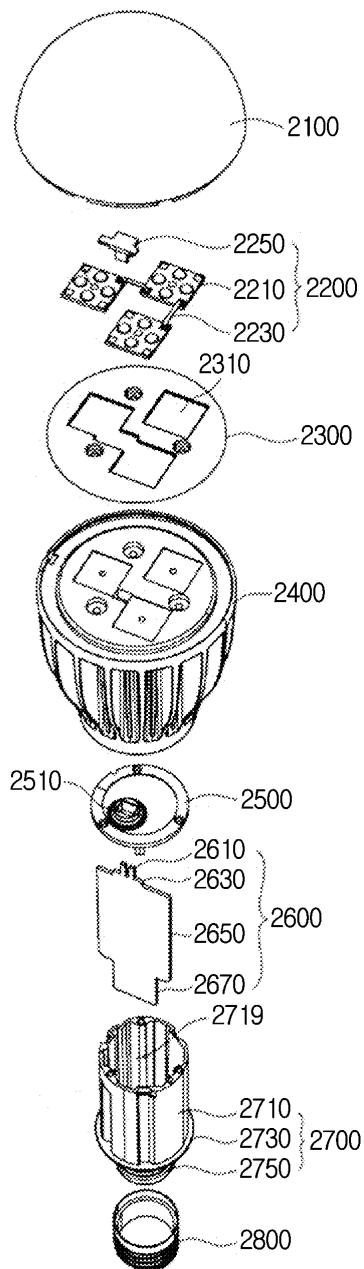

[0102] 도 14 및 도 15는 실시예에 따른 반도체 소자를 포함하는 조명 시스템의 실시예들을 나타낸 분해 사시도이다.

[0103] 도 14에 도시된 바와 같이, 실시예에 따른 조명 장치는 커버(2100), 광원 모듈(2200), 방열체(2400), 전원 제공부(2600), 내부 케이스(2700), 소켓(2800)을 포함할 수 있다. 또한, 실시 예에 따른 조명 장치는 부재(2300)와 홀더(2500) 중 어느 하나 이상을 더 포함할 수 있다. 광원 모듈(2200)은 본 발명에 따른 발광소자(100) 또는 발광소자 패키지(200)를 포함할 수 있다.

[0104] 또한, 도 15에 도시된 바와 같이, 본 발명에 따른 조명 장치는 커버(3100), 광원부(3200), 방열체(3300), 회로부(3400), 내부 케이스(3500), 소켓(3600)을 포함할 수 있다. 광원부(3200)는 실시 예에 따른 발광소자 또는 발광소자 패키지를 포함할 수 있다.

### 산업상 이용가능성

[0105] 실시 예는 평판용 조명 장치에 적용될 수 있다.

[0106] 실시 예는 발광소자를 갖는 평판용 조명 장치에 적용될 수 있다.

[0107] 실시 예는 발광소자를 갖는 차량용 램프에 적용될 수 있다.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

## 도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15