(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6617109号

(P6617109)

(45) 発行日 令和1年12月4日(2019.12.4)

(24) 登録日 令和1年11月15日(2019.11.15)

(51) Int.Cl.

H02M 3/155 (2006.01)

H05B 37/02 (2006.01)

F 1

H02M 3/155

H05B 37/02P

C

請求項の数 14 (全 16 頁)

(21) 出願番号 特願2016-550866 (P2016-550866)

(86) (22) 出願日 平成27年1月30日 (2015.1.30)

(65) 公表番号 特表2017-506057 (P2017-506057A)

(43) 公表日 平成29年2月23日 (2017.2.23)

(86) 國際出願番号 PCT/EP2015/051868

(87) 國際公開番号 WO2015/121079

(87) 國際公開日 平成27年8月20日 (2015.8.20)

審査請求日 平成30年1月26日 (2018.1.26)

(31) 優先権主張番号 14155173.9

(32) 優先日 平成26年2月14日 (2014.2.14)

(33) 優先権主張国・地域又は機関

歐州特許庁 (EP)

(73) 特許権者 516043960

シグニファイ ホールディング ピー ヴ

イ

S I G N I F Y H O L D I N G B. V

.オランダ国 5656 アーネー アイン

トホーフェン ハイ テク キャンパス

48

High Tech Campus 48

, 5656 AE Eindhoven,

The Netherlands

(74) 代理人 100163821

弁理士 柴田 沙希子

最終頁に続く

(54) 【発明の名称】負荷のための電流供給のパルス幅変調を制御するための回路及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ドライバと、前記ドライバに加えられるパルス幅変調された入力信号を制御するための制御装置と、を備える回路であって、前記入力信号が、オンタイム及びオフタイムを含む周期を有し、前記周期が第1の周波数で反復し、前記制御装置が、前記周期又は前記オフタイムに対する前記オンタイムの比である前記入力信号のデューティサイクルを制御し、

前記ドライバが、前記入力信号に基づいて負荷に電流を供給し、各周期の前記オフタイムにわたって、前記ドライバが、電源から前記負荷への電流の供給を抑制し、各周期の前記オンタイムにわたって、前記ドライバが、前記電源から前記負荷に電流を供給するが、前記第1の周波数よりも高い第2の周波数で供給して、前記負荷が、前記デューティサイクルに依存するレベルで出力を発生し、

前記制御装置が、前記負荷の前記出力を所望の出力レベルに設定するように前記デューティサイクルを制御し、前記所望の出力レベルに対応する点の周りで前記デューティサイクルをディザリングし、

前記回路が、前記第2の周波数を測定するため、前記ドライバから前記制御装置へのフィードバックチャネルを更に備え、前記制御装置が、前記フィードバックチャネルを介して測定された前記第2の周波数に依存して、前記デューティサイクルの前記ディザリングを適応させる、

回路。

## 【請求項 2】

10

20

前記制御装置が、前記負荷の前記出力を複数の異なる出力レベルに切り替えるために前記デューティサイクルを制御し、前記ディザリングが、前記異なる出力レベルにそれぞれ対応する複数の点それぞれの周りで前記デューティサイクルをディザリングすることを含む、請求項1に記載の回路。

**【請求項3】**

前記負荷が光源を含み、前記出力が、前記光源によって放出される光を含む、請求項1又は2に記載の回路。

**【請求項4】**

前記制御装置が、前記負荷によって放出される光を複数の異なる光出力レベルに切り替えるために前記デューティサイクルを制御する、請求項3に記載の回路。 10

**【請求項5】**

前記制御装置が、データ信号のシンボルを信号伝送するために、前記異なる出力レベルを使用することによって前記データ信号を光に符号化する、請求項4に記載の回路。

**【請求項6】**

前記制御装置が、前記異なる光出力レベルにそれぞれ対応する複数の点それぞれの周りで前記デューティサイクルをディザリングすることによって前記ディザリングを行う、請求項4又は5に記載の回路。

**【請求項7】**

前記負荷の前記出力が、前記デューティサイクルと前記出力レベルとの関係に従って変化し。 20

前記第1と第2の周波数が合わさって、前記デューティサイクルの規則的なインターバルで反復する前記デューティサイクルと前記出力レベルとの関係のパターンを生み出す、請求項1乃至6の何れか一項に記載の回路。

**【請求項8】**

前記負荷が光源を備え、前記出力が、前記光源によって放出される光を含み、前記関係が、前記デューティサイクルと前記光のレベルとの関係である、請求項7に記載の回路。

**【請求項9】**

前記デューティサイクルが、前記1点の周り又は前記複数の点それぞれの周りで、複数であるn個の離散ステップでディザリングされる、請求項1乃至8の何れか一項に記載の回路。 30

**【請求項10】**

前記デューティサイクルが、前記1点の周り又は前記複数の点それぞれの周りで、P/nのn個のステップでディザリングされ、ここで、Pは前記デューティサイクルの前記規則的なインターバルの周期である、請求項7又は8に従属する請求項9に記載の回路。

**【請求項11】**

前記ディザリングがランダムであり、前記n個のステップはそれぞれ、1周期当たりに選択される確率が1/nである、請求項9又は10に記載の回路。

**【請求項12】**

前記ドライバが降圧コンバータである、請求項1乃至11の何れか一項に記載の回路。

**【請求項13】**

前記フィードバックチャネルが、分圧器又は差動回路を備える、請求項1乃至12の何れか一項に記載の回路。 40

**【請求項14】**

コードを含むコンピュータプログラムであって、前記コードが、コンピュータ可読記憶媒体上で具現化され、1つ又は複数のプロセッサ上で実行されるとき、

入力信号に基づいて負荷に電流を供給するドライバに、パルス幅変調された入力信号が提供されるようにする操作であって、前記入力信号が、オンタイム及びオフタイムを含む周期を有し、前記周期が第1の周波数で反復し、各周期の前記オフタイムにわたって、前記ドライバが、電源から負荷への電流の供給を抑制し、各周期の前記オンタイムにわたって、前記ドライバが、前記第1の周波数よりも高い第2の周波数で、前記電源から前記負 50

荷に電流を供給する操作と、

前記負荷の出力を所望の出力レベルに設定するために、前記周期又は前記オフタイムに対する前記オンタイムの比である前記入力信号のデューティサイクルを制御する操作と、

前記ドライバからのフィードバックチャネルを介して前記第2の周波数を測定する操作と、

前記フィードバックチャネルを介して測定された前記第2の周波数に依存して、前記所望の出力レベルに対応する点の周りで前記デューティサイクルをディザリングする操作とを行う、コンピュータプログラム。

#### 【発明の詳細な説明】

##### 【技術分野】

10

##### 【0001】

本開示は、負荷をドライブするためにドライバに加えられるパルス幅変調された入力信号の制御に関する。

##### 【背景技術】

##### 【0002】

パルス幅変調（P W M）は、負荷に供給される電力を制御するための技法である。マイクロプロセッサ等の制御装置は、周期的な制御信号を生成し、この制御信号は、各周期中、特定の時間（オンタイム）にわたってアサートされ、周期の残りの時間（オフタイム）にわたってアサート停止されるように変調される。デューティサイクルは、変調周期に対するオンタイムの比（又はより全般的には、周期若しくはオフタイムに対するオンタイムの比）を表す。「オン」及び「オフ」は公称のものでよいことに留意されたい。即ち、それらは、絶対的にオンであること、絶対的にオフであること、又は「バックグラウンド」D C レベルに対するハイレベルとローレベルとの間のスイッチングを意味することができる。

20

##### 【0003】

制御装置は、このパルス幅変調された制御信号を、降圧コンバータ又は他のタイプのドライバ等、ドライバの入力に加え、ドライバは、制御信号の変調に基づいて負荷をドライブする。各周期のオンタイム中、ドライバは、電源から負荷に電流を供給し、各周期のオフタイム中、ドライバは、電源から負荷に電流を供給しない。従って、負荷に供給される平均電力は、デューティサイクルに依存する。即ち、より高いデューティサイクルは、電流がより長い時間にわたってオンであることを意味し、従って平均出力はより高い。逆に、より低いデューティサイクルは、電流がより短い時間にわたって供給されることを意味し、従って平均出力はより低い。

30

##### 【0004】

従って、デューティサイクルを制御することによって（即ちP W M周期又はオフタイムに対するオンタイムを変えることによって）、制御装置は、負荷がドライブされる平均出力を制御することが可能である。

##### 【0005】

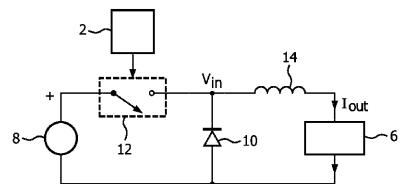

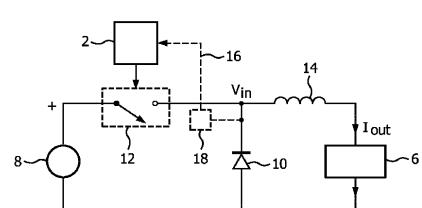

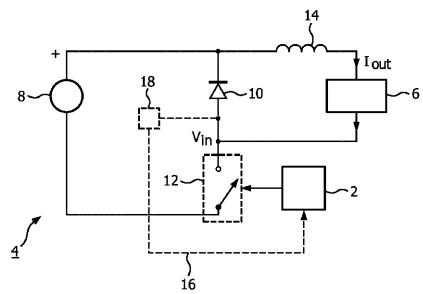

図1は、パルス幅変調に基づいて負荷への出力を制御するという目的で採用される、典型的な降圧コンバータ4を備える回路の概略図である。降圧コンバータ4に加えて、回路は、電源8と、負荷6と、制御装置2、例えば適切にプログラムされたマイクロプロセッサとを備える。降圧コンバータ4は、スイッチ12と、インダクタ14と、ダイオード10とを備える。スイッチ12は、電源8の第2の端子（例えば正の端子）に接続される第1の接点と、インダクタ14の第1の端子に接続される第2の接点とを有する。インダクタ14は、負荷6の第1の端子に接続された第2の端子を有し、負荷6は、電源8の第1の端子に接続された第2の端子を有する。ダイオード10は、インダクタ8の第1の端子（及びスイッチ12の第2の接点）に接続されたカソードと、負荷6の第2の端子（及び電源8の第1の端子）に接続されたアノードとを有する。従って、スイッチ12と電源8が互いに直列に接続され、またインダクタ14と負荷6が互いに直列に接続され、インダクタ14と負荷6との直列構成は、電源8とスイッチ12との直列構成に並列に接続され、

40

50

ダイオード 10 も、(電源 8 と逆バイアスで) 電源 8 とスイッチ 12 との直列構成に並列に接続される。

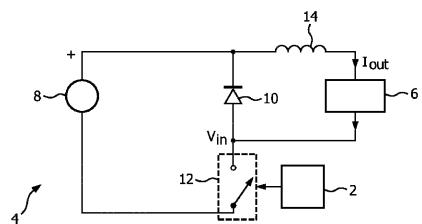

#### 【0006】

図 1 は、ハイサイドスイッチを有する降圧コンバータを示すことに留意されたい。ローサイドスイッチを備える代替構成が、図 2 に示されている。この回路は同様であるが、ただし、スイッチ 12 は、電源の他方の(第 1 の)端子と、負荷 6 の第 2 の端子(及びダイオード 10 のアノード)との間に接続され、電源 8 の第 2 の(例えば正の)端子が、インダクタ 14 の第 1 の端子(及びダイオード 10 のカソード)に接続される。

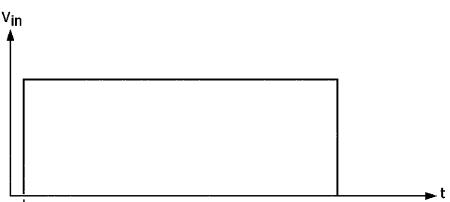

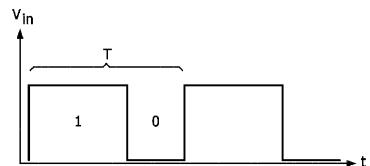

#### 【0007】

何れの変形形態でも、制御装置 2 は、パルス幅変調された制御信号をスイッチ 12 の入力に加えるように構成され、それにより、パルス幅変調された入力信号を電圧信号  $V_{in}$  の形態で発生する。制御信号がオン(アサート。例えば、論理 1)であるとき、スイッチ 12 は閉じており、入力電圧  $V_{in}$  を電源 8 に接続する。制御信号がオフである(アサート停止。例えば、論理 0)であるとき、スイッチ 12 は開いており、 $V_{in}$  が電源 8 から切断される。図 3 に示されるように、これは、矩形のパルス幅変調された入力電圧  $V_{in}$  を生じ、この入力電圧  $V_{in}$  は、制御装置 2 によって発生されたパルス幅変調制御信号に対応する。この矩形の PWM 入力波形は、ハイサイドスイッチ(図 1)の場合にはダイオード 10 のアノードで生じ、ローサイドスイッチ(図 2)の場合にはカソードで生じる。 $V_{in}$  が電源 8 に接続されているオンタイム中、これは、電流が電源 8 からインダクタ 14 及び負荷 6 を通って流れるようにする。 $V_{in}$  が電源から切断されているオフタイム中、これは、(インダクタが通電停止されるときに、幾らかの電流がインダクタ 14 から負荷 6 を通って一時的に流れることはあるが) 電流が電源 8 からインダクタ 14 及び負荷 6 に供給されないことを意味する。

#### 【0008】

しかし、降圧コンバータは単なる一例に過ぎないことに留意されたい。一般に、LED ランプ又は他のランプのドライバに関して、他の形態のスイッチモード電源、例えばフライバックコンバータも使用され得る。

#### 【0009】

制御装置 2 は、パルス幅変調のデューティサイクルを調整して、負荷に供給される電流又は電力、従って負荷の出力を制御する。電流は、LED ドライバの場合に制御される特性であるが、LED にわたる電圧降下がほぼ一定であるので、電流は電力に(ほぼ)比例して対応する。例えば、光源の場合には、パルス幅変調は、放出される光の出力パワー若しくは強度を制御し、又はモータの場合には、パルス幅変調はモータの速度を制御する。現在の技術水準の多くの LED ドライバは、LED を通る電流、従って LED によって放出される光のレベルを制御するための降圧コンバータを利用する。PWM 波形の周波数は、典型的には 4 ~ 16 kHz 程度である。また、現在の技術水準の符号化光制御装置は、LED によって放出される可視光の DC フリー振幅変調を生成するために、デューティサイクルを変えることによってデータを PWM 波形に符号化することもできる。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

しかし、上記のように、パルス幅変調された制御信号は、負荷に直接は加えられず、降圧コンバータ等のドライバを介して加えられる。PWM 波形の各周期のオフ状態では、降圧コンバータは LED に電流を供給しないが、オン状態では、降圧コンバータは、典型的には、高周波数(典型的には 100 ~ 800 kHz の間)での「電流パケット」をそのコイルの二次側、従って LED にプッシュする。これは、本明細書では、(PWM スイッチング周波数とは異なる)「降圧スイッチング周波数」と称され得る。例えば、図 4 を参照されたい。

#### 【0011】

これら 2 つの異なる周波数でのスイッチングの組合せは、問題を引き起こすことがある

10

20

30

40

50

。 PWM信号のスイッチングエッジが第2のより高い周波数の立上りエッジ又は立下りエッジと一致するかどうかにより、これは、PWM波形デューティサイクルと負荷に加えられる電流との関係が必ずしも完全には線形ではないことを意味する。例えば、PWM入力信号 $V_{in}$ の立下りエッジが、降圧コンバータのより高周波数の「ウィッギ」の1つの立下りエッジと一致する場合、PWM入力信号 $V_{in}$ の正確なスイッチング時間は、負荷に供給される電流 $I_{out}$ に影響を及ぼさず、従ってデューティサイクルと負荷電流との関係は線形でない。

#### 【0012】

負荷がLED等の光源の場合、この非線形性により、制御装置2によって発生されるPWM波形のDCフリー符号化にも関わらず、降圧スイッチング周波数とPWMデューティサイクルとの特定の組合せが、LEDによって放出される光における目に見える明滅を引き起こすことを本発明者等は認識している。より全般的には、他の負荷をドライブするための他の種類のドライバも高周波振動又は高調波を受けることがあり、そのような周波数とPWMスイッチング周波数との相互作用が、やはり非線形性等の望ましくない効果を引き起こすことがある。実際には、周波数のそのような組合せを回避することは難しいことがあります、不可能なことさえある。従って、よりロバストなソリューションが望まれ得る。

10

#### 【課題を解決するための手段】

#### 【0013】

本明細書で開示される一態様によれば、パルス幅変調された入力信号を制御するための制御装置と、入力信号に基づいて負荷に電流を供給するように構成されたドライバとを備える回路が提供される。パルス幅変調されたときに、入力信号は、オンタイム及びオフタイムを含む周期を有し、この周期は第1の周波数で反復し、制御装置は、入力信号のデューティサイクルを制御するように構成され、このデューティサイクルは、周期又はオフタイムに対するオンタイムの比である。各周期のオフタイムにわたって、ドライバは、電源から負荷への電流の供給を抑制し、各周期のオンタイムにわたって、ドライバは、電源から負荷に電流を供給するが、第1の周波数よりも高い第2の周波数である。従って、このパルス幅変調に基づいて、負荷は、デューティサイクルに応じたレベルで出力を発生する。更に、本開示によれば、制御装置は、デューティサイクルに「ディザリング」を施すように構成される。即ち、制御装置は、負荷の出力を所望の出力レベルに設定するためにデューティサイクルを使用するが、また、所望の出力レベルに対応する点の周りでデューティサイクルをディザリングする。

20

#### 【0014】

ディザリングは、有利には、第2の周波数（例えば降圧スイッチング周波数）と第1の周波数（PWM周波数）との相互作用によって引き起こされる、デューティサイクルと負荷の出力との関係における望ましくないアーチファクトを制御装置が回避又は少なくとも緩和することができるようとする。

30

#### 【0015】

好ましい実施形態では、回路は、第2の周波数を測定するための、ドライバから制御装置へのフィードバックチャネルを更に備え、制御装置は、前記フィードバックチャネルを介して測定された第2の周波数に依存してディザリングを適応させるように構成される。

40

#### 【0016】

幾つかの実施形態では、制御装置は、負荷の出力を複数の異なる出力レベルに切り替えるためにデューティサイクルを制御するように構成されてよく、前記ディザリングは、前記異なる出力レベルにそれぞれ対応する複数の点それぞれの周りでデューティサイクルをディザリングすることを含んでいてよい。

#### 【0017】

幾つかの実施形態では、負荷は光源を含み、出力は、光源によって放出される光を含む。制御装置は、負荷によって放出される光を複数の異なる光出力レベルに切り替えるためにデューティサイクルを制御するように構成されてよい。符号化光技法によれば、制御装置は、データ信号のシンボルを信号伝送するために、異なる出力レベルを使用することに

50

よってデータ信号を光に符号化するように構成されてよい。そのような実施形態では、制御装置は、異なる光出力レベルにそれぞれ対応する複数の点それぞれの周りでデューティサイクルをディザリングするように構成されてよい。デューティサイクルが（符号化された情報に対応する）実質的にランダムな変数である符号化光の用途において、幾つかの実施形態では、このディザリングは、目に見える明滅の現象を緩和することができる。

#### 【0018】

幾つかの実施形態では、負荷の出力は、デューティサイクルと出力レベルとの関係に従って変化し、第1と第2の周波数が合わさって、デューティサイクルの規則的なインターバルで反復するこの関係のパターンを生じ得る（例えば図5参照）。負荷は光源を備えていてよく、出力は、光源によって放出される光を含んでいてよく、前記関係は、デューティサイクルと光のレベルとの関係である。10

#### 【0019】

幾つかの実施形態では、デューティサイクルは、前記1点の周り又は前記複数の点それぞれの周りで、複数（n個）の離散ステップでディザリングされてよい。デューティサイクルは、前記1点の周り又は前記複数の点それぞれの周りで、P/nのn個のステップでディザリングされてよく、ここで、Pは、前記インターバルである。ディザリングはランダムでよく、n個のステップはそれぞれ、1周期当たりに選択される確率が1/nである。。20

#### 【0020】

幾つかの実施形態では、フィードバックチャネルは、分圧器又は差動回路を備えていてよい。。20

#### 【0021】

本明細書で開示する別の態様によれば、コードを含むコンピュータプログラム製品であって、コードが、コンピュータ可読記憶媒体上で具現化され、1つ又は複数のプロセッサ上で実行されるときに、入力信号に基づいて負荷に電流を供給するドライバに、パルス幅変調された入力信号が提供されるようにする操作であって、入力信号が、オンタイム及びオフタイムを含む周期を有し、周期が第1の周波数で反復し、各周期のオフタイムにわたって、ドライバが、電源から負荷への電流の供給を抑制し、各周期のオンタイムにわたって、ドライバが、第1の周波数よりも高い第2の周波数で、電源から負荷に電流を供給する操作と、負荷の出力を所望の出力レベルに設定するために、周期又はオフタイムに対するオンタイムの比である入力信号のデューティサイクルを制御する操作と、所望の出力レベルに対応する点の周りでデューティサイクルをディザリングする操作とを行うように適合されるコンピュータプログラム製品が提供され得る。30

#### 【0022】

幾つかの実施形態では、コンピュータプログラム製品が、本明細書で開示される制御装置の特徴の任意のものに従って更に構成され得る。

#### 【0023】

本開示の理解を助けるため、及び実施形態が実行され得る方法を示すために、例として添付図面を参照する。

#### 【図面の簡単な説明】

40

#### 【0024】

【図1】負荷及び制御装置を有する降圧コンバータの概略図である。

【図2】負荷及び制御装置を有する別の降圧コンバータの概略図である。

【図3】降圧コンバータの入力電圧の概略図である。

【図4】降圧コンバータの出力電流を示すタイミング図である。

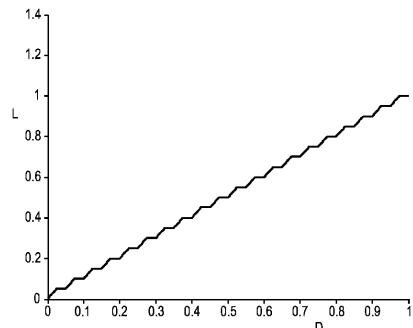

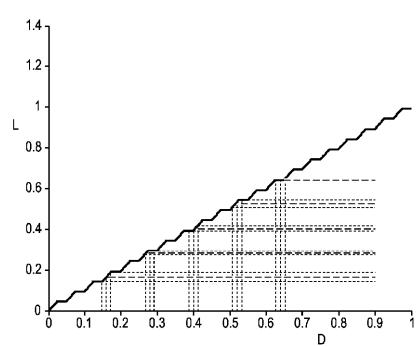

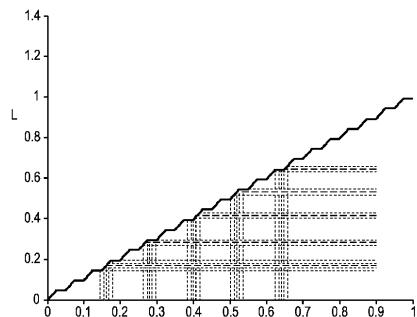

【図5】降圧コンバータ入力のデューティサイクルに対する出力レベルを示すグラフである。

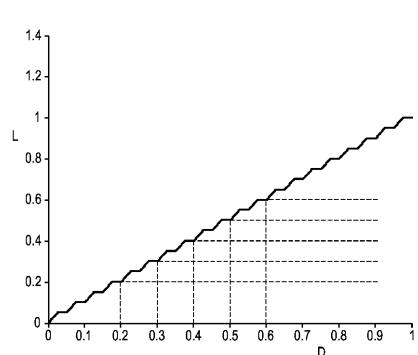

【図6】デューティサイクルに対する出力レベルを示す別のグラフである。

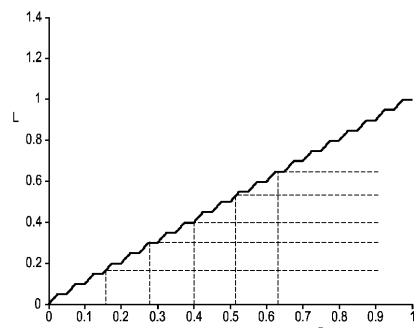

【図7】デューティサイクルに対する出力レベルを示す別のグラフである。

【図8】負荷及び制御装置を有する別の降圧コンバータの概略図である。

50

【図9】負荷及び制御装置を有する別の降圧コンバータの概略図である。

【図10】デューティサイクルに対する出力レベルを示す別のグラフである。

【図11】デューティサイクルに対する出力レベルを示す別のグラフである。

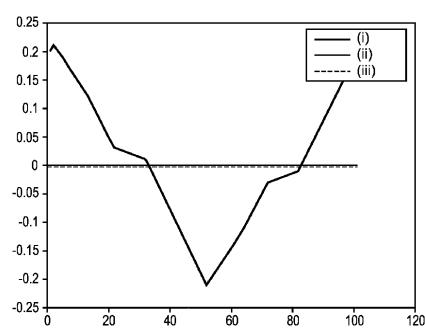

【図12】位相に対する降圧コンバータの出力でのDC成分を示すグラフである。

【図13】位相に対するDC成分を示す別のグラフである。

【図14】位相に対するDC成分を示す別のグラフである。

【図15】位相に対するDC成分を示す別のグラフである。

【図16】位相に対するDC成分を示す別のグラフである。

【図17】位相に対するDC成分を示す別のグラフである。

【発明を実施するための形態】

10

【0025】

論じられるように、現在の技術水準のLED照光用ドライバは、入力PWMデューティサイクルと、発生される出力光レベルとの不規則な（非線形の）マッピングによって特徴付けられる。符号化光伝送の場合、これは、変調システムのDCフリー特性をなくして、目に見える明滅を生じることがある。以下により詳細に説明するように、この明滅は、ドライバの入力にディザを加えることによって、可視性閾値未満のレベルに緩和され得ることが判明した。

【0026】

現在の技術水準のLEDドライバは、所望の光出力を得るために、LEDを通る電流を制御するための降圧コンバータを利用することが多い。PWM制御式ドライバの場合、制御装置2（例えば、適切にプログラムされたマイクロプロセッサ）が、PWM(0,1)波形のデューティサイクルを調整する。このPWM波形の周波数は、典型的には、4~16kHz程度である（又は更に高い）。各PWM周期の「0」状態では、電流はLEDに供給されず、「1」状態では、降圧コンバータは、典型的には、高周波数（典型的には100~800kHzの間）での「電流パケット」をそのコイル14の二次側にプッシュし、それによりLEDを通電する。このより高い「降圧スイッチング周波数」は、入力で見られるインピーダンスを介して負荷に依存する。通常、この第2のはるかに高い周波数での電流は、実際に負荷に送られる前に（コンデンサによって）幾らかはローパスフィルタリングされるが、それにも関わらず存在する。典型的には、この周波数は、PWM周波数よりも少なくとも1桁高い（10倍）。

20

【0027】

パルス幅変調のデューティサイクルは、LED6に供給される平均電流、従ってLEDによって出力される光のレベルを制御する。

【0028】

そのような構成は、符号化光を発生するために使用され得て、それにより、LED又はLEDのアレイ等の光源から放出される可視光にデータが埋め込まれる。これを行う1つのやり方は、放出される光のレベルを変調することであり、これは、異なるシンボルを表現するために複数の離散値の間で入力デューティサイクル（従って出力光レベル）を変えることによって実現され得る。例えば、本出願人によって開発され、「Ternary Manchester」と称されている1つの方式では、データシンボルを符号化するために5つの異なるレベルが使用される。Ternary Manchesterは、国際公開第2012052935号で述べられている。

30

【0029】

図4は、PWM制御式の降圧コンバータ4の出力電流を示す。左側では、制御装置2（例えばマイクロプロセッサ）によって調整されている、单一のPWM周期における「1」状態の開始が見て取れる。右側では、「Ternary Manchester」符号化光の5つの変調レベルに対応する5つの異なるPWM持続時間に関して、「0」状態へのスイッチが見て取れる。軌跡の上のウィグルは、PWM周期の「1」状態中の、降圧コンバータ4のより高周波数のオン／オフスイッチングに対応する。

40

【0030】

50

図 5 は、（制御装置 2 によって加えられる）入力デューティサイクル D と、電流又は電力に関する L E D の平均出力光レベル L との得られるマッピングを示し、これはまた、ドライバ 4 の伝達関数とも称され得る。L E D に関して、（L E D にわたる電圧降下がほぼ一定であるので）光出力パワーは電流に（ほぼ）比例する。デューティサイクルが増加する一方で平均の光出力が増加しない水平プラトー部分に留意されたい。これらのプラート一部分は、P W M 入力信号の「0」状態へのスイッチングに対応し、図 4 での降圧コンバータによって引き起こされる「ウィグル」の 1 つの立下りエッジの位置にある。降圧コンバータ 4 が、各ウィグルの立下りエッジ中に「オフ」に切り替えられるので、立下りエッジ内での P W M 入力信号の正確なスイッチング時間は、降圧コンバータ 4 の二次側に「ブッシュ」される電流に対して影響を及ぼさず、従って一定の光出力をもたらす。通常であれば線形であるこの関係において現れるこれらの異形状（凹凸又は不整）は、デューティサイクルインターバルと共に規則的なインターバルで反復し、即ち（デューティサイクルスケールでの）デューティサイクル空間内で循環的である。図 5（並びに図 6、図 7、図 10 0、及び図 11）の例では、降圧コンバータ「周期」は、デューティサイクルでの 0.0 5 のインターバルである。

#### 【0031】

符号化光の発生のために前述の L E D ドライバを使用する際、問題が生じ得る。

#### 【0032】

符号化光に関して使用される波形（実際には、平均の所要の照光からの偏差）は、明滅を発生しないように注意深く選択され得て、即ち低周波数を含まない。典型的な例は、Ternary Manchester ( T M ) であり、これは、5 つの異なるレベル（この場合には P W M デューティサイクル）、例えば集合 { 0.2, 0.3, 0.4, 0.5, 0.6 } を使用する。図 6 を参照されたい。この例での平均光レベルは、0.4 である。0.4 からの偏差が低周波数成分を有さない、即ち明滅を引き起こさないように、情報を伝送するために異なるレベルが順次に使用される。図 6 の例では、出力光レベルが等間隔にされていることも見て取れ、即ち、バランスの取れた入力が、やはりバランスの取れた出力を生み出す。この場合、これが生じるのは、任意の 2 つの連続するレベル間でデューティサイクル空間において降圧コンバータのちょうど 2 つの「周期」（即ち図 4 のパターンでの 2 つのインターバル）を有するように、P W M 周波数とデューティサイクルレベルとが注意深く選択されているからである。しかし、一般にはこれは当て嵌まらない。

#### 【0033】

図 7 は、符号化光 Ternary Manchester シンボルの変調振幅を 20 % 大きくして同じドライバ 4 が使用される場合を示す。この場合、Ternary Manchester 符号化光の伝送中の平均光レベルが、Ternary Manchester 伝送がない場合の平均光レベル（図 7 の例では 0.4 ）に等しくないので、入力 P W M デューティサイクルの等距離間隔が、得られる出力光レベルの非等距離間隔をもたらし、これが更にコードの D C フリー特性を破壊し、即ち明滅が発生されることに留意されたい。シンボルの他の集合に基づく他の符号化方式でも同様の問題が生じ得ることを理解されたい。

#### 【0034】

これに対処するために、本開示は、「ディザリング」の一形態を提供し、ここで、符号化 P W M 波形のデューティサイクルが、降圧スイッチング周波数に依存して適応される。降圧コンバータ 4 から制御装置 2（例えばマイクロプロセッサ）へのフィードバックチャネルが追加され、それにより、制御装置 2 は、P W M 波形のデューティサイクルを適切に適応し得る。光出力とデューティサイクルとのマッピングが、幾つかの周期的な「変形部」を上に有する線形関数のような形であること（図 5 ）が、ディザリング手法を特に効果的にする。

#### 【0035】

図 8 及び図 9 は、フィードバックチャネル 16 を組み込む 2 つの降圧コンバータ実装形態を示す。図 8 は、ハイサイドスイッチに基づく実装形態を示し、図 9 は、ローサイドスイッチに基づく実装形態を示し、それぞれ図 1 及び 2 と同様であるが、フィードバックチ

10

20

30

40

50

ヤネル 16 を組み込む。

【0036】

図8(ハイサイドスイッチ)では、ダイオード10のカソードで大きな電位変化を測定することによって降圧スイッチング周波数が得られる。従って、フィードバックチャネル16は、ダイオード10のカソードと、制御装置2の入力との間に接続される。

【0037】

図9(ローサイドスイッチ)では、スイッチング周波数を測定するために、接地に対するアノードでの電圧が使用され得る。従って、フィードバックチャネルは、ダイオード10のアノードと制御装置2の入力との間に接続される。

【0038】

フィードバックチャネル16は、ダイオード10のアノード又はカソードとマイクロコントローラとの間に追加の測定回路構成18を備えていてよい。これは、アノード又はカソードに現れ得る大きな電圧(>3.3V)により、望ましいことがある。例えば、測定回路18は、供給及び負荷電圧が比較的一定である場合には分圧器でよく、又はLEDを通る漏れ電流の回避も行う差動回路でよい(漏れ電流は、降圧コンバータ4がオフに切り替えられる場合でさえLED6を点灯したままにする)。

【0039】

以下により詳細に論じられるように、ディザリングは、ヒステリシス電流モードで動作する降圧コンバータ4の局所非線形性を減少するために使用され得る。このヒステリシス電流モードでは、パルス幅変調(PWM)を使用してコンバータ全体をイネーブル及びディスエーブルにすることによって出力電流が変調される。

【0040】

ディザリングは、フィードバックに基づいて制御装置2によって実施される。制御装置は、コードの形態で実装され、コードは、記憶媒体(メモリ)に記憶され、マイクロコントローラ又はより全般的にはプロセッサ上で実行されるように構成される。代替として、制御装置2の幾つか又は全てが、専用ハードウェア回路構成、又はPGAやFPGA等の設定可能若しくは再設定可能なハードウェア回路構成で実装され得ることも除外されない。

【0041】

入力レベルにディザ(小さな偏差)を加えることによって、出力光レベルの不均一な間隔によって引き起こされる明滅が軽減され得る。例示的な用途では、各Ternary Manchesterシンボルが1msの持続時間を有し、PWM周波数が16kHzであり、即ち、特定の変調デューティサイクル入力が選択されると、16個の連続するPWM周期に関して同じデューティサイクル入力が使用される(ディザがない場合)。これら16個のデューティサイクル入力を、全てのTernary Manchesterシンボルに関してディザリングすることによって、各シンボルに関して平均光出力が生成され、この光出力は、ディザなしのバージョンよりもはるかに規則的に間隔を空けられ、従って明滅を緩和する。同様の手法が、他の符号化方式に関しても使用され得る。

【0042】

論じられるように、マイクロプロセッサによって制御された入力と平均光レベル出力との間の実際の伝達関数は、例えば図4におけるように、局所的小規模の異形状によって特徴付けられる。以下では、マイクロプロセッサによって制御された入力と光出力との間の「線形化平均」伝達関数を生成するためにディザを使用する。

【0043】

例えば、図10の例を参照する。ここでは、デューティサイクルにおける水平方向広がりの長さ(即ちディザの幅)が、 $P_{b_c}$ の半分であり、ここで、 $P_{b_c}$ は、「降圧サイクルインターバル」の「周期」である。各入力デューティサイクル $d_{c_i n}$ は、一方が $P_{b_c}$ の1/4だけ右にシフトされ、他方が $P_{b_c}$ の1/4だけ左にシフトされた2つの入力の平均によって置き換えられ得る(図10において、各中央の点線を挟んで両側にある2つの鉛直な点線を参照されたい。それらは、2つのシフトされた位置と、それらの間の概

10

20

30

40

50

念上の中央位置とを表す）。この場合、各対の平均が、図10での5つの太い水平線によって表される出力を生成し、これらは、各連続する対の間で等しい間隔を有し、即ち明滅がないことが示され得る。ここで、これは、あらゆる平均光出力及び任意の妥当な変調深さに関して当てはまる。

#### 【0044】

図10の例では、降圧サイクル周期  $P_{bc} = 0.05$  であり、変調深さ = 0.24 であり、ディザ間隔は 0.025 である。2レベルディザを用いない場合のDC成分は、0.199 であると判明し、2レベルディザを用いた場合のDC成分は、 $-8.8818 \times 10^{-16}$  と判明した。従って、周期的な非線形性の乱れを線形化するための更に単純なディザの効果を見ることができる。

10

#### 【0045】

しかし、2レベルディザリングを使用する上述の実施形態では、PWMデューティサイクルを制御する（及びディザを発生する）制御装置2で  $P_{bc}$  が分かっている場合、且つ水平方向広がりの長さが  $P_{bc}$  の半分に等しい場合にのみ、残留する明滅がないという結果が得られる。

#### 【0046】

これらの条件の任意のものが当て嵌まらない場合、通常、伝達関数の完全な線形化は得られず、減少された残留する明滅があり得る。この場合、nレベルディザが役立つ。

#### 【0047】

図11は、nレベルディザに関する状況を示し、 $n = 4$  である。 $P_{bc}$  が正確には分かれていなくてさえ、又は水平方向広がりの長さ（ディザ幅）が  $P_{bc}$  の半分でない場合でさえ、やはり明滅の大幅な減少が得られることが分かる。

20

#### 【0048】

図11の例では、降圧サイクル周期  $P_{bc} = 0.05$  であり、変調幅 = 0.24 であり、ディザ間隔は 0.025 である。4レベルディザを用いない場合のDC成分は、0.199 であると判明し、4レベルディザを用いた場合のDC成分は、実質的に 0 と判明した。

#### 【0049】

幾つかの実施形態では、制御装置2は、以下のものの1つ、幾つか、又は全てに従ってディザリングを実施するように構成される。

30

- 符号化光の伝送される変調シンボルそれぞれに対応する入力デューティサイクルにnレベルディザリングを施す；

- ディザ振幅の各連続する対の間隔は、 $P_{bc} / n$  にできるだけ近く、ここで、 $P_{bc}$  は、デューティサイクル入力と光出力とのマッピングにおける循環的な異形状に対応する（例えば、図4参照）；

- 単一のシンボルに属するn個のディザ振幅の集合の各要素は、均一な確率  $1/n$  で使用される；

- 一般に、より大きなnは、より小さなnに比べて良い成果をもたらす傾向がある；

- $P_{bc}$  に対する水平方向広がり長さ（全体のディザ幅）の比が分かっている場合、 $k/n$  がその比に近くなるような  $k (1 \leq k \leq n - 1)$  が存在するようにnを選択することが有利である；

- $n = 4$  の場合、4つの連続するPWMシンボルからなるグループが存在し、各グループは、4つの異なるディザリングされたPWM振幅を有する；及び/又は

- $n = 4$  の場合、振幅（又はデューティサイクル）の小さい方から順に、「0」、「1」、「2」、及び「3」が、单一のシンボルに属する4つの異なるディザリングされたPWM振幅に対応する場合、これらのディザリングがグループ内で一時的に現れるべき順序は、「0」、「3」、「2」、「1」である。

40

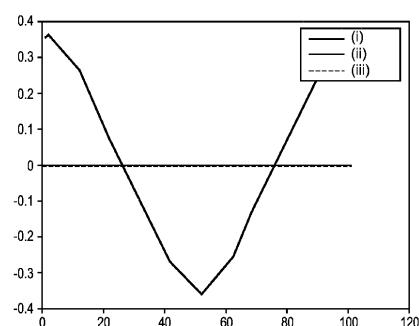

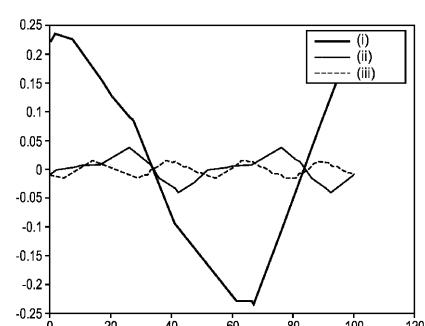

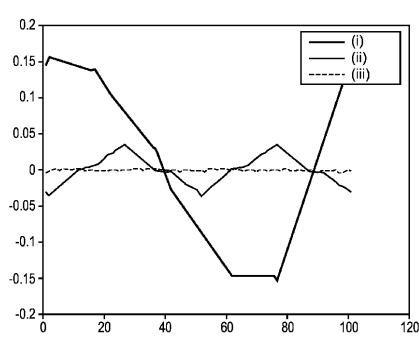

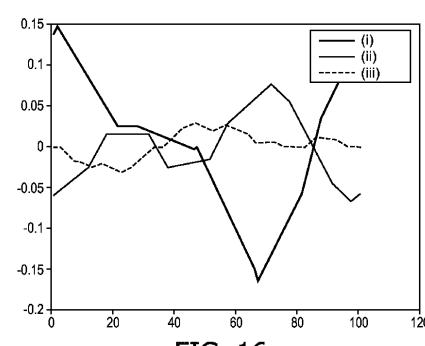

#### 【0050】

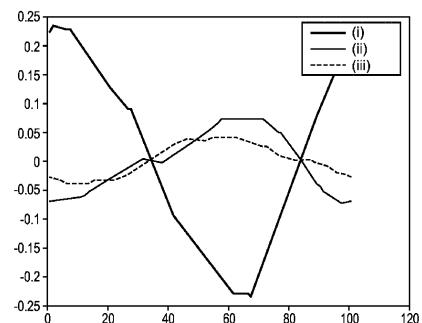

図12～図17は、パラメータの様々な設定に関する（オールゼロのパターン、即ち9個の「0」からなる）V2フォーマットの所与のパケットのDCアンバランス（発生され

50

る明滅を反映する)を示す。パラメータの各集合に関して、「0」入力の値(図6参照)は、1周期 $P_{b_c}$ にわたって変えられる。太い実線(i)は、ディザがない場合を表し、太くない実線(ii)は、2レベルディザを表し、点線(iii)は、4レベルディザを表す。

#### 【0051】

図12は、水平方向広がり=0.5 $P_{b_c}$ を有する例を示し、 $P_{b_c}$ は正確に推定されており、変調深さは0.24である。

#### 【0052】

図13は、水平方向広がり=0.5 $P_{b_c}$ を有する例を示し、 $P_{b_c}$ は正確に推定されており、変調深さは0.28である。

10

#### 【0053】

図12において、既に2レベルディザがDC成分を0に減少していることに留意されたい。これは、 $P_{b_c}$ が正確に推定されており、ディザの水平方向広がりが正確に $P_{b_c}$ の半分であるからである。また、図12において、変調深さは、整数の降圧周期を含まないように選択されることに留意されたい。図13での変調深さ(0.28)は、ディザリングが使用されない場合の、生じ得る最悪のDC成分を与えるように選択されている。

#### 【0054】

図14は、水平方向広がり=0.25 $P_{b_c}$ を有する例を示し、 $P_{b_c}$ は正確に推定されており、変調深さは0.28である。

#### 【0055】

図15は、水平方向広がり=0.33 $P_{b_c}$ を有する例を示し、 $P_{b_c}$ は正確に推定されており、変調深さは0.28である。

20

#### 【0056】

図16は、水平方向広がり=0.33 $P_{b_c}$ を有する例を示し、 $P_{b_c}$ は20%減で推定されており、変調深さは0.24である。

#### 【0057】

図17は、水平方向広がり=0.33 $P_{b_c}$ を有する例を示し、 $P_{b_c}$ は20%減で推定されており、変調深さは0.28である。

#### 【0058】

注:上記のこととは、 $P_{b_c}$ に基づいてディザリングが適応され得る様な例を提示している。 $P_{b_c}$ は、降圧サイクル「周期」であり、即ち、デューティサイクルDと出力レベルLとの関係における循環的な不整(又は「凹凸」)の、デューティサイクル領域での規則的な反復のインターバルである(例えば図5~図7参照)。上でも述べたように、幾つかの実施形態では、ディザリングは、降圧周波数 $f_{b_{u c k}}$ (又は第2の周波数)、即ち時間領域におけるより高周波数の変調(又は「ウィグル」)の周波数のフィードバックに基づいて適応される(図4参照)。更に、デューティサイクル領域内の規則的なインターバル $P_{b_c}$ が時間領域内の降圧周波数 $f_{b_{u c k}}$ (又は第2の周波数)に関係付けられる方法が説明されており、従って、 $f_{b_{u c k}}$ を知ることが、 $P_{b_c}$ に関して表された例に基づくディザリングインターバルの適応を可能にすることが分かる。

30

#### 【0059】

特に、幾つかのデューティサイクル値では、PWM波形の立下りエッジがより高周波数の降圧周波数「ウィグル」のトラフと一致し(図4参照)、他のデューティサイクル値では、PWM波形の立下りエッジが降圧周波数のピークと一致するので、図5~図7で示される規則的な不整が生じることを上で説明した。従って、デューティサイクル値を0%から100%までスイープし、それによりPWM波形の立下りエッジが図4で左から右にスイープすることを考える場合、PWM波形の立下りエッジは、規則的に、降圧周波数のトラフに当たり、次いで降圧周波数のピーク、次いで降圧周波数の別のトラフ、次いで降圧周波数の別のピークに当たり、以下同様である。従って、デューティサイクルを水平軸としてデューティサイクルと出力レベルとの関係がプロットされるとき、図5~図7の規則的な「凹凸」が現れる。

40

50

## 【0060】

$P_{b_c}$  と  $f_{b_{u_c k}}$ との関係は、この説明から当業者によって容易に理解されよう。デューティサイクルを再び 0 % から 100 % ヘスイープすることを考えると、これは、 PWM 波形の立下りエッジを、 1 つの PWM サイクル  $T$  (これも図 4 を参照されたい) の範囲にわたって左から右にスイープすることに対応する。このプロセス中、降圧周波数波形の  $T_{b_{u_c k}}$  ピークが見られ、ここで、  $T_{b_{u_c k}}$  は、時間領域内の降圧周波数  $f_{b_{u_c k}}$  の周期  $1 / f_{b_{u_c k}}$  である。即ち、デューティサイクルが変化するとき、 1 つの PWM 周期  $T$  につき幾つかの  $T_{b_{u_c k}}$  ピークが見られ、従って、デューティサイクル軸 (図 5 ~ 図 7 ) に沿って、凹凸のパターンがインターバル  $P_{b_c} = T_{b_{u_c k}} / T$  で反復する。

## 【0061】

従って、上記の  $P_{b_c}$  に基づいてディザを設定する例と合わせて、ディザリングを適応させるために降圧周波数 (又は第 2 の周波数) のフィードバックが使用され得る様が理解されよう。

10

## 【0062】

上記の実施形態は、例として述べられているにすぎないことを理解されたい。

## 【0063】

例えば、上の説明は降圧コンバータに関して述べられているが、パルス幅変調のオンフェーズ中に PWM 周波数よりも高い周波数で電流が供給される任意のドライバで同様の問題が生じ得る。即ち、フライバックコンバータ等の他のドライバが高調波又は振動を受けることがあり、これは、パルス幅変調周波数でのスイッチングと相まって、非線形性等の問題を生じ得る。更に、本明細書で開示される技法は、符号化光以外の他の用途、又は LED 若しくは光源以外の他の負荷に適用可能であり得る。例えば、照明器具によって放出される照光をより線形に減光すること、又は、モータの速度若しくは幾つかの他の負荷の出力をより線形に制御することが望まれることがある。更に、全ての実施形態において、フィードバックチャネルを介する周波数のフィードバックを作動させる必要は必ずしもなく、更にはそもそも何らかのフィードバックを作動させる必要は必ずしもない。ディザリングは、降圧スイッチング周波数が大まかに (例えば 50 % の誤差で) しか分かっていない場合でさえ、それでも線形性を改良する良い成果をもたらすことができ、実際、ディザソリューションは十分にロバストであり、従って、フィードバックがない場合でさえ小さな変化に対処することができる。

20

## 【0064】

開示される実施形態に対する他の変形は、図面、本開示、及び添付の特許請求の範囲の検討から当業者によって理解され、特許請求される発明を実践する際に実施され得る。特許請求の範囲において、用語「備える」は、他の要素又はステップを除外せず、不定冠詞「a」又は「an」は、複数を除外しない。单一のプロセッサ又は他のユニットが、特許請求の範囲に記載される幾つかの要素の機能を実現することができる。特定の手段が相互に異なる従属請求項に記載されていることだけでは、これらの手段の組合せが有利に使用され得ないことを示さない。コンピュータプログラムは、他のハードウェアと共に供給される、又は他のハードウェアの一部として供給される光記憶媒体やソリッドステート媒体等の適切な媒体に記憶 / 分散されてよいが、インターネット又は他の有線若しくは無線電気通信システムを介する形態等、他の形態で分散されてもよい。特許請求の範囲内の任意の参照符号は、範囲を限定するものとみなされるべきではない。

30

40

【図1】

FIG. 1

【図2】

FIG. 2

【図4】

FIG. 4

【図3】

FIG. 3

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

FIG. 11

【図 12】

FIG. 12

【図 13】

FIG. 13

【図 15】

FIG. 15

【図 14】

FIG. 14

【図 16】

FIG. 16

【図 17】

FIG. 17

---

フロントページの続き

(72)発明者 バッゲン コンスタント ポール マリエ ジョゼフ

オランダ国 5656 アーエー アイントホーフェン ハイ テク キャンパス 5

(72)発明者 ナイセン ステファヌス ヨセフ ヨハネス

オランダ国 5656 アーエー アイントホーフェン ハイ テク キャンパス 5

審査官 佐藤 匡

(56)参考文献 米国特許出願公開第2013/0049634(US, A1)

特開2011-010466(JP, A)

特開2008-167507(JP, A)

特表2013-546127(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155

H05B 37/02

H04B 10/116