(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4904000号

(P4904000)

(45) 発行日 平成24年3月28日(2012.3.28)

(24) 登録日 平成24年1月13日(2012.1.13)

(51) Int.Cl.

F 1

G02B 6/122 (2006.01)

G02B 6/12 (2006.01)G02B 6/12

G02B 6/12A

F

請求項の数 14 (全 8 頁)

(21) 出願番号 特願2004-565218 (P2004-565218)

(86) (22) 出願日 平成15年12月5日 (2003.12.5)

(65) 公表番号 特表2006-507542 (P2006-507542A)

(43) 公表日 平成18年3月2日 (2006.3.2)

(86) 國際出願番号 PCT/US2003/038694

(87) 國際公開番号 WO2004/061498

(87) 國際公開日 平成16年7月22日 (2004.7.22)

審査請求日 平成17年5月24日 (2005.5.24)

(31) 優先権主張番号 10/328,478

(32) 優先日 平成14年12月24日 (2002.12.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 591003943

インテル・コーポレーション

アメリカ合衆国 95052 カリフォルニア州・サンタクララ・ミッション・カレッジ・ブーレバード・2200

(74) 代理人 100104156

弁理士 龍華 明裕

(72) 発明者 ソー ダニエル

アメリカ合衆国、94303 カリフォルニア州、パロアルト、アメリカリヨ アベニュー 1065

(72) 発明者 ヨー チャン ホ

アメリカ合衆国、95119 カリフォルニア州、サンノゼ、マーティンペイイル レーン 268

最終頁に続く

(54) 【発明の名称】垂直テーパ導波路

## (57) 【特許請求の範囲】

## 【請求項1】

Yスプリッタの複数の枝間に嵌合して挿入損失を減少させる光導波路であつて、第1の端部において第1の厚みを有し、第2の端部における第2の厚みへ減少する第1の区分と、

前記第1の区分に一体化した、前記第2の厚みに等しい実質的に一定の厚みを有する第2の区分と

を備え、

前記第2の区分が、前記第1の区分へ向けて先細って形成された複数の側壁を有する切り欠きを備え、

前記第2の区分の終端部が垂直な断面を有する光導波路。

## 【請求項2】

前記切り欠きの頂端が、形状が三角形、曲線的、および平坦のうちの1つである、請求項1に記載の光導波路。

## 【請求項3】

前記第1の区分の前記第1の厚みが、前記第2の厚みに向けて線形、放物線状、および指數関数的のうちの1つのように減少する、請求項1に記載の光導波路。

## 【請求項4】

前記第2の区分の前記複数の側壁が、線形、放物線状、および指數関数的なテーパのうちの1つを備える、請求項1に記載の光導波路。

**【請求項 5】**

前記第1および前記第2の区分が、シリコンオンインシュレータ、シリカ、シリコンオキシナイトライド、リン化インジウム、および族Ⅲ-ⅤおよびⅢ-Ⅵから他のいかなる化合物半導体材料のうちの1つを備える、請求項1に記載の光導波路。

**【請求項 6】**

前記第2の区分は、フォトレジストおよび反応性イオンエッティングにより製造される請求項1に記載の光導波路。

**【請求項 7】**

光導波路の複数の指状構造の間の挿入損失を減少させるための方法であって、導波路の複数の指状構造の間のスラブに対向し、前記スラブに最も近く、前記スラブの高さにほぼ等しく、第1の厚みから第2の厚みへ減少する、第1の区分を設ける段階と、

10

前記第1の区分と一体化して前記導波路の前記複数の指状構造の間に、前記第2の厚みに等しい実質的に一定の厚みを有する第2の区分を設ける段階と、

前記第2の区分内に、1つの中心軸に沿って、前記第1の区分へ向けて先細って形成された複数の側壁を備える切り欠きを設ける段階と

を備え、

前記第2の区分の終端部が垂直な断面を有する、

挿入損失を減少させるための方法。

**【請求項 8】**

前記第1の区分の前記第1の厚みを、線形、放物線状、および指数関数的のうちの1つで前記第2の厚みに減少させる段階を更に備える、請求項7に記載の挿入損失を減少させるための方法。

20

**【請求項 9】**

前記切り欠きの前記複数の側壁を、前記第1の区分に向けて、線形、放物線状、および指数関数的のうちの1つで先細って形成させる段階を更に備える、請求項8に記載の挿入損失を減少させるための方法。

**【請求項 10】**

前記切り欠きの頂端を、三角形状、曲線状、および平坦のうちの1つに形成する段階を更に備える、請求項8に記載の挿入損失を減少させるための方法。

**【請求項 11】**

前記第1および前記第2の区分を、シリコンオンインシュレータ、シリカ、シリコンオキシナイトライド、リン化インジウム、および族Ⅲ-ⅤおよびⅢ-Ⅵから成る他の任意の化合物半導体材料のうちの1つから形成する段階を更に備える、請求項7に記載の挿入損失を減少させるための方法。

30

**【請求項 12】**

前記第2の区分は、フォトレジストおよび反応性イオンエッティングにより製造される請求項7に記載の方法。

**【請求項 13】**

光導波路であって、

スラブと、

40

前記スラブから延びる少なくとも2つの指状構造と、

前記指状構造の間の挿入損失を低減させる垂直テーパ部と、

を備え、

前記垂直テーパ部が、

第1の端部において第1の厚みを有し、第2の端部における第2の厚みへと減少する第1の区分と、

前記第1の区分に一体化した、前記第2の厚みに等しい実質的に一定の厚みを有する第2の区分とを有し、

前記第2の区分が、前記第1の区分へ向けて先細って形成された複数の側壁を有する切り欠きを有し、

50

前記第2の区分の終端部が垂直な断面を有する光導波路。

【請求項14】

前記切り欠きの頂端が、形状が三角形、曲線的、および平坦のうちの1つである、請求項13に記載の光導波路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の1つの実施形態は、複数の光学平面光波回路に関し、より特定的には、1つのアレイ導波路格子（AWG）の1つのスラブ導波路インターフェイスにおける複数の導波路間にあって、挿入損失を緩和するような1つの垂直テープ導波路に関する。 10

【背景技術】

【0002】

波長分割多重（WDM）は、単一のファイバを1つの高性能情報管に変貌させた。この変貌を生じさせた数多くのデバイスのうち、アレイ導波路格子（AWG）は、重要な構成要素の一つであった。複数のAWGは、数多くの互いに異なる周波数チャンネルを1つの単一のファイバ上に同時に多重化および多重分離化することが可能な、非常に汎用性のあるデバイスである。複数の他の平面光波デバイスと共に一体化すると、AWGは、光交差接続および光アドノドロップ多重化などの、数多くの極めて重要な機能を行いうる。複数のAWGの性能を向上させる継続的な動きがある。AWGの挿入損失は、システム内の電力了を決定する複数の重要な性能要素の1つである。 20

なお、本出願に対応する外国の特許出願においては下記の文献が発見または提出されている。

【特許文献1】米国特許第6587604号明細書

【特許文献2】特開平9-061652号公報

【特許文献3】米国特許出願公開第2003/0223719号明細書

【特許文献4】欧州特許出願公開第0881512号明細書

【特許文献5】英国特許出願公開第227854号明細書

【発明の開示】

【発明が解決しようとする課題】

【0003】

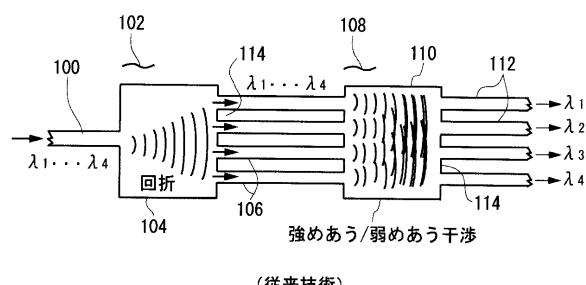

図1は、1つの基本的なAWGがどのように動作して複数のチャンネルを多重分離化するかの1つの例を示す。簡潔にいえば、1つのAWGは、入力／出力導波路と、2つのスラブ領域と、付近の導波路に対して一定の路長差を有するであろう平面導波路の1つの位相アレイとを備えることがある。この例において、1つの入力導波路100は、同時に4つの多重化されたチャンネルを搬送する。もちろん、実際には、このチャンネル数の何倍ものチャンネルが可能である。各チャンネルは、1, 2, 3, および4によって示される、1つの異なる波長または光色によって表される。入力導波路100からの光は、第1のスラブ領域102に入る。入力導波路100は、スラブ102の1つの第1の端部104に結合される。複数の導波路のアレイ106が、スラブ102の反対側から放射状に広がる。 40

【0004】

入力導波路100からスラブ領域102へ入力された光は、限定されたモード寸法を有する誘導モードとして入る。理想的には、入力導波路スラブインターフェイスは、波面が1つの平面波として現れてスラブ102の出力端の曲率に合致するようなやり方で、この誘導モードを変換するように設計される。複数の出力導波路106は、結果生じた光波を捕らえて、それを1つの第2のスラブ領域108へ搬送する。各出力導波路106で搬送された光は、1つの第2のスラブ領域108に入力される。各入力は、1, 2, 3, および4の成分を含有する光信号を搬送し、再び第2のスラブ領域108に誘導モードとして入る。第2のスラブ領域108において、これら複数の信号は回折されて、各出力導波路112で搬送される回折結果の信号が1つの単一のチャンネルまたは波長を備え 50

るよう、強めあうように、または弱めあうように互いに干渉し合う。この仕組みは、反対方向にも同様に働いて、複数のチャンネルを1つの単一の導波路上で多重化する。

#### 【0005】

挿入損失は、典型的には、1つの光信号が1つの媒体または導波路から次に進むかまたは挿入される場合に生じる。いずれの移行点でも、何らかの損失が通常生じる。例えば、誘導媒体内の屈折率の違いによって生じる反射、導波路の構造が不完全なことによる散乱、誘導媒体の複数の物理的寸法の急激な変化による回折が、損失をもたらす。1つのAWGの場合には、挿入損失の複数の主要な寄与の1つが、スラブおよび導波路間の移行のインターフェイスで生じる。例えば、さらに図1を参照して、複数の導波路114間の領域に当たる光信号の部分は失われやすく、システムの総挿入損失をもたらす。

10

#### 【0006】

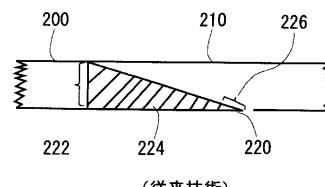

複数のAWGに対する改良がなされて、複数の挿入損失を緩和してきた。例えば、図2Aに示すように、AWGの1つの部分は、1つのスラブ200と、複数の導波路202～210とを備える。加えて、1つの垂直テーパ導波路220が、各複数の導波路202～210間のスラブ導波路インターフェイスに形成される。垂直テーパ導波路220は、基本的に、スラブ220の高さに一致する1つの垂直な高さを有し、スラブ220から最も遠くにあるその終点224において1つのほぼゼロ高さに線形に減少するスラブ200に最も近い点222に1つの楔形状部分を備える。理論上は、そうでなければフィンガー202～210間で失われるであろう光が、代わりに、垂直テーパ導波路220に入り、そこにおいて、少なくとも光の1つの部分が平行に導波路202～210に向かされることにより、挿入損失が減少する。

20

#### 【0007】

導波路220の形状は、図2Bにも示されており、そこでは、導波路210の横に並んで伸びるテープ導波路220の垂直断面図を示されている。スラブ200に最も近いその第1の端222では、テープ導波路220はスラブ200の高さとほぼ同一の1つの高さを有する。導波路の高さは、その終端部224に向かって線形に減少し、そこにおいて、理想的には、テープ導波路220の高さまたは厚みは1つのゼロ厚みに近づく。しかしながら、実際の製造における制約からして、これは不可能である。よって、図2Bに示すように、導波路の厚みが現在の製造性能またはそれ以下の1つの高さにまで減少する場合に、不均一またはギザギザのある1つの断面226が生じてしまう。これら複数の不完全さ226が散乱を生じさせ、挿入損失をもたらす。

30

#### 【発明を実施するための最良の形態】

#### 【0008】

本発明の複数の実施形態の1つは、1つのアレイ導波路格子(AWG)の複数の導波路間に用いられるような1つの垂直テープ導波路を備える。導波路は、いかなる特別な複数の製造ツールまたは装置を必要とせず、例えばフォトレジストおよび反応イオンエッティング(RIE)手法のような伝統的な方法を用いて製造されてもよい。

30

#### 【0009】

フォトレジストフィルムが薄くなるにつれて、フィルムは1つのある最小限の厚みを超えると破れことが多い事は周知である。例えば、1つの特定のフォトレジストについての破壊厚みは、0.3 μmであってもよい。この最小限の厚み以下では、フォトレジストは、もはや、均一の厚みを有する1つの単一の均質なフィルムではない場合がある。フィルムのいかなる破れも、製造中に伝達されて、図2Bの226によって示すようなエッティングされた複数の表面上に更なる粗さを生じさせる。

40

#### 【0010】

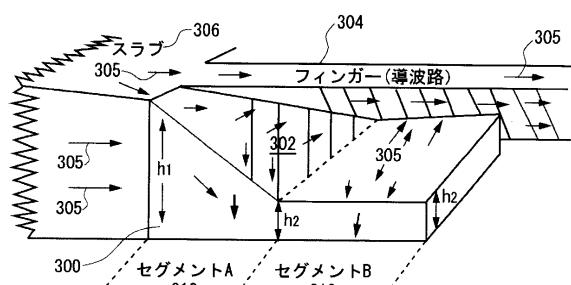

1つの実施形態によれば、1つの粗くエッティングされた表面の生成を防止するために、フォトレジストは、1つの最小限の厚みを維持する必要がある。ここで図3を参照して、本発明の一実施形態に係る1つの垂直テープ導波路300を示す。図示のように、導波路300は、1つのアレイ導波路格子(AWG)の複数の導波路304およびスラブ306間に嵌合するように形成された1つの水平断面302を有する。しかしながら、垂直テー

50

パは2つの区分を有し、区分A310および区分B312として示されている。区分A310は、スラブ306の高さとほぼ等しい1つの第1の高さまたは高さ $h_1$ から1つの第2の高さ $h_2$ へ徐々にまたは滑らかに減少する1つの垂直テーパを有する1つの垂直断面を有する。第2の高さ $h_2$ は、現在の製造技術が確実に解決しうる厚みに作られる。例えば、ゲルマニウムが添加された1つのシリカ平面光波回路については、 $h_1$ および $h_2$ についての1つの典型的な高さは、それぞれ約6.0 μmおよび2.0 μmである。

#### 【0011】

区分B312は、 $h_2$ と等しい実質的に一定の1つの高さを有する。複数の矢印305によって示される、導波路300に入る光は、平行に隣接する複数のフィンガー304に向かう傾向がある。第2の区分312を平坦にして1つの実質的に一定の高さまたは厚みにするこの仕組みは、終端部の不完全さ(図2Bの226)を防ぎ、挿入損失を改良しうる。区分B312は、平坦で緩やかな1つの移行を与えるので、散乱損失を減少させ、よってさらに挿入損失を減少させる。さらに、この設計は、後続の上部被膜配置のアスペクト比を減少させ、よって複数のギャップ充填問題を減少させることができる。

#### 【0012】

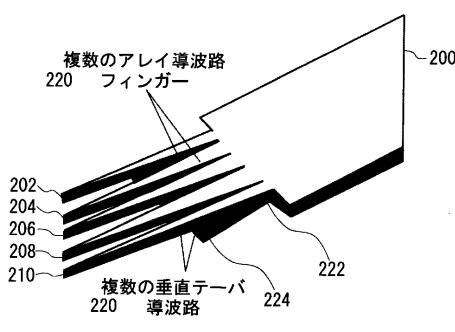

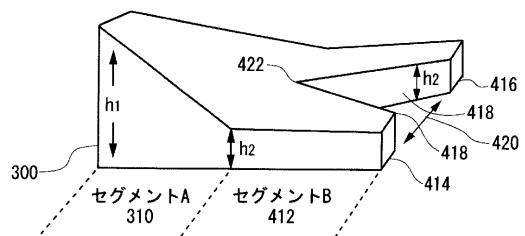

図4は、図3に示したのと同様の本発明のさらに他の実施形態を示す。上記と同様に、区分A310は、1つの垂直テーパを有し、スラブ306インターフェイスからの距離が増加するに従って厚みは線形に減少する。加えて、区分B412は、実質的に一定の1つの厚み $h_2$ を維持しつつ、フォーク形になっており、平行にテーパ状の複数の側壁418を含んで、その結果、燕尾形状となっている。図示のように、フォーク形の区分B412は、2つの突起414および416を有してもよい。各突起414および416は、区分B412内に傾き返して1つの三角形の頂点422に向かう1つの内側壁418を有する。これにより、1つの楔形状の切り欠き420が、1つの中心軸に沿って形成される。突起414および416は共に、 $h_2$ に等しい実質的に均一または一定の1つの厚みを有する。この燕尾形状は、導波路300に入るさらに多くの光を平行に、隣接する複数の導波路(図3の304)に対して向けさせることにより、挿入損失をさらに減少させる。

#### 【0013】

内側壁角418の1つの例として、ゲルマニウムが添加されたシリカ導波路については、図2Aの従来技術で説明したように、垂直テーパ導波路は長さが約180 μmである。これが1つの基準として用いられると、図4の区分310の長さは、約120 μmであつてもよく、なぜならば、区分412の最小限の厚みが約120 μmであり、区分412の最小限の厚みが約2 μmとなるからである。複数の導波路が30 μmずつ離れており、かつ2つの突起414および416の複数の端部の最小幅が2 μmであるとする。この仮説例について、側壁418の角度は、約25度であってもよい。

#### 【0014】

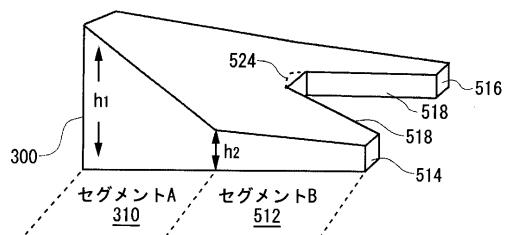

図5は、本発明の追加の複数の実施形態を示す。図4においてと同様に、区分B512は、燕尾形状を有するフォーク形状となっている。図示のように、フォーク形状の区分B512は、2つの突起514および516を有する。各突起514および516は、区分B412内に傾き返して1つの内側壁518を有する。しかしながら、図4に示す実施形態とは異なり、複数の内側壁518は、1つの三角形の頂点で接触せず、むしろ、それぞれは、1つの平坦な頂端522を形成する1つの平坦な垂直面で終端する。代わりに、複数の側壁が接触する点は、曲線的であるものを形成してもよく、または点線524で示すような1つの円状の頂端を有してもよい。これら複数の変更は共に、製造を簡素化する。なぜならば、これらの複数の形状が要求する精度は、図4に示す三角形の頂点422よりも低いからである。

#### 【0015】

図3～5において、 $h_1$ から $h_2$ への区分Aの厚みの変化および区分Bの幅の変化は線形に示しているが、変化は指數関数的、放物線状、または他のそのようないかなる関数のようであってもよい。

#### 【0016】

10

20

30

40

50

本発明の複数の実施形態について、複数のAWGを用いて説明してきたが、開示された複数の導波路は、数多くの他の複数の光学デバイスに組み込まれることができる。実際、1つのY分岐構造を有するあらゆる複数の平面光波構成要素はこのテーパ設計を用いることから利点を得る。例えば、複数の垂直テーパ導光路を用いて、1つのY分岐スプリッタの挿入損失を減少させることができる。

## 【0017】

加えて、開示された複数の導光路は、様々な複数の材料から作成できる。例えば、シリコンオンインシレータ、シリカ、シリコンオキシナイトライド、リン化インジウム、または族I II I - VおよびI I - V Iからの他のいかなる化合物半導体材料が含まれる。

## 【図面の簡単な説明】

10

## 【0018】

【図1】複数のアレイ導波路格子(AWG)の多重化/多重分離化動作を示す1つの図である。

【図2A】挿入損失を緩和する複数のフィンガー間の複数の垂直テーパ導波路を含む1つのAWGを示す1つの図である。

## 【図2B】図2Aに示すAWGの1つの横断面図である。

【図3】本発明の一実施形態に係る、1つの垂直テーパ導波路の1つの平面図である。

【図4】本発明の他の実施形態に係る、1つの垂直テーパ導波路の1つの平面図である。

【図5】本発明のさらに他の実施形態に係る、1つの垂直テーパ導波路の1つの平面図である。

20

【図1】

(従来技術)

【図2B】

(従来技術)

【図3】

【図2A】

(従来技術)

【図4】

【図5】

---

フロントページの続き

審査官 山本 元彦

(56)参考文献 特開2000-147283(JP,A)

特開2002-228867(JP,A)

特開平08-327836(JP,A)

A.Sugita et al., IEEE Photonics Technology Letters, 2000年 9月, Vol.12, No.9, p. 1180-1182

(58)調査した分野(Int.Cl., DB名)

G02B 6/12-6/14

JSTPlus(JDreamII)

JST7580(JDreamII)