(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6374596号

(P6374596)

(45) 発行日 平成30年8月15日(2018.8.15)

(24) 登録日 平成30年7月27日(2018.7.27)

(51) Int.Cl.

F 1

**H03H 17/02 (2006.01)**

H03H 17/02 17/00 6 7 1 Z

**H03H 17/00 (2006.01)**

H03H 17/00 6 2 1 E

H03H 17/00 6 1 1 A

請求項の数 17 (全 29 頁)

(21) 出願番号 特願2017-504028 (P2017-504028)

(86) (22) 出願日 平成27年5月28日 (2015.5.28)

(65) 公表番号 特表2017-528047 (P2017-528047A)

(43) 公表日 平成29年9月21日 (2017.9.21)

(86) 國際出願番号 PCT/US2015/032833

(87) 國際公開番号 WO2016/018501

(87) 國際公開日 平成28年2月4日 (2016.2.4)

審査請求日 平成30年5月28日 (2018.5.28)

(31) 優先権主張番号 14/444,612

(32) 優先日 平成26年7月28日 (2014.7.28)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591025439

ザイリンクス インコーポレイテッド

X I L I N X I N C O R P O R A T E D

アメリカ合衆国 カリフォルニア州 95

124-3400 サンホセ ロジック

ドライブ 2100

(74) 代理人 110002077

園田・小林特許業務法人

(72) 発明者 コープランド, グレゴリー シー.

アメリカ合衆国 カリフォルニア 951

24, サンノゼ, ロジック ドライ

ブ 2100

審査官 竹内 亨

最終頁に続く

(54) 【発明の名称】波高率低減

## (57) 【特許請求の範囲】

## 【請求項 1】

波高率低減(CFR)のためのシステムであって、

入力信号( $x_k$ )を受信するように構成されたピーク検出器と、ウインドウ利得( $G_k$ )およびフィルタ長さに基づいてスケーリングファクタを生成するように構成された最大実行フィルタであって、前記ウインドウ利得( $G_k$ )は前記入力信号( $x_k$ )およびしきい値( $T$ )に基づく、最大実行フィルタと、前記スケーリングファクタおよび前記フィルタ長さに基づいて利得補正( $F_k$ )を生成するように構成されたウインドウCFR利得フィルタと、遅延入力信号を生成するために前記入力信号( $x_k$ )を遅延させるように構成されたディレイと、ピーク補正值を取得するために前記利得補正( $F_k$ )と前記遅延入力信号とを乗算するように構成された乗算器と、前記ピーク補正值および前記遅延入力信号に基づいて出力信号( $y_k$ )を決定するように構成された加算器と、

を備え、

前記ピーク検出器、前記最大実行フィルタ、前記ウインドウCFR利得フィルタ、前記ディレイ、前記乗算器、前記加算器が、少なくとも1つの集積回路において実装される、システム。

## 【請求項 2】

10

20

前記最大実行フィルタは、前記フィルタ長さにわたって前記ウインドウ利得 ( $G_k$ ) の最大利得を決定することにより、前記スケーリングファクタを生成するように構成される、請求項 1 に記載のシステム。

**【請求項 3】**

前記ウインドウ C F R 利得フィルタは、ハニングウインドウフィルタを含む、請求項 1 に記載のシステム。

**【請求項 4】**

前記ウインドウ C F R 利得フィルタは、ブラックマンウインドウフィルタを含む、請求項 1 に記載のシステム。

**【請求項 5】**

前記フィルタ長さは N サンプルに対応し、N は整数である、請求項 1 に記載のシステム。

**【請求項 6】**

前記ウインドウ C F R 利得フィルタは  $N / 2$  を中心とする、請求項 5 に記載のシステム。

**【請求項 7】**

前記利得補正 ( $F_k$ ) は連続関数を含む、請求項 1 に記載のシステム。

**【請求項 8】**

前記ウインドウ利得 ( $G_k$ ) を提供するためのピーカスケーリングユニットをさらに備える、請求項 1 に記載のシステム。

**【請求項 9】**

前記少なくとも 1 つの集積回路は、少なくとも 1 つのフィールドプログラマブルゲートアレイ (FPGA) を含む、請求項 1 に記載のシステム。

**【請求項 10】**

前記ピーカ検出器は、

前記入力信号 ( $x_k$ ) に関する多項式フィットを決定するように、

ピーカ位置を決定するように、および、

前記多項式フィットから前記ピーカ位置での信号のマグニチュードを決定するように、構成される、請求項 1 に記載のシステム。

**【請求項 11】**

波高率低減 (C F R) のための方法であって、

ピーカ検出器によって入力信号 ( $x_k$ ) を受信すること、

最大実行フィルタを使用し、ウインドウ利得 ( $G_k$ ) およびフィルタ長さに基づいてスケーリングファクタを生成することであって、前記ウインドウ利得 ( $G_k$ ) は前記入力信号 ( $x_k$ ) およびしきい値 ( $T$ ) に基づく、生成すること、

ウインドウ C F R 利得フィルタを使用し、前記スケーリングファクタおよび前記フィルタ長さに基づいて利得補正 ( $F_k$ ) を生成すること、

遅延入力信号を取得するために、ディレイによって前記入力信号 ( $x_k$ ) を遅延させること、

乗算器を使用し、ピーカ補正值を取得するために前記利得補正 ( $F_k$ ) と前記遅延入力信号とを乗算すること、ならびに、

出力信号 ( $y_k$ ) を取得するために前記ピーカ補正值を前記遅延入力信号に加算すること、

を含み、

前記ピーカ検出器、前記最大実行フィルタ、前記ウインドウ C F R 利得フィルタ、前記ディレイ、前記乗算器、またはそれらの任意の組み合わせは、少なくとも 1 つの集積回路において実装される、方法。

**【請求項 12】**

前記スケーリングファクタを生成する行為は、前記フィルタ長さにわたって前記ウインドウ利得 ( $G_k$ ) の最大利得を決定することを含む、請求項 11 に記載の方法。

10

20

30

40

50

**【請求項 1 3】**

前記ウインドウ C F R 利得フィルタは、ハニングウインドウフィルタまたはブラックマングウンドウフィルタを含む、請求項1 1に記載の方法。

**【請求項 1 4】**

前記フィルタ長さはNサンプルに対応し、Nは整数である、請求項1 1に記載の方法。

**【請求項 1 5】**

前記ウインドウ C F R 利得フィルタはN / 2を中心とする、請求項1 4に記載の方法。

**【請求項 1 6】**

前記利得補正( $F_k$ )は連続関数を含む、請求項1 1に記載の方法。

**【請求項 1 7】**

ピーカスケーリングユニットを使用し、前記入力信号( $x_k$ )および前記しきい値( $T$ )に基づいて前記ウインドウ利得( $G_k$ )を決定することをさらに含む、請求項1 1に記載の方法。

10

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本開示は、波高率低減(C F R)に関する。特に、本開示はウインドウ C F R に関する。

**【背景技術】****【0 0 0 2】**

波高率低減(C F R)のいくつかの実装において、信号内のピーカマグニチュードを決定することができる。そうしたことは、信号をオーバーサンプリングすること、2つの隣接するマグニチュードよりも大きい信号マグニチュードを識別すること、およびその後、信号マグニチュードのいずれかが所定のしきい値を超えるかどうかを判定するためにテストすることによって、達成可能である。信号のオーバーサンプリングレートが高い場合、ピーカマグニチュードは正確でなく、真のピーク値から大幅に逸脱している可能性がある。オーバーサンプリングレートが減少するのに対応して、ピーカマグニチュードの推定値における正確さも低下する。このピーカマグニチュード推定値の正確さの低下は、C F R 法の品質に直接影響を与える。いくつかのケースでは、ピークキャンセル波高率低減(P C C F R)およびウインドウ C F R(W C F R)のために、検出されたピークの場所および検出されたピークでの複合信号値が必要である。したがって、P C C F R および W C F R ならびに他の C F R 法のために、正確なピーク検出が重要である。

20

**【0 0 0 3】**

C F R を実装するための一方法は、キャンセルパルス法である。この方法は有効であるが、キャンセルパルス法の実行中に、いくつかのピークが見逃される、かつ/または作成される可能性があるという問題に悩まされる。特に、キャンセルパルス法において、パルスキャンセルのためのリソースがないことから、いくつかのピークが見逃される可能性がある。加えて、キャンセルパルスが重複し、建設的に増大する場合、新しいピークが必要に作成される可能性がある。いくつかのケースでは、これらの不必要なピークに対処するために、キャンセルパルス法においてパルスキャンセルを何回か反復することができる。しかしながら、各処理ステージには比較的費用が掛かり、C F R を実装するシステムにおいて待ち時間を大幅に増大させる。これが、C F R を実装する基地局の効率およびキャパシティに悪影響を与えることになる。

30

**【発明の概要】****【0 0 0 4】**

波高率低減(C F R)のためのシステムは、入力信号( $x_k$ )を受信するように構成されたピーク検出器と、ウインドウ利得( $G_k$ )およびフィルタ長さに基づいてスケーリングファクタを生成するように構成された最大実行フィルタであって、ウインドウ利得( $G_k$ )は入力信号( $x_k$ )およびしきい値( $T$ )に基づく、最大実行フィルタと、スケーリングファクタおよびフィルタ長さに基づいて利得補正( $F_k$ )を生成するように較正され

40

50

たウィンドウ C F R 利得フィルタと、遅延入力信号を生成するために入力信号 ( $x_k$ ) を遅延させるように構成されたディレイと、ピーク補正值を取得するために利得補正 ( $F_k$ ) と遅延入力信号とを乗算するように構成された乗算器と、ピーク補正值および遅延入力信号に基づいて出力信号 ( $y_k$ ) を決定するように構成された加算器とを含む。

#### 【0005】

任意選択で、最大実行フィルタは、フィルタ長さにわたってウィンドウ利得 ( $G_k$ ) の最大利得を決定することにより、スケーリングファクタを生成するように構成可能である。

#### 【0006】

任意選択で、ウィンドウ C F R 利得フィルタは、ハニングウィンドウフィルタを含むことができる。

#### 【0007】

任意選択で、ウィンドウ C F R 利得フィルタはブラックマンウィンドウフィルタを含むことができる。

#### 【0008】

任意選択で、フィルタ長さは N サンプルに対応可能であり、N は整数である。

#### 【0009】

任意選択で、ウィンドウ C F R 利得フィルタは  $N/2$  を中心とすることができる。

#### 【0010】

任意選択で、利得補正 ( $F_k$ ) は連続関数を含むことができる。

20

#### 【0011】

任意選択で、システムはウィンドウ利得 ( $G_k$ ) を提供するためのピークスケーリングユニットをさらに備えることができる。

#### 【0012】

任意選択で、ピーク検出器、最大実行フィルタ、ウィンドウ C F R 利得フィルタ、ディレイ、乗算器、加算器、またはそれらの任意の組み合わせは、少なくとも 1 つのフィールドプログラマブルゲートアレイ (FPGA) を使用して実装可能である。

#### 【0013】

任意選択で、ピーク検出器は、入力信号 ( $x_k$ ) に関する多項式フィットを決定するように、ピーク位置を決定するように、および、多項式フィットからピーク位置での信号のマグニチュードを決定するように、構成可能である。

30

#### 【0014】

波高率低減 (C F R) のための方法は、ピーク検出器によって入力信号 ( $x_k$ ) を受信すること、最大実行フィルタを使用しウィンドウ利得 ( $G_k$ ) およびフィルタ長さに基づいてスケーリングファクタを生成することであって、ウィンドウ利得 ( $G_k$ ) は入力信号 ( $x_k$ ) およびしきい値 ( $T$ ) に基づく、生成すること、ウィンドウ C F R 利得フィルタを使用しスケーリングファクタおよびフィルタ長さに基づいて利得補正 ( $F_k$ ) を生成すること、遅延入力信号を取得するためにディレイによって入力信号 ( $x_k$ ) を遅延させること、乗算器を使用してピーク補正值を取得するために利得補正 ( $F_k$ ) と遅延入力信号とを乗算すること、ならびに、出力信号 ( $y_k$ ) を取得するためにピーク補正值を遅延入力信号に加算することを含む。

40

#### 【0015】

任意選択で、スケーリングファクタを生成する行為は、フィルタ長さにわたってウィンドウ利得 ( $G_k$ ) の最大利得を決定することを含み得る。

#### 【0016】

任意選択で、ウィンドウ C F R 利得フィルタはハニングウィンドウフィルタまたはブラックマンウィンドウフィルタを含むことができる。

#### 【0017】

任意選択で、フィルタ長さは N サンプルに対応可能であり、N は整数である。

#### 【0018】

50

任意選択で、ウィンドウ C F R 利得フィルタは N / 2 を中心とすることができる。

**【 0 0 1 9 】**

任意選択で、利得補正 (  $F_k$  ) は連続関数を含むことができる。

**【 0 0 2 0 】**

任意選択で、方法は、ピークスケーリングユニットを使用し、入力信号 (  $x_k$  ) およびしきい値 (  $T$  ) に基づいてウィンドウ利得 (  $G_k$  ) を決定することをさらに含むことができる。

**【 0 0 2 1 】**

波高率低減 ( C F R ) のためのシステムは、入力信号を受信するように構成されたピーク検出器と、ピーク検出器に結合された第 1 のピークキャンセル波高率低減 ( P C C F R ) モジュールと、第 1 の P C C F R モジュールに結合されたウィンドウ C F R モジュールとを含む。第 1 の P C C F R モジュールは、入力信号内の 1 つまたは複数のピークの第 1 のセットを除去するように構成され、ウィンドウ C F R モジュールは、第 1 の P C C F R モジュールが入力信号内の 1 つまたは複数のピークの第 1 のセットを除去した後に、入力信号内の 1 つまたは複数の追加のピークを除去するように構成される。10

**【 0 0 2 2 】**

任意選択で、システムは、入力信号内の 1 つまたは複数のピークの第 2 のセットを除去するように構成された第 2 の P C C F R モジュールをさらに含むことが可能であり、ウィンドウ C F R モジュールは、第 1 の P C C F R モジュールが入力信号内の 1 つまたは複数のピークの第 1 のセットを除去した後、および、第 2 の P C C F R モジュールが入力信号内の 1 つまたは複数のピークの第 2 のセットを除去した後に、入力信号内の 1 つまたは複数の追加のピークを除去するように構成される。20

**【 0 0 2 3 】**

任意選択で、ウィンドウ C F R モジュールは最大実行フィルタを備えることができる。

**【 0 0 2 4 】**

特徴、機能、および利点は様々なケースでは独立に達成可能であるか、または他のケースでは組み合わせてもよい。

**【 0 0 2 5 】**

その他およびさらなる態様および特徴は、以下の詳細な説明を読めば明らかであろう。

**【 0 0 2 6 】**

本開示のこれらおよび他の特徴、態様、および利点は、以下の説明、付属の特許請求の範囲、および添付の図面に関してよりよく理解されよう。30

**【 図面の簡単な説明 】**

**【 0 0 2 7 】**

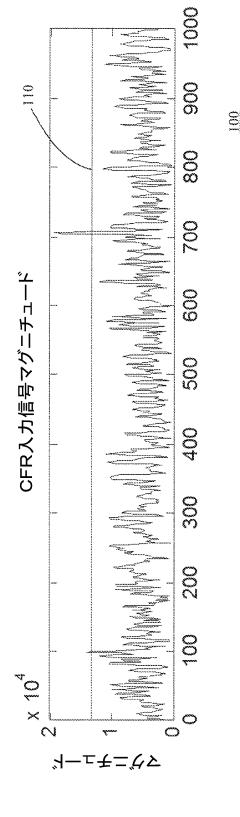

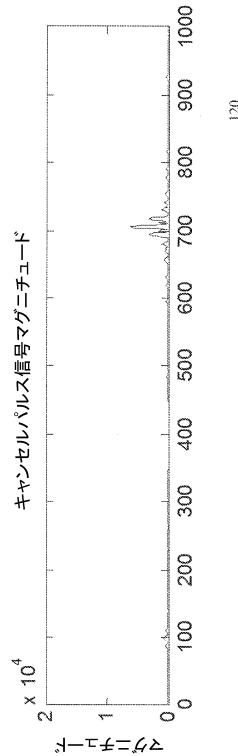

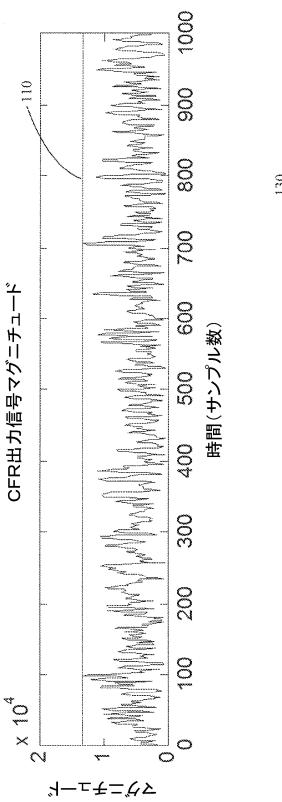

【 図 1 - 1 】時間ドメイン内のピークキャンセル波高率低減 ( P C C F R ) プロセスを示すグラフである。

【 図 1 - 2 】時間ドメイン内のピークキャンセル波高率低減 ( P C C F R ) プロセスを示すグラフである。

【 図 1 - 3 】時間ドメイン内のピークキャンセル波高率低減 ( P C C F R ) プロセスを示すグラフである。40

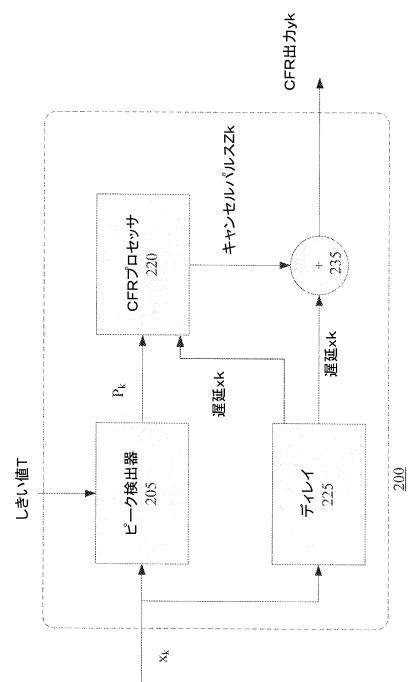

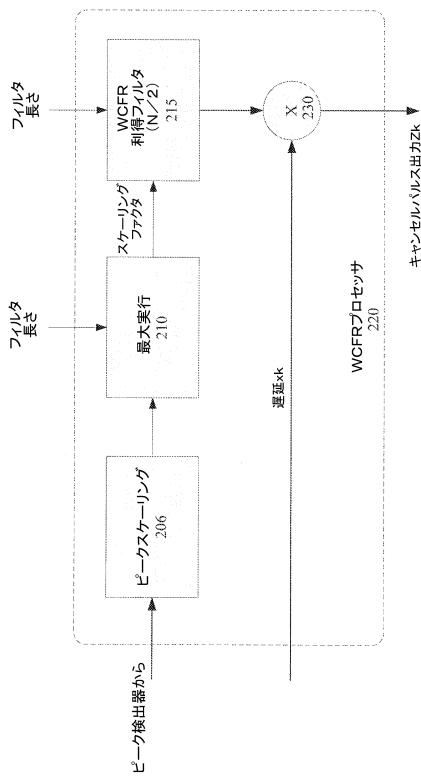

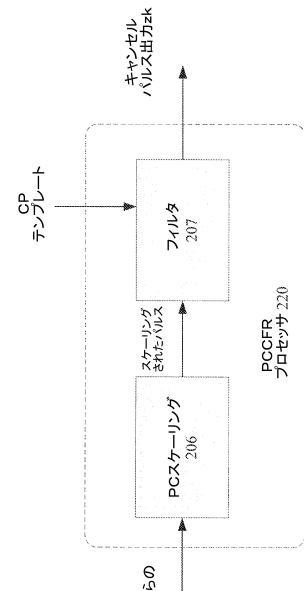

**【 図 2 - 1 】 C F R プロセッサを含むシステムを示す図である。**

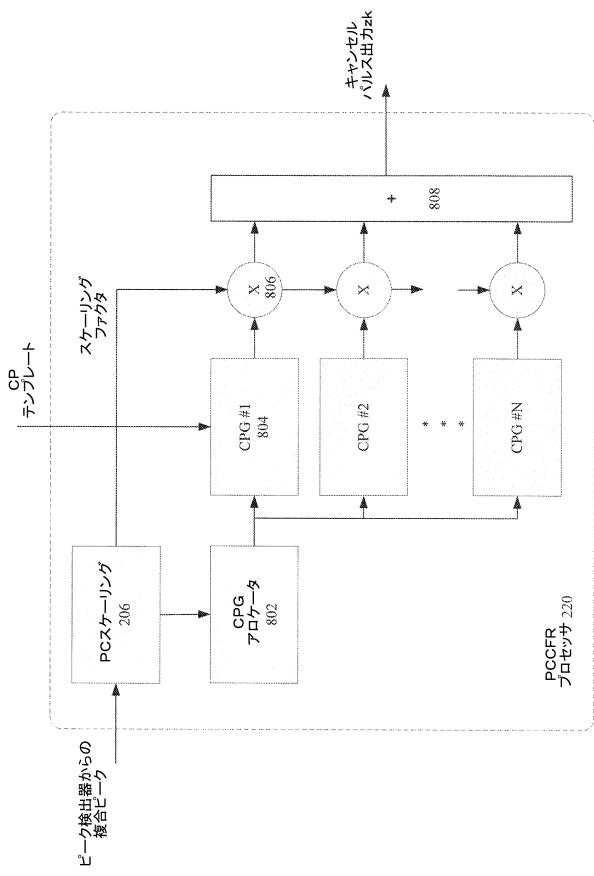

**【 図 2 - 2 】 ウィンドウ C F R プロセッサの例を示す図である。**

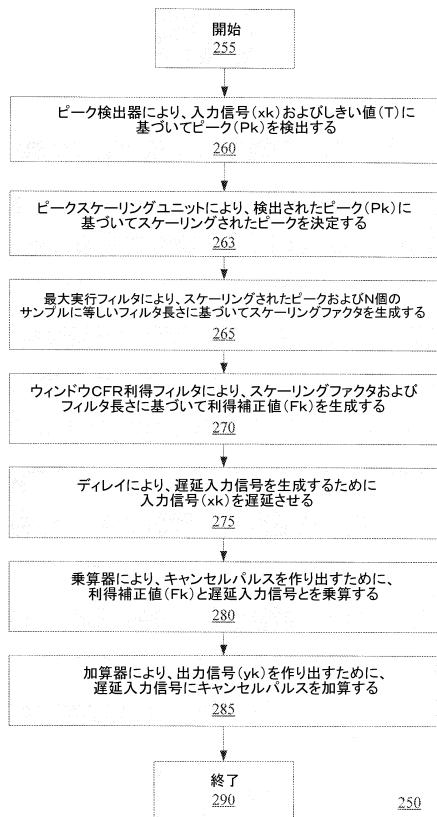

【 図 2 - 3 】図 2 - 2 のウィンドウ C F R プロセッサを伴う図 2 - 1 のシステムによって実行される方法を示す図である。

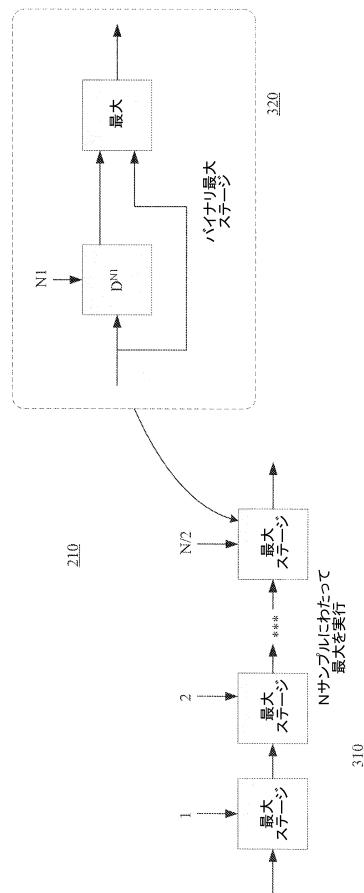

**【 図 3 】 最大実行フィルタの例を示す図である。**

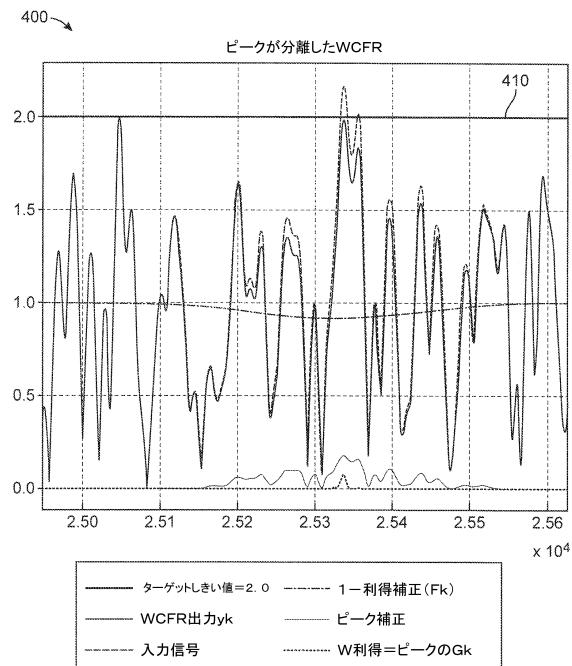

**【 図 4 - 1 】 図 2 - 3 の方法に関連付けられた信号値を示すグラフである。**

【 図 4 - 2 】図 2 - 1 のシステムによって利用可能であるか、または図 2 - 1 のシステムの動作を管理可能な、公式を示す図である。

**【 図 5 - 1 】 P C C F R プロセッサを示す図である。**

**【 図 5 - 2 】 複数のキャンセルパルス生成器 ( C P G ) を含む別の P C C F R プロセッサ**50

を示す図である。

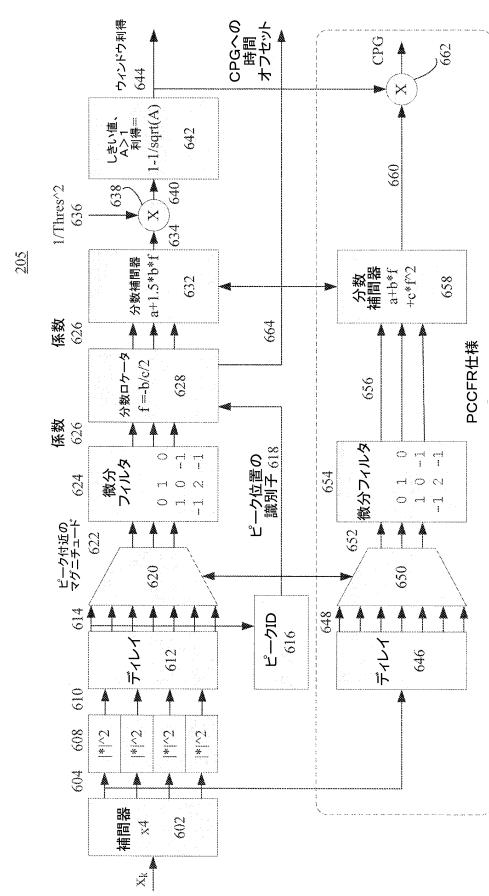

【図 6 - 1】ピーク検出器の例を示す図である。

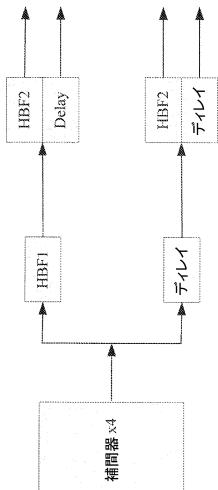

【図 6 - 2】補間器の例を示す図である。

【図 6 - 3】C F R におけるピーク検出のための方法を示す図である。

【図 6 - 4】C F R におけるピーク検出のための方法を示す図である。

【図 7】開示されたシステムおよび方法を使用して達成される結果の例を示すグラフである。

【図 8】ウィンドウ C F R モジュールおよび P C C F R モジュールの組み合わせを含むシステムを示す図である。

【発明を実施するための形態】

10

【0028】

以下、図面を参照しながら様々な特徴が説明される。図面は一定の尺度で描かれているかまたはそうでない場合があること、および、同様の構造または機能の要素は図面全体を通じて同じ参照番号で表されていることに留意されたい。図面は特徴の説明を容易にすることのみを意図していることに留意されたい。加えて、図示された特徴は、すべての態様または利点が示されているとは限らない。特定の特徴に関連して説明される態様または利点は、必ずしもその特徴に限定されているものではなく、たとえそのように示されていない場合、またはそのように明示的に説明されない場合であっても、任意の他の特徴において実施可能である。

【0029】

20

本明細書で開示される方法および装置は、効率的なウィンドウ波高率低減（C F R）およびC F Rにおけるピーク検出を提供する。

【0030】

開示されたシステムは、C F R におけるピーク値を正確に位置特定および測定するためのピーク検出器を含む。ピーク検出器は、信号マグニチュードに対する多項式フィット（たとえば2次フィット）を実行すること、およびその後ピーク位置を抽出することによって、オーバーサンプリングの量を制限する。2次フィットから、ピークがかなり高いサンプリングレートで発見されたかのように、ピーク位置を使用してその位置での信号のマグニチュードを計算することができる。

【0031】

30

いくつかのケースにおいて、開示されたシステムはウィンドウ C F R を利用することができる。ウィンドウ C F R を利用することの利点は、検出時にピークが見失われるのを防ぐこと、および出力時に新しいピークが発生するのも防ぐことである。ウィンドウ C F R を使用することの欠点は、パフォーマンス（エラーベクトルマグニチュード（E V M）に対するピーク対平均値比（P A R）などのメトリクスによって測定可能である）がP C C F R 法ほど良好でない可能性があることである。しかしながら、P C C F R とウィンドウ C F R とを組み合わせて使用することは、複雑さおよびパフォーマンスの観点から良好な妥協点をもたらす。P C C F R が良好な E V M を用いてピークのほとんどを消去する場合、ウィンドウ C F R を使用して残りのピークを「クリーンアップ」することができる。残りのピークがわずかである場合、より多くのP C C F R のステージを使用することに比べて、ウィンドウ C F R を使用することによる劣化は非常に小さい。したがっていくつかのケースでは、ウィンドウ C F R を1つまたは複数のP C C F R ステージ後の後処理として使用することができる。

【0032】

40

システムおよび方法は、指定のしきい値を超える信号ピークからスペクトル形パルスを減じることによってピークを（たとえば、信号の平均電力比まで）低減させる、ピークキャンセルも提供する。システムおよび方法によって提供されるキャンセルパルス（C P）は、入力信号のスペクトルと一致するスペクトルを有するように設計される。したがって、キャンセルパルスはごくわずかな帯域外干渉をもたらす。いくつかのケースでは、入力信号およびキャンセルパルスは複雑であり、ピーク検索は信号マグニチュードに対して実

50

施される場合がある。信号は複雑であるため、各キャンセルパルスは対応するピークの位相に一致するように回転することができる。所与のキャンセルパルス（C P）のピークマグニチュードは、対応する信号ピークマグニチュードと所望のクリッピングしきい値との差異に等しいように設定可能である。開示された方法は、信号位相を保ちながらピーク信号マグニチュードをしきい値まで低減させる。

#### 【0033】

図1-1から図1-3は、時間ドメイン内のピークキャンセル波高率低減（P C C F R）プロセスを示す。特に図1-1は、マグニチュードの変動を伴う入力信号のセクションを示すグラフ100である。グラフ100の水平軸は時間を表し、グラフ100の垂直軸は入力信号のマグニチュードを表す。グラフ100内には、クリッピングしきい値を示す水平線110が示されている。このしきい値を超えるいずれのピークも、ピークキャンセルの候補である。クリッピングしきい値は任意に設定可能であり、異なるケースで異なる値を有することができる。図1-2は、入力信号から減じられることになるキャンセルパルス（時間=700付近に位置する）のマグニチュードを示すグラフ120である。図1-3は、図1-1の入力信号から図1-2のキャンセルパルスを減じた後に取得される、出力信号のマグニチュードを示すグラフ130である。図1-3に示されるように、出力信号は、入力信号内のピーク（時間=700付近に位置する）がキャンセルされていることを除き、入力信号と同じである。

#### 【0034】

図2-1はCFRのためのシステム200を示す。いくつかのケースでは、システム200はキャンセルパルスおよびP C C F Rを提供することができる。システム200は、ピーク検出器205、ピーク検出器205に結合されたCFRプロセッサ220、ディレイ225、および加算器235を含む。

#### 【0035】

ピーク検出器205は、入力信号( $x_k$ )およびしきい値( $T$ )を受信するように構成される。しきい値( $T$ )は、ピークキャンセルのためのクリッピングしきい値を表す所定の値である。たとえばしきい値( $T$ )は、2.0に等しく設定される。しかしながら他の例において、しきい値( $T$ )は2.0より大きいかまたは2.0より小さくてもよい。ピーク検出器205は、入力信号( $x_k$ )およびしきい値( $T$ )に基づいて(たとえば、使用して)ピーク( $P_k$ )を識別するように構成される。いくつかのケースでは、ピーク検出器205はいずれかの既知のピーク検出器を使用して実装可能である。他のケースでは、ピーク検出器205は新規のピーク検出器であってよい。新規のピーク検出器は、図6-1を参照しながら説明する。

#### 【0036】

ディレイ225は、入力信号( $x_k$ )を受信するように、および遅延入力信号を生成するために入力信号( $x_k$ )を遅延させるように構成される。CFRプロセッサ220は、ピーク検出器205から識別されたピーク( $P_k$ )を、およびディレイ225から遅延入力信号( $x_k$ )を受信するように、ならびに識別されたピーク( $P_k$ )および遅延入力信号( $x_k$ )に基づいてキャンセルパルス( $Z_k$ )を出力するように構成される。

#### 【0037】

ディレイ225は、遅延入力信号( $x_k$ )を加算器235に渡すように構成される。加算器235は、キャンセルパルス( $Z_k$ )を遅延入力信号( $x_k$ )に加算し、それによって望ましくないピークを入力信号( $x_k$ )から減じ、利得補正出力信号である出力信号( $y_k$ )を作り出すように構成される。いくつかのケースでは、キャンセルパルス( $Z_k$ )は入力信号( $x_k$ )に関して負の値を有することができる。したがって、加算器235がキャンセルパルス( $Z_k$ )を遅延入力信号( $x_k$ )に加えた場合、キャンセルパルス( $Z_k$ )は遅延入力信号( $x_k$ )から効果的に「減じられる」。

#### 【0038】

いくつかのケースでは、CFRプロセッサ220は、ウィンドウフィルタリングを提供するウィンドウCFRプロセッサを使用して実装可能である。図2-2は、ウィンドウC

10

20

30

40

50

F R プロセッサ 220 の例を示す。ウィンドウ C F R プロセッサ 220 は、図 2 - 1 のシステムを参照しながら説明する。しかしながら、ウィンドウ C F R プロセッサ 220 は、他の実施形態において他のシステムと共に使用可能であることを理解されたい。ウィンドウ C F R プロセッサ 220 は、ピークスケーリングユニット 206、最大実行フィルタ 210、ウィンドウ C F R 利得フィルタ 215、および乗算器 230 を含む。

#### 【0039】

ピークスケーリングユニット 206 は、ピーク検出器 205 から識別されたピーク ( $P_k$ ) を受信するように、およびスケーリングされたピークを出力するために、(たとえば、減算関数を実行することによって) ピークマグニチュードとクリッピングしきい値との間の差異を決定するように構成される。いくつかのケースでは、ピークスケーリングユニット 206 は、 $1 - 1 / \sqrt{r t} (P_k / T^2)$  に等しい出力を提供することができる。またいくつかのケースでは、ウィンドウ C F R プロセッサ 220 はピークスケーリングユニット 206 を含まない場合がある。こうしたケースでは、ピークスケーリングユニット 206 は図 2 - 1 のピーク検出器 205 に組み込むことができる。

#### 【0040】

最大実行フィルタ 210 は、ピークスケーリングユニット 206 からのスケーリングされたピークと、フィルタ長さとを受信するように構成される。フィルタ長さは N サンプルに等しく設定可能であり、N は整数である。最大実行フィルタ 210 は、スケーリングされたピークおよびフィルタ長さに基づいて(たとえば、使用して)、スケーリングファクタを生成するようにも構成される。一実装において、最大実行フィルタ 210 は、フィルタ長さにわたって(たとえば N サンプルにわたって) ウィンドウ利得 ( $G_k$ ) の最大利得を決定することによって、スケーリングファクタを生成するように構成可能である。図 3 は、図 2 - 2 のウィンドウ C F R プロセッサの最大実行フィルタ 210 を実装するために使用可能な、最大実行フィルタ 310 の例を示す。最大実行フィルタ 310 は、N サンプルのウィンドウフィルタ長さにわたって動作するように構成される。いくつかのケースでは、長さ N は 2 のべき乗であってよい。他のケースでは、長さ N は他の数であってよい。図に示されるように、最大実行フィルタ 310 はいくつかのステージを有する。各ステージは、図に示される構成 320 を有するバイナリ最大ステージであってよい。こうした構成により、最大実行フィルタ 210 は、直接的な手法よりも効率的にスケーリングファクタを生成することができる。他のケースでは、各ステージが他の構成を有することができる。使用中、信号最大は各ステージで決定され、最大実行は、各ステージが最大実行値を次のステージに渡すにつれて蓄積していく。たとえば、N = 7 であり、入力信号(サンプル数)が 3、3、4、2、5、7、1 であると想定すると、最大実行は 3、3、4、4、5、7、7 である。

#### 【0041】

図 2 - 2 に戻ると、ウィンドウ C F R 利得フィルタ 215 は、最大実行フィルタ 210 およびフィルタ長さからスケーリングファクタを受信するように、ならびに、最大実行フィルタ 210 およびフィルタ長さからのスケーリングファクタに基づいて(たとえば、使用して) 利得補正 ( $F_k$ ) を生成するように、構成される。いくつかのケースでは、ハニングウィンドウフィルタまたはブラックマンウィンドウフィルタを採用して、ウィンドウ C F R 利得フィルタ 215 を実装することができる。また、いくつかのケースでは、ウィンドウ C F R 利得フィルタ 215 は  $N / 2$  を中心とすることが可能であり、N はフィルタ長さに対応するサンプル数である。

#### 【0042】

乗算器 230 は、図 2 - 1 のシステム 200 のディレイ 225 から遅延入力信号 ( $x_k$ ) を受信するように構成される。乗算器 230 は、ウィンドウ C F R 利得フィルタ 215 からの利得補正 ( $F_k$ ) と遅延入力信号とを乗算して、キャンセルパルス ( $Z_k$ ) を作り出すように構成される。いくつかのケースでは、キャンセルパルス ( $Z_k$ ) はピーク補正值と見なすことができる。

#### 【0043】

10

20

30

40

50

いくつかのケースでは、図2-2のウィンドウCFRプロセッサ220は、少なくとも1つのフィールドプログラマブルゲートアレイ(FPGA)を使用して実装可能である。たとえばいくつかのケースでは、FPGAは、ピークスケーリングユニット206、最大実行フィルタ210、ウィンドウCFR利得フィルタ215、乗算器230、またはそれらの任意の組み合わせを実装するように構成可能である。他のケースでは、ウィンドウCFRプロセッサ220は、汎用プロセッサ、ASICプロセッサ、マイクロプロセッサ、または他のタイプのプロセッサなどの、任意の集積回路を使用して実装可能である。さらなるケースでは、ウィンドウCFRプロセッサ220は、ハードウェア、ソフトウェア、またはその両方の組み合わせを使用して実装可能である。

## 【0044】

10

また、いくつかのケースでは、図2-1のシステム200は少なくとも1つのFPGAを使用して実装可能である。たとえば、いくつかのケースでは、FPGAはピーク検出器205、CFRプロセッサ215、ディレイ225、および加算器235を実装するように構成可能である。他のケースでは、システム200は汎用プロセッサ、ASICプロセッサ、マイクロプロセッサ、または他のタイプのプロセッサなどの、任意の集積回路を使用して実装可能である。さらなるケースでは、システム200は、ハードウェア、ソフトウェア、またはその両方の組み合わせを使用して実装可能である。

## 【0045】

図2-3は、図2-1のシステム200によって実行される方法250を示し、図2-1のCFRプロセッサ220は図2-2のウィンドウCFRプロセッサ220である。項目255で方法が開始される。ピーク検出器が、入力信号( $x_k$ )およびしきい値(T)に基づいてピーク( $P_k$ )を検出する(項目260)。いくつかのケースでは、項目260は、図2-1のシステム200内のピーク検出器205によって実行可能である。

20

## 【0046】

次に、ピークスケーリングユニットが、検出されたピーク( $P_k$ )を受信し、検出されたピークに基づいてスケーリングされたピークを出力する(項目263)。いくつかのケースでは、項目263は、図2-2のウィンドウCFRプロセッサ220内のピークスケーリングユニット206によって実行可能である。

## 【0047】

次に、最大実行フィルタが、スケーリングされたピークおよびNサンプルに等しいフィルタ長さに基づいてスケーリングファクタを生成する(項目265)。いくつかのケースでは、項目265は、図2-2のウィンドウCFRプロセッサ220内の最大実行フィルタ210によって実行可能である。

30

## 【0048】

次に、ウィンドウCFR利得フィルタが、スケーリングファクタおよびフィルタ長さに基づいて利得補正( $F_k$ )を生成する(項目270)。いくつかのケースでは、項目270は、図2-2のウィンドウCFRプロセッサ220内のウィンドウCFR利得フィルタ215によって実行可能である。

## 【0049】

40

次に、ディレイが、遅延入力信号を生成するために入力信号( $x_k$ )を遅延させる(項目275)。いくつかのケースでは、項目275は、図2-1のシステム200内のディレイ225によって実行可能である。

## 【0050】

次に、乗算器が、キャンセルパルスを作り出すために、利得補正( $F_k$ )と遅延入力信号とを乗算する(項目280)。いくつかのケースでは、項目280は、図2-2のウィンドウCFRプロセッサ内の乗算器230によって実行可能である。

## 【0051】

50

次に、加算器が、出力信号( $y_k$ )を作り出すために、遅延入力信号からのキャンセルパルスを加算する(項目285)。出力信号( $y_k$ )において、望ましくないピークはキャンセルパルスによって除去される。いくつかのケースでは、項目285は、図2-1の

システム 200 内の加算器 235 によって実行可能である。その後、項目 290 で方法 250 は終了する。

#### 【0052】

図 4 - 1 は、図 2 - 3 の方法 250 に関する入力信号の例および様々な信号値の例を示すグラフ 400 である。信号値は、図 2 - 1 のシステム 200 のコンポーネントによって生成可能であり、かつ / または、図 2 - 1 のシステム 200 のコンポーネントの出力から導出可能である。グラフ 400 では、水平軸が時間を表し、垂直軸がスケーリングされた信号長さ（たとえば、ボルト）を表す。水平線 410 は、最大許容信号を示すしきい値 ( $T$ ) を表す。図示された例では、しきい値 ( $T$ ) は 2.0 である。他の例では、しきい値 ( $T$ ) は 2.0 より大きいかまたは 2.0 より小さくてよい。グラフ 400 は、入力信号 ( $x_k$ ) の時間履歴の例を含み、この例は、方法 250 の項目 260 においてピーク検出器 205 によって受信される入力信号 ( $x_k$ ) の例であってよい。グラフ 400 は、ウインドウ C F R プロセッサ 220 のウインドウ C F R 利得フィルタ 215 によって決定可能な、ウインドウ利得 ( $G_k$ ) も示す。加えて、グラフ 400 は、方法 250 の項目 280 において乗算器 230 によって出力されるキャンセルパルスの例とすることができます、ピーク補正も示す。さらにグラフ 400 は、1 - 利得補正 ( $F_k$ ) である、適用ウインドウ C F R 利得を示す。このようなパラメータは、遅延信号 ( $x_k$ ) によって乗算された場合、 $x_k - x_k * F_k$  が、システム 200 において乗算器 230 および加算器 235 によって実行される演算を表すため、結果として出力信号 ( $y_k$ ) を生じる。図示された例では、利得補正 ( $F_k$ ) の振幅は、 $N / 2$  で最大実行フィルタの中央に適用されるウインドウ利得 ( $G_k$ ) に少なくとも部分的に基づいて決定される。ウインドウ利得 ( $G_k$ ) は、スペクトル帯域内に利得補正済みウインドウ C F R 出力信号 ( $y_k$ ) を維持するための、平滑関数である。グラフ 400 は、方法 250 の項目 285 において加算器 235 によって出力される出力信号 ( $y_k$ ) の例とすることができます、出力信号 ( $y_k$ ) の例も示す。結果として生じる入力信号 ( $x_k$ ) と補正済みウインドウ C F R 出力信号 ( $y_k$ ) との間の差異はピーク補正であり、ウインドウ利得 ( $G_k$ ) の漸進的適用により、時間間隔にわたって発生する。

#### 【0053】

図 4 - 2 は、図 1 - 2 のシステム 200 によって利用されること、または図 1 - 2 のシステム 200 の動作を管理することが可能な、式を示す。式において、(A) はピーク信号、またはピークでの信号の 2 乗値を表し、(T) はターゲットしきい値を表し、(W) は最大実行フィルタ 210 およびウインドウ C F R 利得フィルタ 215 の組み合わせによって提供されるウインドウフィルタを表す。図に示されるように、ピーク振幅の 2 乗マグニチュードはしきい値 ( $T$ ) によってスケーリングされ、これらの値からピーク時の利得 ( $G_k$ ) が計算される。しきい値のスケーリング後、ウインドウ C F R プロセッサ 220 によるすべての他の処理は、しきい値 ( $T$ ) を知っている必要がない。

#### 【0054】

ウインドウフィルタ W を実装するために様々な技法を採用することができる。いくつかのケースでは、ウインドウフィルタ W のウインドウ長さは約 256 サンプルであってよい。他のケースでは、ウインドウフィルタ W のウインドウ長さは他の長さを有することができる。いくつかのケースでは、ウインドウフィルタ W を実装するためにハニングウインドウを使用することができる。たとえば、ハニングウインドウは以下のようであり得る。

$$w_n = \frac{1 + \cos(2\pi n/(N-1))}{2} \quad -\frac{N}{2} \leq n \leq \frac{N}{2}$$

#### 【0055】

いくつかのケースでは、ハニングウインドウは以下のように 2 つの因数として表すこと

10

20

30

40

50

が可能であり、

$$w_n = w_{1n} * w_{2n}$$

上式では以下の通りである。

$$W_1 = \begin{cases} 1 & -N/4 \leq n \leq N/4 \\ 0 & \text{それ以外の場合} \end{cases}$$

$$W_2 = \begin{cases} \cos(2\pi n/(N-1)) & -N/4 \leq n \leq N/4 \\ 0 & \text{それ以外の場合} \end{cases}$$

10

#### 【0056】

いくつかのケースでは、因数  $W_1$  は、ボックスカー応答を取得するために単一ステージ C I C フィルタを用いて実装可能である。因数  $W_2$  は、通常のシフトレジスタおよび乗算器アレイを使用して実装可能である。他のケースでは、因数  $W_2$  は、C I C フィルタまたは C I C フィルタに似た他のフィルタを使用して実装可能である。

#### 【0057】

また、いくつかのケースでは、長さ  $N$  を有するハニングウィンドウの場合、因数  $W_1$  は長さ  $N/2$  を有することができる。因数  $W_2$  の合計長さも  $N/2$  であってよく、極近似は以下のように決定することが可能であり、

$$\hat{W}_2 = U_1 * U_2 * U_3 / ((N+1)/3)$$

上式では以下の通りである。

$$U_1(k) = \begin{cases} 1 & 0 \leq k \leq (N+1)/3-1 \\ 0 & \text{それ以外の場合} \end{cases}$$

$$U_2(k) = \begin{cases} 1 & 0 \leq k \leq (N+1)/6-1 \\ 0 & \text{それ以外の場合} \end{cases}$$

$$U_3(k) = [1 \ 1]$$

$$\text{長さ } \hat{W}_2 = (N+1)/2$$

20

30

#### 【0058】

項  $U_3$  は、フィルタピークが信号ピークと正確に位置合わせできるように、ハニングフィルタの長さを奇数にするために使用される。

#### 【0059】

いくつかのケースでは、ウィンドウ C F R プロセッサ 220 の動作について、必要な長さ解決には、2 倍異なる長さ  $U_1$ 、 $U_2$  の選択で十分である。ウィンドウ C F R プロセッサ 220 の実装を簡略化するために、フィルタ  $U_1$ 、 $U_2$  の長さが 2 のべき乗である場合、および全体の長さ  $N$  が奇数である場合、有利であり得る。いくつかのケースでは、フィルタ長さ  $N$  は以下のように決定可能である。

$$N = 3 \cdot 2^m - 1$$

40

#### 【0060】

このケースでは、長さ  $U_1$  および  $U_2$  はどちらも 2 のべき乗であり、利得  $(N+1)/3$  も 2 のべき乗である。因数  $W_1$  および  $W_2$  の長さは 2 のべき乗の 3 倍である。他のケースでは、フィルタ長さ  $N$  は他の数式および / または考慮に基づいて決定可能である。また、他のケースでは、フィルタ  $U_1$ 、 $U_2$  の長さは 2 以外の他の数のべき乗であってよい。

50

## 【0061】

いくつかのケースでは、重複するピークに対処するために、上記のフィルタリング技法を調整することができる。上記のアルゴリズムは、ピークが分離している場合に効果がある。しかしながらピークが重複している場合、利得補正是補正利得に重畠する可能性がある。その結果、ウィンドウ C F R プロセッサ 220 のパフォーマンスが低下する可能性がある。オーバーキャンセルが消去される場合、アルゴリズムの修正を採用することができる。フィルタの因数分解から、ピークが重複しない場合、フィルタリングステップ  $W_1$  をピーク時に算出される利得の最大実行フィルタに置き換えることができる。ピークが重複する場合、より小さなピークは最大実行によってシャドーイングされ、考慮対象から効率的に消去されるため、オーバーキャンセルの問題がなくなる。いくつかのケースでは、修正済みアルゴリズムは以下のようになり、

$$g_k = 1 - 1/\sqrt{A/T^2}$$

$$M_{k,N} = \{m \in G_N : m \geq a \forall a \in G_N\}$$

$$G_N = \{g_k : \forall |k - N| \leq M\}$$

$$F_k = M_k * W_2 = M_k * U_1 * U_2 * U_3$$

$$y_k = x_k - F_k * x_k$$

上式で、 $g_k$  は利得であり、 $A$  はピーク値またはピーク値の 2 乗である。上記の数式に基づき、最大実行はボックスカーパルス応答とほぼ同様に効率的に計算することができるが、ピークの重複問題を解決する。

## 【0062】

いくつかのケースでは、キャンセルパルス  $z_k$  は、ウィンドウ C F R プロセッサの代わりに P C C F R プロセッサを使用して達成可能である。図 5 - 1 は、P C C F R プロセッサ 220 の例を示す。P C C F R プロセッサ 220 は、図 2 - 1 のシステム 200 内の C F R プロセッサ 220 の例とすることができます。P C C F R プロセッサ 220 は、ピークキャンセル (P C) スケーリングユニット 206、およびピークスケーリングユニット 206 に結合されたフィルタ 207 (たとえば、デジタルフィルタ) を含む。P C C F R プロセッサ 220 はピーク検出器 (図 2 - 1 のピーク検出器 205 など) に結合され、ピーク検出器からピーク情報などの入力を受信するように構成される。ピークスケーリングユニット 206 は、ピーク検出器からの入力をスケーリングするように、およびスケーリングされた出力 / ピーク (利得と見なし得る) を生成するように、構成される。いくつかのケースでは、P C C F R プロセッサ 220 はピークスケーリングユニット 206 を含まない場合がある。こうしたケースでは、ピークスケーリングユニット 206 を図 2 - 1 のピーク検出器 205 に組み込むことができる。フィルタ 207 は、スケーリングされた出力を受信するように、ならびに、スケーリングされた出力およびキャンセルパルス (C P) テンプレートに基づいてキャンセルパルス  $z_k$  を生成するように、構成される。C P テンプレートは、標準のキャンセルパルスを定義するテンプレートである。いくつかのケースでは、キャンセルパルスはテーブル (メモリ) に記憶可能である。ピークが見つかった場合、テーブルの始めにインデックスが設定される。その後、キャンセルパルス上のポイントを表す各テーブル出力を、算出された利得によってスケーリングすることができる。後続の各サンプル時間に、テーブルインデックスを増分し、同じ定数でスケーリングすることができる。全テーブルが読み取られた後、インデックスをリセットすることができる。いくつかのケースでは、P C C F R プロセッサ 220 に入力を提供するためのピーク検出器は、任意の既知のピーク検出器とすることができます。他のケースでは、ピーク検出器は本明細書で説明するピーク検出器のうちのいずれかとすることができます。

10

20

30

40

50

**【 0 0 6 3 】**

いくつかのケースでは、P C C F R プロセッサが、キャンセルパルス生成器（C P G）を使用して実装可能である。図5-2は、複数のキャンセルパルス生成器（C P G）を含む別のP C C F R プロセッサ220の例を示す。P C C F R プロセッサ220は、図2-1のシステム200内のC F R プロセッサ220の例とすることができる。P C C F R プロセッサ220は、ピークスケーリングユニット206、ピークスケーリングユニット206に結合されたC P G アロケータ802、および、C P G アロケータ802からの入力を受信するために結合された複数のC P G 804を含む。P C C F R プロセッサ220は、それぞれのC P G 804に結合された乗算器806、および乗算器806からの入力を受信するために結合された加算器808も含む。

10

**【 0 0 6 4 】**

アロケータ802は、キャンセル着信ピークのタスクを実行するために、C P Gリソースの割り当てを制御するように構成される。起動中、すべてのC P G 804が利用可能である。第1のピークに達すると、アロケータ802はこれをキャンセルするために第1のC P G 804を割り当て、次いで、割り振られる通りにそのC P G 804をタグ付けする。割り振られると、C P G 804はキャンセルパルスの長さ（サンプル数）には利用不可となる。後続のピークに達すると、アロケータ802は各C P G 804のステータスを通り、最初の利用可能なC P G 804を割り当てる。いくつかのケースでは、すべてのC P G 804が現在ビジーである場合、到達したピークはキャンセルされず、アルゴリズムのその後の反復によってピックアップされることになる。こうした状況は、

20

**【 0 0 6 5 】**

使用中、P C C F R プロセッサ220は、ピーク検出器（ピーク検出器205など）からの入力を受信する。ピーク検出器からの入力は、ピーク位置インジケータ、ピークマグニチュード、ピークに関する位相情報、またはそれらの任意の組み合わせなどの、ピーク情報とすることができます。いくつかのケースでは、ピークスケーリングユニット206は、ピークマグニチュード206とクリッピングしきい値との間の差異を（たとえば、減算関数を実行することによって）決定するように構成可能である。マグニチュード差は、キャンセルパルスをスケーリングするための複合重みを作り出すために、位相情報と組み合わせることができる。

30

**【 0 0 6 6 】**

図2-5に示されるように、P C スケーリングユニット206は、第1のC P G 804に対応する乗算器806にスケーリングファクタを提供する。乗算器806は、第1のC P G 804からの入力も受信し、第1の乗算器出力を生成するために第1のC P G 804からの入力とスケーリングファクタとを乗算する。第1の乗算器出力は加算器808に入力される。追加のC P G 804および対応する乗算器806によって同様の演算が実行され、乗算器806からの出力が加算器808に入力される。いくつかのケースでは、各乗算器806は、見つかったピークと一致させるためにキャンセルパルスをスケーリングするように構成される。C P G 804内に記憶されたキャンセルパルスは、ピークをキャンセルするためにC P Gが必要とするピーク振幅がC P G出力に直接適用できるように、1にスケーリングされる。いくつかのケースでは、P C C F R プロセッサ220はピークスケーリングユニット206を含まない場合がある。このようなケースでは、ピークスケーリングユニット206を図2-1のピーク検出器205に組み込むことができる。

40

**【 0 0 6 7 】**

加算器808は、キャンセルパルス $z_k$ を取得するために、C P G 804からの乗算器出力を加算する。特に、C P G 804からの出力は、ピークをキャンセルするために入力信号に適用されるように、完全なキャンセル波形にするために合計される。

**【 0 0 6 8 】**

いくつかのケースでは、C P G 804は、個別のキャンセルパルスを生成し、それに

50

続いて着信データサンプルからスケーリングおよび減算されるように、構成可能である。各 C P G 8 0 4 は、別々のキャンセルパルス  $c_n$  を着信信号に適用する。いくつかのケースでは、C P G 8 0 4 は、着信サンプルを以下の数式に基づいて個別に処理するよう構成可能であり、

$$\hat{y}_n = x_n - \alpha_{N_0} c_{n-N_0}$$

$$\alpha_{N_0} = (|x_{N_0}| - T) e^{j\phi_{N_0}}, \phi_{N_0} = \langle x_{N_0} \rangle$$

10

上式で、1つのC P G 8 0 4 によるピークキャンセルにより、 $x_n$  は入力であり、

$\hat{y}_n$

は出力である。キャンセルされることになるピークは  $n = N_0$  あるものと推定される。上式に示されるように、ピークキャンセルによる出力は、スケーリングされたキャンセルパルスを入力から減じることによって取得可能であり、ここで  $c$  はキャンセルパルスであり、 $T$  はスケーリングファクタである。 $\phi$  はしきい値  $T$  の関数であり、 $\langle \cdot \rangle$  は  $x_n$  の位相である。他のケースでは、C P G 8 0 4 は以下の数式に基づいて着信サンプルを処理するよう構成可能であり、

20

$$\hat{y}_n = x_n - (G_n x_{n+off}) c_{n-N_0}$$

$$G_n = \begin{cases} 1 / \sqrt{|x_{n+off} / T|^2} & |x_{n+off} / T|^2 > 1 \\ 0 & \text{それ以外の場合} \end{cases}$$

上式で、1つのC P G 8 0 4 によるピークキャンセルにより、 $x_n$  は入力であり、

30

$\hat{y}_n$

は出力である。キャンセルされることになるピークは  $n = N_0$  あるものと推定され、 $x_{n+off}$  は2次補間を伴う分数ピークである。上式に示されるように、ピークキャンセルによる出力は、スケーリングされたキャンセルパルスを入力から減じることによって取得され、ここで  $c$  はキャンセルパルスであり、 $G * x$  はスケーリングファクタである。 $G$  は所望のしきい値  $T$  の関数であることに留意されたい。

#### 【0069】

いくつかのケースでは、C P G 8 0 4 の数は、着信サンプル上でキャンセル可能な連続ピークの数に対応する。したがって、たとえば8つのC P G 8 0 4 を伴う場合、着信サンプル上で最大8つの連続ピークをキャンセルすることができる。これらの動作は反復することができる。たとえばいくつかのケースでは、C P G 8 0 4 の第1のセットから出力してくるサンプル上で、4つまたは他の数のC P G 8 0 4 の別のセットを採用することができる。いくつかのケースでは、P C C F R プロセッサ220は最大8回の反復を提供することができる、各反復は最大12個のC P G 8 0 4 を有することができる。他のケースでは、反復回数は8より少ないかまたは8より多いものとすることができる。また他のケースでは、各反復におけるC P G 8 0 4 の最大数は、12より少ないかまたは12より多いものとすることができる。

40

#### 【0070】

前述のように、図2-1のシステム200は、任意の既知のピーク検出器を使用して実

50

装可能なピーク検出器 205 を含む。他のケースでは、ピーク検出器 205 は図 6 - 1 に示されるような新規のピーク検出器とすることができます。図 6 - 1 のピーク検出器 205 は、図 2 - 1 のシステム 200 のためのピーク検出器 205 とすることができます。しかしながら、図 6 - 1 のピーク検出器 205 は C F R の分野で使用されるものとは限定されず、他の技術領域で使用可能であることに留意されたい。

#### 【0071】

図 6 - 1 に示されるように、ピーク検出器 205 は、補間器 602、マグニチュード 2 乗ユニット 608、第 1 のディレイ 612、ピーク識別 (I D) ユニット 616、第 1 のマルチプレクサ 620、第 1 の微分フィルタ 624、分数口ケータ 628、第 1 の分数補間器 632、第 1 の乗算器 638、利得生成器 642、第 2 のディレイ 646、第 2 のマルチプレクサ 650、第 2 の微分フィルタ 654、第 2 の分数補間器 658、および第 2 の乗算器 662 を含む。

10

#### 【0072】

補間器 602 は、入力信号 ( $x_k$ ) を受信するように、および、少なくとも 1 つの補間された信号 604 を作り出すために入力信号 ( $x_k$ ) を補間するように、構成される。いくつかのケースでは、補間器は  $\times 4$  補間器とすることができます。他のケースでは、補間器は他のタイプの補間器とすることができます。図 6 - 2 は、第 1 のステージにおいて第 1 の半値フィルタを使用し、それに続く第 2 のステージにおいて第 2 の半値フィルタおよび第 3 の半値フィルタを使用することによって、2 ステージの補間を提供するように構成される、 $\times 4$  補間器の例を示す。第 1 の半値フィルタ (HBF1) は 6 つの固有の係数を提供し、第 2 および第 3 の半値フィルタ (HBF2) の各々は、3 つの固有の係数を提供する。

20

#### 【0073】

マグニチュード 2 乗ユニット 608 は、補間された信号 604 を受信するように、および、それらのマグニチュードを取り、それらを 2 乗することによって、補間された信号 604 に基づいてマグニチュード 2 乗信号 610 を生成するように、構成される。

#### 【0074】

第 1 のディレイ 612 は、マグニチュード 2 乗信号 610 を受信するように、および遅延マグニチュード 2 乗信号 614 を作り出すためにマグニチュード 2 乗信号 610 を遅延させるように、構成される。

30

#### 【0075】

ピーク I D ユニット 616 は、遅延マグニチュード 2 乗信号 614 を受信するように、および、遅延マグニチュード 2 乗信号 614 に基づいて、マグニチュード 2 乗信号 614 に関するピーク位置の識別子 618 を決定するように構成される。ピーク位置の識別子 618 は、分数口ケータ 628 に渡される。いくつかのケースでは、ピーク I D ユニット 616 は、信号のマグニチュードの時系列を検査するように構成可能である。現在のマグニチュードがいずれかの側のサンプルのマグニチュードよりも大きい場合、現在の時間位置はピークとしてフラグが立てられる。識別された時間位置は、ピーク位置の識別子 618 の例と見なすことができる。いくつかのケースでは、ピーク I D ユニット 616 が入力信号の複数のデータポイントを順次受信するように、ディレイ 612 からの遅延が提供される。たとえばピーク I D ユニット 616 は、入力信号から 7 つのデータポイントを受信することができる。ピーク I D ユニット 616 はこの 7 つのデータポイントを検査して、ピークが存在するかどうかを判別し、ピークが見つかった場合はピークインデックスを出力する。このピークインデックスは、見つかったピーク値およびいずれかの側の近隣を選択するために使用可能である。たとえば、入力信号は以下の通りである。

40

時間インデックス サンプルのマグニチュード

|   |   |

|---|---|

| 0 | 0 |

| 1 | 1 |

| 2 | 2 |

| 3 | 3 |

50

|   |   |  |

|---|---|--|

| 4 | 2 |  |

| 5 | 1 |  |

| 6 | 0 |  |

## 【0076】

そこでサンプル数3（上記の例では値3）は、サンプル2（値2を有する）およびサンプル4（値2を有する）より大きい。したがってピークは時間3に位置し、マグニチュードは3である。上記の例に続き、後続の処理ではマグニチュードを調べ、信号が補間されている場合、時間3に対する分数オフセットを見つける。他の実施形態において、ピークIDユニット616は、遅延マグニチュード2乗信号とは異なる他のパラメータに基づいて、ピーク位置の識別子618を決定するように構成可能である。たとえば、他のケースでは、ピークIDユニット616は、ピーク位置の識別子618を決定するために、マグニチュードが単調な任意の関数を使用するように構成可能である。たとえばいくつかのケースでは、ピーク位置の識別子618を決定するために、ピークIDユニット616によって複合値( $\sqrt{x^*x + y^*y}$ )、ここで $x$ および $y$ は、複合値の実成分および虚数成分である)のマグニチュードを使用することができる。10

## 【0077】

第1のマルチプレクサ620は、遅延マグニチュード2乗信号614を受信するように、および第1の多重出力信号622を作り出すために遅延マグニチュード2乗信号614を処理するように、構成される。第1の多重出力信号622は、遅延マグニチュード2乗信号614に比べて少ない数のデータを有する。いくつかのケースでは、第1のマルチプレクサ620は、見つかった最大のサンプルマグニチュードと、識別されたピークに隣接する(たとえば、前後の)サンプルのサンプルマグニチュードとを選択するように構成される。したがっていくつかのケースでは、第1の多重出力信号622は、ピークマグニチュードおよび隣接マグニチュードを含むことができる。たとえば第1の多重出力信号622は、望ましい補間の順序に応じて、ピークマグニチュードと、2つまたはそれ以上の隣接マグニチュードとを含むことができる。ピークのそれぞれの側に3つの隣接するマグニチュードが望ましい場合、第1の多重出力信号622は7つのデータ(ピークマグニチュード、およびピークのそれぞれの側に3つの隣接マグニチュード)を含むことになる。ピークのそれぞれの側に1つの隣接マグニチュードが望ましい場合、第1の多重出力信号622は、3つのデータ(ピークマグニチュード、およびピークのそれぞれの側に1つの隣接マグニチュード)を含むことになる。20

## 【0078】

微分フィルタ624は、マルチプレクサ620から第1の多重出力信号622を受信するように、および、第1の多重出力信号622について多項式(ピークマグニチュードおよびピークの隣の隣接マグニチュードを表す、データポイントを有する)をフィットさせるように、構成される。特に、ピークが識別および分離されると、位置およびマグニチュードをピークでフィットせるように補間が実行される。補間は、2次補間または他の次の補間とすることができます。サンプルは、微分フィルタ624を使用して2次多項式(または他の次数を有する多項式)とフィットされる。いくつかのケースでは、微分フィルタ624は、第1の多重出力信号622をフィットさせるために使用される第1の多項式に関する係数626を作り出す。30

## 【0079】

分数口ケータ628は、第1の微分フィルタ624からの第1の多項式に関する係数626およびピークIDユニット616からのピーク位置の識別子618を受信するように、ならびに、第1の多項式に関する係数626およびピーク位置の識別子618に基づいて(たとえば、使用して)、ピークの分数位置664を決定するように、構成される。いくつかのケースでは、ピーク分数位置664は、2次多項式 $y(t) = a + b * t + c * t^2$ の係数に基づいて決定することが可能である。このようなケースでは、ピーク分数位置664は、 $-b / c / 2$ で微分することおよび根を見つけることによって計算可能である。4050

## 【0080】

第1の分数補間器632は、ピークの分数位置664および(分数口ケータ628によって渡される)第1の多項式に関する係数626を受信するように、ならびに、ピークの分数位置664および第1の多項式に関する係数626に基づいて(たとえば、使用して)、第1の多項式のピーク振幅634を決定するように、構成される。いくつかのケースでは、ピーク振幅534は、数式 $a + 1 . 5 * b * f$ を評価することによって決定可能であり、aおよびbは、多項式 $y(t) = a + b * t + c * t^2$ の係数であり、fは分数位置664である。

## 【0081】

第1の微分フィルタ624、分数口ケータ628、および分数補間器632によって実行される演算により、ピーク検出器は、入力信号( $x_k$ )に関する多項式フィットを決定し、多項式からピーク位置を決定し、多項式フィットからピーク位置での信号のマグニチュードを決定することが可能になる。10

## 【0082】

第1の乗算器638は、第1の多項式のピーク振幅634およびスケーリングファクタ636を受信するように、ならびに、第1の多項式のスケーリングされたピーク振幅640を作り出すために、第1の多項式のピーク振幅634とスケーリングファクタ636とを乗算するように、構成される。いくつかのケースでは、スケーリングファクタ636は、1をしきい値の2乗で割った(たとえば、 $1 / T^2$ )ものとすることができます。他のケースでは、スケーリングファクタ636は他の値とすることができます。20

## 【0083】

利得生成器642は、第1の多項式のスケーリングされたピーク振幅640を受信するように、および、第1の多項式のスケーリングされたピーク振幅640に基づいて(たとえば、使用して)ウィンドウ利得( $G_k$ )644を生成するように、構成される。いくつかのケースでは、ウィンドウ利得644は $1 - 1 / \sqrt{r}t(A)$ となるように決定可能であり、ここでAはスケーリングされたピーク振幅640、またはスケーリングされたピーク振幅640の2乗である。他のケースでは、ウィンドウ利得644は $1 - 1 / \sqrt{r}t(A/T^2)$ となるように決定可能である。また他のケースでは、ウィンドウ利得644は他の数式に基づいて決定可能である。またいくつかのケースでは、利得生成器642は、図2-1のシステム200内の最大実行フィルタ210にウィンドウ利得( $G_k$ )644を渡すように構成可能である。30

## 【0084】

図6-1に示されるように、第2のディレイ646は、補間器602から補間された信号604を受信するように、および、遅延された補間信号648を作り出すために補間された信号604を遅延せるように、構成される。

## 【0085】

第2のマルチブレクサ650は、遅延された補間信号648を受信するように、および、第2の多重出力信号652を作り出すために遅延された補間信号648を処理するように、構成される。いくつかのケースでは、第2のマルチブレクサ650は、マルチブレクサ620によって選択されたものに時間的に対応する遅延された補間信号648からデータを選択するように構成される。第2の多重出力信号652は、遅延された補間信号648に比べて数の少ないデータを有する。40

## 【0086】

第2の微分フィルタ654は、第2の多重出力信号652を受信するように、および、第2の多項式に関する係数656を作り出すために第2の多重出力信号652を処理するように、構成される。第2の微分フィルタ654によって実行される動作は、第1の微分フィルタ624を参照しながら説明した動作と同様である。第1の多項式および第2の多項式は異なり、係数626、656も異なることに留意されたい。これは、図6-1内のピーク検出器205の上方分岐がマグニチュードに関して動作し、下方分岐がピークでの複合値の計算用であるためである。したがって、上方分岐に関する係数652は実数であ50

り、下方分岐に関する係数 656 は複素数である。また、いくつかのケースでは、第1の多項式および / または第2の多項式は2次多項式とすることができます。他のケースでは、第1の多項式および / または第2の多項式は、他の次数の多項式とすることができます。

#### 【0087】

第2の分数補間器 658 は、分数口ケータ 628 からの分数位置 664 および第2の多項式に関する係数 656 を受信するように、ならびに、分数位置 664 および第2の多項式に関する係数 656 に基づいて(たとえば、使用して)、出力 660 を生成するように構成される。いくつかのケースでは、出力 660 は数式  $a + b * f + c * f^2$  を評価することによって決定可能であり、ここで  $a$ 、 $b$ 、および  $c$  は多項式  $y(t) = a + b * t + c * t^2$  の係数であり、 $f$  は分数位置 664 である。

10

#### 【0088】

第2の乗算器 662 は、信号 660 およびウィンドウ利得 ( $G_k$ ) 644 を受信するように、ならびに、波高ピーク利得 (CPG) を作り出すために信号 660 とウィンドウ利得 ( $G_k$ ) 644 とを乗算するように構成される。

#### 【0089】

いくつかのケースでは、ピーク検出器 205 は少なくとも1つのFPGAを使用して実装可能である。たとえばいくつかのケースでは、FPGA は、補間器 602、マグニチュード2乗ユニット 608、第1のディレイ 612、ピークIDユニット 616、第1のマルチプレクサ 620、第1の微分フィルタ 624、分数口ケータ 628、第1の分数補間器 632、第1の乗算器 638、利得生成器 642、第2のディレイ 646、第2のマルチプレクサ 650、第2の微分フィルタ 654、第2の分数補間器 658、第2の乗算器 662、またはそれらの任意の組み合わせを実装するように構成可能である。他のケースでは、ピーク検出器 205 は、汎用プロセッサ、ASIC プロセッサ、マイクロプロセッサ、または他のタイプのプロセッサなどの、集積回路を使用して実装可能である。さらなるケースでは、ピーク検出器 205 はハードウェア、ソフトウェア、またはその両方の組み合わせを使用して実装可能である。

20

#### 【0090】

図 6 - 1 のピーク検出器 205 は、PCCR に使用可能であることに留意されたい。こうしたケースでは、ピーク検出器 205 は、ピークおよび CPG の分数位置 664 を出力するだけでよい可能性がある。他のケースでは、ウィンドウ CFR が使用される場合、ピーク検出器 205 の下方分岐(すなわち、第2のディレイ 646、第2のマルチプレクサ 650、第2の微分フィルタ 654、第2の分数補間器 658、および第2の乗算器 662) は任意選択であり、必要でない可能性がある。こうしたケースでは、ピーク検出器 205 は、ピークの分数位置 664 および ウィンドウ利得 644 を出力するだけでよい可能性がある。

30

#### 【0091】

また、図 6 - 1 に示されるピーク検出器 205 は、ピーカスケーリングユニットを含むことに留意されたい。特に、乗算器 638 および 利得生成器 642 は、図 2 - 1 の ウィンドウ CFR プロセッサ 220 のためのピーカスケーリングユニット 206 を構成することができる。こうしたケースでは、ウィンドウ CFR プロセッサ 220 はピーカスケーリングユニット 206 を含まなくてよい。他のケースでは、乗算器 638 および 利得生成器 642 を、ピーカスケーリングユニット 206 として図 2 - 1 の ウィンドウ CFR プロセッサ 220 に組み込むことができる。また、ピーク検出器 205 が図 5 - 1 または図 5 - 2 の PCCR プロセッサと共に使用されるケースでは、乗算器 638、利得生成器 642、および 乗算器 662 は、図 5 - 1 または図 5 - 2 の PCCR プロセッサのためのピーカスケーリングユニット 206 を構成することができる。こうしたケースでは、図 5 - 1 または図 5 - 2 の PCCR プロセッサ 220 は、ピーカスケーリングユニット 206 を含まなくてよい。他のケースでは、乗算器 638、利得生成器 642、および 乗算器 638 を、ピーカスケーリングユニット 206 として図 5 - 1 または図 5 - 2 の PCCR プロセッサ 220 に組み込むことができる。

40

50

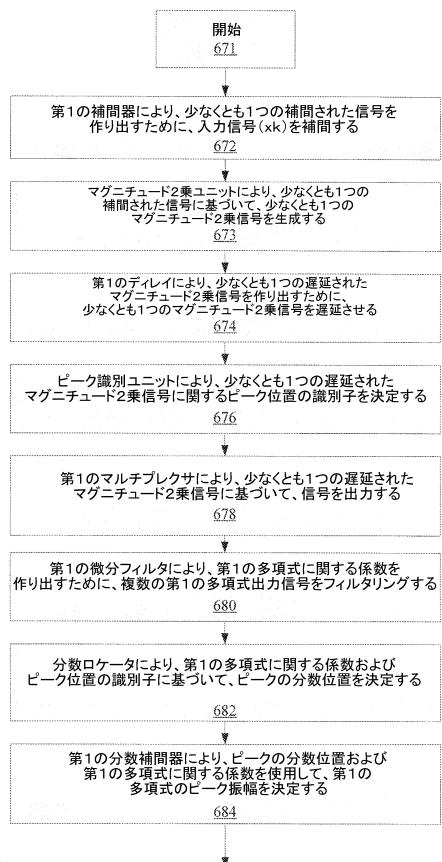

**【0092】**

図6-3および図6-4は、図6-1のピーク検出器205によって実行可能な方法670を示す。他のケースでは、方法670は他のピーク検出器によって実行可能である。項目671で、方法が開始される。

**【0093】**

補間器が、少なくとも1つの補間された信号を作り出すために、入力信号( $x_k$ )を補間する(項目672)。いくつかのケースでは、項目672はピーク検出器205内の補間器602によって実行可能である。

**【0094】**

次に、マグニチュード2乗ユニットが、少なくとも1つの補間された信号に基づいて、

10

少なくとも1つのマグニチュード2乗信号を生成する(項目673)。いくつかのケース

では、項目673はピーク検出器205内のマグニチュード2乗ユニット608によって

実行可能である。

**【0095】**

次に、第1のディレイがその後、少なくとも1つの遅延されたマグニチュード2乗信号

を作り出すために、少なくとも1つのマグニチュード2乗信号を遅延させる(項目674)

。いくつかのケースでは、項目674はピーク検出器205内の第1のディレイ612

によって実行可能である。

**【0096】**

加えて、ピークIDユニットが、少なくとも1つの遅延されたマグニチュード2乗信号

に関するピーク位置の識別子を決定する(項目676)。いくつかのケースでは、項目6

20

76はピーク検出器205内のピークIDユニット616によって実行可能である。

**【0097】**

第1のマルチプレクサがその後、少なくとも1つの遅延されたマグニチュード2乗信号

に基づいて、多重出力信号を作り出すために少なくとも1つの遅延されたマグニチュード

2乗信号を受信する(項目678)。いくつかのケースでは、項目678はピーク検出器

205内の第1のマルチプレクサ620によって実行可能である。

**【0098】**

次に、第1の微分フィルタが、第1の多項式に関する係数を決定するために、マルチブ

レクサから出力信号を受信する(項目680)。いくつかのケースでは、項目680はピ

ーク検出器205内の第1の微分フィルタ624によって実行可能である。

30

**【0099】**

分数口ケータがその後、第1の多項式に関する係数およびピーク位置の識別子に基づい

て、ピークの分数位置を決定する(項目682)。いくつかのケースでは、項目682は

ピーク検出器205内の分数口ケータ628によって実行可能である。

**【0100】**

第1の分数補間器がその後、ピークの分数位置および第1の多項式に関する係数に基づ

いて、第1の多項式のピーク振幅を決定する(項目684)。いくつかのケースでは、項目

684はピーク検出器205内の第1の分数補間器632によって実行可能である。

**【0101】**

第1の乗算器が、第1の多項式のスケーリングされたピーク振幅を作り出すために、第

1の多項式のピーク振幅とスケーリングファクタとを乗算する(項目686)。いくつかの

ケースでは、項目686はピーク検出器205内の第1の乗算器638によって実行可

能である。

**【0102】**

その後、利得生成器が、第1の多項式のスケーリングされたピーク振幅に基づいて、ウ

ィンドウ利得( $G_k$ )を生成する(項目688)。いくつかのケースでは、項目688は

ピーク検出器205内の利得生成器642によって実行可能である。

**【0103】**

第2のディレイが、少なくとも1つの遅延された補間信号を作り出すために、少なくと

50

も 1 つ の 補 間 信 号 を 遅 延 さ せ る ( 項 目 6 9 0 ) 。 い く つ か の ケ ー ス で は 、 項 目 6 9 0 は ピ ー ク 検 出 器 2 0 5 内 の 第 2 の デ イ レイ 6 4 6 に よ っ て 実 行 可 能 で あ る 。

#### 【 0 1 0 4 】

次 に 、 第 2 の マ ルチ プ レクサ が 、 多 重 出 力 信 号 を 作 り 出 す た め に 、 少 な く と も 1 つ の 遅 延 さ れ た 補 間 信 号 を 处 理 す る ( 項 目 6 9 2 ) 。 い く つ か の ケ ー ス で は 、 項 目 6 9 2 は ピ ー ク 検 出 器 2 0 5 内 の 第 2 の マ ルチ プ レクサ 6 5 0 に よ っ て 実 行 可 能 で あ る 。

#### 【 0 1 0 5 】

次 に 、 第 2 の 微 分 フ ィルタ が 、 第 2 の 多 項 式 に 関 す る 係 数 を 作 り 出 す た め に 、 第 2 の マ ルチ プ レクサ 6 5 0 か ら の 出 力 信 号 を 处 理 す る ( 項 目 6 9 4 ) 。 い く つ か の ケ ー ス で は 、 項 目 6 9 4 は ピ ー ク 検 出 器 2 0 5 内 の 第 2 の 微 分 フ ィルタ 6 5 4 に よ っ て 実 行 可 能 で あ る 。

10

#### 【 0 1 0 6 】

次 に 、 第 2 の 分 数 補 間 器 が そ の 後 、 分 数 口 ケ ー タ か ら の 信 号 お よ び 第 2 の 多 項 式 に 関 す る 係 数 を 使 用 す る た め に 、 第 2 の 分 数 補 間 器 6 5 0 か ら の 出 力 信 号 を 处 理 す る ( 項 目 6 9 6 ) 。 い く つ か の ケ ー ス で は 、 項 目 6 9 6 は ピ ー ク 検 出 器 2 0 5 内 の 第 2 の 分 数 補 間 器 6 5 8 に よ っ て 実 行 可 能 で あ る 。

#### 【 0 1 0 7 】

そ の 後 、 第 2 の 乗 算 器 が 、 波 高 ピ ー ク 利 得 ( C P G ) を 作 り 出 す た め に 、 第 2 の 分 数 補 間 器 か ら の 出 力 と ウ ィ ン ド ウ 利 得 ( G<sub>k</sub> ) と を 乘 算 す る ( 項 目 6 9 8 ) 。 い く つ か の ケ ー ス で は 、 項 目 6 9 8 は ピ ー ク 検 出 器 2 0 5 内 の 第 2 の 乗 算 器 6 6 2 に よ っ て 実 行 可 能 で あ る 。

そ の 後 、 方 法 6 7 0 は 項 目 6 9 9 で 終 了 す る 。

20

#### 【 0 1 0 8 】

い く つ か の ケ ー ス で は 、 方 法 6 7 0 は 項 目 6 9 0 、 6 9 2 、 6 9 4 、 6 9 6 、 お よ び 6 9 8 を 含 ま な く て よ く 、 こ れ ら の 項 目 は 任 意 選 択 で あ る 。

#### 【 0 1 0 9 】

上 記 の 例 で 示 さ れ る よ う に 、 開 示 さ れ た ピ ー ク 検 出 器 2 0 5 お よ び ピ ー ク 検 出 の た め の 方 法 6 7 0 は 、 信 号 マ グニ チュード に 対 し て 多 項 式 フ ィット ( た と え ば 、 2 次 フ ィット ) を 実 行 す る こ と 、 お よ び そ の 後 ピ ー ク 位 置 を 抽 出 す る こ と に よ っ て 、 オ ーバー サンプリング の 量 を 制 限 す る 。

多 項 式 フ ィット か ら 、 非 常 に 高 い サンプリング レート を 伴 う ピ ー ク が 見 つ か た か の よ う に 、 そ の 位 置 で の 信 号 の マ グニ チュード を 計 算 す る た め に ピ ー ク 位 置 が 使用 さ れ る 。

い く つ か の ケ ー ス で は 、 ピ ー ク で の 複 合 値 が 必 要 な 場 合 、 導 関 数 お よ び 2 次 導 関 数 を 決 定 す る こ と が 可 て 、 そ の 後 多 項 式 フ ィット で 使用 す る こ と が 可 て 。

ま た い く つ か の ケ ー ス で は 、 ピ ー ク 周 辺 の よ り 多 く の サンプル を フ ィット さ せ る た め に 、 よ り 高 次 の 多 項 式 を 使用 す る こ と が 可 て 。

しか し な が ら 、 ほ と ん ど の 適 用 例 で は 、 複 雜 さ と パ フ ォ ー マ ンス と の 間 の ト レ ー ド オ フ に と て 2 次 多 項 式 が よ り 良 好 で あ る と 見 な し 得 る 。

ま た い く つ か の ケ ー ス で は 、 マ グニ チュード 2 乗 デ ー タ を 分 数 オ フ セ ッ ト 計 算 で 使用 す る こ と が 可 て 。

こ れ は 、 信 号 マ グニ チュード の 検 出 に は よ り 高 い サンプリング レート が 必 要 な 可 能 性 が あ る と い う 事 実 に よ る 。

マ グニ チュード 2 乗 デ ー タ は 、 入 力 サンプル 帯 域 幅 の 2 倍 ( ま た は 他 の 規 定 値 ) を 超 え る こ と が で き な い 帯 域 幅 を 有 す る こ と が 保 証 さ れ 得 、 そ れ に よ って 所 与 の 精 度 要 件 に 必 要 な オ ーバー サンプリング の 量 が 低 減 さ れ る 。

30

#### 【 0 1 1 0 】

上 記 手 法 は 、 ピ ー ク 検 出 器 2 0 5 が C F R で 必 要 な 精 度 お よ び リ ソ ース を 左 右 で き る た め 、 C F R の よ り 統 一 的 な 設 計 お よ び 最 適 化 も 可 能 に す る 。

ウ ィ ン ド ウ C F R お よ び P C C F R に お い て 、 フ イルタ リ ン グ ス テ ー ジ は ナ イ キ 料 ト サンプリング レート 付 近 で 実 行 可 能 で あ る 。

ピ ー ク 検 出 器 後 处 理 は 信 号 上 の ほ ぼ 線 形 動 作 で あ る た め 、 そ れ に よ り 、 ピ ー ク 検 出 器 2 0 5 に よ る 处 理 後 に 必 要 な リ ソ ース が 削 減 さ れ る 。

ピ ー ク 検 出 器 2 0 5 のみ が 、 補 間 ま た は 他 の 同 等 の 处 理 を 必 要 と す る 。

ピ ー ク 検 出 器 2 0 5 を 多 相 手 法 で 実 装 す る こ と に よ って 、 設 計 全 体 が 可 能 最 低 レート で 動 作 可 能 で あ る 。

そ れ に よ り 、 従 来 の 手 法 に 比 べ て よ り 高 帯 域 幅 の 信 号 を 处 理 す る こ と が 可 て 。

40

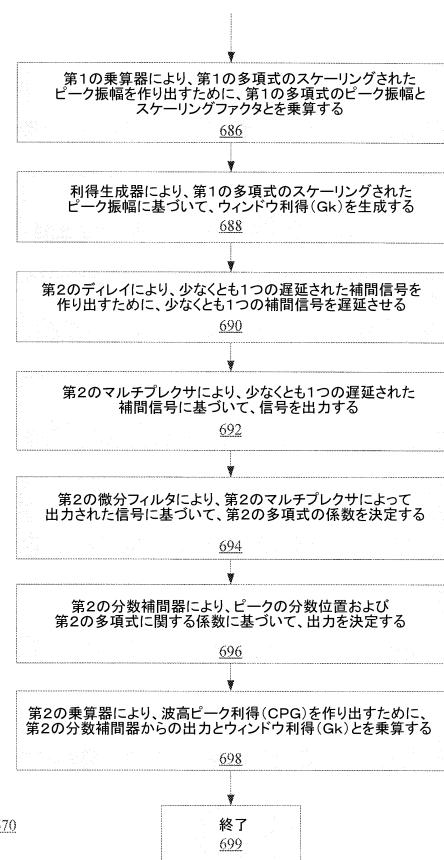

#### 【 0 1 1 1 】

図 7 は 、 開 示 さ れ た シ ス テ ム お よ び 方 法 を 使 用 す る こ と で 達 成 さ れ る 結 果 の 例 を 示 す グ ラフ 7

50

00である。結果は、図2-2を参照しながら説明したような、ウィンドウC F Rプロセッサを使用して生成される。グラフ700は複数の矩形ボックス710を含む。各矩形ボックス710は幅Nを有し、入力信号( $x_k$ )の振幅増加に従う最大実行フィルタ出力の時間履歴を表す。それぞれの矩形ボックス710の中心( $N/2$ )にある垂直ピーク720は、C F Rに関するウィンドウ関数の中心の位置およびそのピーク振幅を表す。滑らかな曲線730は、出力信号( $y_k$ )がしきい値( $T$ )を超えるのを防ぐために入力信号( $x_k$ )に適用される、利得補正( $F_k$ )を表す。連続する利得補正 $F_k$ の適用により、出力信号( $y_k$ )が必要なスペクトル範囲内に維持される。図に示されるように、最大実行フィルタを使用することで、小さいピークの寄与がカウントされないように小さいピークはほとんど陰になり、比較的大きいピークで隠されている。この発見は、ウィンドウC F Rプロセッサの実装を大幅に簡略化し、C F Rサブシステムにおける実質的な最終ステージにしている。最終ステージにウィンドウC F Rプロセッサを含むシステムの例は、図8を参照しながら以下で説明する。

#### 【0112】

また図7に示されるように、曲線730(最大実行フィルタおよび後続の線形フィルタを使用して作成される信号)は、ピーク720を超える境界を非常に適切に示しており、帯域が制限されている。したがって、最大実行フィルタおよび後続の線形フィルタを使用することは、ウィンドウC F R利得プロファイル(曲線730によって表される)を作成する際の、非常に簡単かつ効果的な技法であることがわかっている。存在するすべてのピークを超える境界を示す帯域制限信号を作成するために、他の技法も使用可能であるが、より複雑であり、結果としてパフォーマンスが低下する、かつ/または、すべてのピークを超える境界を示す信号を作成することができない。

#### 【0113】

ウィンドウC F Rを利用することの利点は、検出時にピークが見失われるのを防ぐこと、および出力時に新しいピークが発生するのも防ぐことであることに留意されたい。ウィンドウC F Rを使用することの欠点は、パフォーマンス(エラーベクトルマグニチュード(EVM)対P A Rなどのメトリクスによって測定可能である)がP C C F R法ほど良好でない可能性があることである。しかしながら、P C C F RとウィンドウC F Rとを組み合わせて使用することは、複雑さおよびパフォーマンスの観点から良好な妥協点をもたらす。P C C F Rが良好なEVMを用いてピークのほとんどを消去する場合、ウィンドウC F Rを使用して残りのピークを「クリーンアップ」することができる。残りのピークがわずかである場合、より多くのP C C F Rのステージを使用することに比べて、ウィンドウC F Rを使用することによる劣化は非常に小さい。したがっていくつかのケースでは、ウィンドウC F Rを1つまたは複数のP C C F Rステージ後の後処理として使用することができる。しかしながら、他のケースでは、ウィンドウC F Rを1つまたは複数のP C C F Rステージの前に使用すること、あるいはいずれのP C C F Rステージもなしに単独で使用することが可能である。

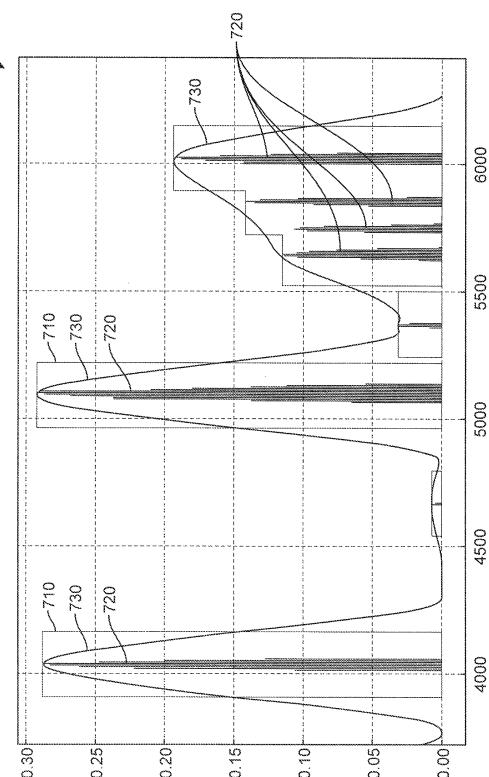

#### 【0114】

いくつかのケースでは、ウィンドウC F Rとピークキャンセル波高率低減(P C C F R)との組み合わせを使用することが望ましい可能性がある。図8は、ウィンドウC F RおよびP C C F Rの組み合わせを含むシステムを示す。図に示されるように、システムは第1のP C C F Rモジュール910、第2のP C C F Rモジュール912、およびウィンドウC F Rモジュール914を有する。いくつかのケースでは、第1のP C C F Rモジュール910および/または第2のP C C F Rモジュール912は、図5-1または図5-2のP C C F Rプロセッサを使用して実装可能である。またいくつかのケースでは、ウィンドウC F Rモジュール914は、図2-2のウィンドウC F Rプロセッサを使用して実装可能である。第1のP C C F Rモジュール910は、入力信号を受信するように、および、第1のP C C F R出力を取得するために第1のP C C F Rを実行することによって入力信号を処理するように、構成される。いくつかのケースでは、第1のP C C F R出力は入力信号を含むが、1つまたは複数のピークの第1のセットは除去されている。第2のP C

10

20

30

40

50

CFR モジュール 912 は、第 2 の PCCR 出力を取得するために、第 2 の PCCR を実行することによって第 1 の PCCR 出力を処理するように構成される。いくつかのケースでは、第 2 の PCCR 出力は入力信号を含むが、1つまたは複数のピークの第 2 のセットは除去されている。ウインドウ CFR モジュール 912 は、第 2 の PCCR 出力を受信するように、および CFR 出力を取得するためにウインドウ CFR を実行するように、構成される。いくつかのケースでは、CFR 出力は入力信号を含むが、1つまたは複数の追加のピークは（ピークの第 1 および第 2 のセットが第 1 の PCCR モジュール 910 および第 2 の PCCR モジュール 912 によって除去された後に）除去されている。例示された図では、2ステージの PCCR を実行するために 2つの PCCR モジュール 912、914 が存在する。他のケースでは、1ステージのみの PCCR を実行するために 1つのみの PCCR モジュールが存在してもよい。さらなるケースでは、2つを超えるそれぞれのステージの PCCR を実行するために 2つを超える PCCR モジュールが存在してもよい。他のケースでは、多重ステージの PCCR を実装するために PCCR モジュールを使用することができる。

10

#### 【0115】

図 8 のシステムは、PCCR 単独の使用およびウインドウ CFR 単独の使用全体にわたって有利である。PCCR は単独で使用される場合、ウインドウ CFR よりも EVM 対 PAR が良好であるという利点を有する。しかしながら PCCR は、CPG リソースの欠如により、いくつかのピークが見失われる可能性があり、PCCR に関するキャンセルパルスが新しいピークを出力に導入する可能性があるという事実により、損害を被る。したがって、PCCR を使用する場合、信号内のすべてのピークを除去するために複数のパスが必要な可能性がある。このデータの再処理が追加の遅延を招き、この待ち時間により基地局のパフォーマンスを低下させる可能性がある。待ち時間が長い場合、スマートフォンへの制御情報が遅延し、データフローの変化に対する反応性が低下する。この影響で、携帯電話上でサポート可能なピークデータレートが低下し、待ち時間が長すぎる場合、他の悪影響を生み出す可能性がある。PCCR を適用する場合、信号からすべてのピークを除去するために 4ステージの処理を使用することが可能であり、1ステージを介する遅延の 4 倍の遅延を招く。他方で、ウインドウ CFR が単独で使用される場合、その動作中にピークが見失われることがないという利点を有する。ウインドウ CFR の欠点は、いくつかのピークが過度にキャンセルされる可能性がある場合、EVM 対 PAR パフォーマンスがより高くなることである。PCCR および WCFR の組み合わせは、両方の方法の利点から恩恵を受けることができる。

20

30

#### 【0116】

図 8 のシステムにおいて、入力信号が 1つまたは複数の PCCR ステージによって最初に処理される場合、入力信号内のほとんどのピークを除去するか、または低レベルまで低減させることができる。その後、わずかな残りのピークを除去するためにウインドウ CFR が使用される場合、PCCR ステージでほとんどのピークが除去されているため、ウインドウ CFR によって導入される追加の EVM は、PCCR が単独で使用される場合に比べてかなり低くなる。いくつかのケースでは、1つのみの PCCR ステージおよび 1つのウインドウ CFR ステージを使用することができる。結果として生じる PCCR および WCFR を介した遅延は同等であるが、パフォーマンスは 4ステージ PCCR とほぼ同様に良好である。したがってこうした組み合わせは、処理および遅延が（PCCR が単独で使用される場合に比べて）半分で、許容可能なパフォーマンスを達成するため、システム経費が削減される。

40

#### 【0117】

前述の方法（たとえば方法 250、670）は、ある順序で発生するあるイベントを示している。他のケースでは、方法におけるイベントの順序は異なってよい。加えて、方法の各部分は、可能であれば並列処理で同時に実行可能であるか、または逐次的に実行可能である。加えて、方法のより多くの部分またはより少ない部分を実行することができる。

#### 【0118】

上記の実施形態では、ウインドウ C F R を参照しながらピーク検出器 205 およびピーク検出のための方法 670 を説明してきた。しかしながら他のケースでは、ピーク検出器 205 およびピーク検出のための方法 670 を他の領域で適用可能である。たとえば他のケースでは、ピーク検出器 205 およびピーク検出のための方法 670 をイメージ処理に使用することができる。いくつかのケースでは、ピーク検出器 205 および方法 670 は、回転前、スケーリング前、または、イメージ内のピクセル値が線形変換処理のいずれかをオーバーフローさせてしまわないことを保証するための他のイメージ処理動作の前に、イメージスケーリングのための真のイメージピークを確立するために、イメージ処理で使用することができる。他のケースでは、ピーク検出器 205 および方法 670 は、コントラスト促進のためのイメージ処理、ガンマ補正、および / または他の非線形処理で使用することができる。さらなるケースでは、ピーク検出器 205 およびピーク検出のための方法 670 は、自動利得制御で使用することができる。たとえばいくつかのケースでは、ピーク検出器 205 および方法 670 は、デジタル処理のため、あるいは無線またはレーダなどの適用例でのアナログ回路による処理のための、最適な範囲内に信号を配置するように、自動利得制御のためのピーク信号レベルを検出するために使用することができる。さらに他のケースでは、ピーク検出器 205 およびピーク検出のための方法 670 は、2乗平均平方根 (RMS) 検出器、ログ検出器などの、任意のタイプの検出器内で実装可能である。いくつかのケースでは、ピーク検出器 205 からの出力は、信号の PAR を測定するために RMS 検出器で使用することができる。またいくつかのケースでは、ピーク検出器 205 はデジタル版の AM 検出器を実装するために使用可能である。他のケースでは、ピーク検出器 205 は、等価版のデジタルログ検出器を実装するために使用可能である。10

#### 【 0119 】

特定の実施形態について図示および説明してきたが、請求される本発明を限定することは意図していないことを理解されよう。したがって明細書および図面は、限定的ではなく例示的な意味であるものと見なされる。請求される本発明は、代替、改変、および等価をカバーすることが意図される。20

【図 1 - 1】

【図 1 - 2】

【図 1 - 3】

【図 2 - 1】

【図2-2】

【図2-3】

【図3】

【図4-1】

【図 4 - 2】

$$\begin{aligned} \tilde{G}_k &= 1 - 1/\sqrt{A/T^2} \\ F_k &= G_k * W \\ Y_k &= X_k - \underbrace{F_k * X_k}_{\text{ピ-ク補正}} \end{aligned}$$

【図 5 - 1】

【図 5 - 2】

【図 6 - 1】

【図 6 - 2】

【図 6 - 3】

【図 6 - 4】

【図 7】

【図8】

---

フロントページの続き

(56)参考文献 米国特許出願公開第2010/0027690(US,A1)

特開2007-251810(JP,A)

米国特許出願公開第2009/0029664(US,A1)

(58)調査した分野(Int.Cl., DB名)

H03H 17/00 - 17/08