(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-20171

(P2006-20171A)

(43) 公開日 平成18年1月19日(2006.1.19)

| (51) Int.C1.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>HO3K</b> 5/08 (2006.01)  | HO3K 5/08  | E 5C024     |

| <b>HO3M</b> 1/08 (2006.01)  | HO3M 1/08  | A 5J022     |

| <b>HO3M</b> 1/10 (2006.01)  | HO3M 1/10  | A 5J039     |

| <b>HO3M</b> 1/38 (2006.01)  | HO3M 1/38  |             |

| <b>HO4N</b> 5/335 (2006.01) | HO4N 5/335 | E           |

審査請求 未請求 請求項の数 10 O L (全 15 頁)

|           |                              |          |                                                   |

|-----------|------------------------------|----------|---------------------------------------------------|

| (21) 出願番号 | 特願2004-197329 (P2004-197329) | (71) 出願人 | 000005223<br>富士通株式会社<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 |

| (22) 出願日  | 平成16年7月2日 (2004.7.2)         | (74) 代理人 | 100074099<br>弁理士 大菅 義之                            |

|           |                              | (74) 代理人 | 100067987<br>弁理士 久木元 彰                            |

|           |                              | (72) 発明者 | 水口 寿孝<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内       |

|           |                              | (72) 発明者 | 船越 純<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内        |

最終頁に続く

(54) 【発明の名称】差動型コンパレータ、アナログ・デジタル変換装置、撮像装置

## (57) 【要約】

【課題】 より少ない消費電流で、高精度のアナログ・デジタル変換を実現することが可能なアナログ・デジタル変換装置を提供する。

【解決手段】 コラムADC回路60において、光電変換信号等のアナログ信号(ADC-in)とランプ波形信号RampVを比較する差動型コンパレータ61および62を多段に設け、差動型コンパレータ62の出力にてインバータ69を介してカウンタ71のラッチ回路70を制御することで、アナログ信号のカウント値のデジタル信号に変換するとともに、個々の差動型コンパレータ61, 62には、入力側および出力側と出力側を短絡するスイッチS1、短絡時のオフセット電圧を保持する容量素子C1, C2からなるオフセットキャンセル機能を設け、C1, C2にオフセットがキャンセルされたADC-inの電圧を保持してランプ波形信号RampVとの比較精度を向上させ、正確なデジタル変換を行う。

【選択図】図1

本発明の一実施の形態である差動型コンパレータを含むアナログ・デジタル変換装置の構成の一例を示すブロック図

**【特許請求の範囲】****【請求項 1】**

第1および第2入力端子の各々に入力される第1および第2入力信号レベルの一致／不一致に応じて出力端子に正および／または負の論理信号を出力する差動型コンパレータであって、

前記第1または第2入力端子の前記差動型コンパレータ側に設けられたオフセット容量素子と、前記オフセット容量素子を含む閉ループを形成するように前記第1および第2入力端子を短絡する第1スイッチと、前記オフセット容量素子と差動型コンパレータの接続点と前記出力端子とを短絡する第2スイッチとを含むオフセットキャンセル機能を備えたことを特徴とする差動型コンパレータ。

10

**【請求項 2】**

請求項1記載の差動型コンパレータにおいて、前段の前記差動型コンパレータから出力される正および負の前記論理信号を次段の前記差動型コンパレータの前記第1および第2入力端子に入力することで、前記差動型コンパレータを多段に接続したことを特徴とする差動型コンパレータ。

**【請求項 3】**

請求項1記載の差動型コンパレータにおいて、前記オフセット容量素子が設けられた前記第1または第2入力端子にはアナログ・デジタル変換対象のアナログ信号が入力され、他の前記第2または第1入力端子にはランプ波形信号が入力され、前記アナログ信号の入力契機から前記アナログ信号と前記ランプ波形信号のレベルが一致するまでの時間を計数するカウンタのオン／オフを前記出力端子の前記論理信号にて制御することで、前記アナログ信号を前記カウンタのカウンタ値としてデジタル変換するアナログ・デジタル変換器として機能することを特徴とする差動型コンパレータ。

20

**【請求項 4】**

第1および第2入力端子の各々に入力されるアナログ信号および基準信号の信号レベルの一致／不一致に応じて出力端子に正および／または負の論理信号を出力する差動型コンパレータと、前記論理信号にて起動および停止が制御されるカウンタとを含み、前記アナログ信号の入力契機から当該アナログ信号と前記基準信号とが一致するまでの間に前記カウンタにて計数されたカウンタ値を前記アナログ信号のデジタル変換値として出力するアナログ・デジタル変換装置であって、

30

前記差動型コンパレータは、前記第1入力端子の前記差動型コンパレータ側に設けられたオフセット容量素子と、前記オフセット容量素子を含む閉ループを形成するように前記第1および第2入力端子を短絡する第1スイッチと、前記オフセット容量素子と前記差動型コンパレータの接続点と前記出力端子とを短絡する第2スイッチとを含むオフセットキャンセル機能を備えたことを特徴とするアナログ・デジタル変換装置。

**【請求項 5】**

請求項4記載のアナログ・デジタル変換装置において、前段の前記差動型コンパレータから出力される正および負の前記論理信号を次段の前記差動型コンパレータの前記第1および第2入力端子に入力することで、前記差動型コンパレータを多段に接続したことを特徴とするアナログ・デジタル変換装置。

40

**【請求項 6】**

請求項4記載のアナログ・デジタル変換装置において、前記アナログ信号が入力される前記第1入力端子に接続され、当該アナログ信号を保持する信号用容量素子をさらに備えたことを特徴とするアナログ・デジタル変換装置。

**【請求項 7】**

請求項4記載のアナログ・デジタル変換装置において、前記基準信号はランプ波形信号であることを特徴とするアナログ・デジタル変換装置。

**【請求項 8】**

各々が光電変換素子を含む複数のピクセル部が行および列方向に二次元的に配列されたピクセルアレイと、個々の前記ピクセル部から出力される光電変換信号をデジタル信号に

50

変換するアナログ・デジタル変換器を含む読み出し回路を備えた撮像装置であって、

前記アナログ・デジタル変換器は、

第1および第2入力端子の各々に入力される前記光電変換信号および基準信号の信号レベルの一致／不一致に応じて出力端子に正および／または負の論理信号を出力する差動型コンパレータと、

前記第1入力端子に設けられたオフセット容量素子と、前記オフセット容量素子を含む閉ループを形成するように前記第1および第2入力端子を短絡する第1スイッチと、前記出力端子と前記オフセット容量素子が設けられた前記第1入力端子とを短絡する第2スイッチとを含むオフセットキャンセル機能と、

を備えたことを特徴とする撮像装置。

10

#### 【請求項9】

請求項8記載の撮像装置において、前記アナログ・デジタル変換器は、前記論理信号にて起動および停止が制御されることで前記アナログ信号の入力契機から当該アナログ信号と前記基準信号とが一致するまでの間に前記カウンタにて計数されたカウンタ値を前記アナログ信号のデジタル変換値として出力するカウンタをさらに含むことを特徴とする撮像装置。

#### 【請求項10】

請求項8記載の撮像装置において、前記アナログ・デジタル変換器には、前段の前記差動型コンパレータから出力される正および負の前記論理信号を次段の前記差動型コンパレータの前記第1および第2入力端子に入力することで、前記差動型コンパレータが多段に設けられていることを特徴とする撮像装置。

20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、差動型コンパレータ、アナログ・デジタル変換装置、撮像装置に関し、特に、C M O S (Complementary Metal Oxide Semiconductor: 相補型金属酸化膜半導体)イメージセンサにおける光電変換信号の読み出し回路等に適用して有効な技術に関する。

##### 【背景技術】

##### 【0002】

たとえば、C C D (Charge Coupled Device: 電荷結合素子)イメージセンサに比較して、周辺の画像処理回路との製造プロセスや動作電圧等の整合性がよく、撮像素子部分と画像処理回路やコントローラなどを1チップに集積することが容易である等の観点から、C M O Sイメージセンサが注目されている。

30

##### 【0003】

このC M O Sイメージセンサは、個々の画素部位において光電変換素子のみならず変換信号の増幅も行う構成であるため、光電変換信号の伝送過程でのノイズに強いという利点があるが、個々の画素部位における増幅器の特性のバラツキに起因する固定パターンノイズが問題となる。

##### 【0004】

このため、直交する行 (row: ロー) および列 (column: コラム) 方向に二次元的に配列された複数の画素の内、コラム方向の画素の組単位に、C D S (相関二重サンプリング) 回路やA D C (アナログ - デジタル変換) 回路をコラム数分だけ並列に並べて配置した構成の、いわゆるコラムA D C方式により、固定パターンノイズを低減する構成が知られている。

40

##### 【0005】

C M O SイメージセンサのコラムA D Cとして、たとえば特許文献1には、光の三原色の各カラーフィルタ毎に設けられた画素のコラムA D Cに対して、異なるアナログ比較基準電圧を選択的に出力することで、各色毎の緻密なカラー制御を実現しようとする技術が開示されている。すなわち、インバータを用いたチョッパ型コンパレータの入出力を短絡させて当該インバータを構成するトランジスタの寄生容量に起因する閾値電圧のシフト分

50

だけ、基準電圧をシフトさせることで、デジタル変換の精度を向上させようとするものである。

#### 【0006】

また、特許文献2には、インバータを二段に接続したチョッパ型比較器のランプ信号入力側にキャパシタを追加し、画素のリセットモード時のオフセット電圧を保持し、カウントモード時に入力されるランプ信号の電圧をオフセット電圧にて補正することで、ピクセル間に存在し得る固定パターン雑音を除去して画質を改善しようとする技術が開示されている。

#### 【0007】

特許文献3には、A/D変換器を構成するインバータに対する基準電圧をシフトさせることで、画素から出力される信号と、基準電圧とを比較するタイミングが、当該基準電圧が線型特性を持つ範囲内で行われるように制御することで、安定したアナログ・デジタル変換特性を実現しようとする技術が開示されている。

#### 【0008】

特許文献4には、複数のアナログ・デジタル変換器を有し、前記アナログ・デジタル変換器の出力を順次選択し、デジタル映像出力を得る固体撮像素子において、ノイズキャンセル(比較)部を、差動増幅器とインバータからなる複数段の増幅器で構成するとともに、2段目以降の増幅器にクランプ回路を設けた構成とすることで、複数の画素の読み出し信号の間で直流レベルの差が生じないようにして画質を向上させようとする技術が開示されている。

#### 【0009】

ところが、上述の特許文献1～4の技術では、いずれも、インバータを単独で、あるいは差動アンプと併用してアナログ・デジタル変換器のコンパレータを構成する場合における以下のような技術的課題を認識していない。

#### 【0010】

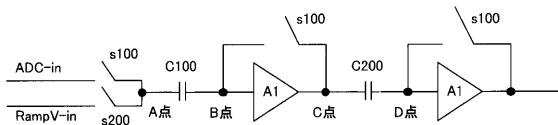

すなわち、図5は、本発明の参考技術であるチョッパ型コンパレータのブロック図である。この図5に示されるような、インバータA100を用いたチョッパ型コンパレータは、スイッチS100, S100×オン時にアナログ信号をC100に貯めて、S100, S100×オフ, S200オンで基準電圧と比較しコンパレータで判定を行うが、B点にはインバータA100を構成するトランジスタのゲート容量などの寄生容量(C200)があるため、比較のための基準電圧が入力されるとA点の電位が変化し、B点はA点の電位を基準にC100に貯めた電荷量分の電位に変化しようとするが、寄生容量C200があるため、B点はC100, C200の容量比で変化してしまい、アナログ・デジタル変換の精度が低下する、という技術的課題がある。

#### 【0011】

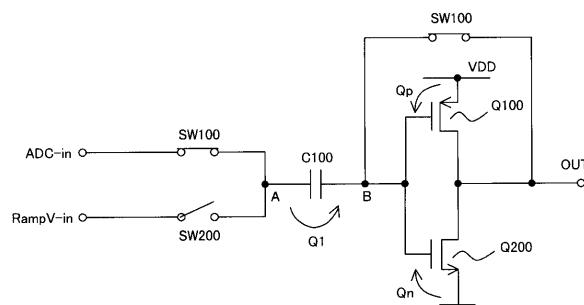

すなわち、図6に示されるように、インバータA100は、CMOSイメージセンサでは、p型のMOSトランジスタQ100と、n型のMOSトランジスタQ200(閾値V<sub>th</sub>)を電源VDDとグランドとの間に直列に設け、両者のゲートを入力とし、ソース間を出力(OUT)とする構成をとるが、Q100およびQ200の寄生容量Q<sub>p</sub>, Q<sub>n</sub>が入力側の容量C100に影響するため、たとえば、SW100をオフ、SW200をオンした時、RampVの入力に対して、Q100およびQ200のゲート電位は、V<sub>th</sub>-C100(ADC-RampV)/(C100+C<sub>p</sub>+C<sub>n</sub>)のように変動し、アナログ・デジタル変換の精度が低下する。

#### 【0012】

また、インバータを用いる構成では、インバータの消費電流が大きいため、特に、CMOSイメージセンサにおけるコラムADCのように、列単位に多数のADCを設ける構成では撮像素子全体のトータルの消費電流は極めて大きくなる。この対策として、Q100およびQ200のゲート長を大きくして消費電流を抑制することも考えられるが、ゲート面積の増大により、寄生容量Q<sub>p</sub>, Q<sub>n</sub>が一層大きくなるため好ましくない。

【特許文献2】特開2002-218324号公報

【特許文献3】特開2000-286706号公報

【特許文献4】特開2000-287137号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

本発明の目的は、より少ない消費電流で、高精度のアナログ・デジタル変換を実現することが可能な差動型コンパレータを提供することにある。

本発明の他の目的は、より少ない消費電流で、高精度のアナログ・デジタル変換を実現することが可能なアナログ・デジタル変換装置を提供することにある。 10

【0014】

本発明の他の目的は、より少ない消費電流で、高画質の映像データ出力することが可能な撮像装置を提供することにある。

【課題を解決するための手段】

【0015】

本発明の第1の観点は、第1および第2入力端子の各々に入力される第1および第2入力信号レベルの一致／不一致に応じて出力端子に正および／または負の論理信号を出力する差動型コンパレータであって、

前記第1または第2入力端子の前記差動型コンパレータ側に設けられたオフセット容量素子と、前記オフセット容量素子を含む閉ループを形成するように前記第1および第2入力端子を短絡する第1スイッチと、前記オフセット容量素子と差動型コンパレータの接続点と前記出力端子とを短絡する第2スイッチとを含むオフセットキャンセル機能を備えた差動型コンパレータを提供する。 20

【0016】

本発明の第2の観点は、第1および第2入力端子の各々に入力されるアナログ信号および基準信号の信号レベルの一致／不一致に応じて出力端子に正および／または負の論理信号を出力する差動型コンパレータと、前記論理信号にて起動および停止が制御されるカウンタとを含み、前記アナログ信号の入力契機から当該アナログ信号と前記基準信号とが一致するまでの間に前記カウンタにて計数されたカウンタ値を前記アナログ信号のデジタル変換値として出力するアナログ・デジタル変換装置であって、 30

前記差動型コンパレータは、前記第1入力端子の前記差動型コンパレータ側に設けられたオフセット容量素子と、前記オフセット容量素子を含む閉ループを形成するように前記第1および第2入力端子を短絡する第1スイッチと、前記オフセット容量素子と差動型コンパレータの接続点と前記出力端子とを短絡する第2スイッチとを含むオフセットキャンセル機能を備えたアナログ・デジタル変換装置を提供する。

【0017】

本発明の第3の観点は、各々が光電変換素子を含む複数のピクセル部が行および列方向に二次元的に配列されたピクセルアレイと、個々の前記ピクセル部から出力される光電変換信号をデジタル信号に変換するアナログ・デジタル変換器を含む読み出し回路を備えた撮像装置であって、

前記アナログ・デジタル変換器は、

第1および第2入力端子の各々に入力される前記光電変換信号および基準信号の信号レベルの一致／不一致に応じて出力端子に正および／または負の論理信号を出力する差動型コンパレータと、

前記第1入力端子に設けられたオフセット容量素子と、前記オフセット容量素子を含む閉ループを形成するように前記第1および第2入力端子を短絡する第1スイッチと、前記出力端子と前記オフセット容量素子が設けられた前記第1入力端子とを短絡する第2スイッチとを含むオフセットキャンセル機能と、

を備えた撮像装置を提供する。

【0018】

10

20

30

40

50

上記した本発明の第1および第2の観点によれば、第1入力信号としてアナログ信号が入力される第1入力端子に信号用容量素子を接続し、この第1入力端子にアナログ信号を入力すると同時に、オフセットキャンセル機能の第1および第2スイッチを閉じて、オフセット容量素子に差動型コンパレータのオフセット電圧を保持した後、当該第1および第2スイッチを開き、その後、第2入力端子に第2入力信号として、ランプ波形信号等の基準信号を入力して第1入力端子側のアナログ信号と比較する際に、信号用容量素子に保持されたアナログ信号が入力される第1入力端子側の電位は、オフセット容量素子に保持されたオフセット電圧にて一定となるため、インバータを用いる場合のように、入力される当該アナログ信号のレベルが寄生容量等で変動することがなくなり、アナログ信号とランプ波形信号の正確な比較が可能となり、当該比較に基づくアナログ信号のデジタル化の精度が向上する。

10

#### 【0019】

また、差動型コンパレータでは、第1および第2入力端子の比較動作が電流量に依存しないため、寄生容量を増加させることなく、消費電流を抑制でき、より少ない消費電流で高精度のアナログ・デジタル変換処理を行うことができる。

#### 【0020】

また、本発明の第3の観点によれば、撮像装置の光電変換信号の読み出し回路に設けられたアナログ・デジタル変換器を差動型コンパレータにて構成するとともにオフセットキャンセル機能を設けたことにより、ランプ波形信号等の基準信号を用いた光電変換信号のデジタル化処理を高精度で行うことができ、得られる画質が向上する。

20

#### 【0021】

また、差動型コンパレータは寄生容量を増加させることなく、消費電流を抑制できるため、たとえば、CMOSイメージセンサにおいて複数のピクセル部の列毎にコラムADC等のアナログ・デジタル変換器を設ける場合のように、多数のアナログ・デジタル変換器を配置する構成において消費電流の抑制効果が大きい。

#### 【発明の効果】

#### 【0022】

本発明によれば、より少ない消費電流で、高精度のアナログ・デジタル変換を実現することが可能な差動型コンパレータを提供することができる。

また、より少ない消費電流で、高精度のアナログ・デジタル変換を実現することが可能なアナログ・デジタル変換装置を提供することができる。

30

#### 【0023】

また、より少ない消費電流で、高画質の映像データ出力することが可能な撮像装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0024】

以下、図面を参照しながら、本発明の実施の形態について詳細に説明する。

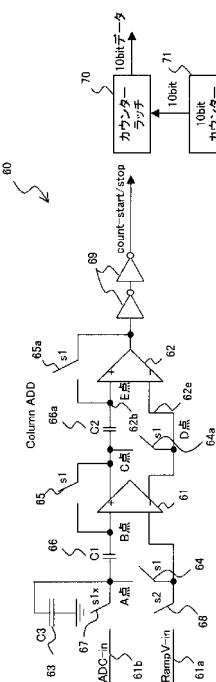

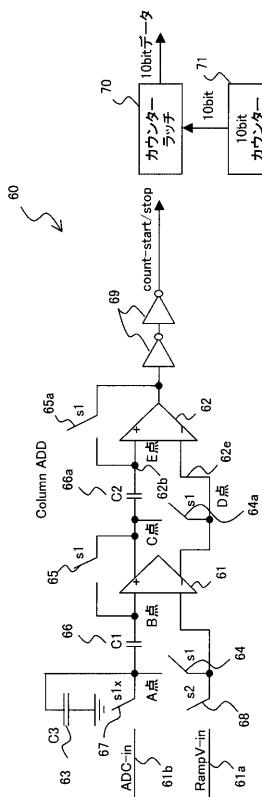

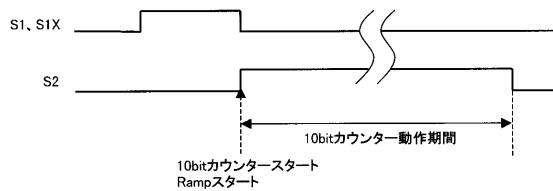

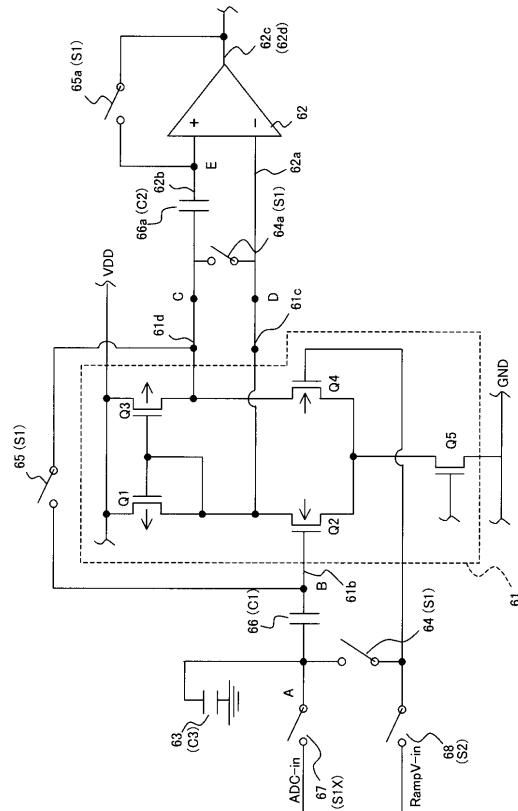

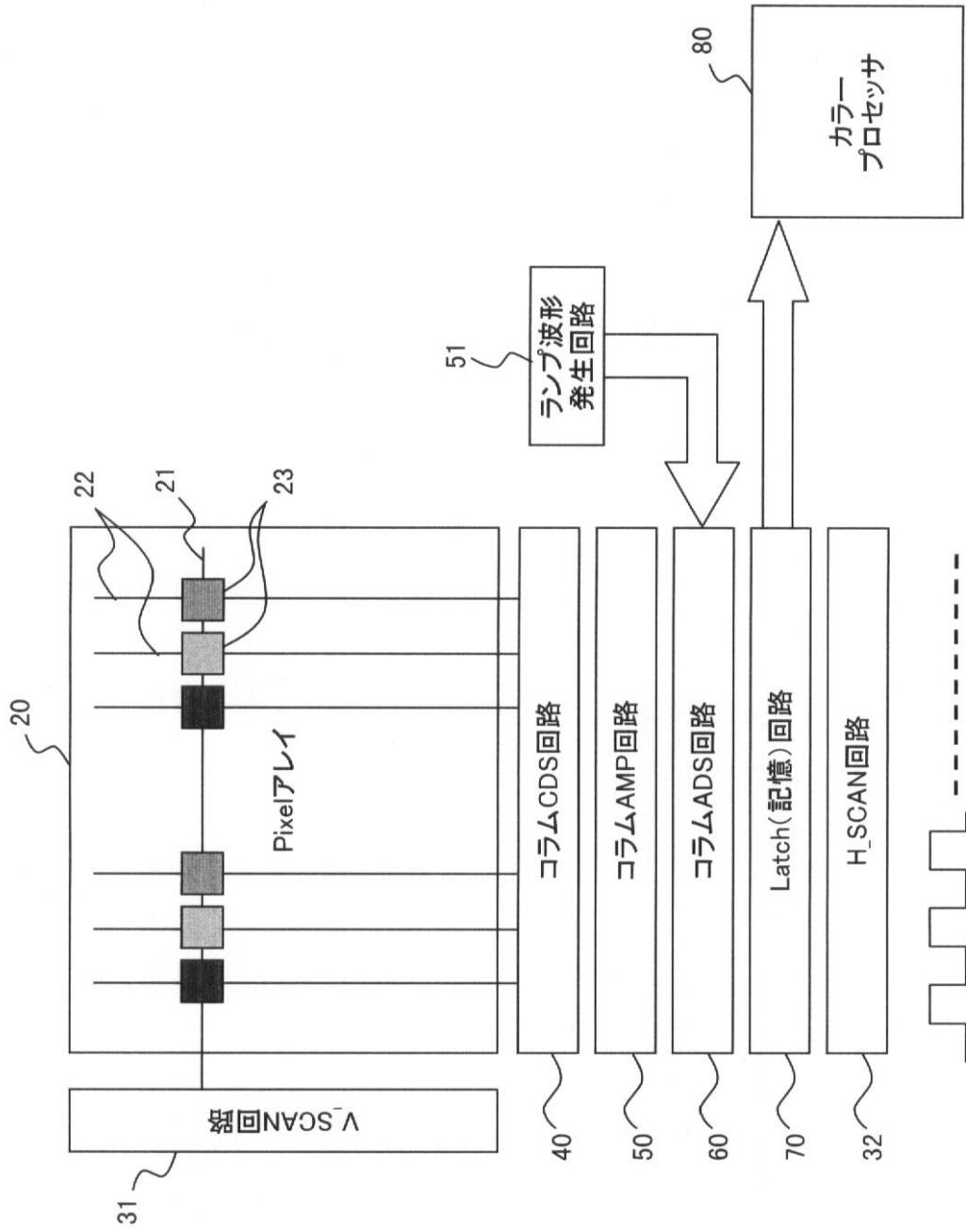

図1は、本発明の一実施の形態である差動型コンパレータを含むアナログ・デジタル変換装置の構成の一例を示すブロック図であり、図2は、その内部構成をより詳細に例示した回路図、図3は、本実施の形態のアナログ・デジタル変換装置を含む撮像装置の全体構成の一例を示すブロック図である。

40

#### 【0025】

本実施の形態では、たとえばCMOSイメージセンサからなる撮像装置10に適用した場合を例にとって説明する。

図3に例示されるように、本実施の形態の撮像装置10は、複数のピクセル部23が行21および列22に沿って二次元的に配列されたピクセルアレイ20と、垂直走査回路31および水平走査回路32を備えている。

#### 【0026】

個々のピクセル部23は、たとえば光電変換素子としてのフォトダイオードと、このフォトダイオードの初期化や出力信号の增幅、タイミング制御を行うためのトランジスタ等で

50

構成されている。個々のピクセル部 23 は、光の三原色のいずれかの色のカラーフィルタで覆われ、各色の光の光電変換を行う。

#### 【0027】

垂直走査回路 31 は、ピクセルアレイ 20 の複数のピクセル部 23 を行 21 の単位で選択するタイミングを制御する。水平走査回路 32 は、行 21 内の個々のピクセル部 23 を、列 22 単位に個別に選択するタイミングを制御する。

#### 【0028】

この実施の形態では、ピクセル部 23 の個々の列 22 単位に、コラム CDS 回路 40、コラム AMP 回路 50、コラム ADC 回路 60 およびラッチ回路 70 が設けられている。

コラム CDS 回路 40 は、相関二重サンプリング技術にて、ピクセル部 23 における光電変換素子のリセット時等に発生するノイズを光電変換信号から除去する処理が行われる。

10

#### 【0029】

コラム AMP 回路 50 は、コラム CDS 回路 40 から出力された光電変換信号を増幅する処理を行う。

コラム ADC 回路 60 は、ランプ波形発生回路 51 から得られるランプ波形信号 Ramp V を用いて、後述のように、光電変換信号のデジタル化処理を行う。

#### 【0030】

ラッチ回路 70 は、列 22 (ピクセル部 23) 単位にデジタル変換後の光電変換信号を保持し、水平走査回路 32 から出力される水平走査信号に同期して後段のカラープロセッサ 80 に出力する処理を行う。

20

#### 【0031】

カラープロセッサ 80 は、各色に対応したピクセル部 23 の各々の光電変換信号のデジタル値を処理して、たとえば、YUV、YCbCr、RGB 等の任意の規格の画像信号に変換して出力する機能を備えている。

#### 【0032】

図 1 に例示されるように、本実施の形態のコラム ADC 回路 60 は、入力側から出力側に順に二段に接続された差動型コンパレータ 61 および差動型コンパレータ 62 と、差動型コンパレータ 62 の出力側とラッチ回路 70 との間に接続されたインバータ 69 を備えている。

30

#### 【0033】

差動型コンパレータ 61 の基準信号入力端子 61a には、スイッチ 68 (スイッチ S2) を介してランプ波形発生回路 51 に接続され、ランプ波形信号 Ramp V が入力される。

#### 【0034】

差動型コンパレータ 61 のアナログ信号入力端子 61b には、スイッチ 67 (スイッチ S1x) を介してピクセル部 23 からの光電変換信号 23a (ADC-in) が入力される。また、このアナログ信号入力端子 61b には、光電変換信号 23a の電圧レベルを保持するための信号用容量素子 63 (信号用容量素子 C3) が設けられている。

#### 【0035】

前段の差動型コンパレータ 61 の出力端子 61c および出力端子 61d は、正負の極性を合わせて後段の差動型コンパレータ 62 の入力端子 62a および入力端子 62b にそれぞれ接続されている。

40

#### 【0036】

本実施の形態の場合、差動型コンパレータ 61 には、その基準信号入力端子 61a および入力端子 61b の短絡を制御するスイッチ 64 (スイッチ S1) と、アナログ信号入力端子 61b と出力端子 61d の短絡を制御するスイッチ 65 (スイッチ S1) と、アナログ信号入力端子 61b におけるスイッチ 64 の短絡位置とスイッチ 65 の短絡位置の間に設けられた容量素子 66 (容量素子 C1) からなるオフセットキャンセル機能を備えている。

50

## 【0037】

同様に、後段の差動型コンパレータ62にも、スイッチ64a(スイッチS1)、スイッチ65a(スイッチS1)、容量素子66a(容量素子C2)からなるオフセットキャンセル機能が設けられている。

## 【0038】

図2に例示されるように、差動型コンパレータ61は、電源VDDに並列に接続されるpMOSトランジスタQ1、nMOSトランジスタQ2、およびpMOSトランジスタQ3、nMOSトランジスタQ4と、これらの系列をまとめて接地するnMOSトランジスタQ5で構成され、各系列のpMOSトランジスタQ1およびpMOSトランジスタQ3のゲートは、pMOSトランジスタQ1のソース側に接続されることによって負荷抵抗を構成し、nMOSトランジスタQ2のゲートにはアナログ信号入力端子61bが接続され、nMOSトランジスタQ4のゲートには基準信号入力端子61aが接続されている。nMOSトランジスタQ5は、定電流源の如く機能する。

## 【0039】

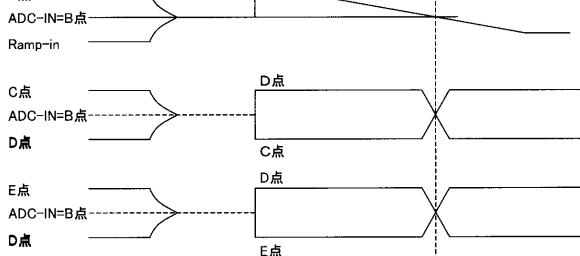

以下、本実施の形態の作用の一例について、図4の線図等を参照して説明する。まず、ピクセルアレイ20では、垂直走査回路31による垂直同期信号にて個々の行21が選択され、当該行21内のピクセル部23の光電変換素子のリセットが実行され、その後、当該行21内における個々のピクセル部23(列22)の読み出しが水平走査回路32からの水平同期信号(列選択出力信号)によって順に実行される。

## 【0040】

そして、一つのピクセル部23(列22)から出力される光電変換信号23aは、コラムCDS回路40にてリセットノイズ等が除去され、コラムAMP回路50にて増幅された後、コラムADC回路60にADC-inとして入力され、アナログ・デジタル変換処理が行われてデジタル化される。

## 【0041】

すなわち、コラムADC回路60では、光電変換信号23aの入力契機である列選択出力信号に同期して、スイッチS1、スイッチS1xを閉じ、到来する光電変換信号23aの電位レベルに対応した電荷が信号用容量素子C3に蓄積されるとともに、スイッチS1にて差動型コンパレータ61(差動型コンパレータ62)の入出力側が短絡されるため、容量素子C1(容量素子C2)には差動型コンパレータ61(差動型コンパレータ61)の閾値電圧(動作点)のレベルを基準とする光電変換信号23aの電位に対応した電荷が蓄積され、図1中のA~E点の電位は、光電変換信号23a(ADC-in)のレベルとなる。

## 【0042】

その後、スイッチS1およびスイッチS1xを開き、スイッチS2を閉じてランプ波形発生回路51から基準信号入力端子61aにランプ波形信号RampVを入力すると、出力側のC点およびD点は、ADC-inのレベルを中心として光電変換信号23aを入力する前とは逆の電位に反転し、インバータ69に反転出力により、カウンタ71では、カウントが開始され、漸減するランプ波形信号RampVが、B点の光電変換信号23aの電圧値とクロスする瞬間に、差動型コンパレータ61および差動型コンパレータ62の出力側のC点~E点の電位が反転し、インバータ69の反転出力により、カウンタ71のカウント値がラッチ回路70にラッチされる。このカウント値は、光電変換信号23aを所定のビット幅のデジタル値に変換したものとなる。

## 【0043】

そして、ラッチ回路70のデジタルデータは、水平同期信号に同期してカラープロセッサ80に出力されて処理される。

このように、本実施の形態によれば、スイッチS1xを閉じて光電変換信号23aを入力する際に、スイッチS1を閉じて、差動型コンパレータ61を構成するトランジスタの閾値電圧を基準とする光電変換信号23aの電圧を容量素子C1,C2および信号用容量素子C3に蓄積することで、差動型コンパレータ61の閾値電圧や寄生容量等がキャンセ

10

20

30

40

50

ルされるので、A点の電位が固定となり、スイッチS1およびスイッチS1xを開き、スイッチS2を閉じて比較のためのランプ波形信号RampVを入力する際に、容量素子C1の電荷変動に起因するB点の電位変動がなくなり、光電変換信号23aとランプ波形信号RampVの比較を精密に行うことが可能となる。

#### 【0044】

このため、光電変換信号23aのデジタル変換のばらつきに起因して、たとえば撮影画像の濃淡や色むら等が発生することがなくなり、撮像装置10から出力される画質が向上する。

#### 【0045】

また、差動型コンパレータ61は、pMOSトランジスタQ1、nMOSトランジスタQ2およびpMOSトランジスタQ3、nMOSトランジスタQ4の各入力系列に共通なnMOSトランジスタQ5で決定される一定電流値の分配によって差動動作するため、nMOSトランジスタQ5で制御される電流値自体を大きくする必要がなく、消費電流を抑制できる。また、電流抑制のために差動型コンパレータ61を構成するトランジスタのゲート長を大きくする必要もなく、寄生容量が大きくなることもない。

#### 【0046】

コラムADC回路60は、列22の各々毎に設けられるため、たとえば、解像度の改善のためにピクセルアレイ20におけるピクセル部23の数や密度を増大させた場合、コラムADC回路60の数も増えるが、本実施の形態のように個々のコラムADC回路60の消費電流を抑制することで、コラムADC回路60におけるデジタル化精度の良い、高画質で高解像度の映像を出力する高性能な撮像装置10を低消費電流（電力）にて実現することが可能となる。

#### 【0047】

なお、本発明は、上述の実施の形態に例示した構成に限らず、その趣旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

##### （付記1）

第1および第2入力端子の各々に入力される第1および第2入力信号レベルの一致／不一致に応じて出力端子に正および／または負の論理信号を出力する差動型コンパレータであって、

前記第1または第2入力端子の前記差動型コンパレータ側に設けられたオフセット容量素子と、前記オフセット容量素子を含む閉ループを形成するように前記第1および第2入力端子を短絡する第1スイッチと、前記オフセット容量素子と差動型コンパレータの接続点と前記出力端子とを短絡する第2スイッチとを含むオフセットキャンセル機能を備えたことを特徴とする差動型コンパレータ。

#### 【0048】

##### （付記2）

付記1記載の差動型コンパレータにおいて、前段の前記差動型コンパレータから出力される正および負の前記論理信号を次段の前記差動型コンパレータの前記第1および第2入力端子に入力することで、前記差動型コンパレータを多段に接続したことを特徴とする差動型コンパレータ。

#### 【0049】

##### （付記3）

付記1記載の差動型コンパレータにおいて、前記オフセット容量素子が設けられた前記第1または第2入力端子にはアナログ・デジタル変換対象のアナログ信号が入力され、他の前記第2または第1入力端子にはランプ波形信号が入力され、前記アナログ信号の入力契機から前記アナログ信号と前記ランプ波形信号のレベルが一致するまでの時間を計数するカウンタのオン／オフを前記出力端子の前記論理信号にて制御することで、前記アナログ信号を前記カウンタのカウンタ値としてデジタル変換するアナログ・デジタル変換器として機能することを特徴とする差動型コンパレータ。

#### 【0050】

10

20

30

40

50

## (付記4)

第1および第2入力端子の各々に入力されるアナログ信号および基準信号の信号レベルの一致／不一致に応じて出力端子に正および／または負の論理信号を出力する差動型コンパレータと、前記論理信号にて起動および停止が制御されるカウンタとを含み、前記アナログ信号の入力契機から当該アナログ信号と前記基準信号とが一致するまでの間に前記カウンタにて計数されたカウンタ値を前記アナログ信号のデジタル変換値として出力するアナログ・デジタル変換装置であって、

前記差動型コンパレータは、前記第1入力端子の前記差動型コンパレータ側に設けられたオフセット容量素子と、前記オフセット容量素子を含む閉ループを形成するように前記第1および第2入力端子を短絡する第1スイッチと、前記オフセット容量素子と差動型コンパレータの接続点と前記出力端子とを短絡する第2スイッチとを含むオフセットキャセル機能を備えたことを特徴とするアナログ・デジタル変換装置。

## 【0051】

## (付記5)

付記4記載のアナログ・デジタル変換装置において、前段の前記差動型コンパレータから出力される正および負の前記論理信号を次段の前記差動型コンパレータの前記第1および第2入力端子に入力することで、前記差動型コンパレータを多段に接続したことを特徴とするアナログ・デジタル変換装置。

## 【0052】

## (付記6)

付記4記載のアナログ・デジタル変換装置において、前記アナログ信号が入力される前記第1入力端子に接続され、当該アナログ信号を保持する信号用容量素子をさらに備えたことを特徴とするアナログ・デジタル変換装置。

## 【0053】

## (付記7)

付記4記載のアナログ・デジタル変換装置において、前記基準信号はランプ波形信号であることを特徴とするアナログ・デジタル変換装置。

## 【0054】

## (付記8)

各々が光電変換素子を含む複数のピクセル部が行および列方向に二次元的に配列されたピクセルアレイと、個々の前記ピクセル部から出力される光電変換信号をデジタル信号に変換するアナログ・デジタル変換器を含む読み出し回路を備えた撮像装置であって、

前記アナログ・デジタル変換器は、

第1および第2入力端子の各々に入力される前記光電変換信号および基準信号の信号レベルの一致／不一致に応じて出力端子に正および／または負の論理信号を出力する差動型コンパレータと、

前記第1入力端子に設けられたオフセット容量素子と、前記オフセット容量素子を含む閉ループを形成するように前記第1および第2入力端子を短絡する第1スイッチと、前記出力端子と前記オフセット容量素子が設けられた前記第1入力端子とを短絡する第2スイッチとを含むオフセットキャセル機能と、

を備えたことを特徴とする撮像装置。

## 【0055】

## (付記9)

付記8記載の撮像装置において、前記アナログ・デジタル変換器は、前記論理信号にて起動および停止が制御されることで前記アナログ信号の入力契機から当該アナログ信号と前記基準信号とが一致するまでの間に前記カウンタにて計数されたカウンタ値を前記アナログ信号のデジタル変換値として出力するカウンタをさらに含むことを特徴とする撮像装置。

## 【0056】

## (付記10)

10

20

30

40

50

付記 8 記載の撮像装置において、前記アナログ・デジタル変換器には、前段の前記差動型コンパレータから出力される正および負の前記論理信号を次段の前記差動型コンパレータの前記第1および第2入力端子に入力することで、前記差動型コンパレータが多段に設けられていることを特徴とする撮像装置。

## 【0057】

(付記11)

付記 8 記載の撮像装置において、前記読み出し回路は、前記アナログ・デジタル変換器の前段に配置され、相関二重サンプリングにて前記光電変換信号に含まれるノイズを除去するノイズ除去回路をさらに含むことを特徴とする撮像装置。

## 【0058】

(付記12)

付記 8 記載の撮像装置において、前記読み出し回路は、前記ピクセル部の前記行または列単位に設けられていることを特徴とする撮像装置。

## 【0059】

(付記13)

付記 8 記載の撮像装置において、前記基準信号は、ランプ波形信号であることを特徴とする撮像装置。

## 【0060】

(付記14)

付記 8 記載の撮像装置において、前記撮像装置は CMOSイメージセンサであることを特徴とする撮像装置。 20

## 【図面の簡単な説明】

## 【0061】

【図1】本発明の一実施の形態である差動型コンパレータを含むアナログ・デジタル変換装置の構成の一例を示すブロック図である。

【図2】本発明の一実施の形態である差動型コンパレータを含むアナログ・デジタル変換装置の内部構成をより詳細に例示した回路図である。

【図3】本発明の一実施の形態であるアナログ・デジタル変換装置を含む撮像装置の全体構成の一例を示すブロック図である。

【図4】本発明の一実施の形態であるアナログ・デジタル変換装置を含む撮像装置の作用例を示すタイミングチャートである。 30

【図5】本発明の参考技術であるチョッパ型コンパレータの構成を示すブロック図である。

【図6】本発明の参考技術であるチョッパ型コンパレータの内部構成を示す回路図である。

## 【符号の説明】

## 【0062】

10 撮像装置

20 ピクセルアレイ

21 行

22 列

23 ピクセル部

23a 光電変換信号 (A D C - i n )

31 垂直走査回路

32 水平走査回路

40 40 コラム C D S 回路

50 コラム A M P 回路

51 ランプ波形発生回路

60 コラム A D C 回路 (アナログ・デジタル変換装置)

61 差動型コンパレータ 50

|           |                            |

|-----------|----------------------------|

| 6 1 a     | 基準信号入力端子                   |

| 6 1 b     | アナログ信号入力端子                 |

| 6 1 c     | 出力端子                       |

| 6 1 d     | 出力端子                       |

| 6 2       | 差動型コンパレータ                  |

| 6 2 a     | 入力端子                       |

| 6 2 b     | 入力端子                       |

| 6 3       | 信号用容量素子 ( C 3 )            |

| 6 4       | スイッチ ( S 1 ) ( 第 1 スイッチ )  |

| 6 4 a     | スイッチ ( S 1 ) ( 第 1 スイッチ )  |

| 6 5       | スイッチ ( S 1 ) ( 第 2 スイッチ )  |

| 6 5 a     | スイッチ ( S 1 ) ( 第 2 スイッチ )  |

| 6 6       | 容量素子 ( C 1 ) ( オフセット容量素子 ) |

| 6 6 a     | 容量素子 ( C 2 ) ( オフセット容量素子 ) |

| 6 7       | スイッチ ( S 1 x )             |

| 6 8       | スイッチ ( S 2 )               |

| 6 9       | インバータ                      |

| 7 0       | ラッチ回路                      |

| 7 1       | カウンタ                       |

| 8 0       | カラープロセッサ                   |

| Q 1       | p M O S トランジスタ             |

| Q 2       | n M O S トランジスタ             |

| Q 3       | p M O S トランジスタ             |

| Q 4       | n M O S トランジスタ             |

| Q 5       | n M O S トランジスタ             |

| R a m p V | ランプ波形信号                    |

【図1】

本発明の一実施の形態である差動型コンパレータを含む

アナログ・デジタル変換装置の構成の一例を示すブロック図

【図4】

本発明の一実施の形態であるアナログ・デジタル変換装置

を含む撮像装置の作用例を示すタイミングチャート

B点

【図2】

本発明の一実施の形態である差動型コンパレータを含む

アナログ・デジタル変換装置の内部構成をより詳細に例示した回路図

【図5】

本発明の参考技術であるチョッパ型コンパレータの構成を示すブロック図

【図6】

本発明の参考技術であるチョッパ型コンパレータの内部構成を示す回路図

【図3】

本発明の一実施の形態であるアナログ・デジタル変換装置

を含む撮像装置の全体構成の一例を示すブロック図

10

---

フロントページの続き

(72)発明者 山縣 誠司

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 樋口 剛

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

F ターム(参考) 5C024 CX04 CY42 GY31 HX23

5J022 AA02 AC04 BA02 BA03 BA06 CA10 CB08 CE01 CF02 CF07

5J039 DA09 DC01 KK18 KK28 MM04 MM08 NN04