(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5091548号

(P5091548)

(45) 発行日 平成24年12月5日(2012.12.5)

(24) 登録日 平成24年9月21日(2012.9.21)

(51) Int.Cl.

G06F 12/08 (2006.01)

F 1

G06F 12/08 501D

G06F 12/08 505B

G06F 12/08 551Z

G06F 12/08 575

請求項の数 2 (全 14 頁)

(21) 出願番号 特願2007-150548 (P2007-150548)

(22) 出願日 平成19年6月6日 (2007.6.6)

(65) 公開番号 特開2008-305082 (P2008-305082A)

(43) 公開日 平成20年12月18日 (2008.12.18)

審査請求日 平成22年6月3日 (2010.6.3)

(73) 特許権者 501285133

川崎マイクロエレクトロニクス株式会社

千葉県千葉市美浜区中瀬一丁目3番地

(74) 代理人 100079175

弁理士 小杉 佳男

(74) 代理人 100094330

弁理士 山田 正紀

(72) 発明者 山下 和憲

千葉県千葉市美浜区中瀬1丁目3番地 川

崎マイクロエレクトロニクス株式会社内

審査官 野田 佳邦

最終頁に続く

(54) 【発明の名称】メモリシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

リンク構造が構築されたDRAMと、

システムバスと、

前記DRAMを前記システムバスを介してアクセスするために、前記リンク構造のリストをアクセスするための先読み情報を付加した読み出し命令を出力するマスタと、

キャッシュメモリと、

前記システムバスと前記DRAMとの間に配備され、前記マスタからの前記DRAMの読み出し命令を受け、前記キャッシュメモリに該読み出し命令に応じたデータが格納されているときは該データを該キャッシュメモリから読み出して前記マスタに送り、該キャッシュメモリに該読み出し命令に応じたデータが格納されていないときは該読み出し命令を前記DRAMに伝えて該DRAMから読み出された該読み出し命令に応じたデータを前記マスタに送るとともに該DRAMから先読みしたデータを前記キャッシュメモリに格納するキャッシュメモリコントローラと、

前記先読み情報を受け取り、該先読み情報に従って前記リンク構造を辿って、前記キャッシュメモリコントローラに、前記DRAMからデータを先読みさせて前記キャッシュメモリに格納させるシーケンサとを備え、

前記シーケンサが、前記先読み情報の番号ごとの、前記読み出し命令に応じたデータのどの部分をアドレスとして認識するかの情報であるアドレスオフセット値を格納する複数のレジスタと、前記先読み情報の番号に対応する前記レジスタに格納されたアドレスオフ

セット値を使って、前記キャッシュメモリコントローラに、前記DRAMからデータを先読みさせるシーケンサマスターとを備えたことを特徴とするメモリシステム。

【請求項 2】

前記キャッシュメモリコントローラが、前記マスターからの読み出し命令を受け取る第1のポートと、前記シーケンサから前記先読みのための読み出し命令を受け取る第2のポートとを有するものであることを特徴とする請求項1記載のメモリシステム。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、DRAMをアクセスするメモリシステムに関する。

【背景技術】

【0002】

一般に、DRAM (Dynamic Random Access Memory) を制御するDRAMコントローラは、所定のバースト長でDRAMにシーケンシャルにアクセスする。従って、DRAMコントローラにアクセスする可能性のあるマスターは、DRAMのバースト長に合わせて、かつシーケンシャルにアクセスすると、DRAMを効率よくアクセスすることができる。

【0003】

20

ここで、一般的に用いられているバスプロトコルは、1回のアクセスで複数のワードを連続して転送するバースト転送の機能を有する。このバースト転送の機能では、マスターが、これから発生するアクセスの総ワード数とアクセス順を予めDRAMコントローラに予告してDRAMをアクセスするため、このバースト転送機能を用いてDRAMへのアクセスを行なうと、DRAMへのアクセス効率を高めることができる。また、バスプロトコルは、1回のアクセスで1ワードを転送するシングル転送の機能も有するが、このシングル転送の機能を用いてDRAMをアクセスした場合は、DRAMへのアクセス効率は低下する。従って、DRAMへのアクセスは、全てバースト転送で行なわれることが好ましい。

【0004】

図9は、バースト転送の機能を説明するための回路構成を示す図、図10は、図9に示す回路構成における処理の流れを示す図である。

30

【0005】

図9には、マスター101と、システムバス102と、DRAMコントローラ103と、DRAM104とが示されている。マスター101とDRAMコントローラ103は、システムバス102に接続されている。また、DRAMコントローラ103は、DRAM104に接続されている。

【0006】

これらマスター101、DRAMコントローラ103、DRAM104は、64ビットのバス幅を有する。ここでは、DRAM104へのアクセスは、4バースト単位 (4×64ビット単位) で行なわれるものとする。図10に示すように、先ず、マスター101からアドレス0hのデータを読み出すための読み出し命令 (READ) が出力される。この読み出し命令は、システムバス102を経由してDRAMコントローラ103に入力される。DRAMコントローラ103は、この読み出し命令を受けて、4バースト単位でDRAM104をアクセスする。これにより、DRAM104からアドレス0h, 8h, 10h, 18hのデータが順次に出力される。DRAMコントローラ103は、DRAM104から出力されたアドレス0h, 8h, 10h, 18hのデータのうちのアドレス0hのデータを、システムバス102を経由してマスター101に出力する。ここで、DRAM104から出力されたアドレス8h, 10h, 18hのデータ (丸印の点線で示す) は破棄される。

40

【0007】

次いで、マスター101からアドレス8hのデータを読み出すための読み出し命令が出力され、これによりDRAM104からアドレス0h, 8h, 10h, 18hのデータが出力

50

される。DRAMコントローラ103は、DRAM104から出力されたアドレス0h, 8h, 10h, 18hのデータのうちのアドレス8hのデータを、システムバス102を経由してマスター101に出力する。ここで、DRAM104から出力されたアドレス0h, 10h, 18hのデータ（丸印の点線で示す）は破棄される。

#### 【0008】

この回路構成では、図10の丸印の点線で示すように、DRAM104から出力された4つのデータのうちの3つのデータが破棄されるため、無駄なアクセスが行なわれることとなり、従ってDRAM104へのアクセス効率は低いこととなる。

#### 【0009】

尚、アクセス順がシーケンシャルでない場合、シングル転送に分割して処理する必要があり、この場合は、1回のアクセスで1つのデータが転送されるため、DRAM104へのアクセス効率はさらに低くなる。

#### 【0010】

ここで、従来より、図9に示す回路構成に加えて、DRAMよりも動作速度が速いSRAM(Static Random Access Memory; キャッシュメモリと称する)と、DRAMから読み出されたデータをキャッシュメモリに格納するためのキャッシュメモリコントローラを備えたメモリシステムが知られている。キャッシュメモリコントローラは、マスターとシステムバスとの間に配備され、またキャッシュメモリはキャッシュメモリコントローラに接続されている。このメモリシステムによれば、DRAMから読み出されたデータ（上記破棄されるデータ）は、キャッシュメモリコントローラによりキャッシュメモリに格納される。このようなメモリシステムとして、例えば、特許文献1に、内部バスで互いに接続された、動作速度が遅いメインメモリ(DRAM)と動作速度が速いキャッシュメモリ(SRAM)とを備え、一度アクセスされたメインメモリのアドレスのデータ（先読みしたデータ）をキャッシュメモリに格納しておき、再度そのアドレスがアクセスされた場合はキャッシュメモリからそのアドレスのデータを読み出すことにより、高速なアクセスを可能にするキャッシュDRAM(メモリシステム)が提案されている。

#### 【0011】

また、上述した図9に示す回路構成では、別の問題として、図10に示すようにアドレス0hの読み出しが行なわれてそのアドレス0hのデータがマスター101に出力されるまで、後続（アドレス8h）の読み出しが行なわれないため、DRAM104へのアクセスやシステムバス102のレイテンシ（命令の開始から実行完了までに要する時間、即ち読み出し/書き込みサイクルを実行するのに要する時間）が大きいという問題がある。従って、システムの応答性が悪いという問題がある。

#### 【0012】

この問題を解決するために、高速なDRAMを選択したりシステムバスの周波数を上げたりすることが考えられるが、コストアップ等の問題が発生する。そこで、例えば特許文献2に、低速メモリから読み出したデータをアドレスと見なした場合は、そのデータをFIFOに格納しておき、低速メモリがアクセスされていないときにFIFOに格納されているデータをキャッシュメモリに格納しておくことにより、ランダムデータの先読みを実現して処理の高速化を図る技術が提案されている。

【特許文献1】特開2002-74942号公報

【特許文献2】特開2005-301792号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0013】

従来のメモリシステムでは、キャッシュメモリコントローラは、マスターとシステムバスとの間に備えられている。このため、キャッシュメモリコントローラは、システムバスを介してDRAMをアクセスする必要がある。従って、アクセス効率が悪いという問題がある。

10

20

30

40

50

**【0014】**

また、特許文献1に提案されたキャッシュDRAMは、DRAMとSRAMが内部バスで接続された特殊な構造を有するメモリシステムであるため、あまり現実的ではない。

**【0015】**

さらに、特許文献2に提案された、低速メモリから読み出したデータをアドレスと見なしてキャッシュメモリに格納してデータの先読みを行なう技術では、アドレスと見なしたデータと全く同じ値をデータとして読み込む可能性があり、従って確実性に欠けるという問題を抱えている。

**【0016】**

本発明は、上記事情に鑑み、処理の高速化が図られたメモリシステムを提供することを目的とする。 10

**【課題を解決するための手段】****【0017】**

上記目的を達成する本発明のメモリシステムは、

DRAMと、

システムバスと、

上記DRAMを上記システムバスを介してアクセスするマスタと、

キャッシュメモリと、

上記システムバスと上記DRAMとの間に配備され、上記マスタからの上記DRAMの読み出し命令を受け、上記キャッシュメモリにその読み出し命令に応じたデータが格納されているときはそのデータをそのキャッシュメモリから読み出して上記マスタに送り、そのキャッシュメモリにその読み出し命令に応じたデータが格納されていないときはその読み出し命令を上記DRAMに伝えてそのDRAMから読み出されたその読み出し命令に応じたデータを上記マスタに送るとともにそのDRAMから先読みしたデータを上記キャッシュメモリに格納するキャッシュメモリコントローラとを備えたことを特徴とする。 20

**【0018】**

本発明のメモリシステムは、システムバスとDRAMとの間に、キャッシュメモリコントローラを備えた構成である。このため、キャッシュメモリコントローラからDRAMへのアクセスを全て1キャッシュライン分のバーストアクセスとすることができる。このようにすることにより、無駄なアクセスの発生が防止され、従ってアクセス効率が高められて処理の高速化が図られる。 30

**【0019】**

ここで、上記マスタが、読み出し命令出力時に以降の読み出し手順を表わす先読み情報を出力するものであって、

上記先読み情報を受け取り、その先読み情報に従って、上記キャッシュメモリコントローラに、上記DRAMからデータを先読みさせて上記キャッシュメモリに格納させるシーケンサを備えたことが好ましい。

**【0020】**

このように、シーケンサが、DRAMからデータを先読みさせ、そのDRAMからのデータを、キャッシュメモリコントローラを介してキャッシュメモリに格納させると、システムバスを使用してDRAMからデータを先読みしてキャッシュメモリに格納させる場合と比較し、システムバスを他の処理に使用することができ、従って処理のさらなる高速化を図ることができる。 40

**【0021】**

また、上記キャッシュメモリコントローラが、読み出し命令を受け取る複数のポートを有するものであることも好ましい態様である。

**【0022】**

このようにすると、キャッシュメモリコントローラは、複数のマスタからの読み出し命令を複数のポートで同時に受け取って処理することができる。従って、処理のさらなる高速化を図ることができる。 50

**【発明の効果】****【0023】**

本発明によれば、処理の高速化が図られたメモリシステムを提供することができる。

**【発明を実施するための最良の形態】****【0024】**

以下、図面を参照して本発明の実施の形態を説明する。

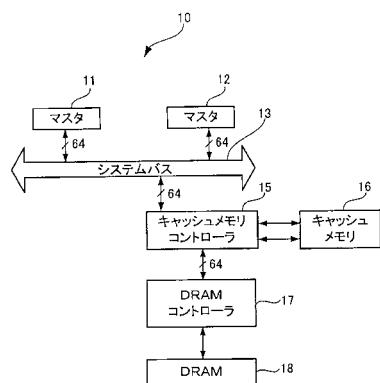

**【0025】**

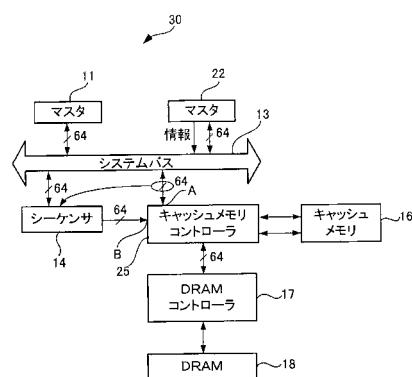

図1は、本発明のメモリシステムの第1実施形態の回路構成を示す図である。

**【0026】**

図1に示すメモリシステム10には、マスタ11, 12と、これらマスタ11, 12が接続されたシステムバス13と、そのシステムバス13に接続されたキャッシュメモリコントローラ15と、そのキャッシュメモリコントローラ15に接続されたキャッシュメモリ16およびDRAMコントローラ17と、そのDRAMコントローラ17に接続されたDRAM18とが備えられている。マスタ11, 12, キャッシュメモリコントローラ15, DRAMコントローラ17は、64ビットのバス幅を有する。また、DRAMコントローラ17は、4バースト単位(4×64ビット単位)でDRAM18をアクセスする。

**【0027】**

マスタ11, 12は、システムバス13, キャッシュメモリコントローラ15, DRAMコントローラ17を経由してDRAM18をアクセスする。

**【0028】**

キャッシュメモリコントローラ15は、システムバス13とDRAMコントローラ17との間に配備され、マスタ12(もしくはマスタ11)からのDRAM18への読み出し命令を受け、キャッシュメモリ16にその読み出し命令に応じたデータが格納されているときはそのデータをキャッシュメモリ16から読み出してマスタ12に送り、キャッシュメモリ16にその読み出し命令に応じたデータが格納されていないときはその読み出し命令をDRAMコントローラ17を介してDRAM18に伝える。さらに、DRAM18から読み出された、その読み出し命令に応じたデータをマスタ12に送るとともにDRAM18から先読みしたデータをキャッシュメモリ16に格納する。

**【0029】**

ここで、キャッシュメモリコントローラ15は、キャッシュメモリ16に1キャッシュライン分のサイズ(64ビット分のサイズ)でアクセスするとともに、DRAMコントローラ17にも1キャッシュライン分のサイズでアクセスする。このため、無駄なアクセスの発生が防止されている。

**【0030】**

また、キャッシュメモリ16は、DRAMコントローラ17へのアクセスの整列化と先読みデータの退避のためにのみ設けられており、従ってキャッシュメモリ16のサイズは小さくて済む。

**【0031】**

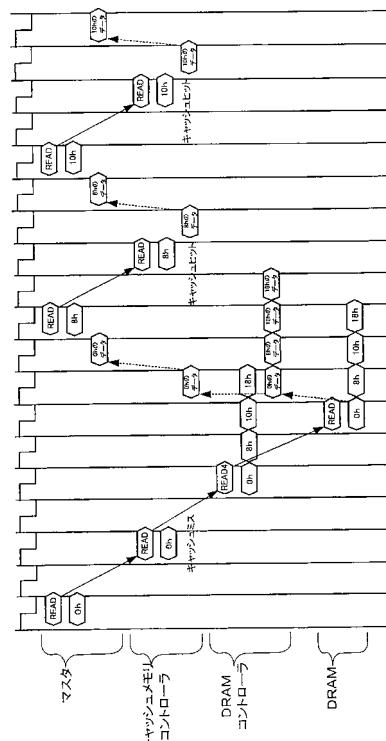

図2は、図1に示すメモリシステムにおける処理の流れを示す図である。

**【0032】**

このメモリシステム10では、この図2に示すように、先ず、マスタ12からアドレス0hのデータを読み出すための読み出し命令(READ)が出力される。この読み出し命令は、キャッシュメモリコントローラ15に入力される。キャッシュメモリコントローラ15は、アドレス0hのデータがキャッシュメモリ16に存在しているか否かを確認する。

**【0033】**

最初の時点では、キャッシュメモリ16には、このアドレス0hのデータは存在しない(キャッシュミスと称する)ため、キャッシュメモリコントローラ15は、DRAMコントローラ17にアクセスする。DRAMコントローラ17は、4バースト単位でDRAM18にアクセスする。これにより、DRAM18からアドレス0h, 8h, 10h, 18hのデータが順次に出力される。DRAMコントローラ17は、DRAM18から出力さ

10

20

30

40

50

れたアドレス 0 h, 8 h, 10 h, 18 h のデータ（図 2 に示す 0 h のデータ, 8 h のデータ, 10 h のデータ, 18 h のデータ）を、キャッシングメモリコントローラ 15 に向けて出力する。

【0034】

キャッシングメモリコントローラ 15 は、これらのデータをキャッシングメモリ 16 に格納するとともに、これらのデータのうちのアドレス 0 h のデータを、システムバス 13 を経由してマスター 12 に出力する。

【0035】

次いで、マスター 12 からアドレス 8 h のデータを読み出すための読み出し命令が、キャッシングメモリコントローラ 15 に向けて出力される。キャッシングメモリコントローラ 15 は、アドレス 8 h のデータがキャッシングメモリ 16 に存在しているか否かを確認する。キャッシングメモリ 16 には、先ほどの処理の過程で既にアドレス 8 h のデータが存在する（キャッシングヒットと称する）ため、キャッシングメモリコントローラ 15 は D R A M コントローラ 17 へのアクセスを行なわずに、キャッシングメモリ 16 へのアクセスを行なう。これにより、キャッシングメモリ 16 からアドレス 8 h のデータがキャッシングメモリコントローラ 15 に出力される。キャッシングメモリコントローラ 15 は、このデータ（8 h のデータ）を、システムバス 13 を経由してマスター 12 に出力する。

【0036】

さらに、マスター 12 からアドレス 10 h のデータを読み出すための読み出し命令が、キャッシングメモリコントローラ 15 に向けて出力される。キャッシングメモリコントローラ 15 は、アドレス 10 h のデータがキャッシングメモリ 16 に存在しているか否かを確認する。キャッシングメモリ 16 には、アドレス 10 h のデータも存在するため、キャッシングメモリコントローラ 15 はキャッシングメモリ 16 へのアクセスを行なう。これにより、キャッシングメモリ 16 からアドレス 10 h のデータがキャッシングメモリコントローラ 15 に出力される。キャッシングメモリコントローラ 15 は、このデータ（10 h のデータ）を、システムバス 13 を経由してマスター 12 に出力する。

【0037】

従来のメモリシステムでは、キャッシングメモリコントローラは、マスターとシステムバスとの間に配備される。このため、キャッシングメモリコントローラは、システムバスを介して D R A M をアクセスする必要がある。従って、アクセス効率が悪いという問題がある。

【0038】

これに対して、第 1 実施形態のメモリシステム 10 では、システムバス 13 と D R A M コントローラ 17 との間に、キャッシングメモリコントローラ 15 が配備されている。このキャッシングメモリコントローラ 15 は、D R A M コントローラ 17 に 1 キャッシュライン分のサイズ（64 ビット × 4 のサイズ）でアクセスする。また、このサイズは D R A M 18 のバーストサイズと同じである。従って、アクセス効率は高く、処理の高速化が図られている。

【0039】

また、従来のメモリシステムでは、キャッシングメモリコントローラでアドレス領域毎にキャッシング可能 / 禁止（キャッシングメモリへのデータの格納可能 / 禁止）を設定しているが、第 1 実施形態のメモリシステム 10 では、このような設定は必要なく、アドレスの全空間にわたりキャッシング可能とすることができます。また、キャッシングメモリ 16 の目的は、前述したように、D R A M コントローラ 15 へのアクセスの整列化と先読みデータの退避にあるので、キャッシングヒット率はそれほど高くなくてもよく、従ってキャッシングメモリ 16 のサイズは小さくて済む。

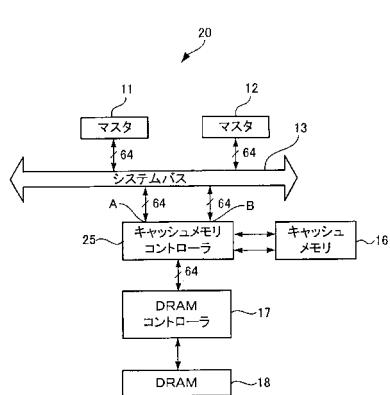

【0040】

図 3 は、本発明のメモリシステムの第 2 実施形態の回路構成を示す図である。

【0041】

尚、図 1 に示すメモリシステム 10 の構成要素と同じ構成要素には同一の符号を付し、異なる点について説明する。

10

20

30

40

50

## 【0042】

図3に示すメモリシステム20は、図1に示すメモリシステム10と比較し、図1に示すキャッシュメモリコントローラ15が、以下に説明するキャッシュメモリコントローラ25に置き換えられている点が異なっている。

## 【0043】

キャッシュメモリコントローラ25は、読み出し命令を受け取る2つのポートA, Bを有する。ポートA, Bは、それぞれ、64ビットのバス幅を有する。このように、第2実施形態のメモリシステム20では、システムバス13とキャッシュメモリコントローラ25との間が多重化されている。このため、キャッシュメモリコントローラ25は、マスタ11, 12からの読み出し命令（アクセス）を並列的に処理することができる。換言すれば、キャッシュメモリコントローラ25の帯域幅（バス幅）が大きくなっている。従って処理の高速化が図られる。

10

## 【0044】

また、マスタ11, 12がポートAとポートBのどちらを使ってアクセスを行なうのかについては、マスタ11, 12毎にどちらを使うのかを固定しておいてもよいし、あるいはアクセスした際に空いていた方のポートを使うようにしてもよい。さらに、データ転送量の少ない方のマスタに固定的に1つのポートを割り当てれば、他のマスタに負担をかけることなくアクセスを行なうことができる。ここで、複数ポートを持った高速メモリは多くのASICベンダで使用可能であるため、第2実施形態のメモリシステム20はASICに好適に搭載することができる。

20

## 【0045】

図4は、本発明のメモリシステムの第3実施形態の回路構成を示す図である。

## 【0046】

第3実施形態のメモリシステム30には、読み出し命令出力時に、以降の読み出し手順を表わす先読み情報を出力するマスタ22が備えられている。

## 【0047】

また、このメモリシステム30には、図3に示すキャッシュメモリコントローラ25のポートBに接続されたシーケンサ14が備えられている。このシーケンサ14は、マスタ22からの先読み情報に従って、キャッシュメモリコントローラ25に、DRAMコントローラ17を介してDRAM18からデータを先読みさせてキャッシュメモリ16に格納させるものである。このように、シーケンサ14とキャッシュメモリコントローラ25とを直結してDRAM18をアクセスすることにより、システムバス13を使用してDRAM18をアクセスする場合と比較し、システムバス13を他の処理に使用することができる、従って処理の高速化を図ることができる。

30

## 【0048】

さらに詳細に説明する。近年では、DRAM内に構築されたリンク構造のデータを1つずつ辿って、所望のデータを得るような回路機能ブロックであるIPコア（Intellectual Property Core）が存在する。

## 【0049】

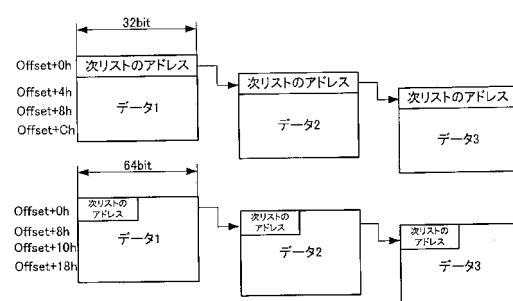

図5は、IPコアのリンク構造の例（2種類）を示す図である。

40

## 【0050】

図5の上段には、32ビットのデータ1が格納される第1のリストと、32ビットのデータ2が格納される第2のリストと、32ビットのデータ3が格納される第3のリストとが、関連づけられたリンク構造例が示されている。ここで、第1のリストの先頭アドレス（Offset+0h）で示されるデータ1の部分は、第2のリストの先頭アドレスを指し示している。また、第2のリストの先頭アドレスで示されるデータ2の部分は、第3のリストの先頭アドレスを指し示している。

## 【0051】

また、図5の下段には、64ビットのデータ1が格納される第1のリストと、64ビットのデータ2が格納される第2のリストと、64ビットのデータ3が格納される第3のリ

50

ストとが、関連づけられたリンク構造例が示されている。ここで、第1のリストの先頭アドレス (0 f f s e t + 0 h) で示されるデータ1の部分のうちの下位の32ビット分のデータ部分は、第2のリストの先頭アドレスを指し示している。また、第2のリストの先頭アドレスで示されるデータ2の部分のうちの下位の32ビット分のデータ部分は、第3のリストの先頭アドレスを指し示している。

#### 【0052】

前述した図4に示すメモリシステム30では、このようなリンク構造のリスト(データ)が取り扱われる。ここで、マスタ22からは、上記リンク構造のリストの読み出し手順を表わす先読み情報が出力される。シーケンサ14は、この先読み情報を受け取る。以下、図6を参照して詳細に説明する。

10

#### 【0053】

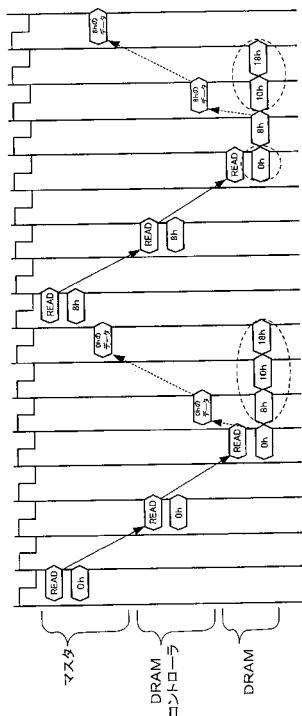

図6は、図4に示すメモリシステムにおける処理の流れを示す図である。

#### 【0054】

先ず、マスタ22から、2バースト分のアドレス(アドレス0h, 8h)のデータを読み出すための読み出し命令(READ2)が出力される。ここで、マスタ22から出力される読み出し命令には、アドレス0h, 8hとともに、図5の下段に示すリンク構造のリストをアクセスするための先読み情報(フラグFLG)が付加される。

#### 【0055】

マスタ22からのリード命令(READ2)は、キャッシュメモリコントローラ25のポートAに入力される。ここで、キャッシュメモリコントローラ25は、フラグFLGが付加されたアドレス0h, 8hのデータがキャッシュメモリ16に存在しているか否かを確認する。

20

#### 【0056】

最初の時点では、キャッシュメモリ16には、アドレス0h, 8hのデータは存在しない(キャッシュミス)ため、キャッシュメモリコントローラ25は、DRAMコントローラ17にアクセスする。これを受け、DRAMコントローラ17は、4バースト単位でDRAM18にアクセスする。詳細には、DRAMコントローラ17から、4バースト分のアドレス(アドレス0h, 8h, 10h, 18h)のデータを読み出すための読み出し命令(READ4)が出力される。これにより、DRAM18からアドレス0h, 8h, 10h, 18hのデータa, b, c, dが出力される。これらのデータa, b, c, dは、DRAMコントローラ17に入力される。さらに、DRAMコントローラ17は、これらのデータa, b, c, dをキャッシュメモリコントローラ25に出力する。

30

#### 【0057】

キャッシュメモリコントローラ25は、DRAMコントローラ17からのデータa, b, c, dをキャッシュメモリ16に格納するとともに、フラグFLGが付されたアドレス0h, 8hに対応するデータa, bにフラグFLGを付して、マスタ22に出力する。

#### 【0058】

ここで、シーケンサ14は、キャッシュメモリコントローラ25のポートBを経由してDRAM18からの、アドレス0hのデータaを読み出す。このデータaは、次のリストの先頭アドレスAを示すものである。これにより、図6の下段に示すように、この先頭アドレスAを含む4バースト分のアドレス(アドレスA, A+8h, A+10h, A+18h)が指定され、これらのアドレスで指定されたデータe, f, g, hがDRAM18から出力される。このようにして、シーケンサ14でDRAM18のデータが先読みされる。さらに、これらのデータe, f, g, hは、DRAMコントローラ17, キャッシュメモリコントローラ25を経由してキャッシュメモリ16に格納される。

40

#### 【0059】

次いで、マスタ22から、2バースト分のアドレス(アドレスA, A+8h)のデータを読み出すための読み出し命令(READ2)が出力される。この読み出し命令には、アドレスA, A+8hとともに先読み情報(フラグFLG)が付加される。

#### 【0060】

50

マスタ22からの読み出し命令 (READ2) は、キャッシュメモリコントローラ25のポートAに入力される。キャッシュメモリコントローラ25は、フラグFLGが付加されたアドレスA, A+8hのデータがキャッシュメモリ16に存在するか否かを確認する。

【0061】

ここでは、キャッシュメモリ16には、アドレスA, A+8hのデータは存在するため (キャッシュヒット)、キャッシュメモリコントローラ25は、キャッシュメモリ16からデータe, fを読み出して、フラグFLGが付されたアドレスA, A+8hに対応するデータe, fにフラグFLGを付して、マスタ22に出力する。

【0062】

このように、第3実施形態のメモリシステム30では、キャッシュメモリコントローラ25がマスタ22にデータ (リードデータ) を出力する際に、そのリードデータにフラグFLGが付加される。また、フラグFLGがシーケンサ14で観測された場合、シーケンサ14はリンク構造アクセスであると認識し、予測されたアドレスのデータの読み出しをDRAM18に対して行なう。さらに、マスタ22は、上述したようにアドレスA, A+8hのデータの読み出しを行なう。ここで、アドレスA, A+8hのデータは、既にキャッシュされているため、低レイテンシでアクセスを完了することができる。また、この時点でのアクセスもフラグFLGが付加されているため、シーケンサ14により先読みが行なわれる。ここで、シーケンサ14が行なう先読み動作は、シーケンサ14とDRAMコントローラ17の間での閉じられた動作 (限定された動作) であるため、システムバス13上のアクセスを阻害 (悪影響を及ぼす) することはほとんどない。

10

【0063】

シーケンサ14の構成としては、小規模のCPUを好適に用いることができる。このCPUで、予測のアルゴリズムをソフトウェアで実現することにより、その後の変更にも柔軟に対応することができる。尚、割り込み応答速度や動作周波数の点で問題がある場合には、このようなCPUを用いた構成とは異なる、以下に示す簡単な回路構成を採用することができる。

20

【0064】

図7は、簡単な回路構成を採用したシーケンサの回路を示す図である。

【0065】

図7には、レジスタ41と、比較&アクション決定部42と、マスタ43とを備えたシーケンサ40とが示されている。尚、この図7には、前述したキャッシュメモリコントローラ25も示されている。

30

【0066】

レジスタ41は、第1のレジスタ部41\_1と、第2のレジスタ部41\_2と、第3のレジスタ部41\_3とを有する。第1のレジスタ部41\_1には、第1のFLG番号と、その第1のFLG番号を使用したときにリードされたデータのどの部分をアドレスとして認識するかの情報 (アドレスオフセット値；単にオフセット値と記述する) が格納される。また、第2のレジスタ部41\_2には、第2のFLG番号と、その第2のFLG番号を使用したときにリードされたデータのどの部分をアドレスとして認識するかの情報 (オフセット値) が格納される。さらに、第3のレジスタ部41\_3には、第3のFLG番号と、その第3のFLG番号を使用したときにリードされたデータのどの部分をアドレスとして認識するかの情報 (オフセット値) が格納される。

40

【0067】

比較&アクション決定部42は、ポートAのアクセスを監視し、ポートAに現れたFLG番号と、レジスタ41に格納されているFLG番号とが一致した場合に、そのレジスタ41に格納されているオフセット値を使ってリードデータからアドレスを取り出す。取り出されたアドレスは、マスタ43に渡される。

【0068】

マスタ43は、比較&アクション決定部42から渡されたアドレスを先頭として4バーストのリード命令を、ポートBに向けて出力 (発行) する。

50

## 【0069】

このようにすることで、リンク構造が1種類ではない場合であっても、リンク構造の種類ごとに異なる手段でアドレスを予測することができる。また、FLG番号とアドレスは、システムバスを介して変更可能にしておくことで、柔軟性を持たせることができる。

## 【0070】

図8は、図7に示すシーケンサの動作を説明するための図である。

## 【0071】

ここでは、第1のレジスタ部41\_1には、オフセット値として‘1’が格納されているものとする。また、第2、第3のレジスタ部41\_2、41\_3には、オフセット値として共に‘0’が格納されているものとする。第1のレジスタ部41\_1に、オフセット値として‘1’が格納されているため、第1のFLG番号を使用したときのアドレスが予測される。

10

## 【0072】

ここで、比較&アクション決定部42は、ポートAに出力された4バースト分のデータa, b, c, dおよびFLG番号を監視する。ここでは、FLG番号は、第1のレジスタ部41\_1に格納されている第1のFLG番号を示すFLG=1であるものとする。比較&アクション決定部42では、このFLG番号(FLG=1)と、第1のレジスタ部41\_1に格納されているオフセット値とが一致したと判定し、データa, b, c, dのうちのデータaをアドレスとして使用する。このデータaは、マスタ43に渡され、このデータaを先頭のアドレスとして4バーストのリード命令を、キャッシュメモリコントローラ25のポートBに向けて出力する。以下、前述したように、キャッシュメモリコントローラ25は、DRAMコントローラ17を介してDRAM18からデータを先読みさせてキャッシュメモリ16に格納させる。

20

## 【図面の簡単な説明】

## 【0073】

【図1】本発明のメモリシステムの第1実施形態の回路構成を示す図である。

【図2】図1に示すメモリシステムにおける処理の流れを示す図である。

【図3】本発明のメモリシステムの第2実施形態の回路構成を示す図である。

【図4】本発明のメモリシステムの第3実施形態の回路構成を示す図である。

30

【図5】IPコアのリンク構造の例(2種類)を示す図である。

【図6】図4に示すメモリシステムにおける処理の流れを示す図である。

【図7】簡単な回路構成を採用したシーケンサの回路を示す図である。

【図8】図7に示すシーケンサの動作を説明するための図である。

【図9】従来のメモリシステムの回路構成を示す図である。

【図10】図9に示すメモリシステムにおける処理の流れを示す図である。

## 【符号の説明】

## 【0074】

10, 20, 30 メモリシステム

11, 12, 22, 43 マスタ

13 システムバス

40

14, 40 シーケンサ

15, 25 キャッシュメモリコントローラ

16 キャッシュメモリ

17 DRAMコントローラ

18 DRAM

41 レジスタ

42 比較&アクション決定部

41\_1 第1のレジスタ部

41\_2 第2のレジスタ部

41\_3 第3のレジスタ部

50

【 図 1 】

【 四 2 】

【図3】

【 図 5 】

【 図 4 】

【図10】

---

フロントページの続き

(56)参考文献 特開平08-055025(JP, A)

特開2000-250808(JP, A)

特開2002-215456(JP, A)

特開平07-056755(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 08 - 12 / 12