(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-119599

(P2004-119599A)

(43) 公開日 平成16年4月15日(2004.4.15)

(51) Int.Cl.<sup>7</sup>

**H01L 29/786**

**G02F 1/1333**

**G02F 1/1368**

**G09F 9/30**

**G09F 9/35**

F 1

H01L 29/78 626C

G02F 1/1333 505

G02F 1/1368

G09F 9/30 310

G09F 9/35 338

テーマコード(参考)

2H090

2H092

3K007

5C094

5F110

審査請求 未請求 請求項の数 16 O L (全 19 頁) 最終頁に続く

(21) 出願番号

特願2002-279289 (P2002-279289)

(22) 出願日

平成14年9月25日 (2002. 9. 25)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107076

弁理士 藤綱 英吉

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 平岩 卓

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 2H090 HA01 HB02X HB07X HC05 HC08

HD01 JA07 JB02 JC07 JD14

KA05 KA08 LA04

最終頁に続く

(54) 【発明の名称】薄膜半導体装置の製造方法、薄膜半導体装置、電気光学装置、および電子機器

## (57) 【要約】

【課題】基板表面の凹凸が薄膜半導体素子に影響を及ぼすことを防止して、電気的特性および信頼性を向上可能な薄膜半導体装置の製造方法、薄膜半導体装置、この薄膜半導体装置を TFT アレイ基板として用いた電気光学装置、およびこの電気光学装置を用いた電子機器を提供すること。

【解決手段】TFT アレイ基板 10において、基板 10 の表面に下地絶縁膜 11 を形成し、この下地絶縁膜 11 の表面側に TFT 30 や蓄積容量 60 を形成する。ここで、下地保護膜 11 は、膜厚が 1 μm 以上の平坦化膜であるため、基板 10 の表面に凹凸が存在している場合、あるいは基板 10 の表面に異物が付着している場合でも、それらの影響が TFT 30 や蓄積容量 60 に及ばない。

【選択図】 図 5

**【特許請求の範囲】****【請求項 1】**

基板の表面に下地絶縁膜を形成し、当該下地絶縁膜の表面側に薄膜半導体素子を形成する薄膜半導体膜装置の製造方法において、

前記下地絶縁膜を前記基板の表面に存在する凹凸を平坦化する平坦化膜として形成した後、当該下地絶縁膜の表面側に前記薄膜半導体素子を形成することを特徴とする薄膜半導体装置の製造方法。

**【請求項 2】**

請求項 1において、前記平坦化膜を形成した後、当該平坦化膜の表面に無機絶縁膜を形成し、当該無機絶縁膜の表面側に前記薄膜半導体素子を形成することを特徴とする薄膜半導体装置の製造方法。 10

**【請求項 3】**

請求項 1または 2において、前記基板の表面をプラズマ処理した後に、前記下地絶縁膜を前記基板の表面に存在する凹凸を平坦化する平坦化膜として形成することを特徴とする薄膜半導体装置の製造方法。

**【請求項 4】**

請求項 1ないし 3のいずれかにおいて、前記基板の表面に有機絶縁膜を塗布した後、当該有機絶縁膜を硬化させて前記下地絶縁膜を形成することを特徴とする薄膜半導体装置の製造方法。

**【請求項 5】**

請求項 1ないし 3のいずれかにおいて、前記基板の表面に無機材料の前駆体を塗布した後、当該前駆体を焼成して前記下地絶縁膜を形成することを特徴とする薄膜半導体装置の製造方法。 20

**【請求項 6】**

請求項 1ないし 3のいずれかにおいて、前記基板の表面に無機絶縁膜を形成した後、該無機絶縁膜の表面に塗膜を形成し、かかる後に、前記塗膜および前記無機絶縁膜を等しい速度でエッティング可能な条件で前記塗膜、および前記無機絶縁膜の表面をエッティングすることにより前記下地絶縁膜を形成する薄膜半導体装置の製造方法。

**【請求項 7】**

請求項 1ないし 6のいずれかに規定する方法で製造したことを特徴とする薄膜半導体装置 30。

**【請求項 8】**

基板の表面に下地絶縁膜が形成されているとともに、当該下地絶縁膜の表面側に薄膜半導体素子が形成された薄膜半導体膜装置において、

前記下地絶縁膜は、前記基板の表面に存在する凹凸を平坦化する平坦化膜として形成されていることを特徴とする薄膜半導体装置。

**【請求項 9】**

請求項 8において、前記平坦化膜の表面に無機絶縁膜が形成され、当該無機絶縁膜の表面側に前記薄膜半導体素子が形成されていることを特徴とする薄膜半導体装置。

**【請求項 10】**

請求項 8または 9において、前記下地絶縁膜は、前記基板の表面に塗布された有機絶縁膜を硬化させてなることを特徴とする薄膜半導体装置。 40

**【請求項 11】**

請求項 8または 9において、前記下地絶縁膜は、前記基板の表面に塗布された無機材料の前駆体を焼成してなることを特徴とする薄膜半導体装置。

**【請求項 12】**

請求項 8または 9において、前記下地絶縁膜は、前記基板の表面に形成された無機絶縁膜の表面をエッチバック法で平坦化してなることを特徴とする薄膜半導体装置。

**【請求項 13】**

請求項 8ないし 12のいずれかに規定する薄膜半導体装置を有し、少なくとも電気光学物 50

質を制御するために前記薄膜半導体素子が用いられたことを特徴とする電気光学装置。

【請求項 1 4】

請求項 1 3 において、前記電気光学物質は、液晶であることを特徴とする電気光学装置。

【請求項 1 5】

請求項 1 3 において、前記電気光学物質は、エレクトロルミネッセンス材料であることを特徴とする電気光学装置。

【請求項 1 6】

請求項 1 4 または 1 5 に規定する電気光学装置を用いたことを特徴とする電子機器。

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は、薄膜トランジスタ（以下、TFT という）などの薄膜半導体素子や薄膜キャパシタ素子が基板上に形成された薄膜半導体装置の製造方法、薄膜半導体装置、この薄膜半導体装置を TFT アレイ基板として用いた電気光学装置、およびこの電気光学装置を用いた電子機器に関するものである。

【0 0 0 2】

【従来の技術】

アクティブマトリクス型液晶装置や有機エレクトロルミネッセンス装置などの電気光学装置では、画素スイッチング用のアクティブ素子として複数の TFT が形成された TFT アレイ基板が薄膜半導体装置として用いられている。

【0 0 0 3】

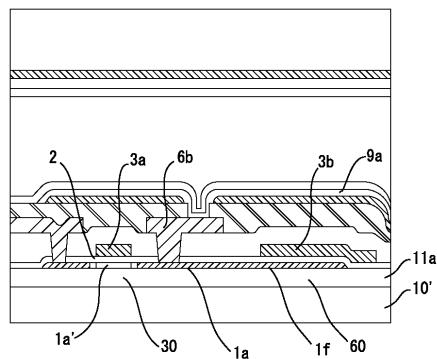

このような TFT アレイ基板では、図 1 3 に示すように、ガラスなどの基板 1 0 の表面側半導体膜 1 a が形成されている。半導体膜 1 a の表面にはシリコン酸化膜からなるゲート絶縁膜 2 が形成され、このゲート絶縁膜 2 の表面にゲート電極が走査線 3 a の一部として形成されている。半導体膜 1 a のうち、走査線 3 a に対してゲート絶縁膜 2 を介して対峙する領域が TFT 3 0 のチャネル領域 1 a になっている。このチャネル領域 1 a に対して一方側にはソース領域が形成され、他方側にはドレイン領域が形成されており、画素電極 9 a は、層間絶縁膜などに形成されたコンタクトホール、およびドレイン電極 6 b を介して TFT 3 0 のドレイン領域に電気的に接続している。また、ドレイン領域からの延設部分 1 f に対しては、ゲート絶縁膜 2 と同時形成された絶縁膜（誘電体膜）を介して容量線 3 b が上電極として対向することにより、蓄積容量 6 0 が構成されている。

【0 0 0 4】

このような TFT アレイ基板において、従来は、ガラスなどの基板 1 0 の表面に膜厚が 0.3 μm 程度のシリコン窒化膜などを下地絶縁膜 1 1 a として形成しておき、ガラスなどの基板 1 0 からナトリウムなどの不純物が半導体膜 1 a に溶出してくるのを防止している（例えば、特許文献 1 等）。

【0 0 0 5】

【特許文献 1】

特開平 2 - 5 0 6 5 3 号公報（第 1 頁 - 第 2 頁、図 1）

【0 0 0 6】

【発明が解決しようとする課題】

しかしながら、従来の下地絶縁膜 1 1 a は、あくまで基板 1 0 から溶出した不純物が TFT 3 0 や蓄積容量 6 0 の電気的特性や信頼性を低下させることを防止するために形成された薄い膜であるため、平坦化効果がない。このため、キズあるいは平坦性の不良等の理由により、基板 1 0 の表面に凹凸が存在している場合、あるいは基板 1 0 の表面に異物が付着している場合、それを完全に覆うことができない。従って、基板 1 0 の表面に存在している凹凸、あるいは基板 1 0 の表面に付着している異物に起因する凹凸が半導体膜 1 a に影響を及ぼす結果、TFT 3 0 および蓄積容量 6 0 の電気的特性や信頼性を低下させるという問題点がある。

【0 0 0 7】

10

20

30

40

50

以上の問題点に鑑みて、本発明の課題は、基板表面の凹凸が薄膜半導体素子に影響を及ぼすことを防止して、電気的特性および信頼性を向上可能な薄膜半導体装置の製造方法、薄膜半導体装置、この薄膜半導体装置を TFT アレイ基板として用いた電気光学装置、およびこの電気光学装置を用いた電子機器を提供することにある。

【 0 0 0 8 】

【課題を解決するための手段】

上記課題を解決するために、本発明では、基板の表面に下地絶縁膜を形成し、当該下地絶縁膜の表面側に薄膜半導体素子を形成する薄膜半導体膜装置の製造方法において、前記下地絶縁膜を前記基板の表面に存在する凹凸を平坦化する平坦化膜として形成した後、当該下地絶縁膜の表面側に前記薄膜半導体素子を形成することを特徴とする。

10

【 0 0 0 9 】

このような方法で製造された薄膜半導体装置では、基板の表面に下地絶縁膜が形成されているとともに、当該下地絶縁膜の表面側に薄膜半導体素子が形成され、前記下地絶縁膜は、何らかの理由により前記基板の表面に存在している凹凸を平坦化する平坦化膜として形成された構造を有している。

【 0 0 1 0 】

本発明では、下地絶縁膜を基板の表面に存在している凹凸を平坦化する平坦化膜として形成するため、キズあるいは平坦性の不良等のような何らかの理由により、基板の表面に凹凸が存在している場合、あるいは基板の表面に異物が付着している場合でも、それらを下地絶縁膜が完全に覆うような形状、または、前記凹凸が前記下地絶縁膜に埋められて、該下地絶縁膜の表面が滑らかに連続した形状となる。このため、基板の表面に存在している凹凸、あるいは基板の表面に付着している異物に起因する凹凸が薄膜半導体素子に影響を及ぼさない。また、本発明において、下地絶縁膜は、平坦化膜として形成されているので、その表面自身に凹凸がない。それ故、薄膜半導体装置の電気的特性や信頼性が向上する。

20

【 0 0 1 1 】

本発明において、前記平坦化膜の表面に無機絶縁膜を形成し、当該無機絶縁膜の表面側に前記薄膜半導体素子が形成することが好ましい。このように構成すると、基板の汚れなどに起因する薄膜半導体素子への汚染を無機絶縁膜で確実に防止することができる。

30

【 0 0 1 2 】

本発明において、前記基板の表面をプラズマ処理した後に、前記下地絶縁膜を前記基板の表面に存在する凹凸を平坦化する平坦化膜として形成した後、当該下地絶縁膜の表面側に前記薄膜半導体素子を形成することを特徴とする。前記プラズマ処理により、基板の表面に存在している凹凸の高さが減少したり、基板の表面に付着している異物が小さくなるので、その後形成される下地絶縁膜の表面の平坦性がさらに向上する。

【 0 0 1 3 】

本発明においては、例えば、前記基板の表面に有機絶縁膜を塗布した後、当該有機絶縁膜を硬化させて前記下地絶縁膜を形成する。

【 0 0 1 4 】

本発明においては、前記基板の表面に無機材料の前駆体を塗布した後、当該無機材料を焼成して前記下地絶縁膜を形成してもよい。

40

【 0 0 1 5 】

本発明においては、前記基板の表面に無機絶縁膜を形成した後、該無機絶縁膜の表面に塗膜を形成し、しかる後に、前記塗膜および前記無機絶縁膜を等しい速度でエッティング可能な条件で前記塗膜および前記無機絶縁膜の表面をエッティングするエッチバック法により前記下地絶縁膜を形成してもよい。

【 0 0 1 6 】

本発明に係る薄膜半導体装置は、例えば、電気光学装置に用いられる。この場合、前記薄膜半導体素子は、少なくとも電気光学物質を制御するために用いられる。

【 0 0 1 7 】

50

このような電気光学装置において、前記電気光学物質として液晶を用いる場合には、TFTアレイ基板と対向基板との間に液晶を保持する。

【0018】

また、前記電気光学物質としてエレクトロルミネッセンス材料を用いた場合には、TFTアレイ基板上に前記電気光学物質としての有機エレクトロルミネッセンス材料層を形成した構造となる。

【0019】

本発明を適用した電気光学装置は、モバイルコンピュータや携帯電話機などといった電子機器に用いることができる。

【0020】

【発明の実施の形態】

図面を参照して、本発明の実施の形態を説明する。なお、以下の説明では、薄膜半導体装置として、電気光学装置のTFTアレイ基板に本発明を適用した例を説明する。

【0021】

(電気光学装置の基本的な構成)

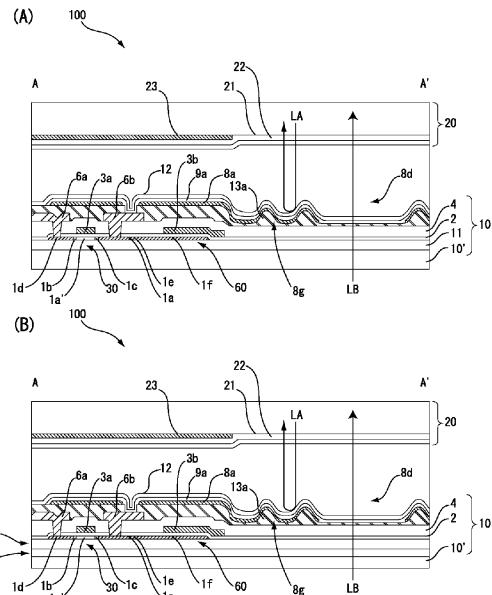

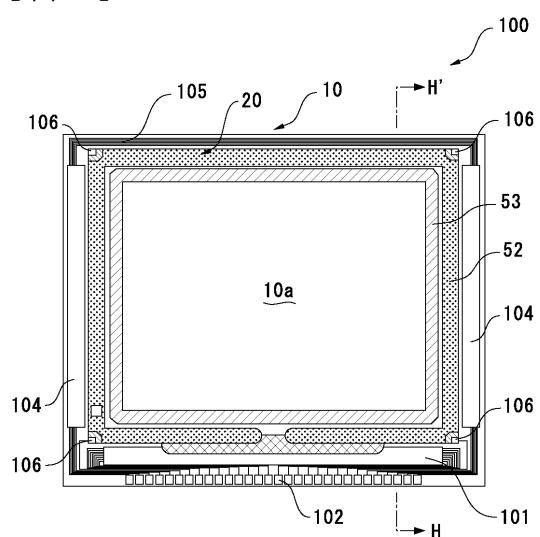

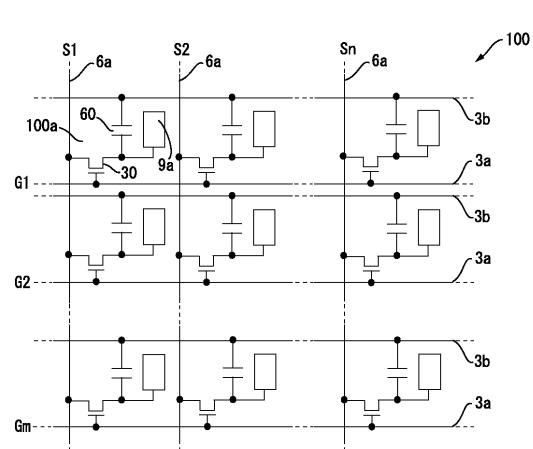

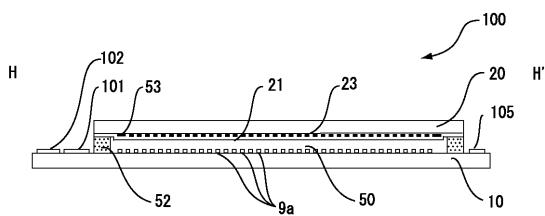

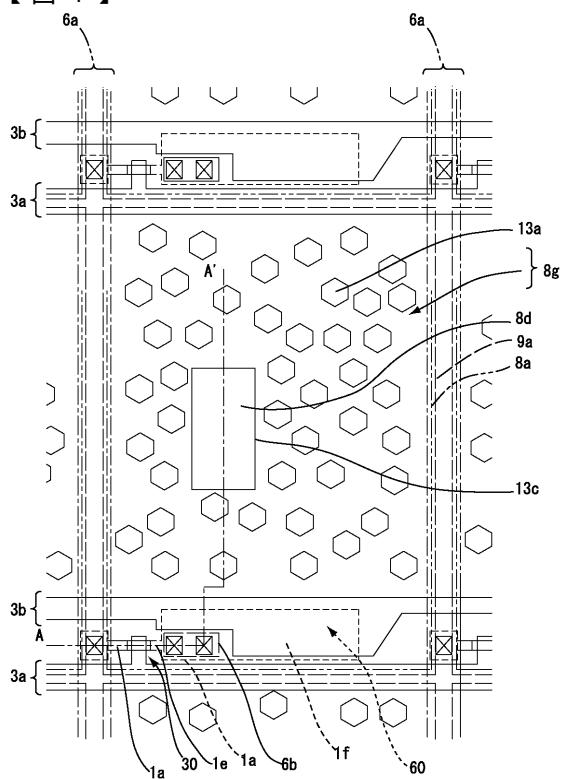

図1は、本発明を適用した電気光学装置を各構成要素とともに対向基板の側から見た平面図であり、図2は、図1のH-H断面図である。図3は、電気光学装置の画像表示領域においてマトリクス状に形成された複数の画素における各種素子、配線等の等価回路図である。なお、本形態の説明に用いた各図では、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならしめてある。

【0022】

図1および図2において、本形態の電気光学装置100は、シール材52によって貼り合わされたTFTアレイ基板10(薄膜半導体装置)と対向基板20との間に、電気光学物質としての液晶50が挟持されており、シール材52の形成領域の内側領域には、遮光性材料からなる周辺見切り53が形成されている。シール材52の外側の領域には、データ線駆動回路101、および実装端子102がTFTアレイ基板10の一辺に沿って形成されており、この一辺に隣接する2辺に沿って走査線駆動回路104が形成されている。TFTアレイ基板10の残る一辺には、画像表示領域の両側に設けられた走査線駆動回路104の間をつなぐための複数の配線105が設けられており、更に、周辺見切り53の下などを利用して、プリチャージ回路や検査回路が設けられることがある。また、対向基板20のコーナー部の少なくとも1箇所においては、TFTアレイ基板10と対向基板20との間で電気的導通をとるための上下導通材106が形成されている。

【0023】

なお、データ線駆動回路101および走査線駆動回路104をTFTアレイ基板10の上に形成する代わりに、たとえば、駆動用LSIが実装されたTAB(テープオートメイティッド、ボンディング)基板をTFTアレイ基板10の周辺部に形成された端子群に対して異方性導電膜を介して電気的および機械的に接続するようにしてもよい。なお、電気光学装置100では、使用する液晶50の種類、すなわち、TN(ツイステッドネマティック)モード、STN(スーパーTN)モード等々の動作モードや、ノーマリホワイトモード/ノーマリブラックモードの別に応じて、偏光フィルム、位相差フィルム、偏光板などが所定の向きに配置されるが、ここでは図示を省略してある。また、電気光学装置100をカラー表示用として構成する場合には、対向基板20において、TFTアレイ基板10の各画素電極(後述する。)に対向する領域にRGBのカラーフィルタをその保護膜とともに形成する。

【0024】

このような構造を有する電気光学装置100の画面表示領域においては、図3に示すように、複数の画素100aがマトリクス状に構成されているとともに、これらの画素100aの各々には、画素電極9<sub>1</sub>、およびこの画素電極9<sub>1</sub>を駆動するための画素スイッチング用のTFT30(薄膜半導体素子)が形成されており、画素信号S1、S2…Snを供給するデータ線6aが当該TFT30のソースに電気的に接続されている。データ線

10

20

30

40

50

6 a に書き込む画素信号 S 1、S 2 ··· S n は、この順に線順次に供給しても構わないし、相隣接する複数のデータ線 6 a 同士に対して、グループ毎に供給するようにしてもよい。また、TFT 3 0 のゲートには走査線 3 a が電気的に接続されており、所定のタイミングで、走査線 3 a にパルス的に走査信号 G 1、G 2 ··· G m をこの順に線順次で印加するように構成されている。画素電極 9 a は、TFT 3 0 のドレインに電気的に接続されており、スイッチング素子である TFT 3 0 を一定期間だけそのオン状態とすることにより、データ線 6 a から供給される画素信号 S 1、S 2 ··· S n を各画素に所定のタイミングで書き込む。このようにして画素電極 9 a を介して液晶に書き込まれた所定レベルの画素信号 S 1、S 2、··· S n は、図 2 に示す対向基板 2 0 の対向電極 2 1 との間で一定期間保持される。

10

## 【0025】

ここで、液晶 5 0 は、印加される電圧レベルにより分子集合の配向や秩序が変化することにより、光を変調し、階調表示を可能にする。ノーマリー ホワイトモードであれば、印加された電圧に応じて入射光がこの液晶 5 0 の部分を通過する光量が低下し、ノーマリーブラックモードであれば、印加された電圧に応じて入射光がこの液晶 5 0 の部分を通過する光量が増大していく。その結果、全体として電気光学装置 1 0 0 からは画素信号 S 1、S 2、··· S n に応じたコントラストを持つ光が出射される。

## 【0026】

なお、保持された画素信号 S 1、S 2、··· S n がリークするのを防ぐために、画素電極 9 a と対向電極との間に形成される液晶容量と並列に蓄積容量 6 0 を付加することがある。例えば、画素電極 9 a の電圧は、ソース電圧が印加された時間よりも 3 衍も長い時間だけ蓄積容量 6 0 (薄膜キャパシタ素子) により保持される。これにより、電荷の保持特性は改善され、コントラスト比の高い電気光学装置 1 0 0 が実現できる。なお、蓄積容量 6 0 を形成する方法としては、図 3 に例示するように、蓄積容量 6 0 を形成するための配線である容量線 3 b との間に形成する場合、あるいは前段の走査線 3 a との間に形成する場合もいずれであってもよい。

20

## 【0027】

## (TFT アレイ基板の構成)

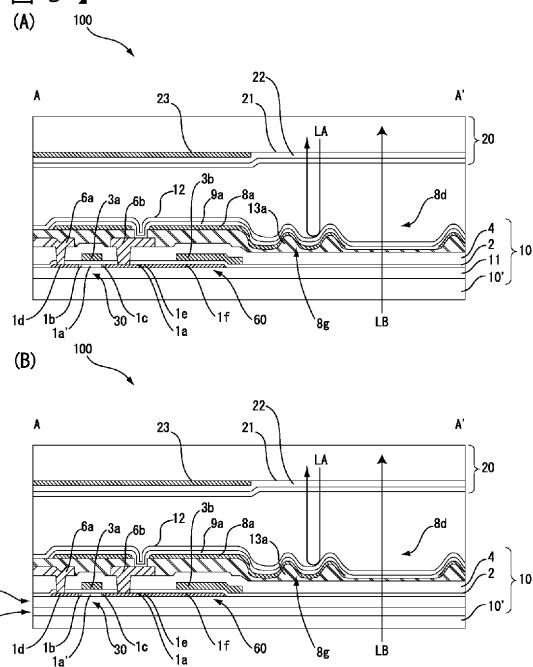

図 4 は、本形態の電気光学装置に用いた TFT アレイ基板の相隣接する複数の画素群の平面図である。図 5 (A) は、電気光学装置の画素の一部を図 4 の A - A 線に相当する位置で切断したときの断面図である。

30

## 【0028】

図 4において、TFT アレイ基板 1 0 上には、複数の透明なITO (Indium Tin Oxide) 膜からなる画素電極 9 a がマトリクス状に形成されており、これら各画素電極 9 a に対して画素スイッチング用の TFT 3 0 がそれぞれ接続している。また、画素電極 9 a の縦横の境界に沿って、データ線 6 a、走査線 3 a、および容量線 3 b が形成され、TFT 3 0 は、データ線 6 a および走査線 3 a に対して接続している。すなわち、データ線 6 a は、コンタクトホールを介して TFT 3 0 の高濃度ソース領域 1 d に電気的に接続し、走査線 3 a は、その突出部分が TFT 3 0 のゲート電極を構成している。なお、蓄積容量 6 0 は、画素スイッチング用の TFT 3 0 を形成するための半導体膜 1 の延設部分 1 f を導電化したものを下電極とし、この下電極 4 1 に容量線 3 b が上電極として重なった構造になっている。

40

## 【0029】

このように構成した画素領域の A - A 線における断面では、図 5 (A) に示すように、TFT アレイ基板 1 0 の基体たる透明な基板 1 0 0 の表面に透明な下地絶縁膜 1 1 が形成され、この下地絶縁膜 1 1 の表面には、厚さが 30 nm ~ 100 nm の島状の半導体膜 1 a が形成されている。

## 【0030】

ここで、下地絶縁膜 1 1 は、後述するように、基板 1 0 0 の表面に何らかの理由により存在している凹凸を平坦化する平坦化膜として形成される。前記凹凸の高さ或いは前記異物

50

の大きさが  $1 \mu m$  以下の小さい場合には、下地絶縁膜 1 1 の膜厚は  $1 \mu m$  以下でも良いが、前記凹凸の高さ或いは前記異物の大きさが  $1 \mu m$  以上と大きい場合には、下地絶縁膜 1 1 を  $1 \mu m$  以上の膜厚としてもよい。このため、何らかの理由により基板 1 0 の表面に凹凸が存在している場合、あるいは基板 1 0 の表面に異物が付着している場合でも、それらを下地絶縁膜 1 1 が完全に覆った状態、或いは前記凹凸や異物が下地絶縁膜 1 1 に埋められて、下地絶縁膜 1 1 の表面が滑らかに連続した形状となる。

【0031】

また、下地絶縁膜 1 1 は、後述するように、基板 1 0 の表面に有機絶縁膜を塗布した後、この有機絶縁膜を硬化させた絶縁膜、基板 1 0 の表面に無機材料の前駆体を塗布した後、この前駆体を焼成した絶縁膜、または基板 1 0 の表面に無機絶縁膜を形成した後、この無機絶縁膜の表面をエッチバック法より平坦化した絶縁膜である。それ故、下地絶縁膜 1 1 は、それ自身の表面も平坦である。

【0032】

半導体膜 1 a の表面には、厚さが約  $50 \sim 150 nm$  のシリコン酸化膜からなるゲート絶縁膜 2 が形成され、このゲート絶縁膜 2 の表面に、厚さが  $300 nm \sim 800 nm$  の走査線 3 a が形成されている。半導体膜 1 a のうち、走査線 3 a に対してゲート絶縁膜 2 を介して対峙する領域が TFT 3 0 のチャネル領域 1 a になっている。このチャネル領域 1 a に対して一方側には、低濃度ソース領域 1 b および高濃度ソース領域 1 d を備えるソース領域が形成され、他方側には低濃度ドレイン領域 1 c および高濃度ドレイン領域 1 e を備えるドレイン領域が形成されている。

【0033】

画素スイッチング用の TFT 3 0 の表面側には、厚さが  $300 nm \sim 800 nm$  のシリコン酸化膜からなる層間絶縁膜 4 が形成され、この層間絶縁膜 4 の表面には、厚さが  $100 nm \sim 300 nm$  のシリコン窒化膜からなる表面保護膜（図示せず）が形成されることがある。層間絶縁膜 4 の表面には、厚さが  $300 nm \sim 800 nm$  のデータ線 6 a が形成され、このデータ線 6 a は、層間絶縁膜 4 に形成されたコンタクトホールを介して高濃度ソース領域 1 d に電気的に接続している。層間絶縁膜 4 の表面にはデータ線 6 a と同時形成されたドレイン電極 6 b が形成され、このドレイン電極 6 b は、層間絶縁膜 4 に形成されたコンタクトホールを介して高濃度ドレイン領域 1 e に電気的に接続している。

【0034】

層間絶縁膜 4 の上層には、透光性の感光性樹脂からなる凹凸形成層 1 3 a が所定のパターンで形成されている、また、凹凸形成層 1 3 a の表面には、アルミニウム膜などからなる光反射膜 8 a が形成されている。従って、光反射膜 8 a の表面には、凹凸形成層 1 3 a の凹凸が反映されて凹凸パターン 8 g が形成されている。

【0035】

また、光反射膜 8 a の上層には ITO 膜からなる画素電極 9 a が形成されている。画素電極 9 a は、光反射膜 8 a の表面に直接、積層され、画素電極 9 a と光反射膜 8 a とは電気的に接続されている。また、画素電極 9 a は、感光性樹脂層 7 a および層間絶縁膜 4 に形成されたコンタクトホールを介してドレイン電極 6 b に電気的に接続している。

【0036】

ここで、光反射膜 8 a には、画素電極 9 a と平面的に重なる領域の一部に矩形の光透過窓 8 d が形成され（図 4 を参照）、この光透過窓 8 d に相当する部分には、ITO からなる画素電極 9 a は存在するが、光反射膜 8 a が存在しない。

【0037】

画素電極 9 a の表面側にはポリイミド膜からなる配向膜 1 2 が形成されている。この配向膜 1 2 は、ポリイミド膜に対してラビング処理が施された膜である。

【0038】

なお、高濃度ドレイン領域 1 e からの延設部分 1 f（下電極）に対しては、ゲート絶縁膜 2 a と同時形成された絶縁膜（誘電体膜）を介して容量線 3 b が上電極として対向することにより、蓄積容量 6 0 が構成されている。

10

20

30

40

50

## 【0039】

なお、TFT30は、好ましくは上述のようにLDD構造をもつが、低濃度ソース領域1b、および低濃度ドレイン領域1cに相当する領域に不純物イオンの打ち込みを行わないオフセット構造を有していてもよい。また、TFT30は、ゲート電極（走査線3aの一部）をマスクとして高濃度で不純物イオンを打ち込み、自己整合的に高濃度のソースおよびドレイン領域を形成したセルフアライン型のTFTであってもよい。

## 【0040】

また、本形態では、TFT30のゲート電極（走査線3a）をソース・ドレイン領域の間に1個のみ配置したシングルゲート構造としたが、これらの間に2個以上のゲート電極を配置してもよい。この際、各々のゲート電極には同一の信号が印加されるようにする。このようにデュアルゲート（ダブルゲート）、あるいはトリプルゲート以上でTFT30を構成すれば、チャネルとソース・ドレイン領域の接合部でのリーク電流を防止でき、オフ時の電流を低減することが出来る。これらのゲート電極の少なくとも1個をLDD構造あるいはオフセット構造にすれば、さらにオフ電流を低減でき、安定したスイッチング素子を得ることが出来る。

## 【0041】

ここで、TFTアレイ基板10では、図5(B)に示すように、透明な基板10の表面に透明な下地絶縁膜11を平坦化膜として形成した後、この平坦化膜としての下地絶縁膜11の表面にシリコン酸化膜などの無機絶縁膜14を形成し、この無機絶縁膜14の表面側にTFT30などを形成してもよい。このように構成すると、後述する下地絶縁膜11（平坦化膜）の効果に加えて、基板10からTFT30への汚染を無機絶縁膜14によって防止できる。

## 【0042】

## （対向基板の構成）

対向基板20では、TFTアレイ基板10に形成されている画素電極9aの縦横の境界領域と対向する領域にブラックマトリクス、あるいはブラックストライプなどと称せられる遮光膜23が形成され、その上層側には、ITO膜からなる対向電極21が形成されている。また、対向電極21の上層側には、ポリイミド膜からなる配向膜22が形成され、この配向膜22は、ポリイミド膜に対してラビング処理が施された膜である。

## 【0043】

## （表示動作）

このように構成した半透過・反射型の電気光学装置100では、画素電極9aの下層側に光反射膜8aが形成されているため、図5(A)に矢印LAで示すように、対向基板20側から入射した光をTFTアレイ基板10側で反射し、対向基板10側から出射された光によって画像を表示する（反射モード）。

## 【0044】

また、TFTアレイ基板10の裏面側に配置されたバックライト装置（図示せず）から出射された光のうち、光反射膜8aが形成されていない光透過窓8dに向かう光は、矢印LBで示すように、光透過窓8dを介して対向基板20側に透過し、表示に寄与する（透過モード）。

## 【0045】

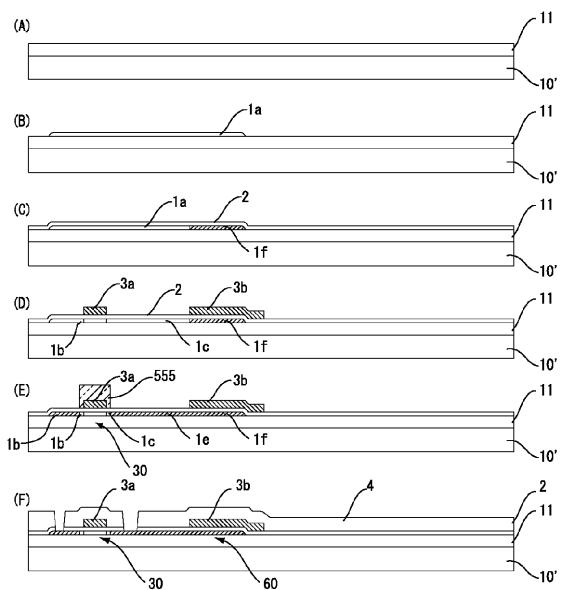

## （TFTアレイ基板の製造方法）

このような構成の電気光学装置100の製造工程のうち、TFTアレイ基板10の製造工程を、図6および図7を参照して説明する。図6および図7はそれぞれ、本形態のTFTアレイ基板10の製造方法を示す工程断面図であり、いずれの図においても、図4のA-A線における断面に相当する。

## 【0046】

まず、図6(A)に示すように、超音波洗浄等により清浄化したガラス等の基板10を準備した後、スピンドルコート法により、アクリル樹脂などの塗膜を形成し、それを光硬化させて、有機絶縁膜からなる透明な下地絶縁膜11を形成する。その結果、基板10の表

10

20

30

40

50

面に形成されている凹凸、あるいは基板 10 の表面に付着していた異物は、下地絶縁膜 11 で完全に覆われ、表面が平坦化される。

【0047】

また、下地絶縁膜 11 を形成するにあたっては、有機絶縁膜に代えて、ガラス等の基板 10 の表面に、スピンドルコート法により、無機絶縁膜の前駆体を塗布した後、焼成して、有機絶縁膜からなる透明な下地絶縁膜 11 を形成してもよい。ここで、使用可能な無機絶縁膜の前駆体としては、ペルヒドロポリシラザンがある。ペルヒドロポリシラザンとは無機ポリシラザンの一種であり、大気中で焼成することによってシリコン酸化膜に転化する塗布型コーティング材料である。たとえば、東燃（株）製のポリシラザンは、-(SiH<sub>2</sub>NH)-を単位とする無機ポリマーであり、キシレンなどの有機溶剤に可溶である。従って、この無機ポリマーの有機溶媒溶液（たとえば、20%キシレン溶液）を塗布液としてスピンドルコート法（たとえば、20001 rpm、20秒間）で塗布した後、450 の温度で大気中で焼成すると、水分や酸素と反応し、CVD法で成膜したシリコン酸化膜と同等以上の緻密なアモルファスのシリコン酸化膜を得ることができる。従って、この方法で成膜したシリコン酸化膜はCVD法で形成したシリコン酸化膜と同等の信頼性を有しているとともに、基板 10 の表面に形成されている凹凸、あるいは基板 10 の表面に付着していた異物は、下地絶縁膜 11 で完全に覆われ、表面が平坦化される。

【0048】

また、基板 10 の表面に付着していた異物が大きい場合や量が多い場合、下地絶縁膜 11 を形成する前に、基板 10 の表面をプラズマ処理し、前記異物をある程度除去してから下地絶縁膜 11 を形成しても良い。表面をプラズマ処理することにより、異物は除去されるものの、基板表面が荒れるという問題点があるが、前記下地絶縁膜 11 は、当該荒れを平坦化する効果があるので、まったく問題がない。前記プラズマ処理は、フレオン（CF<sub>4</sub>）ガスや酸素ガス或いはそれらを含む混合ガス等を用いる。

【0049】

次に、図 6 (B) に示すように、下地絶縁膜 11 の表面に島状の半導体膜 1a（能動層）を形成する。それには、基板温度が 150 ~ 450 の温度条件下で、基板 10 の全面に、アモルファスのシリコン膜からなる半導体膜をプラズマ CVD 法により 30 nm ~ 100 nm の厚さに形成した後、半導体膜に対してレーザ光を照射してレーザアニールを施し、アモルファスの半導体膜を一度溶融させた後、冷却固化過程を経て結晶化させる。この際には、各領域へのレーザ光の照射時間が非常に短時間であり、かつ、照射領域も基板全体に対して局所的であるため、基板全体が同時に高温に熱せられることがない。それ故、基板 10 としてガラス基板などを用いても熱による変形や割れ等が生じない。次に、半導体膜の表面にフォトリソグラフィ技術を用いてレジストマスクを形成し、このレジストマスクを介して半導体膜をエッチングすることにより、島状の半導体膜 1a を形成する。なお、半導体膜 1a を形成するときの原料ガスとしては、たとえばジシランやモノシリランを用いることができる。

【0050】

次に、図 6 (C) に示すように、350 以下の温度条件下で、基板 10 の全面に厚さが 50 nm ~ 150 nm のシリコン酸化膜からなるゲート絶縁膜 2 を形成する。このときの原料ガスは、たとえば TEOS と酸素ガスとの混合ガスを用いることができる。ここで形成するゲート絶縁膜 2 は、シリコン酸化膜に代えてシリコン窒化膜であってもよい。

【0051】

次に、図示を省略するが、所定のレジストマスクを介して半導体膜 1a の延設部分 1f に不純物イオンを打ち込んで、容量線 3b との間に蓄積容量 60 を構成するための下電極を形成する。

【0052】

次に、図 6 (D) に示すように、走査線 3a（ゲート電極）および容量線 3b を形成する。それには、スパッタ法などにより、基板 10 の全面にアルミニウム膜、タンタル膜、モリブデン膜、またはこれらの金属のいずれかを主成分とする合金膜からなる導電膜を 3

0 0 n m ~ 8 0 0 n m の厚さに形成した後、フォトリソグラフィ技術を用いてレジストマスクを形成し、このレジストマスクを介して導電膜をドライエッチングする。

【 0 0 5 3 】

次に、画素 T F T 部および駆動回路の N チャネル T F T 部（図示せず）の側には、走査線 3 a ( ゲート電極 ) をマスクとして、約  $0.1 \times 10^{13} / \text{cm}^2$  ~ 約  $10 \times 10^{13} / \text{cm}^2$  のドーズ量で低濃度の不純物イオン（リンイオン）を打ち込んで、走査線 3 a に対して自己整合的に低濃度ソース領域 1 b および低濃度ドレイン領域 1 c を形成する。ここで、走査線 3 a の真下に位置しているため、不純物イオンが導入されなかった部分は半導体膜 1 a のままのチャネル領域 1 a となる。

【 0 0 5 4 】

次に、図 6 ( E ) に示すように、走査線 3 a ( ゲート電極 ) より幅の広いレジストマスク 5 5 5 を形成して高濃度の不純物イオン（リンイオン）を約  $0.1 \times 10^{15} / \text{cm}^2$  ~ 約  $10 \times 10^{15} / \text{cm}^2$  のドーズ量で打ち込み、高濃度ソース領域 1 d およびドレイン領域 1 e を形成する。

【 0 0 5 5 】

これらの不純物導入工程に代えて、低濃度の不純物の打ち込みを行わずにゲート電極より幅の広いレジストマスクを形成した状態で高濃度の不純物（リンイオン）を打ち込み、オフセット構造のソース領域およびドレイン領域を形成してもよい。また、走査線 3 a をマスクにして高濃度の不純物を打ち込んで、セルファアライン構造のソース領域およびドレイン領域を形成してもよいことは勿論である。

【 0 0 5 6 】

なお、図示を省略するが、このような工程によって、周辺駆動回路部の N チャネル T F T 部を形成する。また、周辺駆動回路の P チャネル T F T 部を形成する際には、画素部および N チャネル T F T 部をレジストで被覆保護して、ゲート電極をマスクとして、約  $0.1 \times 10^{15} / \text{cm}^2$  ~ 約  $10 \times 10^{15} / \text{cm}^2$  のドーズ量でボロンイオンを打ち込むことにより、自己整合的に P チャネルのソース・ドレイン領域を形成する。この際、N チャネル T F T 部の形成時と同様、ゲート電極をマスクとして、約  $0.1 \times 10^{13} / \text{cm}^2$  ~ 約  $10 \times 10^{13} / \text{cm}^2$  のドーズ量で低濃度の不純物（ボロンイオン）を導入して、ポリシリコン膜に低濃度領域を形成した後、ゲート電極より幅の広いマスクを形成して高濃度の不純物（ボロンイオン）を約  $0.1 \times 10^{15} / \text{cm}^2$  ~ 約  $10 \times 10^{15} / \text{cm}^2$  のドーズ量で打ち込んで、L D D 構造（ライトリー・ドープト・ドレイン構造）のソース領域およびドレイン領域を形成してもよい。また、低濃度の不純物の打ち込みを行わずに、ゲート電極より幅の広いマスクを形成した状態で高濃度の不純物（リンイオン）を打ち込み、オフセット構造のソース領域およびドレイン領域を形成してもよい。これらのイオン打ち込み工程によって、C M O S 化が可能になり、周辺駆動回路の同一基板内への内蔵が可能となる。

【 0 0 5 7 】

次に、図 6 ( F ) に示すように、走査線 3 a の表面側に C V D 法などにより、厚さが 3 0 0 n m ~ 8 0 0 n m のシリコン酸化からなる層間絶縁膜 4 を形成した後、フォトリソグラフィ技術を用いてレジストマスクを形成し、このレジストマスクを介して層間絶縁膜 4 をエッチングしてコンタクトホールを形成する。層間絶縁膜 4 を形成するときの原料ガスは、たとえば T E O S と酸素ガスとの混合ガスを用いることができる。

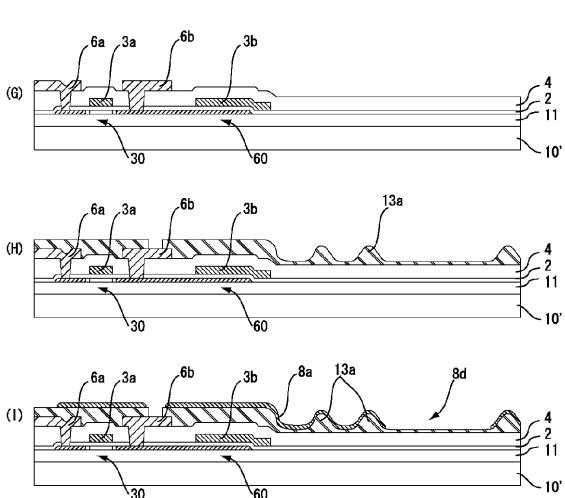

【 0 0 5 8 】

次に、図 7 ( G ) に示すように、層間絶縁膜 4 の表面側にデータ線 6 a およびドレイン電極 6 b を形成する。それには、アルミニウム膜、タンタル膜、モリブデン膜、またはこれらの金属のいずれかを主成分とする合金膜からなる導電膜をスパッタ法などで 3 0 0 n m ~ 8 0 0 n m の厚さに形成した後、フォトリソグラフィ技術を用いてレジストマスクを形成し、このレジストマスクを介して導電膜にドライエッチングを行う。

【 0 0 5 9 】

次に、図 7 ( H ) に示すように、データ線 6 a およびドレイン電極 6 b の表面側、あるいは

10

20

30

40

50

はその表面に表面保護膜を形成した後、スピンドルコート法などを用いて、ポジタイプの感光性樹脂を塗布し、次に、この感光性樹脂をハーフ露光した後、現像し、しかる後に、感光性樹脂に加熱処理を施して、表面になだらかな凹凸を備えた凹凸形成層13aを形成する。この際、凹凸形成層13aには、ドレイン電極6bと画素電極9aとを電気的に接続するためのコンタクトホールを形成しておく。

#### 【0060】

次に、図7(I)に示すように、凹凸形成層13aの表面にアルミニウムなどの金属膜を形成した後、その表面に、フォトリソグラフィ技術を用いて、金属膜をパターニングし、光反射膜8aを形成する。このようにして形成した光反射膜8aでは、凹凸形成層13aの表面形状が反映されるので、光反射膜8aの表面には、エッジのない、なだらかな凹凸パターン8aが形成される。この際、凹凸形成層13aの平坦領域と平面的に重なる領域に光透過窓8dを形成する。

#### 【0061】

次に、光反射膜8aの表面側に厚さが40nm~200nmのITO膜をスパッタ法などで形成した後、フォトリソグラフィ技術を用いてITO膜をパターニングし、図5(A)に示したように、画素電極9aを形成する。

#### 【0062】

しかる後には、画素電極9aの表面側にポリイミド膜(配向膜12)を形成する。それには、ブチルセロソルブやn-メチルピロリドンなどの溶媒に5~10重量%のポリイミドやポリアミド酸を溶解させたポリイミド・ワニスをフレキソ印刷した後、加熱・硬化(焼成)する。そして、ポリイミド膜を形成した基板をレーヨン系繊維からなるパフ布で一定方向に擦り、ポリイミド分子を表面近傍で一定方向に配列させる。その結果、後で充填した液晶分子とポリイミド分子との相互作用により液晶分子が一定方向に配列する。

#### 【0063】

##### (本形態の効果)

このように本形態のTFTアレイ基板10では、下地絶縁膜11を、キズあるいは平坦性の不良等の何らかの理由により、基板10の表面に存在している凹凸を平坦化する平坦化膜として形成するため、基板10の表面に存在している場合、あるいは基板10の表面に異物が付着している場合でも、それらを下地絶縁膜11が完全に覆うような形状、または、前記凹凸が前記下地絶縁膜11に埋められて、該下地絶縁膜11の表面が滑らかに連続した形状となる。このため、基板10の表面に存在している凹凸あるいは基板10の表面に付着している異物に起因する凹凸がTFT30あるいは蓄積容量60に影響を及ぼさない。また、下地絶縁膜11は、平坦化膜として形成されているので、その表面自身に凹凸がない。それ故、TFTアレイ基板10の電気的特性や信頼性が向上する。

#### 【0064】

##### [その他の実施の形態]

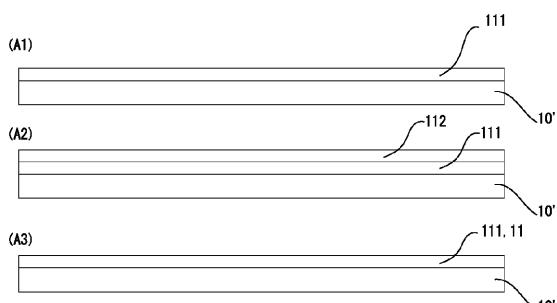

上記形態では、図6(A)を参照して説明した工程において、ガラス等の基板10にスピンドルコート法により形成した塗膜によって下地絶縁膜11を形成したが、図8(A1)~(A3)に示すように、エッチバック法により、無機絶縁膜からなる下地絶縁膜11を形成してもよい。このエッチバック法では、図8(A1)に示すように、まず、ガラス等の基板10の表面に膜厚が1μm以上のシリコン酸化膜などの無機絶縁膜111を形成した後、図8(A2)に示すように、スピンドルコート法によりレジスト膜112(塗膜)を形成し、それを硬化させた後、図8(A3)に示すように、レジスト膜112と無機絶縁膜111が等しい速度でエッチングされる条件でレジスト膜112の表面からエッチングしていく。その結果、成膜時に無機絶縁膜111の表面に凹凸があっても、エッチング後には、無機絶縁膜111の凸部がエッチング除去されるので、厚さが1μm以上の厚い下地絶縁膜11を平坦化膜として形成することができる。

#### 【0065】

また、上記形態では、ガラスなどの基板10を用いた例であったが、シリコンウェーハを基板として用いた半導体装置に本発明を適用してもよい。

## 【0066】

また、上記形態では、電気光学装置100として半透過・反射型の液晶装置を説明したが、光透過窓8dを形成せずに、電気光学装置100を全反射型の液晶装置として構成してもよい。

## 【0067】

さらに、上記形態では、画素スイッチング用のアクティプ素子としてTFTを用いた例を説明したが、アクティプ素子としてMIM(Metal Insulator Metal)素子などの薄膜ダイオード素子(TFD素子/Thin Film Diode素子)を用いた場合も同様である。

## 【0068】

さらにまた、上記形態では、薄膜半導体装置として、アクティプマトリクス型液晶装置に用いるTFTアレイ基板を例に説明したが、液晶以外の電気光学物質を用いた電気光学装置、例えば、図9および図10を参照して以下に説明する有機エレクトロルミネッセンス表示装置に用いるTFTアレイ基板、あるいは電気光学装置以外の薄膜半導体装置の製造などに本発明を適用してもよい。

## 【0069】

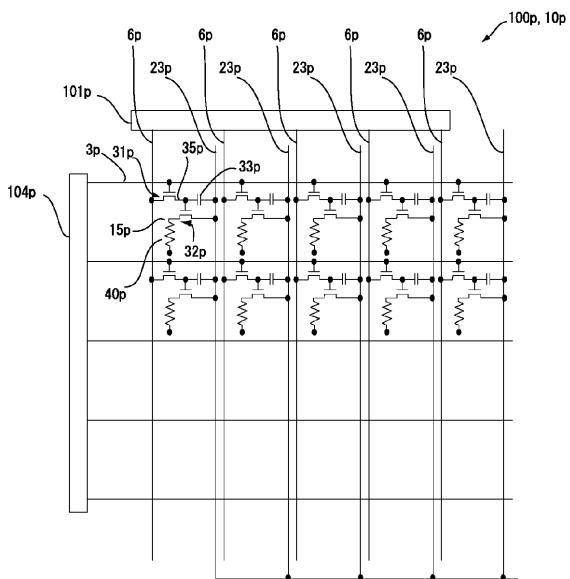

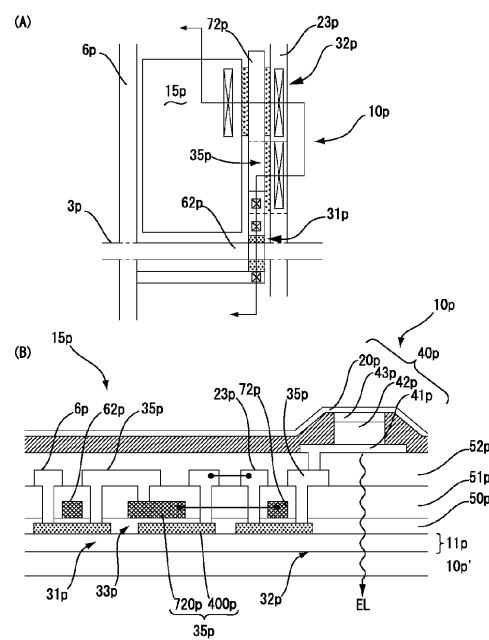

図9は、電荷注入型の有機薄膜エレクトロルミネンス素子を用いたアクティプマトリクス型電気光学装置のブロック図である。図10(A)、(B)はそれぞれ、図9に示す電気光学装置に形成した画素領域を拡大して示す平面図、およびその断面図である。

## 【0070】

図9に示す電気光学装置100pは、有機半導体膜に駆動電流が流れることによって発光するEL(エレクトロルミネンス)素子、またはLED(発光ダイオード)素子などの発光素子をTFTで駆動制御するアクティプマトリクス型の表示装置であり、このタイプの電気光学装置に用いられる発光素子はいずれも自己発光するため、バックライトを必要とせず、また、視野角依存性が少ないなどの利点がある。

## 【0071】

ここに示す電気光学装置100pでは、TFTアレイ基板10p上に、複数の走査線3pと、走査線3pの延設方向に対して交差する方向に延設された複数のデータ線6pと、これらのデータ線6pに並列する複数の共通給電線23pと、データ線6pと走査線3pとの交差点に対応する画素領域15pとが構成されている。データ線6pに対しては、シフトレジスタ、レベルシフタ、ビデオライン、アナログスイッチを備えるデータ側駆動回路101pが構成されている。走査線3pに対しては、シフトレジスタおよびレベルシフタを備える走査側駆動回路104pが構成されている。

## 【0072】

また、画素領域15pの各々には、走査線3pを介して走査信号がゲート電極に供給される第1のTFT31p(薄膜半導体素子)と、この第1のTFT31pを介してデータ線6pから供給される画像信号を保持する保持容量33p(薄膜キャパシタ素子)と、この保持容量33pによって保持された画像信号がゲート電極に供給される第2のTFT32p(薄膜半導体素子)と、第2のTFT32pを介して共通給電線23pに電気的に接続したときに共通給電線23pから駆動電流が流れ込む発光素子40pとが構成されている。

## 【0073】

本形態では、図10(A)、(B)に示すように、いずれの画素領域15pにおいても、島状の2つの半導体膜を利用して第1のTFT31pおよび第2のTFT32pがガラスなどからなる基板10pの表面側に形成されている。また、第2のTFT32pのソース・ドレイン領域の一方には、中継電極35pが電気的に接続し、この中継電極35pには画素電極41pが電気的に接続している。この画素電極41pの上層側には、正孔注入層42p、有機エレクトロルミネンス材料層としての有機半導体膜43p、リチウム含有アルミニウム、カルシウムなどの金属膜からなる対向電極20pが積層されている。ここで、対向電極20pは、データ線6pなどを跨いで複数の画素領域15pにわたって

10

20

30

40

50

形成されている。

【0074】

第2のTFT32pのソース・ドレイン領域のもう一方には、コンタクトホールを介して共通給電線23pが電気的に接続している。これに対して、第1のTFT31pでは、そのソース・ドレイン領域の一方に電気的に接続する電位保持電極35pは、第2のゲート電極72pの延設部分720pに電気的に接続している。この延設部分720pに対しては、その下層側において第2のゲート絶縁膜50pを介して半導体膜400pが対向し、この半導体膜400pは、それに導入された不純物によって導電化されているので、延設部分720pおよび第2のゲート絶縁膜50pとともに保持容量33pを構成している。ここで、半導体膜400pに対しては第1の層間絶縁膜51pのコンタクトホールを介して共通給電線23pが電気的に接続している。

10

【0075】

従って、保持容量33pは、第1のTFT31pを介してデータ線6pから供給される画像信号を保持するので、第1のTFT31pがオフになっても、第2のTFT32pのゲート電極31pは画像信号に相当する電位に保持される。それ故、発光素子40pには共通給電線23pから駆動電流が流れ続けるので、発光素子40pは発光し続け、画像を表示する。

20

【0076】

このように構成した電気光学装置100pでも、基板10pの表面に、上記実施の形態で説明した下地絶縁膜11pを形成しておけば、ガラスなどからなる基板10pの表面に凹凸が形成されている場合、あるいは、基板10pの表面に異物が付着している場合でも、それに起因する凹凸が上層側まで影響を及ぼすことがないので、保持容量33pやTFT31p、32pの電気的特性や信頼性が向上する。

20

【0077】

[電子機器への適用]

次に、本発明を適用した電気光学装置100、100pを備えた電子機器の一例を、図11、図12(A)、(B)を参照して説明する。

30

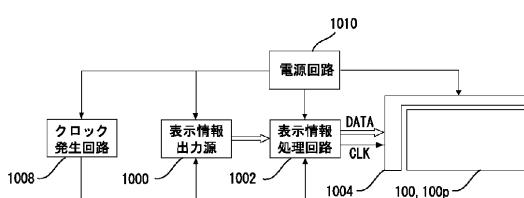

【0078】

図11は、上記の電気光学装置と同様に構成された電気光学装置100を備えた電子機器の構成をブロック図である。図12(A)、(B)はそれぞれ、本発明に係る液晶装置を用いた電子機器の一例としてのモバイル型のパーソナルコンピュータの説明図、および携帯電話機の説明図である。

30

【0079】

図11において、電子機器は、表示情報出力源1000、表示情報処理回路1002、駆動回路1004、電気光学装置100、100p、クロック発生回路1008、および電源回路1010を含んで構成される。表示情報出力源1000は、ROM(Read Only Memory)、RAM(Random Access Memory)、光ディスクなどのメモリ、テレビ信号の画信号を同調して出力する同調回路などを含んで構成され、クロック発生回路1008からのクロックに基づいて、所定フォーマットの画像信号を処理して表示情報処理回路1002に出力する。この表示情報処理回路1002は、たとえば增幅・極性反転回路、相展開回路、ローテーション回路、ガンマ補正回路、あるいはクランプ回路等の周知の各種処理回路を含んで構成され、クロック信号に基づいて入力された表示情報からデジタル信号を順次生成し、クロック信号CLKとともに駆動回路1004に出力する。駆動回路1004は、電気光学装置100、100pを駆動する。電源回路1010は、上述の各回路に所定の電源を供給する。なお、電気光学装置100、100pを構成するTFTアレイ基板の上に駆動回路1004を形成してもよく、それに加えて、表示情報処理回路1002もTFTアレイ基板の上に形成してもよい。

40

【0080】

このような構成の電子機器としては、投射型液晶表示装置(液晶プロジェクタ)、マルチメディア対応のパーソナルコンピュータ(PC)、およびエンジニアリング・ワークステ

50

ーション（EWS）、ページャ、あるいは携帯電話、ワードプロセッサ、テレビ、ビューファインダ型またはモニタ直視型のビデオテープレコーダ、電子手帳、電子卓上計算機、カーナビゲーション装置、POS端末、タッチパネルなどを挙げることができる。

【0081】

すなわち、図12（A）に示すように、パーソナルコンピュータ180は、キーボード181を備えた本体部182と、表示ユニット183とを有する。表示ユニット183は、前述した電気光学装置100、100pを含んで構成される。

【0082】

また、図12（B）に示すように、携帯電話機190は、複数の操作ボタン191と、前述した電気光学装置100、100pからなる表示部とを有している。

10

【0083】

【発明の効果】

以上説明したとおり、本発明では、下地絶縁膜を基板の表面に存在している凹凸を平坦化する平坦化膜として形成するため、基板の表面に凹凸が存在している場合、あるいは基板の表面に異物が付着している場合でも、それらを下地絶縁膜が完全に覆うような形状、または、前記凹凸が前記下地絶縁膜に埋められて、該下地絶縁膜の表面が滑らかに連続した形状となる。このため、基板の表面に存在している凹凸、あるいは基板の表面に付着している異物に起因する凹凸が薄膜半導体素子に影響を及ぼさない。また、本発明において、下地絶縁膜は、平坦化膜として形成されているので、その表面自身に凹凸がない。それ故、薄膜半導体装置の電気的特性や信頼性が向上する。

20

【図面の簡単な説明】

【図1】本発明が適用される電気光学装置を対向基板の側からみたときの平面図である。

【図2】図1のH-H線における断面図である。

【図3】電気光学装置において、マトリクス状に配置された複数の画素に形成された各種素子、配線などの等価回路図である。

【図4】本発明を適用した電気光学装置において、TFTアレイ基板に形成された各画素の構成を示す平面図である。

【図5】（A）、（B）はそれぞれ、本発明を適用した電気光学装置を、図4のA-A線に相当する位置での切断したときの断面図、およびその改良例に係る断面図である。

【図6】（A）～（F）は、本発明を適用した電気光学装置のTFTアレイ基板の製造方法を示す工程断面図である。

【図7】（G）～（I）は、本発明を適用した電気光学装置のTFTアレイ基板の製造方法を示す工程断面図である。

【図8】（A1）～（A3）は、エッチバック法を用いて平坦化膜を形成する様子を示す工程断面図である。

【図9】電荷注入型の有機薄膜エレクトロルミネセンス素子を用いたアクティブマトリクス型電気光学装置のブロック図である。

【図10】（A）、（B）はそれぞれ、図9に示す電気光学装置に形成した画素領域を拡大して示す平面図、およびその断面図である。

【図11】本発明に係る電気光学装置を表示装置として用いた電子機器の回路構成を示すブロック図である。

40

【図12】（A）、（B）はそれぞれ、本発明に係る電気光学装置を用いた電子機器の一実施形態としてのモバイル型のパーソナルコンピュータを示す説明図、および携帯電話機の説明図である。

【図13】従来の薄膜半導体装置の構成を示す断面図である。

【符号の説明】

1a 半導体膜

2 ゲート絶縁膜

3a 走査線

3b 容量線

50

4 層間絶縁膜

6 a データ線

6 b ドレイン電極

8 a 光反射膜

8 d 光透過窓

9 a 画素電極

100、100 p TFTアレイ基板(薄膜半導体装置)

10 基板

11 下地絶縁膜

14 無機絶縁膜

20 対向基板

21 対向電極

30、31 p、32 p TFT(薄膜半導体素子)

33 p 保持容量(薄膜キャパシタ素子)

50 液晶

60 蓄積容量(薄膜キャパシタ素子)

1000、100 p 電気光学装置

10

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

## フロントページの続き

(51) Int.Cl.<sup>7</sup> F I テーマコード(参考)

H 01 L 21/336 G 09 F 9/30 3 6 5 Z

H 05 B 33/02 G 09 F 9/35

H 05 B 33/14 H 05 B 33/02

H 05 B 33/14 A

H 01 L 29/78 6 2 7 A

F ターム(参考) 2H092 GA12 GA59 HA28 JA24 JB05 JB07 JB13 JB22 JB31 JB58

JB61 KA04 KB25 MA01 MA05 MA07 MA10 MA13 MA19 MA27

MA30 NA11 NA19 NA25 PA01 QA07 QA10

3K007 AB18 BA06 BB07 CA00 DB03 FA01

5C094 AA42 AA43 BA03 BA27 BA43 CA19 DA13 EB10 FB01 FB02

FB15

5F110 AA18 BB02 BB04 CC02 DD02 DD05 DD12 DD13 DD17 DD25

EE03 EE04 EE06 EE28 EE44 FF02 FF03 FF29 GG02 GG13

GG25 GG45 HJ01 HJ04 HJ12 HL03 HL04 HL23 HM14 HM15

NN03 NN04 NN24 NN27 NN72 NN73 PP03 QQ11 QQ19