(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6074200号

(P6074200)

(45) 発行日 平成29年2月1日(2017.2.1)

(24) 登録日 平成29年1月13日(2017.1.13)

(51) Int.Cl.

F 1

H04N 5/376 (2011.01)

H04N 5/374 (2011.01)H04N 5/335 760

H04N 5/335 740

請求項の数 11 (全 11 頁)

(21) 出願番号 特願2012-203536 (P2012-203536)

(22) 出願日 平成24年9月14日 (2012.9.14)

(65) 公開番号 特開2014-60540 (P2014-60540A)

(43) 公開日 平成26年4月3日 (2014.4.3)

審査請求日 平成27年9月8日 (2015.9.8)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】走査回路、固体撮像装置及びカメラ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1スイッチと、前記第1スイッチに入力ノードが接続された第1信号出力部と、前記第1信号出力部の出力ノードに接続された第2スイッチと、前記第2スイッチに入力ノードが接続された第2信号出力部とを各々が有する複数の単位回路を含むシフトレジスタと、

複数の第1信号線と、

複数の第2信号線と、

複数の第1バッファと、を有し、

前記複数の第1信号線の一部の複数の信号線が、前記複数の単位回路の前記第1スイッチに信号を供給し、

前記複数の第1信号線の他の一部の複数の信号線が、前記複数の単位回路の前記第2スイッチに信号を供給し、

前記複数の第1信号線の前記一部の複数の信号線は、互いに並んで配置され、

前記複数の第1信号線の前記他的一部の複数の信号線は、互いに並んで配置され、

前記複数の第1信号線の各々は、1つの第1バッファを介して前記複数の第2信号線の1つに接続され、

前記複数の第2信号線の一部の複数の信号線が、前記複数の単位回路の前記第1スイッチに接続されることによって、前記複数の第1信号線の前記一部の複数の信号線が供給する信号が前記複数の単位回路の前記第1スイッチに供給され、

10

20

前記複数の第2信号線の他の一部の複数の信号線が、前記複数の単位回路の前記第2スイッチに接続されることによって、前記複数の第1信号線の前記他の一部の複数の信号線が供給する信号が前記複数の単位回路の前記第2スイッチに供給される

ことを特徴とする走査回路。

【請求項2】

前記複数の第2信号線の前記一部の複数の信号線が互いに並んで配置され、

前記複数の第2信号線の前記他の一部の複数の信号線が互いに並んで配置されている

ことを特徴とする請求項1に記載の走査回路。

【請求項3】

さらに複数の第3信号線と、複数の第2バッファとを有し、

前記複数の第1信号線の各々は、1つの第2バッファを介して前記複数の第3信号線の

1つに接続され、

前記複数の第2信号線は、前記複数の単位回路の一部の単位回路に接続され、

前記複数の第3信号線の一部の複数の信号線が、前記複数の単位回路の他の一部の前記

第1スイッチに接続されることによって、前記複数の第1信号線の前記一部の複数の信号

線が供給する信号が前記複数の単位回路の前記他の一部の前記第1スイッチに供給され、

前記複数の第3信号線の他の一部の複数の信号線が、前記複数の単位回路の前記他の一部

の前記第2スイッチに接続されることによって、前記複数の第1信号線の前記他の一部

の複数の信号線が供給する信号が前記複数の単位回路の前記他の一部の前記第2スイッチ

に供給される

ことを特徴とする請求項2に記載の走査回路。

【請求項4】

前記複数の第3信号線の前記一部の複数の信号線が互いに並んで配置され、

前記複数の第3信号線の前記他の一部の複数の信号線が互いに並んで配置されている

ことを特徴とする請求項3に記載の走査回路。

【請求項5】

前記複数の第1信号線の前記一部の複数の信号線に第1の位相の信号を供給し、前記複

数の第1信号線の前記他の一部の複数の信号線に第2の位相の信号を供給する駆動部をさ

らに有する

ことを特徴とする請求項1から請求項4のいずれか1項に記載の走査回路。

【請求項6】

第1スイッチと、前記第1スイッチに入力ノードが接続された第1信号出力部と、前記

第1信号出力部の出力ノードに接続された第2スイッチと、前記第2スイッチに入力ノ

ドが接続された第2信号出力部とを各々が有する複数の単位回路を含むシフトレジスタと

、

複数の第1信号線と、

前記複数の第1信号線の一部の複数の信号線に第1の位相の信号を供給し、前記複数の

第1信号線の他の一部の複数の信号線に第2の位相の信号を供給する駆動部と、

を有し、

前記複数の第1信号線の前記一部の複数の信号線が、前記複数の単位回路の前記第1ス

イッチに信号を供給し、

前記複数の第1信号線の前記他の一部の複数の信号線が、前記複数の単位回路の前記第

2スイッチに信号を供給し、

前記複数の第1信号線の前記一部の複数の信号線は、互いに並んで配置され、

前記複数の第1信号線の前記他の一部の複数の信号線は、互いに並んで配置され、

前記第2の位相は前記第1の位相の逆位相であって、前記第1の位相の信号および前記

第2の位相の信号の2倍の周波数である信号を伝送する第4信号線をさらに備え、

前記第4信号線は、前記第1の位相の信号を伝送する前記第1信号線と、前記第2の位

相の信号を伝送する前記第1信号線との間に配置されている

ことを特徴とする走査回路。

10

20

30

40

50

**【請求項 7】**

前記複数の第1信号線の前記一部の複数の信号線に第1の位相の信号を供給し、前記複数の第1信号線の前記他の一部の複数の信号線に第2の位相の信号を供給する駆動部をさらに有し、

前記第2の位相は前記第1の位相の逆位相であって、前記第1の位相の信号および前記第2の位相の信号の2倍の周波数である信号を伝送する複数の第4信号線をさらに備え、

前記複数の第4信号線の1つは、前記第1の位相の信号を伝送する前記第2信号線と、前記第2の位相の信号を伝送する前記第2信号線との間に配置され、

前記複数の第4信号線の1つは、前記第1の位相の信号を伝送する前記第3信号線と、前記第2の位相の信号を伝送する前記第3信号線との間に配置されている

ことを特徴とする請求項3または請求項4に記載の走査回路。

**【請求項 8】**

前記第4信号線が伝送する信号のライズエッジは、前記第1の位相の信号及び前記第2の位相の信号の少なくとも一方のライズエッジと同期しており、

前記第4信号線が伝送する信号のフォールエッジは、前記第1の位相の信号及び前記第2の位相の信号の少なくとも一方のフォールエッジと同期している、

ことを特徴とする請求項6または請求項7に記載の走査回路。

**【請求項 9】**

前記第1信号出力部及び前記第2信号出力部がそれぞれインバータである

ことを特徴とする請求項1から請求項8のいずれか1項に記載の走査回路。

**【請求項 10】**

複数の行および複数の列を構成するように複数の画素が配列された画素アレイと、

前記複数の行のうち信号を読み出すべき行を選択する垂直走査回路と、

前記複数の列のうち信号を読み出すべき列を選択する水平走査回路と、を備え、

前記垂直走査回路および前記水平走査回路の少なくとも一方が請求項1から請求項9のいずれか1項に記載の走査回路を含む、

ことを特徴とする固体撮像装置。

**【請求項 11】**

請求項10に記載の固体撮像装置と、

前記固体撮像装置から出力される信号を処理する処理部と、

を備えることを特徴とするカメラ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、走査回路、固体撮像装置及びカメラに関する。

**【背景技術】****【0002】**

固体撮像装置は、画素アレイにおける各画素の画素信号を読み出すために、シフトレジスタを有する走査回路を備えうる。走査回路には複数の信号線が設けられ、当該シフトレジスタは、同じ位相の信号を伝送するための複数の第1信号線と、それと異なる位相の信号を伝送する複数の第2信号線とによって駆動されうる。このような複数の信号線を配置した構成では、信号線間の容量カップリングやクロストークを考慮した設計が必要である。

**【0003】**

特許文献1には、複数の第1信号線と複数の第2信号線との距離が、複数の第1信号線同士（ないし第2信号線同士）の距離よりも大きいバスライン方式半導体記憶装置の配線パターンが開示されている。この構造によると、同じ位相の信号を伝送する信号線間においては容量カップリングが抑制され、異なる位相の信号を伝送する信号線間におけるクロストークが抑制される。よって、走査回路の信号線の配線パターンに上述の構造を適用す

10

20

30

40

50

ることは有効である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平2-284449号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、このことは、各信号線に設けられるバッファを駆動するタイミングの時間差を小さくするため、瞬間に生じる貫通電流の総量が増加することによる電圧降下をもたらしうる。このことは、バッファの数が増大すると、より顕著な問題になりうる。

10

【0006】

本発明の目的は、複数の信号線を有する走査回路の動作の安定化に有利な技術を提供することである。

【課題を解決するための手段】

【0007】

本発明の一つの側面は走査回路にかかり、走査回路は、第1スイッチと、前記第1スイッチに入力ノードが接続された第1信号出力部と、前記第1信号出力部の出力ノードに接続された第2スイッチと、前記第2スイッチに入力ノードが接続された第2信号出力部とを各々が有する複数の単位回路を含むシフトレジスタと、複数の第1信号線と、複数の第2信号線と、複数の第1バッファと、を有し、前記複数の第1信号線の一部の複数の信号線が、前記複数の単位回路の前記第1スイッチに信号を供給し、前記複数の第1信号線の他の一部の複数の信号線が、前記複数の単位回路の前記第2スイッチに信号を供給し、前記複数の第1信号線の前記一部の複数の信号線は、互いに並んで配置され、前記複数の第1信号線の前記他の一部の複数の信号線は、互いに並んで配置され、前記複数の第1信号線の各々は、1つの第1バッファを介して前記複数の第2信号線の1つに接続され、前記複数の第2信号線の一部の複数の信号線が、前記複数の単位回路の前記第1スイッチに接続されることによって、前記複数の第1信号線の前記一部の複数の信号線が供給する信号が前記複数の単位回路の前記第1スイッチに供給され、前記複数の第2信号線の他の一部の複数の信号線が、前記複数の単位回路の前記第2スイッチに接続されることによって、前記複数の第1信号線の前記他の一部の複数の信号線が供給する信号が前記複数の単位回路の前記第2スイッチに供給される

20

ことを特徴とする。

30

【発明の効果】

【0008】

本発明によれば、複数の信号線を有する走査回路の動作を安定化することができる。

【図面の簡単な説明】

【0009】

40

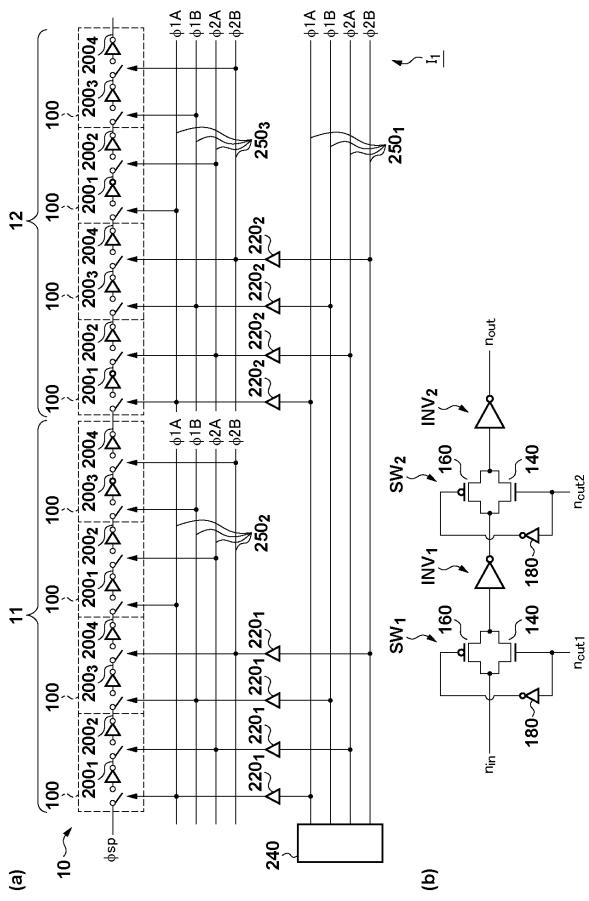

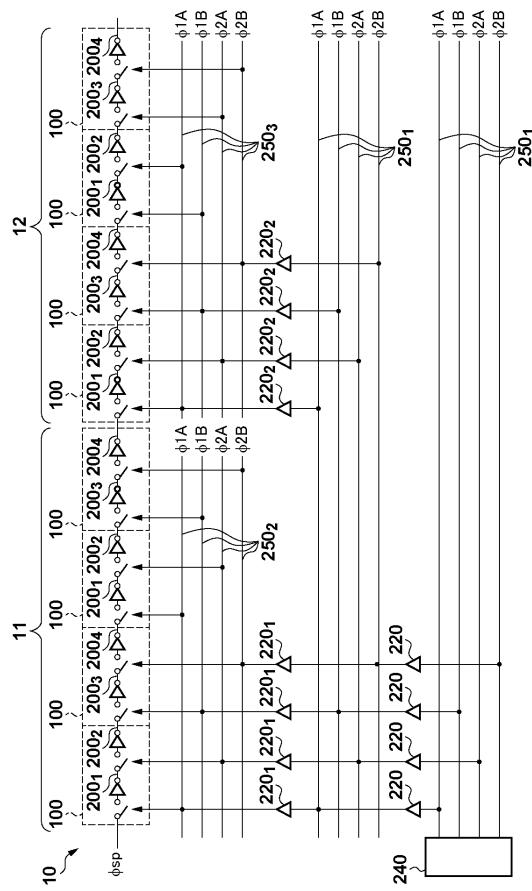

【図1】第1実施形態の走査回路の構成例を説明する図。

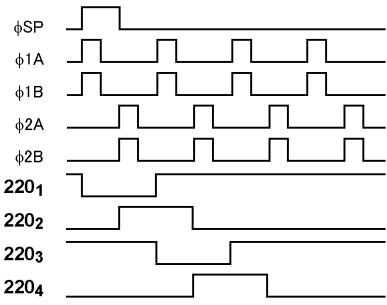

【図2】第1実施形態の走査回路のタイミングチャートの例を説明する図。

【図3】走査回路の他の実施形態の構成例を説明する図。

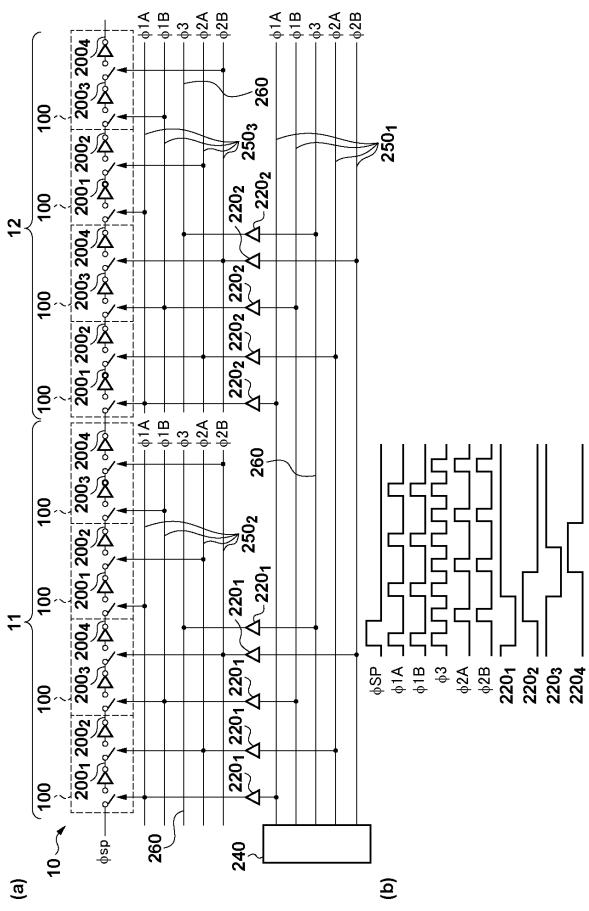

【図4】走査回路の他の実施形態の構成例を説明する図。

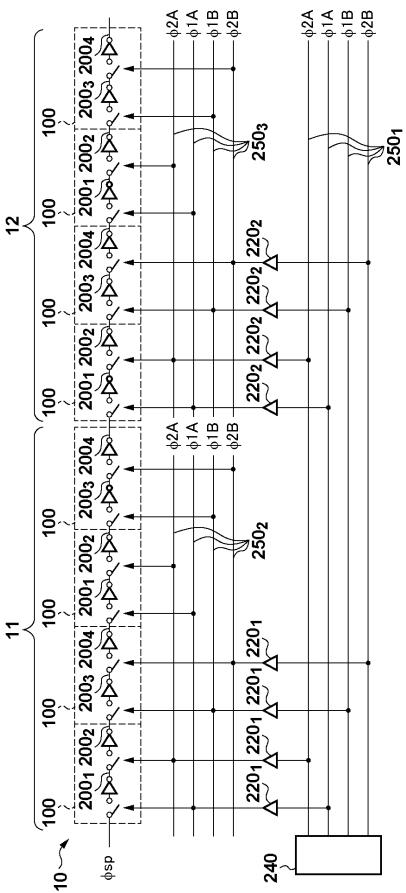

【図5】走査回路の他の実施形態の構成例を説明する図。

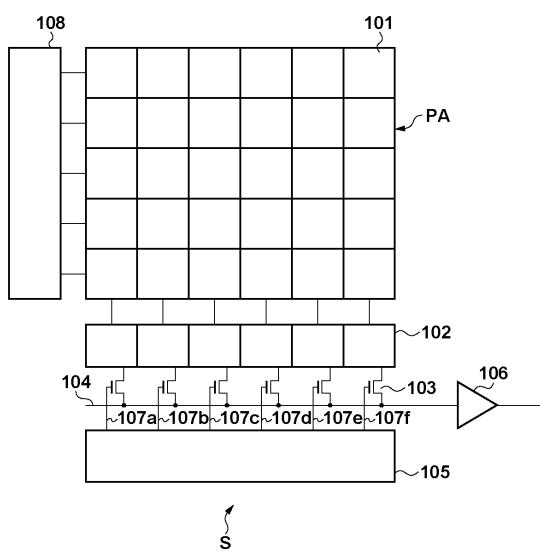

【図6】固体撮像装置の構成例を説明する図。

【発明を実施するための形態】

【0010】

図1乃至5を参照しながら、本実施形態の走査回路I<sub>1</sub>を説明する。走査回路I<sub>1</sub>は、図1(a)に例示されるように、第1信号線250<sub>1</sub>と、第2信号線250<sub>2</sub>と、第3信

50

号線 250<sub>3</sub> と、駆動部 240 と、第1バッファ 220<sub>1</sub> と、第2バッファ 220<sub>2</sub> と、シフトレジスタ 10 とを備えうる。ここでは、第1信号線 250<sub>1</sub> と、第2信号線 250<sub>2</sub> と、第3信号線 250<sub>3</sub> と、駆動部 240 と、第1バッファ 220<sub>1</sub> と、第2バッファ 220<sub>2</sub> とは、それぞれ4つずつ設けられた構成を示すが、仕様に応じた所定数だけ設けられればよく、この数量に限定されない。駆動部 240 は、各第1信号線 250<sub>1</sub> を駆動する。各第1バッファ 220<sub>1</sub> は、それに対応する第1信号線 250<sub>1</sub> 上(第1信号線上)の信号に応じて、対応する第2信号線 250<sub>2</sub> を駆動する。第2バッファ 220<sub>2</sub> は、それに対応する第1信号線 250<sub>1</sub> 上の信号に応じて、対応する第3信号線 250<sub>3</sub> を駆動する。

## 【0011】

10

シフトレジスタ 10 は、各第2信号線 250<sub>2</sub> 上(第2信号線上)の信号によって駆動される第1部分 11 と、各第3信号線 250<sub>3</sub> 上(第3信号線上)の信号によって駆動される第2部分 12 とを有する。4つの第1信号線 250<sub>1</sub> のうちの2本は、同相の信号 1A 及び 1B (1x) を伝送する信号線であり、これらは互いに並んで配置される。また、4つの第1信号線 250<sub>1</sub> のうちの他の2本は、信号 1x とは逆位相の信号 2A 及び 2B (2x) を伝送する信号線であり、これらは互いに並んで配置される。ここでは、信号 1x 及び 2x の信号線が、それぞれ2本ずつ配された構成を示すが、少なくとも2本ずつであればよく、例えば、仕様に応じて4本ずつ配され、計8本の信号線が配されてもよい。第2信号線 250<sub>2</sub> 及び第3信号線 250<sub>3</sub> のそれについても、第1信号線 250<sub>1</sub> と同様にして、信号 1x 及び 2x の信号線がそれぞれ2本ずつ配される。以下では、第1信号線 250<sub>1</sub> と第2信号線 250<sub>2</sub> と第3信号線 250<sub>3</sub> を代表して、単に「信号線 250」と呼び、第1バッファ 220<sub>1</sub> と第2バッファ 220<sub>2</sub> を代表して、単に「バッファ 220」と呼ぶ。

20

## 【0012】

シフトレジスタ 10 は、複数の単位回路 100 が直列に接続されて構成されうる。各単位回路 100 は、図 1 (b) に例示されるように、パルス信号を受ける入力端子 n<sub>in</sub> と、パルス信号を出力する出力端子 n<sub>out</sub> と、制御端子 n<sub>cnt</sub> とを有している。各単位回路 100 は、第1インバータ INV<sub>1</sub> と、第2インバータ INV<sub>2</sub> と、第1スイッチ SW<sub>1</sub> と、第2スイッチ SW<sub>2</sub> と、を含む。第1スイッチ SW<sub>1</sub> は、単位回路 100 の入力端子 n<sub>in</sub> と、第1インバータ INV<sub>1</sub> の入力端子との間に配置されている。第2スイッチ SW<sub>2</sub> は、第1インバータ INV<sub>1</sub> の出力端子と、第2インバータ INV<sub>2</sub> の入力端子との間に配置されている。制御端子 n<sub>cnt</sub> は、第1スイッチ SW<sub>1</sub> を制御するための第1制御端子 n<sub>cnt1</sub> と、第2スイッチ SW<sub>2</sub> を制御するための第2制御端子 n<sub>cnt2</sub> とを含む。第1スイッチ SW<sub>1</sub> 及び第2スイッチ SW<sub>2</sub> (以下、これらを代表して「スイッチ SW」と記す。) には、例えば、NMOSトランジスタ 140 と PMOSトランジスタ 160 とが並列に配されて構成されたアナログスイッチを用いればよい。PMOSトランジスタ 160 のゲートには、制御端子 n<sub>cnt</sub> に入力された信号がインバータ 180 を介して入力される。よって、NMOSトランジスタ 140 と PMOSトランジスタ 160 とは、状態(導通状態または非導通状態)が同時に切り替わる。

30

## 【0013】

40

図 2 は、走査回路 I<sub>1</sub> のタイミングチャート図を示している。走査回路 I<sub>1</sub> には、最初にスタートパルス SP が入力される。前述のとおり、信号 1A と信号 1B とは同相の信号であり、Hi レベルから Low レベルへの遷移と、Low レベルから Hi レベルへの遷移とは、それぞれ同じタイミングである。また、信号 1A 及び 1B と、信号 2A 及び 2B とは逆位相の関係である。各第1スイッチ SW<sub>1</sub> は、信号 1A と 1B とが Hi レベルのときに導通状態になり、Low レベルのときに非導通状態になる。各第2スイッチ SW<sub>2</sub> は、信号 2A と 2B とが Hi レベルのときに導通状態になり、Low レベルのときに非導通状態になる。よって、例えば、各ノード 200<sub>1</sub>、200<sub>2</sub>、200<sub>3</sub> 及び 200<sub>4</sub> の電位レベルは、スタートパルス SP に応答して、図 2 に示されるように、パルスが順にシフトするように伝達する形になる。

50

## 【0014】

ここで、前述のように、信号 1 A 及び 1 B を伝送する信号線は互いに並んで配置され、信号 2 A 及び 2 B を伝送する信号線は互いに並んで配置されうる。例えば、信号 1 A の信号線と信号 1 B の信号線との間に生じる寄生容量（配線間の容量）は、信号 1 A と 1 B とが同相であるため、当該寄生容量において充放電が生じない。このことは、これらの信号が同相でない場合に比べて、伝送すべき信号の波形の鈍りを防ぎ、応答特性等の面から有利である。信号 2 A の信号線と信号 2 B の信号線とについても同様である。各信号は、対応する各バッファ 220 に入力されるが、上記理由により、それらのタイミングの時間差が互いに小さくなる。このことは、一度に駆動されるバッファ 220 の数量が大きい場合は貫通電流の総量が大きくなるため、瞬間的な消費電力の増大をもたらし、それに伴う電圧降下、さらには信号レベルの変動による誤動作をもたらしうる。10

## 【0015】

そこで、各第 2 信号線 250<sub>2</sub> 上の信号は、シフトレジスタ 10 のうち第 1 部分 11 を駆動し、各第 3 信号線 250<sub>3</sub> 上の信号は、シフトレジスタ 10 のうち第 2 部分 12 を駆動する。第 1 部分 11 及び第 2 部分 12 のそれぞれは、少なくとも 2 以上の単位回路 100 に対して 1 つのバッファ 220 が設けられるように構成されている。この構成により、各単位回路 100 に対して 1 つのバッファ 220 が設けられる場合に対して、一度に駆動されるバッファ 220 の数量が低減されるため、走査回路 I<sub>1</sub> の動作が安定化する。

## 【0016】

また、図 1 (a)においては、信号 1 B の信号線と信号 2 A の信号線との配線パターン間の距離は、信号 1 A (又は 2 A) の信号線と信号 1 B (又は 2 B) の信号線との配線パターン間の距離よりも大きくするとよい。前述のように、信号 1 A の信号線と信号 1 B の信号線との間に生じる寄生容量は信号 1 A と 1 B とが同相であるため、当該寄生容量において充放電が生じない。信号 2 A の信号線と信号 2 B の信号線とについても同様である。しかし、図 1 (a)において、信号 1 B と 2 A とは互いに逆位相であるため、互いに隣接する信号 1 B の信号線と信号 2 A の信号線との間に生じる寄生容量において充放電が生じる。このことは、伝搬する信号の波形を鈍らせうる。具体的には、ライズエッジの Low レベルから High レベルへの遷移に要する時間と、フォールエッジの High レベルから Low レベルへの遷移に要する時間とが遅延しうる。そこで、各信号線の配線パターンを、上述のように配置することにより、寄生容量の影響を低減することができる。2030

## 【0017】

また、走査回路 I<sub>1</sub> は、図 3 (a) に例示されるように、信号 3 を伝達する信号線 260 (第 4 信号線) をさらに備える構成を探ってもよい。信号 3 は、図 3 (b) に例示されるように、信号 1 A、1 B、2 A 又は 2 B の 2 倍の周波数である。信号 3 のライズエッジは、信号 1 A 乃至 1 B、及び信号 2 A 乃至 2 B の少なくとも一方のライズエッジと同期している。また、信号 3 のフォールエッジは、信号 1 A 乃至 1 B、及び信号 2 A 乃至 2 B の少なくとも一方のフォールエッジと同期している。信号 3 を伝達する信号線の配線パターンは、第 1 乃至第 3 信号線のそれぞれにおいて、信号 1 B の信号線の配線パターンと信号 2 A の信号線の配線パターンとの間に配されるとい。このような構成を探ることにより、ライズエッジ及びフォールエッジの信号レベルが遷移する際ににおいては寄生容量の充放電が生じないため、上述と同様の効果が期待できる。40

## 【0018】

以上、実施形態を述べたが、本発明はこれらに限られるものではなく、目的、状態、用途及び機能その他の仕様に応じて、適宜、変更が可能であり、他の実施形態によっても為されうる。例えば、シフトレジスタ 10 は、アナログスイッチ及びインバータから成る単位回路で構成されたものを例示したがこれに限定されず、その他の公知の構成を探ってよい。また、例えば、各バッファ 220 が 2 つの単位回路 100 を駆動する構成を例示したが、これに限定されず、3 つ以上でもよい。また、例えば、信号 1 x を伝送する信号線

が互いに並んで配置され、信号  $2 \times$  を伝送する信号線が互いに並んで配置された構成を例示したが、図 4 に例示されるような、一方が他方の間に配置される構成においても、本発明を適用可能である。また、例えば、第 1 乃至第 3 信号線のそれぞれにおける信号線の配置はこれに限定されず、例えば、互いに位相が異なる信号線は互いに異なる配線層にそれぞれ配置してもよい。また、例えば、駆動部 240 と各単位回路 100 との間には 1 段のバッファ 220 が設けられた構成を例示したが、図 5 に例示されるように、本発明の趣旨を逸脱しない範囲で複数段のバッファ 220 を設けてよい。

#### 【0019】

##### ( 固体撮像装置への適用例 )

図 6 を参照しながら本発明の実施形態の固体撮像装置 S について説明する。固体撮像装置 S は、画素アレイ PA、垂直走査回路 108、及び水平走査回路 105 を備えている。画素アレイ PA は、複数の行および複数の列を構成するように複数の画素 101 が配列されて構成される。垂直走査回路 108 は、画素アレイ PA における複数の行のうち、信号を読み出すべき行を選択する走査回路  $I_1$  を含みうる。水平走査回路 105 は、画素アレイ PA における複数の列のうち、信号を読み出すべき列を選択する走査回路  $I_1$  を含みうる。固体撮像装置 S は、複数の列読み出し回路 102、複数の列選択スイッチ 103、共通出力線 104 および增幅回路 106 をさらに備えうる。各列読み出し回路 102 は、画素アレイ PA における複数の行のうち垂直走査回路 108 によって選択された行における対応する列の画素 101 から列信号線を介して信号を読み出す。各列選択スイッチ 103 は、水平走査回路 105 から出力される選択信号 107 ( 107a ~ 107f ) のうち対応する選択信号の論理レベルがアクティブルベルになるとオンして、対応する列読み出し回路と共通出力線 104 とを接続する。增幅回路 106 は、共通出力線 104 に伝達された信号を増幅して出力する。

#### 【0020】

走査回路  $I_1$  が水平走査回路 105 に提供される場合、例えば、該走査回路の出力信号が列選択スイッチ 103 に供給されうる。走査回路  $I_1$  が垂直走査回路 108 に適用される場合は、例えば、走査回路  $I_1$  の出力信号に基づいて、転送信号、リセット信号および行選択信号が生成され、各行の画素に供給されうる。各画素は、例えば、光電変換素子と、フローティングディフュージョンと、転送トランジスタと、增幅トランジスタと、リセットトランジスタと、行選択トランジスタとを含みうる。転送トランジスタは、光電変換素子に蓄積された電荷を転送信号に応じてフローティングディフュージョンに転送する。增幅トランジスタは、フローティングディフュージョンの電位に応じた信号を列信号線に出力する。リセットトランジスタは、リセット信号に応じてフローティングディフュージョンの電位をリセットする。行選択トランジスタは、行選択信号に応じてアクティブになり、これにより增幅トランジスタに列信号線を駆動させる。

#### 【0021】

固体撮像装置 S の動作モードについて、走査回路  $I_1$  を水平走査回路 105 に適用した場合を例示して述べる。固体撮像装置 S は、動作モードとして第 1 モードおよび第 2 モードを含みうる。第 1 モードは、複数の画素のそれぞれの信号を固体撮像装置 S から出力するモードであり、例えば、画素アレイ PA の全ての画素の信号を固体撮像装置 S から出力するモードでありうる。よって、第 1 モードは、いわゆる全画素モードである。

#### 【0022】

一方、第 2 モードは、複数の画素ごとに 1 つの信号を固体撮像装置 S から出力するモードであり、例えば、固体撮像装置 S から出力する各々の信号を複数の画素の信号から得るモードでありうる。固体撮像装置 S から出力する各々の信号を複数の画素の信号から得る方法としては、例えば、複数の画素の信号を合成（例えば、加算、平均化）する方法、複数の画素の信号から 1 つの信号を選択する方法（即ち、他の画素を間引く方法）がある。よって、第 2 モードは、いわゆる縮小モードである。第 2 モードは、例えば、固体撮像装置 S から出力する各々の信号を 2 つの画素の信号から得る 1/2 縮小モードを有する。

#### 【0023】

10

20

30

40

50

シフトレジスタ 10 が有する複数の単位回路 100 は、例えば、2 つのグループ（第 1 グループ及び第 2 グループ）にグループ分けされる。駆動部 240 は、第 1 モードにおいては、各グループの単位回路 100 の制御端子  $n_{c_{n_t}}$  に、クロック信号を供給する。即ち、互いに逆位相のクロック信号である信号  $1x$  と信号  $2x$  とが、対応する制御端子  $n_{c_{n_t}}$  の其々に入力される。これにより、当該クロック信号に応じて、各単位回路 100 は、入力されたパルス信号を順次、シフトさせるように動作する。

#### 【0024】

一方、第 2 モードでは、2 つグループのうち一方（例えば、第 1 グループ）の単位回路 100 の制御端子  $n_{c_{n_t}}$  には、第 1 グループの単位回路 100 がバッファとして動作する論理レベルを供給する。具体的には、駆動部 240 は、信号 1A 及び 1B の代わりに Hi レベルを出力する。そして、他方のグループ（例えば、第 2 グループ）の単位回路 100 の制御端子  $n_{c_{n_t}}$  にはクロック信号を供給する。即ち、駆動部 240 は、信号 2A 及び 2B を出力する。これにより、第 2 グループの単位回路 100 は、その前段の単位回路 100 の出力端子  $n_{o_{u_t}}$  から出力されたパルス信号を、当該クロック信号に応じて、その後段の単位回路 100 の入力端子  $n_{i_n}$  に転送する。このようにして、1 つの期間内に第 1 グループの単位回路 100 とその前段の単位回路 100 からパルス信号を出力させ、ここでは、1/2 縮小モードを実行する。

#### 【0025】

さらに、第 2 モードは、固体撮像装置 S から出力する各々の信号を 3 つ以上の画素の信号から得る 1/3 以下の縮小モードを有しうる。各縮小モードは、例えば、各信号線 250 が、縮小モードのバリエーションに応じた数量の信号線を有する構成にし、駆動部 240 が各縮小モードに対応した信号レベルを出力するように制御して、為されうる。

#### 【0026】

以上では、カメラに含まれる固体撮像装置について述べたが、カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置（例えば、パーソナルコンピュータ、携帯端末）も含まれる。カメラは、上記の実施形態として例示された本発明に係る固体撮像装置と、当該固体撮像装置から出力される信号を処理する処理部とを含みうる。この処理部は、例えば、A/D 変換器および当該 A/D 変換器から出力されるデジタルデータを処理するプロセッサを含みうる。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 小林 秀央

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 小倉 正徳

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 肇

(56)参考文献 特開2008-065085(JP, A)

特開2006-173382(JP, A)

特開2006-237229(JP, A)

特開2002-158933(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378