(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7044007号

(P7044007)

(45)発行日 令和4年3月30日(2022.3.30)

(24)登録日 令和4年3月22日(2022.3.22)

(51)国際特許分類

|        |                 |     |        |       |   |

|--------|-----------------|-----|--------|-------|---|

| H 01 L | 23/58 (2006.01) | F I | H 01 L | 23/56 | D |

| H 05 K | 7/06 (2006.01)  |     | H 05 K | 7/06  | C |

| G 01 K | 1/18 (2006.01)  |     | G 01 K | 1/18  |   |

| G 01 K | 1/14 (2021.01)  |     | G 01 K | 1/14  | L |

請求項の数 4 (全11頁)

(21)出願番号 特願2018-144347(P2018-144347)

(22)出願日 平成30年7月31日(2018.7.31)

(65)公開番号 特開2020-21815(P2020-21815A)

(43)公開日 令和2年2月6日(2020.2.6)

審査請求日 令和2年10月27日(2020.10.27)

(73)特許権者 395011665

株式会社オートネットワーク技術研究所

三重県四日市市西末広町1番14号

(73)特許権者 000183406

住友電装株式会社

三重県四日市市西末広町1番14号

(73)特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(74)代理人 100114557

弁理士 河野 英仁

(74)代理人 100078868

弁理士 河野 登夫

(72)発明者 原口 章

最終頁に続く

(54)【発明の名称】 回路構成体

## (57)【特許請求の範囲】

## 【請求項1】

回路基板と、

該回路基板の一面に実装されているスイッチング素子と、

前記回路基板の周縁部から延出し、前記一面側に折返している折返し部と、

該折返し部に実装され、前記スイッチング素子に接触している温度測定器と

を備え、

該温度測定器及びスイッチング素子間に、熱伝導性を有する固着部が設けられており、

前記温度測定器は前記固着部に埋設されている回路構成体。

## 【請求項2】

前記スイッチング素子、折返し部及び温度測定器は夫々複数ある請求項1に記載の回路構成体。

## 【請求項3】

前記固着部は熱硬化性である請求項1又は2に記載の回路構成体。

## 【請求項4】

前記回路基板の他面に対向し、電力が入力される入力側バスバーと、

前記回路基板の他面に対向し、電力が出力される出力側バスバーと

前記回路基板に設けられ、前記スイッチング素子の入力端子及び出力端子夫々を前記入力側バスバー及び出力側バスバーに接続する導電部と

を備える請求項1から請求項3までのいずれか一つに記載の回路構成体。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、回路構成体に関する。

**【背景技術】****【0002】**

従来、車両における電源及び負荷の間に、電源から負荷への電力供給に係る通電の制御を行なう回路構成体が搭載されている。回路構成体は、スイッチング素子を備え、スイッチング素子のオンオフを制御する制御回路を更に備える。スイッチング素子は、制御回路から入力される信号に基づいてオンオフする。回路構成体は、スイッチング素子のオンオフにより上記通電の制御を行う。

10

**【0003】**

スイッチング素子は過熱による不安定な動作及び故障等を防止するため、温度測定器によりスイッチング素子の温度を測定する場合がある。特許文献1においては、温度測定器(サーミスター)及びスイッチング素子(パワーMOSFET)を同一の回路基板上に実装し、温度測定対象であるスイッチング素子を取り付ける導電部(ランド)と、温度検出器(温度検出素子)が接続される導電部とを一体的に回路基板に形成している。

20

**【先行技術文献】****【特許文献】****【0004】**

【文献】特開2006-237144号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、回路構成体において熱容量の大きい放熱器を使用する場合があり、この場合、特許文献1の技術ではスイッチング素子からの回路基板への熱の伝導が弱くなり、温度検出器の周囲温度が上昇せず、スイッチング素子の温度を良好に測定できず、異常な発熱を良好に検出できない虞がある。

**【0006】**

本発明の目的は、良好にスイッチング素子の温度を測定することができる回路構成体を提供することにある。

30

**【課題を解決するための手段】****【0007】**

本発明の一態様に係る回路構成体は、回路基板と、該回路基板の一面に実装されているスイッチング素子と、前記回路基板の周縁部から延出し、前記一面側に折返している折返し部と、該折返し部に実装され、前記スイッチング素子に接触している温度測定器とを備える回路構成体。

**【発明の効果】****【0008】**

上記によれば、良好にスイッチング素子の温度を測定することができる。

40

**【図面の簡単な説明】****【0009】**

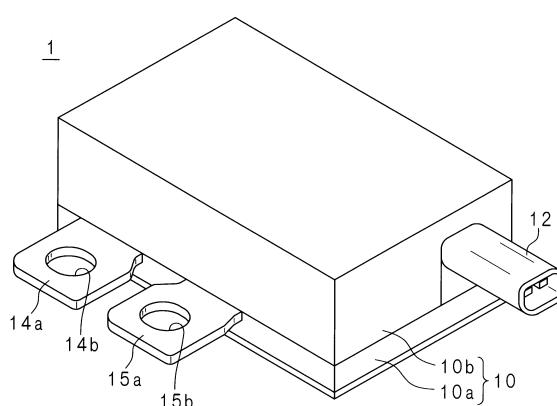

【図1】実施の形態に係る回路構成体の外観斜視図である。

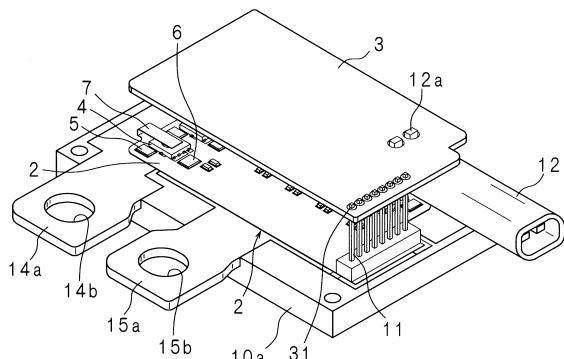

【図2】蓋部を取り外した状態を示す回路構成体の斜視図である。

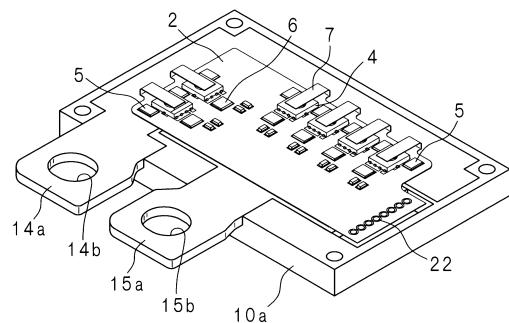

【図3】FETの搭載態様を示す斜視図である。

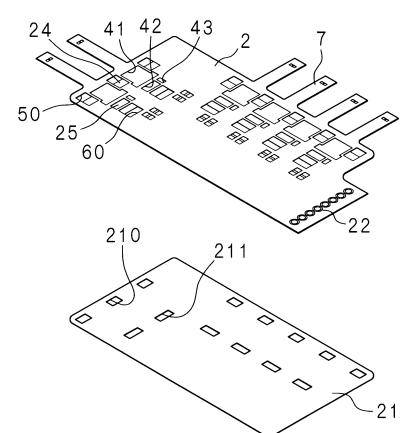

【図4】回路基板を載置していない状態を示す斜視図である。

【図5】FETの搭載を説明する斜視図である。

【図6】第1導電部及び第2導電部を示す部分拡大平面図である。

【図7】サーミスターの搭載態様を示す部分拡大平面図である。

【図8】図7のVIII-VIII線による断面図である。

50

【発明を実施するための形態】

【0010】

本発明の実施態様を列記して説明する。また、以下に記載する実施形態の少なくとも一部を任意に組み合わせても良い。

【0011】

本発明の一態様に係る回路構成体は、回路基板と、該回路基板の一面に実装されているスイッチング素子と、前記回路基板の周縁部から延出し、前記一面側に折返している折返し部と、該折返し部に実装され、前記スイッチング素子に接触している温度測定器とを備える回路構成体。

【0012】

本態様にあっては、温度測定器及びスイッチング素子との距離が近くなり、良好にスイッチング素子の温度を測定することができる。

【0013】

本発明の一態様に係る回路構成体は、前記スイッチング素子、折返し部及び温度測定器は夫々複数ある。

【0014】

本態様にあっては、複数のスイッチング素子の温度を各別に測定することができる。

を防止できる。

【0015】

本発明の一態様に係る回路構成体は、前記温度測定器及びスイッチング素子間には固着部が設けられている。

10

【0016】

本態様にあっては、また、温度測定器を固着部に良好に固定することができる。

【0017】

本発明の一態様に係る回路構成体は、前記固着部は熱硬化性である。

【0018】

本態様にあっては、熱硬化前の固着部に温度測定器を埋め込んだ後熱硬化することにより、温度測定器を良好に固着部に固定することができる。

【0019】

本発明の一態様に係る回路構成体は、前記回路基板の他面に対向し、電力が入力される入力側バスバーと、前記回路基板の他面に対向し、電力が出力される出力側バスバーと前記回路基板に設けられ、前記スイッチング素子の入力端子及び出力端子夫々を前記入力側バスバー及び出力側バスバーに接続する導電部とを備える。

20

【0020】

本態様にあっては、入力側バスバーから入力され出力側バスバーから出力される電力を、スイッチング素子によりオンオフすることができる。

【0021】

以下、本発明をその実施の形態を示す図面に基づいて具体的に説明する。

図1は実施の形態に係る回路構成体の外観斜視図である。回路構成体1は、車両が備えるバッテリ等の電源と、ランプ、ワイパ又はモータ等の負荷との間の電力供給経路に配される。

30

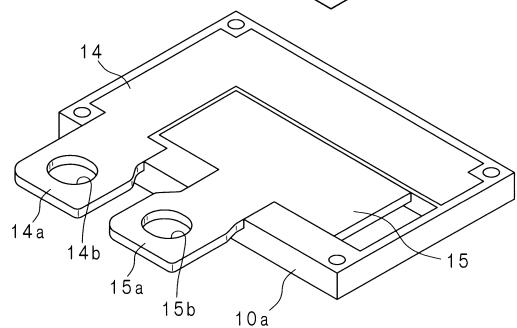

【0022】

回路構成体1は、筐体10を備える。筐体10は直方体状をなし、矩形平板状の本体部10a及び該本体部10aの一面を全面に亘って覆う蓋部10bを有する。

【0023】

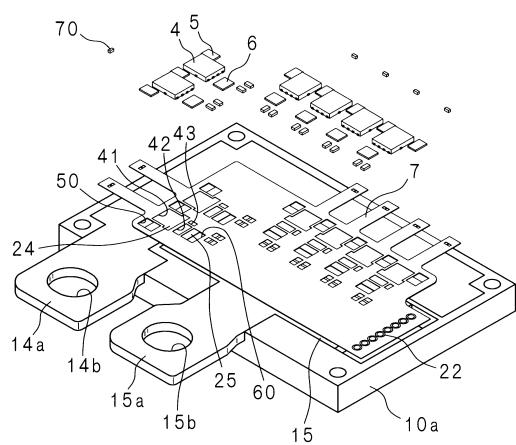

図2は、蓋部10bを取り外した状態を示す回路構成体の斜視図である。回路構成体1は、回路基板2及び制御基板3を備える。回路基板2は例えば、FPC (Flexible printed circuits) 等である。回路基板2には、一面を本体部10aに対向させて載置されている。回路基板2は、後述するFET (Field Effect Transistor) 及び導電片等の電子部品が実装されている。

40

50

## 【0024】

制御基板3は、矩形板状をなし、一面が回路基板に対向し、長手方向が回路基板2の長手方向に沿うように配されている。制御基板3の一面には、抵抗、コイル、コンデンサ、ダイオード等の電子部品と、これらの電子部品を電気的に接続する配線パターンとを含む制御回路(不図示)が設けられている。

## 【0025】

回路基板2の一の短辺部には、棒状の接続コネクタ11が立設されている。回路基板2は、接続コネクタ11を介して制御基板3に接続されている。

## 【0026】

コネクタ12は、外形が筒状をなし、コネクタ12の内部には複数の棒状の端子部12aが設けられている。端子部12aの一端部が外部に設けられたECU(Electronic Control Unit)に信号線(不図示)を介して接続される。コネクタ12における各端子部12aの他端部は、制御基板3の配線パターンに接続されている。コネクタ12は、蓋部10bを本体部10aに取り付けた場合、図1に示すように蓋部10bから突出している。

10

## 【0027】

図3は、FETの搭載態様を示す斜視図である。回路構成体1は、複数のFET4(図では6個)と、複数の第1導電片5(図では8枚)と、複数の第2導電片6(図では6枚)を備える。なお、FET4、第1導電片5及び第2導電片6は図示の個数に限られない。

## 【0028】

FET4は、回路基板2の他面において、前記一の短辺部の反対側の他の短辺部に沿って2個配されており、一の長辺部に沿って4個並設されている。回路基板2の一の短辺部には接続コネクタ11が接続される複数のスルーホール22が並設されている。

20

## 【0029】

第1導電片5は、各FET4を挟むように配されており、回路基板2の他の短辺部に沿って3個、一の長辺部に沿って5個配されている。第2導電片6は、回路基板2の他の短辺部に沿って2個、一の長辺部に沿って4個配されている。第2導電片6は夫々、FET4夫々に対応させて設けられており、FET4よりも内側に位置している。第2導電片6の周囲には、複数のチップ部品が配されている。第1導電片5及び第2導電片6は、導電性及び熱伝導性に優れた銅製のチップが好ましい。

## 【0030】

30

図4は、回路基板2を載置していない状態を示す斜視図である。図5は、FET4の搭載を説明する斜視図である。図6は、第1導電部及び第2導電部を示す部分拡大平面図である。

## 【0031】

図4に示すように、本体部10aの一面には、板状の入力側バスバー14及び出力側バスバー15が面一に設けられている。入力側バスバー14は平面視L字状をなし、L字の直線部分夫々が本体部10aの長辺部及び短辺部に沿うように位置している。入力側バスバー14の一端部には入力端子部14aが連続して設けられ、本体部10aから突出している。

## 【0032】

40

出力側バスバー15は矩形状をなし、本体部10aの一面の中央部に配されている。出力側バスバー15は、長手方向が本体部10aの長手方向に沿うように、入力側バスバー14と所定距離離隔させて配されている。出力側バスバー15において、出力側バスバー15の長辺の中央部には出力端子部15aが連続して設けられ、本体部10aから突出している。

## 【0033】

入力側バスバー14及び出力側バスバー15、入力端子部14a及び出力端子部15aは、例えば、板厚2mmで、表面にニッケルめっきを施したバスバー部材により形成される。

## 【0034】

入力端子部14a及び出力端子部15aには夫々、厚さ方向に貫通する貫通孔14b、1

50

4 b が設けられ、貫通孔 1 4 b, 1 5 b に挿通されたボルト（不図示）により、電源及び負荷に接続される。入力端子部 1 4 a が電源側に接続され、出力端子部 1 5 a が負荷側に接続される。

【 0 0 3 5 】

本体部 1 0 a は、例えばフェノール樹脂、ガラスエポキシ樹脂などの絶縁性樹脂材料を用いたインサート成形により製造される。絶縁性樹脂材料により成形される樹脂成形体は、入力端子部 1 4 a、出力端子部 1 5 a、入力側バスバー 1 4、及び出力側バスバー 1 5 と接合されることによって、これらを一体化する。また、樹脂成形体は、入力端子部 1 4 a 及び出力端子部 1 5 a 間と、入力側バスバー 1 4 及び出力側バスバー 1 5 間とに配されることによって、これらの間を絶縁する。

10

【 0 0 3 6 】

また、回路基板 2 は、図 4 に示すように矩形状の熱伝導性が高く、絶縁性の粘着性シート 2 1 により本体部 1 0 a に接着されている。

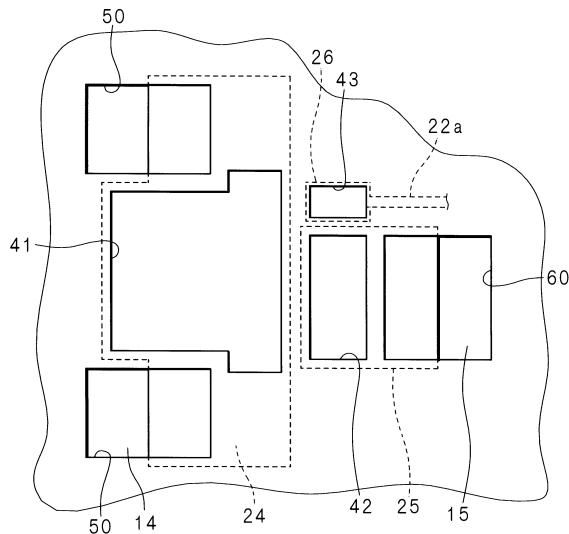

【 0 0 3 7 】

回路基板 2 には、各 F E T 4 に対応する位置に、第 1 開口部 4 1, 第 2 開口部 4 2, 第 3 開口部 4 3 が貫設されている。第 2 開口部 4 2 及び第 3 開口部 4 3 は、回路基板 2 において、第 1 開口部 4 1 よりも内側に位置し、長手方向又は短手方向に沿って並んでいる。第 1 開口部 4 1 は第 2 開口部 4 2 及び第 3 開口部 4 3 よりも大きく、第 2 開口部 4 2 は第 3 開口部 4 3 よりも大きい。

20

【 0 0 3 8 】

また、回路基板 2 には、各第 1 導電片 5 に対応する位置に第 4 開口部 5 0 が貫設されている。更に、各第 2 導電片 6 に対応する位置に第 5 開口部 6 0 が貫設されている。第 5 開口部 6 0 は、第 1 開口部 4 1 とで第 2 開口部 4 2 を挟むように位置している。

【 0 0 3 9 】

回路基板 2 の一面において、第 1 開口部 4 1、第 4 開口部 5 0 に対応する位置に矩形状の第 1 導電部 2 4 が設けられている。第 1 導電部 2 4 は、第 1 開口部 4 1 の全体から他面側に露出しており、第 4 開口部 5 0 の内側半分において他面側に露出している。なお、第 1 導電部は、上記のように露出していれば、全ての第 1 開口部 4 1 及び第 4 開口部 5 0 に対応するように L 字状に設けられてもよく、又は第 1 開口部 4 1 及び第 4 開口部 5 0 毎に設けられていてもよい。

30

【 0 0 4 0 】

第 2 開口部 4 2 及び第 5 開口部 6 0 に対応する位置に矩形状の第 2 導電部 2 5 が設けられている。第 2 導電部 2 5 は、第 2 開口部 4 2 全体から他面側に露出し、第 5 開口部 6 0 の外側半分から他面側に露出している。更に、回路基板 2 の一面において、第 3 開口部 4 3 に対応する位置にはランド部 2 6 が設けられ、第 3 開口部 4 3 全体から他面側に露出している。また、回路基板 2 の一面には、ランド部 2 6 及びスルーホール 2 2 を電気的に接続する接続部 2 2 a が設けられている。第 1 導電部 2 4、第 2 導電部 2 5、ランド部 2 6、接続部 2 2 a は例えば、銅箔により形成されている。

【 0 0 4 1 】

粘着性シート 2 1 には、回路基板 2 の第 4 開口部 5 0 及び第 5 開口部 6 0 に対応する位置に、第 1 孔 2 1 0 及び第 2 孔 2 1 1 が貫設されている。第 1 孔 2 1 0 は第 4 開口部 5 0 の外側半分に対応し、第 2 孔 2 1 1 は第 5 開口部 6 0 の内側半分に対応している。

40

【 0 0 4 2 】

回路基板 2 及び粘着性シート 2 1 は、第 1 導電部 2 4、第 2 導電部 2 5、ランド部 2 6、接続部 2 2 a を含む回路基板 2 の回路パターンが形成されている一面が粘着性シート 2 1 側に位置するように、本体部 1 0 a の一面に重ねて配されている。第 1 孔 2 1 0 は第 4 開口部 5 0 に連なり、かつ第 1 導電部 2 4 に重なっていない。また、第 2 孔 2 1 1 は、第 5 開口部 6 0 に連なり、第 2 導電部 2 5 に重なっていない。

【 0 0 4 3 】

図 6 に示すように、第 4 開口部 5 0 及び第 1 孔 2 1 0 からは入力側バスバー 1 4 の一部が

50

出し、第5開口部60及び第2孔211からは出力側バスバー15の一部が露出している。

【0044】

回路基板2は例えはポリイミドをベース部材として、各導電部等を含むパターンを一面にてエッチング加工により形成し、絶縁性のカバーフィルムを貼り付けたものが使用される。第1導電部24、第2導電部25、ランド部26、接続部22aとしては例えは35μmの銅箔が使用される。また、各導電片は例えは0.2mm～0.5mmの純銅製又は銅合金製であり、表面をスズ、ニッケル等によりめっき処理したものが使用される。

【0045】

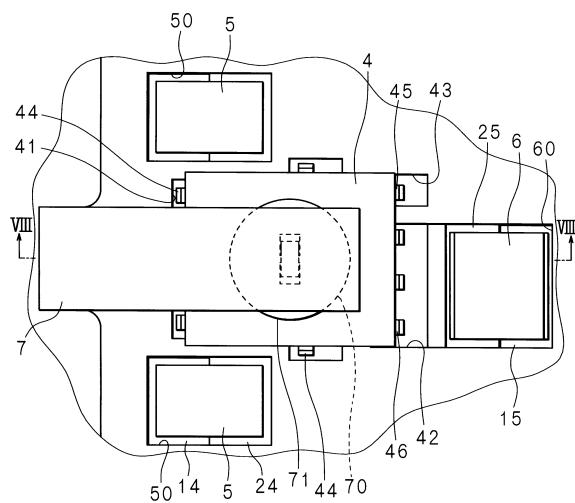

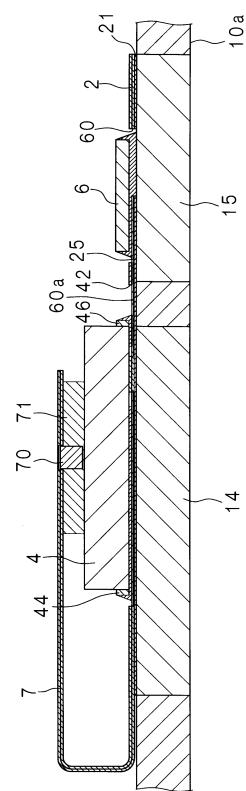

図7は、サーミスタ70の搭載態様を示す部分拡大平面図である。図8は、図7のVII-VII線による断面図である。

10

【0046】

FET4は、直方体状をなしており、一の側面及び該一の側面に連なる二つの側面から突出している4つのドレイン端子44と、前記一の側面の反対側の側面から突出している1つのゲート端子45及び3つのソース端子46とを備える。

【0047】

FET4は第1開口部41～第3開口部43に跨るように配されている。各ドレイン端子44は第1開口部41において第1導電部24にはんだ付けされ、ゲート端子45は第2開口部42においてランド部26にはんだ付けされ、ソース端子46は第3開口部43において第2導電部25にはんだ付けされている。

20

【0048】

第1導電片5は第4開口部50において、入力側バスバー14及び第1導電部24に跨るように配され、これらにはんだにより接続されている。第2導電片6は第5開口部60において、出力側バスバー15及び第2導電部25に跨るように配され、これらにはんだにより接続されている。

【0049】

FET4、第1導電片5及び第2導電片6が接続される第1導電部24及び第2導電部25には、例えは、はんだペーストを塗布し、これらを配置してリフローはんだ付けを行うことにより実装される。

30

【0050】

ここで、粘着性シート21は例えは熱伝導性フィラを含有し、アクリル系又はシリコーン系等の高耐熱性の粘着剤が使用されたシートが好ましい。これにより、FET4の発熱による熱をバスバー側に伝導して放熱でき、また、リフロー時の粘着性シート21の耐熱性を向上できる。

【0051】

回路基板2には、各第1開口部41に対応する位置に折返し部7が設けられている。折返し部7の延出端部には、サーミスタ70が取り付けられている。折返し部7は、回路基板2の短辺部又は長辺部から垂直に延出し、延出端部が各FET4に当接するように折り曲げられている。図4～図5は、折返し部7が折返される前の状態を示す。

40

【0052】

サーミスタ70により、各FET4の温度を個別に測定することができる。サーミスタ70は、回路基板2の銅箔により形成されている回路パターン（不図示）を介してスルーホール22に接続されている。なお、サーミスタ70は温度測定器の一例であり、サーミスタ70に代えて半導体温度センサ等その他の温度測定器を使用していてもよい。

【0053】

また、回路基板2の折返し部7はFET4の取り付け後、基端部側において折り曲げられており、延出端部がFET4の天面に当接している。折返し部7の延出端部に設けられたサーミスタ70は、折返し部7及びFET4に挟まれており、折返し部7及びFET4間に位置する固定部71に埋設することよりFET4の天面に固定されている。

【0054】

50

固着部 7 1 は、例えば熱伝導性フィラを含有した熱硬化性のシリコーン組成物により形成される。FET 4 の天面に熱硬化前のゲル状の固着部 7 1 を FET 4 に塗布し、折返し部 7 を折り曲げてサーミスタ 7 0 を固着部 7 1 に埋め込む。その後、固着部 7 1 を熱硬化させることによりサーミスタ 7 0 が FET 4 に固定される。

【 0 0 5 5 】

以上の構成により、FET 4 のゲート端子 4 5 は、ランド部 2 6 、接続部 2 2 a 、スルーホール 2 2 、接続コネクタ 1 1 を介して制御基板 3 に接続されている。これにより、外部の ECU からの信号に基づく制御基板 3 からの信号が FET 4 に入力される。制御基板 3 からの信号によって、FET 4 のオンオフが切り替えられる。ゲート端子 4 5 に所定の電圧が印加されることにより、ドレイン端子 4 4 及びソース端子 4 6 が導通し、FET 4 がオンになる。

10

【 0 0 5 6 】

また、FET 4 のドレイン端子 4 4 は、第 1 導電部 2 4 、第 1 導電片 5 を介して入力側バスバー 1 4 に接続されている。FET 4 のソース端子 4 6 は、第 2 導電部 2 5 及び第 2 導電片 6 を介して出力側バスバー 1 5 に接続されている。

【 0 0 5 7 】

したがって、制御基板 3 からの信号の入力により FET 4 がオンである場合、入力端子部 1 4 a から供給される電力は、第 1 導電部 2 4 、第 1 導電片 5 、FET 4 のドレイン端子 4 4 及びソース端子 4 6 、第 2 導電部 2 5 及び第 2 導電片 6 を介して出力側バスバー 1 5 を介して、出力端子部 1 5 a から出力される。これにより、回路構成体 1 を介して電源から負荷に電力が供給される。

20

【 0 0 5 8 】

制御基板 3 からの信号の入力により FET 4 がオフである場合、FET 4 のドレイン端子 4 4 及びソース端子 4 6 間は導通せず、電源から負荷への電力の供給が停止される。

【 0 0 5 9 】

更にサーミスタ 7 0 は、回路基板 2 の回路パターン、スルーホール 2 2 、接続コネクタ 1 1 を介して制御基板 3 に接続されている。これにより、サーミスタ 7 0 が測定した温度に係る信号を制御基板 3 に入力することができる。したがって、制御基板 3 はサーミスタ 7 0 からの信号に基づいて、FET 4 が過熱しているか否かを検出できる。制御基板 3 は FET 4 が過熱している場合、FET 4 をオフとし、FET 4 の過熱を防止することができる。

30

【 0 0 6 0 】

上記の構成によれば、サーミスタ 7 0 が FET 4 の天面に対して固定されているので、FET 4 の周辺温度を測定する等の態様よりも FET 4 との距離が近くなり、良好に FET 4 の温度を測定することができる。これにより、FET 4 の温度が上昇し、所定の閾値温度以上になった場合に FET 4 の過熱の有無を判定できる。また、サーミスタ 7 0 は固着部 7 1 に埋設されて固定されるため、より確実に固定することができる。

【 0 0 6 1 】

今回開示された実施形態はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は、上記した意味では無く、特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内のすべての変更が含まれることが意図される。

40

【 符号の説明 】

【 0 0 6 2 】

1 回路構成体

1 0 筐体

1 0 a 本体部

1 0 b 蓋部

1 1 接続コネクタ

1 2 コネクタ

1 2 a 端子部

50

|       |               |    |

|-------|---------------|----|

| 1 4   | 入力側バスバー       |    |

| 1 4 a | 入力端子部         |    |

| 1 4 b | 貫通孔           |    |

| 1 5   | 出力側バスバー       |    |

| 1 5 a | 出力端子部         |    |

| 1 5 b | 貫通孔           |    |

| 2     | 回路基板          |    |

| 2 1   | 粘着性シート(接着シート) |    |

| 2 1 0 | 第1孔           | 10 |

| 2 1 1 | 第2孔           |    |

| 2 2   | スルーホール        |    |

| 2 2 a | 接続部           |    |

| 2 4   | 第1導電部         |    |

| 2 5   | 第2導電部         |    |

| 2 6   | ランド部          |    |

| 3     | 制御基板          |    |

| 4 1   | 第1開口部         |    |

| 4 2   | 第2開口部         |    |

| 4 3   | 第3開口部         |    |

| 4     | FET           | 20 |

| 4 4   | ドレン端子         |    |

| 4 5   | ゲート端子         |    |

| 4 6   | ソース端子         |    |

| 5     | 第1導電片         |    |

| 5 0   | 第4開口部         |    |

| 6     | 第2導電片         |    |

| 6 0   | 第5開口部         |    |

| 7     | 折返し部          |    |

| 7 0   | サーミスタ(温度測定器)  |    |

| 7 1   | 固定部           | 30 |

【図面】

【図2】

40

50

【図3】

【図4】

10

20

【図5】

【図6】

30

40

50

【図7】

【図8】

10

20

30

40

50

---

フロントページの続き

三重県四日市市西末広町1番14号 株式会社オートネットワーク技術研究所内

審査官 正山 旭

(56)参考文献 国際公開第2001/015228 (WO, A1)

特開平09-289281 (JP, A)

特開2004-253759 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 23/58

H05K 7/06

G01K 1/18

G01K 1/14