#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

### (43) International Publication Date 4 November 2010 (04.11.2010)

##

## (10) International Publication Number WO 2010/127049 A2

(51) International Patent Classification: H04B 15/00 (2006.01) H04B 1/10 (2006.01)

(21) International Application Number:

PCT/US2010/032858

(22) International Filing Date:

28 April 2010 (28.04.2010)

(25) Filing Language:

**English**

(26) Publication Language:

English

(30) Priority Data:

12/433,200

30 April 2009 (30.04.2009) US

- (71) Applicant (for all designated States except US): QUAL-COMM Incorporated [US/US]; ATTN: International IP Administration, 5775 Morehouse Drive, San Diego, California 92121-1714 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): SIKRI, Divaydeep [IN/GB]; 5775 Morehouse Drive, San Diego, California 92121-1714 (US). ABRISHAMKAR, [US/US]; 5775 Morehouse Drive, San Diego, California 92121-1714 (US). **DE LAURENTIIS, Nico** [IT/GB]; Drive, San Diego, 5775 Morehouse California 92121-1714 (US).

- (74) Agent: VU, Kenneth K D; ATTN: International IP Administration, 5775 Morehouse Drive, San Diego, California 92121-1714 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Declarations under Rule 4.17:**

[Continued on next page]

(54) Title: HYBRID SAIC RECEIVER

(57) Abstract: Systems and methods of receiving data in a communication system are disclosed. The methods include equalizing a plurality of samples to suppress intersymbol interference and provide a first set of detected bits based on a first set of reference bits comprising a training sequence on a first iteration. The methods further include suppressing cochannel interference in the plurality of input samples and provide a set of suppressed samples based on a second set of reference bits comprising the first set of detected bits on a second iteration. The methods further include equalizing the set of suppressed samples to suppress intersymbol interference and provide a second set of detected bits based on the second set of reference bits on the second iteration.

WO 2010/127049 A2

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

## Published:

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

1

#### HYBRID SAIC RECEIVER

#### **BACKGROUND**

#### Field

[0001] The present invention relates to wireless communication and, in particular, relates to antenna interference cancellation.

#### **Background**

**[0002]** In a communication system, a transmitter processes data to generate a modulated signal and transmits the modulated signal on a frequency band/channel and via a communication channel to a receiver. The transmitted signal is distorted by the communication channel, corrupted by noise, and further degraded by co-channel interference, which is interference from other transmitters transmitting on the same frequency band/channel. The receiver receives the transmitted signal, processes the received signal, and attempts to recover the data sent by the transmitter. The distortion due to the communication channel, the noise, and the co-channel interference all hinder the receiver's ability to recover the transmitted data.

[0003] There is therefore a need in the art for a receiver that can effectively deal with co-channel interference and channel distortion.

#### **SUMMARY**

[0004] A receiver comprising a hybrid demodulator that can be configured as an interference suppression (IS) demodulator on a first iteration and as a SAIC demodulator on a subsequent iteration is disclosed. This hybrid configuration can be utilized when a measured signal level associated with a received signal is below a threshold level.

[0005] According to one aspect of the subject technology, a receiver in a wireless communication system comprises an interference suppressor configured to suppress cochannel interference. The receiver can further comprise an equalizer configured to suppress intersymbol interference. The receiver can further comprise a controller configured to: a) control the equalizer to suppress intersymbol interference in a plurality of input samples of a received signal and provide a first set of detected bits based on a first set of reference bits comprising a training sequence on a first iteration; b) control

WO 2010/127049

2

PCT/US2010/032858

the interference suppressor to suppress co-channel interference in the plurality of input samples and provide a set of suppressed samples based on a second set of reference bits comprising the first set of detected bits on a second iteration; and c) control the equalizer to suppress intersymbol interference in the set of suppressed samples of b) and provide a second set of detected bits based on the second set of reference bits on the second iteration.

[0006] According to another aspect of the subject technology, a method for processing input samples of a signal received in a wireless communication system comprises: a) equalizing a plurality of input samples to suppress intersymbol interference and provide a first set of detected bits based on a first set of reference bits comprising a training sequence on a first iteration; b) suppressing co-channel interference in the plurality of input samples and provide a set of suppressed samples based on a second set of reference bits comprising the first set of detected bits on a second iteration; and c) equalizing the set of suppressed samples of the step b) to suppress intersymbol interference and provide a second set of detected bits based on the second set of reference bits on the second iteration.

[0007] According to yet another aspect of the subject technology, a receiver comprises first interference suppressing means for suppressing co-channel interference. The receiver can further comprise second interference suppressing means for suppressing intersymbol interference. The receiver can further comprise controlling means for: a) controlling the second interference suppressing means to suppress intersymbol interference in a plurality of input samples of a received signal and provide a first set of detected bits based on a first set of reference bits comprising a training sequence on a first iteration; b) controlling the first interference suppressing means to suppress co-channel interference in the plurality of input samples and provide a set of suppressed samples based on a second set of reference bits comprising the first set of detected bits on a second iteration; and c) controlling the second interference suppressing means to suppress intersymbol interference in the set of suppressed samples of b) and provide a second set of detected bits based on the second set of reference bits on the second iteration.

[0008] According to yet another aspect of the subject technology, a machine-readable medium comprises instructions for processing input samples of a signal received in a wireless communication system. The instructions comprise code for: a) controlling the

second interference suppressing means to suppress intersymbol interference in a plurality of input samples of a received signal and provide a first set of detected bits based on a first set of reference bits comprising a training sequence on a first iteration; b) controlling the first interference suppressing means to suppress co-channel interference in the plurality of input samples and provide a set of suppressed samples based on a second set of reference bits comprising the first set of detected bits on a second iteration; and c) controlling the second interference suppressing means to suppress intersymbol interference in the set of suppressed samples of b) and provide a second set of detected bits based on the second set of reference bits on the second iteration.

[0009] It is understood that other configurations of the subject technology will become readily apparent to those skilled in the art from the following detailed description, wherein various configurations of the subject technology are shown and described by way of illustration. As will be realized, the subject technology is capable of other and different configurations and its several details are capable of modification in various other respects, all without departing from the scope of the subject technology. Accordingly, the drawings and detailed description are to be regarded as illustrative in nature and not as restrictive.

#### BRIEF DESCRIPTION OF THE DRAWINGS

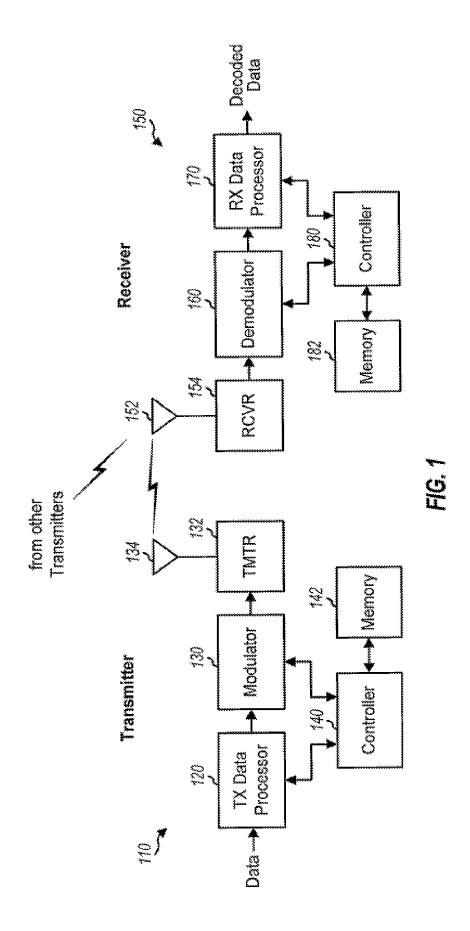

[0010] FIG. 1 is a block diagram of a transmitter and a receiver in a wireless communication system;

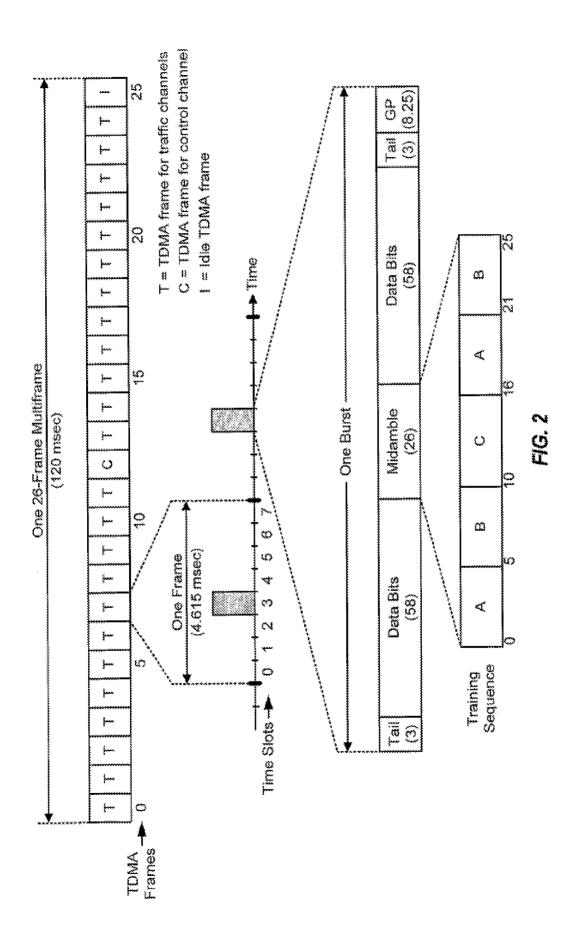

[0011] FIG. 2 is a diagram illustrating exemplary frame and burst formats in GSM in accordance with one aspect of the subject technology;

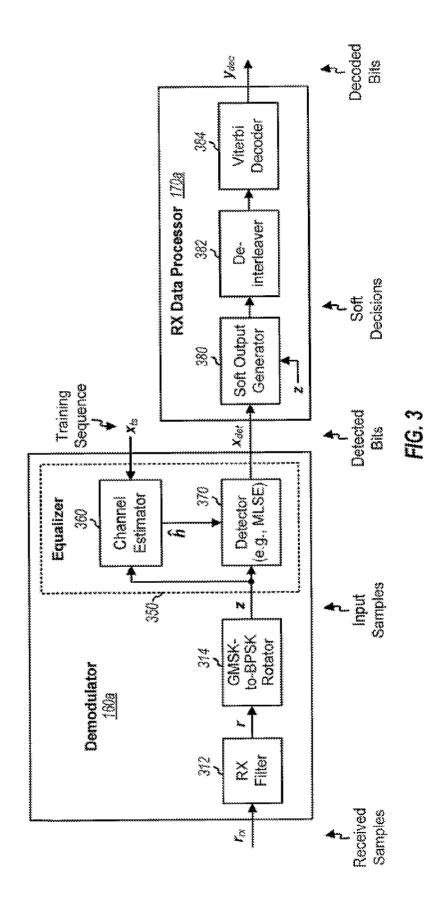

[0012] FIG. 3 is a block diagram of a receiver comprising a demodulator and a receive (RX) data processor for GSM;

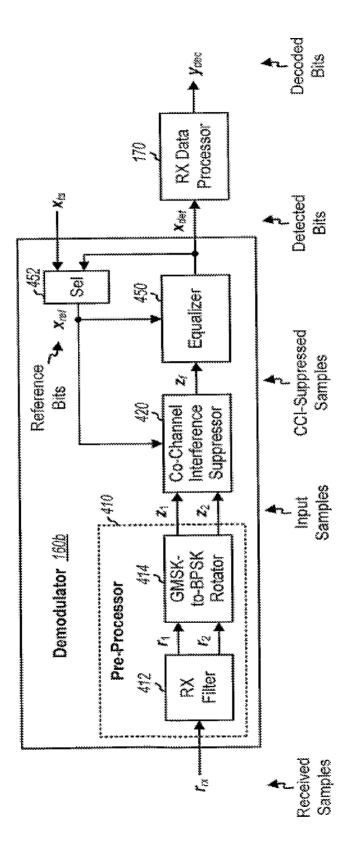

[0013] FIG. 4 is a block diagram of a receiver comprising a SAIC demodulator configured to perform detection with an interference suppression for use in a wireless communication system;

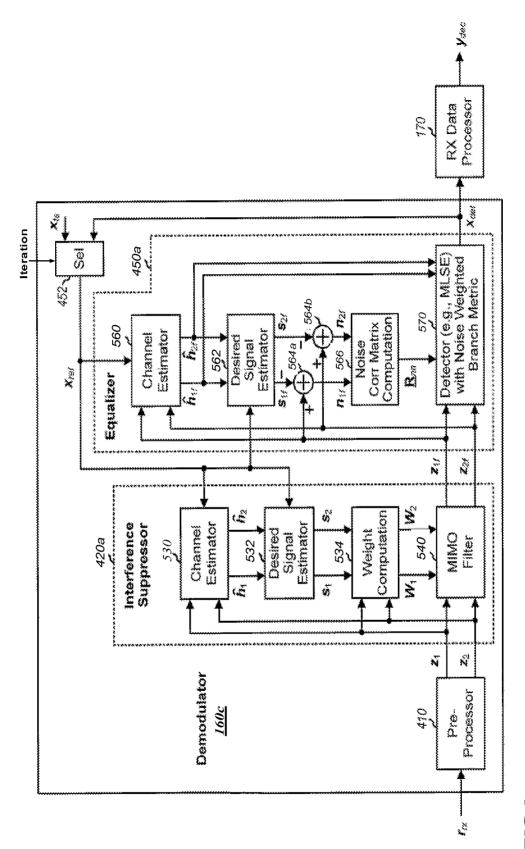

[0014] FIG. 5 is a block diagram of a receiver comprising a SAIC demodulator configured to perform detection with an interference suppression and noise decorrelation for use in a wireless communication system;

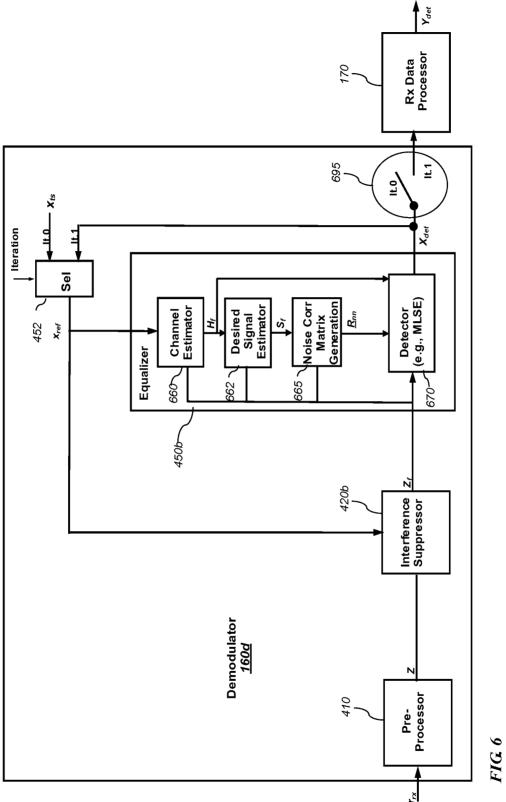

[0015] FIG. 6 is a block diagram of a receiver comprising a SAIC demodulator that is substantially similar to the receiver shown in FIG. 5;

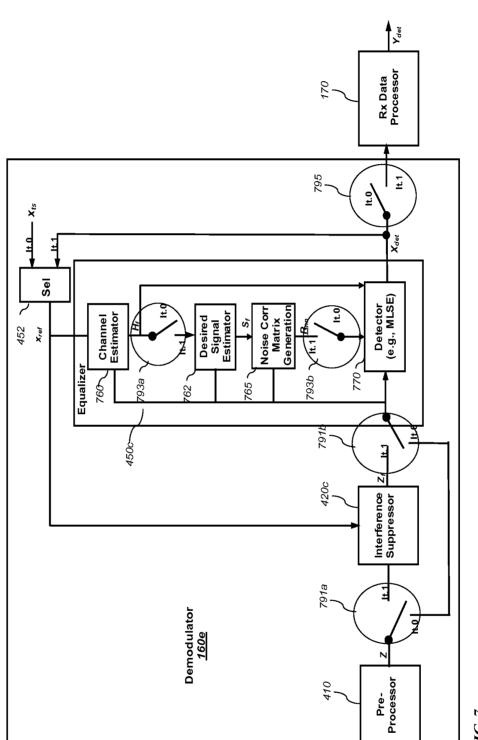

[0016] FIG. 7 is a block diagram illustrating a receiver comprising an exemplary hybrid SAIC demodulator in accordance with one aspect of the subject technology;

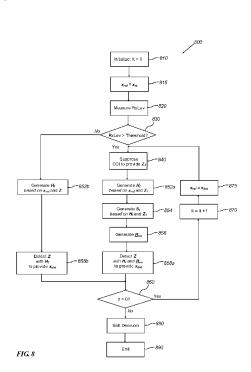

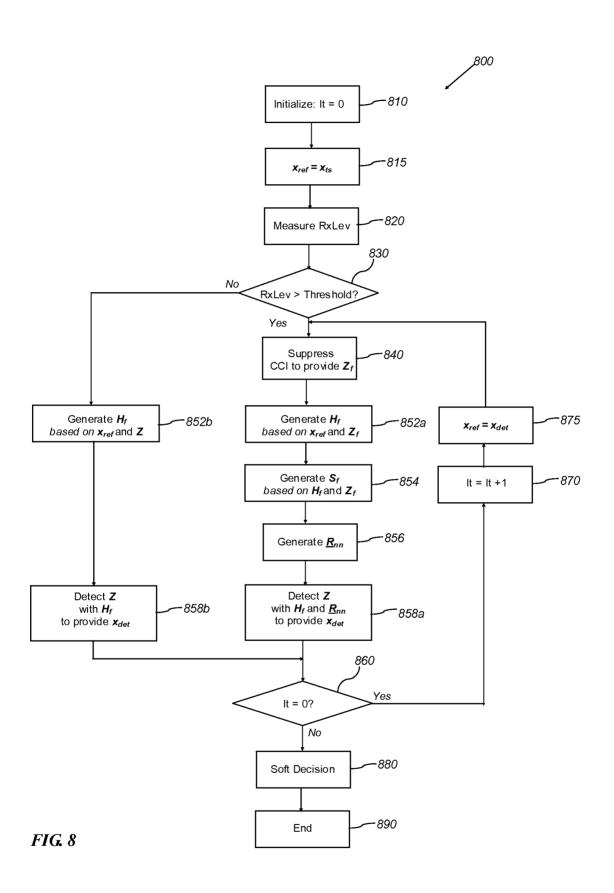

[0017] FIG. 8 is a flow diagram illustrating an exemplary process 800 for operation of a hybrid demodulator in accordance with one aspect of the subject technology;

[0018] FIG. 9 is a block diagram illustrating a computer system with which certain aspects of the subject technology may be implemented.

#### **DETAILED DESCRIPTION**

[0019] A receiver comprising a hybrid demodulator that can be configured as an IS demodulator on a first iteration and as a SAIC demodulator on a subsequent iteration is disclosed. For clarity, various aspects of a receiver are specifically described below for Global System for Mobile Communications (GSM) technology. FIG. 1 shows a block diagram of a transmitter 110 and a receiver 150 in a wireless communication system. The transmitter 110 may be a base station or a wireless device, and the receiver 150 may also be a wireless device or a base station. At the transmitter 110, a transmit (TX) data processor 120 receives, formats, encodes, and interleaves data based on a coding and interleaving scheme and provides a stream of input bits to a modulator 130. For GSM, the modulator 130 performs GMSK modulation on the input bits and provides a GMSK modulated signal (or simply, a GMSK signal). GMSK is a continuous phase modulation scheme used in GSM and is described below. A transmitter unit (TMTR) 132 conditions (e.g., filters and amplifies) the GMSK signal and generates a radio frequency (RF) modulated signal, which is transmitted via an antenna 134 to receiver 150.

**[0020]** In one aspect, to generate a GMSK signal, the modulator 130 receives input bits  $\underline{a}$  from the TX data processor 120 and performs differential encoding on the inputs bits to generate code symbols c. On new code symbol is generated for each new input bit. Each input bit and each code symbol have a real value either +1 or -1. The modulator 130 further filters each code symbol with a Gaussian lowpass filter to generate a frequency pulse having a duration of approximately four sample periods (4T). The modulator 130 integrates the frequency pulses for the code symbols to generate a

modulating signal and further modulates a carrier signal with the modulating signal to generate the GMSK signal.

[0021] At the receiver 150, an antenna 152 receives the RF modulated signal from the transmitter 110 and RF modulated signals from other transmitters in the GSM system. The antenna 152 provides a received GMSK signal to a receiver unit (RCVR) 154. The receiver unit 154 conditions and digitizes the received GMSK signal and provides received samples. A demodulator 160 processes the received samples and provides detected bits, as described below. An RX data processor 170 processes (e.g., deinterleaves and decodes) the detected bits and recovers the data sent by transmitter 110. The processing by the demodulator 160 and the RX data processor 170 can be complementary to the processing by modulator 130 and TX data processor 120, respectively, at the transmitter 110.

[0022] Controllers 140 and 180 direct operation at transmitter 110 and receiver 150, respectively. Memory units 142 and 182 provide storage for program codes and data used by controllers 140 and 180, respectively.

[0023] FIG. 2 shows exemplary frame and burst formats in GSM. The timeline for downlink transmission is divided into multiframes. For traffic channels used to send user-specific data, each multiframe, such as exemplary multiframe 201, includes 26 TDMA frames, which are labeled as TDMA frames 0 through 25. The traffic channels are sent in TDMA frames 0 through 11 and TDMA frames 13 through 24 of each multiframe, as identified by the letter "T" in FIG. 2. A control channel, identified by the letter "C," is sent in TDMA frame 12. No data is sent in the idle TDMA frame 25 (identified by the letter "I"), which may be used by the wireless devices to make measurements for neighbor base stations.

[0024] Each TDMA frame, such as exemplary TDMA frame 202, is further partitioned into eight time slots, which are labeled as time slots 0 through 7. Each active wireless device/user is assigned one time slot index for the duration of a call. User-specific data for each wireless device is sent in the time slot assigned to that wireless device and in TDMA frames used for the traffic channels.

[0025] The transmission in each time slot is called a "burst" in GSM. Each burst, such as exemplary burst 203, includes two tail fields, two data fields, a training sequence (or midamble) field, and a guard period (GP). The number of bits in each field is shown inside the parentheses. GSM defines eight different training sequences that may be sent

in the training sequence field. Each training sequence, such as midamble 204, contains 26 bits and is defined such that the first five bits are repeated and the second five bits are also repeated. Each training sequence is also defined such that the correlation of that sequence with a 16-bit truncated version of that sequence is equal to (a) sixteen for a time shift of zero, (b) zero for time shifts of  $\pm 1$ ,  $\pm 2$ ,  $\pm 3$ ,  $\pm 4$ , and  $\pm 5$ , and (3) a zero or non-zero value for all other time shifts.

[0026] One approach to locating a midamble in a burst of symbols serially compares hypotheses regarding the midamble position to determine which hypothesis provides the highest correlation energy between the known midamble sequence and the hypothesized position in the burst of symbols. This method is very sensitive to interference from multi-paths of the same midamble sequence, which can cause the correlation energy of inaccurate hypotheses to be affected by time-delayed copies thereof.

[0027] FIG. 3 shows a demodulator 160a and an RX data processor 170a at the receiver 150 shown in FIG. 1. Within the demodulator 160a, an RX filter 312 filters the received samples  $r_{rx}$  from receiver unit 154 and provides intermediate samples  $r_{rx}$ .

[0028] A GMSK-to-BPSK rotator 314 performs phase rotation on the intermediate samples r and provides input samples z. For example, the rotator 314 can rotate the intermediate samples by successively more negative phases, or  $0^{\circ}$  for r(t), then -90° for r(t+1), then -180° for r(t+2), then -270° for r(t+3), then  $0^{\circ}$  for r(t+4), and so on.

[0029] An equalizer 350 performs equalization on the input samples z to remove intersymbol interference caused by multipath in the wireless channel. For the design shown in FIG. 3, the equalizer 350 includes a channel estimator 360 and a detector 370. The channel estimator 360 receives the input samples z and a training sequence  $x_{ts}$  and derives an estimate of the effective channel impulse response  $\hat{h}$ .

[0030] The detector 370 receives the input samples z and the channel estimate  $\hat{h}$  and performs detection to recover input bits a. The detector 370 may implement a maximum likelihood sequence estimator (MLSE) that determines a sequence of bits that is most likely to have been transmitted given the input sample sequence z and the channel estimate  $\hat{h}$ . The MLSE can use a Viterbi algorithm with  $2^{L-1}$  states, where L is the length of the channel estimate  $\hat{h}$ . Detection with MLSE for GSM is well known in the art and not described in detail herein. The detector 370 provides detected bits  $x_{det}$ , which are hard decision estimates of the input bits a sent by the transmitter 110.

[0031] Within the RX data processor 170a, a soft output generator 380 receives the detected bits  $x_{det}$  and the input samples z and generates soft decisions that indicate the confidence in the detected bits. The soft output generator 380 may implement an Ono algorithm that is well known in the art. A de-interleaver 382 de-interleaves the soft decisions in a manner complementary to the interleaving performed by the transmitter 110. A Viterbi decoder 384 decodes the deinterleaved soft decisions and provides decoded data  $y_{dec}$ , which is an estimate of the traffic data provided to the TX data processor 120 at the transmitter 110.

[0032] FIG. 4 is a block diagram of an exemplary single antenna interference cancellation (SAIC) demodulator 160b configured to perform detection with interference suppression for use in a wireless communication system. The receiver unit 154 (FIG. 1) may digitize the received GMSK signal at twice the sample rate and provide 2x oversampled received samples  $r_{lx}$ . Within a pre-processor 410, an RX filter 412 filters the received samples and provides a sequence of "early" samples  $r_l$  and a sequence of "late" samples  $r_2$ . The RX filter 412 may be a poly-phase filter. A GMSK-to-BPSK rotator 414 performs phase rotation on each sequence of intermediate samples,  $r_m$  for m=1, 2, and provides a corresponding sequence of input samples  $\mathbb{Z}_m$ .

[0033] An interference suppressor 420 receives the two input sample sequences  $z_i$  and  $z_2$ , suppresses co-channel interference from the undesired transmitter(s), and provides sequences of CCI-suppressed samples  $z_{if}$  and  $z_{2f}$ . An equalizer 450 performs equalization on the CCI-suppressed samples  $z_{if}$  and  $z_{2f}$  to suppress intersymbol interference and provides detected bits  $x_{det}$ . The interference suppressor 420 and the equalizer 450 may be implemented in various manners, and several exemplary designs are described below.

[0034] The demodulator 160b may perform co-channel interference suppression and equalization for a single iteration or for multiple iterations to improve performance. Each iteration of the co-channel interference suppression and equalization is called an outer iteration. A selector (SEL) 452 receives the training sequence  $x_{ts}$  and the detected bits  $x_{det}$  and provides reference bits  $x_{ref}$  for the interference suppressor 420 and the equalizer 450. In general, the selector 452 may provide the same reference bits to both the interference suppressor 420 and the equalizer 450 (as shown in FIG. 4) or different reference bits to the interference suppressor 420 and the equalizer 450 (not shown in FIG. 4).

[0035] FIG. 5 is a block diagram of an exemplary SAIC demodulator 160c configured to perform detection with interference suppression and noise decorrelation for use in a wireless communication system. The exemplary SAIC demodulator 160c shown in FIG. 5, in addition to being configured to suppress co-channel interference, is also configured to perform detection with noise decorrelation. Within the demodulator 160c, a pre-processor 410 processes the received samples  $z_{rx}$  and provides two sequences of complex-valued input samples  $z_1$  and  $z_2$ . The demodulator 160c includes an interference suppressor 420a and an equalizer 450a.

[0036] The interference suppressor 420a is configured to suppress co-channel interference and provides two sequences of CCI-suppressed samples  $z_{If}$  and  $z_{2f}$ . The interference suppressor 420a includes a channel estimator 530, a desired signal estimator 532, a weight computation unit 534, and a multiple-in multiple-out (MIMO) filter 540. The channel estimator 530 may implement a least-squares (LS) estimator, a linear minimum mean square error (LMMSE), an adaptive filter, or some other type of estimator. The interference suppressor 420a may perform channel estimation and MIMO filtering for a single iteration or for multiple iterations to improve performance. The equalizer 450a includes a channel estimator 560, a desired signal estimator 562, a pair of summers 564a, 564b, a noise correlation matrix computation unit 566, and a detector 570 (e.g., an MLSE).

[0037] Operation of the exemplary SAIC demodulator 160c is now described. The following description is a summary of a more detailed description of operation of a SAIC demodulator provided in provided in U.S. Patent Application No. 11/122,654, titled "Interference Suppression With Virtual Antennas", which is incorporated herein by reference in its entirety. The channel estimator 530 receives one or more sequences of complex-valued input sample sequences (e.g., the first sequence  $z_1$  and the second sequence  $z_s$ ) from the pre-processor 410 and the reference bits  $x_{ref}$  from the selector 452 and derives effective channel impulse response estimates (e.g.,  $\hat{h}_I$  for  $z_1$  and  $\hat{h}_2$  for  $z_2$ ). The channel estimator 530 may implement a least-squares (LS) estimator, a linear minimum mean square error (LMMSE), an adaptive filter, or some other type of estimator. The desired signal estimator 532 receives the reference bits  $x_{ref}$  and the effective channel response estimates  $\hat{h}_I$  and  $\hat{h}_2$  for the first and second sequences  $z_I$  and  $z_2$  and derives a desired signal estimate  $s_I$  and  $s_2$  based on  $s_{ref}$  and  $s_2$ . The weight

computation unit 534 receives the input sample sequences  $z_1$  and  $z_2$  and the desired signal estimates  $s_1$  and  $s_2$  generates weights  $W_1$  and  $W_2$  for the MIMO filter 540.

[0038] The MIMO filter 540 may include two separate filters which are referred to as first and second MIMO filters. The first MIMO filter filters the input sample sequences  $z_1$  and  $z_2$  with the weights  $W_1$  and provides a first CCI-suppressed sample sequence  $z_{1f}$ . The second MIMO filter filters the input sample sequences  $z_1$  and  $z_2$  with the weights  $W_2$  and provides a second CCI-suppressed sample sequence  $z_{2f}$ . The first and second MIMO filters operate independently of one another. The weight computation unit 534 derives the weights  $W_1$  such that the mean square error between the CCI-suppressed samples  $z_{1f}$  and the desired signal estimate  $s_1$  is minimized. The weight computation unit 534 derives the weights  $W_2$  such that the mean square error between the CCI-suppressed samples  $z_{2f}$  and the desired signal estimate  $s_2$  is minimized.

[0039] Turning now to the equalizer 450a, the channel estimator 560 receives the two CCI-suppressed sample sequences  $z_{lf}$  and  $z_{2f}$  provided by the interference suppressor 420a and the reference bits  $x_{ref}$  provided by the selector 452 and derives improved effective channel impulse response estimates  $\hat{h}_{lf}$  and  $\hat{h}_{2f}$  for sequences  $z_{lf}$  and  $z_{2f}$ , respectively. In one aspect, the selector 452 provides a training sequence  $(x_{ts})$ , (e.g., the midamble 204 shown in FIG. 2) on a first iteration (e.g., It.0) and a combination of the hard decision (e.g.,  $x_{det}$ ) and the training sequence on a subsequent iteration (e.g., It.1). In one embodiment, the combination is represented by:  $x_{ref} = [x_{det}(1) x_{det}(2) \dots x_{det}(58) x_{ts}(1) x_{ts}(2) \dots x_{ts}(26) x_{det}(59) x_{det}(60) \dots x_{det}(116)]$ . That is, the reference bits are arranged in temporal order, with the training sequence in the middle. The channel estimates  $\hat{h}_{lf}$  and  $\hat{h}_{2f}$  are typically of higher quality than the channel estimates  $\hat{h}_{l}$  and  $\hat{h}_{2f}$  used to derive the channel estimates  $\hat{h}_{lf}$  and  $\hat{h}_{2f}$ .

[0040] The desired signal estimator 562 receives the reference bits  $\mathbf{x}_{ref}$  and the improved channel estimates  $\hat{\mathbf{h}}_{lf}$  and  $\hat{\mathbf{h}}_{2f}$ , derives a desired signal estimate  $\mathbf{s}_{lf}$  based on  $\mathbf{x}_{ref}$  and  $\hat{\mathbf{h}}_{lf}$ , derives a desired signal estimate  $\mathbf{s}_{2f}$  based on  $\mathbf{x}_{ref}$  and  $\hat{\mathbf{h}}_{2f}$ , and provides the two desired signal estimates  $\mathbf{s}_{lf}$  and  $\mathbf{s}_{lf}$  are typically of higher quality than the desired signal estimates  $\mathbf{s}_{l}$  and  $\mathbf{s}_{l}$  because of the improved channel estimates  $\hat{\mathbf{h}}_{lf}$  and  $\hat{\mathbf{h}}_{2f}$  used to derive the desired signal estimates  $\mathbf{s}_{lf}$  and  $\mathbf{s}_{2f}$ .

[0041] The summer 564a subtracts the desired signal estimate  $s_{lf}$  from the CCI-suppressed samples  $z_{lf}$  and provides a noise estimate  $n_{lf}$ . The summer 564b subtracts

PCT/US2010/032858

the desired signal estimate  $s_{2f}$  from the CCI- suppressed samples  $z_{2f}$  and provides a noise estimate  $n_{2f}$ . The computation unit 566 computes a 4x4 noise correlation matrix  $\underline{R}_{nn}$  based on the real and imaginary parts of the noise samples in  $n_{1f}$  and  $n_{2f}$ .

[0042] The detector 570 receives the CCI-suppressed sample sequences  $z_{lf}$  and  $z_{2f}$ , the improved channel estimates  $\hat{h}_{lf}$  and  $\hat{h}_{2f}$ , and the noise correlation matrix  $\underline{R}_{nn}$ . The detector 570 can perform detection based on the inputs and provides the detected bits  $x_{det}$  that are deemed most likely to have been transmitted based on the branch metrics. In certain embodiment, the detector 570 is implemented with an MLSE. In other embodiments, the detector 570 may be implemented with other types of equalizers such as a decision feedback equalizer (DFE).

[0043] For the exemplary receiver shown in FIG. 5, a new channel estimate and a new desired signal estimate are derived for each outer iteration. In general, new or prior channel estimates may be used for each inner and outer iteration, and new or prior desired signal estimates may be used for each inner and outer iteration. For example, the channel estimates  $\hat{h}_1$  and  $\hat{h}_2$  may be derived once based on the training sequence and used for all outer iterations.

[0044] FIG. 6 is a block diagram of an exemplary SAIC demodulator 160d that is substantially similar to the SAIC demodulator 160c of FIG. 5. The SAIC demodulator 160d is shown to include a pre-processor 410, an interference suppressor 420b, an equalizer 450b, a selector 452, and a switch 695. The SAIC demodulator 160d illustrated in FIG. 6 is substantially similar to the SAIC demodulator 160c illustrated in FIG. 5, except that the constituent components (e.g., a channel estimator, a desired signal estimator, a weight computation unit, and a MIMO filter) of the interference suppressor 420b are not shown; and some constituent components of the equalizer 450b are regrouped for simplicity and ease of illustration. For example, the equalizer 450b of FIG. 6 is shown to include a channel estimator 660, a desired signal generator 662, a noise correlation matrix generation module 665, and a detector 670. correlation matrix generation module 665 can include a pair of summers and a noise correlation matrix computation unit such as the elements 564a, 564b, 566 shown in FIG. 5. The switch 695 is included in FIG. 6 to indicate that the detection processing is not conclusive after the first iteration, and that only after the second iteration, the detected bits move forward to the RX data processor 170. For example, in an embodiment in which no actual physical switch is used, a software subroutine associated with the

detection processing does not make data representative of the detected bits to another subroutine associated with the RX data processing until after the second iteration is completed.

[0045], Additionally, it shall be appreciated that symbols such as Z,  $Z_f$  H, and S can include one or more data sequences. For example, a single line connecting the preprocessor 410 and the interference suppressor 420b can indicate a single line carrying a single sequence of input samples (e.g.,  $z_I$ ) or multiple (e.g., two) lines carrying multiple sequences of input samples (e.g.,  $z_I$  and  $z_I$ ). Similarly,  $z_I$  can denote  $z_I$  or  $z_I$  and  $z_I$ , and  $z_I$  and  $z_I$

[0046] Operation of the SAIC demodulator 160d is substantially the same as the operation of the SAIC demodulator 160c described above with respect to FIG. 5. An interference suppressor 420b suppresses interference (e.g., co-channel interference) using a training sequence  $(x_{ts})$ , (e.g., a midamble portion of the burst) on a first iteration (e.g., It.0) and a hard decision (e.g.,  $x_{det}$ ) from a detector (e.g., MLSE) on a subsequent iteration (e.g., It.1). Under a fair signal-to-noise ratio (SNR) condition (e.g., while the signal strength is substantially equal to or greater than the background white noise), a SAIC demodulator such as the one illustrated by FIGs. 5 and 6 offers advantages over a non-SAIC demodulator such as the one illustrated by FIG. 3 However, under a poor SNR condition (e.g., while the signal strength is sufficiently less than the background white noise), the SAIC demodulator becomes ineffective as compared to the non-SAIC demodulation scheme because midamble length is not sufficient for training and does not provide sufficient noise smoothening. Therefore, under a poor SNR condition, the non-SAIC demodulation receiver (e.g., without the co-channel interference suppression and the noise correlation matrix provided by the elements 420b, 661, and 665) can provide a better detection performance than the SAIC demodulation receiver.

[0047] For improved detection performance, a hybrid SAIC demodulator is implemented wherein the demodulator is configured as a non-SAIC demodulator such as the one shown in FIG. 3 on a first iteration (e.g., It.0) and as a SAIC demodulator such as the one shown in FIGs. 5 and 6 on a subsequent iteration (e.g., It.1) under a poor SNR condition. FIG. 7 is a block diagram illustrating a receiver comprising an exemplary hybrid SAIC demodulator 160e in accordance with one aspect of the subject technology. The architecture of the hybrid demodulator 160e is substantially similar to the architecture of the SAIC demodulator 160d illustrated in FIG. 6, with the key

differences being that the hybrid SAIC demodulator 160e additionally includes: a pair of bypass switches 791a,b configured to bypass or skip an interference suppressor 420c; and a pair of bypass switches 793a,b configured to bypass or skip a desired signal generator 762 and a noise matrix generation module 765 within the equalizer 450c. It shall be appreciated by one skilled in the art in view of the present disclosure that the switches 791a,b, 793a,b, and 795 shown in FIG. 7 can be implemented by hardware, software, or firmware.

[0048] In a first configuration corresponding to the first iteration (It.0), the pairs of bypass switches 791a,b and 793a,b are in first positions such that: 1) the co-channel interference suppressor 420c is bypassed or skipped, and sequences of input samples (e.g.,  $z_I$  and  $z_2$ ) flow from the pre-processor 410 to the detector (e.g., MLSE); and 2) the desired signal estimator 762 and the noise correlation matrix generation module 765 are bypassed or skipped. The channel estimator 760 receives a first set of reference bits  $(x_{ref})$  comprising a training sequence  $(x_{ts})$  and derives a first set of one or more channel estimates (e.g.,  $\hat{h}_{If}$  and  $\hat{h}_{2f}$ ). The detector 770 performs detection on Z, the sequences of input samples (e.g.,  $z_I$  and  $z_I$ ), with  $z_I$ , the set of one or more channel estimates, to provide a set of detected bits  $z_I$ . In this configuration, the hybrid SAIC demodulator 160e behaves substantially like a non-SAIC demodulator, such as the demodulator 160a illustrated in FIG. 3.

[0049] In a second configuration corresponding to a second iteration (It.1), for example, the pairs of bypass switches 791a,b and 793a,b are in second positions such that the hybrid demodulator 160e is configured as, and behaves like, a SAIC demodulator, such as the SAIC demodulator 160d illustrated in FIG. 6. The co-channel interference suppressor 420c performs interference suppression on Z, the sequences of input samples (e.g.,  $z_I$  and  $z_2$ ), using a second set of reference bits comprising the detected bits ( $x_{det}$ ) obtained from the first iteration described above to provide  $Z_6$  a set of suppressed samples (e.g.,  $z_{If}$  and  $z_{2f}$ ). Within the equalizer 450c, the channel estimator 760 receives a second set of reference bits comprising the detected bits ( $x_{det}$ ) obtained from the first iteration described above and derives a second set of one or more channel estimates (e.g.,  $\hat{h}_{If}$  and  $\hat{h}_{2f}$ ). A desired signal estimator 762 receives the second set of one or more channel estimates and derives  $S_6$  a set of one or more desired signal estimates (e.g.,  $s_{If}$  and  $s_{2f}$ ). A noise correlation matrix generation module 765 receives the set of one or more desired signal estimates and computes  $\underline{R}_{nn}$ , a noise correlation matrix. The

detector 770 performs detection on Z, the sequences of input samples (e.g.,  $z_I$  and  $z_2$ ) with  $H_f$ , the set of one or more channel estimates, to provide a set of detected bits ( $x_{det}$ ). [0050] In one aspect, the hybrid SAIC demodulator 160e can be configured as a non-SAIC demodulator (e.g., the demodulator 160a of FIG. 3) on a first iteration and a SAIC demodulators (e.g., the demodulator 160d of FIG. 6) on a subsequent iteration as described above under a poor SNR condition, e.g., when the background white noise is dominant as compared to a signal strength. When the SNR condition improves (e.g., the signal strength is dominant as compared to the white noise), the hybrid demodulator 160e can be configured as a SAIC demodulator (e.g., the demodulator 160d) on all iteration levels including the first iteration.

[0051] FIG. 8 is a flow diagram illustrating an exemplary process 800 for operation of a hybrid demodulator in accordance with one aspect of the subject technology. For clarity, the process 800 is described with references to labeled components of the hybrid SAIC demodulator 160e as shown in FIG. 7. However, one skilled in the art would understand in view of the present disclosure that the methodology of the process 800 is not so limited and is applicable to different SAIC demodulator configurations known in the art. The process 800 begins at a state 800, in which an iteration variable (It) is initialized to 0. The process 800 proceeds to a state 815, in which the reference bits  $(x_{ref})$  are assigned to a training sequence  $(x_{ts})$ , e.g., by the selector 452, to provide a first set of reference bits comprising the training sequence. The process 800 proceeds to a state 820, in which a received signal strength or level (RxLev) is measured. By way of example, RxLev, given by  $\frac{1}{G} \square \frac{1}{N}$ , can be computed as follows: The received samples are squared and added to compute the signal energy at the equalizer input. Division by N gives the signal power at the input of the equalizer. The power is divided by the gain G of the receiver chain to translate it into the received power at the antenna. The process 800 proceeds to a decision state 830, in which a query is made as to whether the measured RxLev is larger than a threshold level.

[0052] The threshold level can be determined at the product design stage for the receiver based on various factors including an experimentally or theoretically determined background white noise level inherent to the receiver design. For example, suppose that the background white noise level is -100dbm for a particular receiver design. Subsequently, a determination can be made as to at what signal power level below the background white noise level (e.g., -100dbm) the performance advantage of

the SAIC detection is lost and the non-SAIC detection is favorable to the SAIC detection. This determination can be made experimentally or theoretically. For example, if is determined that the performance advantage of the SAIC detection as compared to the non-SAIC detection is lost at 5dbm below the background white noise level of -100dbm, the threshold is set at -95dbm.

#### RxLev > Threshold

[0053] Returning to the process 800 (FIG. 8), if the answer to the query at the decision state 830 is Yes (indicating, e.g., a fair SNR condition), the remainder of the operation 800 of the hybrid demodulator substantially tracks that of a SAIC demodulator, such as the demodulator 160d of FIG. 6. For example, the process 800 proceeds to a state 840, in which co-channel interference in a plurality of input samples (Z) is suppressed, e.g., by the interference suppressor 420c, to provide a set of suppressed samples  $(Z_t)$  based on the first set of reference bits assigned at the state 815. The process 800 proceeds to a state 852a, in which a set of one or more channel estimates ( $H_{d}$ ) is derived, e.g., by the channel estimator 760, based on the first set of reference bits comprising the training sequence assigned at the state 815 and the set of suppressed samples provided at the state 840. The process 800 proceeds to a state 854, in which a set of one or more desired signal estimates (S<sub>t</sub>) is derived, e.g., by the desired signal estimator 762, based on the set of suppressed samples provided at the state 840 and the set of one or more channel estimates derived at the state 852a. The process 800 proceeds to a state 854, in which a noise correlation matrix  $(\underline{R}_{nn})$  is computed, e.g., by the noise correlation matrix generation module 765, based on the set of suppressed samples provided at the state 840 and the set of one or more desired signal estimates derived at the state 854. The process 800 proceeds to a state 858a, in which the detector 770 detects the set of suppressed samples based on the set of one or more channel estimates derived at the state 852a to provide a first set of detected bits.

[0054] The process 800 then proceeds to a decision state 860, in which a query is made as to whether the iteration variable (It) is 0. At this stage, the query condition is satisfied because It=0, and the process 800 proceeds to a state 870, where the iteration variable (It) is incremented from 0 to 1. The process 800 begins its second iteration (It=0) stage by proceeding to a state 875, in which the reference bits ( $x_{ref}$ ) are assigned to the first set of detected bits obtained on the first iteration at the state 858a to provide a second set of reference bits comprising the first set of detected bits. The process 800

then loops back to the state 840, and the steps 840-858a described above are repeated, with a notable difference this time being that: 1) a second set of channel estimates ( $H_t$ ) is derived based on the second set of reference bits comprising the first set of detected bits obtained on the first iteration (It=0) as opposed to the first set of reference bits comprising the training sequence; and 2) a second set of detected bits is obtained at the state 858a based on the second set of channel estimates. After the second set of detected bits is obtained, the process proceeds to the decision state 860 again. This time, the query condition (It=0?) is no longer satisfied, and the process 800 ends the demodulation and proceeds to a state 880, in which a soft decision is performed on the second set of detected bits, e.g., by the Rx data processor 170 to provide  $y_{det}$ . The process 800 ends at state 890.

## $RxLev \leq Threshold$

[0055] On the other hand, if the answer to the query at the decision state 830 is No (indicating, e.g., a poor SNR condition), the operation of the hybrid demodulator takes on its "hybrid" nature. For example, on a first iteration (e.g., It=0), the operation of the hybrid demodulator substantially tracks that of a non-SAIC demodulator, such as the demodulators 160a of FIG. 3; on a subsequent iteration (e.g., It=1), the operation substantially tracks that of a SAIC demodulator such as the demodulator 160d of FIG. 6. As way of illustration, on the first iteration (It=0), the process 800 bypasses the cochannel interference suppression and proceeds to a state 852b, in which a set of one or more channel estimates  $(H_f)$  is derived, e.g., by the channel estimator 760, based on the first set of reference bits comprising the training sequence assigned at the state 815 and the plurality of input samples (as opposed to the set of suppressed samples if RxLev>Threshold). The process 800 bypasses the desired signal estimation and the noise correlation matrix generation and proceeds to a state 858b, in which the detector 770 detects the plurality of input samples (as opposed to the set of suppressed samples if RxLev>Threshold) based on the set of one or more channel estimates derived at the state 852b to provide a first set of detected bits.

[0056] The process 800 then proceeds to the decision state 860, in which a query is made as to whether the iteration variable (It) is 0. At this stage, the query condition is satisfied because It=0, and the process 800 proceeds to a state 870, where the iteration variable (It) is incremented from 0 to 1. The process 800 then begins its second

iteration stage by proceeding to a state 875, in which the reference bits  $(x_{ref})$  are assigned to the first set of detected bits obtained on the first iteration at the state 858b to provide a second set of reference bits comprising the first set of detected bits. The process 800 then proceeds to a state 840, in which co-channel interference in the plurality of input samples (Z) is suppressed, e.g., by the interference suppressor 420c, to provide a set of suppressed samples  $(Z_f)$  based on the second set of reference bits comprising the first set of detected bits obtained at the state 858b. The process 800 proceeds to a state 852a, in which a set of one or more channel estimates  $(H_t)$  is derived, e.g., by the channel estimator 760, based on the second set of reference bits comprising the first set of detected bits assigned at the state 875 and the set of suppressed samples provided at the state 840. The process 800 proceeds to a state 854, in which a set of one or more desired signal estimates ( $S_t$ ) is derived, e.g., by the desired signal estimator 762, based on the set of suppressed samples provided at the state 840 and the set of one or more channel estimates derived at the state 852a. The process 800 proceeds to a state 854, in which a noise correlation matrix ( $\underline{R}_{nn}$ ) is computed, e.g., by the noise correlation matrix generation module 765, based on the set of suppressed samples provided at the state 840 and the set of one or more desired signal estimates derived at the state 854. The process 800 proceeds to a state 858a, in which the detector 770 detects the set of suppressed samples based on the set of one or more channel estimates derived at the state 852a to provide a second set of detected bits.

[0057] After the second set of detected bits is obtained at the state 858a, the process proceeds to the decision state 860 again. This time, the query condition (It=0?) is no longer satisfied, and the process 800 ends the demodulation and proceeds to a state 880, in which a soft decision is performed on the second set of detected bits, e.g., by the Rx data processor 170 to provide  $y_{det}$ . The process 800 ends at state 890.

**[0058]** It shall be appreciated that the process 800 described above is for illustration purpose only, and a multitude of variations can be made to the described process without departing from the scope of the present disclosure. For example, in one variation, instead of ending the demodulation after the second iteration, the demodulation steps of the states 840-858a can be repeated for additional  $It_{ps} - 2$  times, where  $It_{ps}$  denotes a preset upper limit on the number of iterations, or until another preestablished condition is satisfied (e.g., when the SNR does not improve any further) before proceeding to the soft decision at the state 880. In another variation, the state

815 can be performed at any point between the state 820 and the state 840 or the state 852b. In yet another variation, the set of reference bits used for suppressing co-channel interference at the state 840 can be different from the set of reference bits used for generating the set of one or more channel estimates at the state 852a. In yet another variation, the hybrid demodulator may not generate the  $\underline{R}_{nn}$  matrix to perform the noise decorrelation, in which case the states 854 and 856 may not be present.

17

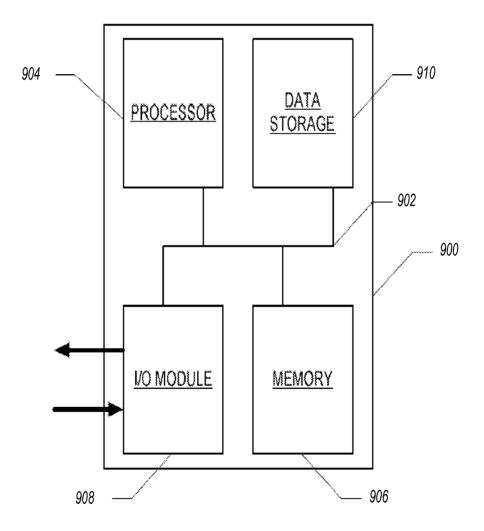

[0059] FIG. 9 is a block diagram that illustrates a computer system 900 upon which an aspect may be implemented. Computer system 900 includes a bus 902 or other communication mechanism for communicating information, and a processor 904 coupled with bus 902 for processing information. Computer system 900 also includes a memory 906, such as a random access memory ("RAM") or other dynamic storage device, coupled to bus 902 for storing information and instructions to be executed by processor 904. Memory 906 may also be used for storing temporary variable or other intermediate information during execution of instructions to be executed by processor 904. Computer system 900 further includes a data storage device 910, such as a magnetic disk or optical disk, coupled to bus 902 for storing information and instructions.

**[0060]** Computer system 900 may be coupled via I/O module 908 to a display device (not illustrated), such as a cathode ray tube ("CRT") or liquid crystal display ("LCD") for displaying information to a computer user. An input device, such as, for example, a keyboard or a mouse may also be coupled to computer system 900 via I/O module 908 for communicating information and command selections to processor 904.

[0061] According to one aspect, various functions of a hybrid SAIC demodulator described herein are performed by a computer system 900 in response to processor 904 executing one or more sequences of one or more instructions contained in memory 906. Such instructions may be read into memory 906 from another machine-readable medium, such as data storage device 910. Execution of the sequences of instructions contained in main memory 906 causes processor 904 to perform the process steps described herein. One or more processors in a multi-processing arrangement may also be employed to execute the sequences of instructions contained in memory 906. In alternative aspects, hard-wired circuitry may be used in place of or in combination with software instructions to implement various aspects. Thus, aspects are not limited to any specific combination of hardware circuitry and software.

WO 2010/127049

18

[0062] The term "machine-readable medium" as used herein refers to any medium that participates in providing instructions to processor 904 for execution. Such a medium may take many forms, including, but not limited to, non-volatile media, volatile media, and transmission media. Non-volatile media include, for example, optical or magnetic disks, such as data storage device 910. Volatile media include dynamic memory, such as memory 906. Transmission media include coaxial cables, copper wire, and fiber optics, including the wires that comprise bus 902. Transmission media can also take the form of acoustic or light waves, such as those generated during radio frequency and infrared data communications. Common forms of machine-readable media include, for example, floppy disk, a flexible disk, hard disk, magnetic tape, any other magnetic medium, a CD-ROM, DVD, any other optical medium, punch cards, paper tape, any other physical medium with patterns of holes, a RAM, a PROM, an EPROM, a FLASH EPROM, any other memory chip or cartridge, a carrier wave, or any other medium from which a computer can read.

[0063] Those of skill in the art would appreciate that the various illustrative blocks, modules, elements, components, methods, and algorithms described herein may be implemented as electronic hardware, computer software, or combinations of both. Furthermore, these may be partitioned differently than what is described. To illustrate this interchangeability of hardware and software, various illustrative blocks, modules, elements, components, methods, and algorithms have been described above generally in terms of their functionality. Whether such functionality is implemented as hardware or software depends upon the particular application and design constraints imposed on the overall system. Skilled artisans may implement the described functionality in varying ways for each particular application.

[0064] It is understood that the specific order or hierarchy of steps or blocks in the processes disclosed is an illustration of exemplary approaches. Based upon design preferences, it is understood that the specific order or hierarchy of steps or blocks in the processes may be rearranged. The accompanying method claims present elements of the various steps in a sample order, and are not meant to be limited to the specific order or hierarchy presented.

[0065] The previous description is provided to enable any person skilled in the art to practice the various aspects described herein. Various modifications to these aspects will be readily apparent to those skilled in the art, and the generic principles defined

19

herein may be applied to other aspects. Thus, the claims are not intended to be limited to the aspects shown herein, but is to be accorded the full scope consistent with the language claims, wherein reference to an element in the singular is not intended to mean "one and only one" unless specifically so stated, but rather "one or more." Unless specifically stated otherwise, the term "some" refers to one or more. Pronouns in the masculine (e.g., his) include the feminine and neuter gender (e.g., her and its) and vice versa. All structural and functional equivalents to the elements of the various aspects described throughout this disclosure that are known or later come to be known to those of ordinary skill in the art are expressly incorporated herein by reference and are intended to be encompassed by the claims. Moreover, nothing disclosed herein is intended to be dedicated to the public regardless of whether such disclosure is explicitly recited in the claims. No claim element is to be construed under the provisions of 35

U.S.C. §112, sixth paragraph, unless the element is expressly recited using the phrase

"means for" or, in the case of a method claim, the element is recited using the phrase

"step for."

20

#### **CLAIMS**

#### WHAT IS CLAIMED IS:

- 1. A receiver in a wireless communication system, comprising: an interference suppressor configured to suppress co-channel interference; an equalizer configured to suppress intersymbol interference; and a controller configured to:

- a) control the equalizer to suppress intersymbol interference in a plurality of input samples of a received signal and provide a first set of detected bits based on a first set of reference bits comprising a training sequence on a first iteration;

- b) control the interference suppressor to suppress co-channel interference in the plurality of input samples and provide a set of suppressed samples based on a second set of reference bits comprising the first set of detected bits on a second iteration; and

- c) control the equalizer to suppress intersymbol interference in the set of suppressed samples of b) and provide a second set of detected bits based on the second set of reference bits on the second iteration.

- 2. The receiver according to claim 1, wherein the controller is further configured to compare a strength of the received signal to a threshold prior to performing a) c); and, if the strength of the received signal is greater than the threshold, skip a) c) and alternatively:

- d) control the interference suppressor to suppress co-channel interference in the plurality of input samples to provide a first set of suppressed samples based on the first set of reference bits on a first alternative iteration; and

- e) control the equalizer to suppress intersymbol interference in the set of suppressed samples of d) to provide a set of detected bits based on the first set of reference bits on the first alternative iteration.

- 3. The receiver according to claim 2, wherein the controller is further configured to control the interference suppressor and the equalizer to perform one or more subsequent iterations of interference suppression and equalization, respectively, to improve performance.

- 4. The receiver according to claim 3, wherein the controller, on one of the one or more subsequent iterations, is further configured to:

- f) control the interference suppressor to suppress co-channel interference in a previous set of suppressed samples to provide a next set of suppressed samples based on a next set of reference bits comprising a set of detected bits obtained on a previous iteration, and

- g) control the equalizer to suppress intersymbol interference in the next set of suppressed samples of f) to provide a next set of detected bits based on the next set of reference bits.

- 5. The receiver according to claim 4, wherein the controller is further configured to repeat f(x) g(y) for a plurality of iterations.

- 6. The receiver according to claim 1, wherein the interference suppressor comprises:

- a channel estimator configured to derive at least one channel estimate based on the plurality of input samples;

- a desired signal estimator configured to derive at least one desired signal estimate based on the at least one channel estimate,

- a weight computation unit configured to compute weights used to suppress cochannel interference; and

- a filter configured to filter the plurality of input samples with the weights to generate the set of suppressed samples.

- 7. The receiver according to claim 6, wherein the channel estimator is a least-squares (LS) estimator.

- 8. The receiver according to claim 6, wherein the filter is a multiple-input multiple-output (MIMO) filter.

- 9. The receiver according to claim 1, wherein the equalizer comprises: a channel estimator configured to derive a set of one or more channel estimates;

- a desired signal generator configured to derive a set of one or more desired signal estimates based on the set of one or more channel estimates;

- a noise correlation matrix generation module configured to compute a noise correlation matrix based on the set of one or more desired signal estimates; and

- a detector configured to perform detection on received samples.

- 10. The receiver according to claim 9, wherein the channel estimator is a least-squares (LS) estimator.

- 11. The receiver according to claim 9, wherein the detector is a maximum likelihood sequence estimator (MLSE).

- 12. The receiver according to claim 9, if the controller determines that a strength of the received signal is less than or equal to a threshold, the controller is configured to control the equalizer to:

perform the detection on the plurality of input samples with a first set of one or more channel estimates to provide the first set of detected bits on the first iteration, the first set of one or more channel estimates having been derived based on the plurality of input samples and the first set of reference bits; and

perform the detection on the set of suppressed samples with a second set of one or more channel estimates and the noise correlation matrix to provide the second set of detected bits on the second iteration, the second set of one or more channel estimates having been derived based on the plurality of input samples and the second set of reference bits.

- 13. A method for processing input samples of a signal received in a wireless communication system, the method comprising:

- a) equalizing a plurality of input samples to suppress intersymbol interference and provide a first set of detected bits based on a first set of reference bits comprising a training sequence on a first iteration;

- b) suppressing co-channel interference in the plurality of input samples and provide a set of suppressed samples based on a second set of reference bits comprising the first set of detected bits on a second iteration; and

23

c) equalizing the set of suppressed samples of the step b) to suppress intersymbol interference and provide a second set of detected bits based on the second set of reference bits on the second iteration.

14. The method according to claim 13, wherein the step a) comprises:

deriving a first set of one or more channel estimates based on the plurality of input samples and the first set of reference bits; and

detecting the plurality of input samples based on the first set of one or more channel estimates.

15. The method according to claim 13, wherein the step c) comprises:

deriving a second set of one or more channel estimates based on the set of suppressed samples and the second set of reference bits;

deriving a set of one or more desired signal estimates based on the set of suppressed samples and the second set of one or more channel estimates;

computing a noise correlation matrix based on the set of suppressed samples and the set of one or more desired signal estimates; and

detecting the plurality of input samples based the second set of one or more channel estimates and the noise correlation matrix.

- 16. The method according to claim 13, further comprising comparing a strength of the received signal to a threshold prior to the steps a) c); and if the strength of the received signal is greater than the threshold, skipping the steps a) c) and alternatively:

- d) suppressing co-channel interference in the plurality of input samples to provide a set of suppressed samples based on the first set of reference bits on a first alternative iteration; and

- e) equalizing the set of suppressed samples of the step d) to provide a set of detected bits based on the first set of reference bits on the first alternative iteration.

- 17. The method according to claim 16, further comprising performing one or more subsequent iterations of interference suppression and equalization to improve performance.

PCT/US2010/032858

- 18. The method according to claim 17, further comprising, on one of the one or more subsequent iterations:

- f) suppressing co-channel interference in a previous set of suppressed samples to provide a next set of suppressed samples based on a next set of reference bits comprising a set of detected bits obtained on a previous iteration, and

- g) equalizing the next set of suppressed samples of the step f) to provide a next set of detected bits based on the next set of reference bits.

- 19. The method according to claim 18, wherein the steps f(x) g(y) are repeated for a plurality of iterations.

- 20. The method according to claim 16, wherein the threshold is determined at a product design stage based at least in part on a background white noise level of the receiver.

## 21. A receiver comprising:

first interference suppressing means for suppressing co-channel interference; second interference suppressing means for suppressing intersymbol interference;

controlling means for:

and

- a) controlling the second interference suppressing means to suppress intersymbol interference in a plurality of input samples of a received signal and provide a first set of detected bits based on a first set of reference bits comprising a training sequence on a first iteration;

- b) controlling the first interference suppressing means to suppress cochannel interference in the plurality of input samples and provide a set of suppressed samples based on a second set of reference bits comprising the first set of detected bits on a second iteration; and

- c) controlling the second interference suppressing means to suppress intersymbol interference in the set of suppressed samples of b) and provide a second set of detected bits based on the second set of reference bits on the second iteration.

25

- 22. A machine-readable medium comprising instructions for processing input samples of a signal received in a wireless communication system, the instructions comprising code for:

- a) equalizing a plurality of input samples to suppress intersymbol interference and provide a first set of detected bits based on a first set of reference bits comprising a training sequence on a first iteration;

- b) suppressing co-channel interference in the plurality of input samples and provide a set of suppressed samples based on a second set of reference bits comprising the first set of detected bits on a second iteration; and

- c) equalizing the set of suppressed samples of the step b) to suppress intersymbol interference and provide a second set of detected bits based on the second set of reference bits on the second iteration.

FIG. 4

FIG 5

FIG 7

FIG. 9