(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6066955号

(P6066955)

(45) 発行日 平成29年1月25日(2017.1.25)

(24) 登録日 平成29年1月6日(2017.1.6)

(51) Int.Cl.

H04N 1/393 (2006.01)

G06T 3/40 (2006.01)

F 1

H04N 1/393

G06T 3/40 710

請求項の数 9 (全 19 頁)

(21) 出願番号 特願2014-77522 (P2014-77522)

(22) 出願日 平成26年4月4日 (2014.4.4)

(65) 公開番号 特開2015-201672 (P2015-201672A)

(43) 公開日 平成27年11月12日 (2015.11.12)

審査請求日 平成27年5月12日 (2015.5.12)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100099324

弁理士 鈴木 正剛

(72) 発明者 矢野 譲

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 鈴木 明

(56) 参考文献 特開2011-135387 (JP, A)

特開2001-189852 (JP, A)

最終頁に続く

(54) 【発明の名称】 画像形成装置

## (57) 【特許請求の範囲】

## 【請求項 1】

記録媒体上の画像を形成する画像形成手段と、

前記画像を記録媒体に定着させる定着手段と、

前記画像を示す画像データを格納する格納手段と、

前記記録媒体の搬送方向に対応する第1方向において注目画素の位置を示す第1位置情報の生成と、前記第1方向に直交する第2方向における前記注目画素の位置を示す第2位置情報の生成と、前記記録媒体の搬送方向に対応する第1方向における変倍情報に基づき、前記画像を示す画像データを前記第1方向において複数のエリアに分割するための条件の設定と、を制御する制御手段と、

シード値に基づき乱数値を生成する乱数値生成手段と、

前記シード値を保持する保持手段と、を有し、

前記制御手段は、前記注目画素の第1位置情報が前画素の第1位置情報と異なり、かつ、前記注目画素のエリアがその前画素のエリアと異なる場合、前記乱数値生成手段に設定されるシード値を前記保持手段に格納し、前記注目画素の前記第1位置情報が前画素の前記第1位置情報と異なり、かつ、前記注目画素のエリアが前画素のエリアと同一である場合、前記保持手段に保持されている前記シード値を前記乱数値生成手段に設定し、前記注目画素ごとに、前記乱数値生成手段により乱数値を生成させ、この生成された乱数値、前記第2位置情報および前記第1位置情報に基づき、前記注目画素に対応する画像データを前記格納手段から読み出すことにより前記画像に対する変倍を行うことを特徴とする、

10

20

画像形成装置。

【請求項 2】

前記乱数値生成手段は、複数個の2値データの記録素子を縦列接続するとともに、いずれかの記録素子間に論理演算回路を介在させて構成された擬似乱数値生成回路を有し、

前記シード値は、前記複数個の記録素子が保持する2値データの集合であり、

前記乱数値生成手段は、前記シード値に基づく一の乱数値を生成した後、前記記録素子に保持される2値データをそれぞれ所定方向に隣接する他の記録素子に移行させ、これにより変化したシード値に基づいて次の乱数値を生成することを特徴とする、

請求項1記載の画像形成装置。

【請求項 3】

10

前記制御手段は、前記生成された乱数値に基づき前記第1位置情報を修正し、該修正された第1位置情報と前記第2位置情報とに対応する画像データを前記格納手段から読み出すように制御することを特徴とする、

請求項1又は2に記載の画像形成装置。

【請求項 4】

前記制御手段は、拡大処理する場合は前記生成された乱数値に応じた画像データを2度読み出し、縮小処理する場合は、前記生成された乱数値に応じた画像データの読み出しを行わないように制御することを特徴とする、

請求項1、2又は3に記載の画像形成装置。

【請求項 5】

20

前記画像データは、前記画像の主走査方向及び副走査方向に配列された画素の集合であり、

前記画像データを複数のエリアに分割する分割手段を有し、

前記分割手段は、分割されたエリア毎に、入力された拡大率に応じて前記乱数値で定めた位置に画素を挿入し、又は入力された縮小率に応じて前記乱数値で定めた位置の画素を削除する処理を行うことを特徴とする、

請求項1乃至4いずれか一項に記載の画像形成装置。

【請求項 6】

前記乱数値生成手段が生成する乱数値によって、前記エリア内の1つの画素が特定されることを特徴とする、

30

請求項2乃至5いずれか一項に記載の画像形成装置。

【請求項 7】

前記乱数値生成手段が生成した乱数値が、前記エリア内の画素に対応しない値である場合、当該乱数値生成手段は、新たなシード値を用いて乱数値を生成することを特徴とする、

請求項2乃至6いずれか一項に記載の画像形成装置。

【請求項 8】

前記制御手段は、主走査方向の画素の位置を表す主走査位置に対応する副走査方向の画素の位置を、前記シード値に基づいて生成された乱数値により決定することを特徴とする、

40

請求項2乃至7いずれか一項に記載の画像形成装置。

【請求項 9】

前記制御手段は、処理の対象となるエリアが切り替わる度に、異なるシード値を前記保持手段に保持させ、当該エリアにおける処理の開始前に、前記乱数値生成手段に当該シード値に基づく乱数値を生成させることを特徴とする、

請求項1記載の画像形成装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像データを変倍する画像処理装置に関する。

50

**【背景技術】****【0002】**

静電潜像により画像を形成する処理を行う画像処理装置では、構成部品の取り付け位置のばらつき、又は、形成された画像を定着する際の熱などの影響を受け、転写部材上に形成された画像サイズと本来意図する画像サイズが異なってしまうという問題がある。

**【0003】**

このような問題に対し、特許文献1に開示された画像読み取り装置では、本来意図する画像サイズと、出力された画像の画像サイズとから、画像を形成する工程での拡大率又は縮小率(変倍率)を測定する。そして、変倍の元画像データに対し、測定された変倍率の逆補正を行ったデータを入力画像として用いる。その結果、最終的に出力される画像サイズが10

本来意図する画像サイズとなる。

**【0004】**

例えば、画像形成を行った際に、入力画像サイズに対する出力画像サイズが、主走査方向で99[%]、副走査方向で101[%]のサイズとなるとする。この場合、入力画像サイズに対して、測定された変倍率の逆数を積算してから画像形成処理を行うと、本来意図する画像サイズとなる。具体的には、入力画像の画像サイズを主走査方向に1.010

101... (99[%])の逆数 = 100 / 99 倍、副走査方向に0.990099... (1

01の逆数 = 100 / 101) 倍する。すると、出力画像の画像サイズは、主走査方向1

.010101... × 99[%] = 100[%]、副走査方向0.990099... × 101

[%] = 100[%]となる。

**【0005】**

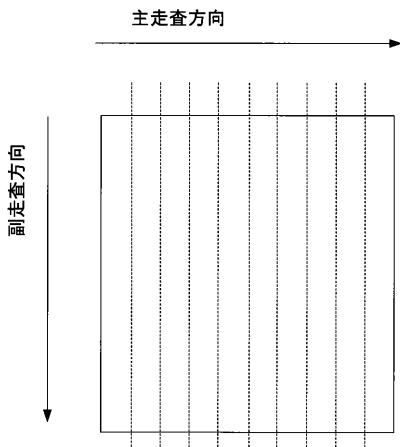

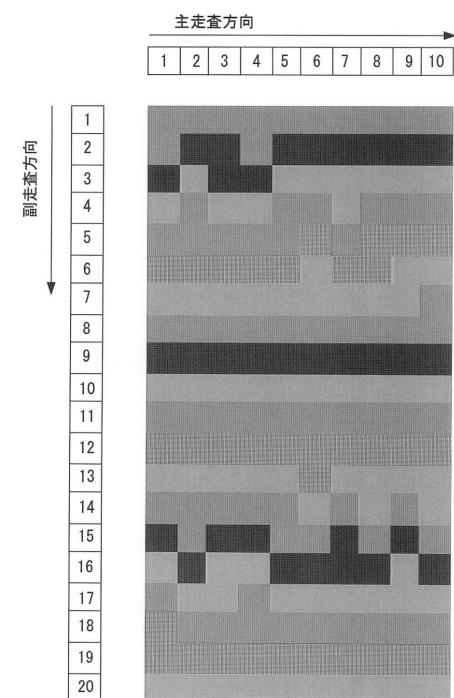

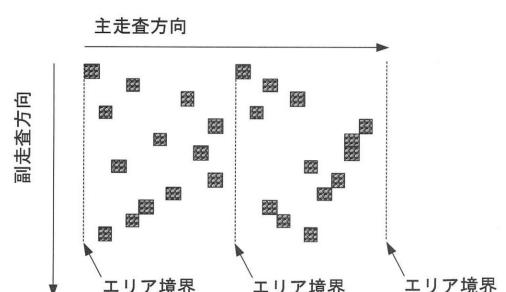

入力画像データを変倍する場合、特許文献1に開示された画像読み取り装置では、主走査方向について、入力画像サイズと変倍率を積算した画像サイズとから、差分となる画素数を算出する。そして、入力画像を、主走査方向において、差分となる画素数で複数のエリアに分割する。例えば、図16に示すように、主走査方向で入力画像サイズと出力画像サイズの差分が10画素であった場合、入力画像を主走査方向に垂直な線(図16の点線)で10分割する。その後、分割されたエリア(領域)毎に、主走査方向1ラインにつき1ヶ所となるようにランダムな位置を決定して画素を特定する。同一エリア内であっても、ランダムな位置は異なる。このようにして決定されたランダムな位置に対し、変倍率が拡大を示す場合は、画素を追加し、縮小を示す場合は、画素を削除する。

**【0006】**

図17は、決定されたランダムな位置で特定された画素を視覚的に表した模式図である。図17では、分割されたエリアの一部分を拡大している。図17に示すエリア境界は、図16に示した点線部分に相当する。上記の変倍率積算フローは、主走査方向のみならず、副走査方向においても同様となる。

**【先行技術文献】****【特許文献】****【0007】****【特許文献1】特開2008-99114号公報****【発明の概要】****【発明が解決しようとする課題】****【0008】**

一定の副走査ライン単位で画像データを入出力し、画像処理を行う画像処理装置において、上記の変倍率積算フローによる副走査方向の変倍を行う場合、ランダムな位置を決定するための乱数値をメモリに記録しておく必要がある。乱数値は、複数ラインに跨る位置情報であり、乱数値が適用される範囲分の走査が終了するまで、乱数値を保持しなければならないためである。

**【0009】**

ここで、画像データを1ラインずつ処理する画像処理装置により、副走査方向に画像を拡大処理する場合の例を説明する。便宜上、分割されたエリアの副走査方向の画素数を1

50

0画素とする。

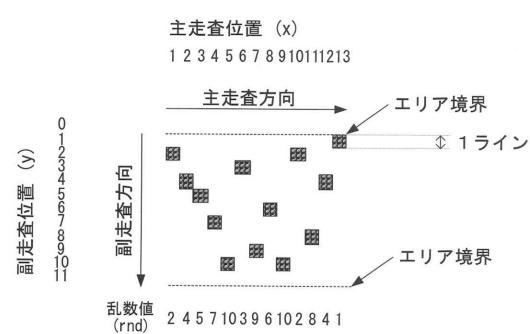

図18は、副走査方向の変倍の際に、分割されたエリアの1つにおいて、ランダムな位置が決定される様子を表した図である。主走査位置を表す座標値を「x」、副走査位置を表す座標値を「y」とする。1ラインずつ画像処理を行うので、座標値 $y = 1$ のデータ{(x, y) = (1, 1) (x, y) = (2, 1) (x, y) = (3, 1) (x, y) = (4, 1) ...}を出力した後に、座標値 $y = 2$ のデータを出力する。更に座標値 $y = 3$ 、 $y = 4$ 、...、 $y = 11$ と順番に出力する。

#### 【0010】

なお、図18に例示した拡大処理では、エリア内で副走査方向に1画素拡大されることが予め分かっているため、入力画像におけるエリアの副走査方向が10画素とした場合、出力画像の副走査方向の画素数は、 $10 + 1 = 11$ 画素となる。ランダムな位置を決定するための乱数値は、エリア境界を越えたとき、つまり、座標値 $y = 1$ の画像を出力しているときに生成する必要がある。座標値 $y = 2$ のときに乱数値を算出した場合、座標値 $y = 1$ で画像処理を行うべき値が生成されたときに、座標値 $y = 1$ の画像は、既に出力済みであり、処理が不可能となるためである。以下、このことを具体例を挙げて説明する。

10

#### 【0011】

乱数値rnd(x)は、エリアの副走査方向の画素位置(画素数)に対応した乱数値であり、以下の例では乱数値rnd(x)が、以下の(1)から(13)のようになった場合の動作を説明する。

- (1) 座標値 $x = 1$ 、乱数値rnd(1) = 2

- (2) 座標値 $x = 2$ 、乱数値rnd(2) = 4

- (3) 座標値 $x = 3$ 、乱数値rnd(3) = 5

- (4) 座標値 $x = 4$ 、乱数値rnd(4) = 7

- (5) 座標値 $x = 5$ 、乱数値rnd(5) = 10

- (6) 座標値 $x = 6$ 、乱数値rnd(6) = 3

- (7) 座標値 $x = 7$ 、乱数値rnd(7) = 9

- (8) 座標値 $x = 8$ 、乱数値rnd(8) = 6

- (9) 座標値 $x = 9$ 、乱数値rnd(9) = 10

- (10) 座標値 $x = 10$ 、乱数値rnd(10) = 2

- (11) 座標値 $x = 11$ 、乱数値rnd(11) = 8

- (12) 座標値 $x = 12$ 、乱数値rnd(12) = 4

- (13) 座標値 $x = 13$ 、乱数値rnd(13) = 1

20

#### 【0012】

座標値(x, y) = (1, 1)の画像を出力するとき、乱数値rnd(1)を参照する。乱数値rnd(1) = 2なので、決定されたランダムな位置は座標値 $y = 2$ である。そのため、座標値 $y = 1$ では何も処理を行わない。座標値(x, y) = (2, 1)、(x, y) = (3, 1)、...、(x, y) = (12, 1)も同様である。座標値(x, y) = (13, 1)の画像を処理するとき、乱数値rnd(13) = 1である。この乱数値rnd(13)の値と、現在処理しているラインの値とが一致するため、拡大処理を行う必要が生じる。拡大処理を行うためには、1ライン前の画像、つまり座標値(x, y) = (13, 0)の画像を出力する必要がある。以後、座標値 $x = 13$ の画像は副走査方向に1ラインずつシフトする。

30

次に、座標値(x, y) = (1, 2)の画像の処理するため乱数値rnd(2)を参照し、座標値(x, y) = (2, 2)の画像を出力するために乱数値rnd(2)の値が参照される。その後、座標値(x, y) = (13, 11)の画像を出力するまで、処理が繰り返される。

40

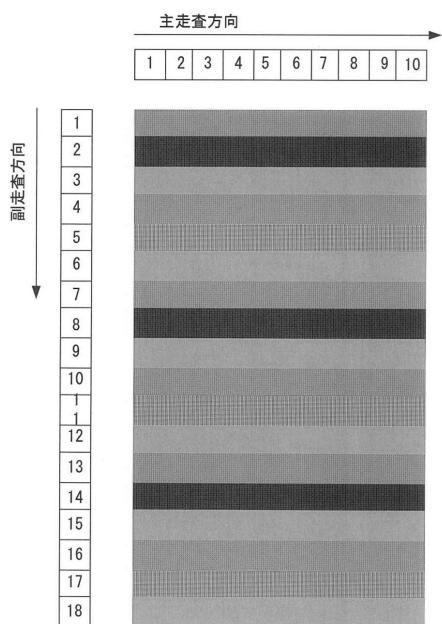

#### 【0013】

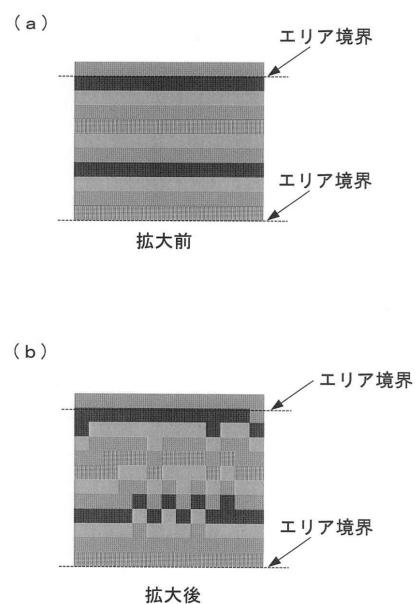

このようにして拡大処理が施されることで、図19(a)に示す入力画像が、図19(b)に示す出力画像になる。入力画像では、エリアの副走査方向の画素数が10画素であったものが、拡大処理後の副走査方向の画素数は11画素となっている。つまり、副走査

50

方向に  $11 / 10 \times 100 - 100 = 10$  [ % ] 拡大されたことになる。なお、拡大処理に伴い、エリアの境界線も 1 ラインシフトする。

以上説明した拡大処理フローでは、座標値  $y = 1$  から座標値  $y = 11$  までのデータを出力している間、座標値  $y = 1$  で算出された乱数値が常に参照される。そのため、座標値  $y = 1$  で算出された乱数値は、メモリに記録しておく必要がある。

#### 【0014】

上記フローは、拡大処理する場合の説明であるが、縮小処理の場合には、画素を追加する処理を削除する処理になる。そして、画像のシフト方向を遅れ方向から詰める方向にして処理を行う。但し、縮小処理の場合であっても、乱数値をメモリに記録しておく必要があることに変わりはない。また、便宜上、主走査方向の画素数が 13 画素の場合を例にして説明したが、実際の画像処理装置においては、主走査方向の画素数が 800 画素以上となることがある。そのため、乱数値を記憶するための大容量のメモリが必要となり、画像処理装置の製造コストを増加させる要因となるという課題が残る。10

#### 【0015】

本発明は、処理に使用する乱数値を記録するためのメモリを軽減することを目的とする。。

#### 【課題を解決するための手段】

#### 【0016】

本発明の画像形成装置は、記録媒体上の画像を形成する画像形成手段と、前記画像を記録媒体に定着させる定着手段と、前記画像を示す画像データを格納する格納手段と、前記記録媒体の搬送方向に対応する第1方向において注目画素の位置を示す第1位置情報の生成と、前記第1方向に直交する第2方向における前記注目画素の位置を示す第2位置情報の生成と、前記記録媒体の搬送方向に対応する第1方向における変倍情報に基づき、前記画像を示す画像データを前記第1方向において複数のエリアに分割するための条件の設定と、を制御する制御手段と、シード値に基づき乱数値を生成する乱数値生成手段と、前記シード値を保持する保持手段と、を有し、前記制御手段は、前記注目画素の第1位置情報が前画素の第1位置情報と異なり、かつ、前記注目画素のエリアがその前画素のエリアと異なる場合、前記乱数値生成手段に設定されるシード値を前記保持手段に格納し、前記注目画素の前記第1位置情報が前画素の前記第1位置情報と異なり、かつ、前記注目画素のエリアが前画素のエリアと同一である場合、前記保持手段に保持されている前記シード値を前記乱数値生成手段に設定し、前記注目画素ごとに、前記乱数値生成手段により乱数値を生成させ、この生成された乱数値、前記第2位置情報および前記第1位置情報に基づき、前記注目画素に対応する画像データを前記格納手段から読み出すことにより前記画像に対する変倍を行うことを特徴とする。2030

#### 【発明の効果】

#### 【0017】

本発明によれば、処理に使用する乱数値を記録するためのメモリを軽減させることができる。40

#### 【図面の簡単な説明】

#### 【0018】

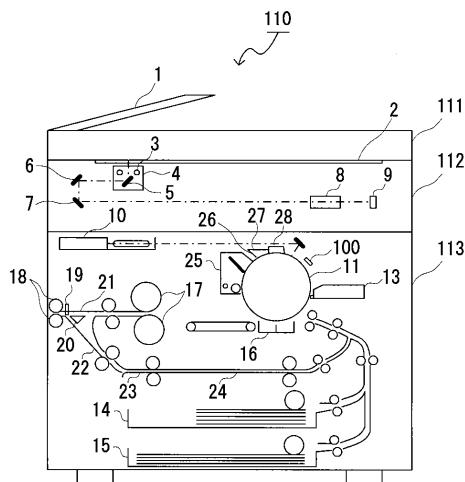

【図1】本実施形態の画像処理装置の概略縦断面図。

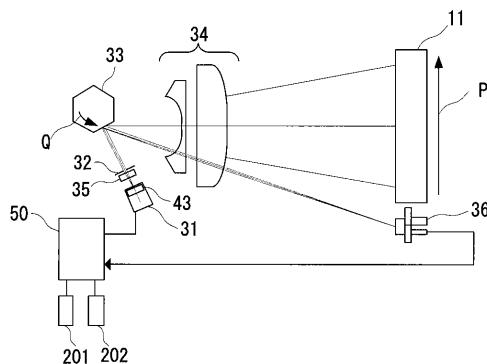

【図2】画像処理装置の露光制御部の詳細を示した構成例図。

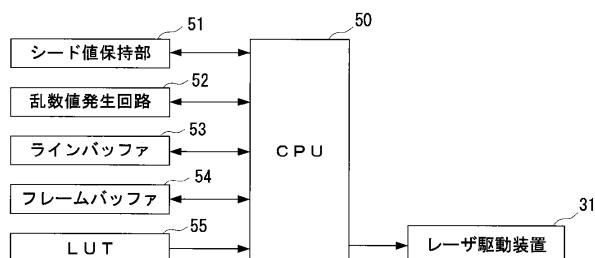

【図3】レーザ駆動装置に接続された画像処理CPU周辺の構成例図。

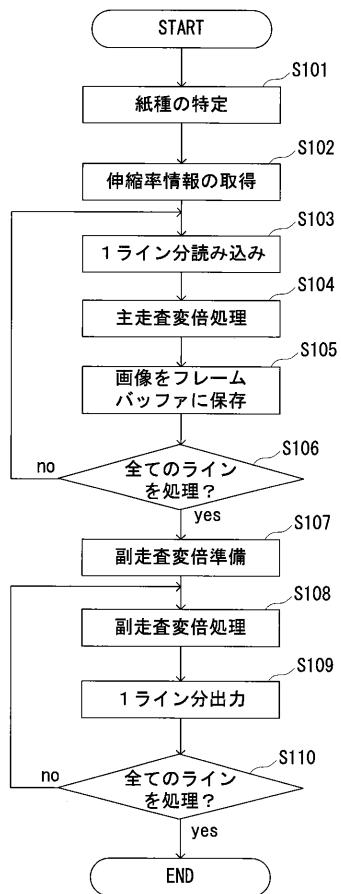

【図4】変倍処理の処理手順を示すフローチャート。

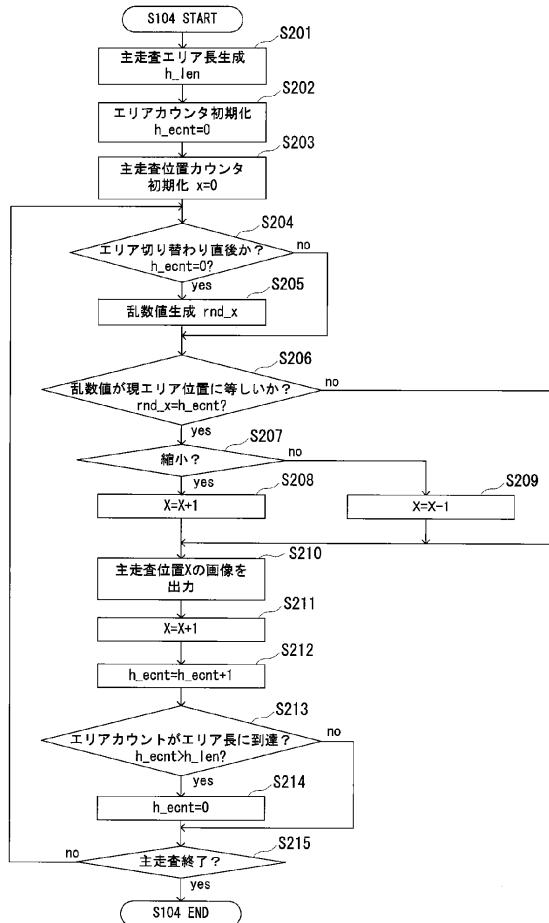

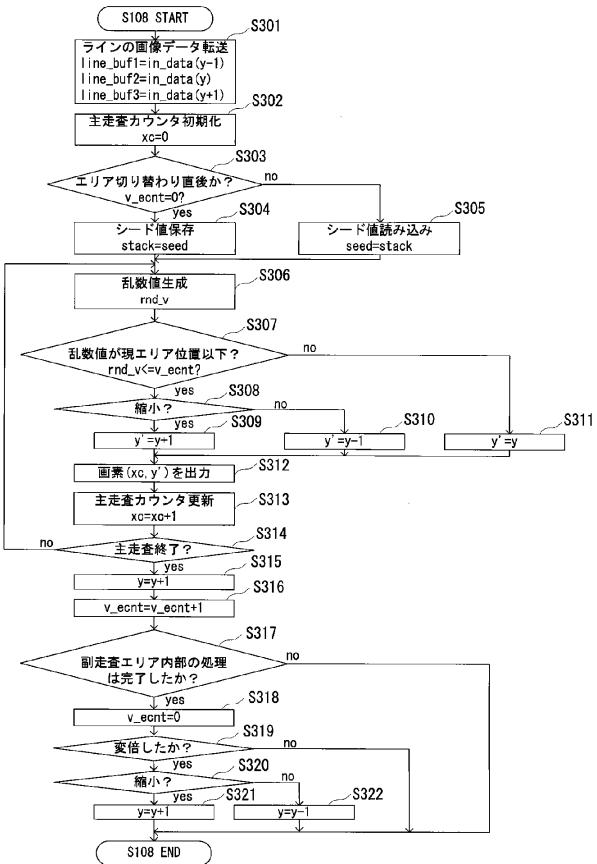

【図5】主走査方向の変倍処理の具体的な処理手順を示すフローチャート。

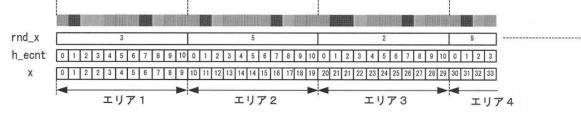

【図6】主走査方向の変倍処理のタイミングチャート。

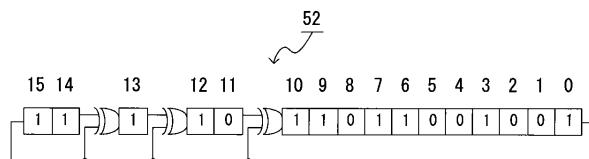

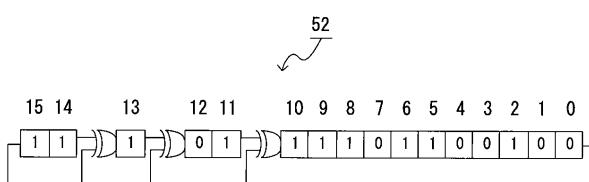

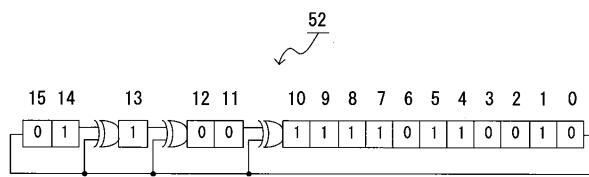

【図7】乱数値発生回路の模式図。

【図8】乱数値発生回路と1回シフト後のシード値を示す図。

【図9】乱数値発生回路と2回シフト後のシード値を示す図。50

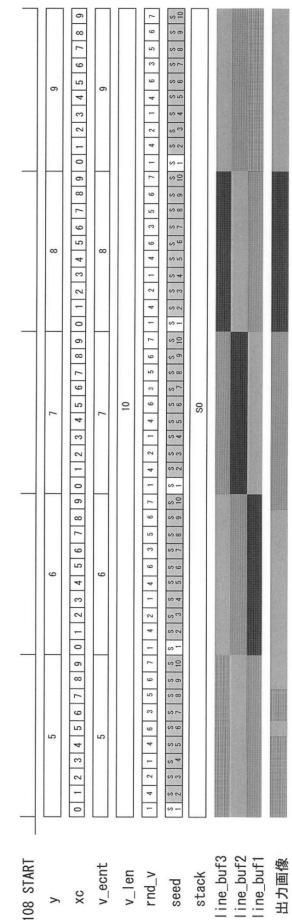

- 【図10】副走査方向の変倍処理の具体的な処理手順を示すフロー チャート。

- 【図11】副走査方向の変倍処理のタイミングチャート。

- 【図12】図11に続く副走査方向の変倍処理のタイミングチャート。

- 【図13】図12に続く副走査方向の変倍処理のタイミングチャート。

- 【図14】副走査方向の変倍処理時の入力画像例。

- 【図15】副走査方向の変倍処理時の出力画像例。

- 【図16】入力画像を主走査毎のエリアに分割した様子を示す図。

- 【図17】主走査方向の変倍処理の際に、乱数値により変倍処理を行う箇所が決定されたことを示す図。

- 【図18】副走査方向の変倍処理の際に、乱数値により変倍処理を行う箇所が決定されたことを示す図。 10

- 【図19】(a)は変倍処理される入力画像、(b)は変倍処理後の出力画像を示す図。

- 【発明を実施するための形態】

- 【0019】

以下、図面を参照しながら実施形態例を説明する。

- 【0020】

[第1実施形態例]

図1は、第1実施形態に係る画像処理装置の概略縦断面図である。

この画像処理装置110は、原稿を所定の読み取り部位まで給送する原稿給送部111、給送された原稿を読み取る画像読み取り部112、読み取った画像データに基づき作像する画像形成部113を含んで構成される。 20

- 画像処理装置110の基本的な動作について、図1を参照しながら説明する。

原稿給送部111の原稿給紙装置1に積載された原稿は、1枚ずつ、画像読み取り部112の原稿台ガラス面2上まで給送される。

- 【0021】

原稿が給送されると、画像読み取り部112のスキャナーユニット4に備わるランプ3が点灯し、原稿表面に光を照射すると共に、スキャナーユニット4が副走査方向へと移動する。原稿表面からの反射光は、スキャナーユニット4に備わるミラー5、ミラー6、7を介して集光部8を通過し、その後、イメージセンサ部9に入力される。イメージセンサ部9は、反射光を画像信号(画像データ)へ変換する。この画像信号は、画像形成部113の露光制御部10へ出力される。 30

- 【0022】

露光制御部10は、画像信号に応じて、露光制御部10に搭載されたレーザ駆動装置を制御し、レーザ光を発生させる。レーザ光の照射により感光体11上に作られた潜像は、電位センサ100において、感光体11上の電位が所望の値になっているかどうかが監視される。所望の値のときは、現像器13により現像される。

- 感光体11は、露光制御部10の出力ライン毎に同期するように回転駆動され、簾状のライン走査を繰り返すことにより、画像を形成する。また、潜像タイミングにあわせて、転写部材積載部14又は15から転写部材が搬送され、転写部16に於いて、上記現像されたトナー像が転写部材上に転写される。転写されたトナー像は、定着部17で転写部材に定着された後、排出口ローラ対18より装置外部に排出される。 40

- 転写後の感光体11の表面は、クリーナ25により清掃される。清掃された感光体11の表面は、補助帯電器26で除電され、1次帯電器28により良好な帯電を得られるよう調整される。その上で、感光体11上の残留電荷を露光ランプ27により消去させて、1次帯電器28により感光体11の表面を帯電させる。画像処理装置110は、この工程を繰り返して複数枚の画像形成を行う。

- 【0023】

転写部材の両面に画像を形成する場合は、転写部材の表面に画像が形成された後、定着部17から搬送された転写部材の後端がシート検知部19により検知されたときに、排出口ローラ対18の回転を停止する。排出通路21に設けられたフラッパー20は、通路を反 50

転通路 22へ切り替える。その後、排出口一対 18が逆転して、転写部材を反転通路 22へ搬送する。転写部材は、反転通路 22から反転搬送路入口 23を経由して反転搬送路 24へ搬送される。転写部材は、反転搬送路 24から再び転写部 16へ搬送されて、前記した画像形成動作と同様にして、転写部材の裏面に画像が形成される。

#### 【0024】

図 2 は、露光制御部 10 の詳細を示した構成図である。露光制御部 10 は、半導体レーザ 43 と、レーザ駆動装置 31、絞り 32、回転多面鏡（以下、ポリゴンミラーという。）33、f - レンズ 34、コリメータレンズ 35、ビームディテクトセンサ（以下、BDセンサという。）36 を含んで構成される。露光制御部 10 は、また、画像処理用 CPU（以下、単に「CPU」とする。）50、パルス幅変調のためのルックアップテーブル（以下、LUTとする。）、後述するもう一つの LUT 55 などが格納される RAM 201 を有する。RAM 201 は、また、後述するシード値保持部 51 として機能する。

10

露光制御部 10 は、さらに、画像データを一時的に格納するための RAM 202 を有する。具体的には、RAM 202 は、後述するラインバッファ 53、フレームバッファ 54 として使用される。露光制御部 10 は、画像データに従ってパルス幅変調されたレーザ光を主走査方向に走査することにより、感光体 11 の表面を露光する。

#### 【0025】

イメージセンサ部 9 から出力された画像信号は、CPU 50 に入力される。CPU 50 は、入力された画像信号を画像処理装置 110 の作像モードに応じた PWM（パルス幅変調）テーブル変換を行い、レーザ駆動信号としてレーザ駆動装置 31 に出力する。また、PWM テーブル変換を行った後、走査変倍率（拡大率又は縮小率）設定に応じて、画素の追加又は削除を行う。レーザ駆動装置 31 は、CPU 50 からレーザ駆動信号を受信し、半導体レーザ 43 を駆動する。

20

#### 【0026】

半導体レーザ 43 の内部には、レーザ光の一部を検出する PD（フォト・ダイオード）センサが設けられており、PD センサの検出信号を用いてレーザダイオードのオートパワー・コントロール制御を行う。半導体レーザ 43 から発せられたレーザ光は、コリメータレンズ 35 及び絞り 32 によりほぼ平行光となり、所定の光径でポリゴンミラー 33 に入射する。ポリゴンミラー 33 は、矢印 Q で示す方向に等角速度の回転をするように、図示しない駆動装置により駆動される。この回転に伴い、入射したレーザ光は、連続的に角度が変位された偏向ビームとなって反射される。

30

#### 【0027】

偏向ビームは、f - レンズ 34 により集光する。その際、f - レンズ 34 は、偏向ビームの歪曲収差の補正を行う。そのため、偏向ビームは、像担持体としての感光体 11 上に矢印 P の方向に向けて等速で結合走査される。

BD センサ 36 は、ポリゴンミラー 33 からの反射光を検出する。この信号は、主走査方向の画像形成位置を一定にするために、ポリゴンミラー 33 の回転と画像データの書き込みを同期させるための同期信号（主走査同期信号）である。

#### 【0028】

上記プロセスにより、転写部材上に画像が形成されるが、転写されたトナー像を定着部 17 で定着する際に加えられる熱により、転写部材が伸縮してしまう場合がある。転写部材が伸縮すると、転写部材上に出力される画像サイズと、イメージセンサ部 9 から入力された画像サイズとが異なるものとなる。転写部材の伸縮率は、転写部材の材質によってほぼ一定である。例えば、ユーザが予め転写部材の種類を図示しないコントロールパネルを介して指定することで、CPU 50 において伸縮率の逆数の変倍処理を行い、出力画像のサイズをユーザの意図通りにすることができます。

40

#### 【0029】

次に、CPU 50 において画像データを変倍する処理について詳細に説明する。本実施形態では、定着によって転写部材（例えば記録紙）が主走査方向に 90 . 90909... (= 100 / 110) [%] 縮小、副走査方向に 90 . 90909... (= 100 / 110)

50

[ % ] 縮小する場合の例を説明する。入力画像サイズは、主走査方向 100 画素、副走査方向 100 画素に相当するものとする。また、CPU50 の入出力画像単位は、1 ライン（1 ライン入力する毎に 1 ライン出力）とする。

#### 【0030】

図 3 は、レーザ駆動装置 31 に接続された CPU50 周辺の構成図である。図 4 は、CPU50 による変倍処理の処理手順を示すフローチャートである。図 3 と図 4 を参照しながら、画像処理装置 110 における画像の変倍処理の処理手順について説明する。

#### 【0031】

CPU50 は、図示しないコントロールパネルを介してユーザにより設定された転写部材の種類示す転写部材情報を取得する（S101）。また、取得された転写部材情報に対応する伸縮率情報を、LUT55 から取得する（S102）。LUT55 は、画像処理装置 110 が予めライブラリとして備えているデータであり、例えば、転写部材情報に対応させて転写部材の主走査方向および副走査方向に対する伸縮率情報が格納されている。転写部材の伸縮率情報の代わりに画像に対する変倍率（拡大率又は縮小率）情報が格納されている構わない。ステップ S102 の処理において、主走査方向・副走査方向それぞれに対する伸縮率情報が取得される。

以下、主走査方向が 90.90909... (= 100 / 110) [ % ] 縮小し、副走査方向が 90.90909... (= 100 / 110) [ % ] 縮小する転写部材が指定されている例を用いて説明する。よって、LUT55 から取得される伸縮率情報は、主走査方向に 10 [ % ] 縮小、副走査方向に 10 [ % ] 縮小という値となる。したがって、元画像データを主走査方向に 10 [ % ] 拡大、副走査方向に 10 [ % ] 拡大した画像を転写部材上に形成することが必要となる。このように、元画像データを主走査方向に 10 [ % ] 拡大、副走査方向に 10 [ % ] 拡大した画像を転写部材上に形成することにより、画像形成プロセスにおいて、それぞれ 90.90909... [ % ] 縮小されることになる。その結果として、100 (110 × 100 / 110) [ % ] のサイズで画像が出力されることになる。

なお、S101 のフローを省略して、ユーザが直接、図示しないコントロールパネルを介して伸縮率を指定するようにしても良い。

#### 【0032】

その後、CPU50 は、1 ライン分の画像データを読み込む（S103）。また、読み込んだ 1 ライン分の画像データに対して主走査方向の変倍処理（主走査変倍処理）を行い、処理後の 1 ライン分の画像データを出力する（S104）。主走査変倍処理の詳細については後述する。

CPU50 は、出力した処理後の 1 ライン分の画像データをフレームバッファ 54 に記録させる（S105）。作像するページ全体に対して、ステップ S103 からステップ S105 の各処理を繰り返す。これにより、最終的にページ全体の画像データがフレームバッファ 54 に記録される。

#### 【0033】

CPU50 は、1 ページの画像全体に対して主走査変倍処理が行われたか否かを判定する（S106）。具体的には、1 ライン分の画像データを読み込む毎に、読み込んだトータルのライン数を、例えば RAM201 に記録する。そして、記録されたトータルのライン数と、入力画像データの副走査サイズが等しくなったことを検出し、ページ全体の処理が終了したと判定する。未処理の画像データが残っている場合（S106 : no）、ステップ S103 の処理へ戻り、処理を繰り返す。

#### 【0034】

未処理の画像データが残っていない場合（S106 : yes）、CPU50 は、副走査方向の変倍処理（副走査変倍処理）を行うための前処理として、副走査変倍処理で使用する各パラメータの初期化を行う（S107）。詳細については、副走査変倍処理の詳細と合わせて後述する。

その後、CPU50 は、主走査同期信号の検知を契機に、主走査変倍処理後の 1 ライン分の画像データに対して副走査変倍処理を開始し、処理後の 1 ライン分の画像データを出

10

20

30

40

50

力する（S108）。副走査変倍処理の詳細については、後述する。

#### 【0035】

CPU50は、副走査変倍処理を行った画像データを1ライン分出力する（S109）。その後、CPU50は、全てのライン数分（ページ全体）の画像データを処理したか否かを判定する（S110）。具体的には、ステップS109の処理で出力したトータルのライン数を、例えばRAM201に記録する。そして、記録されたトータルのライン数と、入力画像データの副走査サイズの変倍後のライン数が等しくなったことを検出し、ページ全体の処理が終了したと判定する。例えば、入力画像の副走査ライン数が100画素、伸縮率が10[%]拡大であれば、トータルライン数が $100 \times 110\% = 110$ ラインとなったときに、全てのライン数分の処理が終了したことになる。全てのライン数分の処理が終了していない場合（S110：no）、ステップS108の処理へ戻り、処理を繰り返す。

10

全てのライン数分の処理が終了した場合（S110：yes）、CPU50は、変倍処理を終了する。

#### 【0036】

次に、ステップS104の主走査変倍処理の処理手順を詳細に説明する。

図5は、図4で示したステップS104の主走査方向の変倍処理の具体的な処理手順を示すフローチャートである。

CPU50は、主走査エリア長h\_1enを算出する（S201）。まず、入力画像サイズと主走査変倍後の画像サイズとの差分を算出する。そして、主走査入力画像サイズを差分画素数の絶対値で分割することにより、主走査エリア長h\_1enを求める。本実施形態の例の場合、主走査入力画像サイズは100画素、主走査方向へ10[%]拡大であるため、主走査変倍後の主走査方向の画像サイズは $100 + 100 \times 10\% = 110$ 画素、差分画素数は $110 - 100 = 10$ となる。主走査エリア長h\_1enは、主走査入力画像サイズ $100 / 10 = 10$ 画素となる。

20

CPU50は、主走査エリア長h\_1enの値に基づいて、入力された1ライン分の画像データを複数のエリア（領域）に分割する。分割されたそれぞれのエリアが一つの処理単位となる。

#### 【0037】

次に、CPU50は、エリアカウンタh\_ecntを初期化（h\_ecnt = 0）する（S202）。エリアカウンタh\_ecntは、分割されたエリア内での主走査位置をカウントするために用いられる。なお、エリアカウンタh\_ecnt = 0のときに、エリアが切り替わったタイミングであることを示す。

30

さらに、CPU50は、主走査カウンタxも初期化（x = 0）する（S203）。主走査カウンタxは、入力された主走査方向1ライン分の画像データの中から、出力すべき画像データを特定するための主走査位置を示す。主走査カウンタxの値が0（ゼロ）のとき、主走査方向において画像の先端の位置する画像データであることを示す。

#### 【0038】

CPU50は、処理対象のエリアが切り替わったか否か、つまり、新しいエリアの処理へ移行したか否かを判定する（S204）。具体的には、エリアカウンタh\_ecntが、h\_ecnt = 0のときに新しいエリアの処理へ移行したと判定する。エリアが切り替わった（h\_ecnt = 0）場合（S204：yes）、CPU50は、乱数値発生回路52に指示を出し、乱数値rnd\_xを生成し、RAM201に記憶する（S205）。ステップS205の処理において生成された乱数値rnd\_xは、同一のエリアに対して使用される。生成された乱数値rnd\_xは、0（ゼロ）以上で、且つ、主走査エリア長h\_1en未満の範囲内の値である。乱数値rnd\_xの生成方法は、例えば一般的なM系列の原始多項式を利用した擬似乱数値生成回路を使用することができる。なお、主走査エリア長h\_1enの上限値は、画質の低下具合を見ながらチューニングする方法を取っても良い。

40

#### 【0039】

エリアが切り替わっていない場合 (S 2 0 4 : y e s)、CPU50は、処理対象の主走査位置 $\times$ に対応する乱数値rnd $_x$ の値とエリアカウンタh\_e c n tの値を比較する (S 2 0 6)。比較した結果、一致する場合 (S 2 0 6 : y e s)、変倍処理を行う必要があるため、CPU50は、画像データに施す変倍処理が縮小させるものか、又は、拡大させるものかを判定する (S 2 0 7)。縮小させる場合 (S 2 0 7 : y e s)、CPU50は、出力画像の位置を1画素早めるために、主走査カウンタ $\times$ の値に1を加算する (S 2 0 8)。このように、縮小させる変倍処理のときは、通常時に出力すべき画像を削除して、次以降の画像を詰めて出力する処理を行う。一方、拡大させる場合 (S 2 0 7 : n o)、CPU50は、出力画像の位置を1画素遅くするために、主走査カウンタ $\times$ の値から1を減算する (S 2 0 9)。このように、拡大させる変倍処理のときは、通常時に出力すべき画像の代わりに1つ前の画像を再度出力して、次以降の画像を遅らせて出力する処理を行う。10

#### 【0040】

ステップS 2 0 6の処理において、一致しない場合 (S 2 0 6 : n o)、CPU50は、主走査カウンタ $\times$ の値に基づき、現在の主走査位置に該当する画素を入力された1ライン分の画像データから決定して、これを出力する (S 2 1 0)。主走査カウンタ $\times$ の値が負である場合、あるいは、入力された画像データサイズ以上となった場合、CPU50は、転写部材上にトナーが載らないような画像データ値を出力する。

なお、主走査変倍処理では、ステップS 2 0 1の処理で算出されたエリア毎に乱数値を生成する。エリアが切り替わった直後に乱数値を生成させ、同一エリア内ではこの乱数値を使用する。よって、エリアが切り替わった直後に生成された乱数値をRAM 2 0 1に記録する。20

#### 【0041】

CPU50は、ステップS 2 1 0の処理で画像を1画素出力した後、次の画素の処理に移行すべく、主走査カウンタ $\times$ の値に1を加算する (S 2 1 1)。CPU50は、また、次の画素の処理に移行すべくエリアカウンタh\_e c n tの値に1を加算する (S 2 1 2)。

その後、CPU50は、処理対象となる次の画素が新しいエリアのものか否かを判定する (S 2 1 3)。具体的には、エリアカウンタh\_e c n tの値と主走査エリア長h\_1 e nの値を比較する。その結果、エリアカウンタh\_e c n tの値が、主走査エリア長h\_1 e nの値を越えた場合 (S 2 1 3 : y e s)、CPU50は、新しいエリアへ移行したと判定しエリアカウンタh\_e c n tを初期化 (h\_e c n t = 0) する (S 2 1 4)。30

#### 【0042】

エリアカウンタh\_e c n tの値が、主走査エリア長h\_1 e nの値を越えていない場合 (S 2 1 3 : N o)、CPU50は、入力された主走査1ラインの画像データの全てに対して処理したか否かを判定する (S 2 1 5)。具体的には、エリアカウンタh\_e c n t = 0となった回数が、ステップS 2 0 1の処理で算出した差分画素に1加算した回数現れたか否かで判定する。また、エリアが切り替わる毎にエリアカウンタh\_e c n tは初期化される。そのため、エリア切り替わり回数が、差分画素に1加算した回数現れていれば、全てのエリアの処理が終了したことになる。全てのエリアの処理が終了した場合 (S 2 1 5 : y e s)、ステップS 1 0 4の処理を終了する。なお、ステップS 2 1 5の処理における判定は、主走査カウンタ $\times$ の値が、主走査変倍後の主走査方向の画像サイズに到達したか否か判定するようにして構わない。全てのエリアの処理が終了していない場合 (S 2 1 5 : n o)、CPU50は、ステップS 2 0 4の処理へ戻り、処理を繰り返す。40

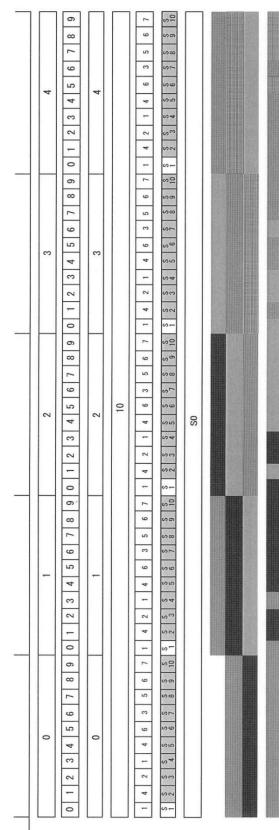

#### 【0043】

図6は、図5で示したステップS 2 0 1からステップS 2 1 5の処理における主走査変倍処理のタイミングチャートである。図6は、また、実際の入出力画像の一部を視覚的に表している。図6(a)は、入力された1ライン分の画像データである。図6(a)では、主走査カウンタ $\times$ 、主走査エリア長h\_1 e n、ハッチング処理された四角それぞれが入力画像の1画素を表しており、それぞれの関係を示している。図6(b)は、処理後に50

出力された 1 ライン分の画像データである。図 6 ( b ) では、乱数値  $r_{nd\_x}$ 、エリアカウンタ  $h\_ecnt$ 、主走査カウンタ  $x$ 、ハッチング処理された四角それぞれが出力画像 1 画素を表しており、それぞれの関係を示している。

図 6 ( b ) に示すように、エリア 1 では、生成された乱数値  $r_{nd\_x}$  の値が「 3 」であるため、エリアカウンタ  $h\_ecnt$  の値が「 3 」のときに、ステップ S 209 の処理において主走査カウンタ  $x$  の値から「 1 」が減算される。そのため、出力画像データは、主走査カウンタ  $x = 2$  のものが 2 画素連続で出力される。エリア 2 では、エリアカウンタ  $h\_ecnt = 5$  の箇所で、また、エリア 3 では、エリアカウンタ  $h\_ecnt = 2$  の箇所で同様の処理となっている。ステップ S 201 の処理において算出された差分画素数は 10 画素であるため、同様の処理をエリア 10 まで行った後に、主走査変倍処理を終了する。

10

#### 【 0044 】

次に、図 4 で示したステップ S 107、S 108、S 109 の副走査変倍処理の詳細について説明する。

ステップ S 107 の処理において、CPU50 は、副走査変倍処理で使用する各パラメータの初期化を行う。具体的には、副走査位置カウンタ  $y$  の初期化 ( $y = 0$ )、副走査エリア位置カウンタ  $v\_ecnt$  の初期化 ( $v\_ecnt = 0$ )、シード値保持部 51 に記録されているシード値  $seed$  (後述) の初期化を行う。また、CPU50 は、副走査エリア長  $v\_len$  を算出する。副走査エリア長  $v\_len$  は、入力画像サイズと副走査変倍後の画像サイズの差分を算出し、副走査入力画像サイズを差分画素数の絶対値で除算した値である。

20

本実施形態では、副走査入力画像サイズは 100 画素、副走査方向の伸縮率 10 [ % ] 拡大であるため、副走査変倍後の副走査方向の画像サイズは  $100 + 100 \times 10 [ \% ] = 110$  画素、差分画素数は  $110 - 100 = 10$  となる。よって、副走査エリア長  $v\_len$  は、 $v\_len = 100 / 10 = 10$  となる。CPU50 は、副走査エリア長  $v\_len$  の値に基づいて、入力された 1 ライン分の画像データを副走査方向に分割して複数のエリア (領域) にする。分割されたそれぞれのエリアが一つの処理単位となり、エリア毎に副走査変倍処理を行う。

#### 【 0045 】

ここで、乱数値について詳しく説明する。本実施形態では、乱数値を生成するために、M 系列の原始多項式を利用した疑似乱数値発生回路を使用する。図 7 は、16 次の原始多項式を回路化した乱数値発生回路 52 を模式的に示した図である。

30

乱数値発生回路 52 は、16 個の 2 値データの記録素子を縦列接続するとともに、いずれかの記録素子間に 3 つの論理演算回路を介在させて構成される。複数個の記録素子を、それぞれ  $bit$  (ビット) 15 から  $bit0$  (図 7 中では、15、14・・・と示している) と定義する。また、 $bit14$  と  $bit13$ 、 $bit13$  と  $bit12$ 、 $bit11$  と  $bit10$  の間には、それぞれ論理演算回路の一例である EXOR ゲートが介在する。シード値は、乱数値の種となるもので、乱数値発生回路 52 の各  $bit$  の 2 値データの集合として定義される。

40

#### 【 0046 】

図 7 において、乱数値発生回路 52 のシード値は「 1111011011001001 」である。例えば、出力される乱数値は、このシード値の  $bit2$  から  $bit0$  の出力で決定される。図 7 において、 $bit2$  から  $bit0$  の値を順に並べると、「 001 」となる。これを 10 進数化することにより、乱数値「 1 」が生成される。乱数値を再度生成したい場合は、記録素子が保持する 2 値データをそれぞれ所定方向に隣接する他の記録素子に移行させ、これにより変化したシード値に基づいて次の乱数値を生成する。具体的には、乱数値発生回路 52 のシード値を右側にシフトさせる。乱数値発生回路 52 のシード値を右側にシフトさせて、乱数値を再度生成するときの具体的な手順は以下の通りである。

#### 【 0047 】

( a )  $bit0$  の値を一時変数  $temp$  (図示省略) に保存する。

50

- ( b ) bit 0 の値に bit 1 の値を代入する。

- ( c ) bit 1 の値に bit 2 の値を代入する。

- ( d ) bit 2 の値に bit 3 の値を代入する。

- ( e ) bit 3 の値に bit 4 の値を代入する。

- ( f ) bit 4 の値に bit 5 の値を代入する。

- ( g ) bit 5 の値に bit 6 の値を代入する。

- ( h ) bit 6 の値に bit 7 の値を代入する。

- ( i ) bit 7 の値に bit 8 の値を代入する。

- ( j ) bit 8 の値に bit 9 の値を代入する。

- ( k ) bit 9 の値に bit 10 の値を代入する。

- ( l ) bit 10 の値に一時変数 temp と bit 11 の EXOR 値を代入する。

- ( m ) bit 11 の値に bit 12 の値を代入する。

- ( n ) bit 12 の値に一時変数 temp と bit 13 の EXOR 値を代入する。

- ( o ) bit 13 の値に一時変数 temp と bit 14 の EXOR 値を代入する。

- ( p ) bit 14 の値に bit 15 の値を代入する。

- ( q ) bit 15 の値に一時変数 temp の値を代入する。

このように、( a ) から ( q ) まで処理されて、次の乱数値が生成される。

#### 【 0 0 4 8 】

図 8 は、シフト後の乱数値発生回路 5 2 のシード値を示している。シフト後の bit 2 から bit 0 の値を用いて乱数値を生成する。bit 2 から bit 0 までの値を順に並べると、「1 0 0」となる。これを 10 進数化することにより、乱数値「4」が生成される。乱数値発生回路 5 2 は、初期のシード値から論理演算で順次乱数値を算出する。そのため、シード値を決定すれば、以降に生成される乱数値が一意に再現することができる。本実施形態では、乱数値発生回路 5 2 から 3 つの bit を取り出して乱数値を生成している。そのため、生成される乱数値の範囲は、「0」から「7」までのいずれかの値となる。

#### 【 0 0 4 9 】

例えば、より広範囲の乱数値を取得したい場合、乱数値発生回路 5 2 から取り出す bit 数を増やせば良い。例えば、3 つの bit を取り出しているところを、4 つの bit を取り出すようにすることで、生成される乱数値の範囲は「0」から「15」までのいずれかの値となる。また、生成したい乱数値の上限が 2 の乗数 - 1 (「-」はマイナス) でない場合、範囲外の乱数値が生成された場合などには、再度シード値のシフトを行い、範囲内の乱数値が生成されるまでシフトを繰り返せば良い。例えば、「0」から「3」の範囲内で乱数値を生成したい場合の例を考える。図 8 の時点で生成された乱数値は「4」であり、範囲外の値である。そこで、シード値をもう一度シフトすると、図 9 に示すような乱数値発生回路 5 2 のシード値となる。再度のシフト後の乱数値発生回路 5 2 が生成する乱数値は「2」になり、「0」から「3」の範囲内であるため、この値を乱数値として使用する。

#### 【 0 0 5 0 】

図 10 は、図 4 で示したステップ S 1 0 8 の副走査方向の変倍処理の具体的な処理手順を示したフロー チャートである。

CPU50 は、フレームバッファ 5 4 から、副走査位置カウンタ  $y - 1$ 、 $y$ 、 $y + 1$  それぞれに該当する 1 ライン分の画像データを、ラインバッファ 5 3 の各領域 (line\_buf 1、line\_buf 2、line\_buf 3) に転送する (S 3 0 1)。なお、副走査位置カウンタ  $y - 1$ 、 $y$ 、 $y + 1$  が、画像データ外のラインを示すときには、データ 0 (ゼロ) が取得される。データ 0 は、転写部材上にトナー像を形成しないデータである。

#### 【 0 0 5 1 】

CPU50 は、主走査位置カウンタ  $x_c$  を初期化 ( $x_c = 0$ ) する (S 3 0 2)。主走査位置カウンタ  $x_c$  は、入力された主走査方向画像データの中から、出力すべき画像データの主走査位置を示す。

10

20

30

40

50

CPU50は、副走査エリアが切り替わり、新しいエリアの処理に移行したか否かを判定する(S303)。副走査エリアが切り替わった(v\_e\_c\_n\_t = 0)場合(S303:y\_e\_s)、CPU50は、そのときの乱数値発生回路52のシード値をシード値保持部51に記録する。つまり、新しい副走査エリアにおいて処理が開始される直前のシード値を、シード値保持部51に記録する(S304)。

副走査エリアが切り替わっていない場合(S303:n\_o)、CPU50は、シード値保持部51に記録されているシード値を読み込む(S305)。つまり、一の副走査エリアでの処理が継続している間は、シード値保持部51に記録されているシード値が読み込まれる。

#### 【0052】

10

CPU50は、乱数値発生回路52に指示を出し、ステップS304の処理において記録したシード値、又は、ステップ305の処理において読み込んだシード値いずれかに基づいて、当該エリアの処理開始前に、乱数値rnd\_vを生成させる(S306)。

その後、CPU50は、生成された乱数値rnd\_vの値が、副走査エリア位置カウンタv\_e\_c\_n\_tの値以下か否かを判定する(S307)。乱数値rnd\_vの値が、副走査エリア位置カウンタv\_e\_c\_n\_tの値以下の場合(S307:y\_e\_s)、変倍処理を行う必要があるため、CPU50は、画像データに施す変倍処理が縮小させるものか、又は、拡大させるものかを判定する(S308)。縮小させる場合(S308:y\_e\_s)、CPU50は、出力画像ラインy'の値として、副走査位置カウンタyの値に1を加算した値を代入する(S309)。拡大させる場合(S308:n\_o)、CPU50は、出力画像ラインy'の値として、副走査位置カウンタyの値から1を減算した値を代入する(S310)。

20

乱数値rnd\_vの値が、副走査エリア位置カウンタv\_e\_c\_n\_tの値を超える場合(S307:n\_o)、CPU50は、出力画像ラインy'の値として、副走査位置カウンタyの値を代入する(S311)。

#### 【0053】

その後、CPU50は、配列された画素の中から、主走査位置カウンタx\_cの値と出力画像ラインy'の値から特定された位置の画素を、ラインバッファ53の所定の領域から読み込んで出力する(S312)。出力画像ラインy'は、ラインバッファ53の領域選択に用いられる。具体的には、ステップS309の処理を経由する場合、ラインバッファ53の領域l\_i\_n\_e\_b\_u\_f\_3が参照される。また、ステップS310の処理を経由する場合、ラインバッファ53の領域l\_i\_n\_e\_b\_u\_f\_1が参照される。さらに、ステップS311の処理を経由する場合、ラインバッファ53の領域l\_i\_n\_e\_b\_u\_f\_2が参照される。主走査位置カウンタx\_cは、ラインバッファ中の主走査方向で画素の特定に用いられる。

30

#### 【0054】

CPU50は、主走査位置の更新のため、主走査位置カウンタx\_cの値に1を加算する(S313)。そして、CPU50は、主走査位置カウンタx\_cの値に基づき、主走査終了か否か、すなわち主走査サイズ全ての出力が完了されたか否かを判定する(S314)。主走査サイズは、入力画像サイズではなく、主走査方向の変倍が行われた後の画像サイズである。本実施形態では、主走査方向の入力画像が100画素、伸縮率が10[%]拡大であるから、主走査方向の変倍後の画素数は110画素である。よって、主走査位置カウンタx\_cの値がx\_c = 110に到達したときに、主走査サイズ全ての出力が完了したと判定する。

40

CPU50は、完了していないと判定した場合(S314:n\_o)、ステップS306の処理へ戻り、処理を繰り返す。また、CPU50は、完了したと判定した場合(S314:y\_e\_s)、副走査位置の更新のため、副走査位置カウンタyの値に1を加算する(S315)。そして、副走査エリア位置の更新のため、CPU50は、副走査エリア位置カウンタv\_e\_c\_n\_tの値に1を加算する(S316)。

#### 【0055】

50

その後、CPU50は、副走査エリア内の処理が完了したか否かを判定する(S317)。具体的には、伸縮率が拡大方向である場合、副走査エリア位置カウンタv\_e\_c\_n\_tの値が、副走査エリア長v\_l\_e\_nの値に1を加算した値と等しくなったことを検出し、処理が完了したと判定する。また、伸縮率が縮小方向である場合、副走査エリア位置カウンタv\_e\_c\_n\_tの値が、副走査エリア長v\_l\_e\_nの値から1を減算した値と等しくなったことを検出し、処理が完了したと判定する。伸縮率が0[%]である場合、副走査エリア位置カウントv\_e\_c\_n\_tの値が、副走査エリア長v\_l\_e\_nの値と等しくなったことを検出し、処理が完了したと判定する。

副走査エリア内の処理が完了した場合(S317:y\_e\_s)、CPU50は、副走査エリア位置を初期化(v\_e\_c\_n\_t=0)する(S318)。そうでない場合(S317:n\_o)、処理を終了する。

10

#### 【0056】

CPU50は、変倍処理していなければ(S319:n\_o)、処理を終了する。変倍処理している場合(S319:y\_e\_s)、CPU50は、変倍処理が縮小方向であるか、又は、拡大方向であるかを判定する(S320)。拡大方向である場合(S320:n\_o)、副走査位置カウンタyの値に1を加算(y=y+1)する(S322)。また、縮小方向である場合(S320:y\_e\_s)、CPU50は、副走査位置カウンタyの値から1を減算(y=y-1)する(S321)。このようにして、CPU50によりステップS108の処理が行われる。

#### 【0057】

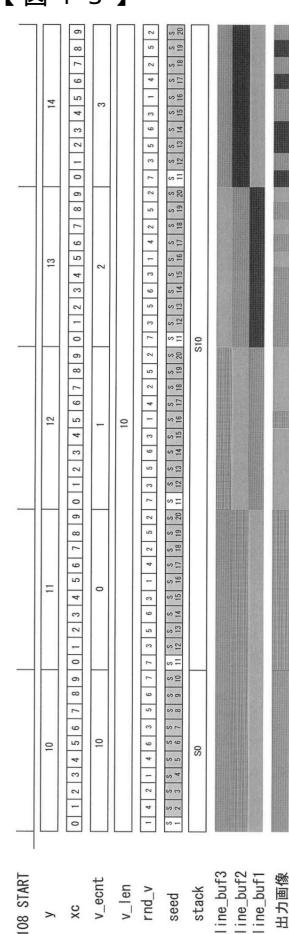

図11、図12、図13は、ステップS107からステップS109の副走査方向の変倍処理のタイミングチャートである。副走査位置カウンタy=4までのタイミングチャートが図11、副走査位置カウンタy=9までのタイミングチャートが図12、副走査位置カウンタy=4までのタイミングチャートが図13である。また、図11、図12、図13それぞれは、実際の入出力画像の一部を視覚的に表している。

なお、フレームバッファ54には、図14に示すような主走査画素数10、副走査画素数18の画像データが記録されているものとする。また、副走査方向の変倍率は10[%]拡大とする。

#### 【0058】

図11、図12、図13では、合わせて、副走査位置カウンタy=14までのタイミングチャートまで例示しているが、画像処理装置110の動作としては、この後も処理が継続する。図11、図12、図13それぞれに示す「S108 START」は、主走査同期信号が出力されるタイミングを示す。また、「seed」のS0からS20は、それぞれシード値を示し、「stack」のS0、S10は、シード値保持部51に記録されているシード値を示す。図11、図12、図13それぞれに示す「line\_buf1」、「line\_buf2」、「line\_buf3」は、ラインバッファ53の各領域に記録された画像データを視覚的に表している。

30

図11、図12、図13それぞれに示す「出力画像」は、変倍処理後に outputされる画像データを視覚的に表している。変倍処理後に outputされる画像データを、1ラインずつつなぎあわせると、図15に示すような変倍処理後の画像が得られる。この様にして、フレームバッファ54に記録された画像データが拡大処理される。

40

#### 【0059】

このように、本実施形態の画像処理装置110では、同じエリア内の画像処理においては、シード値保持部51に記録されたシード値に基づいて乱数値発生回路52が乱数値を生成する。これにより、乱数値を記録するためのメモリを省略することができる。

また、主走査方向の主走査位置毎にどの副走査位置で1画素挿入又は1画素削除するかを記憶しておく方式に比べて、搭載すべきメモリの容量が低減されるため、画像処理装置の製造コストの低減を図ることができる。

さらに、各主走査位置において必ず1画素挿入又は1画素削除される補正処理となるため、所定範囲内ないしページ全体において、過剰に画素の挿入又は画素の削除がされてし

50

まう主走査位置の発生を抑止することができる。これにより、画像を拡大又は縮小するときの画質の低下を抑制することができる。

〔 0 0 6 0 〕

上記説明した実施形態は、本発明をより具体的に説明するためのものであり、本発明の範囲が、これらの例に限定されるものではない。

## 【符号の説明】

〔 0 0 6 1 〕

1・・・原稿給紙装置、2・・・原稿台ガラス面、3・・・ランプ、4・・・スキャナユニット、5、6、7・・・ミラー、8・・・集光部、9・・・イメージセンサ部、100・・・露光制御部、11・・・感光体、13・・・現像器、14、15・・・転写部材積載部、16・・・転写部、17・・・定着部、18・・・排紙部、20・・・フラッパー、21・・・排出通路、22・・・反転通路、23・・・反転搬送路入口、24・・・反転搬送路、25・・・クリーナ、26・・・補助帶電器、27・・・露光ランプ、28・・・1次帶電器、31・・・レーザ駆動装置、32・・・絞り、33・・・ポリゴンミラー、34・・・f-レンズ、35・・・コリメータレンズ、36・・・B Dセンサ、43・・・半導体レーザ、50・・・画像処理C P U、51・・・シード値保持部、52・・・乱数値発生回路、53・・・ラインバッファ、54・・・フレームバッファ、55・・・L U T、100・・・電位センサ、110・・・画像処理装置、111・・・原稿給送部、112・・・画像読み取り部、113・・・画像形成部。

( 1 )

〔 四 2 〕

( 3 )

【図4】

【図5】

【図7】

【図8】

【図9】

【図10】

【図 1 6】

【図 6】

(a) 入力されたライン画像データ

(b) 出力されたライン画像データ

【図 1 2】

【図 1 1】

【図 1 3】

【図14】

【図15】

【図17】

【図18】

【図19】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

H 04 N      1 / 393

G 06 T      3 / 40