(12)

## Patentschrift

(21) Aktenzeichen: 10 2016 201 542.7

(51) Int Cl.: **H03B 19/14 (2006.01)**

(22) Anmelddatum: 02.02.2016

(43) Offenlegungstag: 18.08.2016

(45) Veröffentlichungstag

der Patenterteilung: 14.10.2021

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

**2015-026705** 13.02.2015 JP

(72) Erfinder:

**Kurusu, Hitoshi, Tokyo, JP; Tsukahara, Yoshihiro, Tokyo, JP**

(73) Patentinhaber:

**Sonrai Memory Ltd., Dublin, IE**

(56) Ermittelter Stand der Technik:

(74) Vertreter:

**Peterreins Schley Patent- und Rechtsanwälte

PartG mbB, 80331 München, DE**

US 2002 / 0 024 411 A1

JP 2010- 16 532 A

(54) Bezeichnung: **Frequenzvervielfacher**

(57) Hauptanspruch: Frequenzvervielfacher, aufweisend:

einen Eingangsanschluss (T1);

einen Ausgangsanschluss (T2);

einen ersten Transistor (Tr1), der einen ersten Gate-Anschluss (G1), an den ein Hochfrequenzsignal von dem Eingangsanschluss (T1) angelegt wird, einen ersten Drain-Anschluss (D1), von dem ein Ausgangssignal an den Ausgangsanschluss (T2) ausgegeben wird, und einen ersten Source-Anschluss (S1) aufweist;

einen zweiten Transistor (Tr2), der einen zweiten Gate-Anschluss (G2), einen zweiten Source-Anschluss (S2), an den ein Hochfrequenzsignal von dem Eingangsanschluss (T1) angelegt wird, und einen zweiten Drain-Anschluss (D2), von dem ein Ausgangssignal an den Ausgangsanschluss (T2) ausgegeben wird, aufweist; und

einen stabilisierenden Widerstand (26), der ein Widerstand ist, der mit dem zweiten Gate-Anschluss (G2) verbunden ist, wobei kein Widerstand in dem Pfad für das Hochfrequenzsignal vorhanden ist, und

wobei der stabilisierende Widerstand (26) eine Reflexionsverstärkung unterdrückt, die von dem zweiten Transistor (Tr2) erzeugt wird.

**Beschreibung**

## Hintergrund der Erfindung

## Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung betrifft einen Frequenzvervielfacher, der eine elektrische Leistung zum Beispiel in einem Mikrowellen- oder einem Millimeter-Wellen-Hochfrequenzband vervielfacht.

## Stand der Technik

**[0002]** Das offengelegte, japanische Patent JP H03 - 158 008 A offenbart einen Frequenzvervielfacher, in dem ein Transistor mit einem an eine Masse angeschlossenen Source-Anschluss und ein Transistor mit einem an Masse angeschlossenen Gate-Anschluss parallel miteinander verbunden sind. Von einer elektrischen Leistung einer in diesen Frequenzvervielfacher gegebenen Grundfrequenz, gibt der Transistor mit dem an Masse angeschlossenen Source-Anschluss eine elektrische Leistung in der Gegenphase und der Transistor mit dem an Masse angeschlossenen Gate-Anschluss gibt eine elektrische Leistung in Phase mit dem Eingangssignal aus. Deshalb löschen sich diese elektrischen Leistungen aus, wenn sie auf der Ausgangsseite kombiniert werden. Elektrische Leistungen einer harmonischen Frequenz der zweiten Ordnung, die in Phase miteinander von den zwei Transistoren ausgegeben werden, werden von einem Ausgangsanschluss abgenommen.

**[0003]** Das offengelegte, japanische Patent JP 2001 - 244 746 A offenbart die Bereitstellung von Dämpfungswiderständen für eine Stabilisierung auf den Ausgangsseiten der zwei Transistoren.

**[0004]** Der Frequenzvervielfacher, der in dem offengelegten, japanischen Patent JP H03 - 158 008 A offenbart wird, hat ein Problem, dass eine Schwingung aufgrund einer negativen Widerstandscharakteristik des Transistors mit dem an Masse angeschlossenen Gate-Anschluss auftritt, die sich in einem Hochfrequenzband wie einem Mikrowellenband oder Millimeter-Wellen-Band zeigt.

**[0005]** Der Frequenzvervielfacher, der in dem offengelegten, japanischen Patent JP 2001 - 244 746 A offenbart wird, hat ein Problem, dass eine elektrische Leistung der harmonischen Frequenz zweiter Ordnung, die von den Transistoren erzeugt wird, von den Dämpfungswiderständen verbraucht wird und eine Umsetzungsverstärkung, die eine Eigenschaft des Frequenzvervielfachers ist, reduziert wird. US 2002 / 024 411 A1 und JP 2010 - 16 532 A offenbaren Frequenzvervielfacherschaltungen. Im Unterschied zu den Merkmalen des Gegenstands nach Hauptanspruch 1 ist in US 2002 / 024 411 A1 und JP 2010 - 16 532 A jedoch nicht beschrieben, dass „ein stabilisierender Widerstand ... mit dem zweiten Gate-Anschluss verbunden ist, ...wobei der stabilisierende Widerstand eine Reflexionsverstärkung unterdrückt, die von dem zweiten Transistor erzeugt wird“. US 2002 / 024 411 A1 und JP 2010 - 16 532 A offenbaren andere Mittel zur Unterdrückung von Reflexionen.

## Zusammenfassung der Erfindung

**[0006]** Die vorliegende Erfindung ist verwirklicht worden, um die vorstehend beschriebenen Probleme zu lösen, und eine Aufgabe der vorliegenden Erfindung ist, einen Frequenzvervielfacher zur Verfügung zu stellen, der in der Lage ist, Instabilitäten wie eine negative Widerstandscharakteristik, die durch einen Transistor mit einem an Masse angeschlossenen Gate-Anschluss gezeigt wird, zu reduzieren, ohne einen Widerstand vorzusehen, durch den eine Hochfrequenz hindurchtritt.

**[0007]** Die Merkmale und Vorteile der vorliegenden Erfindung können wie folgt zusammengefasst werden.

**[0008]** Gemäß einem Aspekt der vorliegenden Erfindung weist ein Frequenzvervielfacher einen Eingangsanschluss, einen Ausgangsanschluss, einen ersten Transistor, der einen ersten Gate-Anschluss, an den ein Hochfrequenzsignal von dem Eingangsanschluss angelegt wird, einen ersten Drain-Anschluss, von dem ein Ausgangssignal an den Ausgangsanschluss ausgegeben wird, und einen ersten Source-Anschluss aufweist, einen zweiten Transistor, der einen zweiten Gate-Anschluss, einen zweiten Source-Anschluss, an den das Hochfrequenzsignal von dem Eingangsanschluss angelegt wird, und einen zweiten Drain-Anschluss, von dem ein Ausgangssignal an den Ausgangsanschluss ausgegeben wird, aufweist, und einen stabilisierenden Widerstand auf, der ein mit dem zweiten Gate-Anschluss verbundener Widerstand ist, wobei kein Widerstand in dem Pfad für das Hochfrequenzsignal vorhanden ist, und wobei der stabilisierende Widerstand eine Reflexionsverstärkung unterdrückt, die durch den zweiten Transistor erzeugt wird.

**[0009]** Andere und weitere Aufgaben, Merkmale und Vorteile der Erfindung werden aus der nachfolgenden Beschreibung ersichtlicher.

#### Figurenliste

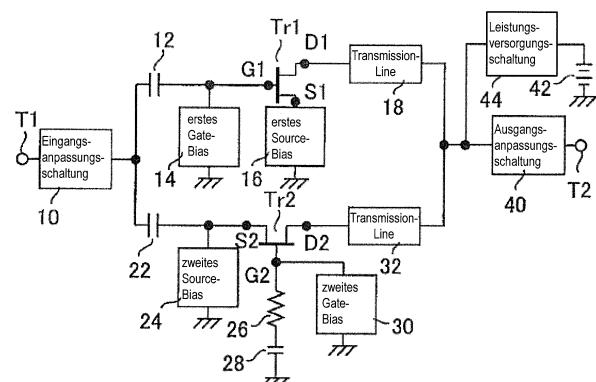

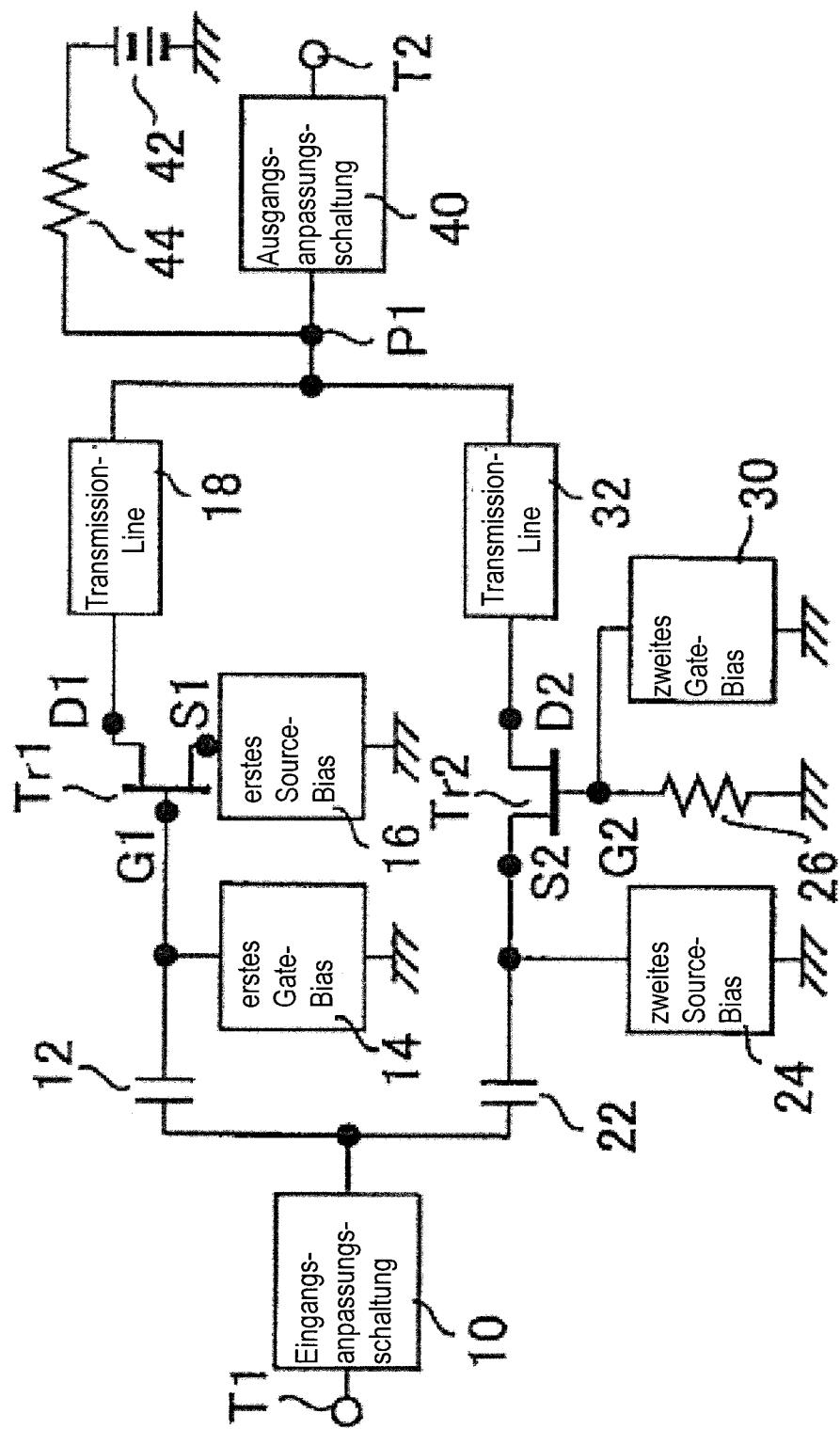

**Fig. 1** ist ein Schaltbild eines Frequenzvervielfachers gemäß einer ersten Ausführungsform;

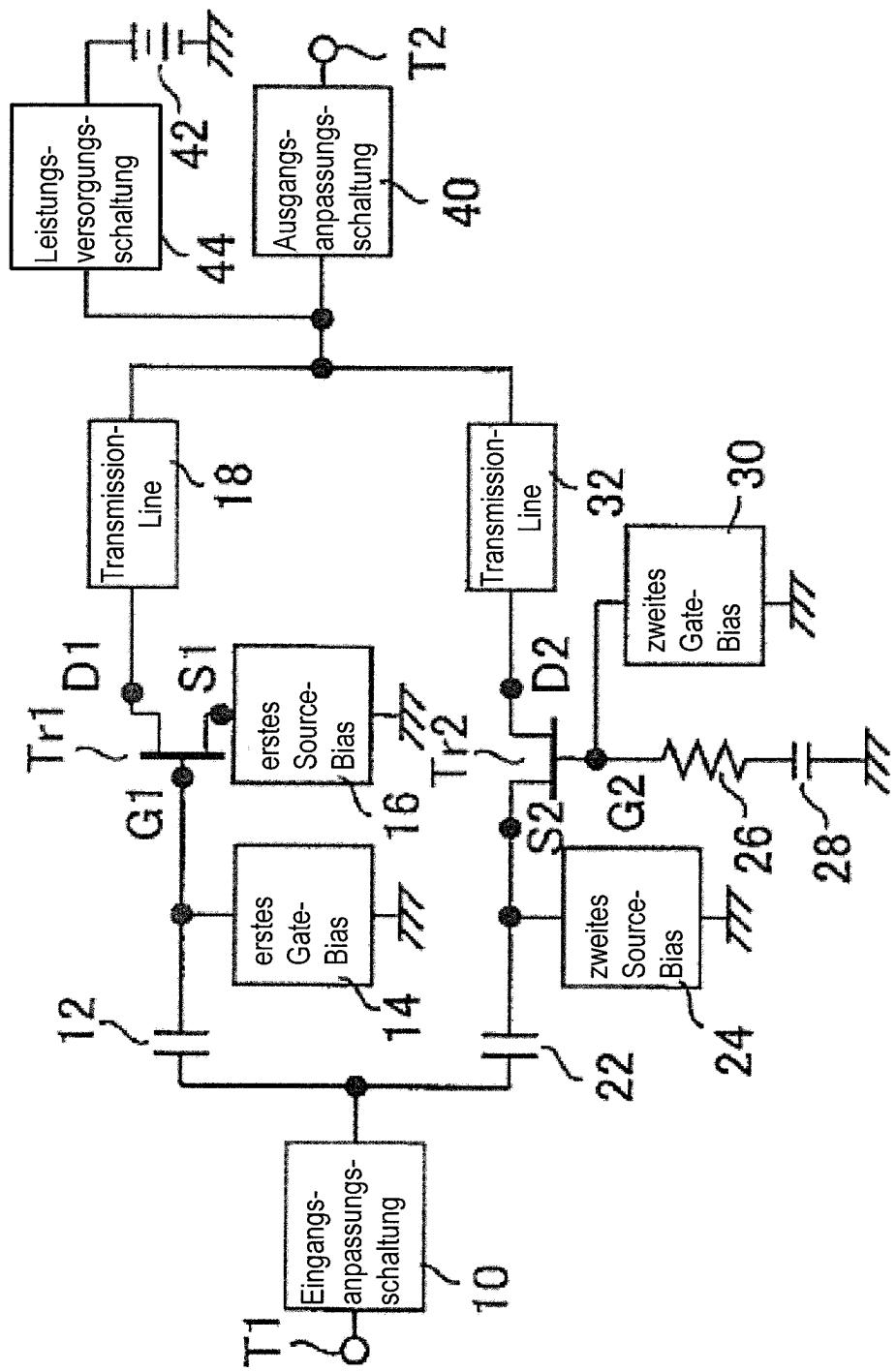

**Fig. 2** ist ein Schaltbild eines Frequenzvervielfachers gemäß der zweiten Ausführungsform;

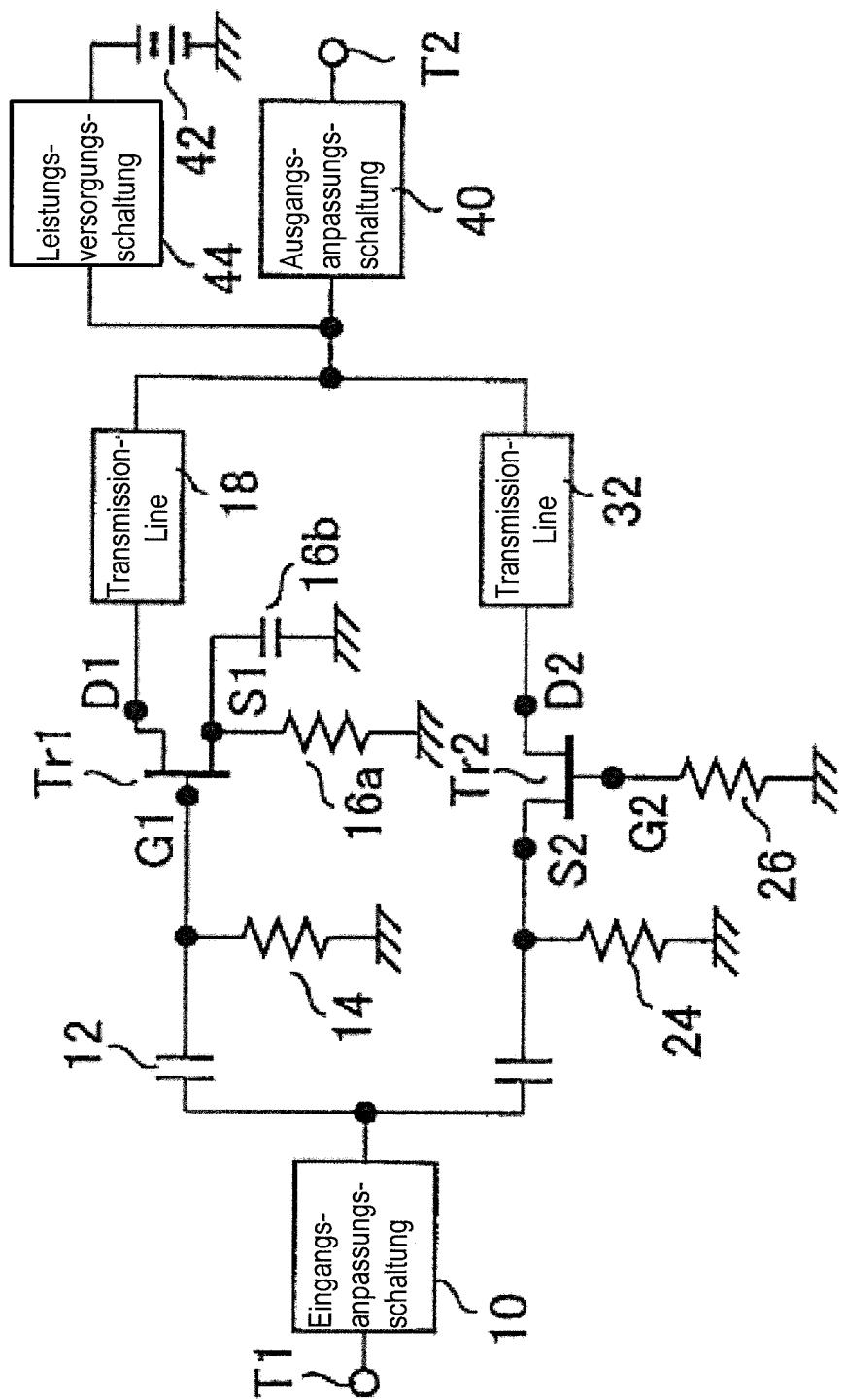

**Fig. 3** ist ein Schaltbild eines Frequenzvervielfachers gemäß der dritten Ausführungsform; und

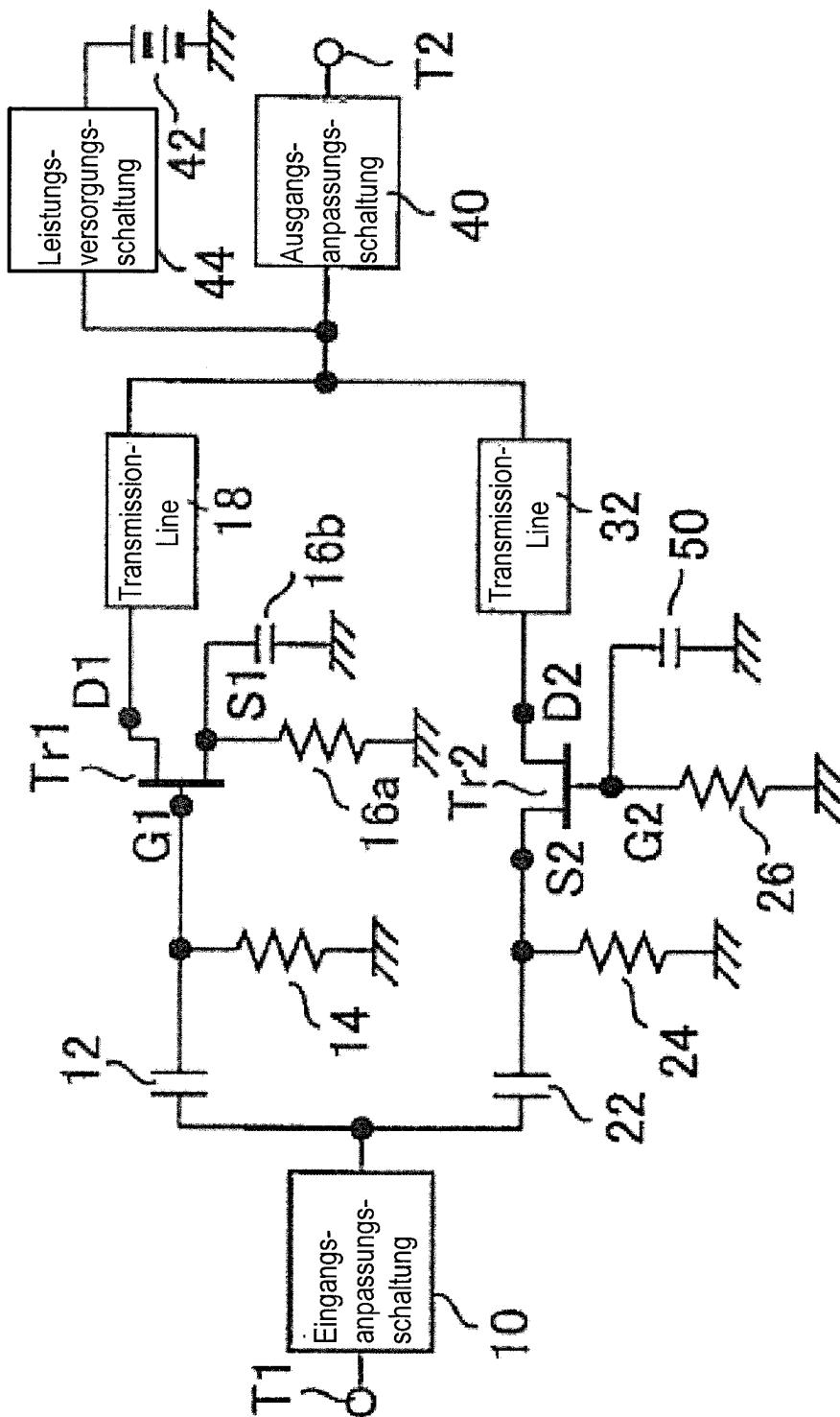

**Fig. 4** ist ein Schaltbild eines Frequenzvervielfachers gemäß der vierten Ausführungsform.

#### Detaillierte Beschreibung der bevorzugten Ausführungsformen

**[0010]** Ein Frequenzvervielfacher gemäß einer Ausführungsform der vorliegenden Erfindung wird unter Bezugnahme auf die Zeichnungen beschrieben. Komponenten, die identisch sind oder zueinander korrespondieren, werden durch die gleichen Bezugszeichen gekennzeichnet, und eine wiederholte Beschreibung für sie wird in einigen Fällen weggelassen.

#### Erste Ausführungsform

**[0011]** **Fig. 1** ist ein Schaltbild eines Frequenzvervielfachers gemäß einer ersten Ausführungsform der vorliegenden Erfindung. Dieser Frequenzvervielfacher vervielfacht die Frequenz eines Hochfrequenzsignals, das an einen Eingangsanschluss **T1** angelegt wird, um ein ganzzahliges Vielfaches und gibt das resultierende Signal durch einen Ausgangsanschluss **T2** aus. Eine Eingangsanpassungsschaltung **10** ist mit dem Eingangsanschluss **T1** verbunden. Eine Ausgangsanpassungsschaltung **40** ist mit dem Ausgangsanschluss **T2** verbunden.

**[0012]** Der Frequenzvervielfacher gemäß der ersten Ausführungsform weist einen ersten Transistor **Tr1**, der ein Transistor mit einem an Masse angeschlossenen Source-Anschluss ist, und einen zweiten Transistor **Tr2**, der ein Transistor mit einem an Masse angeschlossenen Gate-Anschluss ist, auf. Der erste Transistor **Tr1** weist einen ersten Gate-Anschluss **G1**, an den ein Hochfrequenzsignal von dem Eingangsanschluss **T1** angelegt wird, einen ersten Drain-Anschluss **D1**, von dem ein Ausgangssignal an den Ausgangsanschluss **T2** ausgegeben wird, und einen ersten mit Masse verbundenen Source-Anschluss **S1** auf.

**[0013]** Der erste Gate-Anschluss **G1** ist durch einen gleichstromblockierenden Kondensator **12** mit der Eingangsanpassungsschaltung **10** verbunden. Eine erste Gate-Bias-Schaltung **14** ist zwischen dem ersten Gate-Anschluss **G1** und einem mit Masse verbindenden Leiter angeschlossen. Eine erste Source-Bias-Schaltung **16** ist zwischen dem ersten Source-Anschluss **S1** und einem mit Masse verbindenden Leiter angeschlossen. Der erste Drain-Anschluss **D1** ist durch eine Transmission-Line **18** mit der Ausgangsanpassungsschaltung **40** verbunden.

**[0014]** Der zweite Transistor **Tr2** weist einen zweiten Gate-Anschluss **G2**, einen zweiten Source-Anschluss **S2**, an den ein Hochfrequenzsignal von dem Eingangsanschluss **T1** angelegt wird, und einen zweiten Drain-Anschluss **D2**, von dem ein Ausgangssignal an den Ausgangsanschluss **T2** ausgegeben wird, auf.

**[0015]** Der zweite Source-Anschluss **S2** ist durch einen gleichstromblockierenden Kondensator **22** mit der Eingangsanpassungsschaltung **10** verbunden. Eine zweite Source-Bias-Schaltung **24** ist zwischen dem zweiten Source-Anschluss **S2** und einem mit Masse verbindenden Leiter angeschlossen. Ein stabilisierender Widerstand **26**, d.h. ein Widerstand und ein Kondensator **28** sind zwischen dem zweiten Gate-Anschluss **G2** und der Masse angeschlossen. Weiter ist eine zweite Gate-Bias-Schaltung **30** zwischen dem zweiten Gate-Anschluss **G2** und einem mit Masse verbindenden Leiter angeschlossen. Der zweite Drain-Anschluss **D2** ist durch eine Transmission-Line **32** mit der Ausgangsanpassungsschaltung **40** verbunden.

**[0016]** Eine Leistungsversorgungsschaltung **44**, die mit einer Leistungsversorgung **42** verbunden ist, ist mit Ausgangsseiten der Transmission-Lines **18** und **32** verbunden. Wie aus **Fig. 1** ersichtlich ist, ist in den Hochfrequenzsignalpfaden von dem Eingangsanschluss **T1** zu dem Ausgangsanschluss **T2** kein Widerstand vorhanden.

**[0017]** Der Betrieb des Frequenzvervielfachers gemäß der ersten Ausführungsform der vorliegenden Erfindung wird nachfolgend beschrieben. Die Bias-Spannung zwischen dem Gate-Anschluss und dem Source-Anschluss des ersten Transistors **Tr1** wird in der Nähe der Abschneidspannung des ersten Transistors **Tr1** einge-

stellt. Die Bias-Spannung zwischen dem Gate-Anschluss und dem Source-Anschluss des zweiten Transistors **Tr2** wird in der Nähe der Abschnürspannung des zweiten Transistors **Tr2** eingestellt.

**[0018]** Wenn ein Hochfrequenzsignal (sinusförmige Wellenform) an den Eingangsanschluss **T1** angelegt wird, gibt der erste Transistor **Tr1** eine gleichgerichtete positive Halbwelle aus und der zweite Transistor **Tr2** gibt eine gleichgerichtete negative Halbwelle mit der invertierten Polarität aus. Die Grundwelle und ungerade Harmonische, die in dem von dem Drain-Anschluss des ersten Transistors **Tr1** ausgegebenen Signal enthalten sind, und diejenigen, die in dem von dem Drain-Anschluss des zweiten Transistors **Tr2** ausgegebenen Signal enthalten sind, sind zueinander gegenphasig und heben einander deshalb auf. Gerade Harmonische, die von den Drain-Anschlüssen des ersten und des zweiten Transistors **Tr1** und **Tr2** ausgegeben werden, liegen in Phase zueinander und verstärken einander deshalb. Eine elektrische Leistung der harmonischen Frequenzen zweiter Ordnung kann deshalb von dem Ausgangsanschluss **T2** abgenommen werden.

**[0019]** Ein Y-Parameter (YSource) des ersten Transistors **Tr1** wird vereinfacht und ohne Beschreibung seiner parasitären Komponenten wie folgt ausgedrückt.

$$Y_{\text{Source}} = \begin{pmatrix} j\omega(C_{gs} + C_{dg}) & -j\omega C_{dg} \\ g_m - j\omega C_{dg} & j\omega(C_{ds} + C_{dg}) \end{pmatrix} \quad [\text{Gleichung 1}]$$

**[0020]** Ein Y-Parameter (YGate) des zweiten Transistors **Tr2** wird wie folgt ausgedrückt.

$$Y_{\text{Gate}} = \begin{pmatrix} g_m + j\omega(C_{gs} + C_{ds}) & -j\omega C_{ds} \\ - (g_m + j\omega C_{ds}) & j\omega(C_{ds} + C_{dg}) \end{pmatrix} \quad [\text{Gleichung 2}]$$

**[0021]** Ein S-Parameter S22, der einen Reflexionskoeffizienten auf der Ausgangsseite repräsentiert, wird davon wie folgt ausgedrückt. Die folgende Gleichung ist ohne Berücksichtigung des stabilisierenden Widerstands **26** gebildet.

$$S_{22} = \frac{1 + g_m + \omega^2(C_{gs}C_{ds} + C_{gs}C_{dg} + C_{ds}C_{dg}) + j\omega(C_{gs} - C_{dg} - g_mC_{dg})}{1 + g_m - \omega^2(C_{gs}C_{ds} + C_{gs}C_{dg} + C_{ds}C_{dg}) + j\omega(C_{gs} + C_{dg} + 2C_{ds} + g_mC_{dg})} \quad [\text{Gleichung 3}]$$

**[0022]** Diese Gleichung zeigt, dass  $|S_{22}| = 1$ , wenn die Frequenz 0 ist und wenn die Frequenz gegen unendlich geht, und dass  $|S_{22}|$  bei allen Frequenzen dazwischen gleich oder größer als 1 ist. In den eigentlichen Vortrichtungscharakteristiken wird aufgrund von Widerstandskomponenten und Ähnlichem  $|S_{22}| < 1$  gezeigt, wenn die Frequenz 0 ist und wenn die Frequenz gegen unendlich geht, aber  $|S_{22}| > 1$  und ein negativer Widerstand wird in einem Mikrowellenband oder einem Millimeter-Wellen-Band gezeigt. Somit existiert in der Schaltung, die den zweiten Transistor (Transistor mit einem an Masse angeschlossenen Gate-Anschluss) verwendet, ein Frequenzband, in dem ein negativer Widerstand gezeigt wird. Folglich wird ein negativer Widerstand auch in dem gesamten Frequenzvervielfacher gezeigt, und die Charakteristik ist instabil.

**[0023]** In dem Frequenzvervielfacher gemäß der ersten Ausführungsform der vorliegenden Erfindung, ist der stabilisierende Widerstand **26** mit dem zweiten Gate-Anschluss **G2** verbunden, und S22 wird deshalb wie folgt ausgedrückt.

$$S_{22} = \frac{1 + g_m + \omega^2(C_{gs}C_{ds} + C_{gs}C_{dg} + C_{ds}C_{dg}) + j\omega(C_{gs} - C_{dg} - g_mC_{dg} + R(C_{gs} + C_{dg}))}{1 + j\omega - \omega^2(1 + 2R)(C_{gs}C_{ds} + C_{gs}C_{dg} + C_{ds}C_{dg}) + j\omega(C_{gs} + C_{dg} + 2C_{ds} + (1 + 2R)g_mC_{dg} + R(C_{gs} + C_{dg}))} \quad [\text{Gleichung 4}]$$

**[0024]** Als eine Folge des Vorsehens des stabilisierenden Widerstands **26** erscheint  $2Rg_mC_{dg}$  in dem imaginären Term des Nenners. Es ist deshalb durch eine geeignete Festlegung von R (stabilisierender Widerstand) möglich, dass  $|S_{22}| < 1$  nicht überschreitet. Als eine Folge zeigt der zweite Transistor **Tr2**, d.h. der Transistor mit dem an Masse angeschlossenen Gate-Anschluss, keinen negativen Widerstand und der Frequenzvervielfacher kann stabil betrieben werden.

**[0025]** Eine Reflexionsverstärkung, die durch den zweiten Transistor **Tr2** erzeugt wird, kann durch Einstellen des Widerstandswerts des stabilisierenden Widerstands **26** auf einen solchen Wert, dass der absolute Wert von  $S_{22}$ , welches ein von der Ausgangsseite aus gesehener Reflexionskoeffizient ist, 1 nicht überschreitet ( $S_{22}$  ist gleich oder kleiner als 1), unterdrückt werden. Außerdem kann, da kein Widerstand (Dämpfungswiderstand) in dem Pfad, durch den das Hochfrequenzsignal passiert, vorgesehen ist, eine Reduzierung einer Wandlungsverstärkung des Frequenzvervielfachers aufgrund eines Verbrauchs von elektrischer Leistung der zweiten harmonischen Frequenz durch einen Dämpfungswiderstand verhindert werden.

**[0026]** Verschiedene Modifikationen können an dem Frequenzvervielfacher gemäß der ersten Ausführungsform der vorliegenden Erfindung vorgenommen werden. Zum Beispiel ist kein spezielles Mittel zum Einstellen von jeder der Gate-Source-Bias-Spannungen an dem Transistor mit einem an Masse angeschlossenen Source-Anschluss (erster Transistor **Tr1**) und an dem Transistor mit einem an Masse angeschlossenen Gate-Anschluss (zweiter Transistor **Tr2**) in der Nähe der Abschnürspannung spezifiziert. Das Gleiche gilt auch bezüglich Frequenzvervielfachern gemäß Ausführungsformen, die nachfolgend beschrieben werden. Jeder der Frequenzvervielfacher gemäß den nachfolgend beschriebenen Ausführungsformen weist eine Zahl von Gemeinsamkeiten mit der ersten Ausführungsform auf und wird deshalb hauptsächlich im Hinblick auf Unterscheidungspunkte von der ersten Ausführungsform beschrieben.

#### Zweite Ausführungsform

**[0027]** **Fig. 2** ist ein Schaltbild des Frequenzvervielfachers gemäß der zweiten Ausführungsform der vorliegenden Erfindung. Die erste Gate-Bias-Schaltung **14**, die mit dem ersten Gate-Anschluss **G1** verbunden ist, ist aus einem Widerstand gebildet. Die erste Source-Bias-Schaltung **16**, die mit dem ersten Source-Anschluss **S1** verbunden ist, ist aus einer Schaltung gebildet, in der ein Widerstand **16a** und ein Kondensator **16b** parallel miteinander verbunden sind. Diese Anordnung benötigt keine unabhängigen Leistungsversorgungen zum Anlegen der Gate-Spannung und der Source-Spannung an den ersten Transistor **Tr1**.

**[0028]** Die zweite Source-Bias-Schaltung **24**, die mit dem zweiten Source-Anschluss **S2** verbunden ist, ist aus einem Widerstand gebildet. Diese Anordnung benötigt keine unabhängige Leistungsversorgung zum Anlegen der Source-Spannung an den zweiten Transistor **Tr2**.

**[0029]** Ein Anschluss des stabilisierenden Widerstands **26** ist mit dem Gate-Anschluss des zweiten Transistors **Tr2** verbunden, während der andere Anschluss des stabilisierenden Widerstands **26** direkt mit einem an Masse angeschlossenen Metall verbunden ist. In diesem Fall fungiert der stabilisierende Widerstand **26** als Gate-Bias-Schaltung, und es besteht keine Notwendigkeit für eine unabhängige Leistungsversorgung zum Anlegen der Gate-Spannung.

**[0030]** Als ein Ergebnis kann der Frequenzvervielfacher unter Verwendung der einzelnen Leistungsversorgung **42**, die mit den Drain-Anschlüssen des ersten Transistors **Tr1** und des zweiten Transistors **Tr2** verbunden ist, betrieben werden.

#### Dritte Ausführungsform

**[0031]** **Fig. 3** ist ein Schaltbild des Frequenzvervielfachers gemäß der dritten Ausführungsform der vorliegenden Erfindung. Durch den Widerstandswert **R** des stabilisierenden Widerstands **26** wird der negative Widerstand des zweiten Transistors **Tr2** unterdrückt und die Verstärkung des zweiten Transistors **Tr2** wird gleichzeitig reduziert.

**[0032]** Ein Kondensator **50** ist deshalb parallel zu dem stabilisierenden Widerstand **26** vorgesehen. Das heißt, der Kondensator **50** ist zwischen dem zweiten Gate-Anschluss **G2** und einer Masse angeschlossen, wodurch er die Reduzierung einer Verstärkung des zweiten Transistors **Tr2** begrenzt. Die Eingangs-Ausgangs-Anpassung wird durch den Kondensator **50** verändert, um die Reduzierung einer Verstärkung des zweiten Transistors **Tr2** zu begrenzen. Als eine Folge des Vorsehens des Kondensators **50** wird jedoch der Stabilisierungseffekt (Effekt eines Reduzierens eines negativen Widerstands) reduziert. Deshalb besteht eine Notwendigkeit, die Kapazität des Kondensators **50** zu reduzieren.

#### Vierte Ausführungsform

**[0033]** **Fig. 4** ist ein Schaltbild eines Frequenzvervielfachers gemäß der vierten Ausführungsform der vorliegenden Erfindung. Die Leistungsversorgung **42** zum Bereitstellen eines Potentials an den ersten Drain-An-

schluss **D1** und den zweiten Drain-Anschluss **D2** ist in einer Zweigleitung vorgesehen, die von der Hauptleitung abzweigt, durch die ein Hochfrequenzsignal passiert. Ein Widerstand ist als eine Leistungsversorgungsschaltung **44** vorgesehen. Das heißt, ein Widerstand ist in Serie mit der Zweigleitung verbunden. Der Verbindungs-

punkt zwischen der Zweigleitung und der Hauptleitung ist ein Verbindungspunkt **P1**.

**[0034]** Eine Vorrichtung für eine Verwendung in einem Mikrowellen- oder einem Millimeter-Wellen-Band verwendet gewöhnlich eine Leitung, die eine Leitungslänge von  $\frac{1}{4}$  der Wellenlänge bezüglich der Betriebsfrequenz aufweist, und einen Kondensator zum Kurzschließen eines Leitungsendes bei einer Hochfrequenz. Solch eine Leitung ist so geformt, dass sie erscheint, als sei sie von dem Verbindungspunkt zu einem Pfad, durch den ein Hochfrequenzsignal passiert gesehen am Ende offen, wodurch der Einfluss auf Hochfrequenzcharakteristiken eliminiert wird.

**[0035]** Wenn ein Widerstand, der von dem Verbindungspunkt **P1** aus gesehen einen solchen Widerstandswert aufweist, dass der Einfluss auf Hochfrequenzcharakteristiken eliminiert wird, als eine Leistungsversorgungsschaltung vorgesehen ist, dann tritt gleichzeitig ein Spannungsabfall auf. In einem Verstärker wird deshalb die Effizienz merklich reduziert, wenn die Leistungsversorgungsschaltung aus einem Widerstand gebildet wird.

**[0036]** Auch in dem Frequenzvervielfacher, der eine Frequenzvervielfachung auf Mikrowellen ausführt, tritt ein Spannungsabfall auf, wenn die Leistungsversorgungsschaltung **44** aus einem Widerstand gebildet wird. Der Strom, der durch den Frequenzvervielfacher fließt, ist jedoch klein, und deshalb ist der Einfluss der Effizienzreduzierung durch das gesamte System klein. Die Fläche, die von der Leistungsversorgungsschaltung **44**, die aus einem Widerstand gebildet wird, eingenommen wird, ist im Vergleich zu der, die durch die  $\frac{1}{4}$  Wellenlängen-

Leitung eingenommen wird, deutlich kleiner. Der Frequenzvervielfacher kann deshalb verkleinert werden.

**[0037]** Eine geeignete Kombination der Merkmale des Frequenzvervielfachers gemäß den vorstehend beschriebenen Ausführungsformen kann zusammengestellt werden.

**[0038]** Gemäß der vorliegenden Erfindung ist ein Widerstand mit dem Gate-Anschluss des Transistors mit dem an Masse angeschlossenen Gate-Anschluss verbunden, sodass der Transistor mit dem an Masse angeschlossenen Gate-Anschluss stabilisiert werden kann.

**[0039]** Offenbar sind angesichts der vorstehenden Lehren viele Modifikationen und Variationen der vorliegenden Erfindung möglich. Es ist daher verständlich, dass innerhalb des Gültigkeitsumfangs der angehängten Ansprüche die Erfindung anders als ausdrücklich beschrieben ausgeführt werden kann.

**[0040]** Neben der vorstehenden schriftlichen Beschreibung der Erfindung wird zu deren ergänzender Offenbarung hiermit explizit auf die zeichnerische Darstellung der Erfindung in **Fig. 1** bis **Fig. 4** Bezug genommen.

#### Bezugszeichenliste

- 10** Eingangsanpassungsschaltung

- 12** Kondensator

- 14** erste Gate-Bias-Schaltung

- 16** erste Source-Bias-Schaltung

- 16a** Widerstand

- 16b** Kondensator

- 18** Transmission-Line

- 22** Kondensator

- 24** zweite Source-Bias-Schaltung

- 26** Widerstand

- 28** Kondensator

- 30** zweite Gate-Bias-Schaltung

- 32** Transmission-Line

- 40** Ausgangsanpassungsschaltung

|            |                               |

|------------|-------------------------------|

| <b>42</b>  | Leistungsversorgung           |

| <b>44</b>  | Leistungsversorgungsschaltung |

| <b>50</b>  | Kondensator                   |

| <b>D1</b>  | erster Drain-Anschluss        |

| <b>D2</b>  | zweiter Drain-Anschluss       |

| <b>G1</b>  | erster Gate-Anschluss         |

| <b>G2</b>  | zweiter Gate-Anschluss        |

| <b>P1</b>  | Verbindungspunkt              |

| <b>S1</b>  | erster Source-Anschluss       |

| <b>S2</b>  | zweiter Source-Anschluss      |

| <b>T1</b>  | Eingangsanschluss             |

| <b>T2</b>  | Ausgangsanschluss             |

| <b>Tr1</b> | erster Transistor             |

| <b>Tr2</b> | zweiter Transistor            |

### Patentansprüche

1. Frequenzvervielfacher, aufweisend:

einen Eingangsanschluss (T1);

einen Ausgangsanschluss (T2);

einen ersten Transistor (Tr1), der einen ersten Gate-Anschluss (G1), an den ein Hochfrequenzsignal von dem Eingangsanschluss (T1) angelegt wird, einen ersten Drain-Anschluss (D1), von dem ein Ausgangssignal an den Ausgangsanschluss (T2) ausgegeben wird, und einen ersten Source-Anschluss (S1) aufweist;

einen zweiten Transistor (Tr2), der einen zweiten Gate-Anschluss (G2), einen zweiten Source-Anschluss (S2), an den ein Hochfrequenzsignal von dem Eingangsanschluss (T1) angelegt wird, und einen zweiten Drain-Anschluss (D2), von dem ein Ausgangssignal an den Ausgangsanschluss (T2) ausgegeben wird, aufweist; und

einen stabilisierenden Widerstand (26), der ein Widerstand ist, der mit dem zweiten Gate-Anschluss (G2) verbunden ist,

wobei kein Widerstand in dem Pfad für das Hochfrequenzsignal vorhanden ist, und

wobei der stabilisierende Widerstand (26) eine Reflexionsverstärkung unterdrückt, die von dem zweiten Transistor (Tr2) erzeugt wird.

2. Frequenzvervielfacher gemäß Anspruch 1, wobei der Widerstandswert des stabilisierenden Widerstands (26) auf einen solchen Wert eingestellt ist, dass der absolute Wert von  $S_{22}$ , was ein von der Ausgangsseite gesehener Reflexionskoeffizient ist, 1 nicht überschreitet.

3. Frequenzvervielfacher gemäß Anspruch 1 oder 2, weiter aufweisend:

eine erste Gate-Bias-Schaltung (14), die mit dem ersten Gate-Anschluss (G1) verbunden ist;

eine erste Source-Bias-Schaltung (16), die mit dem ersten Source-Anschluss (S1) verbunden ist; und

eine zweite Source-Bias-Schaltung (24), die mit dem zweiten Source-Anschluss (S2) verbunden ist,

wobei jede der ersten Gate-Bias-Schaltung (14), der ersten Source-Bias-Schaltung (16) und der zweiten Source-Bias-Schaltung (24) aus einem Widerstand gebildet ist.

4. Frequenzvervielfacher gemäß einem der Ansprüche 1 bis 3, weiter aufweisend einen Kondensator (50), der mit dem zweiten Gate-Anschluss (G2) verbunden ist.

5. Frequenzvervielfacher gemäß einem der Ansprüche 1 bis 4, weiter aufweisend:

eine Leistungsversorgung (42), die mit einer Zweigleitung verbunden ist, die von einer Hauptleitung abzweigt, durch die das Hochfrequenzsignal passiert, wobei die Leistungsversorgung (42) ein Potential an den ersten Drain-Anschluss (D1) und an den zweiten Drain-Anschluss (D2) bereitstellt; und

einen Widerstand (44), der in Serie mit der Zweigleitung verbunden ist.

Es folgen 4 Seiten Zeichnungen

## Anhängende Zeichnungen

FIG.1

FIG.2

FIG.3

FIG.4