## United States Patent [19]

#### Winkler

3,523,232

3,526,300

3,627,080

[45] Nov. 27, 1973

| [54]                 | SPEED PATTERN GENERATOR FOR<br>ELEVATOR SYSTEMS |                                                    |

|----------------------|-------------------------------------------------|----------------------------------------------------|

| [75]                 | Inventor:                                       | Charles L. Winkler, Pittsburgh, Pa.                |

| [73]                 | Assignee:                                       | Westinghouse Electric Corporation, Pittsburgh, Pa. |

| [22]                 | Filed:                                          | May 17, 1972                                       |

| [21]                 | Appl. No.                                       | : 254,006                                          |

| [52]<br>[51]<br>[58] | Int. Cl.                                        |                                                    |

| [56]                 |                                                 | References Cited                                   |

UNITED STATES PATENTS

8/1970

9/1970

12/1971

Hall et al. ..... 187/29

Yuminaka et al. ..... 187/29

Primary Examiner—Bernard A. Gilheany Assistant Examiner—W. E. Duncanson, Jr. Attorney—A. T. Stratton et al.

#### [57] ABSTRACT

A speed pattern generator for elevator control which provides a time dependent speed reference pattern, with control over maximum jerk directly incorporated into the pattern itself. The speed pattern is developed by starting with a step signal whose two magnitudes determine maximum jerk. The specific magnitude of the step signal which is selected, and time spent at each magnitude of the step signal is determined by acceleration and speed feedback circuits. The step or jerk signal is integrated to provide an acceleration signal, and the acceleration signal is integrated to provide a speed pattern signal which, regardless of how fast the elevator system responds thereto, positively limits the maximum jerk.

17 Claims, 23 Drawing Figures

SHEET 02 OF 19

SHEET OU OF 19

## SHEET 05 OF 19

SHEET 07 OF 19

SHEET 08 OF 19

SHEET 09 OF 19

### SHEET 10 OF 19

CORRIDOR CALLS CAR CAN CONSIDER WHEN TRAVELLING IN A GIVEN DIRECTION

FIG. 11

SHEET 11 OF 19

SHEET 12 OF 19

FIG. 15A

FIG. 15B

### SHEET 15 OF 19

AND

NLC o Ly

MXVMo

914

SHEET 18 OF 19

# SPEED PATTERN GENERATOR FOR ELEVATOR SYSTEMS

# CROSS-REFERENCES TO RELATED APPLICATIONS

Certain of the apparatus disclosed but not claimed in the present application, is claimed in the following concurrently filed, copending applications:

Application Ser. No. 254,007, filed May 17, 1972, entitled "FLOOR SELECTOR FOR AN ELEVATOR 10 SYSTEM," which application is assigned to the same assignee as the present application.

Application Ser. No. 254,119, filed May 17, 1972, entitled "DISTANCE SLOWDOWN CONTROL FOR ELEVATOR SYSTEMS," which application is as- 15 signed to the same assignee as the present application.

Application Ser. No. 254,005, filed May 17, 1972, entitled "TERMINAL SLOWDOWN CONTROL FOR ELEVATOR SYSTEMS," which application is assigned to the same assignee as the present application. 20

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The invention relates in general to elevator systems, and more specifically to a speed pattern generator for 25 elevator systems.

2. Description of the Prior Art

Elevator systems which utilize electromechanical controllers provide no direct control of jerk via the speed pattern, but depend upon other factors to limit 30 jerk. The design of the car dynamic controller is a compromise between a plurality of criteria, such as system response time, landing characteristics, and value of deceleration during the slowdown phase. During installation of the elevator system, the system is carefully adjusted to provide the required jerk limitation, which again involves compromise between factors such as deceleration overshoot, landing overshoot, and oscillations in car speed during acceleration. Further, the system may require periodic readjustment of jerk, if the parameters of the dynamic system drift due to aging, temperature and wear.

Elevator systems with solid state controllers may provide control over maximum jerk in the speed pattern itself. For example, U.S. Pat. No. 3,523,232 discloses a position versus time pattern generator, which develops an acceleration signal and then superposes jerk constraint on the acceleration signal via an integrator. This jerk constraint acceleration signal is integrated twice to obtain the command position signal with respect to time. U.S. Pat. No. 3,350,612 uses a capacitor to smooth the transitions between the various portions of a pattern signal.

#### SUMMARY OF THE INVENTION

The present invention is a new and improved speed pattern generator of the solid state type, which provides a time optimum speed pattern signal with controlled jerk incorporated into the speed pattern. Further, the maximum jerk is directly controlled, and adjustable.

More specifically, an on-off type signal or step signal is provided which represents the value of jerk, or rate of change of acceleration. The step signal is switchable between first and second magnitudes, with the actual jerk to which the elevator car will be subjected being determined by the signal magnitudes.

The first and second magnitudes of the step or jerk signal provide currents of opposite polarity. The current responsive to the magnitude selected is integrated to provide a signal representing car acceleration, or deceleration, and the acceleration signal is integrated to generate the time dependent speed reference signal for the motor controller.

Acceleration and speed feedback loops select one of the two magnitudes of the jerk signal, to incorporate the jerk constraint during the transition periods between: (1) zero car speed and maximum acceleration, (2) maximum acceleration and maximum velocity, (3) maximum velocity and maximum deceleration, and (4) maximum deceleration and zero car speed. During the period when the car is at rest, and during the periods of constant acceleration and constant velocity or speed, the feedback circuits switch the jerk signal between its two magnitudes such that jerk is averaged to zero, with the switching rate being faster than the response time of the elevator car.

The time dependent speed pattern provides a pattern for a complete run, and may be used to control a complete run on relatively low speed elevator systems. On higher speed elevator systems, the time dependent speed pattern may be used for certain phases of the run, with the time dependent signal being replaced by distance dependent reference signals for other phases of the run. For example, the time dependent speed pattern may be used to accelerate the car and for the full speed phase, switching to a distance dependent slowdown signal when maximum deceleration is reached during the slowdown phase.

In the disclosed speed pattern generator, the value of jerk is not dependent upon system transfer functions, there is no need for field adjustment, and since there is no interaction between jerk control and other parameters, the other parameters may be optimized independently of the jerk control.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The invention may be better understood, and further advantages and uses thereof more readily apparent, when considered in view of the following detailed description of exemplary embodiments, taken with the accompanying drawings, in which:

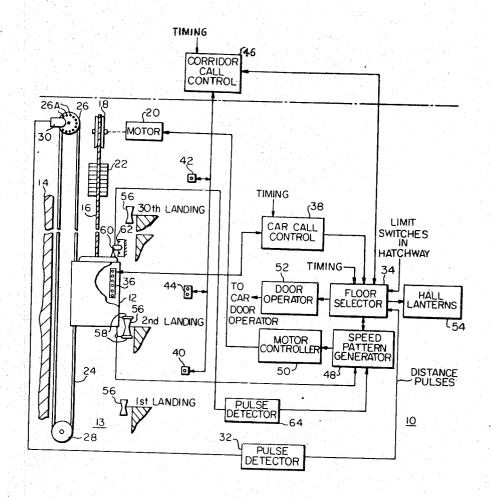

FIG. 1 is a partially schematic and partially block diagram illustrating an elevator system which may utilize the teachings of the invention;

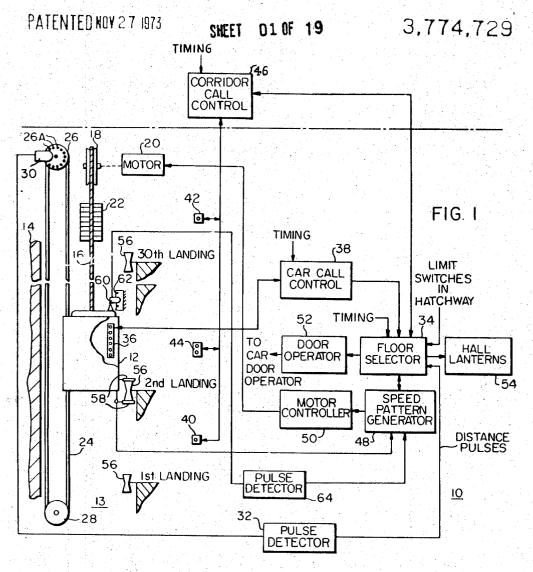

FIG. 2 is a block diagram of a floor selector which embodies the basic concepts of the invention;

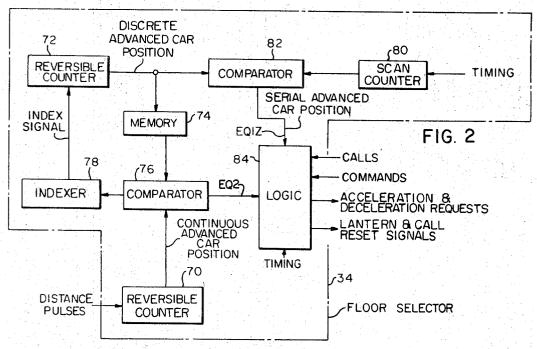

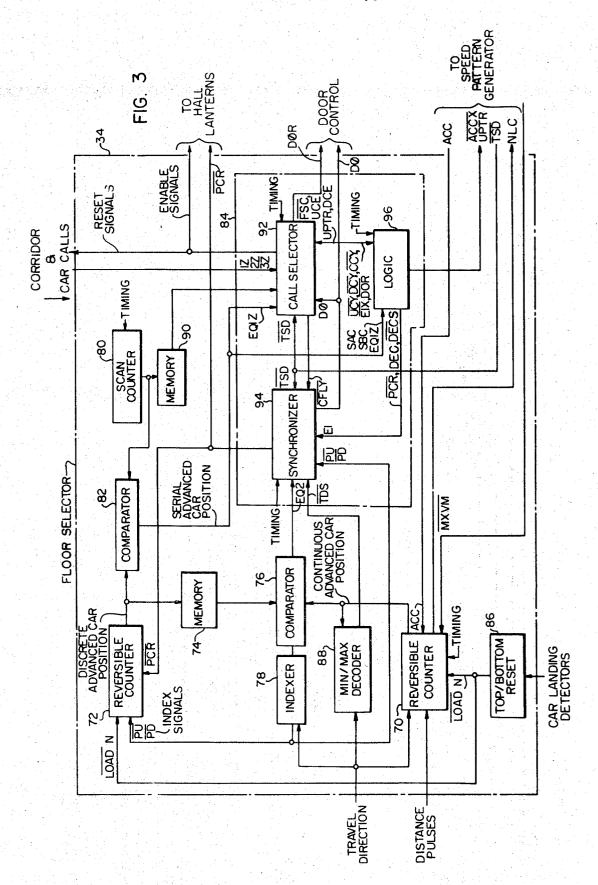

FIG. 3 is a block diagram of a floor selector which embodies the basic concepts of the invention, and additionally illustrates a preferred embodiment thereof;

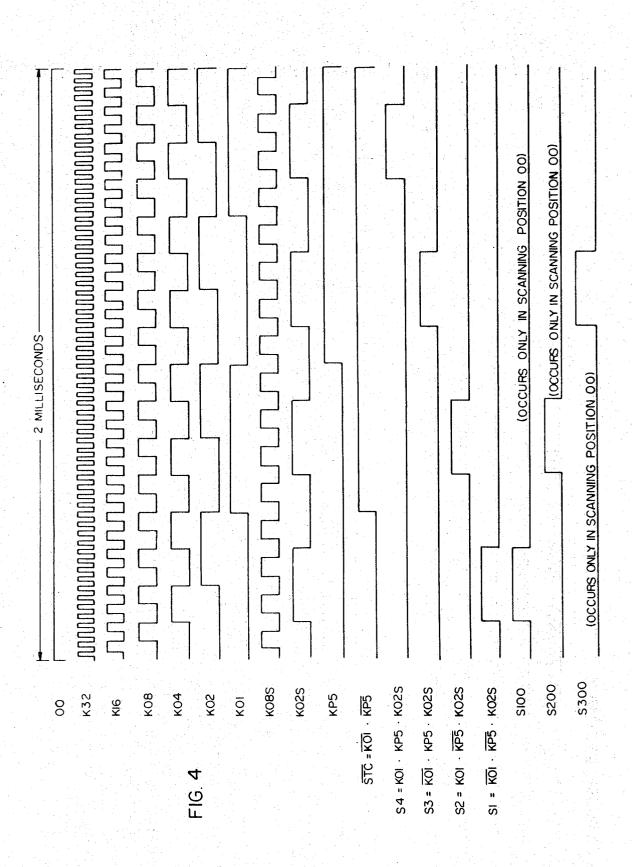

FIG. 4 is a timing diagram for scanning position zero of the scan counter, which illustrates the development of certain of the timing signals used in the floor selector;

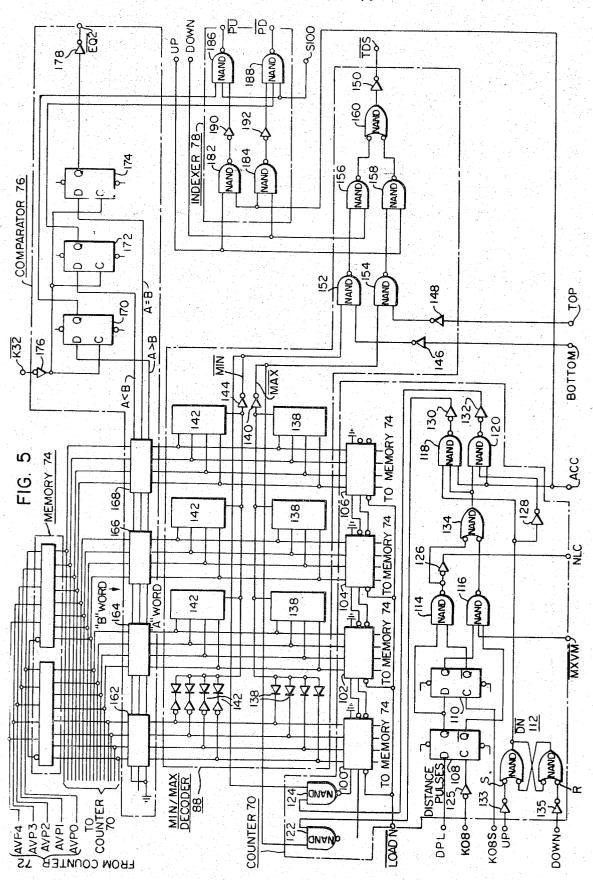

FIG. 5 is a schematic diagram of a counter, decoder, memory, comparator and indexer suitable for use in the floor selector shown in FIG. 3;

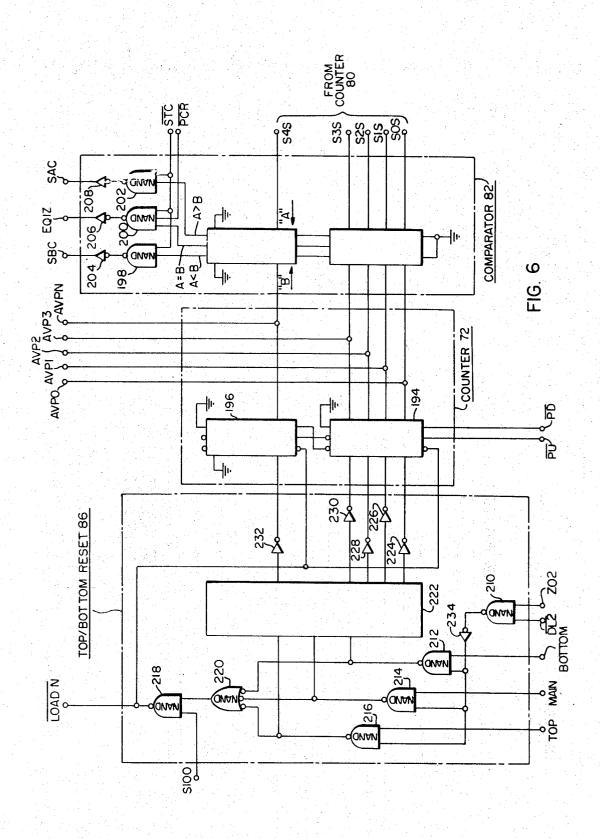

FIG. 6 is a schematic diagram of a counter, comparator, and top/bottom reset suitable for use in the floor selector shown in FIG. 3;

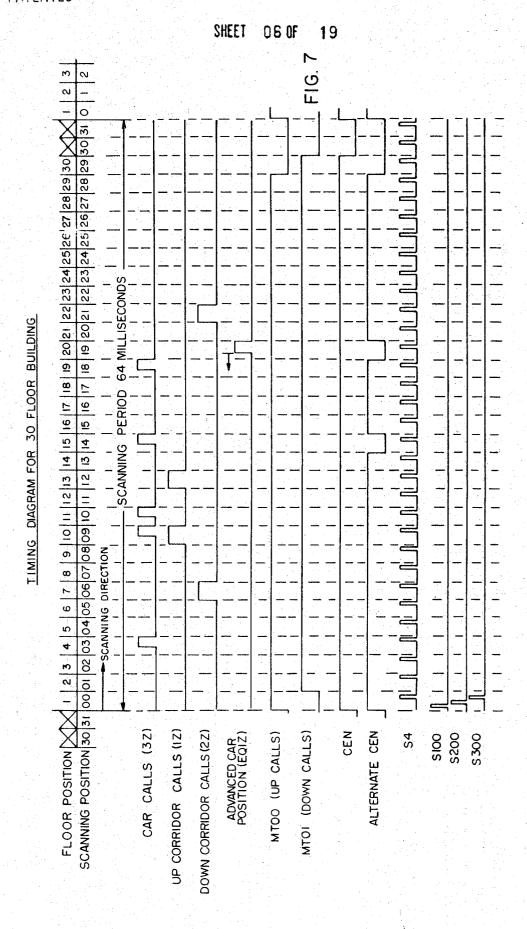

FIG. 7 is a timing diagram for a 30 floor building which illustrates certain signals explanatory of the operation of the floor selector shown in FIG. 3;

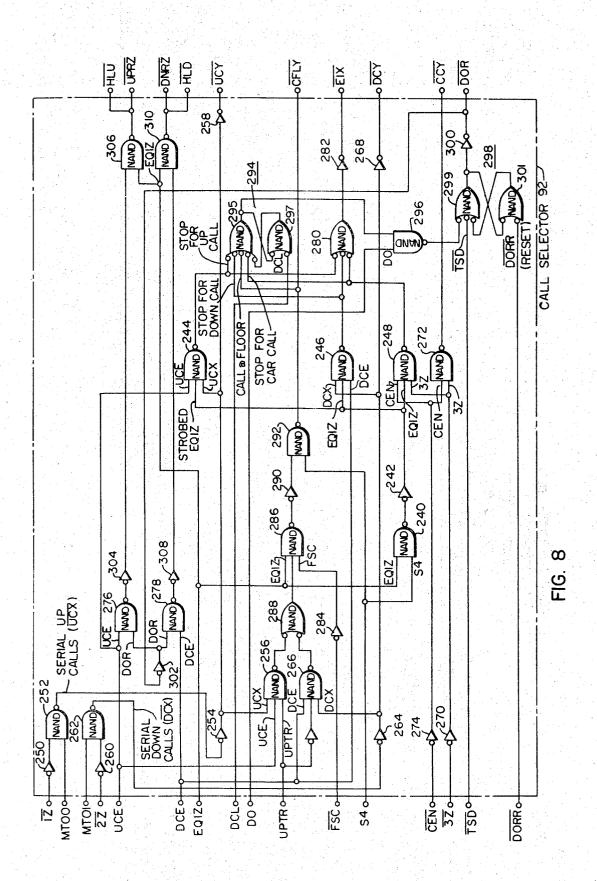

FIG. 8 is a schematic diagram of a call selector suitable for use in the floor selector shown in FIG. 3;

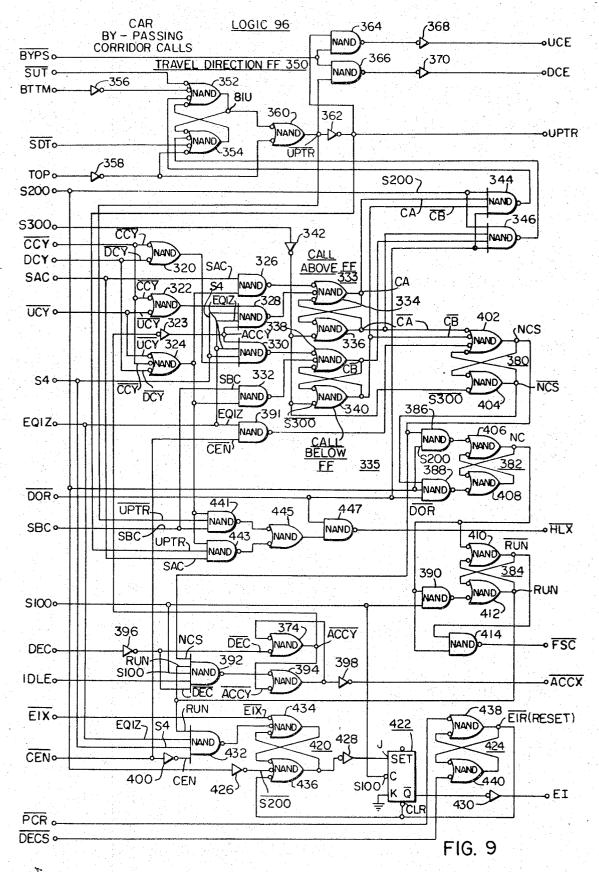

FIG. 9 is a schematic diagram of logic circuitry suitable for use in the floor selector shown in FIG. 3;

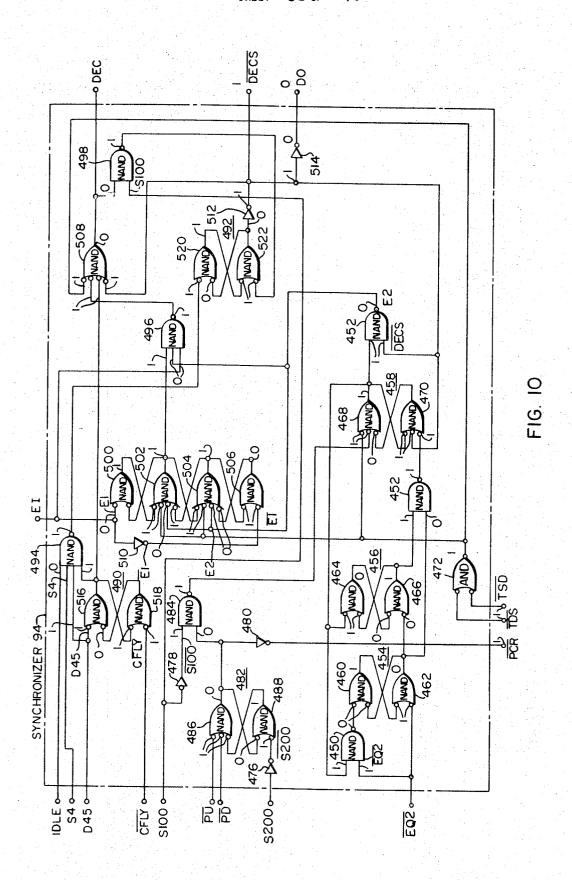

FIG. 10 is a schematic diagram of a synchronizer suit- 5 able for use in the floor selector shown in FIG. 3;

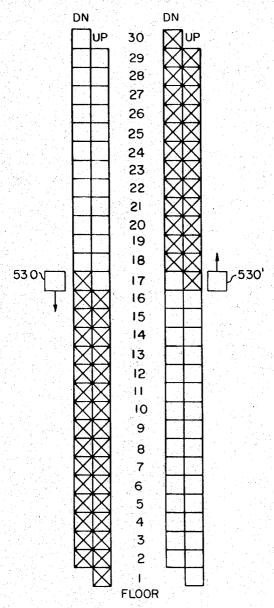

FIG. 11 is a diagram which illustrates which corridor calls a car can consider when it is set for up and down travel:

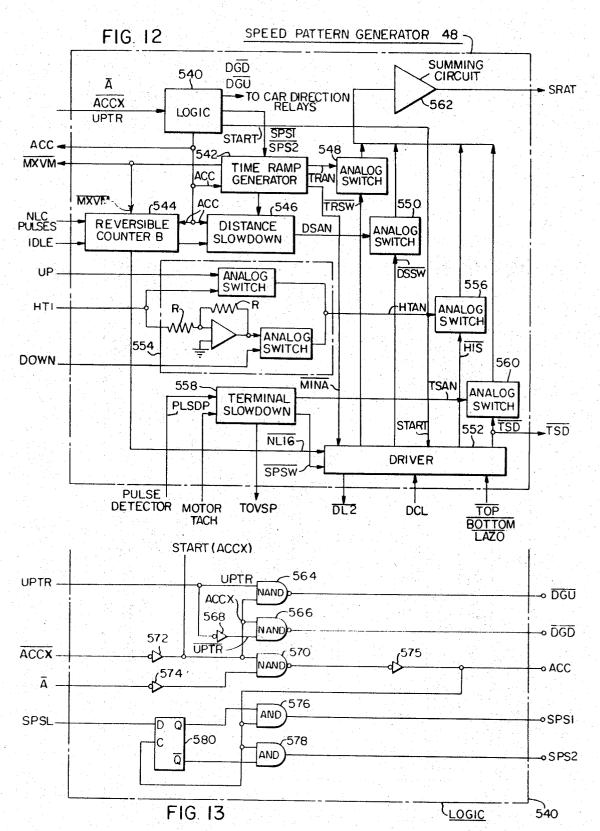

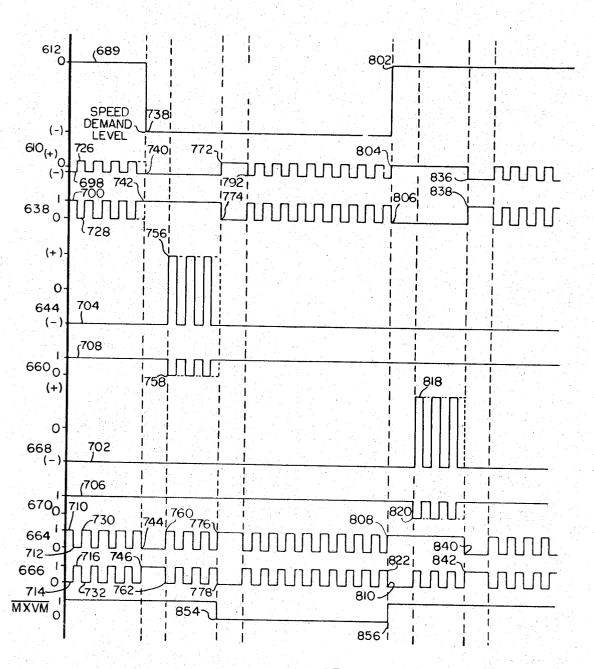

FIG. 12 is a block diagram of a speed pattern generator which may be used in the elevator system shown in FIG. 1; information is directed to the floor selector 34. Corridor calls, as registered by pushbuttons may in the corridors, such as the up pushbutton 40 kg.

FIG. 13 is a schematic diagram of logic circuitry suitable for use in the speed pattern generator shown in FIG. 12;

FIG. 14 is a schematic diagram of a time ramp generator suitable for use in the speed pattern generator shown in FIG. 12;

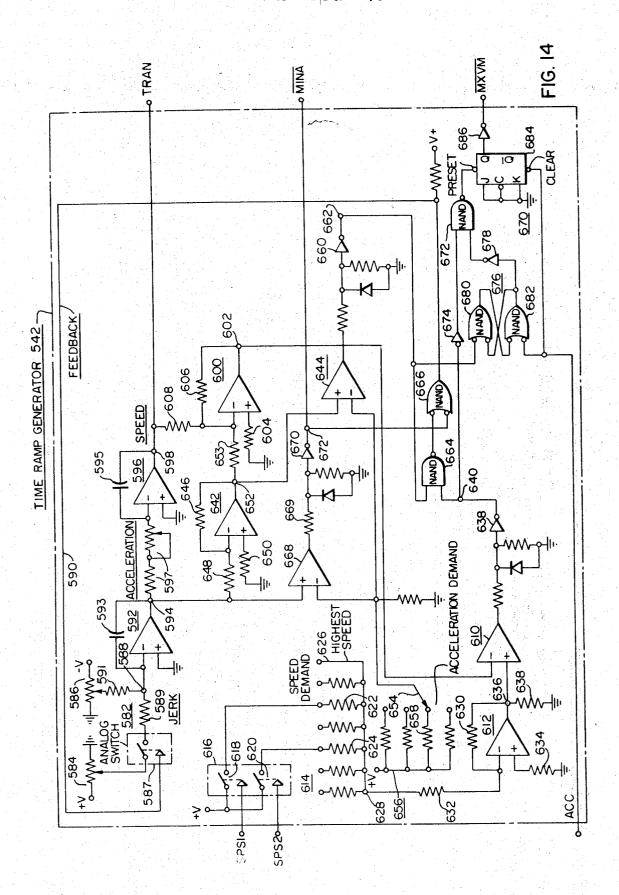

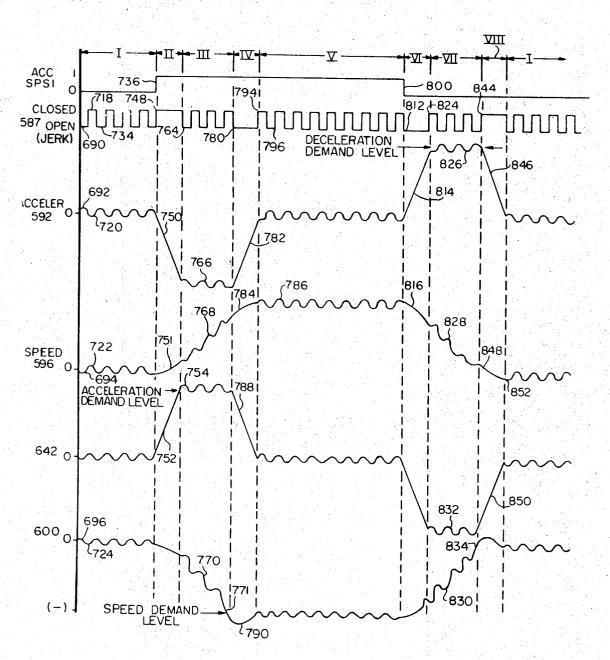

FIG. 15 is a graph illustrating the waveforms at various circuit points of the time ramp generator shown in 20 from pulse detector 32 to develop information concerning the position of the car 12 in the hatchway 13,

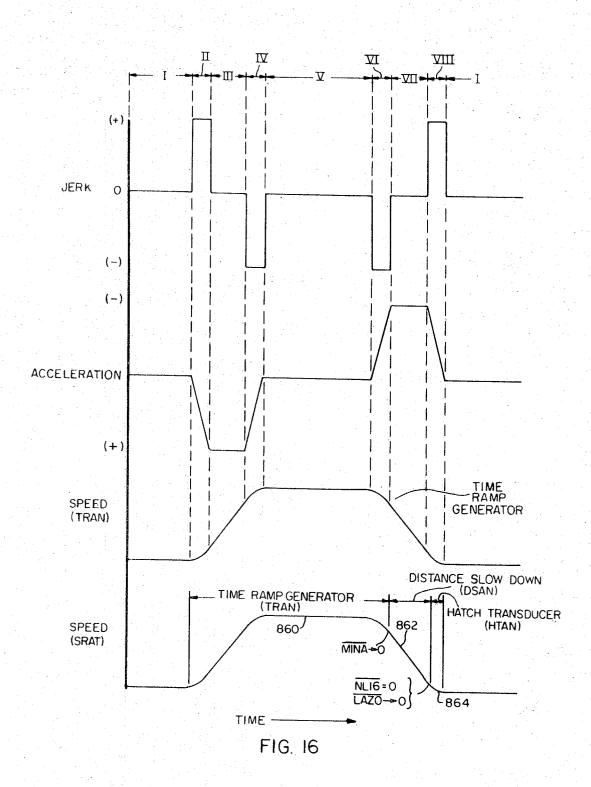

FIG. 16 is a graph illustrating time dependent jerk, acceleration, and speed signals for the speed pattern generator shown in FIG. 12;

FIG. 17 is a schematic diagram of a distance slow- 25 down circuit suitable for use in the speed pattern generator shown in FIG. 12;

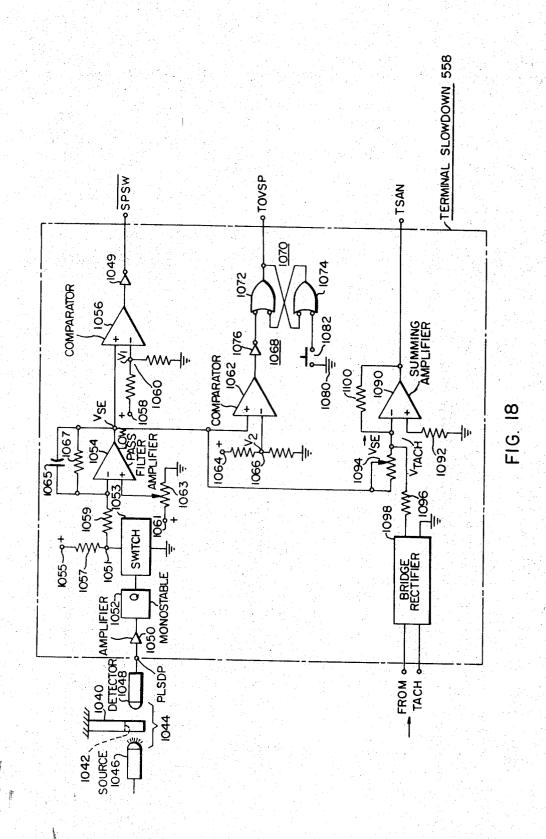

FIG. 18 is a schematic diagram of a terminal slow-down circuit suitable for use in the speed pattern generator shown in FIG. 12;

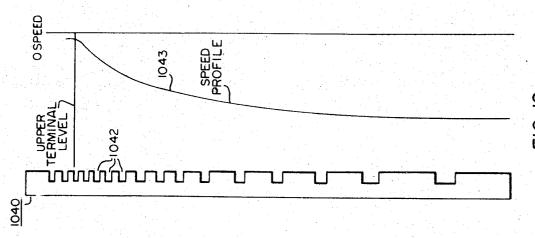

FIG. 19 illustrates a terminal slow-down blade of the type which may be used in conjunction with a pulse generator to provide pulses for the terminal slow-down circuit shown in FIG. 18;

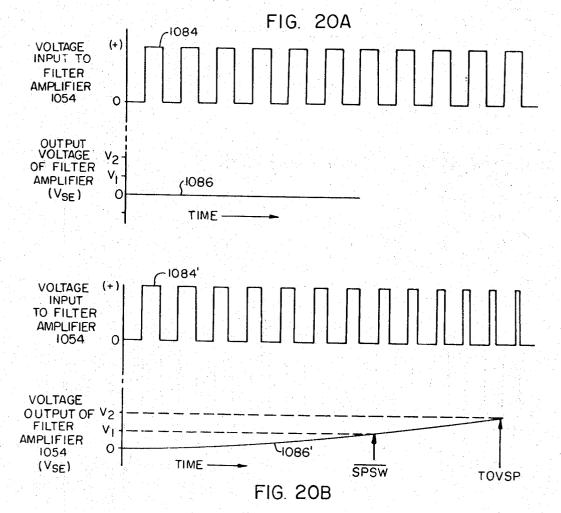

FIGS. 20A and 20B are graphs which illustrate the 35 operation of the terminal slow-down circuit shown in FIG. 18; and

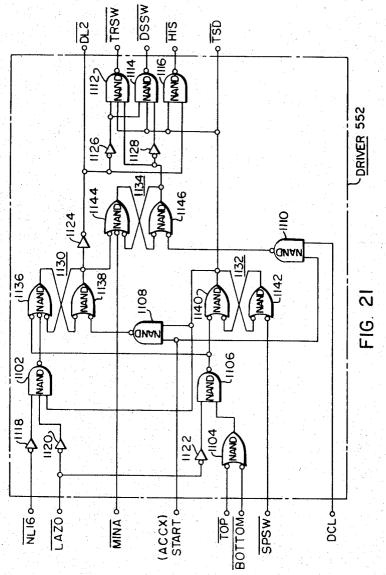

FIG. 21 is a schematic diagram of a driver circuit which may be used in the speed pattern generator shown in FIG. 12.

#### **DESCRIPTION OF PREFERRED EMBODIMENTS**

#### FIG. 1

Referring now to the drawings, and FIG. 1 in particular, there is shown an elevator system 10 wherein a car 12 is mounted in a hatchway 13 for movement relative to a structure 14 having a plurality of landings, such as 30, with only the first, second and 30 landings being shown in order to simplify the drawing. The car 12 is supported by a rope 16 which is reeved over a traction sheave 18 mounted on the shaft of a drive motor 20, such as a direct current motor as used in the Ward-Leonard drive system. A counterweight 22 is connected to the other end of the rope 16. A governor rope 55 24, which is connected to the top and bottom of the car 12, is reeved over a governor sheave 26 located above the highest point of travel of the car in the hatchway 13, and over a pulley 28 located at the bottom of the hatchway. A pickup 30 is disposed to detect movement 60 of the car 12 through the effect of circumferentially spaced openings 26A in the governor sheave 26. The openings in the governor sheave are spaced to provide a pulse for each standard increment of travel of the car, such as a pulse for each 0.5 inch of car travel. Pickup 30, which may be of any suitable type, such as optical or magnetic, provides pulses in response to the movement of the openings 26A in the governor sheave.

Pickup 30 is connected to a pulse detector 32 which provides distance pulses for a floor selector 34. Distance pulses may be developed in any other suitable manner, such as by a pickup disposed on the car which cooperates with regularly spaced indicia in the hatchway.

Car calls, as registered by pushbutton array 36 mounted in the car 12, are recorded and serialized in car call control 38, and the resulting serialized car call information is directed to the floor selector 34.

Corridor calls, as registered by pushbuttons mounted in the corridors, such as the up pushbutton 40 located at the first landing, the down pushbutton 42 located at the thirtieth landing, and the up and down pushbuttons 15 44 located at the second and other intermediate landings, are recorded and serialized in corridor call control 46. The resulting serialized corridor call information is directed to the floor selector 34.

The floor selector 34 processes the distance pulses from pulse detector 32 to develop information concerning the position of the car 12 in the hatchway 13, and also directs these processed distance pulses to a speed pattern generator 48 which generates a speed reference signal for a motor controller 50, which in turn provides the drive voltage for motor 20.

The floor selector 34 keeps track of the car 12, the calls for service for the car, provides the request to accelerate signal to the speed pattern generator 48, and provides the deceleration signal for the speed pattern generator 48 at the precise time required for the car to decelerate according to a predetermined deceleration pattern and stop at a predetermined floor for which a call for service has been registered. The floor selector 34 also provides signals for controlling such auxiliary devices as the door operator 52, the hall lanterns 54, and controls the resetting of the car call and corridor call controls when a car or corridor call has been serviced.

Landing, and leveling of the car at the landing, is accomplished by a hatch transducer system which utilizes inductor plates 56 disposed at each landing, and transformer 58 disposed on the car 12.

The motor controller 50 includes a speed regulator responsive to the reference pattern provided by the speed pattern generator 48. The speed control may be derived from a comparison of the actual speed of the motor and that called for by the reference pattern by using a drag magnet regulator, such as disclosed in U.S. Pat. Nos. 2,874,806 and 3,207,265, which are assigned to the same assignee as the present application. The precision landing system using inductor plates 56 and transformer 58 is described in detail in U.S. Pat. No. 3,207,265.

An overspeed condition near either the upper or lower terminal is detected by the combination of a pickup 60 and slowdown blades, such as a slowdown blade 62. The pickup 60 is preferably mounted on the car 12, and a slowdown blade is mounted near each terminal. However, a single slowdown blade mounted on the car could cooperate with pickups disposed near each terminal. The slowdown blade has spaced openings, such as a toothed edge, with the teeth spaced to generate pulses in the pickup 60 when there is relative motion between them, which pulses are processed in pulse detector 64 and directed to the speed pattern generator 48 where the pulses are used to detect overspeed.

#### FIG. 2

FIG. 2 is a block diagram of floor selector 34, which embodies the basic concepts thereof. The distance pulses from the pulse detector 32 are applied to a reversible counter 70, which starts with ZERO count at the lowest or first landing, counts up when the car is travelling upwardly, and counts down when the car is travelling downwardly. Counter 70 is forcibly reset to ZERO at the bottom landing, in the event it is a few 10 counts off, and it may also be reset to the count representing the uppermost landing when it arrives at that floor, to correct any error in the count. Counter 70 is preferably a binary counter having the number of bits necessary to count to the binary number determined by 15 the standard increment used to generate a pulse, and the height between the lowest and uppermost floors.

Counter 70 is arranged to output a binary number which continuously changes as the car moves relative to the structure, to continuously indicate the advanced 20 car position, as opposed to the actual position of the car in the hoistway. This continuous advanced car position is the point at which the car could be brought to a stop from its current velocity under a predetermined deceleration schedule. The continuous advanced car 25 position is more important than the actual position of the car in high speed elevator systems, as several floors are needed to bring the car to a smooth stop without unnecessary stress on the passengers.

As disclosed in the hereinbefore mentioned U.S. Pat. 30 No. 3,589,474, the continuous advanced car position may be generated directly in the reversible counter 70 by generating pulses at twice the rate of the distance pulses when the car is accelerating, and at the same rate as the distance pulses when the car is travelling at constant speed. When deceleration is initiated, the counting of the distance pulses is discontinued such that when the car comes to a stop, the count in the counter reflects the actual car position.

A second reversible counter 72 provides a signal 40 which indicates the discrete advanced car position in terms of floor number. The second reversible counter 72 is also preferably a binary counter, having the number of bits necessary to provide a binary word for the uppermost floor. Counter 72 may be reset at one or both of the terminals, and it is indexed up or down, as required, as the count of the continuous advanced car position changes, as will be hereinafter described.

A read only memory 74 is provided, which, when addressed by the binary word of counter 72, which represents the discrete advanced car position with a floor number, outputs a binary word having the number of bits necessary to describe the exact location of that floor relative to the structure, with a resolution of the same standard increment used to generate pulses, such as 0.5 inch. The read only memory is preferably a matrix of fused diodes, with the presence of a diode corresponding to a logical ONE, while a missing diode, i.e., one in which its fuse has been blown, represents a logical ZERO. A diode may be disconnected from the matrix by discharging a charged capacitor across it and blowing the fuse in series with it. Thus, the read only memory may be precisely set for each floor of the structure it is associated with, during field installation. For example, the elevator car is leveled at the bottom floor, the counter 70 is reset to all ZERO's, the floor selector for the read only memory 74 is set to the bot-

tom floor and the bits of counter 70 are each connected to a bit of the read only memory through an inverter and a switch, which when actuated, discharges a capacitor through the associated diode of the read only memory if the inverted bit of counter 70 is a logical ONE. Thus, when counter 70 registers all ZERO's at the bottom landing, the inverted bits are all ONE's and all of the diodes of the read only memory 74 would be disconnected from the circuit for floor position one. The car is then moved by a hand operation to the next landing and leveled exactly with the floor without overshooting. The count of counter 70 thus describes the exact location of this floor relative to the structure, and the word or floor selector of the read only memory is set to the second word. Depressing the switch will set the second word of the memory to the count in the counter 70. This sequence is repeated until the exact location of all of the floors have been preset into the read only memory. Thus, addressing memory 74 with a word from counter 72 containing the number of bits necessary to describe the number of a floor, causes the memory 74 to output a word having the number of bits necessary to accurately describe the location of the floor in the structure with the same resolution used in counter 70 to describe the continuous advanced car position. For example, a 5 bit input word describing a floor number may output a 16 bit word describing the location of that floor in the structure.

A bit-by-bit comparator 76 is provided which compares the binary output words of counter 70 and memory 74. When the binary words of counter 70 and memory 74 are equal, comparator 76 outputs an equality signal EQ2. Thus, when the car is travelling upwardly, when the binary words of counter 70 and memory 74 are equal, the equality signal EQ2 is generated. The equality signal EQ2 indicates slowdown must be initiated at this time or the car cannot stop at the discrete advanced car position. If deceleration is not initiated at that point, counter 70 will continue to count up in response to the distance pulses, the binary word of counter 70 will exceed the binary word of memory 74, and comparator 76 provides a signal for indexer 78. Indexer 78 provides a signal for counter 72 which increments the counter 72 to output the binary word for the next higher floor.

When the car is travelling downwardly and the binary word of counter 70 becomes equal to the binary word of memory 74, the equality signal EQ2 is generated. If deceleration is not initiated at this time, counter 70 will continue to count down in response to the distance pulses and as soon as the binary word of counter 70 is less than the binary word of memory 74, comparator 76 provides a signal for indexer 78, which in turn provides an index signal for counter 72, decrementing counter 72 by one floor to indicate the floor number of the next lower floor. The output of memory 74 is thus changed to the address of that floor.

A third counter 80 is provided which is a continuous scan type counter, preferably of the binary type, which starts at ZERO, counts to a predetermined binary number in a predetermined period of time, and starts the next predetermined period of time at ZERO again, thus dividing each succeeding predetermined period of time into a plurality of intervals or time slots. The location of the same interval in any predetermined period of time is thus identified by the same binary number. The number of intervals in each scanning period is deter-

mined by the number of floors in the structure, with the number of intervals being at least as large as the number of floors. A five bit scan counter, for example, will provide 32 intervals before automatically resetting to ZERO and starting the next scanning period. If the number of floors is greater than 32, a six bit counter will provide 64 intervals, etc. The length of time for each interval is determined by the rate at which call information can be gathered from the car and corridor pushbuttons, which rate is limited due to noise pickup in the travelling cable. A time interval of 2 milliseconds has been found to be satisfactory. Thus, with a five bit scan counter, a predetermined scan period would be 32 times 2 or 64 milliseconds, with each of the 32 intervals occupying 2 milliseconds of the period. The scan counter 80 is controlled by a master system clock.

A second bit-by-bit comparator 82 is provided which compares the binary output word of counter 72, which describes the floor number of a discrete advanced car position, with the binary output of the scan counter 80. Comparator 82 provides a signal EQIZ during each predetermined period of time when the binary number of the scanning position of the scan counter 80 is equal to the binary word of counter 72. Signal EQIZ may thus be termed the serial advanced car position signal, as it locates the advanced car position at the specific interval or time slot of the scan which identifies the floor of the advanced car position.

A logic circuit 84 receives car and corridor calls, with 30 the car calls, up corridor calls, and down corridor calls each being in serial form, synchronized with the scan counter. Thus, a car call for a predetermined floor would appear in the time slot or interval for that floor, as developed by the scan counter. In like manner, up 35 and down corridor calls from specific floors would appear in their associated intervals of each scan period. The logic circuit 84 detects coincidence of a call for service, which the car is conditioned to serve, for the floor of the advanced car position. If the car travel di- 40 rection is up, the car is conditioned to consider car and corridor calls registered for the floors ahead of its travel direction. The car will handle all requests for up service ahead of it, and when there are no more requests for up service, it is conditioned to go to the high- 45 est registered call for down service, and then serve all requests for down travel registered ahead of it. Once no calls ahead of it request down service, the car is conditioned to go to the lowest call requesting up service, and handle all calls for up service ahead of it.

The coincidence of a call for service for the floor of the serial advanced car position signal is memorized by the logic circuit 84, and when the equality signal EQ2 is generated by the comparator 76, deceleration is immediately initiated, which prevents counter 70 from 55registering any further distance pulses. The count of counter 72 thus is not indexed, and when the car stops at the floor at which service was requested, the discrete advanced car position and the continuous advanced car position will both be the actual car position. If coincidence of a request for service for the floor of the discrete advance car position is not detected before the equality signal EQ2 is generated by comparator 76, the next distance pulse will cause the comparator to provide a signal for indexer 78, which indexes counter 72 to provide a binary number representing the number of the next floor at which the car can stop.

FIG. 3

FIG. 3 is a block diagram of floor selector 34, which presents a detailed functional view of a preferred embodiment of the invention, with like reference numerals in FIGS. 2 and 3 indicating like components, which will not be described in detail since they have already been described relative to FIG. 2.

More specifically, FIG. 3 includes a top/bottom reset 10 means 86 which is responsive to car landing detectors at the top and bottom floors to provide a load signal, termed LOAD N for the counters 70 and 72. Memories addressed by the specific terminal location output a binary word describing the location, i.e., a floor number 15 with respect to counter 72 and the location of the floor in the structure with respect to counter 70, which words are loaded into the counters when the LOAD N counter signal is generated.

A min/max decoder 88 is provided which detects ar20 rival of the continuous advanced car position at the top

and bottom floors and initiates terminal slowdown with

a signal TDS in the event coincidence of the serial advanced car position signal EQIZ with a call for service

for the approaching terminal does not occur before the

25 generation of the equality signal EQ2.

A read only memory 90 is provided which is preset to identify which intervals, if any, are not assigned to floors, and to identify the intervals which do not have up and down corridor calls, i.e., the upper and lower floors, respectively.

The logic circuit 84 of FIG. 2 is shown in greater detail in FIG. 3. Logic circuit 84 includes a call selector circuit 92, a synchronizer circuit 94, and a logic circuit 96. The call selector circuit 92 receives the serial advanced car position signal EQ1Z and detects any coincidence between signal EQ1Z and the serial up and down corridor calls, and car calls, 1Z, 2Z and 3Z, respectively. When coincidence is detected, a coincidence signal EIX is generated which is synchronized in the logic circuit 96 and applied to the synchronizer 94 as signal EI. The synchronizer determines if the request to stop at the floor of the advanced car position signal El occurs prior to the generation of the equality signal EQ2 by comparator 76. If the EI signal is received by the synchronizer 94 prior to its receiving the equality EQ2, a deceleration request signal DEC is generated which is processed by the logic circuit 96 to provide a signal ACCX for the speed pattern generator 48. If an El signal is not received by the time the equality signal EQ2 is generated, comparator 76 provides a signal for indexer 78, and indexer 78 provides a pulse-up or pulse-down signal PU or PD, respectively, for indexing counter 72 to output the binary word representing the floor number where the car can stop according to the predetermined deceleration schedule. The remaining signals shown in FIG. 3 will be described when the circuits for performing the various functions are described.

FIG. 4

Before describing the circuits which may be used in the floor selector 34, it will helpful to illustrate the development of some of the timing signals used in the operation of the floor selector. FIG. 4 is a timing diagram which illustrates the signals generated during scanning position ZERO, termed 00, of the scan counter 30 shown in FIG. 2, which will be assumed to be a 2 milli-

10

35

45

HTAN

IDLE LAZO

LOAD N

HIS

second interval. The system or master clock is a 32 Khz. signal, termed K32, from which the other timing signals are derived. Signals K16, K08, K04, K02, K01 and KP5 are 16 Khz., 8 Khz., 4 Khz., 2 Khz., 1 Khz., and 500 hz. square wave timing or clock signals, respectively, developed by dividing the basic clock signal K32 in a binary counter.

Clock signals K08S and K02S are developed by shifting clock signals K08 and K02, respectively, forward by

Clock signal STC is developed by inverting clock signals K01 and KP5 and using these inverted signals as inputs for a NAND gate ( $\overline{STC} = \overline{KO1} \cdot \overline{KP5}$ ).

Clock signals S1, S2, S3 and S4 are developed in the first, second, third and fourth quadrants, respectively, 15 PCR of each scanning position, with signal S1 being equal to KO1 KP5 KO2S, signal S2 being equal KO1·KP5·K02S, signal S3 being equal to KO1·KP5-KO2S, and signal S4 being equal to KO1 KP5 KO2S.

All of the preceeding signals are developed during 20 SAC each scanning position of scan counter 80.

Clock signals S100, S200 and S300 are developed only during scanning position 00 of scan counter 80, with signal S100 being equal to 00 S2, signal S200 being equal to 00 S2, and signal S300 being equal to 25 00·S3.

In order to better understand the following detailed description of circuits which may be used in the invention, the signals generated by the various circuits, and the functions thereof, are listed below. Timing signals 30

are not listed, as they are shown in FIG. 4. SIGNAL FUNCTION CAR TO ACCELERATE OR TRAVEL AT FULL SPEED ACCELERATION REQUEST ACC ACCX AVPO-AVP4 ADVANCED CAR POSITION IN BINARY CAR IS WITHIN 18" OF BOTTOM воттом TERMINAL CAR BYPASSING CORRIDOR CALLS

CALL ABOVE FLOOR OF ADVANCED BYPS CAR POSITION CALL BELOW FLOOR OF ADVANCED CB **CAR POSITION** SERIAL CAR CALLS

CALL ENABLE

CALL AT FLOOR DURING FIRST SCAN

DOWN CALL ENABLE

DOORS CLOSED CCY CFLY DCE DCL SERIAL DOWN CALLS DECELERATION REQUEST DEC DECS SYNCHRONIZED DEELERATION REQUEST DGD SIGNAL TO DRIVE "GO DOWN" INTERFACE RELAY

SIGNAL TO DRIVE "GO UP" INTERFACE

RELAY

SIGNAL TO DRIVE LANDING

DGU DL2

INTERFACE

DOOR OPEN REQUEST ENABLE

DOOR OPEN REQUEST DOR DOOR OPEN REQUEST

RESET-DOOR OPEN REQUEST

SIGNAL WHICH IS TRUE WHEN CAR IS

SET TO TRAVEL DOWN

DISTANCE PULSES

SERIAL DOWN CORRIDOR CALL RESET

SPEED PATTERN FROM DISTANCE

STOWDOWN CIRCUIT DORR DOWN

DNRZ DSAN

SLOWDOWN CIRCUIT DRIVING SIGNAL FOR DSAN SWITCH DOOR MASTER RELAY DRIVER DSSW D45

CALL AT

ADVANCED CAR

POSITION

E1X EQ1Z EQ2 REQUEST FOR STOP SERIAL CAR POSITION

ADVANCED CAR POSITION EQUAL TO

FLOOR LEVEL FSC FIRST SCAN

HLd ENABLE FOR DOWN HALL LANTERNS ENABLE FOR UP HALL LANTERNS HALL LANTERN ENABLE HLU

SIGNAL FROM HATCH TRANSDUCER

SIGNAL FROM HATCH TRANSDUCER CIRCUIT DRIVER SIGNAL FOR HTAN SWITCH

CAR IDLE, READY TO MAKE RUN

CAR ±10 INCHES FROM FLOOR LEVEL LOAD CAR POSITION COUNTERS CAR WITHIN 18 INCHES OF MAIN

MAIN FLOOR MINA MAXIMUM DECELERATION мтоо MEMORY TRACK MEMORY TRACK MAXIMUM VELOCITY MTO1 MXVM LOGIC ZERO WHEN NO CALLS LOGIC ZERO WHEN NO CALLS INPUT PULSES TO COUNTER 544

NCS NLC OUTPUT OF DISTANCE TO GO TO LANDING COUNTER 544 **NL12** NL16 CAR IS WITHIN 16 INCHES OF LANDING

ZONE. INDICIATES ADVANCED CAR FLOOR POSITION HAS CHANGED

PULSE ADVANCED CAR POSITION

COUNTER DOWN ΡĎ

PLSDP PULSES FROM TERMINAL SLOWDOWN BLADE PULSE ADVANCED CAR POSITION UP

SCANNING ABOVE ADVANCED CAR POSITION SBC SCANNING BELOW ADVANCED CAR

POSITION SDT SET SELECTOR FOR DOWN TRAVEL SPEED SELECTION SWITCH TERMINAL OVERSPEED DETECTED SPEED SELECTION NO. 1 SPEED SELECTION NO. 2 SPSW SPS1

SPS2 SRAT SPEED PATTERN SIGNAL FOR MOTOR CONTROLLER START

SIGNAL TO START CAR IN RESPONSE TO ACCELERATION REQUEST SET SELECTOR FOR UP TRAVEL SOS-

SCANNING SIGNALS

TERMINAL STOP SIGNAL

CAR WITHIN 18' OF TOP FLOOR

EXCESSIVE TERMINAL OVERSPEED

AUXILIARY SPEED PATTERN USED S4S TDS TOP TOVSP **TSAN DURING TERMINAL SLOWDOWN** TSD CAR ON TERMINAL SLOWDOWN WHEN

TRAN TIME DEPENDENT SPEED PATTERN DRIVER SIGNAL FROM TRAN UP CALL ENABLE UCE

SERIAL UP CORRIDOR CALLS SIGNAL WHICH IS TRUE WHEN CAR IS SET TO TRAVEL UP 40 UPRZ SERIAL UP CORRIDOR CALL RESET UP TRAVEL

UPTR ZO2 CAR WITHIN 2 INCHES OF FLOOR LEVEL

SERIAL UP CORRIDOR CALLS SERIAL DOWN CORRIDOR CALLS SERIAL CAR CALLS

#### FIGURE 5

FIG. 5 is a schematic diagram of a reversible counter, a decoder, a read only memory, a comparator, and an indexer, which may be used for the counter 70, min/max decoder 88, the memory 74, the comparator 76, and indexer 78 shown in FIG. 3, with like reference numerals in FIGS. 3 and 5 indicating like components.

Counter 70 includes a plurality of 4 bit synchronous 55 binary counters, with four counters 100, 102, 104 and 106 being illustrated. The actual number of bits, and thus the actual number of cascaded counters required. depends upon the standard increment used to provide the distance pulses, and the distance between the lowest and uppermost floors.

Counter 70 requires that the distance pulses, termed DPL pulses, which are generated by the governor sheave 26 and converted to logic level by the pulse detector 32 shown in FIG. 1, be generated at double rate during acceleration of the car, to establish a continuous advanced car position, at normal rate after the car reaches maximum velocity, and to be discontinued when the car initiates deceleration, in order for the advanced car position and actual car position to coincide as the car comes to a stop at a landing. The DPL pulses must be directed to the count-up or count-down inputs of counter 70, depending upon the direction of car travel. The speed pattern generator 48 requires that it receive the distance pulses at the rate they are generated at all times during car movement. All of these functions are provided by the circuit which includes first and second type D, positive edge triggered flipflops 108 and 110, a cross-coupled NAND gate flipflop 112, first, second, third, fourth fifth, sixth and seventh NAND gates 114, 116, 118, 120, 124 and 134, respectively, first, second, third, fourth, fifth, sixth and seventh NOT gates or inverters 125, 126, 128, 130, 132, 133 and 135, respectively.

The DPL distance pulses are applied to an input terminal which is identified with the same letters as the signal applied thereto, as are the input and output terminals in all of the various figures to be described herein. Input terminal DPL is connected to the D input 20 of flip-flop 108. Clock signals K08 are connected to the C input of flip-flop 108 via inverter 125. The Q output of flip-flop 108 is connected to the D input of flip-flop 110 and to an input of NAND gate 114. The  $\overline{Q}$  output of flip-flop 108 is connected to an input of NAND gate 25 116. Clock signals K08S are connected to the C input of flip-flop 110. The Q and  $\overline{Q}$  inputs of flip-flop 110 are connected to inputs of NAND gates 116 and 114, respectively. Input terminal MXVM is connected to an input of NAND gate 116. Signal MXVM, as will be 30 hereinafter described, is generated by the speed pattern generator 48, with signal MXVM going to logical ZERO when the elevator car reaches maximum veloc-

The output of NAND gate 114 is connected to an input of NAND gate 134, and via inverter 126 to an output terminal NLC. Output terminal NLC provides distance pulses NLC when pulses are generated by the governor sheave, at the same rate that they are generated. The output of NAND gate 116 is connected to the other input of NAND gate 134.

The output of NAND gate 134 is connected to inputs of both NAND gates 118 and 120.

Flip-flop 112 is a travel direction flip-flop, with its set input S connected to an input terminal UP via inverter 133, and its reset input connected to an input terminal DOWN via inverter 135. Signals UP and DOWN are logic signals responsive to the direction of car travel, with signal UP being a logical ONE when the car is travelling up and signal DOWN being a logical ONE when the car is travelling down. The useful output of flip-flop 112 is termed  $\overline{\rm DN}$ , and it is connected to an input of NAND gate 118, and to an input of NAND gate 120 via inverter 128.

An input terminal ACC is connected to the remaining inputs of both NAND gates 118 and 120. Signal ACC, which is provided by the speed pattern generator 32, becomes true or a logical ONE when the brake relay for the drive motor is picked up, and false or a logical ZERO when the car is requested to initiate deceleration

The output of NAND gate 118 is connected to an input of NAND gate 122 via inverter 130. The output of NAND gate 120 is connected to an input of NAND gate 124 via inverter 132. The remaining inputs of NAND gates 122 and 124 are connected to the MAX and MIN outputs of min/max decoder 88, and, as will

hereinafter be explained, signal MAX becomes true, or logical ZERO when the output word of the continuous advanced car position (counter 70), is equal to the binary word describing the upper terminal floor, and signal MIN becomes true or logical ZERO when the output word of the continuous advanced car position is all ZERO's, describing the lower terminal floor.

In the operation of counter 70, it will be assumed that the car is set for up travel, with signal UP being true, 10 and the car is starting to accelerate. Input terminal UP is at the logical ONE level and input terminal DOWN is at the logical ZERO level, which, when both are inverted, sets flip-flop 112. The output signal DN will be at the logic ONE level, applying a logic ONE to an 15 input of NAND gate 118, and a logic ZERO to an input of NAND gate 120 via inverter 128. Thus, NAND gate 120 is blocked. When the brake relay is picked up, signal ACC will go to the logic ONE level, since the car is not decelerating. Thus, a pulse appearing at the output of NAND gate 134 will drive the output of NAND gate 118 low, and inverter 130 will apply a logic ONE to the input of NAND gate 122. As long as the continuous advanced car position is not at the upper terminal, MAX will be at the logic ONE level, and gate 122 will output a logic ZERO each time the output of NAND gate 134 goes low. The output of NAND gate 122 is connected to the "count up" input of counter 100.

NAND gate 134 is operated by the combination of flip-flops 108 and 110, and NAND gates 114 and 116, to output twice as many pulses as distance pulses received, until the car reaches maximum velocity, as signaled by MXVM going low. Flip-flop 108 receives distance pulses DPL at its D input from terminal DPL and it is clocked by timing signals K08 via inverter 125. The Q output of flip-flop 108 applies pulses at the rate of the distance pulses to NAND gate 114, and NAND gate 114 provides an input to NAND gate 134 and to the NLC output terminal. Thus, as long as distance pulses are received, they will be applied at the rate they are received to an input of NAND gate 134 and to output terminal NLC.

Flip-flop 110 has its D input connected to the Q output of flip-flop 108, and it is clocked by timing signals K08S, which is the K08 clock signal shifted forward by 90°. This arrangement causes flip-flop 110 to switch 90 degrees later than flip-flop 108 in the 8 Khz. clock signal, resulting in, for each distance pulse, output Q of flip-flop 108 and output  $\overline{Q}$  of flip-flop 110 both being at the logic ONE level for 90 degrees, driving the output of NAND gate 114 low for 90 degrees. This overlapping occurs at the start of the positive Q output of flip-flop 108, and the termination of the  $\overline{Q}$  output of flip-flop 110, which provides the pulse near the start of the DPL pulse.

This overlapping of logic ONE states also occurs between the  $\overline{Q}$  and Q outputs of flip-flops 108 and 110, respectively, at the termination of the Q output of flip-flop 110 and at the start of the  $\overline{Q}$  output of flip-flop 108, providing a pulse at the output of NAND 116 near the termination of a DPL pulse, which pulse is therefore spaced from the pulse provided at the output of NAND gate 114 in response to a DPL pulse.

Since the outputs of NAND gates 114 and 116 are high until driven low near the start and finish of a DPL pulse, respectively, the output of NAND gate 134 is driven high twice for each DPL pulse, thus providing pulses to the count-up input of counter 100 at twice the

DPL rate, while pulses are provided at the same rate as the DPL pulses at output terminal NLC.

When the car reaches maximum velocity, signal MXVM goes low, blocking gate 116, and the count-up input of counter 100 then receives pulses at the same 5 rate as the distance pulses are received. When deceleration of the car is initiated, signal ACC goes low, blocking gate 118 from sending any further pulses to counter 100, enabling the count of counter 70 to coincide with the actual car position as the car comes to a stop at a 10 landing.

When the car is travelling downwardly, the direction flip-flop 112 blocks NAND gate 118 and enables NAND gate 120, directing the output of NAND gate 134 to the count-down input of counter 100 via NAND 15 gate 124, as long as  $\overline{\text{MIN}}$  is high.

The min/max decoder 88 forces deceleration of the car when the continuous advanced car position, indicated by the count of counter 70, reaches either terminal, and it also blocks counter 70 from registering any 20 further distance pulses when this situation occurs. The MAX output of decoder 88 is responsive to a plurality of diodes 138 connected to the output of counter 70 which are at the logic ONE level when the continuous advanced car position is equal to the binary word describing the position of the upper terminal floor. When these diodes all have their cathode electrode connected to a logical ONE, the input side of an inverter 140, which is connected to the anode electrodes of the diodes, goes high, and the output of inverter 140 is driven 30 low to provide a true MAX signal.

The MIN output of decoder 88 is responsive to a plurality of serially connected inverter/diode combinations, referred to generally with reference numeral 142, which are connected to the outputs of counter 70. 35 When the outputs of counter 70 are all at the logic ZERO level, indicating that the continuous advanced car position is the lowest floor, the input side of an inverter 144, which is connected to the anode electrodes of the diodes, is high, due to the inverters, and the output of inverter 144 is at the logic ZEKO level.

The MIN and MAX outputs are used to terminate the counting of counter 70, as hereinbefore described, and they are also used to initiate terminal slowdown via the circuit which includes input terminals BOTTOM, TOP, UP and DOWN, inverters 146, 148 and 150, NAND gates 152, 154, 156, 158 and 160 and output terminal TDS.

Input terminals BOTTOM and TOP are connected to limit switches in the hatchway, which cause the BOTTOM and TOP input terminals to be at a logical ONE level when the car is within 18 inches of the bottom and top floors, respectively. Thus, NAND gates 152 and 154 are enabled as long as the car is not within 18 inches of either terminal. NAND gates 156 and 158 are responsive to car direction, with NAND gate 156 being enabled when the car is set to travel downwardly, and NAND gate 158 being enabled when the car is set to travel upwardly.

In the operation of the min/max decoder, assume that the car is travelling upwardly. Signals MIN and MAX are both at the logic ONE level, as are the inverted BOTTOM and TOP signals. Thus, the outputs of NAND gates 152 and 154 are at the logic ZERO level, the outputs of NAND gates 156 and 158 are both at the logic ONE level, the output of NAND gate 160 is at the logic ZERO level, and the output of inverter 150 is a

logic ONE, providing a high or false TDS signal. When the output of counter 70 reaches the binary word which describes the upper floor, signal MAX goes low, the output of NAND gate 154 goes high, the output of NAND gate 158 goes low, the output of NAND gate 160 goes high, and the output of inverter 150 goes low, the true level for the terminal slowdown signal TDS. Signal TDS is applied to the synchronizer 94, as will be hereinafter explained.

In a similar manner, when the car is travelling downwardly and signal  $\overline{\text{MIN}}$  goes low, indicating that the continuous advanced car position has arrived at the lower terminal, the output of NAND gate 152 goes high, the output of NAND gate 156 goes low, the output of NAND gate 160 goes high, and the output of inverter 150 goes low.

Memory 74, which may be a read-only memory such as Intersil No. IM 5600, is arranged, at the time of the installation of the elevator, to output a binary number which is the exact binary address of the floor relative to the structure, using the standard increment, represented by the binary number which is responsive to the floor of the discrete advanced car position, as determined by counter 72.

Comparator 76 includes a plurality of bit-by-bit comparators 162, 164, 166 and 168, having an input for the 'A" word connected to outputs of counters 100, 102, 104 and 106, and an input for the "B" word connected to the output of memory 74. Memory 74 is of the type which has three outputs. An A < B output which is at the logic ONE level when the word A is less than the word B, an A = B output which is at the logic ONE level when the words are equal, and an A > B output which is a logical ONE when the word A is larger than the word B. The A < B output is connected to the D input of a type D positive edge triggered flip-flop 170, the A = B output is connected to the D input of flip-flop 174, and the A > B output is connected to the D input of a flip-flop 170. The clock inputs of these flip-flops is connected to receive clock signals K32 via an inverter 176. The Q outputs of flip-flops 170 and 172 are connected to indexer 78, while the Q output of flip-flop 174 is connected to output terminal EQ2 via inverter 178. 45 Output terminal  $\overline{EQ2}$  provides the equality signal  $\overline{EQ2}$ when the continuous advanced car position arrives at the floor level of the discrete advanced car position.

In the operation of comparator 76, it will first be assumed that the car is travelling upwardly. Word A will thus be less than word B, and the A < B output will be at the logic ONE level, while the other outputs are at the logic ZERO level. Flip-flop 172 thus outputs a logical ONE signal while the outputs of flip-flops 170 and 174 are low. When input words A and B are equal, indicating the car must now initiate slowdown if it is to stop at the floor of the discrete advanced car position according to a predetermined deceleration schedule, the A = B output goes to logical ONE, flip-flop 174 outputs a logical ONE, and signal EQ2 goes low or true. If deceleration is initiated, signal ACC goes low and the counter 70 remains at the count of the discrete advanced car position, and word A will continue to equal word B until the car stops, and then starts to move away from the floor. If deceleration is not initiated when the A = B output is high, the first distance pulse after equality will cause the A>B output of the comparator to go high, and flip-flop 170 outputs a logical ONE.

The indexer 78 is responsive to the outputs of flipflops 170 and 172, to index the discrete advanced car position to represent the next floor at which the car can stop. Indexer 78 includes NAND gates 182, 184, 186 and 188, inverters 190 and 192, it is responsive to input terminals UP, DOWN, ACC, and S100, and it is connected to output terminals PU and PD which are connected to counter 72, and to synchronizer 94. NAND gates 182 and 184 have inputs connected to the UP and DOWN input terminals, respectively, and each have 10 inputs connected to input terminal ACC. Thus, when the car is travelling upwardly and the car is not decelerating, NAND gate 182 outputs a ZERO, which is inverted to enable NAND gate 186. NAND gate 184 outgate 188. In a similar manner, when the car is travelling downwardly, NAND gate 186 is blocked and NAND gate 188 is enabled. Thus, when the car is travelling upwardly, the A <B output of comparator 176 and its associated flip-flop 172 have no circuit affect, as NAND 20 gate 188 is blocked. As soon as the A> B output goes to the logic ONE level, the output of flip-flop 170 goes high and the S100 strobe, which occurs only during scanning interval 00 of the scan counter 80, drives the output of NAND gate 186 low, which is the true level 25 for signal PU. When signal PU goes low, it advances counter 72 to indicate the next higher floor number, and the output of memory 74 changes to indicate the floor address of that floor, which number is again higher than the continuous advanced car position. The A < B output of comparator 76 thus goes high while its other outputs are low.

When the car is travelling downwardly, the A word responsive to the continuous advanced car position is larger than the B word responsive to the discrete ad- 35 vanced car position, and the A<B output of comparator 76 is high, which has no circuit affect since gate 186 is blocked. When the continuous advanced car position reaches the discrete advanced car position, the A = Boutput goes high and signal EQ2 goes low. If deceleration is initiated the counter 70 is blocked by signal ACC going low. If deceleration is not initiated, counter 70 continues to count down, and as soon as the A<B output goes high, flip-flop 172 goes high and the output of NAND gate 188 will go low upon receiving the S100 strobe during scanning slot 00, to index the counter 72 with a true or low PD signal to represent the next lower floor. When the counter 72 is indexed, the comparator 76 will output a logical ONE at the A>B output, and the above sequence is repeated.

#### FIGURE 6

FIG. 6 is a schematic diagram of a reversible counter, a top/bottom reset, and a comparator, which may be used for counter 72, top/bottom reset 86, and comparator 82 shown in FIG. 3. Like reference numerals in FIGS. 6 and 3 indicate like components.

Counter 72 includes the necessary number of cascaded synchronous 4-bit binary counters required to represent the number of the floors in the associated structure, with two counters 194 and 196 being illustrated. The count-up input of counter 194 is connected to input terminal PU, which receives index pulses from indexer 78, and the count-down input of counter 194 is connected to input terminal PD, which receives index pulses from indexer 78. Th output of counter 72 is connected to memory 74, hereinbefore described,

via output terminals AVPO, AVP1, AVP2, AVP3 and AVP4, and to one input of comparator 82. Comparator 82 is a bit-by-bit comparator, which has its other input connected to the scan counter 80. Comparator 82 has three outputs, an A<B output which is high when the output of scan counter 80 is less than the binary output word of counter 72, an A = B output which is high when the scan counter is at the time slot of the discrete advanced car position, and an A > B output which is high when th output word of the scan counter 80 exceeds the output word of counter 72.

The outputs of comparator 82 are used to develop the serial advanced car position signal EQ1Z, the scanning below the discrete advanced car position signal puts a logic ONE which is inverted to block NAND 15 SBC, and the scanning above the discrete advanced car position signal SAC. These signals are developed by a circuit which includes an input terminal STC, which receives a strobe signal STC which occurs during each scanning slot of scan counter 80, as represented in FIG. 4, an input terminal PCR, which receives a PCR signal which is low or true each time the indexer 78 provides an index signal PU or PD, as will be explained when the synchronizer 94 is described, NAND gates 198, 200 and 202, inverters 204, 206 and 208, and output terminals SBC, EQ1Z and SAC.

In the operation of comparator 82, when the scan counter 80 is scanning (counting) below the floor of the discrete advanced car position, the A<B output is high, which is strobed by signal STC during each scanning slot to provide a low output from NAND gate 198, which is inverted by inverter 204 to provide a high or true SBC signal.

When the scan counter 80 reaches the count which represents the floor of the advanced car position, the A = B output goes high, and the output of NAND gate 200 goes low when  $\overline{STC}$  goes high, as long as the counter 72 is enabled by a high PCR signal (counter 72 not being indexed). The low output of NAND gate 200 is inverted by inverter 206 to provide a true EQ1Z serial advanced car position signal in the proper scanning slot of scan counter 80. When the scan counter 80 passes the count of the discrete advanced car position, the A > B output goes high and NAND gate 202 outputs a logical ZERO when strobe STC goes high during each scanning slot. The low output of NAND gate 202 is inverted by inverter 208 to provide a high or true SAC signal, which indicates scanning above the discrete advanced car position.

The top/bottom reset 86 resets both of the reversible counters 70 and 72 with the proper count at both the top and bottom floors, to start the elevator car from either terminal with the proper count, prior to a run which is initiated from these floors.

The top/bottom reset 86 includes NAND gates 210, 212, 214, 216, 218 and 220, a read only memory 222, inverters 224, 226, 228, 230, 232 and 234, input terminals TOP, BOTTOM, MAIN, DL2, Z02 and S100, and an output terminal LOAD N.

NAND gate 210 has its inputs connected to input terminals DL2 and Z02, with signal DL2 being a signal developed by the speed pattern generator 48 when the car is going to stop at a landing. When DL2 is at the logic ZERO level, it corresponds to "run," and when DL2 is at the logic ONE level it corresponds to "land." Signal ZO2 is developed by a limit switch in the hatchway, with signal ZO2 being a logic ONE when the car is within 2 inches of the landing level. The signals TOP. BOTTOM and MAIN are developed by switches in the hatchway, and are at the logic ONE level when the car is within 18 inches of the top, bottom and main floors, respectively. If the bottom floor is the main floor, the MAIN input terminal and NAND gate 214 may be 5 eliminated. The S100 input terminal receives clock pulse S100 generated during scan slot 00 of the scan counter 80. The output of NAND gate 218 is connected to counter 72, and also to the LOAD N output terminal, which terminal is connected to counter 70 10 shown in FIG. 5.

Read-only memory 22 is set to output the floor number in binary of the specific floor addressing the memory. For example, when the output of NAND gate 212 goes low, memory 222 will output the floor number of 15 the bottom floor, which is 00001. When the output of NAND gate 216 goes low, memory 222 will output the number of the top floor, which in our 30 floor example, would be 11110.

When the elevator car is at a floor other than a floor 20 at which the counters are reset, the inputs to NAND gate 220 will all be high and its output will be low, blocking NAND gate 218. When the car arrives at one of the reset floors, NAND gate 210 enables the NAND gates 212, 214, and 216, and depending upon which 25 reset floor the car is located at, one of these NAND gates addresses the read-only memory 222 and enables NAND gate 220. Clock signal S100 in scanning slot 00 of the scan counter drives the output of NAND gate 218 low, which loads the proper floor number into 30 counter 72. Counter 72 is thus forced to the correct output number, and this output addresses memory 74 of FIG. 5. Memory 74 provides the exact location of the floor relative to the structure, in terms of the standard increment. In addition to the output of memory  $74^{-35}$ being used by comparator 76, the output of memory 74 is also connected to the load input of counter 70, as illustrated in FIG. 5. The LOAD N signal from the top/bottom reset 86 is connected to the LOAD N input of terminal 70, and when the  $\overline{LOAD\ N}$  signal goes low,  $^{40}$ the output of memory 74 is loaded into counter 70, to always start counter 70 with the correct count at each reset floor. This resetting of counters and memories at the selected reset floors occurs automatically during the operation of the elevator car. If power is lost during the operation of the elevator, causing the counters to lose their count, normal system operation is achieved, following power return, by running the car manually to one of the reset floors.

#### FIG. 7

FIG. 7 is a timing diagram for a thirty floor building, illustrating the various scanning slots or intervals of the scan counter 80, and the relationship of selected signals thereto, such as car calls and up and down corridor calls. Since the building of the example has thirty floors, the scan counter 80 may be a 5-bit counter, which provides 32 intervals or slots for each scan. Since it is assumed that each interval is 2 milliseconds, the scan time for each scanning period is 64 milliseconds. If the building has more than thirty-two floors, a 6-bit counter would be used to handle structures with 33 through 64 floors, and a 7-bit scan counter would handle structures with 65 through 128 floors. The other counters and memories would be selected accordingly.

The car calls, referred to as signals 3Z are serialized and synchronized with the scan counter 80 to appear

in the time slot for the floor which they request the car to travel to. For example, each of the car pushbuttons may be connected by a wire to a gate, with the gates being sequentially enabled by the output of the scan counter, such that scanning slot 00 would enable the gate associated with the first floor, etc. The outputs of the gates would be collected to present the car call information in serial form. For purposes of example, it will be assumed that the car is travelling downwardly, the discrete advanced car position, represented by signal EQ1Z, is at the 20th floor, and the car has car calls (signal 3Z) for the 19th, 15th, 11th, 10th and fourth floors.

The up and down corridor calls, represented by signals 1Z and 2Z, respectively, may also be gated by the scan counter 80 to serialize and synchronize the calls into the scanning slots associated with the floor number from which they are registered. As illustrated in FIG. 7, up corridor calls 1Z are separately serialized, with calls for up service being registered from the 10th and 13th floors. Down corridor calls 2Z are registered for the seventh and 22th floors.

Signals MTOO and MTO1 shown in FIG. 7 are provided by read-only memory 90 shown in FIG. 3, and are used as enabling signals to insure that the scanning slots of the scan counter not used to represent floors are disregarded, as well as disregarding the scanning slots for the uppermost and lowermost floors when considering up and down corridor calls, respectively. Thus, memory track MTOO, which is used to enable up corridor calls 1Z, is a logic ONE for scanning slots 00 through 28, representing floors 1 through 29, and a logic ZERO for scanning slots 29, 30 and 31. Memory track MTO1 is used to enable down corridor calls 2Z, and is thus a logic ONE for scanning slots 01 through 29, representing floors 2 through 30, and a logic ZERO for scanning slots 00, 30 and 31.

Signal CEN is a call enable signal, for car calls, provided by a read-only memory track, such as from read-only memory 90. Signal CEN may simply be used to insure that the scanning slots not used to represent floors are disregarded by the car call circuits; or, as illustrated by the alternate CEN signal in FIG. 7, it may be used to prevent the car from going to specific floors in response to a car call, such as floors 15, 20 and 30.

The remaining signals shown in FIG. 7 are clock signals developed in FIG. 4, and hereinbefore described.

In the timing diagram of FIG. 7, the car, which is travelling downwardly, would stop at the floors for which car calls 3Z are registered, and it would stop at the seventh floor to serve the registered down call 2Z for that floor. When the car has served its last call in the down direction, it will proceed to the lowest registered up corridor call, and then handle all of the registered up calls. Upon handling the last call for service in the up direction, the car will proceed to the highest registered down call. The circuitry for operating the car in this manner will be hereinafter described.

#### FIG. 8

FIG. 8 is a schematic diagram of a call selector which may be used for the call selector 92 shown in FIG. 3. The primary function of the call selector 92 is to detect coincidence between the floor of the discrete advanced car position signal EQ1Z and a request for service for that floor, and to provide a request to stop signal EIX when such coincidence is detected. Auxiliary functions

of the call selector 92 are the resetting of corridor calls, the enabling of the hall lanterns, providing the door open request, and detecting a call at the floor at the start of each run.

More specifically, call selector 92 includes input ter-5 minals  $\overline{1Z}$ ,  $\overline{2Z}$  and  $\overline{3Z}$  for receiving the serial up and down corridor calls and car calls, respectively, input terminals TM00, MT01 and CEN for receiving the memory track signals MT00, MT01 and CEN, respectively, input terminals UCE and DCE for receiving up 10 and down call enable signals, respectively, for logic circuit 96, input terminals DCL, DO and DORR for receiving door closed, door open enable, and door reset signals, respectively, input terminal UPTR which receives a signal from logic circuit 96 which indicates direction of car'travel, input terminal FSC which receives a signal from logic circuit 96 when the first scan is initiated at the start of a run, and input terminal S4 for receiving timing pulses during each scanning slot.

The serial advanced car position signal EQ1Z ap- 20 pears at input terminal EQ1Z in the scanning slot allocated to its specific floor position, and it is strobed by clock signal S4 through NAND gate 240, inverted by inverter 242, to appear at the logic ONE level at the input of each of the NAND gates 244, 246 and 248. 25

Serial up corridor calls which appear at input terminal  $\overline{1Z}$  are inverted by inverter 250, screened by memory track signal MT00 through NAND gate 252, inverted to the logic ONE level by inverter 254, applied to an input of each of the NAND gates 244, 256, and also via inverter 258 to output terminal  $\overline{UCY}$ , which provides serial up corridor calls as screened by memory track  $\overline{MT00}$ .

Serial down corridor calls which appear at input terminal  $\overline{2Z}$  are inverted by inverter 260, screened by memory track signal MT01 through NAND gate 262, inverted to the logic ONE level by inverter 264, applied to an input of each of the NAND gates 246 and 266, and also via inverter 268 to output terminal  $\overline{DCY}$ , which provides serial down corridor calls, as screened by memory track MT01.

Serial car calls which appear at input terminal  $\overline{3Z}$  are inverted by inverter 270 and applied to an input terminal of each of the NAND gates 272 and 248. The car call enable signal applied to input terminal  $\overline{CEN}$  is inverted by inverter 274 and applied to another input on each of the NAND gates 272 and 248. Car calls for floors for which the car is enabled appear at the output of NAND gate 272 and at the output terminal  $\overline{CCY}$ .

When the up call enable signal at input terminal UCE, which is received from logic circuit 96, is at the logic ONE level, NAND gates 244, 256 and 276 are enabled. At this time, the down call enable signal at input terminal DCE will be at the logic ZERO level, blocking NAND gates 246, 266 and 278. When the down call enable signal at input terminal DCE, which is also received from logic circuit 96, is at the logic ONE level, signal UCE will be at the logic ZERO level, NAND gates 246, 266 and 278 will be enabled, and NAND gates 244, 256 and 276 will be blocked.

The outputs of NAND gates 244, 246 and 248 are normally high when no coincidence of the discrete advanced car position and a call for service for that floor is detected, and since these outputs are all connected to an input of NAND gate 280, the NAND gate 280 outputs a logic ZERO in the absence of coincidence, which is inverted to the logic ONE level by inverter

282. Thus, the signal at output terminal  $\overline{EIX}$ , which is the request to stop signal, is false or at the ONE logic level in the absence of coincidence.

When a corridor or car call is registered for the floor of the discrete advanced car position, signal  $\overline{EIX}$  goes true or low in the following manner. If the coincidence detected is an up corridor call, and the car is enabled for up calls, the input signals to NAND gate 244, i.e., UCE, strobed EQ1Z, and UCX, with the latter indicating screened up corridor calls, will all be at the logic ONE level simultaneously during the scan slot of the floor of the discrete advanced car position, driving the output of NAND gate 244 low, the output of NAND gate 280 high, and the output terminal  $\overline{EIX}$  low via inverter 282.

If the coincidence detected is a down corridor call, and the car is enabled for down calls, the input signals for NAND gate 246, i.e., DCE, strobed EQ1Z and DCX, the latter indicating screened down corridor calls, will all be at the logic ONE level simultaneously during the scan slot of the floor of the discrete advanced car position, driving the output of NAND gate 246 low, the output of NAND gate 280 high, and the output terminal EIX low.

If the coincidence detected is a car call, and the car is enabled for the floor of the discrete advanced car position signal, the input signals CEN, strobed EQ1Z, and 3Z for NAND gate 248 will all be at the logic ONE level simultaneously during the scan slot of the floor of the discrete advanced car position, driving the output of NAND gate 248 low, the output of NAND gate 280 high, and output terminal EIX low.

When the elevator car starts a run, the logic circuit 96 provides a true or low FSC signal during the first complete scan of scan counter 80, starting at timing signal S200 and ending at timing signal S100, which is applied to input terminal FSC of call selector 92. This true or low FSC signal is inverted by inverter 284, applying a logic ONE to an input of NAND gate 286. Since the discrete advanced car position and the actual car position are the same at the start of a run, signal EQ1Z will appear in the time slot for the floor where the car is located. If there is an up corridor call at the floor where the car is located, a true corridor signal UCX will be applied to an input of AND gate 256. If the car is enabled for up calls, signal UCE will be true, and if the car is set for up travel, signal UPTR will be true, driving the output of NAND gate 256 low.

In a similar manner, if there is a down corridor call at the floor where the car is located, a true down corridor signal DCX will be applied to an input of NAND gate 266. If the car is enabled for down calls, signal DCE will be true, and if the car is set for down travel signal UPTR will be false or high, driving the output of NAND gate 256 low.

The outputs of NAND gates 256 and 266 are connected to inputs of NAND gate 288. If there is no call at the floor, these outputs will be high and the output of NAND gate 288 will be low. If one of the outputs of the NAND gates 256 or 266 goes low, indicating a call at the floor, the output of NAND gate 288 will go high. When the output of NAND gate 288 goes high during the first scan, the output of NAND gate 286 goes low, which is inverted by inverter 290 and applied to an input of a NAND gate 292. The other input of NAND gate 292 is connected to receive clock signal S4, which signal strobes the call at the floor through NAND gate

292 where it is applied to an input terminal  $\overline{\text{CFLY}}$ , which indicates a call at the floor. The output of NAND gate 292 is also applied to one of the set inputs of a first door flip-flop 294. Flip-flop 294 may be of the cross-coupled NAND gate type, having NAND gates 295 and 5297.

Set inputs of the first door flip-flop 294, i.e., the inputs of NAND gate 295, are also connected to be responsive to the outputs of NAND gates 244, 246 and 248. Thus, a call at the floor, or a request to stop for 10 a car call or a corridor call, will set the first door flipflop 294, providing a logic ONE at the output of NAND gate 295, and a logic ONE at the input of NAND gate 296. The other input of NAND gate 296 is connected to input terminal DO, which is at the logic ONE level 15 when the door open request is enabled. Thus, when NAND gate 296 is enabled by a high DO signal and flip-flop 294 is set, a second door flip-flop 298 will be set. Flip-flop 298 may be of the cross-coupled NAND gate type, having NAND gates 299 and 301. NAND 20 gate 299 provides a logic ONE at its output, which is inverted by inverter 300 and applied to output terminal DOR. A low DOR signal is a request to open the doors of the car, which request is directed to door operator circuits 52 shown in FIG. 1. The door operator circuits 25 may be conventional. When the non-interference or normal door open time times out, the door operator circuits 52 provide a low DORR signal at input terminal DORR, which resets the second door flip-flop 298. When the doors actually close, a low DCL signal, applied to input terminal DCL, initiated by a limit switch associated with the car and hatch doors, resets the first door flip-flop 294.

It will be noted that the second door flip-flop 298 may be set, initiating a door open request, by a low terminal slowdown signal TSD, applied to input terminal TSD, and connected to one of the set inputs of flip-flop 298. Thus, terminal slowdown, initiated by the speed pattern generator 48, as will be hereinafter described, will also initiate the opening of the car and hatch doors.

The output of inverter 300 is inverted by inverter 302 and connected to an input of each of the NAND gates 276 and 278, which also have inputs connected to receive up call enable and down call enable signals UCE and DCE, respectively. Thus, when the car is enabled for up calls and a door open request is initiated, the output of NAND gate 276 goes low, and this signal is inverted by inverter 304 and applied to an input of NAND gate 306. NAND gate 306 also has an input connected to receive the serial advanced car position signal EQ1Z. When the serial advanced car position signal EQ1Z goes high, the output of NAND gate 306 goes low, and this output is connected to output terminal HLU, which enables the up hall lantern for the floor of the serial advanced car position, and to output terminal UPRZ, which resets the up corridor pushbutton for the floor of the serial advanced car position. The hall lantern control 54 and corridor call control 46 shown in FIG. 1, which receives these enabling and reset signals, may be conventional.

In a similar manner, when the car is enabled for down calls, and a door open request is initiated, the output of NAND gate 278 goes low, and this signal is inverted by inverter 308 and applied to an input of NAND gate 310. The serial advanced car position signal EQ1Z is connected to another input of NAND gate 310, and when it is received, the output of NAND gate 310 goes

low, providing a low down hall lantern enable signal HLD, and a low or true down corridor reset signal DNRZ.

#### FIG. 9

FIG. 9 is a schematic diagram of a logic circuit which may be used for the logic circuit 96 shown in FIG. 3. The function of the logic circuit 96 is to receive the serial calls UCY, DCY and CCY for the call selector 92, determine where a call is relative to the serial advanced car position EQ1Z, determine in which direction the car should travel and provide travel direction signal UPTR in response thereto, enable the car for up or down calls with enable signals UCE and DCE, respectively, request starting of the car with a true ACCX signal when it is idle, in response to a call for service, provide the first scan signal FSC for the call selector 92. provide a high or true EI signal when there is a call at the floor of the serial advanced car position, provide a true or low  $\overline{ACCX}$  signal when a deceleration request is made by the synchronizer 94, and enable the hall lantern control with a true HLX signal.

More specifically, car and corridor calls are connected to selected inputs of NAND gates 320, 322, and 324, with the serial car calls, which are received at input terminal CCY being connected to an input terminal on all three of these NAND gates, the serial up corridor calls, which are received at input terminal UCY, 30 are connected to input terminals of NAND gates 322 and 324, and the serial down corridor calls, applied to input terminal DCY, are connected to input terminals of NAND gates 320 and 324. In the absence of any calls, the outputs of all three of these NAND gates will be low. A car call  $\overline{CCY}$  will drive the outputs of all three of these NAND gates high. An up corridor call UCY will drive the outputs of NAND gates 322 and 324 high. A down call DCY will drive the outputs of NAND gates 320 and 324 high.

The outputs of NAND gates 320, 322, and 324 are connected to selected inputs of NAND gates 326, 328, 330 and 332, with the output of NAND gate 320 being connected to an input of NAND gate 330, the output of NAND gate 322 connected to an input of NAND gate 328, and the output of NAND gate 324 connected to inputs of NAND gates 326 and 332.

NAND gate 326 also has an input connected to input terminal SAC, which receives a high or true SAC signal from comparator 82 in FIG. 6 when the scan counter 80 is scanning above the floor position of the serial advanced car position.

NAND gate 328 also has inputs connected to input terminal S4, which receives clock signals during each scanning slot, as shown in FIG. 7, to input terminal EQ1Z from comparator 82 which provides the serial advanced car position in the appropriate scanning slot, and to the output of a NAND gate 374 via inverter 323. The output of inverter 323 is high when a request is made to accelerate the car, as will be hereinafter explained.

NAND gate 330 also has inputs connected to the output of inverter 323, to input terminal EQ1Z, and to input terminal S4.

NAND gate 332 also has an input connected to input terminal SBC, which is true when comparator 82 indicates the scan counter 80 is scanning below the floor of the serial advanced car position signal EQ1Z.

The outputs of NAND gates 326, 328, 330 and 332 are connected to selected inputs of a "call above" flipflop 333, and a "call below" flip-flop 335. The call above flip-flop 333 includes two cross-coupled NAND gates 334 and 336, with inputs of NAND gates 334 being connected to outputs of NAND gates 326 and 328. An input of NAND gate 336 is connected to input terminal S300 via inverter 342, which resets the call above flip-flop 330 during scanning slot 00 of the scan counter 80.

The call below flip-flop 335 includes two cross-coupled NAND gates 338 and 340, with inputs of NAND gate 338 being connected to outputs of NAND gates 330 and 332. An input of NAND gate 340 is connected to input terminal S300 via inverter 342, to also 15 reset the call below flip-flop 335 during scanning slot 00.

The call above flip-flop 333 is set, triggering the output of NAND gate 334, referred to as signal CA, to a logic ONE level, by the output of NAND gate 326 20 going low, which indicates the scan counter 80 is scanning above the floor of the serial advanced car position, and while scanning there an up or down corridor call or car call was detected. When the output signal CA of NAND gate 334 goes high, the output of NAND gate 25 336, referred to as signal  $\overline{CA}$ , goes low. The call above flip-flop may also be set by the output of NAND gate 328 going low, which indicates that there is a request to accelerate, and a car or up corridor call at the floor of the car (the floors of the serial advanced car position 30 and the actual car position are the same). When the call above flip-flop is set during the scan cycle of scan counter 80, it is reset by signal \$300 during scanning slot 00.

The call below flip-flop 335 is set, triggering the output of NAND gate 338, referred to as signal CB, to a logic ONE level, and the output of NAND gate 340, referred to as  $\overline{CB}$ , to a logic ZERO level, by the output of NAND gate 332 going low. This indicates that the scan counter 80 is scanning below the floor position of the serial advanced car position, and while scanning there an up or down corridor call, or car call, was detected. The call below flip-flop 335 may also be set by the output of NAND gate 330 going low, indicating that there is a request to accelerate the car, and that there is a down corridor or car call at the floor where the car is located.