(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6859945号

(P6859945)

(45) 発行日 令和3年4月14日(2021.4.14)

(24) 登録日 令和3年3月30日(2021.3.30)

(51) Int.Cl.

F 1

H04L 25/02 (2006.01)

H03K 17/16 (2006.01)

H03K 17/687 (2006.01)H04L 25/02

H04L 25/02

H03K 17/16

H03K 17/687F

V

D

請求項の数 12 (全 14 頁)

(21) 出願番号

特願2017-247635 (P2017-247635)

(22) 出願日

平成29年12月25日(2017.12.25)

(65) 公開番号

特開2019-114948 (P2019-114948A)

(43) 公開日

令和1年7月11日(2019.7.11)

審査請求日

令和1年12月2日(2019.12.2)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 110000567

特許業務法人 サトー国際特許事務所

(72) 発明者 本田 阜矢

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 岸上 友久

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

審査官 川口 貴裕

最終頁に続く

(54) 【発明の名称】 リンギング抑制回路

## (57) 【特許請求の範囲】

## 【請求項 1】

一対の高電位側信号線、低電位側信号線によりハイ、ローの2値レベルに変化する差動信号を伝送する伝送線路に接続され、前記信号の伝送に伴い発生するリンギングを抑制するリンギング抑制回路において、

前記一対の信号線間に接続される線間スイッチング素子(N4, P4)と、

前記差動信号のレベルがハイからローに変化したことを検出すると、前記線間スイッチング素子をオンさせてその状態を固定し、一定のオン時間を計時した後に前記オン状態を解除する制御部(9)と、

この制御部が前記線間スイッチング素子をオンさせた時点から一定のマスク時間を設定し、前記マスク時間内は、前記制御部が前記差動信号のレベルがハイからローに変化したことを検出しないようにマスクする連続起動防止部(22, 42)とを備えるリンギング抑制回路。

## 【請求項 2】

前記マスク時間の終了時点は、前記差動信号のレベルがハイからローに変化した時点から、信号データの1ビット長以上で且つ2ビット長未満に設定される請求項1記載のリンギング抑制回路。

## 【請求項 3】

前記制御部は、

初期状態でリセットされている第1フリップフロップ(FF2)と、

10

20

初期状態でリセットされており、セット状態になると前記第1フリップフロップをリセットするための信号を出力する第2フリップフロップ(FF1)と、

この第2フリップフロップの出力端子と前記第1フリップフロップのリセット端子との間に配置される遅延回路(6)と、

前記差動信号のレベルがローからハイに変化したことを検出すると、前記第1フリップフロップをセットする信号を出力する第1セット信号出力部(4, F E T\_N7)と、

前記線間スイッチング素子がターンオンしたことを検出すると、前記第2フリップフロップをセットする信号を出力する第2セット信号出力部(3)と、

前記第1フリップフロップがセットされると、前記線間スイッチング素子の導通制御端子をオンレベルにすることを可能にするオン設定部(8)とを備える請求項1又は2記載のリンク抑制回路。 10

#### 【請求項4】

前記連続起動防止部(22)は、初期状態でリセットされており、前記第2フリップフロップがセットされることに伴いセット状態になると、前記マスク時間を設定するマスク信号を出力するフリップフロップ(FF3)と、

このフリップフロップがセットされた時点から、前記マスク時間に相当する時間が経過した時点で当該フリップフロップをリセットするリセット信号生成部(23)と、

前記第1フリップフロップをセットする信号を、前記マスク信号により無効化するための論理ゲート(AND1)とで構成される請求項3記載のリンク抑制回路。 20

#### 【請求項5】

前記論理ゲートは、前記第1セット信号出力部と、前記第1フリップフロップとの間に配置されている請求項4記載のリンク抑制回路。 20

#### 【請求項6】

前記論理ゲートは、前記第1セット信号出力部の前段に配置されている請求項4記載のリンク抑制回路。 20

#### 【請求項7】

前記連続起動防止部(32)は、初期状態でリセットされており、前記第1フリップフロップがセットされることに伴いセット状態になると、前記マスク時間を設定するマスク信号を出力するフリップフロップ(FF3)と、

このフリップフロップがセットされた時点から、前記マスク時間に相当する時間が経過した時点で当該フリップフロップをリセットするリセット信号生成部(33)と、 30

前記第1フリップフロップがセットされた信号を、前記マスク信号により無効化するための論理ゲート(AND1)とで構成される請求項3記載のリンク抑制回路。 30

#### 【請求項8】

前記第2セット信号出力部は、非電位基準側導通端子が抵抗素子(R3)を介して電源に接続され、電位基準側導通端子及び導通制御端子がそれぞれ前記線間スイッチング素子の電位基準側導通端子及び導通制御端子に接続される検出用スイッチング素子(N6, P6)を備え、

前記オン設定部は、電位基準側導通端子が前記線間スイッチング素子の電位基準側導通端子に接続される第1～第4スイッチング素子(N0～N3, P0～P3)と、 40

電位基準側導通端子が電源に接続され、非基準側導通端子が抵抗素子(R1)を介して、前記第2スイッチング素子の非基準側導通端子及び前記第3スイッチング素子の導通制御端子に接続される第5スイッチング素子(P1, N1)と、

電位基準側導通端子が電源に接続され、非基準側導通端子が抵抗素子(R2)を介して、前記第3スイッチング素子の非基準側導通端子及び前記線間スイッチング素子の導通制御端子に接続される第6スイッチング素子(P2, N2)とを備え、

前記第1スイッチング素子の導通制御端子は、前記線間スイッチング素子の導通制御端子に接続され、

前記第2及び第4スイッチング素子の導通制御端子は、前記第1スイッチング素子の非基準側導通端子に接続されると共に、抵抗素子(R0)を介して前記線間スイッチング素 50

子の非基準側導通端子に接続され、

前記第3スイッチング素子の導通制御端子は、前記第2スイッチング素子の非基準側導通端子に接続され、

前記第1フリップフロップがセットされると、前記第5スイッチング素子はオンして前記第6スイッチング素子はオフするように構成される請求項3から7の何れか一項に記載のリンクギング抑制回路。

【請求項9】

前記差動信号のレベルがローからハイから変化したことを検出すると、前記制御部による前記変化の検出を一定時間だけマスクする検出マスク部(5)を備える請求項1から3の何れか一項に記載のリンクギング抑制回路。

10

【請求項10】

前記差動信号のレベルがローからハイから変化したことを検出すると、前記制御部による前記変化の検出を一定時間だけマスクする検出マスク部(5)を備える請求項4から8の何れか一項に記載のリンクギング抑制回路。

【請求項11】

前記検出マスク部は、第1セット信号出力部が前記第1フリップフロップに出力するセット信号を遅延させる遅延回路を備える請求項10記載のリンクギング抑制回路。

【請求項12】

前記マスク時間の終了時点は、前記差動信号のレベルがハイからローに変化した時点から、信号データの1ビット長以上で、且つ2ビット長から前記一定時間を減じた時間未満に設定される請求項9から11の何れか一項に記載のリンクギング抑制回路。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、差動信号を伝送する伝送線路に接続されるリンクギング抑制回路に関する。

【背景技術】

【0002】

伝送線路を介してデジタル信号を伝送する場合、受信側においては、信号レベルが変化するタイミングで信号エネルギーの一部が反射することで、オーバーシュートやアンダーシュートのような波形の歪み、すなわちリンクギングが生じる問題がある。そして、従来、波形歪みを抑制する技術については様々な提案がされている。

30

【0003】

例えば特許文献1では、伝送路の信号がCAN通信におけるドミナントからレセシティブに変化した際に、伝送線路間に接続されているFETを一定時間固定的にオンすることでインピーダンスを整合させて、リンクギングを抑制する技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2017-63399号公報

【発明の概要】

【発明が解決しようとする課題】

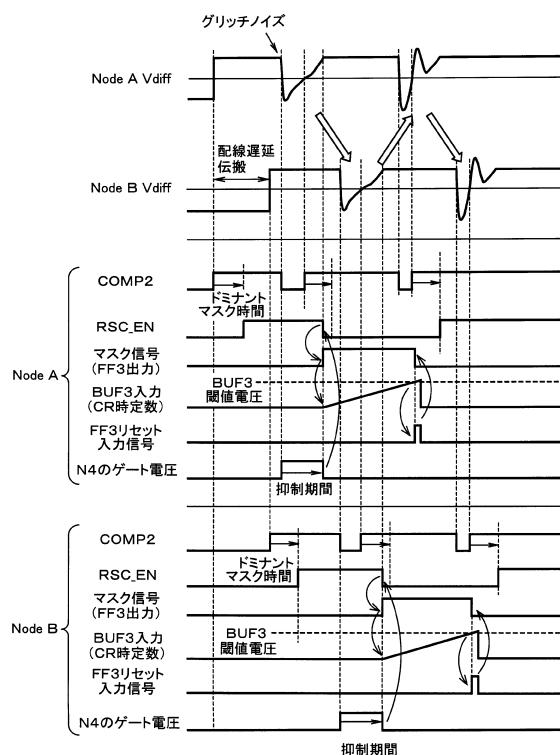

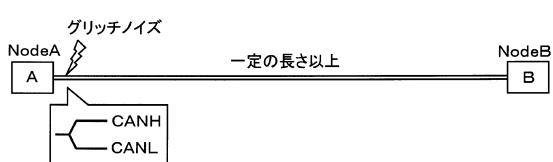

【0005】

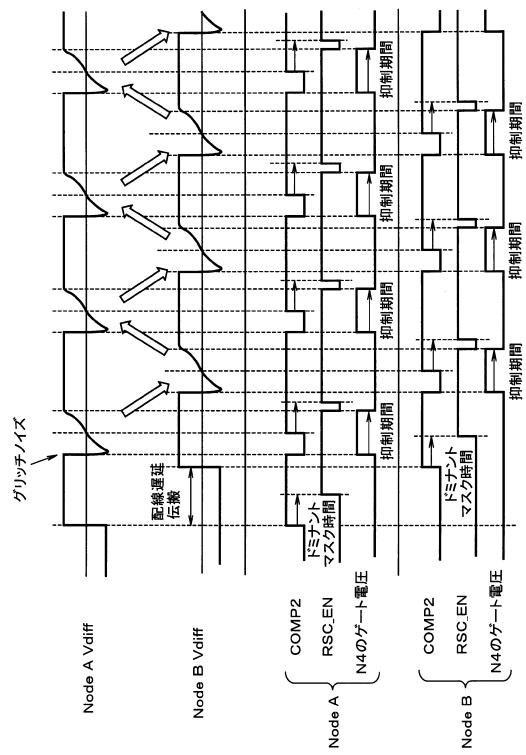

しかしながら、特許文献1の構成には、以下のような問題があることが分かった。特許文献1のリンクギング抑制回路を搭載した複数の通信ノードによりネットワークを構成する。この際に、図16に示すように通信線の長さが一定以上になっており、通信ノードAにおいて差動信号がドミナントを示している際にグリッジノイズが印加されて瞬間的にレセシティブに変化すると、当該通信ノードAにおいてリンクギング抑制動作が行われる。すると、その動作によって信号波形が歪むことになる。

【0006】

図17に示すように、その歪んだ波形の信号は、配線遅延分の遅れを以って他の通信ノ

40

50

ード B に到達するため、その通信ノード B においてもリンクギング抑制動作が行われる。その動作によって歪んだ波形の信号は、また元の通信ノード A に到達する。このように、通信ノード A, B 間で歪んだ波形の信号の伝送が繰り返されて波形の歪みが収束せず、通信エラーを発生させてしまう。

【0007】

本発明は上記事情に鑑みてなされたものであり、その目的は、グリッジノイズが印加された場合に発生する信号波形の歪みを、連鎖させることなく収束できるリンクギング抑制回路を提供することにある。

【課題を解決するための手段】

【0008】

請求項 1 記載のリンクギング抑制回路によれば、制御部は、差動信号のレベルがハイからローに変化したことを検出すると、線間スイッチング素子をオンさせてその状態を固定し、一定時間を計時した後に前記オン状態を解除する。連続起動防止部は、制御部が線間スイッチング素子をオンさせた時点から一定のマスク時間を設定し、マスク時間内は制御部が差動信号のレベルがハイからローに変化したことを検出しないようにマスクする。

【0009】

このように構成すれば、差動信号のレベルがハイを示している状態で瞬間的にローレベルに変化するようなグリッジノイズが印加されても、制御部はその変化を検出しない。したがって従来技術とは異なり、複数の通信ノード間でリンクギング抑制動作が交互に行われ、信号波形の歪が連続的に発生することを防止できる。

【0010】

請求項 2 記載のリンクギング抑制回路によれば、マスク時間の終了時点を、差動信号のレベルがハイからローに変化した時点から、信号データの 1 ビット長以上で且つ 2 ビット長未満に設定する。このように構成すれば、差動信号のレベルがハイからローに変化してリンクギング抑制動作を行った後、差動信号のレベルがローを示している期間にノイズが重畠された際に、誤動作が発生することを確実に防止できる。

【図面の簡単な説明】

【0011】

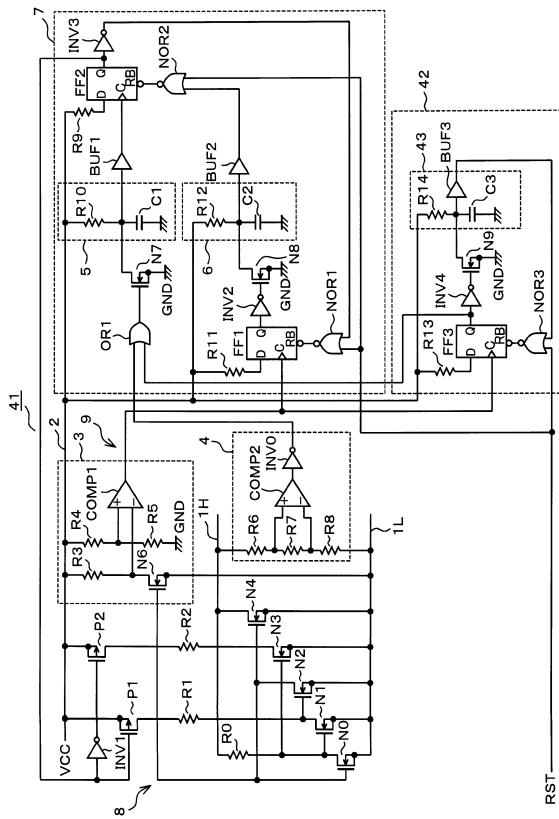

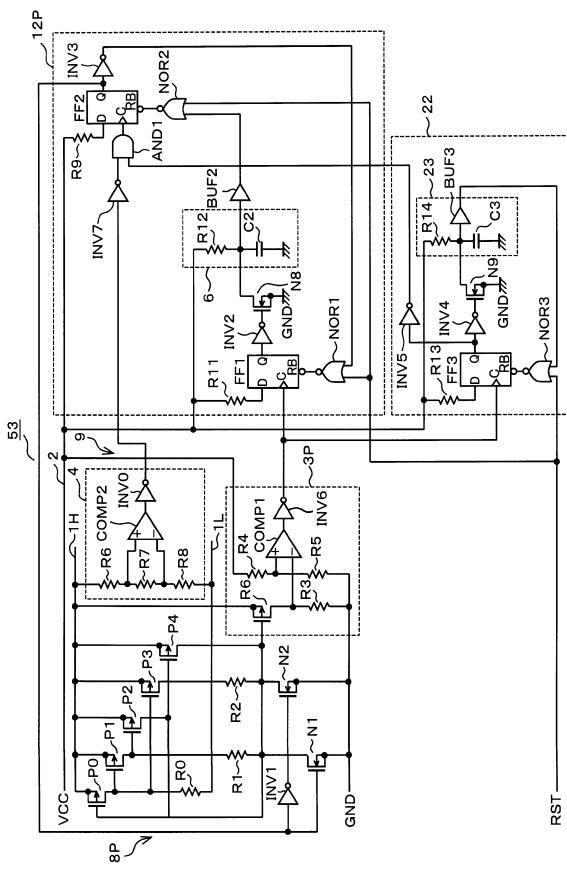

【図 1】第 1 実施形態であり、リンクギング抑制回路の構成を示す図

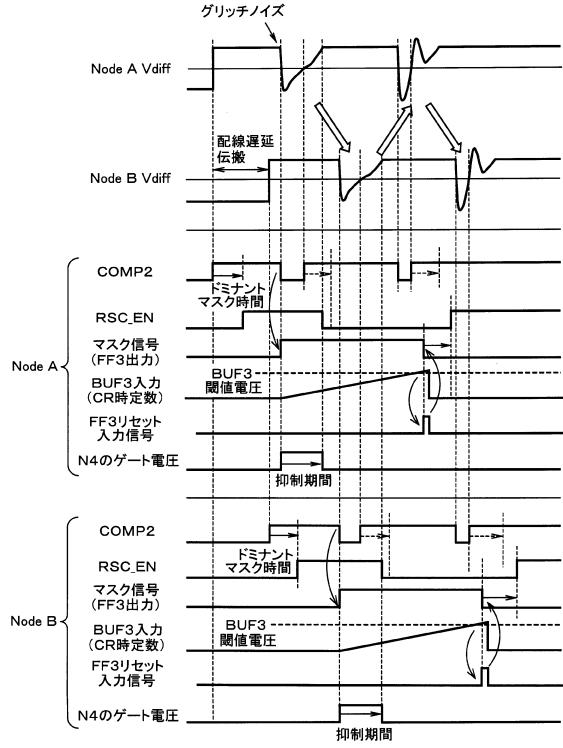

【図 2】動作タイミングチャート

30

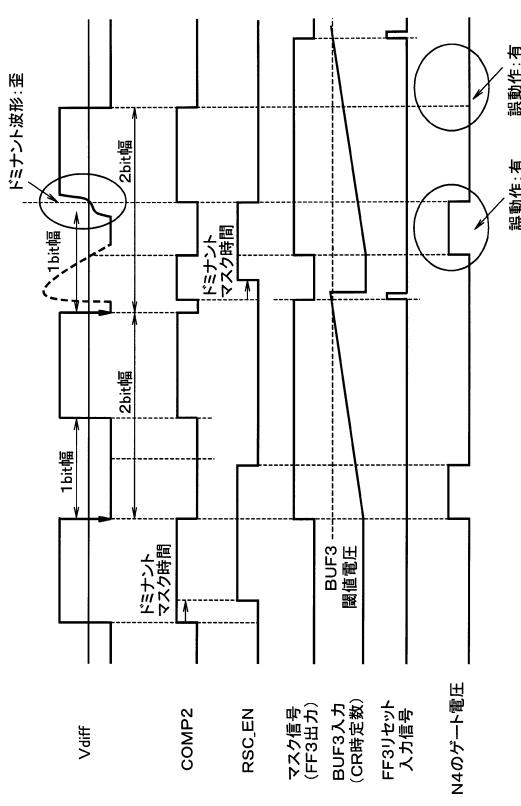

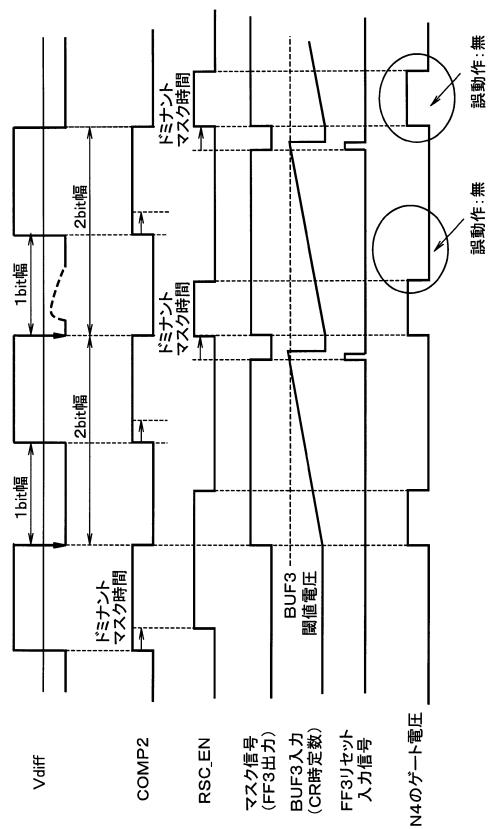

【図 3】マスク時間の終了時点を説明するタイミングチャート（その 1）

【図 4】マスク時間の終了時点を説明するタイミングチャート（その 2）

【図 5】マスク時間の終了時点を説明するタイミングチャート（その 3）

【図 6】マスク時間の終了時点を説明するタイミングチャート（その 4）

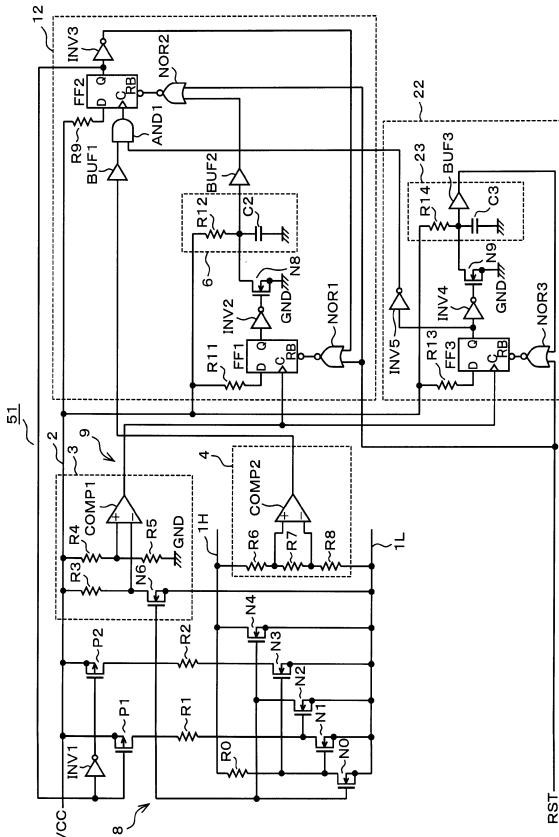

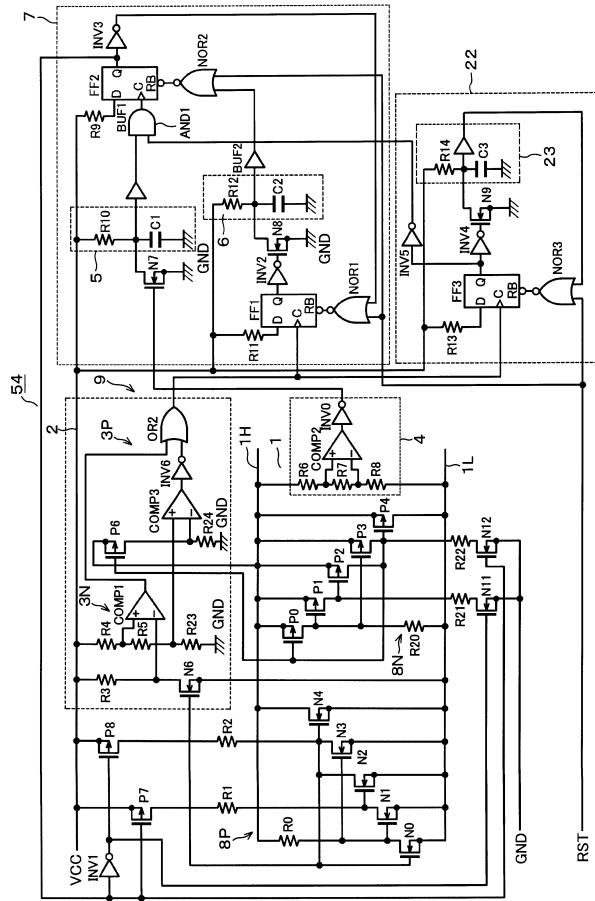

【図 7】第 2 実施形態であり、リンクギング抑制回路の構成を示す図

【図 8】動作タイミングチャート

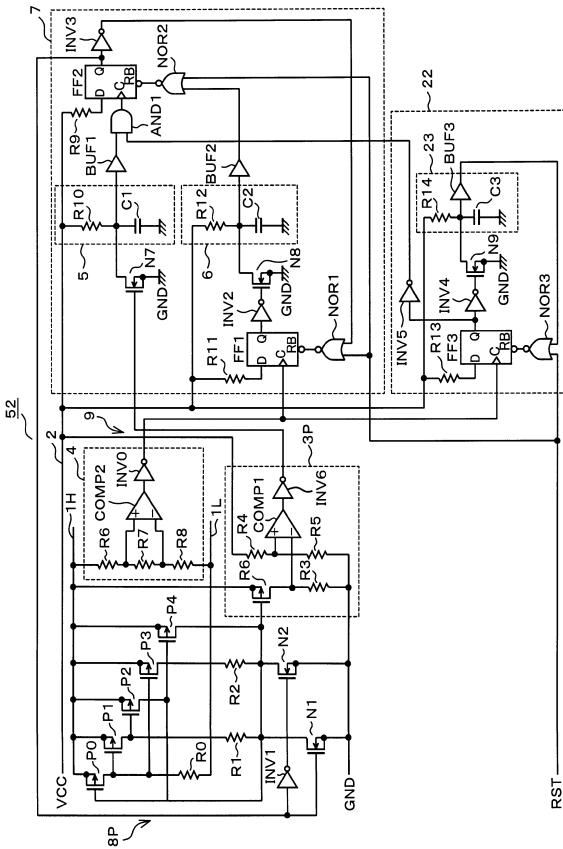

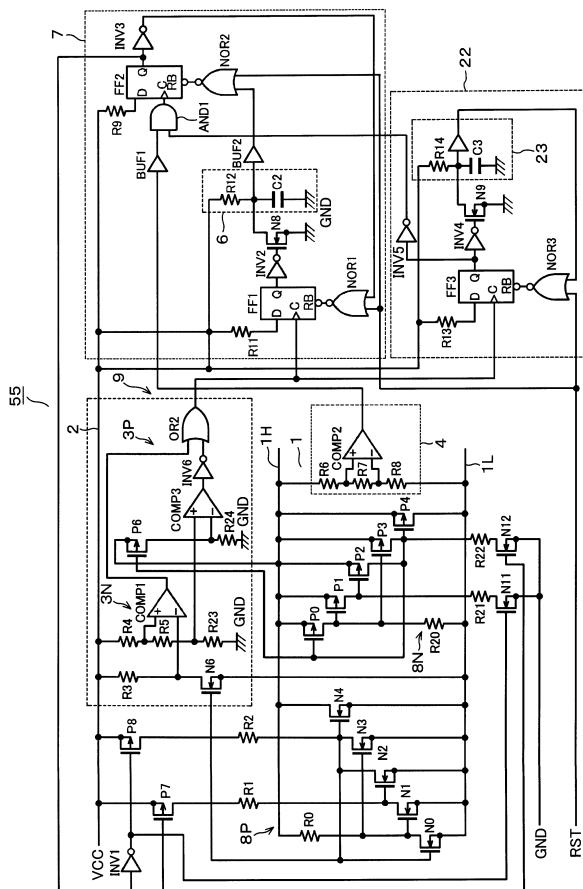

【図 9】第 3 実施形態であり、リンクギング抑制回路の構成を示す図

【図 10】動作タイミングチャート

【図 11】第 4 実施形態であり、リンクギング抑制回路の構成を示す図

【図 12】第 5 実施形態であり、リンクギング抑制回路の構成を示す図

40

【図 13】第 6 実施形態であり、リンクギング抑制回路の構成を示す図

【図 14】第 7 実施形態であり、リンクギング抑制回路の構成を示す図

【図 15】第 8 実施形態であり、リンクギング抑制回路の構成を示す図

【図 16】従来技術を説明する 2 つの通信ノードの接続状態を示す図

【図 17】動作タイミングチャート

【発明を実施するための形態】

【0012】

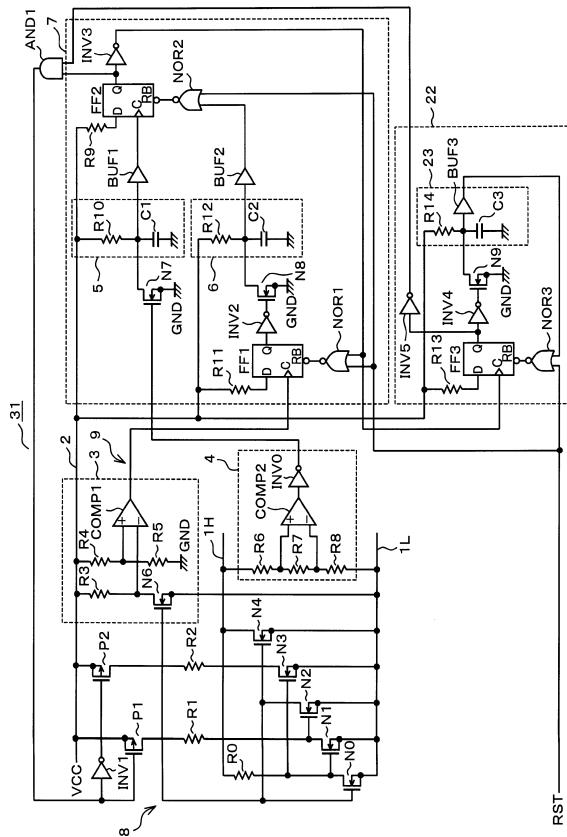

（第 1 実施形態）

本発明は、特許文献 1 に開示されている発明を基本構成として改良を加えたものであるから、以下特許文献 1 に準拠して説明する。図 1 に示すリンクギング抑制回路 21 は、特許

50

文献 1 の第 1 実施形態である図 1 に示すリングング抑制回路 1 0 に、連続起動防止回路 2 2 を追加したものである。リングング抑制回路 1 0 相当部分によるリングング抑制動作自体は、特許文献 1 と同様である。

【 0 0 1 3 】

連続起動防止回路 2 2 は、ON 状態保持回路 7 における D フリップフロップ FF 1 を中心とする構成と同様の構成であり、D フリップフロップ FF 3, インバータゲート INV 4, N チャネル MOSFET\_N 9, バッファ BUF 3, NOR ゲート NOR 3, 抵抗素子 R 1 4 及びコンデンサ C 3 の直列回路を備えている。前記直列回路は、遅延回路 2 3 を構成している。但し、バッファ BUF 3 の出力端子は、NOR ゲート NOR 3 の入力端子の一方に接続されている。D フリップフロップ FF 3 のクロック端子 C は、コンパレータ COMP 1 の出力端子に接続されている。 10

【 0 0 1 4 】

また、バッファ BUF 1 の出力端子と D フリップフロップ FF 2 のクロック端子 C との間には、NOT ゲート INV 5 及び AND ゲート AND 1 が挿入されている。D フリップフロップ FF 3 の出力端子 Q は、AND ゲート AND 1 の入力端子の一方に接続されており、ハイアクティブのマスク信号を出力する。尚、連続起動防止部に相当する連続起動防止回路 2 2 は、AND ゲート AND 1 も含む構成である。遅延回路 2 3 はリセット信号生成部に相当し、AND ゲート AND 1 は論理ゲートに相当する。

【 0 0 1 5 】

次に、本実施形態の作用について説明する。図 2 に示すように、通信ノード A では、差動信号の立上りエッジのタイミングで比較回路 4 のコンパレータ COMP 2 の出力信号がハイレベルになる。その時点から、遅延回路 5 の作用により「ドミナントマスク時間」が経過した後に、D フリップフロップ FF 2 が output する信号 RSC\_EN がハイレベルになる。 20

【 0 0 1 6 】

ここで、図 1 に示したケースと同様に、通信ノード A において差動信号がドミナントを示している際に、グリッジノイズが印加されたとする。すると、FET\_N 1 及び N 3 のゲートがローレベルになり、これらがターン OFF する。この時、FET\_P 2 が ON しているので FET\_N 1, N 4 及び N 6 のゲートが抵抗素子 R 2 を介してハイレベルになり、これらがターン ON する。尚、ゲートは導通制御端子に相当する。また、電位基準側導通端子は FET のソースに相当し、非基準側導通端子はドレインに相当する。 30

【 0 0 1 7 】

これに伴い、ON 確認回路 3 のコンパレータ COMP 1 の出力端子 Q がハイレベルになり、D フリップフロップ FF 1 及び FF 3 がトリガされる。これにより、D フリップフロップ FF 3 がマスク信号を出力する。マスク信号がハイレベルを示すことで、FET\_N 9 がターン OFF してコンデンサ C 3 の充電が開始され、バッファ BUF 3 の入力端子のレベルが上昇する。

【 0 0 1 8 】

バッファ BUF 3 の出力端子がハイレベルになると、NOR ゲート NOR 3 を介して D フリップフロップ FF 3 がリセットされ、マスク信号がローレベルになる。マスク信号がハイレベルを示している間は、差動信号がドミナントを示している際にレセシシブルレベルに変化しても、AND ゲート AND 1 を介して D フリップフロップ FF 2 がトリガされなくなる。したがって、リングング抑制動作が再起動されることはない。 40

【 0 0 1 9 】

そして、上記の通信ノード A におけるリングング抑制回路 2 1 の動作は、配線長に伴う伝搬遅時間を経過した後、通信ノード B においても同様に行われる。その結果、通信ノード A 側におけるグリッジノイズの印加により、リングング抑制動作が通信ノード A, B のそれぞれにおいて 1 回だけ行われる。それに伴う信号波形の歪は生じるが、従来のように歪んだ波形の信号の伝送が繰り返されることはない。

【 0 0 2 0 】

尚、遅延回路 2 3において遅延時間を設定することで決定されるマスク時間の終了時点は、差動信号がドミナントからレセシシブに変化した基準時点から、信号データの 1 ビット長以上で、且つ 2 ビット長から「ドミナントマスク時間」を減じた時間未満に設定する。これにより、差動信号がレセシシブを示している期間にノイズが重畠された際に、リングング抑制動作が行われることを防止できる。

【 0 0 2 1 】

図 3 及び図 4 に示すように、マスク時間の終了時点を基準時点から 1 ビット長以上とすることで、基準時点直後のレセシシブ期間における誤動作が防止される。また、図 5 及び図 6 に示すように、終了時点を基準時点から { ( 2 ビット長 ) - ( ドミナントマスク時間 ) } 未満にすることで、基準時点の 2 ビット後に到来したレセシシブ期間における誤動作が防止される。尚、ドミナントマスク時間を設定しない場合には、マスク時間の終了時点の最大を 2 ビット長未満にすれば良い。

10

【 0 0 2 2 】

以上のように本実施形態によれば、制御部 9 は、伝送線路 1 において伝送される差動信号がドミナントからレセシシブに変化したことを検出すると、F E T \_ N 4 をオンさせてその状態を固定し、遅延回路 6 により一定時間を計時した後にそのオン状態を解除する。そして、連続起動防止回路 2 2 は、制御部 9 が F E T \_ N 4 をオンさせた時点から一定のマスク時間を設定し、マスク時間内は制御部が差動信号のレベルがハイからローに変化したことを検出しないようにマスクする。

【 0 0 2 3 】

20

具体的には、連続起動防止部 2 2 を、初期状態でリセットされており、D フリップフロップ F F 1 がセットされることに伴いセット状態になると、マスク時間を設定するマスク信号を出力する D フリップフロップ F F 3 と、D フリップフロップ F F 3 がセットされた時点から、マスク時間に相当する時間が経過した時点で当該フリップフロップ F F 3 をリセットする遅延回路 2 3 と、D フリップフロップ F F 2 をセットする信号を、マスク信号により無効化するための A N D ゲート A N D 1 とで構成した。

【 0 0 2 4 】

このように構成すれば、差動信号がドミナントを示している状態で、瞬間的にレセシシブに変化するようなグリッジノイズが印加されても制御部 9 はその変化を検出しない。したがって従来技術とは異なり、通信ノード A , B 間でリングング抑制動作が交互に行われ、信号波形の歪が連続的に発生することを防止できる。

30

【 0 0 2 5 】

また、マスク時間の終了時点を、差動信号のレベルがドミナントからレセシシブに変化した基準時点から、信号データの 1 ビット長以上で且つ { ( 2 ビット長 ) - ( ドミナントマスク時間 ) } 未満に設定する。これにより、基準時点直後、及び基準時点の 2 ビット後に到来するレセシシブ期間における誤動作を確実に防止できる。

【 0 0 2 6 】

そして、特許文献 1 と同様に、制御部 9 を、D フリップフロップ F F 2 と、セット状態になると D フリップフロップ F F 2 をリセットするための信号を出力する D フリップフロップ F F 1 と、D フリップフロップ F F 1 の出力端子 Q と D フリップフロップ F F 2 のリセット端子 R B との間に配置される遅延回路 6 と、差動信号がレセシシブからドミナントから変化したことを検出すると D フリップフロップ F F 2 をセットする信号を出力する比較回路 4 及び F E T \_ N 7 と、F E T \_ N 4 がターン ON したことを検出すると D フリップフロップ F F 1 をセットする信号を出力する ON 確認回路 3 と、D フリップフロップ F F 2 がセットされると F E T \_ N 4 のゲートを ON レベルにすることを可能にするオン設定部 8 とで構成した。

40

【 0 0 2 7 】

また、ON 確認回路 3 は、ドレインが抵抗素子 R 3 を介して電源線 2 に接続され、ソース及びゲートがそれぞれ F E T \_ N 4 のソース及びゲートに接続される F E T \_ N 6 を備える。オン設定部 8 は、ソースが低電位側信号線 1 L に接続される F E T \_ N 0 ~ N 3 と

50

、ソースが電源線 2 に接続され、ドレインが抵抗素子 R 1 を介して F E T \_ N 1 のドレイン及び F E T \_ N 2 のゲートに接続される F E T \_ P 1 と、ソースが電源線 2 に接続され、ドレインが抵抗素子 R 2 を介して F E T \_ N 3 のドレイン及び F E T \_ N 1 のゲートに接続される F E T \_ P 2 とを備える。

【 0 0 2 8 】

そして、F E T \_ N 0 のゲートを F E T \_ N 4 のゲートに接続し、F E T \_ N 1 及び N 3 のゲートを、F E T \_ N 0 のドレインに接続すると共に抵抗素子 R 0 を介して高電位側信号線 1 H に接続し、F E T \_ N 2 のゲートを F E T \_ N 1 のドレインに接続し、D フリップフロップ F F 2 がセットされると、F E T \_ P 1 は ON して F E T \_ P 2 は OFF するように構成した。

10

【 0 0 2 9 】

また、遅延回路 5 は、差動信号のレベルがレセシシブからドミナントに変化したことを検出すると、比較回路 4 が F E T \_ N 7 を介して出力する D フリップフロップ F F 2 のセット信号を遅延させることで、制御部 8 による前記変化の検出を一定時間だけマスクする。これらの構成により、基本的なリングング抑制動作については、特許文献 1 と同様に実行される。

【 0 0 3 0 】

( 第 2 実施形態 )

以下、第 1 実施形態と同一部分には同一符号を付して説明を省略し、異なる部分について説明する。図 7 に示すように、第 2 実施形態のリングング抑制回路 3 1 は、連続起動防止回路 2 2 を構成する AND ゲート A N D 1 の入力端子の一方が、D フリップフロップ F F 2 の出力端子 Q に接続されている点が相違している。D フリップフロップ F F 3 のクロック端子 C は、NOT ゲート I N V 3 の出力端子に接続されている。そして、信号 R S C \_ E N は、AND ゲート A N D 1 を介して出力される。

20

【 0 0 3 1 】

次に、第 2 実施形態の作用について説明する。初期状態で、D フリップフロップ F F 3 の出力端子 Q はローレベルである。よって図 8 に示すように、差動信号がドミナントからレセシシブに変化すると、信号 R S C \_ E N は第 1 実施形態と同じタイミングで立上る。D フリップフロップ F F 2 がリセットされて信号 R S C \_ E N が立ち下がると、D フリップフロップ F F 3 がトリガされ、マスク信号が立ち上がる。したがって、その立上りのタイミングは、第 1 実施形態よりも遅くなる。

30

【 0 0 3 2 】

以上のように第 2 実施形態によれば、連続起動防止回路 3 2 を、D フリップフロップ F F 3 と、遅延回路 2 3 と、D フリップフロップ F F 2 がセットされた信号を、マスク信号により無効化するための AND ゲート A N D 1 とで構成した。これにより、第 1 実施形態と同様の効果が得られる。

【 0 0 3 3 】

( 第 3 実施形態 )

図 9 に示すように、第 3 実施形態のリングング抑制回路 4 1 は、連続起動防止回路 4 2 を備えている。連続起動防止回路 4 2 は、第 1 実施形態の連続起動防止回路 2 2 より NOT ゲート I N V 5 を削除し、AND ゲート 1 に替えて OR ゲート O R 1 を用いている。O R ゲート O R 1 は、比較回路 4 の NOT ゲート I N V 0 の出力端子と、F E T \_ N 7 のゲートとの間に配置されている。

40

【 0 0 3 4 】

次に、第 3 実施形態の作用について説明する。図 10 に示すように、マスク信号は第 1 実施形態と同じタイミングで立上る。そして、コンパレータ C O M P 2 の出力信号が次にローレベルに変化した際に、マスク信号がハイレベルになることで O R ゲート O R 1 の出力信号はハイレベルを維持する。これにより、D フリップフロップ F F 2 がトリガされることをマスクする。そのため、遅延回路 4 3 について設定される遅延時間は、第 1 実施形態よりも長めに設定されている。

50

## 【0035】

以上のように第3実施形態によれば、連続起動防止回路42のORゲートOR1を、DフリップフロップFF2の前段となるNOTゲートINV0とFET\_N7との間に配置した。これにより、第1実施形態と同様の効果が得られる。

## 【0036】

## (第4～第8実施形態)

図11から図15は第4～第8実施形態を示す。これらのリングング抑制回路51～55は、特許文献1の第2～第6実施形態であるリングング抑制回路11, 13～16に、第1実施形態の連続起動防止回路22を加えたものである。尚、符号の都合上、特許文献1の各実施形態で示していた符号を、以下のように変更している。

10

- ・第3～第6実施形態 NOTゲートINV4, INV5 INV6

- ・第4実施形態 NOTゲートINV4 INV7

- ・第5, 第6実施形態 ORゲートOR1 OR1

## 【0037】

## (その他の実施形態)

マスク時間の終了時点の最大値は、必ずしも基準時点から1ビット長以上で且つ{(2ビット長)-(ドミナントマスク時間)}未満に設定する必要は無い。

第4～第8実施形態に、第1実施形態の連続起動防止回路22に換えて、第2又は第3実施形態の連続起動防止回路32又は42を適用しても良い。

遅延回路5及び6, 23, 43は、抵抗素子及びコンデンサで構成するものに限らず、例えば定電流源との組み合わせで構成しても良い。

20

抵抗素子R1, R2, R21, R22を、定電流源に置き換えても良い。

本開示は、実施例に準拠して記述されたが、本開示は当該実施例や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

## 【符号の説明】

## 【0038】

図面中、1は通信バス、1Hは高電位側信号線、1Lは低電位側信号線、2は電源線、3はON確認回路、4は比較回路、5, 6は遅延回路、7はON状態保持回路、8はオン設定部、9は制御部、21, 31, 41, 51～55はリングング抑制回路、FF1, FF2, FF3はDフリップフロップ、N0～N9はNチャネルMOSFETを示す。

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 义 9 】

【図10】

【 図 1 1 】

【 図 1 2 】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(56)参考文献 特開2017-063399(JP, A)

特開2002-330182(JP, A)

特開平01-296838(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 25/02

H03K 17/16

H03K 17/687