(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-210773

(P2011-210773A)

(43) 公開日 平成23年10月20日(2011.10.20)

(51) Int.Cl.

H01L 21/60 (2006.01)

F 1

H01L 21/60 311Q

H01L 21/92 602G

H01L 21/92 602R

テーマコード(参考)

5 F O 4 4

審査請求 未請求 請求項の数 9 O L (全 13 頁)

(21) 出願番号

特願2010-74492(P2010-74492)

(22) 出願日

平成22年3月29日(2010.3.29)

(71) 出願人 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100109667

弁理士 内藤 浩樹

(74) 代理人 100109151

弁理士 永野 大介

(74) 代理人 100120156

弁理士 藤井 兼太郎

(72) 発明者 櫻井 大輔

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

F ターム(参考) 5F044 KK01 KK17 LL01 QQ02

(54) 【発明の名称】半導体装置の構造および製造方法

## (57) 【要約】

【課題】挿ピッチかつ高い接続信頼性を確保した簡単な構造の半導体装置、および製造方法を提供する。

【解決手段】半導体素子1の電極端子1b上に突起状電極1aを形成する。突起状電極1aよりも大きくなり、位置を合わせた転写用の金型4に、粘着層5を供給し半田粒子3を付与する。金型4と半導体素子1の対向する位置を合わせ、加熱・加圧して半田粒子3を突起状電極1a上に付与、金型4を引き剥がして半導体素子1を個片化する。半導体素子1の突起状電極1aに対向して回路基板2の電極端子2aの位置を合わせて、加熱、荷重し半導体素子1を回路基板2上へ搭載する。半導体素子1の端部の回路基板2との距離が最も大きな電極同士でも、微細半田が鼓状に伸びて接合し平行度の悪化を吸収する。端部電極の熱応力集中を微小半田接合部(半田接合部3c)が受けて、電極直下の脆弱な絶縁膜の熱応力を低減して剥離や亀裂を防ぎ、高い接続信頼性を確保する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

電子部品の複数の電極の少なくとも 1 つの電極に対して 2 個以上の半田粒子を付与する工程と、前記電子部品の電極と回路基板の電極とを対向して配置する工程と、前記電子部品の電極表面に付与した半田粒子と前記回路基板の電極とを当接させる工程と、前記半田粒子を加熱する工程と、からなり。

前記半田粒子が溶融した 2 個以上の微小半田接合体を介して前記電子部品の電極と前記回路基板の電極とを電気的に接続することを特徴とする半導体装置の製造方法。

**【請求項 2】**

回路基板の複数の電極の少なくとも 1 つの電極に対して 2 個以上の半田粒子を付与する工程と、前記回路基板の電極と電子部品の電極とを対向して配置する工程と、前記回路基板の電極表面に付与した半田粒子と前記電子部品の電極とを当接させる工程と、前記半田粒子を加熱する工程と、からなり。

前記半田粒子が溶融した 2 個以上の微小半田接合体を介して前記回路基板の電極と前記電子部品の電極とを電気的に接続することを特徴とする半導体装置の製造方法。

**【請求項 3】**

電子部品の複数の電極の少なくとも 1 つの電極に対して 2 個以上の第 1 半田粒子を付与する工程と、回路基板の複数の電極の少なくとも 1 つの電極に対して 2 個以上の第 2 半田粒子を付与する工程と、前記電子部品の電極と前記回路基板の電極とを対向して配置する工程と、前記電子部品の電極表面に付与した第 1 半田粒子と前記回路基板の電極、または前記回路基板の電極表面に付与した第 2 半田粒子と前記電子部品の電極、または前記第 1 半田粒子と前記第 2 半田粒子を当接させる工程と、前記第 1 半田粒子および前記第 2 半田粒子を加熱する工程と、からなり。

前記第 1 半田粒子および / または前記第 2 半田粒子が溶融した 2 個以上の微小半田接合体を介して前記回路基板の電極と前記電子部品の電極とを電気的に接続することを特徴とする半導体装置の製造方法。

**【請求項 4】**

前記電子部品の電極表面に付与した第 1 半田粒子と、前記回路基板の電極表面に付与した第 2 半田粒子とは粒子間隔が異なることを特徴とする請求項 3 記載の半導体装置の製造方法。

**【請求項 5】**

前記電子部品の電極表面に付与した第 1 半田粒子と、前記回路基板の電極表面に付与した第 2 半田粒子とは粒子径が異なることを特徴とする請求項 3 または 4 記載の半導体装置の製造方法。

**【請求項 6】**

前記電子部品の電極表面に形成した第 1 半田粒子の粒子間隔が、前記回路基板の電極表面に形成した第 2 半田粒子の粒子径より大きいことを特徴とする請求項 3 ~ 5 のいずれか 1 項に記載の半導体装置の製造方法。

**【請求項 7】**

前記回路基板の電極表面に形成した第 2 半田粒子の粒子間隔が、前記電子部品の電極表面に形成した第 1 半田粒子の粒子径より大きいことを特徴とする請求項 3 ~ 5 のいずれか 1 項に記載の半導体装置の製造方法。

**【請求項 8】**

電子部品の電極と、該電極に対向して配置された回路基板の電極が、半田を介して接合される半導体装置において、

前記電子部品の電極と前記回路基板の電極とが対向して配置された少なくとも 1 つの電極組は、前記半田を溶融した 2 個以上の微小半田接合体を介して接合されたことを特徴とする半導体装置。

**【請求項 9】**

前記電子部品の電極と前記回路基板の電極とが対向して配置された電極組は、前記電極

10

20

30

40

50

組の複数の中で間隔の最も大きい電極同士は2個以上の微小半田接合体を介して接合されたことを特徴とする請求項8記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の構造および製造方法に関するものである。

【背景技術】

【0002】

近年、半導体素子の高密度化と電極端子の多ピン化の両立を進めるべく、半導体素子の電極端子の狭ピッチ化、面積縮小化が図られている。

10

【0003】

通常、フリップチップ実装においては、LSIなどの半導体素子の電極端子上に半田バンプなどの突起電極を形成し、その半導体素子をフェイスダウンにより実装基板の接続端子に対して圧接・加熱してバンプ接続させることで実装している。

【0004】

しかし、狭ピッチ化の進展は著しいため、従来のように電極端子をペリフェラルに配置する手段では、電極端子間で短絡が発生したり、半導体素子と実装基板との熱膨張係数の差により接続不良などが発生することがある。そこで、電極端子をエリア状に配置することで、電極端子間ピッチを広げる方法がとられてきたが、近年ではエリア配置でも狭ピッチ化の進展が著しい。

20

【0005】

半田バンプを形成する方法として、半田をスクリーン印刷やディスペンサーで電解メッキで電極上に形成した後、リフロー炉で半田融点以上に加熱することによって突起状の半田バンプを形成する工法がとられてきた。

【0006】

しかし、近年さらに半田接合部のピッチが狭く、半導体素子・基板電極間の隙間も小さくなってきたため、フリップチップ実装時の加熱工程において溶融した半田が変形し、半田の表面張力により半田バンプ同士がつながる半田ブリッジ不良が発生するといった問題が起きるようになってきた。

【0007】

このような要求に対応するものとして、バンプを2層構成にする方法が提案されている。

30

【0008】

例えば、金や銅からなる突起電極表面を覆うように、金属粒子を含有した絶縁性皮膜を形成する方法がある（例えば、特許文献1参照）。この方法によれば、絶縁性皮膜や突起電極がフリップチップ時に溶融せずに、半導体素子と基板間に注入する封止樹脂の硬化収縮による圧縮方向の力によって電気的に導通をとることができ、ブリッジ発生を防ぐことができ、狭ピッチ化に対応できる。

【0009】

しかしながら、近年要求される電極間ピッチの狭ピッチ化の要求は非常に厳しいため、特許文献1のように、金属粒子と金属電極が拡散接合せずに接触のみで導通を確保する接続形態であれば、電極面積が小さくなると当然電極間に介在する導電粒子の数が少くなり、接続抵抗が高く、信号の伝送損失が増大するという問題がある。

40

【0010】

そこで、バンプを下層金属と上層金属とからなる2層構成にし、高融点金属からなる下層金属上に半田からなる上層金属を形成する方法が採用されるようになってきた。この方法によれば、半田一層からなるバンプよりも半田量を減らすことができ、フリップチップ実装時の平面方向への半田つぶれ量が減り、半田ブリッジ発生を防ぐことができるだけでなく、半田と基板電極とが拡散接合するので、接続抵抗は低く、信号の伝送損失を損なうこともない（例えば、特許文献2参照）。

50

**【先行技術文献】****【特許文献】****【0011】**

【特許文献1】特開2003-282617号公報

【特許文献2】特開平9-97791号公報

**【発明の概要】****【発明が解決しようとする課題】****【0012】**

しかしながら、近年要求される配線ルールの微細化や高速信号処理に対応する目的で半導体素子の層間絶縁膜に低誘電率膜（いわゆるLow-k膜やULK（Ultra Low-k）膜など）が用いられるようになってきた。低誘電率膜自体は、誘電率を下げるために多数の数nmの空孔を有するポーラス状（多孔質）とされている。

10

**【0013】**

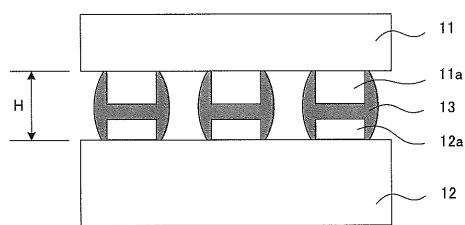

図7は特許文献2に記載の実施例の半導体装置を概念的に示す断面図である。特許文献2の図7に示すように、半導体素子11の電極11aと回路基板12の電極12a同士が半田13で拡散接合される。このような構成をとれば、フリップチップ工程における半田溶融後の冷却過程において、半導体素子11と回路基板12の弾性率および線膨張係数の差に起因する熱応力が、半導体素子のコーナー部分の半田13の接合部に集中することになる。このため、その熱応力が半導体素子11の電極11a直下に直接伝わり、電極11a直下にある脆弱な低誘電率膜の剥離や亀裂を発生させるといった問題がある。

20

**【0014】**

また、急激な温度差が発生するような使用環境下においても、同様な熱応力集中が発生して、電極直下にある脆弱な低誘電率絶縁膜の剥離や亀裂が発生するといった問題がある。

**【0015】**

本発明は、前記問題に鑑み、脆弱膜を有する半導体素子において、高い接続信頼性を確保できる簡易な構造の半導体装置、および半導体装置を形成する製造方法を提供することを目的とする。

**【課題を解決するための手段】****【0016】**

30

前記の目的を達成するために、本発明の請求項1に係る半導体装置の製造方法は、電子部品の複数の電極の少なくとも1つの電極に対して2個以上の半田粒子を付与する工程と、前記電子部品の電極と回路基板の電極とを対向して配置する工程と、前記電子部品の電極表面に付与した半田粒子と前記回路基板の電極とを当接させる工程と、前記半田粒子を加熱する工程と、からなり、前記半田粒子が溶融した2個以上の微小半田接合体を介して前記電子部品の電極と前記回路基板の電極とを電気的に接続することを特徴とする。

**【0017】**

また、請求項2に記載した半導体装置の製造方法は、回路基板の複数の電極の少なくとも1つの電極に対して2個以上の半田粒子を付与する工程と、前記回路基板の電極と電子部品の電極とを対向して配置する工程と、前記回路基板の電極表面に付与した半田粒子と前記電子部品の電極とを当接させる工程と、前記半田粒子を加熱する工程と、からなり、前記半田粒子が溶融した2個以上の微小半田接合体を介して前記回路基板の電極と前記電子部品の電極とを電気的に接続することを特徴とする。

40

**【0018】**

また、請求項3に記載した半導体装置の製造方法は、電子部品の複数の電極の少なくとも1つの電極に対して2個以上の第1半田粒子を付与する工程と、回路基板の複数の電極の少なくとも1つの電極に対して2個以上の第2半田粒子を付与する工程と、前記電子部品の電極と前記回路基板の電極とを対向して配置する工程と、前記電子部品の電極表面に付与した第1半田粒子と前記回路基板の電極、または前記回路基板の電極表面に付与した第2半田粒子と前記電子部品の電極、または前記第1半田粒子と前記第2半田粒子を当接

50

させる工程と、前記第1半田粒子および前記第2半田粒子を加熱する工程と、からなり、前記第1半田粒子および／または前記第2半田粒子が溶融した2個以上の微小半田接合体を介して前記回路基板の電極と前記電子部品の電極とを電気的に接続することを特徴とする。

**【0019】**

また、請求項4に記載した発明は、請求項3の半導体装置の製造方法であって、前記電子部品の電極表面に付与した第1半田粒子と、前記回路基板の電極表面に付与した第2半田粒子とは粒子間隔が異なることを特徴とする。

**【0020】**

また、請求項5に記載した発明は、請求項3，4の半導体装置の製造方法であって、前記電子部品の電極表面に付与した第1半田粒子と、前記回路基板の電極表面に付与した第2半田粒子とは粒子径が異なることを特徴とする。 10

**【0021】**

また、請求項6に記載した発明は、請求項3～5の半導体装置の製造方法であって、前記電子部品の電極表面に形成した第1半田粒子の粒子間隔が、前記回路基板の電極表面に形成した第2半田粒子の粒子径より大きいことを特徴とする。

**【0022】**

また、請求項7に記載した発明は、請求項3～5の半導体装置の製造方法であって、前記回路基板の電極表面に形成した第2半田粒子の粒子間隔が、前記電子部品の電極表面に形成した第1半田粒子の粒子径より大きいことを特徴とする。 20

**【0023】**

また、請求項8に記載した半導体装置は、電子部品の電極と、該電極に対向して配置された回路基板の電極が、半田を介して接合される半導体装置において、前記電子部品の電極と前記回路基板の電極とが対向して配置された少なくとも1つの電極組は、前記半田を溶融した2個以上の微小半田接合体を介して接合されたことを特徴とする。

**【0024】**

また、請求項9に記載した発明は、請求項8の半導体装置において、前記電子部品の電極と前記回路基板の電極とが対向して配置された電極組は、前記電極組の複数の中で間隔の最も大きい電極同士は2個以上の微小半田接合体を介して接合されたことを特徴とする。 30

**【0025】**

前記製造方法、装置構成によれば、半導体装置における脆弱な半導体素子のフリップチップ実装において、優れた接続信頼性が確保できる。

**【発明の効果】**

**【0026】**

本発明によれば、半導体装置のコーナー電極における熱応力集中を軟らかく延びやすい微小半田接合体が受けるため、電極直下にある脆弱な低誘電率絶縁膜が受ける熱応力が低減され、脆弱な低誘電率絶縁膜の剥離や亀裂を防ぐことができ、高い接続信頼性が確保できるという効果を奏する。

**【図面の簡単な説明】**

**【0027】**

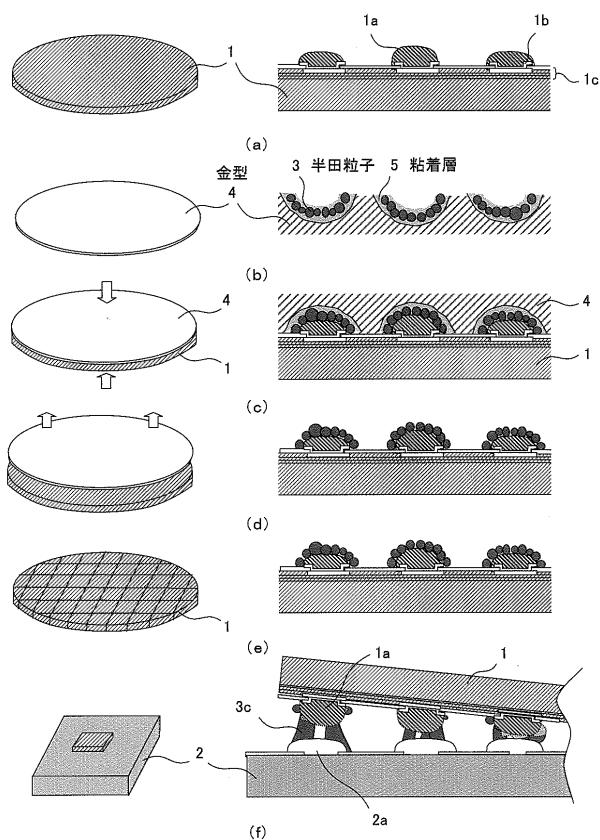

**【図1】**本発明の実施形態1における半導体装置を概念的に示す断面図

**【図2】**本実施形態1における半導体装置の製造方法(a)～(f)を概念的に示す断面図

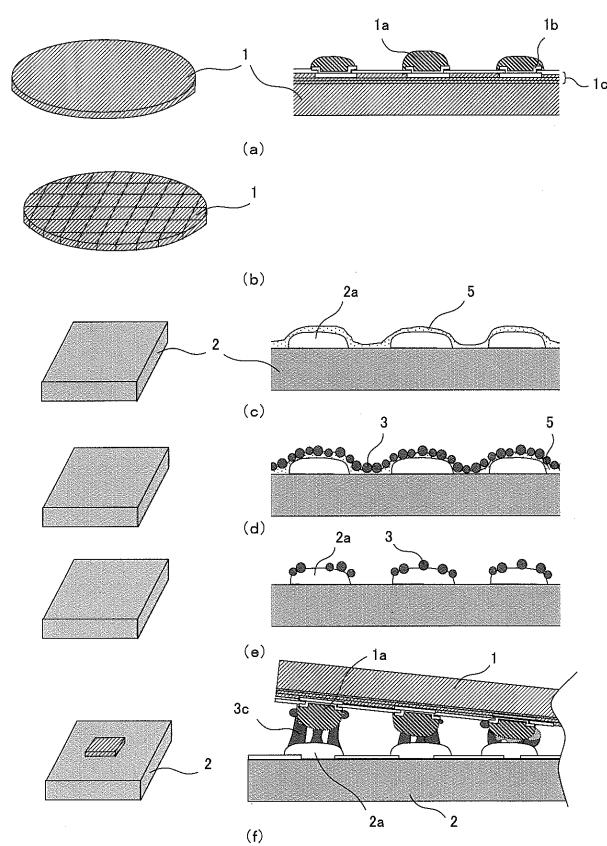

**【図3】**本実施形態2における半導体装置の製造方法(a)～(f)を概念的に示す断面図

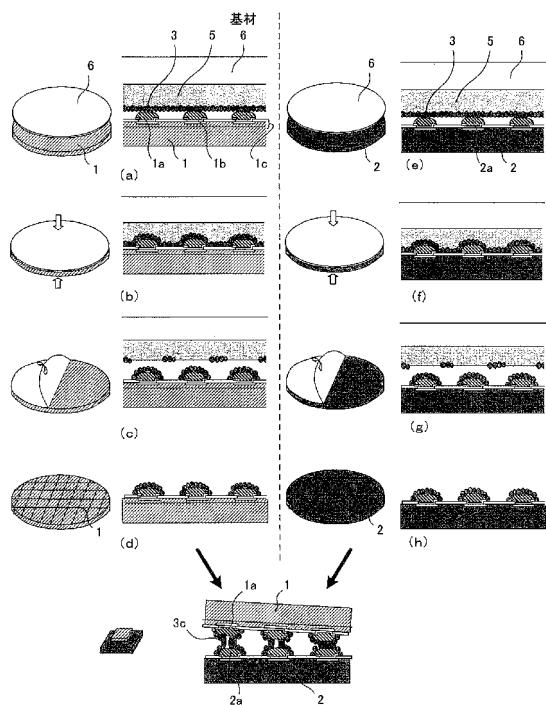

**【図4】**本実施形態3における半導体装置の製造方法(a)～(i)を概念的に示す断面図

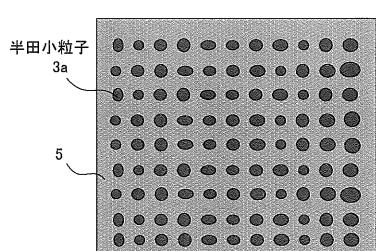

**【図5】**本実施形態3における(a)，(b)は半田粒子付着基材を概念的に示す平面図、(c)は半導体装置を概念的に示す断面図

10

20

30

40

50

【図6】本実施形態3における(a),(b)は基材の半田粒子配置を概念的に示す平面図、(c)は半導体装置を概念的に示す断面図

【図7】従来の半導体装置を概念的に示す断面図

【発明を実施するための形態】

【0028】

以下、図面を参照して本発明における実施の形態を詳細に説明する。

【0029】

(実施形態1)

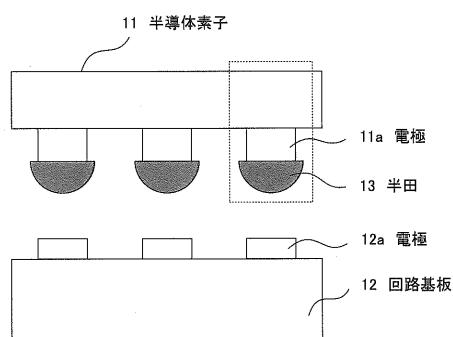

図1は本発明の実施形態1における半導体装置を概念的に示す断面図である。電子部品たる半導体素子1の電極面の内層には、例えばCuやAlからなる微細配線層と脆弱な低誘電率絶縁膜(例えば、Low-k層やUltra Low-k層)を含む多層配線層1cが設けられており、その最表面に複数の電極端子1bがエリア配置で設けられている。例えば電極端子1bはAlやCuからなる。その電極端子1b上にTi/Cu、Ti/W/Cuなどからなるシード層が設けられ、その上にNi/Au、Au、Cuなどの半田が濡れる金属からなる突起状電極1aが設けられている。

10

【0030】

一方、半導体素子1を実装した回路基板2(例えば、ガラスエポキシ多層基板、アラミド多層基板、シリコンからなる)には、半導体素子1の突起状電極1aに対向する配置の電極端子2aを有している。電極端子2aは、例えば、Ni/AuやNi/Pd/Au等からなる。

20

【0031】

半導体素子1の突起状電極1aと回路基板2の電極端子2aとは半田接合部3cにより電気的・機械的に接続されており、半田接合部3cと突起状電極1a、および半田接合部3cと電極端子2a間は、固層拡散または固液拡散反応が起こり、中間に合金層が形成され、強固に接合がされている。

【0032】

ここで、半導体素子1と回路基板2の間隔(図1中のA)が最大の半田接合部3cは、2個の微小半田接合体からなる。半田溶融工程において、半導体素子1と回路基板2の線膨張係数の違いにより、半導体素子1の最外郭に位置する接合部近傍にて、最も反りが発生しやすくなるため、半導体素子1と回路基板2の間隔が最も大きくなることが多い。

30

【0033】

さらに、半導体素子1の面内では、最外郭に位置する接合部近傍で熱応力も最大になる。このように間隔が最も大きい位置において、熱応力は最も受けるが、2個の微小半田接合体で接続することによって、1個の微小半田接合体の時よりも小さい径で、引張方向の力を受けることにより、半田部分への応力集中が増し、応力集中点が脆弱膜から半田接合部3cへ移る。しかし、半田接合部3cは伸び率が大きく、突起状電極1a、電極端子2aとは強固に接合されているので、半田接合部3cが破損することはなく伸びて、多層配線層1cの脆弱な低誘電率膜も剥離や亀裂の発生を防ぐことができる。

【0034】

半田の組成は、例えば、SnAg、SnAgCu、SnZn、SnZnBi、SnPb、SnBi、SnAgBiIn、SnIn、In、Snなどからなり、最大間隔Aの大きさに合わせ、半田伸び率から自由に材料を選ぶことができる。

40

【0035】

例えば、半導体素子1の電極端子1bの間隔が0.05mmの場合では、突起状電極1aの径は0.020~0.035mm、高さは、0.05~0.20mm、回路基板2の電極端子2aの径は0.020~0.035mm、高さは0.05~0.10mm、微小半田構造体の径は0.002~0.010mmであり、径の伸び率は50%である。

【0036】

図示はしていないが、半導体素子1と回路基板2の電極面との間には、封止樹脂が充填されていても構わない。充填されることにより、より信頼性が向上する。

50

## 【0037】

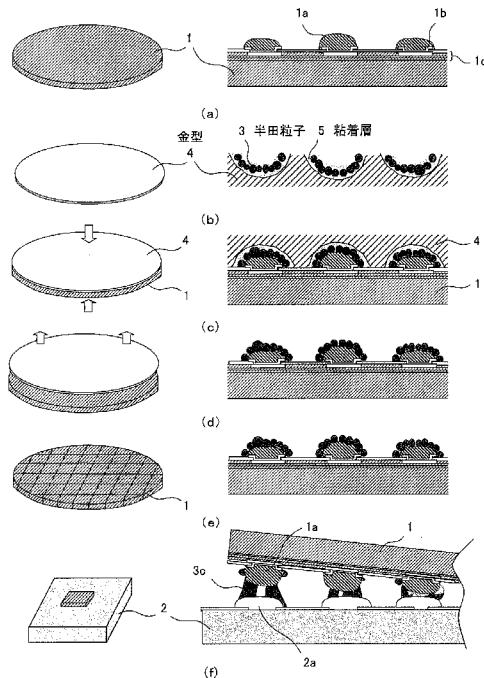

図2は本実施形態1における半導体装置の製造方法(a)～(f)を概念的に示す断面図である。以下に製造方法を説明する。

## 【0038】

まず、図2(a)に示すとおり、ウェーハ形態である半導体素子1の電極面全面に、スパッタリング法や蒸着により、シード層を形成する。次に、電解メッキ工法により全面に金属膜を形成する。感光レジスト層を形成し、電極端子1bの位置の突起状電極1aの形成部分を露光した後、剥離液を用いて感光レジストを剥離する。この工程により、電極端子1b上に、突起状電極1aが形成される。例えば、シード層には、Ti/Cu、金属膜は、Ni/Auを用いたがこれに限られない。

10

## 【0039】

次に、図2(b)に示すとおり、突起状電極1aよりも大きな形状に突起状電極1aの位置に合わせて、くり抜かれた転写用の金型4の中に、スプレーやディスペンサーなどの方法で粘着層5を金型4全面に供給した後、半田粒子3を全面に均一に付与する。

## 【0040】

次に、図2(c)に示すとおり、半導体素子1の突起状電極1aと、その突起状電極1aに対応した金型4に設けられた凹み穴が対向するように、金型4と半導体素子1の位置を合わせ、加熱・加圧を行う。これにより、半田粒子3と突起状電極1aとが溶融し、かつ半田粒子3同士が粒子形状を残すような温度、時間条件下で加熱加圧する。このとき、微細な半田粒子3を用いると酸化皮膜が占める面積が大きく、溶融を阻害しやすくなり、粒子形状を残した状態で拡散できる。例えば、半田粒子3の径が0.002～0.008mmの時、金型4の温度：210、加圧時間：10～50sで、大気圧下で加圧した。

20

## 【0041】

次に、図2(d)に示すとおり、金型4を半導体素子1から引き剥がすことにより、半田粒子3が粒子形状で付与された突起状電極1aが形成される。その後、図2(e)に示すとおり、ブレードダイシングやレーザダイシングなどの手段により、半導体素子1を個片化する。

## 【0042】

次に、図2(f)に示すとおり、半導体素子1の突起状電極1aに対向するように回路基板2の電極端子2aと位置を合わせた後、加熱し、引き上げ荷重を加えながら低荷重で、半導体素子1を回路基板2上へ搭載する。例えば、加熱温度：220～240、加圧時間：3～10秒で加圧するとよい。なお、半導体素子1を搭載する前にフラックスを供給しても構わない。溶融が困難な粒子形状の微細な半田粒子3においても、フラックスにより、半田の濡れ性が向上し、微細な半田接合部3cを形成しやすくなる。

30

## 【0043】

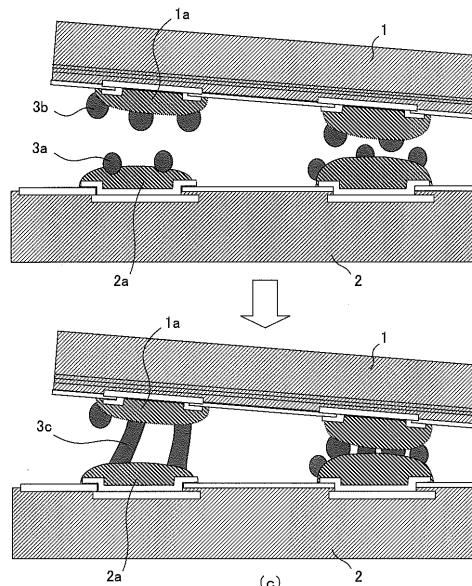

ここで、低荷重で搭載することにより、半導体素子1と回路基板2の平行度が悪くなり、半導体素子1の端部の回路基板2との距離が最も大きくなつた箇所の電極同士であっても、微細半田が図2(f)のように鼓状に伸びて接合するため、平行度の悪化を吸収することができる。

## 【0044】

図2(f)に示す半田接合部3cのように、鼓状に伸びた状態の微細半田を「微小半田接合体」と定義する。半導体素子1の突起状電極1aと回路基板2の電極端子2aとは2個以上の「微小半田接合体」で電気的に接続している。ここで、半導体素子1と回路基板2との距離が最も小さい箇所の電極同士は、複数の「微小半田接合体」で電気的に接続していてもよいし、従来と同様の1つの半田接合体で電気的に接続していてもよい。

40

## 【0045】

本実施形態1の製造方法を用いた半導体装置を、断面研磨により断面解析した結果、最外郭にある半田接合部3cは2個の微細半田接合体からなることが確認され、脆弱な低誘電率膜も剥離・亀裂が発生していないことが確認できた。さらに、温度サイクル試験(1サイクル：-45、85、各5分)に投入した結果、1000cycles(サイクル)で

50

も安定した接続抵抗を確保することができた。

【0046】

このように、最も半導体素子1と回路基板2の間隔が離れた半田接合部3cは2個の微細半田接合体でなることにより、脆弱な低誘電率膜が受ける応力が低減され、高い接続信頼性が確保できる。

【0047】

(実施形態2)

図3は本発明の実施形態2における半導体装置の製造方法(a)~(f)を概念的に示す断面図である。以下に製造方法を説明する。

【0048】

まず、図3(a)に示すとおり、ウェーハ形態である半導体素子1の電極面全面に、スパッタリング法や蒸着により、シード層を形成する。次に、電解メッキ工法により全面に金属膜を形成する。感光レジスト層を形成した後、電極端子1bの位置の突起状電極1aの形成部分を露光した後、剥離液を用いて感光レジストを剥離する。この工程により、電極端子1b上に、突起状電極1aが形成される。例えば、シード層には、Ti/Cu、金属膜は、Cuを用いたがこれに限られない。

【0049】

次に、図3(b)に示すとおり、半導体素子1をダイシングブレードやレーザ加工により、半導体素子1を個片化する。

【0050】

次に、図3(c)に示すとおり、ガラスエポキシ多層基板からなる回路基板2には無電解メッキ工法により突起状の電極端子2aを形成する。例えば、電極端子2aの組成は、Ni/Au、Ni/Pd/Au、Cuなど半田の濡れ性が良好な材料を選定する。その後、半田粒子3を全面に均一に付与するため、スプレーやディスペンサーなどの方法で粘着層5を回路基板2全面に供給する。

【0051】

次に、図3(d)に示すとおり、リフロー炉などの加熱手段で、半田粒子3を全面に均一付与した回路基板2を加熱し、半田粒子3と電極端子2aとが溶融し、かつ平面方向で半田ブリッジを起こすことなく粒子形状を残すような温度、時間、ガス雰囲気条件下で加熱する。ここで、微細な半田粒子3を用いると酸化皮膜が占める面積が大きく、溶融を阻害しやすくなるので、隣接する端子同士で半田ブリッジを起こすことなく、粒子形状を残した状態で拡散できる。例えば、半田は、Sn3.0Ag0.5Cuを用い半田粒子径が0.003~0.008mmの時、温度：225、加圧時間：3~8sで、ギ酸ガス雰囲気中で加熱した。

【0052】

次に、図3(e)に示すとおり、回路基板2を洗浄液に浸漬し、超音波を印加し洗浄した。この工程により、電極端子2a間に存在する半田粒子3が除去され、突起状の電極端子2a上に半田粒子3が電極端子2aと拡散接合された状態で付与される。

【0053】

次に、図3(f)に示すとおり、半導体素子1の突起状電極1aに対向するように回路基板2の電極端子2aと位置を合わせた後、加熱し、引き上げ荷重を加えながら低荷重で、半導体素子1を回路基板2上へ搭載する。例えば、加熱温度：250~260、加圧時間：3~10秒、窒素ガス雰囲気下で加圧した。なお、半導体素子1を搭載する前にフラックスまたはフラックス成分を含有する封止樹脂を供給しても構わない。溶融が困難な微細半田においても、フラックスにより、半田の濡れ性が向上し、微細半田接合体を形成しやすくなる。ここで、低荷重で搭載することにより、半導体素子1と回路基板2の平行度が悪くなるが、微細半田が図のように鼓状に伸びて接合するため、平行度の悪化を吸収することができる。

【0054】

本実施形態2の製造方法を用いた半導体装置を、断面研磨により断面解析した結果、最

10

20

30

40

50

外郭にある突起状電極 1 a、電極端子 2 a では、半導体素子 1 と回路基板 2 の間隔が最も離れており、半田接合部 3 c は 3 個の微細半田接合体からなることが確認され、脆弱な低誘電率膜も剥離・亀裂が発生していないことが確認できた。さらに、温度サイクル試験(1 サイクル: -45 、 85 、各 5 分)に投入した結果、1000 cycle (サイクル) でも安定した接続抵抗を確保することができた。

#### 【0055】

このように、半導体素子 1 と回路基板 2 の電極側に半田粒子 3 を付与した場合においても、最も半導体素子 1 と回路基板 2 の間隔が離れた半田接合部 3 c は 2 個以上の微細半田接合体でなることにより、脆弱な低誘電率膜が受ける応力が低減され、高い接続信頼性が確保できる。

10

#### 【0056】

##### (実施形態 3)

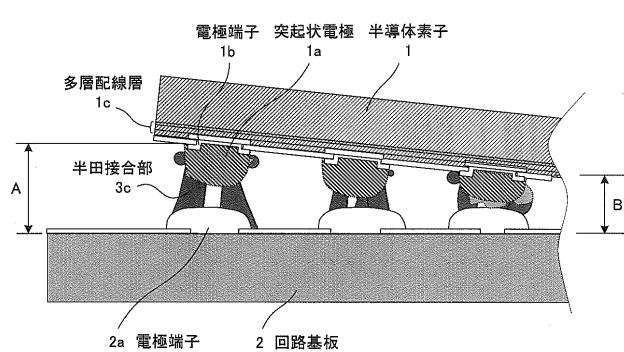

図 4 は本発明の実施形態 3 における半導体装置の製造方法 (a) ~ (i) を概念的に示す断面図である。以下に製造方法を説明する。

#### 【0057】

まず、ウェーハ形態であり、シリコンからなる半導体素子 1 の A 1 からなる電極端子 1 b 上に、無電解メッキ工法を用いて Ni-P / Au からなる突起状電極 1 a を形成する。

#### 【0058】

一方、スプレーやディスペンサー、バーコーター、スピンドルコーターなどの手段で、例えば PET や PEN からなる基材 6 全面に粘着層 5 を塗布し、その上に半田粒子 3 を均等に分散するように付着させる。例えば、半田粒子 3 として、組成、Sn 3.5 Ag 8.0 In 0.5 Bi、粒子径 0.002 ~ 0.006 mm の粒子を用いることができる(図 4 (a) 参照)。

20

#### 【0059】

次に、前記基材 6 の半田粒子 3 が付着された面と半導体素子 1 の突起状電極 1 a の面同士を加熱・加圧しながら貼り付ける。ここで、半田粒子 3 が局所的に溶融し、突起状電極 1 a と拡散接合し、かつ平面方向で半田ブリッジを起こすことなく粒子形状を残すような温度、時間条件下で加熱・加圧する(図 4 (b) 参照)。なお、粘着層 5 は、半田粒子 3 を基材 6 に保持させる機能、半田酸化皮膜を除去する機能、離型機能を有する材料を用いることが望ましいが、これに限られない。図示しないが、フラックスや離型材などの材料をさらに基材 6 上に供給しても構わない。

30

#### 【0060】

次に、加熱しながら基材 6 を半導体素子 1 から剥離する。この工程により、突起状電極 1 a の間に存在する半田粒子 3 は基材 6 側に付着したまま、半導体素子 1 上からは除去され、突起状電極 1 a 上に半田粒子 3 が突起状電極 1 a と拡散接合された状態で付与される(図 4 (c), (d) 参照)。

#### 【0061】

次に、ウェーハ形態であり、シリコンからなる回路基板 2 にも、半導体素子 1 と同様の工程にて、半田粒子 3 が回路基板 2 の電極端子 2 a 上に電極端子 2 a と拡散接合された状態で付与される(図 4 (e) ~ (g) 参照)。

40

#### 【0062】

次に半導体素子 1 および回路基板 2 をそれぞれ、ブレードダイシングやレーザダイシング工法により個片化する(図 4 (d), (h) 参照)。

#### 【0063】

次に、半導体素子 1 の突起状電極 1 a に対向するように回路基板 2 の電極端子 2 a と位置を合わせた後、加熱し、引き上げ荷重を加えながら低荷重で、半導体素子 1 を回路基板 2 上へ搭載する。例えば、加熱温度: 210 ~ 230 、加圧時間: 2 ~ 9 秒、窒素ガス雰囲気下で加圧した。なお、半導体素子 1 を搭載する前にフラックスまたはフラックス成分を含有する封止樹脂を供給しても構わない。溶融が困難な微細半田においても、フラックスにより、半田の濡れ性が向上し、微細半田接合体を形成しやすくなる。ここで、低荷

50

重で搭載することにより、半導体素子 1 と回路基板 3 の平行度が悪くなるが、微細半田が図のように鼓状に伸びて接合するため、平行度の悪化を吸収することができる（図 4（i）参照）。

#### 【0064】

本実施形態 3 の製造方法を用いた半導体装置を、断面研磨により断面解析した結果、最外郭にある突起状電極 1 a、電極端子 2 a では、半導体素子 1 と回路基板 2 の間隔が最も離れており、半田接合部 3 c は 2 個の微細半田接合体からなることが確認され、脆弱な低誘電率膜も剥離・亀裂が発生していないことが確認できた。さらに、温度サイクル試験（1 サイクル：-55、125、各 5 分）に投入した結果、1000 cycles（サイクル）でも安定した接続抵抗を確保することができた。

10

#### 【0065】

このように、半導体素子 1 の突起状電極 1 a と回路基板 2 の電極端子 2 a の両側に半田粒子 3 を付与した場合において、最も半導体素子 1 と回路基板 2 の間隔が離れた半田接合部 3 c は 2 個以上の微細半田接合体でなるとともに、微細半田接合体の高さが高くなることで、温度サイクル試験で受けるせん断方向の応力を緩和する効果が働くため、脆弱な低誘電率膜が受ける応力がより低減され、高い接続信頼性が確保できる。

#### 【0066】

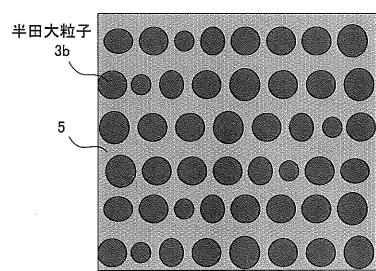

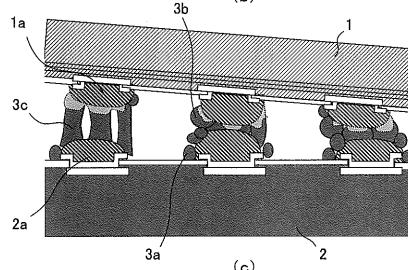

また、図 5（a）、（b）は本実施形態 3 における半田粒子付着基材を概念的に示す平面図であり、図 5（c）は本実施形態 3 における半導体装置を概念的に示す断面図である。

20

#### 【0067】

図 5（a）において、微細な半田小粒子 3 a が、粘着層が全面に塗布された基材上に分散配置されている。図 5（b）においても、微細な半田大粒子 3 b が、粘着層が全面に塗布された基材上に分散配置されている。ここで、半田小粒子 3 a の粒子径は、半田大粒子 3 b の粒子径よりも小さく、半田大粒子 3 b の粒子径の 1/2 以下であることが望ましい。また互いの半田小粒子 3 a の中心との間隔の距離（ピッチ）は、互いの半田大粒子 3 b の中心との間隔の距離（ピッチ）よりも小さい。

#### 【0068】

図 5（c）において、半導体素子 1 には半田大粒子 3 b が付着した基材を、回路基板 2 には半田小粒子 3 a が付着した基材を用いて、前述した製造方法により、それぞれの突起状電極 1 a、電極端子 2 a に微細半田粒子を拡散接合させる。この工程により、半導体素子 1 には大きな半田大粒子 3 b が、回路基板 2 には小さな半田小粒子 3 a が電極に拡散接合される。

30

#### 【0069】

そして、半導体素子 1 を回路基板 2 に実装する工程において、半導体素子 1 の突起状電極 1 a 上の半田大粒子 3 b の隙間に、回路基板 2 の電極端子 2 a 上の半田小粒子 3 a が入り込む形態で搭載され、かみ合うので、加熱中に回路基板 2 の反りが大きくなってしまっても、半導体素子 1 と回路基板 2 の平面方向の位置ずれを抑えながら、前述の微小半田接合体を形成することができる。

40

#### 【0070】

なお、半導体素子 1 には半田小粒子 3 a とし、回路基板には半田大粒子 3 b としてもよい。

#### 【0071】

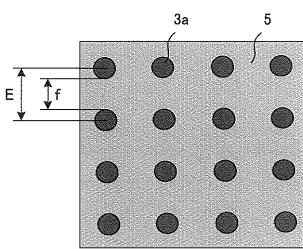

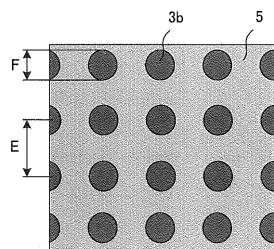

また、図 6（a）、（b）は本実施形態 3 における基材の半田粒子配置を概念的に示す平面図であり、図 6（c）は本実施形態 3 における半導体装置を概念的に示す断面図である。

#### 【0072】

図 6（a）において、微細な半田小粒子 3 a が回路基板 2 用の粘着層 5 を全面に塗布した基材上に分散配置され、図 6（b）において、微細な半田大粒子 3 b が、半導体素子 1 用の粘着層 5 を全面に塗布した基材上に分散配置されている。ここで、半田小粒子 3 a、

50

半田大粒子 3 b 共に同一のピッチ E ( 図 6 中に E で示す半田粒子の中心との間隔の距離 ) で並べられている。また半田大粒子 3 b の径 ( F ) は、半田小粒子 3 a の隣接する粒子間の間隔 ( f ) 以下である。

#### 【 0 0 7 3 】

なお、半導体素子 1 の突起状電極 1 a に小さな半田小粒子 3 a を配置し、回路基板 2 の電極端子 2 a に大きな半田大粒子 3 b を配置してもよい。

#### 【 0 0 7 4 】

そして、前述と同様の工程を実施すると、半導体素子 1 を回路基板 2 に実装する工程において、半導体素子 1 の突起状電極 1 a 上の半田大粒子 3 b の隙間に、回路基板 2 の電極端子 2 a 上の半田小粒子 3 a が入り込む形態で搭載される。したがって、半田大粒子 3 b と半田小粒子 3 a とが交互に配置できるので、加熱中に回路基板 2 等の反りが大きくなり、半導体素子 1 と回路基板 2 の平面方向の位置ずれが大きくなってしまっても、間隔の狭くなった半田大粒子 3 b と半田小粒子 3 a とにより微小半田接合部が形成される。このことにより、2 個以上の微小半田接合部を介して 1 組の半導体素子 1 の突起状電極 1 a と回路基板 2 の電極端子 2 a とを電気的に接続することが可能となる。

10

#### 【 0 0 7 5 】

以上の各実施形態では、電子部品として半導体素子、回路基板を例示して説明したが、これに限られない。電極端子間ピッチが狭いコンデンサ、コイル、抵抗などの受動部品を用いる場合も同様の効果が得られる。また、半導体素子はウェーハ形態を例示して説明したが、これにも限られない。半導体素子を長方形または正方形に個片化した状態で製造したとしても同様の効果が得られる。

20

#### 【 産業上の利用可能性 】

#### 【 0 0 7 6 】

本発明は、複数の微細半田接合部によって半導体素子電極と回路基板電極とを電気的・機械的に接合する半導体装置の構造および製造方法であり、狭ピッチの接続においても高い信頼性を実現することができ、狭ピッチ化が進展する半導体素子や、低誘電率材料などからなる層間絶縁膜を有する半導体素子などを実装する実装分野において特に有用である。

#### 【 符号の説明 】

#### 【 0 0 7 7 】

30

- 1 , 1 1 半導体素子

- 1 a 突起状電極

- 1 b , 2 a 電極端子

- 1 c 多層配線層

- 2 , 1 2 回路基板

- 3 半田粒子

- 3 a 半田小粒子

- 3 b 半田大粒子

- 3 c 半田接合部

- 4 金型

- 5 粘着層

- 6 基材

- 1 1 a , 1 2 a 電極

- 1 3 半田

40

【図1】

【図2】

【図3】

【図4】

【図5】

(a)

(b)

(c)

【図6】

(a)

(b)

(c)

【図7】