(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5013812号

(P5013812)

(45) 発行日 平成24年8月29日(2012.8.29)

(24) 登録日 平成24年6月15日(2012.6.15)

(51) Int.Cl.

F 1

**HO4N 5/367 (2011.01)**

**HO4N 5/374 (2011.01)**

**HO1L 27/146 (2006.01)**

**HO4N 101/00 (2006.01)**

HO4N 5/335 67O

HO4N 5/335 74O

HO1L 27/14 A

HO4N 101:00

請求項の数 4 (全 12 頁)

(21) 出願番号

特願2006-291718 (P2006-291718)

(22) 出願日

平成18年10月26日 (2006.10.26)

(65) 公開番号

特開2008-109504 (P2008-109504A)

(43) 公開日

平成20年5月8日 (2008.5.8)

審査請求日

平成21年10月26日 (2009.10.26)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(72) 発明者 永田 桂次

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置及び補正方法

## (57) 【特許請求の範囲】

## 【請求項 1】

被写体像からの光を受光して信号電荷を発生する光電変換部と、前記光電変換部からの信号電荷が転送される半導体領域と、前記光電変換部の信号電荷を前記半導体領域に転送する転送手段と、前記半導体領域の信号電荷に応じた電圧信号を読み出す読み出し手段とを有する画素を複数備えた撮像素子と、

前記撮像素子の飽和画素を探索し、飽和画素が検出された場合に、前記飽和画素の隣接画素が飽和しているかどうかを判断する飽和検出手段と、

前記飽和検出手段により前記飽和画素の隣接画素が飽和していないと判断された場合に、前記飽和画素が欠陥画素であると判定し、前記飽和画素の隣接画素が飽和していると判断された場合に、前記飽和画素が欠陥画素ではないと判定する欠陥画素判定手段と、

前記欠陥画素判定手段により判定された欠陥画素において、前記光電変換部からの信号電荷が前記半導体領域に転送される前に前記半導体領域に蓄積された信号電荷に応じた電圧信号を読み出すことで得られるノイズ信号レベルの所定割合を前記欠陥画素の隣接画素から読み出される電圧信号から減算する減算手段と、

前記欠陥画素の周辺画素から出力される電圧信号を用いて前記欠陥画素の電圧信号を補間する補正手段と

を有することを特徴とする撮像装置。

## 【請求項 2】

前記飽和検出手段は、前記ノイズ信号が予め設定された閾値より大きい場合に、該ノイ

ズ信号を読み出した画素を飽和画素として検出することを特徴とする請求項 1 に記載の撮像装置。

**【請求項 3】**

被写体像からの光を受光して信号電荷を発生する光電変換部と、前記光電変換部からの信号電荷が転送される半導体領域と、前記光電変換部の信号電荷を前記半導体領域に転送する転送手段と、前記半導体領域の信号電荷に応じた電圧信号を読み出す読み出し手段とを有する画素を複数備えた撮像素子から得られる電圧信号の補正方法であって、

前記撮像素子の飽和画素を探索し、飽和画素が検出された場合に、前記飽和画素の隣接画素が飽和しているかどうかを判断する飽和検出工程と、

前記飽和検出工程で前記飽和画素の隣接画素が飽和していないと判断された場合に、前記飽和画素が欠陥画素であると判定し、前記飽和画素の隣接画素が飽和していると判断された場合に、前記飽和画素が欠陥画素ではないと判定する欠陥画素判定工程と、

前記欠陥画素判定工程で判定された欠陥画素において、前記光電変換部からの信号電荷が前記半導体領域に転送される前に前記半導体領域に蓄積された信号電荷に応じた電圧信号を読み出すことで得られるノイズ信号レベルの所定割合を前記欠陥画素の隣接画素から読み出される電圧信号から減算する減算工程と、

前記欠陥画素の周辺画素から出力される電圧信号を用いて前記欠陥画素の電圧信号を補間する補正工程と、

を有することを特徴とする補正方法。

**【請求項 4】**

前記飽和検出工程では、前記ノイズ信号が予め設定された閾値より大きい場合に、該ノイズ信号を読み出した画素を飽和画素として検出することを特徴とする請求項 3 に記載の補正方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、撮像装置及び補正方法に関し、更に詳しくは、撮像素子を用いた撮像装置において、撮像素子の欠陥画素の出力を補正する技術に関するものである。

**【背景技術】**

**【0002】**

従来、デジタルカメラやビデオカメラ等の撮像装置において、CCD や CMOS センサ等の固体撮像素子が一般的に使用されている。この固体撮像素子では、製造過程において発生する欠陥画素が、画質の低下や製造上の歩留まりを下げる要因の一つとなっていることが知られている。欠陥画素を完全に無くすことは困難であることから、一般的に、欠陥画素の周囲画素を用いた補間処理を行って画質向上を図ることが知られている。

**【0003】**

欠陥画素から出力される信号の補正技術として、例えば、特許文献 1 の「従来の技術」に記載された方法が知られている。この方法では、まず、固体撮像素子の工場出荷時等に、所定の条件下において標準電荷蓄積時間、固体撮像素子を露光して得られる出力値を用いて欠陥画素を判定する。そして、その際に取得した欠陥画素の位置情報及び出力レベル等の情報を記憶しておき、撮像時には、この記憶した欠陥画素の位置情報及び出力レベル等の情報を基にして、欠陥画素に隣接する画素の出力レベルを用いて、欠陥画素の出力の補間処理を行う。

**【0004】**

一方、長秒時露光時に行う以下のような技術が提案されている。まず、実撮影に先立つてダーク画像を撮影し、そのダーク画像から所定出力以上のものを欠陥画素として抽出して記憶しておき、実撮影で得られた画像に対して、抽出した欠陥画素を補正する。また、抽出された欠陥画素以外については、実撮影で得られた各画素の出力レベルから、ダーク画像における対応する画素の出力レベルを減算する、所謂黒引きを行う。このように補正することで、長秒時露光時に起こる欠陥画素の出力レベルの増大に対しても、システムが

10

20

30

40

50

破錠をせず、画像劣化を最小限に抑えた補正をすることができる（例えば、特許文献 2 を参照）。

#### 【 0 0 0 5 】

また、欠陥画素の出力を補正するための複数の補正用データを備え、電荷蓄積時間や撮影感度等の撮影条件、温度等の撮影環境に応じて最適なデータを選択して、撮影画像の補正を行う技術も提案されている（例えば、特許文献 1 を参照）。

#### 【 0 0 0 6 】

【特許文献 1】特開 2003 - 333435 号公報

【特許文献 2】特開 2001 - 028713 号公報

【特許文献 3】特開 2006 - 222762 号公報

10

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【 0 0 0 7 】

欠陥画素には暗電流に起因し、温度や電荷の蓄積時間によって出力レベルが大きく変化するものがある。このような暗電流に起因する欠陥画素の出力レベルは、高温下や長時間の露光（長秒時露光）時により暗電流が増加することで増大する。

#### 【 0 0 0 8 】

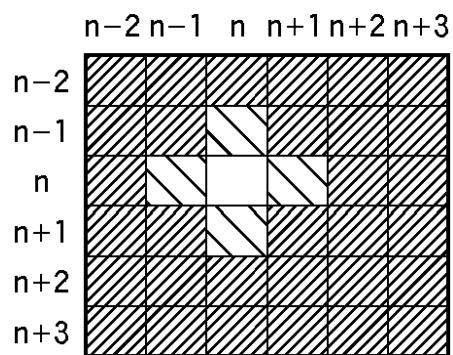

上述した暗電流起因の欠陥画素からは、暗電流の増加によって蓄積された電荷が画素の飽和レベル以上に達した場合に、以下のような現象が起きる。即ち、画素の飽和レベルを超えた分の数パーセントが隣接画素に漏れ込んでしまい、その結果、図 7 に示すように、隣接画素の出力レベルが不必要に高くなり、十字状の欠陥画素領域となってしまう。図 7 では、座標 (n, n) が暗電流起因の欠陥画素であり、その上下左右に隣接する座標 (n-1, n)、(n+1, n)、(n, n-1)、(n, n+1) に位置する画素も電荷の漏れ込みにより出力レベルが高くなってしまう現象が生じた様子を示している。

20

#### 【 0 0 0 9 】

上記特許文献 2 に記載の方法では、キズを抽出するために実撮影に先立って実撮影と同じ電荷蓄積時間でダーク画像を取り込む時間が必要であるため、撮影が指示されてから実際に撮影が行われるまでのレリーズタイムラグが長くなってしまう。特に、電荷の隣接画素への漏れ込みが生じるほどの長秒時撮影では、レリーズタイムラグが非常に長くなってしまう。しかしながら、レリーズタイムラグを短くしようとすると今度は、電荷が漏れ込んだ隣接画素を抽出することができず、補正ができないという問題があった。

30

#### 【 0 0 1 0 】

また、図 7 に示すような暗電流起因の十字状の欠陥画素領域に対して特許文献 1 のような補正を行おうとすると、以下のような問題があった。即ち、温度・電荷の蓄積時間によって出力レベルが変化するので、各欠陥画素に対して条件毎に隣接画素の補正を行う可動化の情報とアドレスを持っておく必要があり、記憶させておくメモリの容量が必要であった。

#### 【 0 0 1 1 】

また近年では、CMOS センサにおいてフローティングディフュージョン部に漏れ込んだ信号を利用して飽和出力を算出し、ダイナミックレンジ拡大を行う提案が成されている（例えば、特許文献 3 参照）。しかしながら、FD 部に漏れ込んだ信号が、被写体からの光により飽和したしたものか、欠陥画素による暗電流等のノイズ信号による飽和かを判断ができないため、画質劣化を防ぐ手段にはなっていない。

40

#### 【 0 0 1 2 】

本発明は上記問題点を鑑みてなされたものであり、特別な装置構成を追加せず、かつ、レリーズタイムラグを短く留めたまま、欠陥画素が飽和した場合に画像信号を適切に補正できるようにすることを目的とする。

#### 【課題を解決するための手段】

#### 【 0 0 1 3 】

上記目的を達成するために、本発明の撮像装置は、被写体像からの光を受光して 信号電

50

荷を発生する光電変換部と、前記光電変換部からの信号電荷が転送される半導体領域と、前記光電変換部の信号電荷を前記半導体領域に転送する転送手段と、前記半導体領域の信号電荷に応じた電圧信号を読み出す読み出し手段とを有する画素を複数備えた撮像素子と、前記撮像素子の飽和画素を探索し、飽和画素が検出された場合に、前記飽和画素の隣接画素が飽和しているかどうかを判断する飽和検出手段と、前記飽和検出手段により前記飽和画素の隣接画素が飽和していないと判断された場合に、前記飽和画素が欠陥画素であると判定し、前記飽和画素の隣接画素が飽和していると判断された場合に、前記飽和画素が欠陥画素ではないと判定する欠陥画素判定手段と、前記欠陥画素判定手段により判定された欠陥画素において、前記光電変換部からの信号電荷が前記半導体領域に転送される前に前記半導体領域に蓄積された信号電荷に応じた電圧信号を読み出すことで得られるノイズ信号レベルの所定割合を前記欠陥画素の隣接画素から読み出される電圧信号から減算する減算手段と、前記欠陥画素の周辺画素から出力される電圧信号を用いて前記欠陥画素の電圧信号を補間する補正手段とを有する。

#### 【0014】

また、被写体像からの光を受光して信号電荷を発生する光電変換部と、前記光電変換部からの信号電荷が転送される半導体領域と、前記光電変換部の信号電荷を前記半導体領域に転送する転送手段と、前記半導体領域の信号電荷に応じた電圧信号を読み出す読み出し手段とを有する画素を複数備えた撮像素子から得られる電圧信号の本発明の補正方法は、前記撮像素子の飽和画素を探索し、飽和画素が検出された場合に、前記飽和画素の隣接画素が飽和しているかどうかを判断する飽和検出工程と、前記飽和検出工程で前記飽和画素の隣接画素が飽和していないと判断された場合に、前記飽和画素が欠陥画素であると判定し、前記飽和画素の隣接画素が飽和していると判断された場合に、前記飽和画素が欠陥画素ではないと判定する欠陥画素判定工程と、前記欠陥画素判定工程で判定された欠陥画素において、前記光電変換部からの信号電荷が前記半導体領域に転送される前に前記半導体領域に蓄積された信号電荷に応じた電圧信号を読み出すことで得られるノイズ信号レベルの所定割合を前記欠陥画素の隣接画素から読み出される電圧信号から減算する減算工程と、前記欠陥画素の周辺画素から出力される電圧信号を用いて前記欠陥画素の電圧信号を補間する補正工程とを有する。

#### 【発明の効果】

#### 【0015】

本発明によれば、特別な装置構成を追加せず、かつ、レリーズタイムラグを短く留めたまま、欠陥画素が飽和した場合に画像信号を適切に補正することができる。

#### 【発明を実施するための最良の形態】

#### 【0016】

以下、添付図面を参照して本発明を実施するための最良の形態を詳細に説明する。

#### 【0017】

<第1の実施形態>

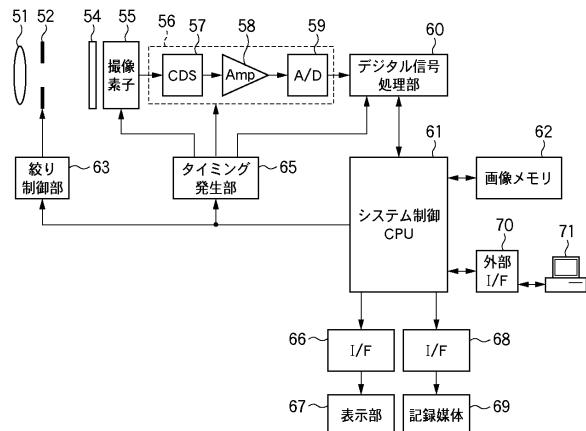

図1は本発明の実施の形態における撮像装置として、デジタルスチルカメラの概略構成を示すブロック図である。

#### 【0018】

図1において、51は被写体の光学像を撮像素子55に結像させるレンズ、52はレンズ51を通った光の光量を調節するための絞りであり、絞り制御部63により制御される。54は撮像素子55に入射する光の波長あるいは、空間周波数を制限する光学フィルタ、55はレンズ51を介して結像された被写体の光学像を電気的な画像信号に変換する撮像素子である。56は撮像素子55から出力される画像信号のアナログ処理とアナログ-ディジタル変換を行うアナログフロントエンドである。アナログフロントエンド56はノイズを除去する二重相関サンプリング(CDS)回路57、信号ゲインを調整するアンプ58、アナログ信号をデジタル化するA/D変換器59で構成される。60はアナログフロントエンド56より出力されたデジタル画像データに各種の補正を行ったり、画像データを圧縮するデジタル信号処理部である。

10

20

30

40

50

## 【0019】

65は撮像素子55、アナログフロントエンド56、デジタル信号処理部60に、各種タイミング信号を出力するタイミング発生部、61は各種演算とデジタルスチルカメラ全体を制御するシステム制御CPUである。62は画像データを一時的に記憶するための画像メモリ、66は撮影された画像を表示するための表示インターフェース部、67は液晶ディスプレイ等の表示部である。68は記録媒体に記録または読み出しを行うための記録インターフェース部、69は画像データや付加データ等を記録するための半導体メモリ等の着脱可能な記録媒体、70は外部コンピュータ71等と通信するための外部インターフェース部である。

## 【0020】

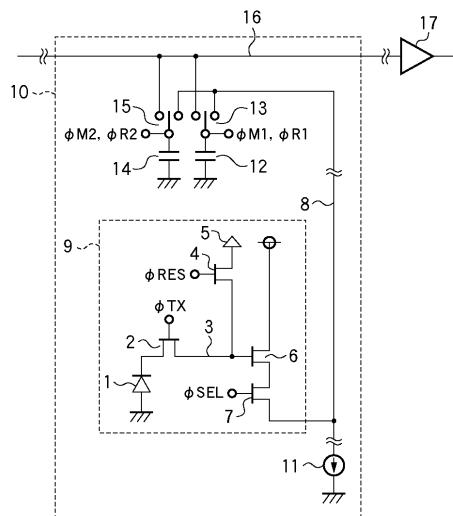

図2は撮像素子55の主に1画素分の回路を示す図であり、ここではCMOSセンサの構成を示している。

## 【0021】

図2において、1はフォトダイオード(PD)であり、転送スイッチ2を介してフローティングディフュージョン部(FD)3に接続される。また、FD3はリセットスイッチ4を介してリセット電圧を供給する電源線5に接続されている。また、FD3は電界効果トランジスタ(FET)6のゲートになっている。FET6のドレインは所定電圧に接続され、ソースは選択スイッチ7を介して、垂直出力線8に接続されている。ここまで要素により、画素9が構成されている。同様な構成を有する画素が垂直出力線8に沿って複数個構成され列10を構成し、同様な構成を有する列を水平方向に複数個構成することによりエリアセンサが構成される。

## 【0022】

また、それぞれの垂直出力線8には少なくとも1つの定電流源11が接続されており、選択された画素のFD3の電荷により垂直出力線8の電圧が決まる構成になっている。また、垂直出力線8には画素出力を一時記憶するためのメモリとしてのコンデンサ12がスイッチ13を介して接続されており、また、飽和出力を一時記憶するためのメモリとしてのコンデンサ14がスイッチ15を介して接続されている。また、これらのコンデンサ12、14はそれぞれスイッチ13、15を介して読み出し線16に接続されており、コンデンサ12、14に記憶された画素出力は読み出し線16から出力アンプ17を介して読み出される。

## 【0023】

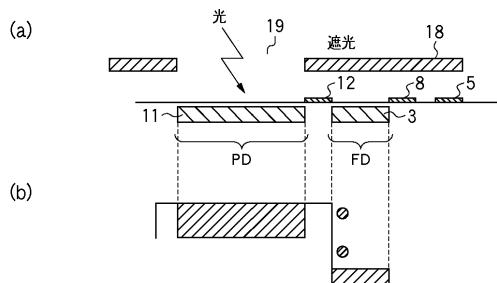

図3は図2に示す画素9のPD1、FD3の断面構成及び飽和時の各構成のポテンシャルの概念を示す図である。なお、図2に対応する構成には同じ参照番号を付している。

## 【0024】

図3(a)において、11はPD1の拡散領域、12は転送スイッチ2のゲート電極、3はフローティングディフュージョン部(半導体拡散領域)、19はPD1上の遮光膜の開口部、18はFD1上の遮光膜である。8は垂直信号線、5は電源線である。図3(b)に示すように、PD1で発生した電荷が飽和するとFD3に漏れ込む。

## 【0025】

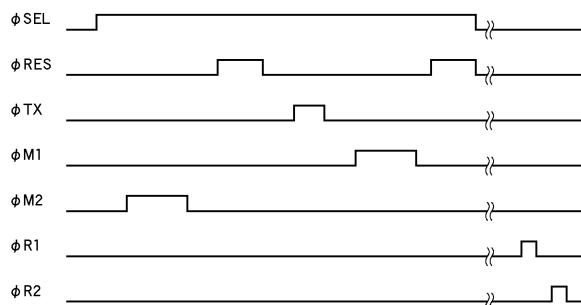

図4はタイミング発生部65から出力される各種パルスのタイミングを示す。以下、図4を参照して動作を説明する。

## 【0026】

ある画素を選択するとき、選択対象の画素の選択パルスSELが「High(H)」になり、選択スイッチ7がオンされる。このとき、PD1が飽和していれば電荷がFD3に流れ込み、FD3にはPD1の飽和電荷量を超えた分の電荷が蓄積されている。このようにPD1の電荷が転送スイッチ2を介して転送される前にFD3に蓄積されている電荷(ノイズ成分)はFET6により電荷電圧変換され、垂直出力線8に電荷に対応した電圧が出力される。

## 【0027】

この状態でメモリパルスM2をHにしてスイッチ15を垂直出力線8に接続すること

10

20

30

40

50

によって、読み出されたノイズ成分の電荷に対応する電圧をコンデンサ14に一時記憶する。

**【0028】**

その後、リセットパルスRESを「H」にして、リセットスイッチ4をオンにし、FD3を所定のリセット電圧にリセットする。次に、転送パルスTXを「H」にして、転送スイッチ2をオンにし、PD1に蓄積された電荷（光成分）をFD3に読み出す。FD3に読み出された光成分の電荷はFET6により電荷電圧変換され、対応する電圧が垂直出力線8に出力される。この状態でメモリパルスM1を「H」にしてスイッチ13を垂直出力線8に接続することによって、光成分の電荷に対応した電圧をコンデンサ12に一時記憶する。

10

**【0029】**

次に、読み出しパルスR1を「H」にしてスイッチ13を読み出し線16に接続し、一時記憶した光成分の電荷に対応した電圧を読み出し線16に出力し、出力アンプ17を介して光信号として出力する。さらにその後、読み出しパルスR2を「H」にしてスイッチ15を読み出し線16に接続し、ノイズ成分の電荷に対応した電圧を読み出し線16に出力し、出力アンプ1を介してノイズ信号として出力する。

**【0030】**

このようにして撮像素子55から出力された光信号とノイズ信号はA/D変換器59によりデジタルデータに変換され、光信号から光出力画像、ノイズ信号からノイズレベルと領域を示すノイズ画像として、図1のデジタル信号処理部60に送られる。

20

**【0031】**

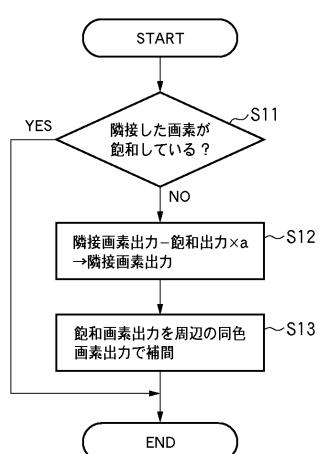

次に本第1の実施形態においてデジタル信号処理部60内で実行される、欠陥画素信号の補正処理について、図5のフローチャートを参照して説明する。

**【0032】**

先ず、ステップS11でノイズ画像から飽和画素を検出し、更に隣接した画素が飽和しているかを判断する。飽和画素の検出方法としては、例えば、ノイズ画像の各ノイズ信号値を予め設定された値やノイズ画像の平均信号値などと比較し、ノイズ信号値の方が大きい場合に、対応する画素が飽和していると判断する。ただし、本発明は飽和画素の検出方法によって制限されるものではなく、公知の方法を用いて検出しても良い。

**【0033】**

隣接する画素が飽和している場合には、被写体が明るいために画素の飽和が発生しているものと判断し、そのままルーチンを終了する。これは、被写体からの光はレンズ51やローパスフィルタ等の光学フィルタ54を通過し、拡散されるため、被写体からの光による飽和領域が1画素の大きさとなることはないからである。これに対し、欠陥画素の暗電流による飽和は1画素単独で発生する。このため、飽和領域の大きさにより欠陥画素によるものか被写体からの光によるものかを判断することができる。

30

**【0034】**

ステップS11で飽和画素が単独である、即ち、飽和画素が隣接していないと判断された場合、ステップS12に進み、飽和画素のノイズ信号レベルの所定の割合aの信号レベルを、光出力画像においてその飽和画素に隣接する画素の光信号から減算する。所定の割合aは欠陥画素の暗電流が長時間蓄積により飽和し、飽和を超えたレベルのうち隣接画素に漏れ込む割合に相当する。飽和画素が1画素で存在した場合、被写体輝度による飽和ではなく、画素欠陥の暗電流による飽和であると判断でき、隣接する画素の信号レベルとの差は大きいと推測される。この補正を行うことで、飽和画素に隣接する画素の本来の光信号を得ることができ、画質劣化を防ぐことができる。

40

**【0035】**

次にステップS13へ進み、単独に飽和している画素は欠陥画素と判断し、光出力画像における欠陥画素の光信号を同色の周辺画素の光信号を用いて補間して、この処理を終了する。

**【0036】**

50

このようにすることで、欠陥画素が飽和している場合に、欠陥画素及び周辺の光信号を適切に補正することができる。

#### 【0037】

次に、上述した補正処理を行うデジタルスチルカメラにおける撮影時の動作について説明する。

#### 【0038】

不図示の電源スイッチが入れられるとメイン電源がオンとなり、コントロール系の電源がオンし、さらに、アナログフロントエンド56等の撮像系回路の電源がオンとなる。

#### 【0039】

その後、露光量を制御するために、システム制御CPU61は、絞り制御部63を介して絞り52を開放にする。この状態で撮像素子55から出力された画像信号はアナログフロントエンド56で変換された後、デジタル信号処理部60に入力される。そのデータを基にしてシステム制御CPU61は露出の演算を行う。この測光を行った結果により明るさを判断し、その結果に応じてシステム制御CPU61は絞り52を制御する。10

#### 【0040】

次に、撮像素子55から出力された画像信号から高周波成分を取り出し、鮮鋭度の演算をシステム制御CPU61で行う。その後、レンズ51を駆動して再び鮮鋭度の演算を行って、合焦か否か（鮮鋭度が最大か否か）を判断し、合焦していないと判断したときは、レンズ51を駆動してから再び鮮鋭度の演算を行う。この制御を鮮鋭度が最大となるまで繰り返し、鮮鋭度が最大となった（合焦が確認された）後に、撮像素子55の電子シャッター機能を利用して、上述したようにして本露光の開始、露光の終了を行う。その後各行毎に順次、光出力画像及びノイズ画像を出力する。撮像素子55から出力された画像信号はアナログフロントエンド56で二重相関サンプリング等のノイズ除去、増幅、A/D変換が行われ、デジタル化される。20

#### 【0041】

デジタル化された画像信号は、デジタル信号処理部60を通り、上記処理を行った後、システム制御CPU61により画像メモリ62に書き込まれる。その後、画像メモリ62に記憶された画像データは、システム制御CPU61の制御により記録インターフェース部68を通り半導体メモリ等の着脱可能な記録媒体69に記録される。また、撮影された画像データを、表示インターフェース部66を通り液晶ディスプレイ等の表示部67に表示する。或いは、外部インターフェース部70を通り直接コンピュータ71等に入力して画像の加工を行っても良い。30

#### 【0042】

なお、上記本第1の実施形態では、図5のステップS11において、飽和画素が欠陥画素か否かの判断を行うが、この判断をダイナミックレンジの拡大に利用することが可能である。例えば、飽和画素が欠陥画素でない場合には、飽和画素のノイズ信号を光信号に加算することにより、ダイナミックレンジを拡大することができる。

#### 【0043】

<第2の実施形態>

次に、本発明の第2の実施形態について、図面を参照して説明する。40

#### 【0044】

なお、基本的な装置構成は、第1の実施形態において図1～図3を参照して説明したものとの同様であり、また、撮像素子の駆動タイミングは図4を参照して説明したものとの同様であるため、説明を省略する。

#### 【0045】

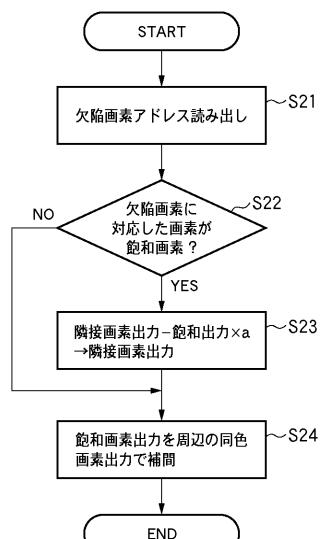

図6は、本発明の第2の実施形態における図1のデジタル信号処理部60で行われる欠陥画素信号の補正処理を示すフローチャートである。

#### 【0046】

先ず、ステップS21で、例えば特許文献1に記載されているようにして不図示のメモリに予め記憶してある欠陥画素のアドレスを読み出す。ただし、本第2の実施形態では、50

欠陥画素のアドレスが記憶してあれば良く、出力レベルは記憶しておく必要はない。次に、ステップ S 2 2 に進んで、読み出した欠陥画素のアドレスに対応するノイズ画像の画素のノイズ信号のレベルから、欠陥画素が飽和しているか否かを判断する。なお、ここでの判断は、図 5 のステップ S 1 1 において飽和画素を検出した時と同様の方法を利用することができる。

#### 【0047】

ステップ S 2 2 において欠陥画素が飽和画素でない場合は、隣接画素への飽和信号の漏れ込みがないと判断し、隣接画素への補正をせずステップ S 2 4 へ進む。ステップ S 2 2 で欠陥画素が飽和画素であると判断された場合、ステップ S 2 3 に進み、欠陥画素のノイズ信号レベルの所定の割合  $a$  の信号レベルを、光出力画像においてその欠陥画素に隣接する画素の光信号から減算する。所定の割合  $a$  は欠陥画素の暗電流が長時間蓄積により飽和し、飽和を超えたレベルのうち隣接画素に漏れ込む割合に相当する。欠陥画素が飽和画素である場合、隣接する画素の信号レベルとの差は大きいと推測される。この補正を行うことで、飽和画素に隣接する画素の本来の光信号を得ることができ、画質劣化を防ぐことができる。

#### 【0048】

次にステップ S 2 4 へ進み、光出力画像における欠陥画素の光信号を同色の周辺画素の光信号を用いて補間して、この処理を終了する。

#### 【0049】

また飽和信号の隣接画素への漏れ込み量を固定としているが、撮影環境に対応して変更しても良い。

#### 【0050】

##### <他の実施形態>

なお、本発明は、複数の機器（例えば撮像装置、インターフェイス機器、コンピュータなど）から構成されるシステムに適用しても、一つの機器からなる装置（例えば、撮像装置など）に適用してもよい。複数の機器により構成する場合、撮像装置のアナログフロンティエンド 5 6 から出力される光出力画像及びノイズ画像をそのまま外部コンピュータ 7 1 に出力し、外部コンピュータ 7 1 において図 5 又は図 6 の処理を行うようにすればよい。

#### 【0051】

また、本発明の目的は、以下の様にして達成することも可能である。まず、前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記憶媒体（または記録媒体）を、システムあるいは装置に供給する。そして、そのシステムあるいは装置のコンピュータ（または C P U や M P U ）が記憶媒体に格納されたプログラムコードを読み出し実行する。この場合、記憶媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記憶媒体は本発明を構成することになる。

#### 【0052】

また、コンピュータが読み出したプログラムコードを実行することにより、前述した実施形態の機能が実現されるだけでなく、以下のようにして達成することも可能である。即ち、読み出したプログラムコードの指示に基づき、コンピュータ上で稼働しているオペレーティングシステム（O S ）などが実際の処理の一部または全部を行い、その処理によって前述した実施形態の機能が実現される場合である。ここでプログラムコードを記憶する記憶媒体としては、例えば、フレキシブルディスク、ハードディスク、R O M 、R A M 、磁気テープ、不揮発性のメモリカード、C D - R O M 、C D - R 、D V D 、光ディスク、光磁気ディスク、M O などが考えられる。また、L A N （ローカル・エリア・ネットワーク）やW A N （ワイド・エリア・ネットワーク）などのコンピュータネットワークを、プログラムコードを供給するために用いることができる。

#### 【図面の簡単な説明】

#### 【0053】

【図 1】本発明の第 1 の実施形態における撮像装置の構成を示すブロック図である。

10

20

30

40

50

【図2】本発明の第1の実施形態における撮像素子の主に1画素分の構成を示す回路図である。

【図3】本発明の第1の実施形態における画素の断面及び各構成のポテンシャルの概念を示す図である。

【図4】本発明の第1の実施形態における撮像素子の駆動タイミング図である。

【図5】本発明の第1の実施形態における欠陥画素信号の補正処理を示すフローチャートである。

【図6】本発明の第2の実施形態における欠陥画素信号の補正処理を示すフローチャートである。

【図7】欠陥画素が飽和して電荷が周辺画素に漏れ込んだ場合の例を示した図である。 10

【符号の説明】

【0054】

- 1 フォトダイオード

- 2 転送スイッチ

- 3 フローディングディフュージョン部

- 4 リセットスイッチ

- 5 電源線

- 6 電界効果トランジスタ

- 7 選択スイッチ

- 8 垂直出力線

- 9 画素

- 11 定電流源

- 12、14 コンデンサ

- 13、15 スイッチ

- 16 読み出し線

- 55 撮像素子

- 65 タイミング発生部

- 59 A/D変換器

- 60 デジタル信号処理部

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

審査官 鈴木 肇

(56)参考文献 特開2002-281391(JP,A)

特開2006-229362(JP,A)

特開2006-197425(JP,A)

特開平08-075544(JP,A)

特開昭64-032773(JP,A)

特開2005-175682(JP,A)

特開2007-174124(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762