(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-243232

(P2006-243232A)

(43) 公開日 平成18年9月14日(2006.9.14)

| (51) Int.C1.                | F 1                                                  | テーマコード (参考) |

|-----------------------------|------------------------------------------------------|-------------|

| <b>G09G 3/36 (2006.01)</b>  | G09G 3/36                                            | 2 H 09 3    |

| <b>G02F 1/133 (2006.01)</b> | G02F 1/133 520                                       | 5 C 00 6    |

| <b>G09G 3/20 (2006.01)</b>  | G02F 1/133 550<br>G09G 3/20 612 F<br>G09G 3/20 621 L | 5 C 08 0    |

審査請求 有 請求項の数 13 O L (全 34 頁) 最終頁に続く

|           |                            |                                                        |

|-----------|----------------------------|--------------------------------------------------------|

| (21) 出願番号 | 特願2005-57198 (P2005-57198) | (71) 出願人 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日  | 平成17年3月2日 (2005.3.2)       | (74) 代理人 100090479<br>弁理士 井上 一                         |

|           |                            | (74) 代理人 100090387<br>弁理士 布施 行夫                        |

|           |                            | (74) 代理人 100090398<br>弁理士 大渕 美千栄                       |

|           |                            | (74) 代理人 100101649<br>弁理士 伊奈 達也                        |

|           |                            | (74) 代理人 100104710<br>弁理士 竹腰 昇                         |

最終頁に続く

(54) 【発明の名称】基準電圧発生回路、表示ドライバ、電気光学装置及び電子機器

## (57) 【要約】

【課題】 F R C 方式で高精度なガンマ補正を簡易に実現できる基準電圧発生回路、表示ドライバ、電気光学装置及び電子機器を提供する。

【解決手段】 基準電圧発生回路 54 は、複数の基準電圧を発生するためのガンマ補正データが設定される第 1 ~ 第 J (J は 2 以上の整数) のガンマ補正データレジスタ 220-1 ~ 220-J と、各ガンマ補正データレジスタに設定されたガンマ補正データに基づいて、各グループの第 1 ~ 第 L (L は 3 以上の整数) の選択用電圧の中から選択された第 1 ~ 第 K (K は L より小さい自然数) の基準電圧として出力する第 1 ~ 第 J の基準電圧選択回路 210-1 ~ 210-J を含み、F R C 方式が P (P は 2 以上の整数) フレームを 1 周期とする場合に、Q (2 Q P, Q は 整数) 種類の基準電圧選択回路の 1 つから出力される第 1 ~ 第 K の基準電圧を、フレーム単位に切り換えて出力する。

【選択図】 図 10

**【特許請求の範囲】****【請求項 1】**

電気光学装置をフレームレートコントロール方式で駆動する際に、ガンマ補正を行うための複数の基準電圧を発生する基準電圧発生回路であって、

前記複数の基準電圧を発生するためのガンマ補正データが設定される第 1 ~ 第 J ( J は 2 以上の整数 ) のガンマ補正データレジスタと、

第 h ( 1 ≤ h ≤ J, h は整数 ) の基準電圧選択回路が第 h のガンマ補正データレジスタに設定された前記ガンマ補正データに基づいて、電位の高い順又は電位の低い順に並ぶ第 h グループの第 1 ~ 第 L ( L は 3 以上の整数 ) の選択用電圧の中から選択された K 種類の選択用電圧を、電位の高い順又は電位の低い順に第 1 ~ 第 K ( K は J より小さい自然数 ) の基準電圧として出力するための第 1 ~ 第 J の基準電圧選択回路とを含み、

前記フレームレートコントロール方式が P ( P は 2 以上の整数 ) フレームを 1 周期とする場合に、前記第 1 ~ 第 J の基準電圧選択回路のうち Q ( 2 ≤ Q ≤ P, Q は整数 ) 種類の基準電圧選択回路の 1 つから出力される第 1 ~ 第 K の基準電圧を、フレーム単位に切り換えて前記複数の基準電圧として出力することを特徴とする基準電圧発生回路。

**【請求項 2】**

請求項 1 において、

1 フレーム毎に更新されるカウント値に基づいて、前記 Q 種類の基準電圧選択回路の中から選択された基準電圧選択回路からの第 1 ~ 第 K の基準電圧を前記複数の基準電圧として出力することを特徴とする基準電圧発生回路。

**【請求項 3】**

請求項 1 又は 2 において、

シリアルに入力された前記ガンマ補正データを所与のビット数のパラレルデータに変換するシリアル / パラレル変換回路と、

前記パラレルデータの各ビットの信号レベルを変換するレベルシフタとを含み、

前記第 1 ~ 第 J のガンマ補正データレジスタには、前記ビット数単位に、前記レベルシフタによって信号レベルが変換された前記パラレルデータが設定されることを特徴とする基準電圧発生回路。

**【請求項 4】**

請求項 1 乃至 3 のいずれかにおいて、

前記第 1 ~ 第 L の選択用電圧が、第 1 ~ 第 J グループの各グループで共通であることを特徴とする基準電圧発生回路。

**【請求項 5】**

請求項 1 乃至 4 のいずれかにおいて、

前記第 1 ~ 第 J のガンマ補正データレジスタのいずれに前記ガンマ補正データを設定するかを指定するためのデータ設定レジスタを含み、

前記第 1 ~ 第 J のガンマ補正データレジスタのうち前記データ設定レジスタの設定値に対応したガンマ補正データレジスタに、前記レベルシフタによって信号レベルが変換された前記ガンマ補正データを設定することを特徴とする基準電圧発生回路。

**【請求項 6】**

請求項 1 乃至 5 のいずれかにおいて、

前記ガンマ補正データは、

各ビットのデータが各選択用電圧に対応付けられ基準電圧として出力するか否かを示す L ビットのデータであることを特徴とする基準電圧発生回路。

**【請求項 7】**

請求項 1 乃至 6 のいずれかにおいて、

前記基準電圧選択回路が、

第 1 の選択用電圧を前記第 1 の基準電圧として出力するための第 1 のスイッチ素子と、第 2 の選択用電圧を前記第 1 の基準電圧として出力するための第 2 のスイッチ素子と、第 2 の選択用電圧を前記第 2 の基準電圧として出力するための第 3 のスイッチ素子と、

10

20

30

40

50

第3の選択用電圧を前記第2の基準電圧として出力するための第4のスイッチ素子とを含み、

前記第1のスイッチ素子が、

前記ガンマ補正データの第1のビットのデータによりイネーブルに設定されたことを条件に、前記第1の選択用電圧を前記第1の基準電圧として出力し、

前記第2のスイッチ素子が、

前記ガンマ補正データの第1のビットのデータによりディセーブルに設定され、且つ前記ガンマ補正データの第2のビットのデータによりイネーブルに設定されたことを条件に、前記第2の選択用電圧を前記第1の基準電圧として出力し、

前記第3のスイッチ素子が、

前記ガンマ補正データの第1のビットのデータによりイネーブルに設定され、且つ前記ガンマ補正データの第2のビットのデータによりイネーブルに設定されたことを条件に、前記第2の選択用電圧を前記第2の基準電圧として出力し、

前記第4のスイッチ素子が、

前記ガンマ補正データの第1のビットのデータによりイネーブルに設定され、且つ前記ガンマ補正データの第2のビットのデータによりディセーブルに設定され、且つ前記ガンマ補正データの第3のビットのデータによりイネーブルに設定されたことを条件に、前記第3の選択用電圧を前記第2の基準電圧として出力し、

前記基準電圧選択回路が、

前記第1～第Kの基準電圧のうち少なくとも前記第1及び第2の基準電圧を出力することを特徴とする基準電圧発生回路。

#### 【請求項8】

請求項7において、

各スイッチセルが、第1～第4のスイッチ素子の各スイッチ素子を有する第1～第4のスイッチセルを含み、

前記第1のスイッチセルが、

前記ガンマ補正データの第1のビットのデータによりイネーブルに設定されたとき、前記第2のスイッチセルへのディセーブル信号をアクティブにすると共に、前記第3のスイッチセルへのイネーブル信号をアクティブにし、

前記ガンマ補正データの第1のビットのデータによりディセーブルに設定されたとき、前記第2のスイッチセルへのディセーブル信号を非アクティブにすると共に、前記第3のスイッチセルへのイネーブル信号を非アクティブにし、

前記第2のスイッチセルが、

前記ガンマ補正データの第2のビットのデータによりイネーブルに設定され、且つ前記第1のスイッチセルからのディセーブル信号が非アクティブであることを条件に前記第2の選択用電圧を前記第1の基準電圧として出力すると共に、前記第4のスイッチセルへのイネーブル信号をアクティブにし、

それ以外のときには、前記第4のスイッチセルへのイネーブル信号を非アクティブにし、

前記第3のスイッチセルが、

前記ガンマ補正データの第2のビットのデータによりイネーブルに設定され、且つ前記第1のスイッチセルからのイネーブル信号がアクティブであることを条件に前記第2の選択用電圧を前記第2の基準電圧として出力すると共に、前記第4のスイッチセルへのディセーブル信号をアクティブにし、

それ以外のときには、前記第4のスイッチセルへのディセーブル信号を非アクティブにし、

前記第4のスイッチセルが、

前記ガンマ補正データの第3のビットのデータによりイネーブルに設定され、且つ前記第3のスイッチセルからのディセーブル信号が非アクティブであり、且つ前記第2のスイッチセルからのイネーブル信号がアクティブであることを条件に前記第3の選択用電圧を

10

20

30

40

50

前記第2の基準電圧として出力することを特徴とする基準電圧発生回路。

【請求項9】

請求項1乃至6のいずれかにおいて、

前記基準電圧選択回路が、

前記第1の選択用電圧を前記第1の基準電圧として出力するための第1のスイッチ素子

を有する第1のスイッチセルと、

前記第2の選択用電圧を前記第1の基準電圧として出力するための第2のスイッチ素子

を有する第2のスイッチセルと、

前記第2の選択用電圧を前記第2の基準電圧として出力するための第3のスイッチ素子

を有する第3のスイッチセルと、

前記第3の選択用電圧を前記第2の基準電圧として出力するための第4のスイッチ素子

を有する第4のスイッチセルとを含み、

前記第1のスイッチセルは、

前記ガンマ補正データの第1のビットのデータが供給されると共に、前記第2及び第3

のスイッチセルに対してイネーブル信号を出力し、

前記第2のスイッチセルは、

前記ガンマ補正データの第2のビットのデータが供給されると共に、前記第3及び第4

のスイッチセルに対してイネーブル信号を出力し、

前記第3のスイッチセルは、

前記ガンマ補正データの第2のビットのデータが供給されると共に、前記第4のスイッ

チセルに対してイネーブル信号を出力し、

前記第4のスイッチセルは、

前記ガンマ補正データの第3のビットのデータが供給され、

前記基準電圧選択回路が、

前記第1～第Kの基準電圧のうち少なくとも前記第1及び第2の基準電圧を出力するこ

とを特徴とする基準電圧発生回路。

【請求項10】

フレームレートコントロール方式により電気光学装置の複数のデータ線を駆動するため

の表示ドライバであって、

請求項1乃至9のいずれか記載の基準電圧発生回路と、

前記基準電圧発生回路からの前記第1～第Kの基準電圧の中から、階調データに対応し

た基準電圧を選択し、データ電圧として出力する電圧選択回路と、

前記データ電圧に基づいて前記データ線を駆動する駆動回路とを含むことを特徴とする

表示ドライバ。

【請求項11】

複数の走査線と、

複数のデータ線と、

前記複数の走査線の1つと前記複数のデータ線の1つとにより特定される画素電極と、

前記複数の走査線を走査する走査ドライバと、

前記複数のデータ線を駆動する請求項10記載の表示ドライバとを含むことを特徴とす

る電気光学装置。

【請求項12】

請求項10記載の表示ドライバを含むことを特徴とする電子機器。

【請求項13】

請求項11記載の電気光学装置を含むことを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基準電圧発生回路、表示ドライバ、電気光学装置及び電子機器に関する。

【背景技術】

**【 0 0 0 2 】**

液晶表示 (Liquid Crystal Display : LCD) パネルに代表される電気光学装置は、携帯型の電子機器に搭載されることが多くなる一方で、多階調化による色調豊富な画像表示が要求される。

**【 0 0 0 3 】**

一般に、画像表示を行うための映像信号は、表示装置の表示特性に応じてガンマ補正が行われる。電気光学装置を例にとれば、複数の基準電圧の中から、階調値を定める階調データに対応した基準電圧が選択され、この選択された基準電圧に基づいて画素の透過率を変化させる。そのため、ガンマ補正是、各基準電圧の電圧レベルを変化させることで実現される。

10

**【 0 0 0 4 】**

このような各基準電圧は、特許文献 1 ~ 特許文献 4 に開示されているように、ラダー抵抗回路の両端の電圧を、該ラダー抵抗回路を構成する複数の抵抗素子により分割された電圧として生成される。従って、各抵抗素子の抵抗値を変更することで各基準電圧の電圧レベルを変化させることができる。

【特許文献 1】特開 2003 - 23354 号公報

【特許文献 2】特開 2003 - 23355 号公報

【特許文献 3】特開 2003 - 23356 号公報

【特許文献 4】特開 2003 - 23357 号公報

**【発明の開示】**

20

**【発明が解決しようとする課題】****【 0 0 0 5 】**

しかしながら、LCDパネルの高精細化及び多様化によって、より高精度なガンマ補正が要求される場合がある。この場合、ラダー抵抗回路を構成する複数の抵抗素子の各抵抗素子の抵抗値を変化させるだけでは、高精度に基準電圧を発生させることが難しい。特に、LCDパネルの種類が変わった場合に、簡素な構成で、LCDパネルに応じた高精度な基準電圧を発生させることが困難である。そのため、複数種類のガンマ補正を実現させるための制御及び構成が複雑になるという問題がある。

**【 0 0 0 6 】**

また階調表示のための駆動方式としてフレームレートコントロール (Frame Rate Control : FRC) 方式が採用される場合においても、より高精細な階調表示が要求されている。

30

**【 0 0 0 7 】**

更に、ガンマ補正を制御するためのガンマ補正データを基準電圧発生回路に設定することが考えられる。例えば、階調レベル数の増加に伴いガンマ補正データのビット数が多くなると、ガンマ補正データの設定に時間を要するようになったり、ガンマ補正データの設定に伴う電力消費が多くなったりする。このためガンマ補正データのビット数が増加した場合であっても、低消費電力でガンマ補正データを設定できることが望ましい。

**【 0 0 0 8 】**

本発明は、以上のような技術的課題に鑑みてなされたものであり、その第 1 の目的とするところは、フレームレートコントロール方式で高精度なガンマ補正を簡易に実現できる基準電圧発生回路、表示ドライバ、電気光学装置及び電子機器を提供することにある。

40

**【 0 0 0 9 】**

また本発明の第 2 の目的は、簡素な構成で、高精度なガンマ補正を実現させるための基準電圧発生回路、表示ドライバ、電気光学装置及び電子機器を提供することにある。

**【課題を解決するための手段】****【 0 0 1 0 】**

上記課題を解決するために本発明は、

電気光学装置をフレームレートコントロール方式で駆動する際に、ガンマ補正を行うための複数の基準電圧を発生する基準電圧発生回路であって、

50

前記複数の基準電圧を発生するためのガンマ補正データが設定される第1～第J（Jは2以上の整数）のガンマ補正データレジスタと、

第h（1～J、hは整数）の基準電圧選択回路が第hのガンマ補正データレジスタに設定された前記ガンマ補正データに基づいて、電位の高い順又は電位の低い順に並ぶ第hグループの第1～第L（Lは3以上の整数）の選択用電圧の中から選択されたK種類の選択用電圧を、電位の高い順又は電位の低い順に第1～第K（KはLより小さい自然数）の基準電圧として出力するための第1～第Jの基準電圧選択回路とを含み、

前記フレームレートコントロール方式がP（Pは2以上の整数）フレームを1周期とする場合に、前記第1～第Jの基準電圧選択回路のうちQ（2～P、Qは整数）種類の基準電圧選択回路の1つから出力される第1～第Kの基準電圧を、フレーム単位に切り換えて前記複数の基準電圧として出力する基準電圧発生回路に係る。

#### 【0011】

また本発明に係る基準電圧発生回路では、

1フレーム毎に更新されるカウント値に基づいて、前記Q種類の基準電圧選択回路の中から選択された基準電圧選択回路からの第1～第Kの基準電圧を前記複数の基準電圧として出力することができる。

#### 【0012】

上記のいずれかの発明によれば、階調表示のための駆動方式としてFRC方式が採用される場合においても、フレーム単位に各基準電圧の電圧レベルを変化させることができるので、FRC方式において、より高精細な階調表示を実現させることができるようになる。

#### 【0013】

また本発明に係る基準電圧発生回路では、

シリアルに入力された前記ガンマ補正データを所与のビット数のパラレルデータに変換するシリアル／パラレル変換回路と、

前記パラレルデータの各ビットの信号レベルを変換するレベルシフタとを含み、

前記第1～第Jのガンマ補正データレジスタには、前記ビット数単位に、前記レベルシフタによって信号レベルが変換された前記パラレルデータが設定されてもよい。

#### 【0014】

本発明によれば、シリアルに入力されるガンマ補正データをパラレルに変換後、ガンマ補正データに設定できるようになる。そのため、ガンマ補正データのビット数分のクロックを発生させて、ガンマ補正データレジスタに高速に書き込み制御を行うことなく、より少ないクロック数だけクロックを発生させてガンマ補正データレジスタに低速に書き込み制御を行うことができるようになる。そのため、ガンマ補正データの設定に伴う電力消費を大幅に削減できるようになる。

#### 【0015】

しかもレベルシフタでは、パラレルデータのビット数分の信号レベルを変換すればよいため、回路規模の増大を抑えることができる。

#### 【0016】

また本発明に係る基準電圧発生回路では、

前記第1～第Lの選択用電圧が、第1～第Jグループの各グループで共通であってよい。

#### 【0017】

本発明によれば、複数の選択用電圧を共通に生成するようにすることで、第1～第Jの基準電圧選択回路の各基準電圧選択回路が、それぞれ選択用電圧を発生させる必要がなくなるので、基準電圧発生回路の回路規模を削減できるようになる。

#### 【0018】

また本発明に係る基準電圧発生回路では、

前記第1～第Jのガンマ補正データレジスタのいずれに前記ガンマ補正データを設定するかを指定するためのデータ設定レジスタを含み、

10

20

30

40

50

前記第1～第Jのガンマ補正データレジスタのうち前記データ設定レジスタの設定値に対応したガンマ補正データレジスタに、前記レベルシフタによって信号レベルが変換された前記ガンマ補正データを設定することができる。

#### 【0019】

本発明によれば、簡素な構成で複数のガンマ補正データレジスタにガンマ補正データを設定し、或いは複数種類の第1～第Kの基準電圧を出力させることができるようになる。

#### 【0020】

また本発明に係る基準電圧発生回路では、

前記ガンマ補正データは、

各ビットのデータが各選択用電圧に対応付けられ基準電圧として出力するか否かを示す

10

Lビットのデータであってもよい。

#### 【0021】

また本発明に係る基準電圧発生回路では、

前記基準電圧選択回路が、

第1の選択用電圧を前記第1の基準電圧として出力するための第1のスイッチ素子と、

第2の選択用電圧を前記第1の基準電圧として出力するための第2のスイッチ素子と、

第2の選択用電圧を前記第2の基準電圧として出力するための第3のスイッチ素子と、

第3の選択用電圧を前記第2の基準電圧として出力するための第4のスイッチ素子とを

含み、

前記第1のスイッチ素子が、

前記ガンマ補正データの第1のビットのデータによりイネーブルに設定されたことを条件に、前記第1の選択用電圧を前記第1の基準電圧として出力し、

前記第2のスイッチ素子が、

前記ガンマ補正データの第1のビットのデータによりディセーブルに設定され、且つ前記

記ガンマ補正データの第2のビットのデータによりイネーブルに設定されたことを条件に、

前記第2の選択用電圧を前記第1の基準電圧として出力し、

前記第3のスイッチ素子が、

前記ガンマ補正データの第1のビットのデータによりイネーブルに設定され、且つ前記

記ガンマ補正データの第2のビットのデータによりイネーブルに設定されたことを条件に、前記

第2の選択用電圧を前記第2の基準電圧として出力し、

前記第4のスイッチ素子が、

前記ガンマ補正データの第1のビットのデータによりイネーブルに設定され、且つ前記

記ガンマ補正データの第2のビットのデータによりディセーブルに設定され、且つ前記

記ガンマ補正データの第3のビットのデータによりイネーブルに設定されたことを条件に、前記

第3の選択用電圧を前記第2の基準電圧として出力し、

前記基準電圧選択回路が、

前記第1～第Kの基準電圧のうち少なくとも前記第1及び第2の基準電圧を出力するこ

とができる。

#### 【0022】

また本発明に係る基準電圧発生回路では、

各スイッチセルが、第1～第4のスイッチ素子の各スイッチ素子を有する第1～第4の

スイッチセルを含み、

前記第1のスイッチセルが、

前記ガンマ補正データの第1のビットのデータによりイネーブルに設定されたとき、前

記第2のスイッチセルへのディセーブル信号をアクティブにすると共に、前記第3のスイ

ッチセルへのイネーブル信号をアクティブにし、

前記ガンマ補正データの第1のビットのデータによりディセーブルに設定されたとき、

前記第2のスイッチセルへのディセーブル信号を非アクティブにすると共に、前記第3のスイ

ッチセルへのイネーブル信号を非アクティブにし、

前記第2のスイッチセルが、

10

20

30

40

50

前記ガンマ補正データの第2のビットのデータによりイネーブルに設定され、且つ前記第1のスイッチセルからのディセーブル信号が非アクティブであることを条件に前記第2の選択用電圧を前記第1の基準電圧として出力すると共に、前記第4のスイッチセルへのイネーブル信号をアクティブにし、

それ以外のときには、前記第4のスイッチセルへのイネーブル信号を非アクティブにし、

前記第3のスイッチセルが、

前記ガンマ補正データの第2のビットのデータによりイネーブルに設定され、且つ前記第1のスイッチセルからのイネーブル信号がアクティブであることを条件に前記第2の選択用電圧を前記第2の基準電圧として出力すると共に、前記第4のスイッチセルへのディセーブル信号をアクティブにし、

10

それ以外のときには、前記第4のスイッチセルへのディセーブル信号を非アクティブにし、

前記第4のスイッチセルが、

前記ガンマ補正データの第3のビットのデータによりイネーブルに設定され、且つ前記第3のスイッチセルからのディセーブル信号が非アクティブであり、且つ前記第2のスイッチセルからのイネーブル信号がアクティブであることを条件に前記第3の選択用電圧を前記第2の基準電圧として出力することができる。

#### 【0023】

また本発明に係る基準電圧発生回路では、

20

前記基準電圧選択回路が、

前記第1の選択用電圧を前記第1の基準電圧として出力するための第1のスイッチ素子を有する第1のスイッチセルと、

前記第2の選択用電圧を前記第1の基準電圧として出力するための第2のスイッチ素子を有する第2のスイッチセルと、

前記第2の選択用電圧を前記第2の基準電圧として出力するための第3のスイッチ素子を有する第3のスイッチセルと、

前記第3の選択用電圧を前記第2の基準電圧として出力するための第4のスイッチ素子を有する第4のスイッチセルとを含み、

前記第1のスイッチセルは、

30

前記ガンマ補正データの第1のビットのデータが供給されると共に、前記第2及び第3のスイッチセルに対してイネーブル信号を出力し、

前記第2のスイッチセルは、

前記ガンマ補正データの第2のビットのデータが供給されると共に、前記第3及び第4のスイッチセルに対してイネーブル信号を出力し、

前記第3のスイッチセルは、

前記ガンマ補正データの第2のビットのデータが供給されると共に、前記第4のスイッチセルに対してイネーブル信号を出力し、

前記第4のスイッチセルは、

40

前記ガンマ補正データの第3のビットのデータが供給され、

前記基準電圧選択回路が、

前記第1～第Kの基準電圧のうち少なくとも前記第1及び第2の基準電圧を出力することができる。

#### 【0024】

これらのいずれかの発明によれば、上記の効果に加えて、第1～第4のスイッチ素子を少なくとも含み、第1の選択用電圧を第2の基準電圧として出力するためのスイッチ素子を不要にできるようになる。更に、第1及び第2の基準電圧のみを出力する場合には、第3の選択用電圧を第1の基準電圧として出力するためのスイッチ素子についても不要にできるようになる。従って、高精度なガンマ補正を実現するための基準電圧を、簡素な構成で選択できる基準電圧選択回路を提供できるようになる。

50

## 【0025】

また本発明は、

フレームレートコントロール方式により電気光学装置の複数のデータ線を駆動するための表示ドライバであって、

上記のいずれか記載の基準電圧発生回路と、

前記基準電圧発生回路からの前記第1～第Kの基準電圧の中から、階調データに対応した基準電圧を選択し、データ電圧として出力する電圧選択回路と、

前記データ電圧に基づいて前記データ線を駆動する駆動回路とを含む表示ドライバに関係する。

## 【0026】

本発明によれば、FRC方式で高精度なガンマ補正を簡易に実現できる基準電圧発生回路を含む表示ドライバを提供できる。

## 【0027】

また本発明は、

複数の走査線と、

複数のデータ線と、

前記複数の走査線の1つと前記複数のデータ線の1つとにより特定される画素電極と、前記複数の走査線を走査する走査ドライバと、

前記複数のデータ線を駆動する上記記載の表示ドライバとを含む電気光学装置に関する。

10

20

20

## 【0028】

本発明によれば、FRC方式で高精度なガンマ補正を簡易に実現できる電気光学装置を提供できる。

## 【0029】

また本発明は、上記記載の表示ドライバを含む電子機器に関する。

## 【0030】

また本発明は、上記記載の電気光学装置を含む電子機器に関する。

## 【0031】

これらのいずれかの発明によれば、FRC方式で高精度なガンマ補正を簡易に実現できる基準電圧発生回路を含む電子機器を提供できる。

30

## 【発明を実施するための最良の形態】

## 【0032】

以下、本発明の実施の形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成のすべてが本発明の必須構成要件であるとは限らない。

## 【0033】

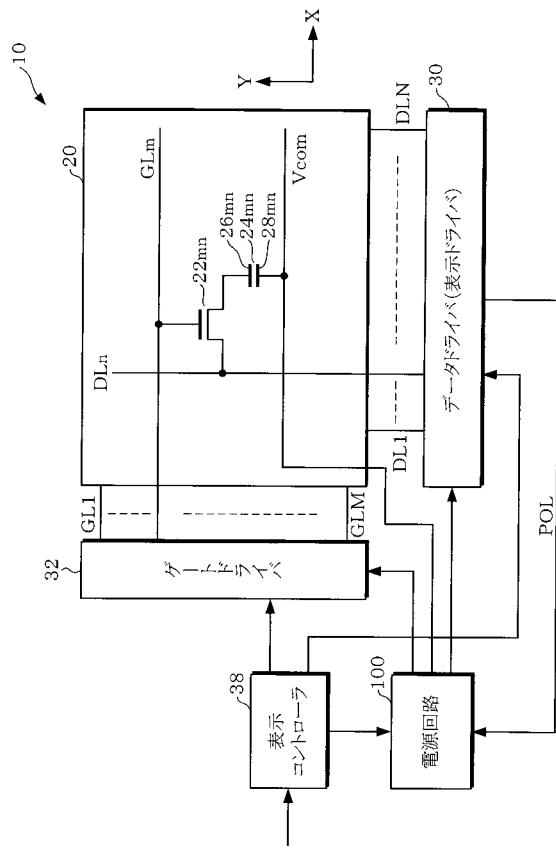

## 1. 液晶表示装置

図1に、本実施形態におけるアクティブマトリックス型の液晶表示装置の構成の概要を示す。ここでは、アクティブマトリックス型の液晶表示装置について説明するが、単純マトリックス型の液晶表示装置についても、本実施形態における基準電圧選択回路を含むデータドライバ(表示ドライバ)を適用できる。

40

## 【0034】

液晶表示装置10は、LCDパネル(広義には表示パネル、更に広義には電気光学装置)20を含む。LCDパネル20は、例えばガラス基板上に形成される。このガラス基板上には、Y方向に複数配列されそれぞれX方向に伸びる走査線(ゲートライン)GL1～GLM(Mは2以上の整数)と、X方向に複数配列されそれぞれY方向に伸びるデータ線(ソースライン)DL1～DLN(Nは2以上の整数)とが配置されている。また、走査線GLm(1≤m≤M、mは整数、以下同様。)とデータ線DLn(1≤n≤N、nは整数、以下同様。)との交差位置に対応して、画素領域(画素)が設けられ、該画素領域に薄膜トランジスタ(Thin Film Transistor:以下、TFTと略す。)22mnが配置され

50

ている。

【0035】

TFT22mnのゲートは、走査線GLnに接続されている。TFT22mnのソースは、データ線DLnに接続されている。TFT22mnのドレインは、画素電極26mnに接続されている。画素電極26mnと、これに対向する対向電極28mnとの間に液晶が封入され、液晶容量（広義には液晶素子）24mnが形成される。画素電極26mnと対向電極28mnとの間の印加電圧に応じて画素の透過率が変化するようになっている。対向電極28mnには、対向電極電圧Vcomが供給される。

【0036】

このようなLCDパネル20は、例えば画素電極及びTFTが形成された第1の基板と、対向電極が形成された第2の基板とを貼り合わせ、両基板の間に電気光学材料としての液晶を封入させることで形成される。

【0037】

液晶表示装置10は、データドライバ（広義には表示ドライバ）30を含む。データドライバ30は、階調データに基づいて、LCDパネル20のデータ線DL1～DLNを駆動する。

【0038】

液晶表示装置10は、ゲートドライバ（広義には走査ドライバ）32を含むことができる。ゲートドライバ32は、一垂直走査期間内に、LCDパネル20の走査線GL1～GLMを走査する。

【0039】

液晶表示装置10は、電源回路100を含むことができる。電源回路100は、データ線の駆動に必要な電圧を生成し、これらをデータドライバ30に対して供給する。電源回路100は、例えばデータドライバ30のデータ線の駆動に必要な電源電圧VDDH、VSSHや、データドライバ30のロジック部の電圧を生成する。

【0040】

また電源回路100は、走査線の走査に必要な電圧を生成し、これをゲートドライバ32に対して供給する。

【0041】

更に電源回路100は、対向電極電圧Vcomを生成する。電源回路100は、データドライバ30によって生成された極性反転信号POLのタイミングに合わせて、高電位側電圧VCOMHと低電位側電圧VCOMLとを周期的に繰り返す対向電極電圧Vcomを、LCDパネル20の対向電極に出力する。

【0042】

液晶表示装置10は、表示コントローラ38を含むことができる。表示コントローラ38は、図示しない中央処理装置（Central Processing Unit：以下、CPUと略す。）等のホストにより設定された内容に従って、データドライバ30、ゲートドライバ32、電源回路100を制御する。例えば、表示コントローラ38は、データドライバ30及びゲートドライバ32に対し、動作モードの設定、内部で生成した垂直同期信号や水平同期信号の供給を行う。本実施形態では、ガンマ補正データが、データドライバ30の外部に設けられた不揮発性メモリから初期化処理において読み込まれるようになっているが、表示コントローラ38が、データドライバ30に対してガンマ補正データを供給し、種々のガンマ補正を実現できるようにしてもよい。

【0043】

なお図1では、液晶表示装置10に電源回路100又は表示コントローラ38を含めて構成するようにしているが、これらのうち少なくとも1つを液晶表示装置10の外部に設けて構成するようにしてもよい。或いは、液晶表示装置10に、ホストを含めるように構成することも可能である。

【0044】

また、データドライバ30は、ゲートドライバ32及び電源回路100のうち少なくと

10

20

30

40

50

も1つを内蔵してもよい。

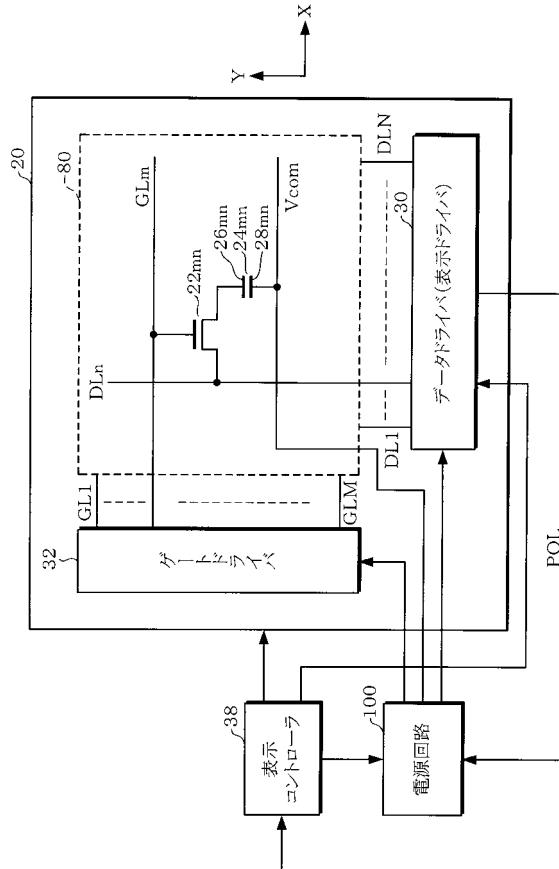

【0045】

更にまた、データドライバ30、ゲートドライバ32、表示コントローラ38及び電源回路100の一部又は全部をLCDパネル20上に形成してもよい。例えば図2では、LCDパネル20上に、データドライバ30及びゲートドライバ32が形成されている。このようにLCDパネル20は、複数のデータ線と、複数の走査線と、複数の走査線の各走査線及び複数のデータ線の各データ線とに接続された複数のスイッチ素子と、複数のデータ線を駆動する表示ドライバとを含むように構成することができる。LCDパネル20の画素形成領域80に、複数の画素が形成されている。

【0046】

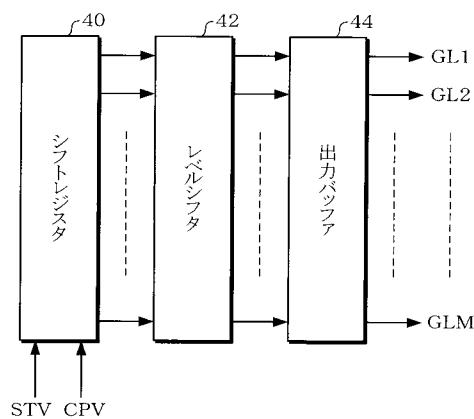

2. ゲートドライバ

図3に、図1のゲートドライバ32の構成例を示す。

【0047】

ゲートドライバ32は、シフトレジスタ40、レベルシフタ42、出力バッファ44を含む。

【0048】

シフトレジスタ40は、各走査線に対応して設けられ、順次接続された複数のフリップフロップを含む。このシフトレジスタ40は、クロック信号CPVに同期してスタートパルス信号STVをフリップフロップに保持すると、順次クロック信号CPVに同期して隣接するフリップフロップにスタートパルス信号STVをシフトする。ここで入力されるクロック信号CPVは水平同期信号であり、スタートパルス信号STVは垂直同期信号である。

【0049】

レベルシフタ42は、シフトレジスタ40からの電圧のレベルを、LCDパネル20の液晶素子と TFT のトランジスタ能力とに応じた電圧のレベルにシフトする。この電圧レベルとしては、例えば20V~50Vの高い電圧レベルが必要になる。

【0050】

出力バッファ44は、レベルシフタ42によってシフトされた走査電圧をバッファリングして走査線に出力し、走査線を駆動する。

【0051】

3. データドライバ

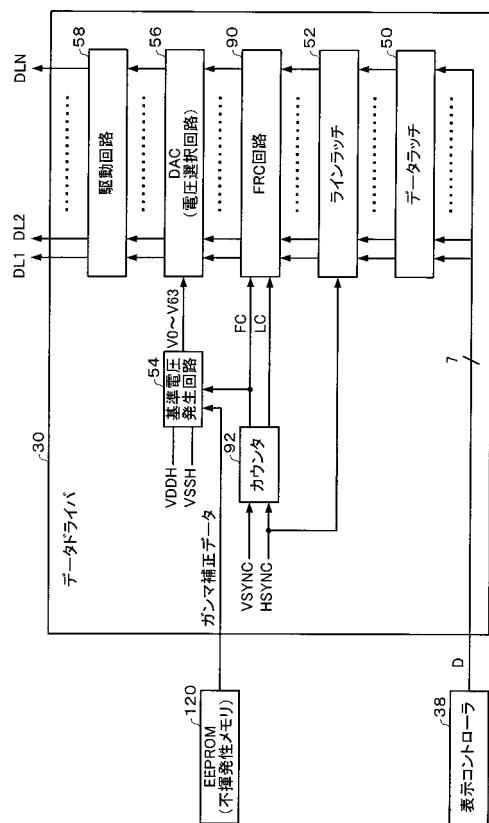

図4に、図1のデータドライバ30の構成例のブロック図を示す。図4では、1ドット当たりの階調データのビット数が7であるものとして説明するが、本発明が階調データのビット数に限定されるものではない。また図4のデータドライバでは、説明の簡略化のために2フレームを1周期とするFRС方式で駆動するものとするが、FRС方式の1周期のフレーム数に限定されるものではない。

【0052】

データドライバ30は、データラッチ50、ラインラッチ52、基準電圧発生回路54、DAC(Digital/Analog Converter)(広義には、電圧選択回路)56、駆動回路58を含む。またデータドライバ30は、フレームレートコントロール方式で駆動するためにFRС回路90、カウンタ92を含む。

【0053】

データドライバ30には、画素単位(又は1ドット単位)でシリアルに階調データが入力される。この階調データは、ドットクロック信号DCLKに同期して入力される。ドットクロック信号DCLKは、表示コントローラ38から供給される。図4では、説明の簡略化のため、1ドット単位で階調データが入力されるものとする。

【0054】

データラッチ50は、ドットクロック信号DCLKに同期して、取り込み開始信号をシフトし、そのシフト出力に同期して、階調データをラッチすることで、例えば一水平走査分の階調データを取り込む。

10

20

30

40

50

## 【0055】

ラインラッチ52は、データラッチ50にラッチされた一水平走査分の階調データを、水平同期信号H Syncの変化タイミングでラッチする。

## 【0056】

カウンタ92は、水平同期信号H Syncのパルスがアクティブになる毎にその値が更新されるカウント値LCを出力する。またカウンタ92は、水平同期信号V Syncのパルスがアクティブになる毎にその値が更新されるカウント値FC(1フレーム毎に更新されるカウント値)を出力する。カウント値FCは、基準電圧発生回路54に供給される。またカウント値FCの最下位ビット(Least Significant Bit: LSB)のデータは、FRC回路90に供給される。更にカウント値LCのLSBのデータは、FRC回路90に供給される。10

## 【0057】

FRC回路90は、フレームレートコントロール方式を実現するために、ラインラッチ52から各ドットが7ビットの階調データを6ビットの階調データに変換する。変換後の6ビットの階調データは、カウント値FCのLSB及びカウント値LCのLSBに基づいて生成され、2フレームを1周期として中間調の階調表示が実現される。

## 【0058】

基準電圧発生回路54は、各基準電圧が各階調データに対応する複数の基準電圧を生成する。より具体的には、基準電圧発生回路54は、電位の高い順又は電位の低い順に並ぶ第1～第K(Kは2以上の整数)の基準電圧を発生させる。この場合に、基準電圧発生回路54は、電位の高い順又は電位の低い順に並ぶ第1～第L(LはKより大きい整数)の選択用電圧を一旦生成し、Lビットのガンマ補正データに基づいて第1～第Lの選択用電圧の中から選択されたK種類の選択用電圧を、電位の高い順又は電位の低い順に第1～第Kの基準電圧として出力する。ここで、ガンマ補正データの各ビットのデータが、各選択用電圧に対応しており、各選択用電圧を各基準電圧として出力するか否かを示す。20

## 【0059】

更に本実施形態では、フレームレートコントロール方式がP(Pは2以上の整数、図4ではPが2)フレームを1周期とする場合に、基準電圧発生回路54が、第1～第J(Jは2以上の整数)の基準電圧選択回路のうちQ(2≤Q≤P、Qは整数)種類の基準電圧選択回路の1つから出力される第1～第Kの基準電圧を、フレーム単位に切り換えて複数の基準電圧として出力できる。30

## 【0060】

以下では、Lが256、Kが64であるものとして説明する。この場合、基準電圧発生回路54は、高電位側電源電圧VD DHと低電位側電源電圧VSSHとに基づいて、各基準電圧が6ビットの各階調データに対応する複数の基準電圧V0～V63を生成する。

## 【0061】

DAC56は、FRC回路90から出力される変換後の階調データに対応したデータ電圧を、出力線ごとに生成する。より具体的には、DAC56は、基準電圧発生回路54によって生成された複数の基準電圧V0～V63の中から、FRC回路90から出力された1出力線分の階調データに対応した基準電圧を選択し、選択した基準電圧をデータ電圧として出力する。40

## 【0062】

駆動回路58は、各出力線がLCDパネル20の各データ線に接続される複数の出力線を駆動する。より具体的には、駆動回路58は、DAC56によって出力線毎に生成されたデータ電圧に基づいて、各出力線を駆動する。即ち、駆動回路58は、階調データに基づいて選択された基準電圧をデータ電圧として、該データ電圧に基づいてデータ線を駆動する。駆動回路58は、出力線毎に設けられたボルテージフォロワ接続された演算増幅器を有し、該演算増幅器がDAC56からのデータ電圧に基づいて各出力線を駆動する。

## 【0063】

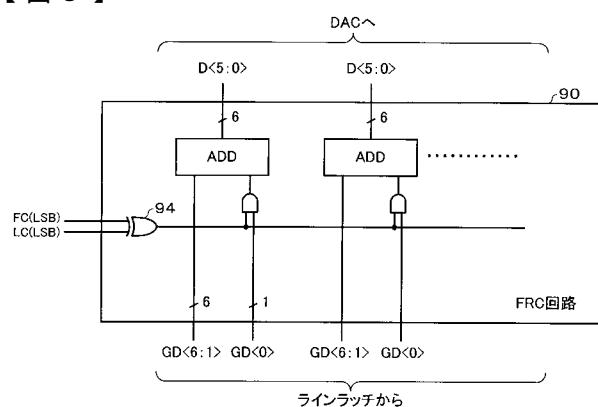

図5に、図4のFRC回路90の構成の概要を示す。

50

## 【0064】

FRC回路90には、ラインラッチ52から、出力線毎に7ビットの階調データGD<6:0>が入力される。そして階調データの上位6ビットであるGD<6:1>が加算器ADDにそのまま入力される。

## 【0065】

またFRC回路90は、排他的論理和回路94を含み、排他的論理和回路94が、カウント値FCのLSBとカウント値LCのLSBの排他的論理和演算結果を出力する。そしてこの排他的論理和演算結果と階調データのLSBであるGD<0>との論理積演算結果が加算器ADDに入力される。

## 【0066】

即ち、加算器ADDは、階調データの上位6ビットのGD<6:1>と1ビットの論理積演算結果とを加算して、変換後の6ビットの階調データD<5:0>として出力する。

## 【0067】

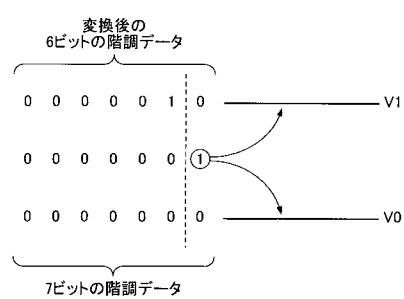

図6に、図5のFRC回路90が出力する6ビットの階調データの説明図を示す。

## 【0068】

上述のようにFRC回路90には、7ビットの階調データが入力される。そして、変換後の6ビットの階調データに変換する際に、階調データの上位6ビットのGD<6:1>と1ビットの論理積演算結果との加算結果を用いる。

## 【0069】

例えば7ビットの階調データ「0000000」に対応した基準電圧をV0、「0000010」に対応した基準電圧をV1とした場合に、7ビットの階調データ「00000001」に対応した中間調を表現するために、基準電圧V0、V1を所定の頻度で用いればよい。そこで本実施形態では、上記の加算結果を用いることで7ビットの階調データ「0000001」に対応した中間調表示を実現する。

## 【0070】

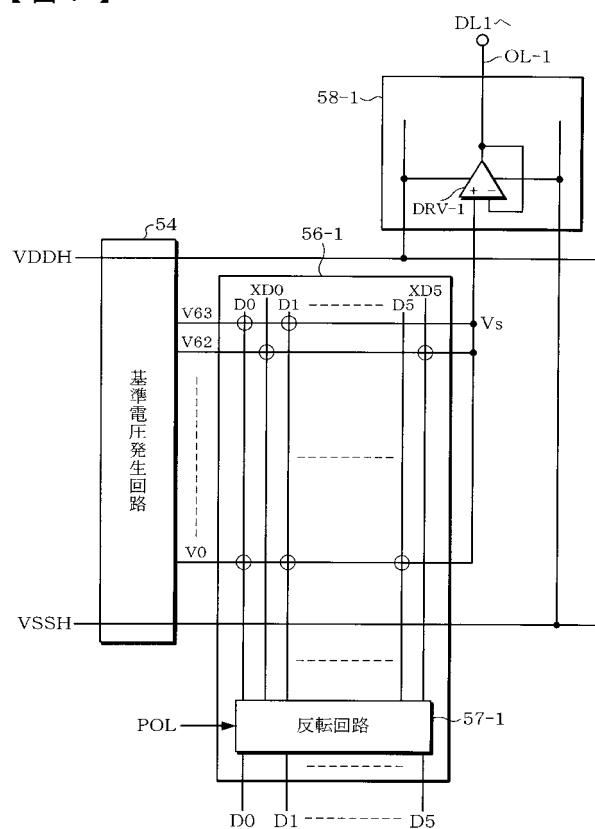

図7に、基準電圧発生回路54、DAC56、駆動回路58の構成の概要を示す。ここでは、駆動回路58のうち、データ線DL1と電気的に接続される出力線OL-1を駆動する構成のみを示すが、他の出力線についても同様である。

## 【0071】

基準電圧発生回路54は、高電位側電源電圧VDDH及び低電位側電源電圧VSSHの間の電圧を抵抗回路により分割した複数の電圧を、基準電圧V0～V63として出力する。なお、極性反転駆動の場合、実際には所定の電位を基準とした液晶素子の印加電圧の極性が正の場合と負の場合とで電圧が対称とならないため、正極性の駆動期間で用いられる基準電圧と、負極性の駆動期間で用いられる基準電圧とが生成される。図7では、その一方を示している。

## 【0072】

DAC56-1は、ROMデコーダ回路により実現することができる。DAC56-1は、6ビットの階調データに基づいて、基準電圧V0～V63のうちいずれか1つを選択して選択電圧Vsとして演算増幅器DRV-1に出力する。なお、他の演算増幅器DRV-2～DRV-Nについても、同様に、対応する6ビットの階調データに基づいて選択された電圧が出力される。

## 【0073】

DAC56-1は、反転回路57-1を含む。反転回路57-1は、極性反転信号POLに基づいて階調データを反転する。そして、DAC56-1には、6ビットの階調データD0～D5と、6ビットの反転階調データXD0～XD5とが入力される。反転階調データXD0～XD5は、階調データD0～D5をそれぞれビット反転したものである。そして、DAC56-1において、基準電圧発生回路54により生成された多値の基準電圧V0～V63のうちのいずれか1つが階調データに基づいて選択される。

## 【0074】

例えば極性反転信号POLの論理レベルが「H」のとき、6ビットの階調データD0～

10

20

30

40

50

D5「000010」(=2)に対応して、基準電圧V2が選択される。また例えば極性反転信号POLの論理レベルが「L」のとき、階調データD0～D5を反転した反転階調データXD0～XD5を用いて基準電圧を選択する。即ち、反転階調データXD0～XD5が「111101」(=61)となり、基準電圧V61が選択される。

#### 【0075】

このようにしてDAC56-1により選択された選択電圧Vsは、演算増幅器DRV-1に供給される。

#### 【0076】

そして、演算増幅器DRV-1は、選択電圧Vsに基づいて出力線OL-1を駆動する。

10 また、電源回路100は、上述したように、極性反転信号POLに同期して対向電極の電圧を変化させる。こうして、液晶に印加される電圧の極性を反転させて駆動する。

#### 【0077】

図4では、データドライバ30の内部又は外部に設けられた不揮発性メモリとしてのEEPROM(Electrically Erasable Programmable Read Only Memory)に、予めガンマ補正データが保存されている。EEPROMは、データを電気的に書き換えできる。データドライバ30は、リセット後に開始される所定の初期化処理中にEEPROM120からガンマ補正データを読み込むようになっている。

#### 【0078】

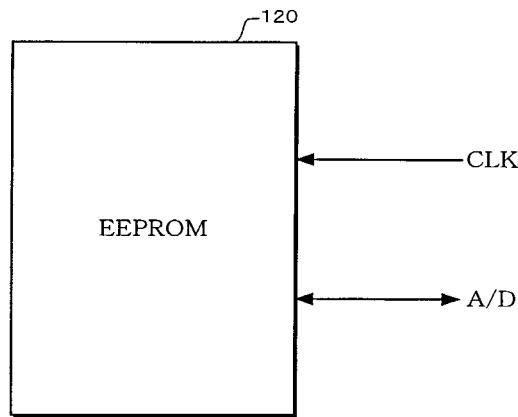

図8に、EEPROM120の構成の概要を示す。

#### 【0079】

EEPROM120には、アドレス/データ分割バスと、クロックラインとが接続される。アドレス/データ分割バス及びクロックラインとは、データドライバ30に接続される。

#### 【0080】

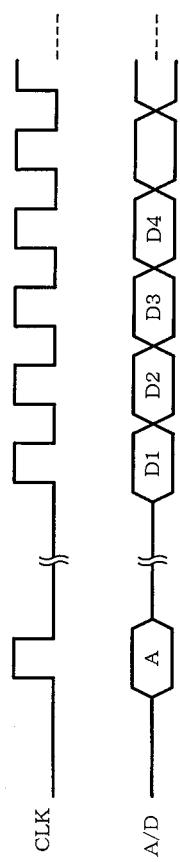

図9に、EEPROM120の読み出し制御の一例のタイミング図を示す。

#### 【0081】

データドライバ30は、例えばアドレス/データ分割バスにアドレスデータAを出力すると共に、クロックラインにクロック1パルスを出力することで、EEPROM120にアドレスデータAを設定することができる。このアドレスデータAは、データドライバ30が読み出す制御データ(例えばガンマ補正データ等)が保存されるEEPROM120のメモリ空間上のアドレスである。

30

#### 【0082】

データドライバ30は、その後、クロックラインに順次クロックを供給する。EEPROM120では、取り込まれたアドレスデータAをクロックに同期してインクリメントする。そして、アドレスデータAに対応する記憶データ(制御データ)が、クロックラインのクロックに同期してアドレス/データ分割バスに出力される。

#### 【0083】

本実施形態では、初期化処理中に、データドライバ30が図9で説明したようにEEPROM120からガンマ補正データを読み出し、基準電圧発生回路54が内蔵する複数のガンマ補正データレジスタのいずれかに該ガンマ補正データを設定する。

#### 【0084】

##### 4. 基準電圧発生回路

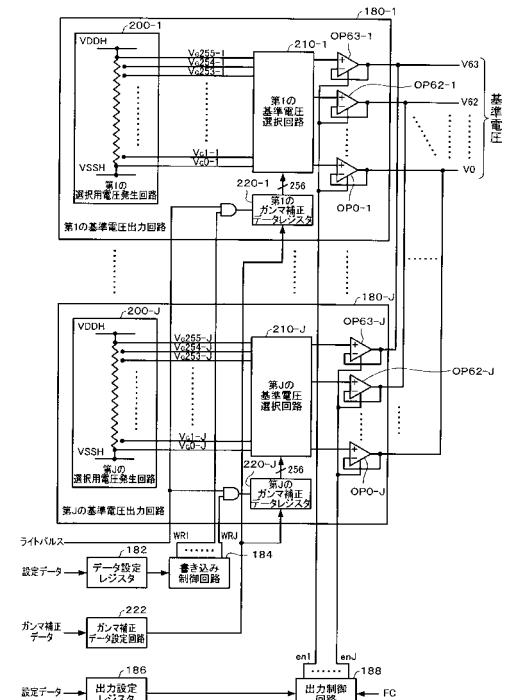

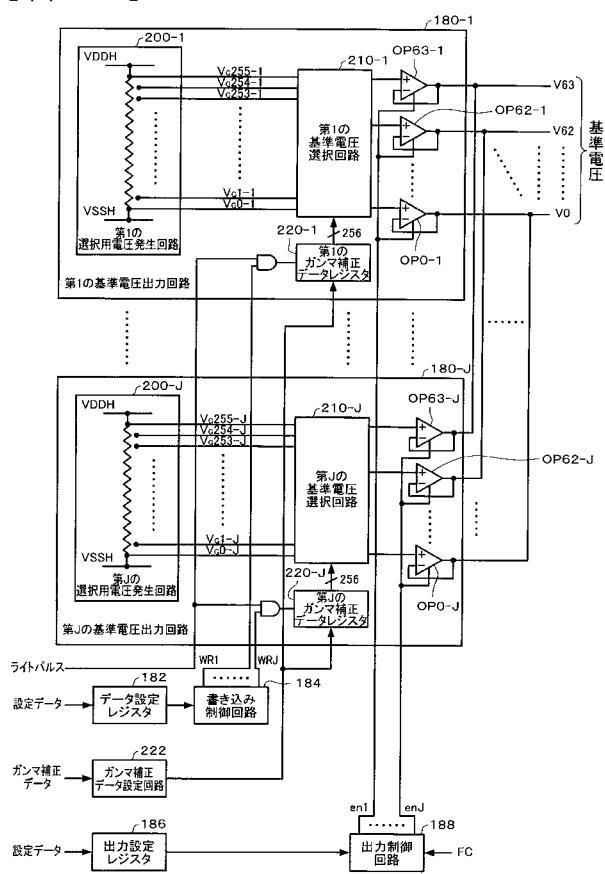

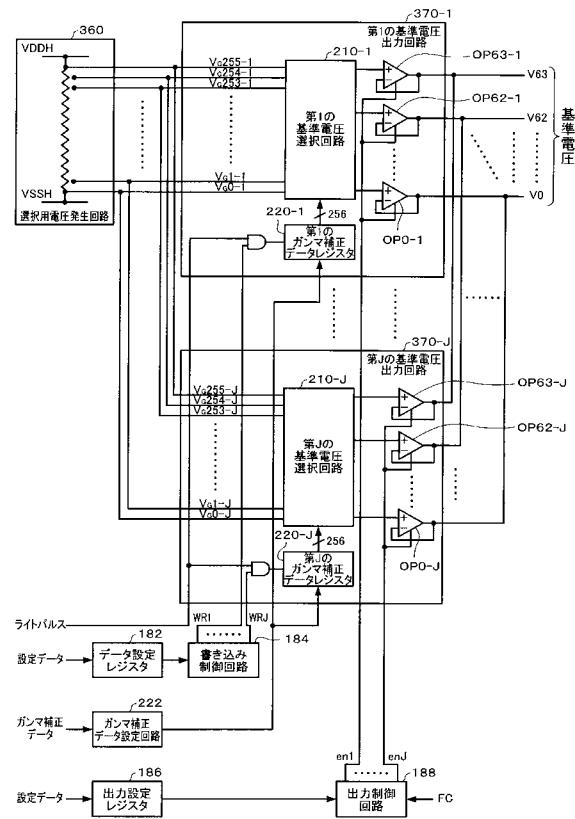

図10に、本実施形態における基準電圧発生回路54の構成例のブロック図を示す。

#### 【0085】

基準電圧発生回路54は、第1～第J(Jは2以上の整数)の基準電圧出力回路180-1～180-J、ガンマ補正データ設定回路222を含む。

#### 【0086】

第1～第Jの基準電圧出力回路180-1～180-Jの各基準電圧出力回路の構成は共通であり、第h(1≤h≤J、hは整数)の基準電圧出力回路は、第hのガンマ補正データレジスタと第hの基準電圧選択回路を含む。従って、基準電圧発生回路54は、第1

50

～第Jのガンマ補正データレジスタ220-1～220-Jと第1～第Jの基準電圧選択回路210-1～210-Jとを含むことができる。

#### 【0087】

また第hの基準電圧出力回路180-hは、第hの選択用電圧発生回路200-hを含むことができる。第hの選択用電圧発生回路200-hは、両端に高電位側電源電圧VDDH及び低電位側電源電圧VSSHが供給されるラダー抵抗回路を含む。このラダー抵抗回路は、直列に接続された複数の抵抗素子を有する。そして、抵抗素子同士が電気的に接続されるノードを出力ノードとして、該出力ノードから選択用電圧を出力する。なお各抵抗素子の抵抗値は、ホスト又は表示コントローラ38からの制御によって変更できることが望ましい。

10

#### 【0088】

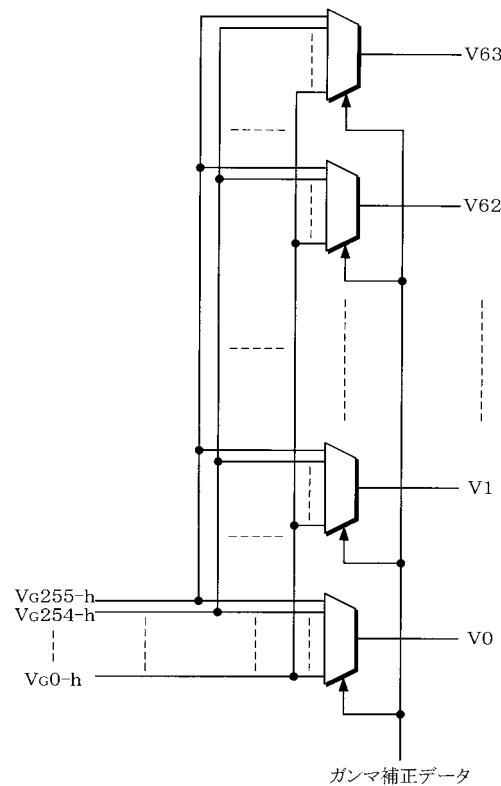

こうして第hの選択用電圧発生回路200-hは、電位の低い順に並ぶ選択用電圧VG0-h～VG255-h(第hグループの第1～第Lの選択用電圧)を出力する。なお、選択用電圧発生回路200-hは、電位の高い順に並ぶ選択用電圧VG0-h～VG255-hを出力するようにしてもよい。

#### 【0089】

ガンマ補正データレジスタ220-hには、各ビットのデータが各選択用電圧に対応付けられ、基準電圧として出力するか否かを示すLビットのガンマ補正データが設定される。

#### 【0090】

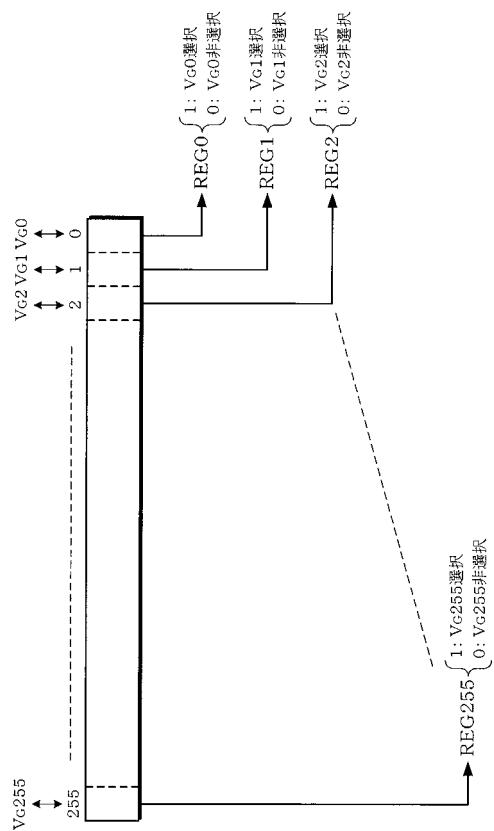

図11に、本実施形態のガンマ補正データの説明図を示す。

20

#### 【0091】

選択用電圧がL種類の場合、ガンマ補正データはLビット構成である。従って、図10におけるガンマ補正データは256ビット構成である。ガンマ補正データの各ビットのデータは、各選択用電圧を基準電圧として出力するか否かを示す。本実施形態では、ビットのデータが「1」のときは当該ビットに対応する選択用電圧を基準電圧として出力することを示し、ビットのデータが「0」のときは当該ビットに対応する選択用電圧を基準電圧として出力しないことを示す。従って、256ビット構成のガンマ補正データは、256ビットのうちいずれかの64ビットだけが「1」で、残りが「0」であるデータとなる。

30

#### 【0092】

図11では、ガンマ補正データの最上位ビットである255ビット目のデータがREG255となり、・・・、ガンマ補正データの最下位ビットである0ビット目のデータがREG0となる。

#### 【0093】

図10において、ガンマ補正データ設定回路222は、1ビットずつシリアルに入力されるガンマ補正データを8ビット構成のパラレルデータに変換し、該パラレルデータを第1～第Jのガンマ補正データレジスタ220-1～220-Jのいずれか1つに設定する制御を行う。こうすることで、ガンマ補正データが256ビットで構成されていても、パラレルデータを32回ガンマ補正データレジスタに設定すればよい。従って、例えば256クロックのライトパルスで第1～第Jのガンマ補正データレジスタ220のそれぞれに高速に書き込み制御を行うことなく、32クロックのライトパルスで各ガンマ補正データレジスタに低速に書き込み制御を行えばよい。そのため、ガンマ補正データの設定に伴う電力消費を大幅に削減できるようになる。

40

#### 【0094】

図12に、図8の第1～第Jの基準電圧選択回路210-1～210-Jのうちの1つの第hの基準電圧選択回路210-hの動作例の説明図を示す。

#### 【0095】

図12では、ガンマ補正データの最下位ビットが「0」、下位2ビット目が「1」、下位3ビット目が「1」、・・・、最上位ビットが「1」である。ガンマ補正データの最下位ビットが「0」であるため、当該ビットに対応する選択用電圧VG0-hは基準電圧と

50

して出力されない。

【0096】

一方、ガンマ補正データの下位2ビット目が「1」であるため、当該ビットに対応する選択用電圧 $V_G 1 - h$ は基準電圧として出力される。従って、選択用電圧 $V_G 1 - h$ が、基準電圧 $V_0$ として出力される。

【0097】

ガンマ補正データの下位3ビット目が「1」であるため、当該ビットに対応する選択用電圧 $V_G 2 - h$ は基準電圧として出力される。従って、選択用電圧 $V_G 2 - h$ が、基準電圧 $V_1$ として出力される。

【0098】

同様に、ガンマ補正データの上位2ビット目が「0」であるため、当該ビットに対応する選択用電圧 $V_G 254 - h$ は基準電圧として出力されない。これに対して、ガンマ補正データの最上位ビットが「1」であるため、当該ビットに対応する選択用電圧 $V_G 255 - h$ は基準電圧として出力される。従って、選択用電圧 $V_G 255 - h$ が、基準電圧 $V_6$ として出力される。

【0099】

こうすることで、基準電圧発生回路54が、電位の高い順又は電位の低い順に並ぶ第1～第Lの選択用電圧の中から選択されたK種類の選択用電圧を、電位の高い順又は電位の低い順に並ぶ第1～第Kの基準電圧として発生させることができる。

【0100】

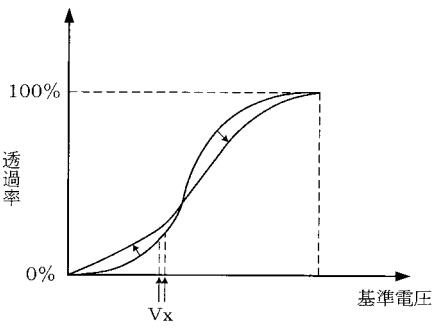

図13に、ガンマ特性の説明図を示す。

【0101】

図13は、横軸に基準電圧、縦軸に画素の透過率を示す。上述のように、本実施形態では、基準電圧 $V_x$ の電圧レベルを選択用電圧の中から選択して、複数種類の電圧レベルを出力させることができる。従って、LCDパネルの種類に応じた木目細かいガンマ補正を実現できる。

【0102】

また選択用電圧発生回路200のラダー抵抗回路を構成する各抵抗素子の抵抗値を可変制御できるようにすることで、基準電圧発生回路54が出力する複数の基準電圧 $V_0 \sim V_6$ の電圧レベルを多様化できる。

【0103】

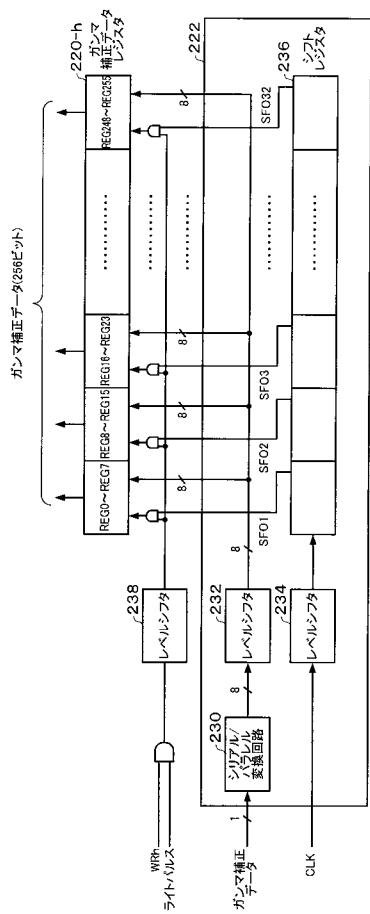

図14に、第hのガンマ補正データレジスタ220-h及びガンマ補正データ設定回路222の構成例を示す。

【0104】

図14では、第hのガンマ補正データレジスタ220-hにガンマ補正データを書き込むための構成例を示すが、他のガンマ補正データレジスタについても同様である。

【0105】

ガンマ補正データ設定回路222は、シリアル/パラレル変換回路230、レベルシフタ232、234、シフトレジスタ236を含むことができる。

【0106】

シリアル/パラレル変換回路230は、1ビットずつシリアルに入力されたガンマ補正データを、8ビットのパラレルデータに変換する。レベルシフタ232は、パラレルデータの各ビットの信号レベルを変換する。即ち、小振幅のロジック電源電圧の間を振幅するパラレルデータの各ビットの信号レベルを、大振幅の液晶駆動電源電圧の間を振幅させないように変換する。

【0107】

シフトレジスタ236は、各フリップフロップが直列に接続された複数のフリップフロップを有し、ガンマ補正データの各ビットのデータの入力同期クロックとしてのクロックCLKに同期したシフト動作を行って、8ビット毎にシフト出力SFO1、SFO2、…、SFO32を出力する。従って、シフトレジスタ236は、256個のフリップフ

10

20

30

40

50

ロップが直列に接続されたものということができる。このシフトレジスタ 236 は、所与のスタートパルスをクロック CLK に同期してシフトさせる。図 14 では、レベルシフタ 234 が、クロック CLK の信号レベルを変換した後にシフトレジスタ 236 に入力される。

#### 【0108】

図 14 におけるレベルシフタ 238 は、ライトパルスと書き込みイネーブル信号 WRh との論理積演算結果の信号レベルを変換する。信号レベルが変換された該論理積演算結果の信号が、更にシフト出力 SFO1、SFO2、…、SFO32 によりマスク制御される。マスク制御後の信号により、レベルシフタ 232 の出力が、ガンマ補正データレジスタ 220 に 8 ビットずつ設定される。

10

#### 【0109】

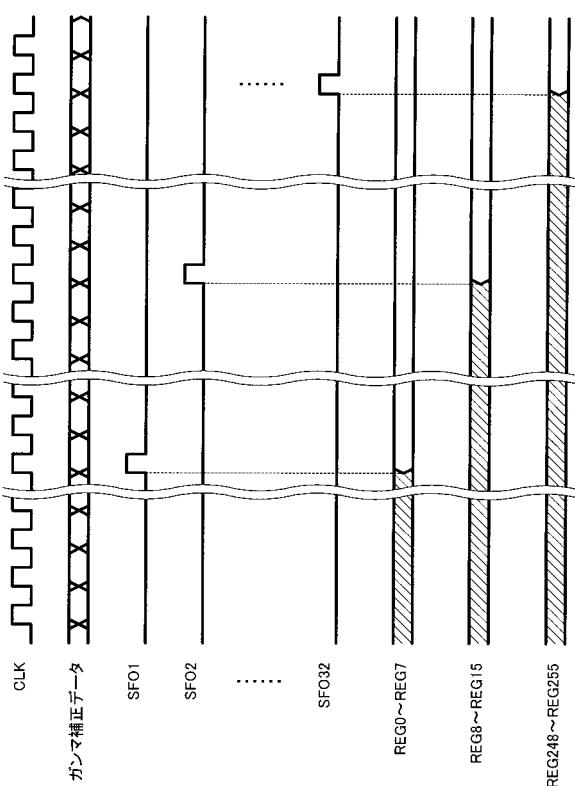

図 15 に、図 14 のガンマ補正データ設定回路 222 の動作例のタイミング図を示す。

#### 【0110】

即ち、シリアルに入力されるガンマ補正データが 8 ビットのパラレルデータに変換される。そしてガンマ補正データの 8 ビット毎にシフト出力が出力され、ガンマ補正データレジスタ 220 に 8 ビットずつ設定される。

#### 【0111】

本実施形態では、ガンマ補正データ設定回路 222 においてパラレルデータに変換されたガンマ補正データが、第 1 ~ 第 J のガンマ補正データレジスタ 220-1 ~ 220-J のいずれか 1 つに設定される。そのため基準電圧発生回路 54 は、データ設定レジスタ 182、書き込み制御回路 184 を含むことが望ましい。

20

#### 【0112】

データ設定レジスタ 182 には、第 1 ~ 第 J のガンマ補正データレジスタ 220-1 ~ 220-J のいずれにガンマ補正データ（パラレルデータ）を設定するかを指定するための設定データが、ホストや表示コントローラ 38 によって設定される。書き込み制御回路 184 は、データ設定レジスタ 182 の設定値をデコードする。そして書き込み制御回路 184 は、第 1 ~ 第 J のガンマ補正データレジスタ 220-1 ~ 220-J の書き込みイネーブル信号 WR1 ~ WRJ のうち、データ設定レジスタ 182 の設定値のデコード結果に対応したガンマ補正データレジスタの書き込みイネーブル信号をアクティブに設定する。図 14 では、第 h のガンマ補正データレジスタ 220-h への書き込みイネーブル信号 WRh によりガンマ補正データの書き込み制御が行われている。

30

#### 【0113】

こうして、第 1 ~ 第 J のガンマ補正データレジスタ 220-1 ~ 220-J のうちデータ設定レジスタ 182 の設定値に対応したガンマ補正データレジスタに、レベルシフタ 232 によって信号レベルが変換されたガンマ補正データが設定される。

#### 【0114】

図 10 において、第 h の基準電圧選択回路 210-h は、第 h のガンマ補正データレジスタ 220-h に設定されたガンマ補正データに基づいて選択用電圧 Vg0-h ~ Vg255-h (第 h グループの第 1 ~ 第 L の選択用電圧) の中から選択された 64 (= K) 種類の選択用電圧を、電位の低い順に基準電圧 V0 ~ V63 (第 1 ~ 第 K の基準電圧) として出力することができる。なお、基準電圧選択回路 210 は、電位の高い順に並ぶ基準電圧 V0 ~ V63 を出力するようにしてもよい。

40

#### 【0115】

なお第 h の基準電圧出力回路 180-h は、各インピーダンス変換回路の入力に第 1 ~ 第 K の基準電圧の各基準電圧が供給される第 1 ~ 第 K のインピーダンス変換回路を含むことが望ましい。即ち、第 h の基準電圧出力回路 180-h が、第 h の基準電圧選択回路 210-h の出力がその入力に供給されるインピーダンス変換回路 OPO-h、OP1-h、…、OP63-h を含むことが望ましい。このインピーダンス変換回路は、例えばボルテージフォロワ接続された演算増幅器により構成される。従って、例えばインピーダンス変換回路 OPO-h ~ OP63-h によってインピーダンス変換されて、DAC56

50

に各基準電圧が供給されることになる。このため、選択用電圧発生回路の高電位側又は低電位側電源電圧が供給される信号線から基準電圧選択回路 210 や D A C 56 を経路とするインピーダンスが増大することに起因する各信号線の充電時間が長くなることを抑えることができる。

#### 【0116】

また本実施形態における基準電圧発生回路 54 は、第 1 ~ 第 J の基準電圧選択回路のいずれか 1 つから基準電圧 V0 ~ V63 (第 1 ~ 第 K の基準電圧) を出力する。そのため 10 に示す基準電圧発生回路 54 は、出力設定レジスタ 186、出力制御回路 188 を含むことが望ましい。

#### 【0117】

出力設定レジスタ 186 には、第 1 ~ 第 J の基準電圧選択回路 210 - 1 ~ 210 - J のいずれから基準電圧 V0 ~ V63 (第 1 ~ 第 K の基準電圧) を出力するかを指定するための設定データが、ホストや表示コントローラ 38 によって設定される。より具体的には、出力設定レジスタ 186 には、フレームレートコントロール方式で 1 周期を構成する各フレームにおいて、出力すべき第 1 ~ 第 J の基準電圧選択回路 210 - 1 ~ 210 - J の 1 つを指定する設定データが設定される。

#### 【0118】

出力制御回路 188 は、出力設定レジスタ 186 の設定値をデコードする。そして出力制御回路 188 は、第 1 ~ 第 J の基準電圧選択回路 210 - 1 ~ 210 - J の出力イネーブル信号 en1 ~ enJ のうち、出力設定レジスタ 186 の設定値のデコード結果に対応した基準電圧選択回路からの基準電圧 V0 ~ V63 の出力イネーブル信号をアクティブに設定する。例えば図 10 では、出力イネーブル信号 en1 ~ enJ のそれぞれが、各基準電圧出力回路に設けられたインピーダンス変換回路の出力イネーブル信号として供給されている。インピーダンス変換回路がボルテージフォロワ接続された演算増幅器により構成される場合、出力イネーブル信号がアクティブのときには該演算増幅器の動作電流を発生させ、出力イネーブル信号が非アクティブの時には該演算増幅器の動作電流を停止又は制限させる。

#### 【0119】

なおフレームレートコントロール方式で 1 周期を構成する各フレームにおいて、第 1 ~ 第 J の基準電圧選択回路 210 - 1 ~ 210 - J のうち出力すべき基準選択回路の順序が予め決められている場合には、出力設定レジスタ 186 が省略された構成を採用することができる。

#### 【0120】

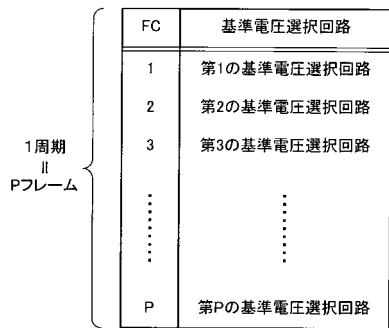

図 16 に、出力すべき基準選択回路の順序が予め決められている場合の出力制御回路 188 の動作例の説明図を示す。

#### 【0121】

図 16 では、フレームレートコントロール方式で 1 周期を構成するフレーム数が P であるものとする。そして、P フレームの各フレームにおいて、第 1 ~ 第 J の基準電圧選択回路 210 - 1 ~ 210 - J のうち出力すべき基準選択回路の順序が予め決められている。出力制御回路 188 は、1 フレーム毎に更新されるカウント値 FC に対応した基準電圧出力回路が選択されるように出力イネーブルをアクティブにすればよい。

#### 【0122】

こうして、第 1 ~ 第 J の基準電圧選択回路 210 - 1 ~ 210 - J のうち、いずれか 1 つの基準電圧選択回路から出力された基準電圧 V0 ~ V63 (第 1 ~ 第 K の基準電圧) が、出力される。

#### 【0123】

なお図 16 では、フレームレートコントロール方式の 1 周期を構成する P フレームの各フレームにおいて、選択される基準電圧選択回路を異ならせていたが、Q 種類の基準電圧選択回路の中から選択された基準電圧選択回路からの第 1 ~ 第 K の基準電圧を複数の基準電圧 V0 ~ V63 として出力するようにしてもよい。

10

20

30

40

50

## 【0124】

なお図5及び図6では、1フレーム毎に更新されるカウント値FC及び1ライン毎に更新されるカウント値LCに基づいてフレームレートコントロール方式を実現していたが、これに限定されるものではない。例えば1フレーム毎に更新されるカウント値FCのみに基づいてフレームレートコントロール方式を実現してもよい。

## 【0125】

以上のように基準電圧発生回路54は、1フレーム毎に更新されるカウント値に基づいて、Q種類の基準電圧選択回路の中から選択された基準電圧選択回路からの第1～第Kの基準電圧を複数の基準電圧として出力できる。

## 【0126】

10

## 4.1 基準電圧選択回路

次に、本実施形態の第1～第Jの基準電圧選択回路210-1～210-Jについて説明する。第1～第Jの基準電圧選択回路210-1～210-Jの各基準電圧選択回路の構成は共通とすることができるので、以下では第hの基準電圧選択回路210-hについて説明する。

## 【0127】

第hの基準電圧選択回路210-hは、電位の降順又は昇順に並ぶK種類の選択用電圧の中から選択されたL種類の選択用電圧を、電位の降順又は昇順に並ぶL種類の基準電圧として出力する。そのため、第hの基準電圧選択回路210-hの機能を単純に回路で実現しようとすると、回路規模が大きくなってしまう。

20

## 【0128】

図17に、本実施形態の比較例における第hの基準電圧選択回路の構成例のブロック図を示す。

## 【0129】

比較例では、基準電圧毎に、256入力1出力のセレクタが設けられている。この場合、各セレクタは、ガンマ補正データに基づいて選択用電圧 $V_{G0-h} \sim V_{G255-h}$ のうちの1つを選択することになる。

30

## 【0130】

従って、基準電圧の種類を増加させる毎に、256入力1出力のセレクタを追加する必要が生じ、第hの基準電圧選択回路のみならず、基準電圧発生回路54の回路規模の増大を招き、消費電力を増大させることにもなる。

## 【0131】

そこで、本実施形態では、以下に説明するように、第hの基準電圧選択回路の機能をスイッチマトリックス構成で実現させるようにしている。こうすることで、第hの基準電圧選択回路210-hの回路規模の増大を抑えることができるようになる。しかも、比較例と比べて、選択用電圧の種類や基準電圧の種類が増加しても、第hの基準電圧選択回路210-hの回路規模の増大が少なくて済む。

## 【0132】

40

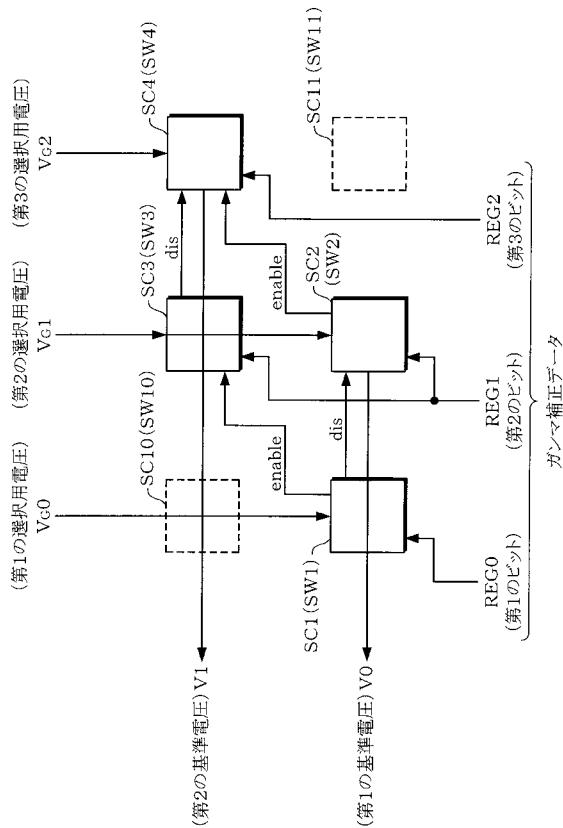

図18に、本実施形態における第hの基準電圧選択回路210-hの構成例のブロック図を示す。ここでは、説明の簡略化のため、選択用電圧が3種類( $V_{G0-h}$ 、 $V_{G1-h}$ 、 $V_{G2-h}$ )、基準電圧が2種類(V0、V1)であるものとする。選択用電圧が3種類以上で、且つ基準電圧が2種類以上の第hの基準電圧選択回路210-hは、図18の構成を必ず含む。従って、本実施形態において、電位の高い順又は電位の低い順に並ぶ第1～第Kの基準電圧を発生させる基準電圧発生回路54は、図18に示すように第1～第Kの基準電圧のうち少なくとも第1及び第2の基準電圧を出力する基準電圧選択回路を含むことができる。

## 【0133】

図18の基準電圧選択回路は、3ビットのガンマ補正データに基づいて、電位の高い順又は電位の低い順に並ぶ第1～第3の選択用電圧 $V_{G0-h} \sim V_{G2-h}$ の中から、電位の高い順又は低い順に並ぶ第1及び第2の基準電圧V0、V1を選択する。

50

## 【0134】

この基準電圧選択回路は、第1～第4のスイッチ素子SW1～SW4を含む。第1のスイッチ素子SW1は、第1の選択用電圧 $V_{G0}-h$ を第1の基準電圧 $V_0$ として出力するためのスイッチ回路である。第2のスイッチ素子SW2は、第2の選択用電圧 $V_{G1}-h$ を第1の基準電圧 $V_0$ として出力するためのスイッチ回路である。第3のスイッチ素子SW3は、第2の選択用電圧 $V_{G1}-h$ を第2の基準電圧 $V_1$ として出力するためのスイッチ回路である。第4のスイッチ素子SW4は、第3の選択用電圧 $V_{G2}-h$ を第2の基準電圧 $V_1$ として出力するためのスイッチ回路である。各スイッチ回路は、各選択用電圧が供給される信号線と各基準電圧が出力される信号線とを電気的に接続又は遮断することができる。

10

## 【0135】

そして、第1のスイッチ素子SW1は、ガンマ補正データの第1のビットのデータREG0によりイネーブルに設定されたことを条件に、第1の選択用電圧 $V_{G0}-h$ を第1の基準電圧 $V_0$ として出力する。第2のスイッチ素子SW2は、ガンマ補正データの第1のビットのデータREG0によりディセーブルに設定され、且つガンマ補正データの第2のビットのデータREG1によりイネーブルに設定されたことを条件に、第2の選択用電圧 $V_{G1}-h$ を第1の基準電圧 $V_0$ として出力する。第3のスイッチ素子SW3は、ガンマ補正データの第1のビットのデータREG0によりイネーブルに設定され、且つガンマ補正データの第2のビットのデータREG1によりイネーブルに設定されたことを条件に、第2の選択用電圧 $V_{G1}-h$ を第2の基準電圧 $V_1$ として出力する。第4のスイッチ素子SW4は、ガンマ補正データの第1のビットのデータREG0によりイネーブルに設定され、且つガンマ補正データの第2のビットのデータREG1によりディセーブルに設定され、且つガンマ補正データの第3のビットのデータREG2によりイネーブルに設定されたことを条件に、第3の選択用電圧 $V_{G2}-h$ を第2の基準電圧 $V_1$ として出力する。

20

## 【0136】

なお図18の基準電圧選択回路は、各スイッチセルが第1～第4のスイッチ素子SW1～SW4の各スイッチ素子を有する第1～第4のスイッチセルSC1～SC4を含むことができる。そして、各スイッチセルは、他のスイッチセルから供給されるイネーブル信号及びディセーブル信号に基づいて、内蔵するスイッチ素子のオンオフ制御を行うと共に、別のスイッチセルにイネーブル信号及びディセーブル信号を出力する。

30

## 【0137】

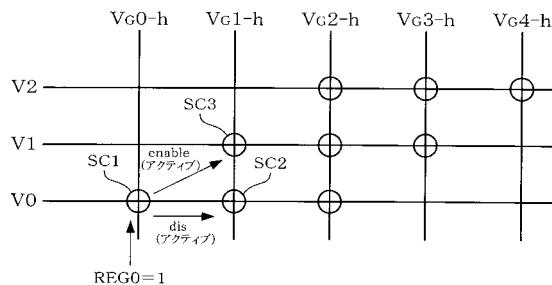

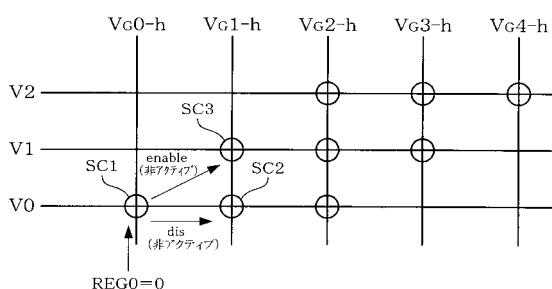

図19(A)、図19(B)に、スイッチセルが他のスイッチセルに出力するイネーブル信号及びディセーブル信号を説明する図を示す。図19(A)、図19(B)では、4種類の選択用電圧から3種類の基準電圧を選択する例を示している。

## 【0138】

図19(A)において、例えばガンマ補正データの第1のビットのデータREG0により第1のスイッチセルSC1がイネーブルに設定されたとき、第1のスイッチセルSC1は、第2のスイッチセルSC2へのディセーブル信号disをアクティブにし、第3のスイッチセルへのイネーブル信号enableをアクティブにする。

40

## 【0139】

第2のスイッチセルSC2は、第1のスイッチセルSC1からのディセーブル信号disを用いて、第2のスイッチセルSC2が内蔵する第2のスイッチ素子SW2のオンオフ制御を行う。同様に、第3のスイッチセルSC3は、第1のスイッチセルSC1からのイネーブル信号enableを用いて、第3のスイッチセルSC3が内蔵する第3のスイッチ素子SW3のオンオフ制御を行う。

## 【0140】

これに対して、図19(B)において、例えばガンマ補正データの第1のビットのデータREG0により第1のスイッチセルSC1がディセーブルに設定されたとき、第1のスイッチセルSC1は、第2のスイッチセルSC2へのディセーブル信号disを非アクティブにし、第3のスイッチセルへのイネーブル信号enableを非アクティブにする。

50

## 【0141】

この場合も図19(A)と同様に、第2のスイッチセルSC2は、第1のスイッチセルSC1からのディセーブル信号d<sub>is</sub>を用いて、第2のスイッチセルSC2が内蔵する第2のスイッチ素子SW2のオンオフ制御を行う。また第3のスイッチセルSC3は、第1のスイッチセルSC1からのイネーブル信号enableを用いて、第3のスイッチセルSC3が内蔵する第3のスイッチ素子SW3のオンオフ制御を行う。

## 【0142】

より具体的には、第1のスイッチセルSC1は、ガンマ補正データの第1のビットのデータREG0によりイネーブルに設定されたとき、第2のスイッチセルSC2へのディセーブル信号d<sub>is</sub>をアクティブにすると共に、第3のスイッチセルSC3へのイネーブル信号enableをアクティブにする。また、第1のスイッチセルSC1は、ガンマ補正データの第1のビットのデータREG0によりディセーブルに設定されたとき、第2のスイッチセルSC2へのディセーブル信号d<sub>is</sub>を非アクティブにすると共に、第3のスイッチセルSC3へのイネーブル信号enableを非アクティブにする。

10

## 【0143】

第2のスイッチセルSC2は、ガンマ補正データの第2のビットのデータREG1によりイネーブルに設定され、且つ第1のスイッチセルSC1からのディセーブル信号d<sub>is</sub>が非アクティブであることを条件に第2の選択用電圧V<sub>G</sub>1を第1の基準電圧V0として出力すると共に、第4のスイッチセルSC4へのイネーブル信号enableをアクティブにする。それ以外のとき、第2のスイッチセルSC2は、第4のスイッチセルSC4へのイネーブル信号enableを非アクティブにする。

20

## 【0144】

第3のスイッチセルSC3は、ガンマ補正データの第2のビットのデータREG1によりイネーブルに設定され、且つ第1のスイッチセルSC1からのイネーブル信号enableがアクティブであることを条件に第2の選択用電圧V<sub>G</sub>1を第2の基準電圧V1として出力すると共に、第4のスイッチセルSC4へのディセーブル信号d<sub>is</sub>をアクティブにする。それ以外のとき、第3のスイッチセルSC3は、第4のスイッチセルSC4へのディセーブル信号d<sub>is</sub>を非アクティブにする。

## 【0145】

第4のスイッチセルSC4は、ガンマ補正データの第3のビットのデータREG2によりイネーブルに設定され、且つ第3のスイッチセルSC3からのディセーブル信号d<sub>is</sub>が非アクティブであり、且つ第2のスイッチセルSC2からのイネーブル信号enableがアクティブであることを条件に第3の選択用電圧V<sub>G</sub>2を第2の基準電圧V1として出力する。

30

## 【0146】

このようにイネーブル信号及びディセーブル信号を伝搬させることで、1つのスイッチセルを繰り返し接続するだけで済み、基準電圧選択回路の設計や、その変更が容易になる。なお、このディセーブル信号をイネーブル信号として伝搬させるようにしてもよいことは言うまでもない。

40

## 【0147】

図20に、図18の基準電圧選択回路の動作例を示す。

## 【0148】

図20に示すように、図18の基準電圧選択回路は、電位の高い順又は電位の低い順に並ぶ第1～第3の選択用電圧V<sub>G</sub>0-h～V<sub>G</sub>2-hが、3ビットのガンマ補正データにより「1」が設定されたビットのデータに基づいて、電位の高い順又は電位の低い順に並ぶ第1及び第2の基準電圧V0、V1を出力する。

## 【0149】

このようなスイッチ素子又は該スイッチ素子を含むスイッチセルを採用して、上記のように信号(イネーブル信号、ディセーブル信号)を伝搬させることで、スイッチマトリックス構成で基準電圧選択回路を実現した場合であってもスイッチ素子又はスイッチセルの

50

数を削減できる。

#### 【0150】

一般に、スイッチマトリックス構成で第1～第3の選択用電圧 $V_{G0-h} \sim V_{G2-h}$ から第1及び第2の基準電圧 $V_0$ 、 $V_1$ を選択する回路を実現する場合、 $6 (= 3 \times 2)$ 個のスイッチ素子又はスイッチセルが必要となる。

#### 【0151】

これに対して、電位の高い順又は低い順に2つの基準電圧を出力するという特性を考慮すると、第3の選択用電圧 $V_{G2-h}$ が第1の基準電圧 $V_0$ として出力されることはない。同様に、第1の選択用電圧 $V_{G0-h}$ が第2の基準電圧 $V_1$ として出力されることはない。従って、図18の場合、スイッチ素子SW10（スイッチ素子SW10を含むスイッチセルSC10）及びスイッチ素子SW11（スイッチ素子SW11を含むスイッチセルSC11）を省略できる。10

#### 【0152】

本実施形態では、基準電圧選択回路が、電位の高い順又は電位の低い順に並ぶ第1～第Lの選択用電圧の中から、電位の高い順又は電位の低い順に並ぶ第1～第Kの基準電圧を選択する。このため、本実施形態の場合には、1つの基準電圧を出力するために $(L-K+1)$ 個のスイッチセルが必要とされる。そのため、この基準電圧選択回路は、 $K \times (L-K+1)$ 個のスイッチセルで実現できる。

#### 【0153】

以下では、本実施形態の基準電圧選択回路の具体的な回路構成例について説明する。20

#### 【0154】

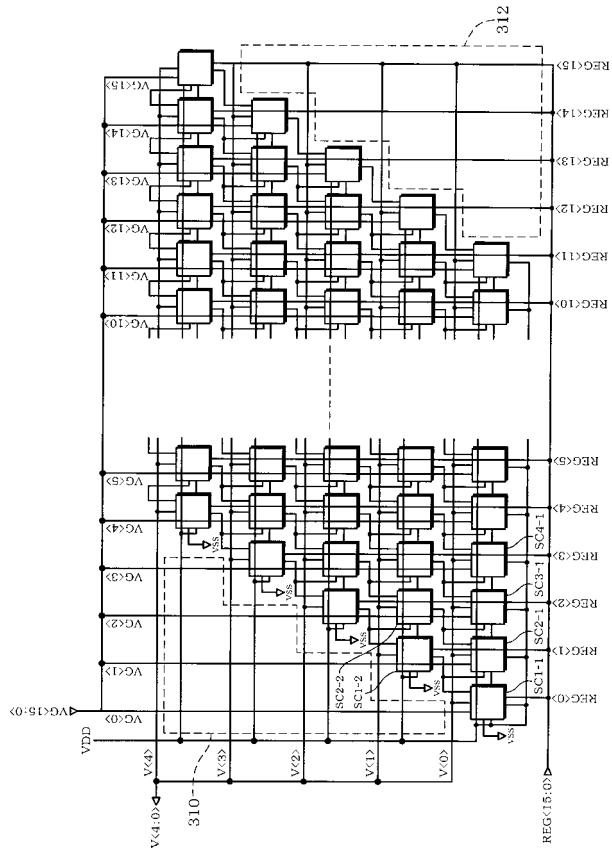

図21に、第hの基準電圧選択回路 $210-h$ の具体的な回路構成例を示す。図21では、Lが16（第1～第16の選択用電圧 $V_{G0-h} \sim V_{G15-h}$ ）で、Kが5（第1～第4の基準電圧 $V_0 \sim V_4$ ）の構成例を示す。

#### 【0155】

$V_{G<15:0>}^<$ が第1～第16の選択用電圧 $V_{G0-h} \sim V_{G15-h}$ を示し、 $V_{G<15:0>}^<$ の各ビットの信号線に各選択用電圧が供給される。 $V<4:0>$ が第1～第4の基準電圧 $V_0 \sim V_4$ を示し、 $V<4:0>$ の各ビットの信号線に各基準電圧が出力される。REG $<15:0>$ は、16ビットのガンマ補正データである。

#### 【0156】

単純にスイッチマトリックス構成を採用した場合、 $80 (= 5 \times 16)$ 個のスイッチセルが必要となるにも関わらず、本実施形態では、 $60 (= 5 \times (16 - 5 + 1))$ 個のスイッチセルで実現できる。これは、上述した理由により、図18の回路部分310、312のスイッチセルを省略できるからである。30

#### 【0157】

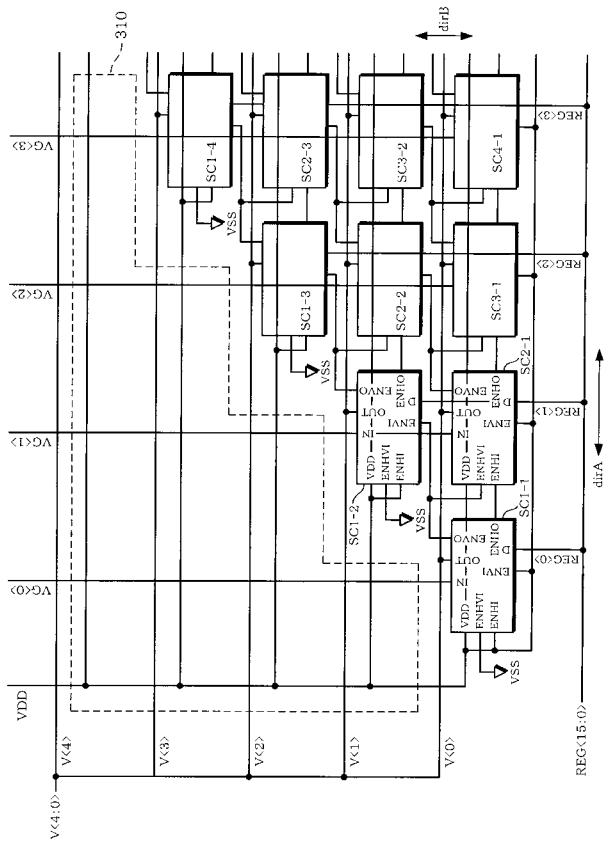

図22に、図21の回路図の一部の拡大図を示す。

#### 【0158】

図22において、図21と同一部分には同一符号を付し適宜説明を省略する。図22において、例えばスイッチセルSC1-1、SC2-1、SC3-1、SC4-1、…、SC2-1、SC2-2、…のそれぞれは同一構成である。40

#### 【0159】

各スイッチセルは、VDD端子、ENHVI端子、ENHI端子、ENVII端子、D端子、ENHO端子、ENVID端子、OUT端子、IN端子を含む。

#### 【0160】

VDD端子は、高電位側の電源電圧VDDを供給するための端子である。このスイッチセルでは低電位側の電源電圧VSSを供給するための端子の図示は省略されている。ENHVI端子は、dirB方向に並ぶセルに供給されるイネーブル信号enableが入力される端子である。ENHI端子は、dirA方向に並ぶセルに供給されるイネーブル信号enable（論理レベルを反転したディセーブル信号disと等価）が入力される端子である。ENVII端子は、dirB方向に並ぶセルに供給されるイネーブル信号ena

b1eが入力される端子である。ENHO端子は、dirA方向に並ぶセルに供給されるイネーブル信号enable（論理レベルを反転したディセーブル信号disと等価）が出力される端子である。D端子は、ガンマ補正データのビットのデータが入力される端子である。ENVD端子は、dirB方向に並ぶセルに供給されるイネーブル信号enableを出力するための端子である。OUT端子は、基準電圧を供給するための端子である。IN端子は、選択用電圧が供給される端子である。

#### 【0161】

従って、図22に示すように、基準電圧選択回路は、第1～第4のスイッチセルSC1-1、SC2-1、SC1-2、SC2-2を含むことができる。第1のスイッチセルSC1-1は、電位の高い順又は電位の低い順に並ぶ第1～第3の選択用電圧のうちの第1の選択用電圧を、電位の高い順又は低い順に並ぶ第1及び第2の基準電圧のうちの第1の基準電圧として出力するための第1のスイッチ素子を有する。第2のスイッチセルSC1-2は、第2の選択用電圧を第1の基準電圧として出力するための第2のスイッチ素子を有する。第3のスイッチセルSC1-2は、第2の選択用電圧を第2の基準電圧として出力するための第3のスイッチ素子を有する。第4のスイッチセルSC2-2は、第3の選択用電圧を第2の基準電圧として出力するための第4のスイッチ素子を有する。

#### 【0162】

そして第1のスイッチセルSC1-1には、各ビットのデータが各選択用電圧に対応付けられ基準電圧として出力するか否かを示すレジットのガンマ補正データの第1のビットのデータが供給されると共に、第1のスイッチセルSC1-1は、第2及び第3のスイッチセルSC2-1、SC1-2に対してイネーブル信号を出力する。第2のスイッチセルSC2-1には、ガンマ補正データの第2のビットのデータが供給されると共に、第2のスイッチセルSC2-1は、第3及び第4のスイッチセルSC1-2、SC2-2に対してイネーブル信号を出力する。第3のスイッチセルSC1-2には、ガンマ補正データの第2のビットのデータが供給されると共に、第3のスイッチセルSC1-2は、第4のスイッチセルSC2-2に対してイネーブル信号を出力する。第4のスイッチセルSC2-2には、ガンマ補正データの第3のビットのデータが供給される。

#### 【0163】

図22では、上述のディセーブル信号disを、イネーブル信号enableとして出力する。アクティブに設定されたイネーブル信号enableと非アクティブに設定されたディセーブル信号disとが等価であり、非アクティブに設定されたイネーブル信号enableとアクティブに設定されたディセーブル信号disとが等価だからである。

#### 【0164】

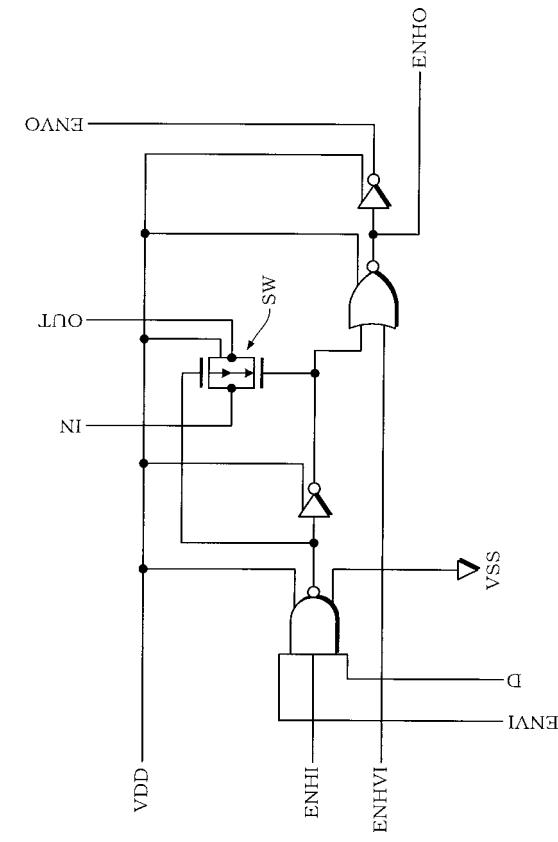

図23に、図22のスイッチセルの回路構成例を示す。

#### 【0165】

図23では、スイッチ素子SWが、トランスマルチエクソートにより構成される。ENVI端子、D端子及びENHI端子からの入力信号の論理積演算結果が「H」のとき、スイッチ素子SWが導通状態となり、IN端子とOUT端子が同電位となる。該論理積演算結果が「L」のとき、スイッチ素子SWが非導通状態となる。

#### 【0166】

この論理積演算結果とENHV端子からの入力信号との論理和演算結果が、ENV0端子から出力される。また論理積演算結果とENHV端子からの入力信号との論理和演算結果の反転結果は、ENHO端子から出力信号となる。

#### 【0167】

##### 4.1 第1の変形例

図10に示す本実施形態では、第1～第Jの基準電圧出力回路180-1～180-Jのそれぞれが、選択用電圧発生回路を備え、該選択用電圧発生回路からの選択用電圧の中から基準電圧を選択していた。本実施形態の第1の変形例では、第1～第Jの基準電圧出力回路の選択用電圧を共通化している。

#### 【0168】

10

20

30

40

50

図24に、本実施形態の第1の変形例における基準電圧発生回路の構成例のブロック図を示す。なお図24において、図10と同一部分には同一符号を付し、適宜説明を省略する。

#### 【0169】

第1の変形例における基準電圧発生回路350は、選択用電圧発生回路360と、第1～第Jの基準電圧出力回路370-1～370-Jを含む。選択用電圧発生回路360は、電位の低い順に並ぶ選択用電圧 $V_{G0} \sim V_{G255}$ を出力する。なお、選択用電圧発生回路360は、電位の高い順に並ぶ選択用電圧 $V_{G0} \sim V_{G255}$ を出力するようにしてよい。この選択用電圧 $V_{G0} \sim V_{G255}$ は、第1～第Jの基準電圧出力回路370-1～370-Jにおける選択用電圧 $V_{G0-1 \sim V_{G255}-1}, V_{G0-2 \sim V_{G255}-2}, \dots, V_{G0-J \sim V_{G255}-J}$ として供給される。10

#### 【0170】

第1～第Jの基準電圧出力回路370-1～370-hのうちの1つである第hの基準電圧出力回路370-hは、第hの基準電圧選択回路210-h、第hのガンマ補正データレジスタ220-hを含む。このため第1～第Jの基準電圧出力回路370-1～370-hの選択用電圧 $V_{G0} \sim V_{G255}$ が、選択用電圧発生回路360から供給される点を除いて、図10に示す本実施形態と同様であるためその他の説明を省略する。

#### 【0171】

第1の変形例によれば、選択用電圧発生回路を共通化したため、本実施形態と比較して基準電圧発生回路の回路規模を小さくできるという効果が得られる。20

#### 【0172】

##### 4.2 第2の変形例

本実施形態のガンマ補正データ設定回路222は、シフトレジスタのシフト出力に同期してパラレルデータをガンマ補正データレジスタ220に設定していたが、本発明はこれに限定されるものではない。

#### 【0173】

本実施形態の変形例におけるガンマ補正データ設定回路400は、ガンマ補正データレジスタの書き込み領域を指定するアドレスに基づいて、上記のパラレルデータをガンマ補正データに設定する。30

#### 【0174】

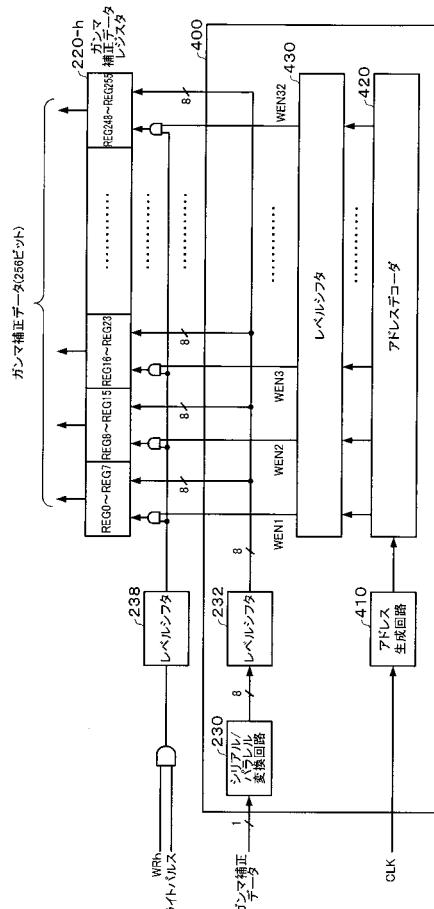

図25に、本実施形態の第2の変形例におけるガンマ補正データ設定回路400の構成例のブロック図を示す。図25において図14と同一部分に同一符号を付し、適宜説明を省略する。

#### 【0175】

基準電圧発生回路54は、図10のガンマ補正データ設定回路222に代えて本変形例におけるガンマ補正データ設定回路400を含むことができる。

#### 【0176】

ガンマ補正データ設定回路400は、アドレス生成回路410を含み、アドレス生成回路410によって生成されたアドレスに基づいて、レベルシフタ232によって信号レベルが変換されたガンマ補正データをガンマ補正データレジスタ220に設定することができる。ここでアドレス生成回路410の機能は、ガンマ補正データの各ビットのデータの入力同期クロックとしてのクロックCLKをカウントするカウンタにより実現できる。40

#### 【0177】

ガンマ補正データ設定回路400は、アドレスデコーダ420とレベルシフタ430とを含むことができる。アドレスデコーダ420は、アドレス生成回路410によって生成されたアドレスをデコードし、ガンマ補正データのビットのデータREG0～REG7、REG1～REG15、…、REG248～REG255のいずれの領域を書き込み領域とするアドレスかを判別する。アドレスデコーダ420のデコード結果は、レベルシフタ430によってその信号レベルが変換されて、ライトイネーブル信号WEN1～WEN32として出力される。50

## 【0178】

例えばクロックCLKをカウントし、カウント値が1～8の間ではガンマ補正データのビットのデータREG0～REG7の書き込み領域を指定するためにライトイネーブル信号WEN1のみがアクティブとなる。またカウント値が17～24の間では、ガンマ補正データのビットのデータREG16～REG23の書き込み領域を指定するためにライトイネーブル信号WEN3のみがアクティブとなる。

## 【0179】

ライトイネーブル信号WEN1～WEN3は、レベルシフタ238の出力によりマスク制御される。

## 【0180】

第2の変形例によれば、本実施形態と同様に、例えば256クロックのライトパルスでガンマ補正データレジスタ220に高速に書き込み制御を行うことなく、32クロックのライトパルスでガンマ補正データレジスタ220に低速に書き込み制御を行えばよい。そのため、ガンマ補正データの設定に伴う電力消費を大幅に削減できるようになる。

10

## 【0181】

なお第2の変形例の構成を第1の変形例に適用できることは言うまでもない。

## 【0182】

## 5. 電子機器

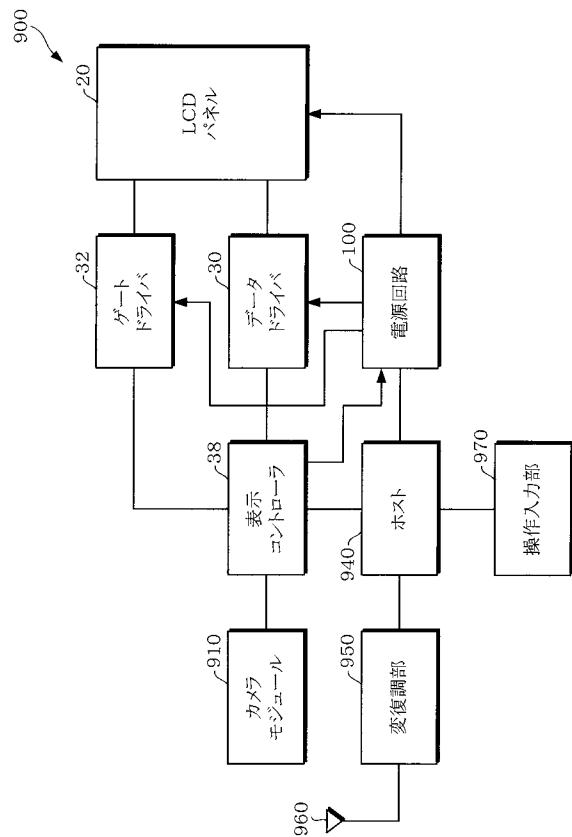

図26に、本実施形態における電子機器の構成例のブロック図を示す。ここでは、電子機器として、携帯電話機の構成例のブロック図を示す。図26において、図1又は図2と同一部分には同一符号を付し、適宜説明を省略する。

20

## 【0183】

携帯電話機900は、カメラモジュール910を含む。カメラモジュール910は、CCDカメラを含み、CCDカメラで撮像した画像のデータを、YUVフォーマットで表示コントローラ38に供給する。

## 【0184】

携帯電話機900は、LCDパネル20を含む。LCDパネル20は、データドライバ30及びゲートドライバ32によって駆動される。LCDパネル20は、複数のゲート線、複数のソース線、複数の画素を含む。

30

## 【0185】

表示コントローラ38は、本実施形態又はその第1又は第2の変形例におけるデータドライバ30及びゲートドライバ32に接続され、データドライバ30に対してRGBフォーマットの表示データを供給する。

## 【0186】

電源回路100は、データドライバ30及びゲートドライバ32に接続され、各ドライバに対して、駆動用の電源電圧を供給する。またLCDパネル20の対向電極に、対向電極電圧Vcomを供給する。

## 【0187】

ホスト940は、表示コントローラ38に接続される。ホスト940は、表示コントローラ38を制御する。またホスト940は、アンテナ960を介して受信された表示データを、変復調部950で復調した後、表示コントローラ38に供給できる。表示コントローラ38は、この表示データに基づき、データドライバ30及びゲートドライバ32によりLCDパネル20に表示させる。

40

## 【0188】

ホスト940は、カメラモジュール910で生成された表示データを変復調部950で変調した後、アンテナ960を介して他の通信装置への送信を指示できる。

## 【0189】

ホスト940は、操作入力部970からの操作情報に基づいて表示データの送受信処理、カメラモジュール910の撮像、LCDパネル20の表示処理を行う。

## 【0190】

50

なお、本発明は上述した実施の形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能である。例えば、本発明は上述の液晶表示パネルの駆動に適用されるものに限らず、エレクトロクミネッセンス、プラズマディスプレイ装置の駆動に適用可能である。

#### 【0191】

また本実施形態では、EEPROMからガンマ補正データを読み込むものとして説明したが、これに限定されるものではなくホストや表示コントローラ等の外部回路からガンマ補正データを読み込むようにしてもよい。

#### 【0192】

また、本発明のうち従属請求項に係る発明においては、従属先の請求項の構成要件の一部を省略する構成とすることもできる。また、本発明の1の独立請求項に係る発明の要部を、他の独立請求項に従属させることもできる。

#### 【図面の簡単な説明】

#### 【0193】

【図1】本実施形態における液晶表示装置の構成の概要を示す図。

【図2】本実施形態における液晶表示装置の他の構成の概要を示す図。

【図3】図1のゲートドライバの構成例を示す図。

【図4】図1のデータドライバの構成例のブロック図。

【図5】図4のFRC回路の構成の概要を示す図。

【図6】図5のFRC回路が出力する6ビットの階調データの説明図。

【図7】図4の基準電圧発生回路、DAC、駆動回路の構成の概要を示す図。

【図8】本実施形態のEEPROMの概要を示す図。

【図9】EEPROMの読み出し制御の一例のタイミング図。

【図10】本実施形態における基準電圧発生回路の構成例のブロック図。

【図11】本実施形態のガンマ補正データの説明図。

【図12】第hの基準電圧選択回路の動作例の説明図。

【図13】ガンマ特性の説明図。

【図14】第hのガンマ補正データレジスタ及び第hのガンマ補正データ設定回路の構成例を示す図。

【図15】図14のガンマ補正データ設定回路の動作例のタイミング図。

【図16】出力すべき基準選択回路の順序が予め決められている場合の出力制御回路の動作例の説明図。

【図17】本実施形態の比較例における第hの基準電圧選択回路の構成例のブロック図。

【図18】本実施形態における第hの基準電圧選択回路の構成例のブロック図。

【図19】図19(A)、図19(B)はスイッチセルが他のスイッチセルに出力するインバブル信号及びディセーブル信号を説明する図。

【図20】図18の基準電圧選択回路の動作例を示す図。

【図21】本実施形態の第hの基準電圧選択回路の具体的な回路構成例を示す図。

【図22】図21の回路図の一部の拡大図。

【図23】図22のスイッチセルの回路構成例を示す図。

【図24】本実施形態の第1の変形例における基準電圧発生回路の構成例のブロック図。

【図25】本実施形態の第2の変形例におけるガンマ補正データ設定回路の構成例のブロック図。

【図26】本実施形態における電子機器の構成例のブロック図。

#### 【符号の説明】

#### 【0194】

10 液晶表示装置、20 LCDパネル、30 データドライバ、

32 ゲートドライバ、38 表示コントローラ、40 シフトレジスタ、

42 レベルシフタ、44 出力バッファ、50 データラッチ、

52 ラインラッチ、54、350 基準電圧発生回路、56、56-1 DAC、50

57-1 反転回路、58、58-1 駆動回路、90 FRC回路、

92 カウンタ、94 排他的論理和回路、100 電源回路、

120 EEPROM、

180-1 ~ 180-J、370-1 ~ 370-J 第1 ~ 第Jの基準電圧出力回路、

182 データ設定レジスタ、184 書き込み制御回路、

186 出力設定レジスタ、188 出力制御回路、

200-1 ~ 200-J 第1 ~ 第Jの選択用電圧発生回路、

210-1 ~ 210-J 第1 ~ 第Jの基準電圧選択回路、

220-1 ~ 220-J 第1 ~ 第Jのガンマ補正データレジスタ、

222、400 ガンマ補正データ設定回路、230 シリアル／パラレル変換回路、10

232、234、238、430 レベルシフタ、236 シフトレジスタ、

360 選択用電圧発生回路、410 アドレス生成回路、

420 アドレスデコーダ、dis ディセーブル信号、

enable イネーブル信号、en1 ~ enJ 出力イネーブル信号、

REG0 ガンマ補正データの第1のビットのデータ、

REG1 ガンマ補正データの第2のビットのデータ、

REG2 ガンマ補正データの第3のビットのデータ

SC1 第1のスイッチセル、SC2 第2のスイッチセル、

SC3 第3のスイッチセル、SC4 第4のスイッチセル、

SW1 第1のスイッチ素子、SW2 第2のスイッチ素子、

SW3 第3のスイッチ素子、SW4 第4のスイッチ素子、

V0 第1の基準電圧、V1 第2の基準電圧、VG0-h 第1の選択用電圧、

VG1-h 第2の選択用電圧、VG2-h 第3の選択用電圧、

WR1 ~ WRJ 書き込みイネーブル信号

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

| 選択用電圧   | ガンマ補正データ | 基準電圧 |

|---------|----------|------|

| VG255-h | REG255=1 | V63  |

| VG254-h | REG254=0 | —    |

| VG253-h | REG253=0 | —    |

| VG252-h | REG252=1 | V62  |

| ⋮       | ⋮        | ⋮    |

| VG3-h   | REG3=0   | —    |

| VG2-h   | REG2=1   | V1   |

| VG1-h   | REG1=1   | V0   |

| VG0-h   | REG0=0   | —    |

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

(A)

(B)

【図20】

| REG2 | REG1 | REG0 | V1    | V0    |

|------|------|------|-------|-------|

| 1    | 1    | 0    | Vc2-h | Vg1-h |

| 1    | 0    | 1    | Vg2-h | Vg0-h |

| 0    | 1    | 1    | Vg1-h | Vg0-h |

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|        |      |         |

|--------|------|---------|

| G 09 G | 3/20 | 6 2 3 F |

| G 09 G | 3/20 | 6 2 3 J |

| G 09 G | 3/20 | 6 3 1 V |

| G 09 G | 3/20 | 6 4 1 E |

| G 09 G | 3/20 | 6 4 1 K |

| G 09 G | 3/20 | 6 4 1 Q |

(72)発明者 森田 晶

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 2H093 NA16 NA51 NA61 NC03 NC09 NC11 NC16 NC22 NC23 NC26

NC29 NC34 ND01 ND03 ND17

5C006 AA14 AA16 AA17 AC21 AF13 AF25 AF44 AF45 AF46 AF51

AF52 AF53 AF71 AF83 AF84 BB16 BC12 BF08 BF14 BF24

BF25 BF43 EB04 FA01 FA18 FA56

5C080 AA10 BB05 DD04 DD28 EE29 FF11 JJ02 JJ04 JJ05