(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2015-516693

(P2015-516693A)

(43) 公表日 平成27年6月11日(2015.6.11)

(51) Int.Cl.

F 1

テーマコード (参考)

|               |           |        |       |   |

|---------------|-----------|--------|-------|---|

| HO 1 L 25/065 | (2006.01) | HO 1 L | 25/08 | Y |

| HO 1 L 25/07  | (2006.01) | HO 1 L | 23/04 | E |

| HO 1 L 25/18  | (2006.01) | HO 1 L | 23/08 | C |

| HO 1 L 23/04  | (2006.01) |        |       |   |

| HO 1 L 23/08  | (2006.01) |        |       |   |

審査請求 未請求 予備審査請求 未請求 (全 24 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2015-512167 (P2015-512167) |

| (86) (22) 出願日 | 平成25年5月9日 (2013.5.9)         |

| (85) 翻訳文提出日   | 平成26年11月11日 (2014.11.11)     |

| (86) 國際出願番号   | PCT/IB2013/053749            |

| (87) 國際公開番号   | W02013/171636                |

| (87) 國際公開日    | 平成25年11月21日 (2013.11.21)     |

| (31) 優先権主張番号  | 61/648,098                   |

| (32) 優先日      | 平成24年5月17日 (2012.5.17)       |

| (33) 優先権主張国   | 米国 (US)                      |

| (31) 優先権主張番号  | 61/654,888                   |

| (32) 優先日      | 平成24年6月3日 (2012.6.3)         |

| (33) 優先権主張国   | 米国 (US)                      |

| (31) 優先権主張番号  | 61/670,616                   |

| (32) 優先日      | 平成24年7月12日 (2012.7.12)       |

| (33) 優先権主張国   | 米国 (US)                      |

|          |                                                                      |

|----------|----------------------------------------------------------------------|

| (71) 出願人 | 514287812<br>イーガントゥ リミテッド<br>イスラエル国、43000 ラ アナーナ<br>、ハティドハー ストリート 16 |

| (74) 代理人 | 100086461<br>弁理士 斎藤 和則                                               |

| (72) 発明者 | ダクヒヤ、マイケル<br>イスラエル国、62308 テル アヴィ<br>ブ、ワイズマン ストリート 27                 |

| (72) 発明者 | シャークド、エラン<br>イスラエル国、43569 ラ アナーナ<br>、ハナール ストリート 7                    |

最終頁に続く

(54) 【発明の名称】電子集積のための3次元モジュール

## (57) 【要約】

電子モジュール(20, 39, 60, 80, 132, 140, 144)は、空洞(40, 42, 134, 142)を内包する絶縁材料からなる基板(21)を含む。空洞内の第1の導電性接点(44)は空洞内に搭載された少なくとも1つの第1の電子部品(32)と接触するように構成される。前記空洞を取り囲む前記基板の表面上の第2の導電性接点(44)は空洞の上をまたいで搭載される少なくとも1つの第2の電子部品(28, 30)に接触するように構成される。基板内の導電性トレース(36, 48)は第1と第2の導電性接点と電気通信する。

【選択図】図2

FIG. 2

**【特許請求の範囲】****【請求項 1】**

電子モジュールであって、

空洞を内包する絶縁材料からなる基板と；

前記空洞内に搭載された少なくとも 1 つの第 1 の電子部品と接触するように構成された前記空洞内の第 1 の導電性接点と；

前記空洞の上をまたいで搭載される少なくとも 1 つの第 2 の電子部品に接触するように構成される、前記空洞を取り囲む前記基板の表面上の第 2 の導電性接点と；そして

前記第 1 と第 2 の導電性接点と電気通信する前記基板内の導電性トレースと；

を有することを特徴とする、モジュール。

10

**【請求項 2】**

前記導電性接点は、物理的および電気的に前記電子部品の下面上の第 2 の接点パッドに接触するように構成される、前記基板上の第 1 の接点パッドを有する、ことを特徴とする請求項 1 に記載のモジュール。

**【請求項 3】**

前記第 2 の電子部品は、集積回路チップおよびインターポーヴからなる部品のグループから選択される、ことを特徴とする請求項 1 または 2 に記載のモジュール。

**【請求項 4】**

前記少なくとも 1 つの第 1 の電子部品は、さらなる集積回路チップおよびディスクリート部品からなるさらなる部品のグループから選択される、ことを特徴とする請求項 3 に記載のモジュール。

20

**【請求項 5】**

前記導電性トレースは、前記空洞を取り囲む前記基板の表面に直角な方向に前記基板を貫通するビアを有する、ことを特徴とする請求項 1 - 4 のいずれかに記載のモジュール。

**【請求項 6】**

前記ビアは事前設定された格子の上にレイアウトされる、ことを特徴とする請求項 5 に記載のモジュール。

**【請求項 7】**

前記ビアはそれぞれの前記接点に対して事前に設定された 1 組の角度で配置される、ことを特徴とする請求項 5 に記載のモジュール。

30

**【請求項 8】**

少なくとも 1 つの前記ビアは前記第 1 の導電性接点と前記第 2 の導電性接点とを接続するように構成される、ことを特徴とする請求項 5 に記載のモジュール。

**【請求項 9】**

前記基板の外部表面上にプリント回路基板に接触するための複数の接点パッドを有し、ここにおいて少なくとも 1 つの前記ビアは、前記導電性接点の 1 つと前記外部表面上の前記接点パッドの 1 つとを接続するように構成される、ことを特徴とする請求項 5 に記載のモジュール。

**【請求項 10】**

前記導電性トレースは、前記空洞を取り囲む前記基板の表面に平行な 1 つまたはそれ以上の平面に配置される導電線を有する、ことを特徴とする請求項 1 - 9 のいずれかに記載のモジュール。

40

**【請求項 11】**

前記導電線は均一でない厚みを有する、ことを特徴とする請求項 10 に記載のモジュール。

**【請求項 12】**

前記空洞を取り囲む前記基板の表面に直角な前記基板の側面に複数の接点パッドを有し、ここにおいて少なくとも 1 つの前記導電線は、前記導電性接点の 1 つと前記基板の側面の前記接点パッドの 1 つとを接続するように構成される、ことを特徴とする請求項 10 に記載のモジュール。

50

**【請求項 1 3】**

前記導電線は少なくとも、前記空洞の内部表面により画定される第1の平面に配置される第1の線と、前記空洞を取り囲む前記基板の前記表面を含む第2の平面に配置される第2の線と、を有することを特徴とする請求項10に記載のモジュール。

**【請求項 1 4】**

前記基板の外部表面の中または上に埋め込まれた1つまたはそれ以上のディスクリート電子部品を有する、ことを特徴とする請求項1-13のいずれかに記載のモジュール。

**【請求項 1 5】**

前記ディスクリート電子部品は前記部品または前記モジュール全体が事前設定の動作特性に適合するように構成されそしてトリミングされる、ことを特徴とする請求項14に記載のモジュール。

10

**【請求項 1 6】**

前記基板の外部表面の中または上に埋め込まれた前記部品は、抵抗、フラットコンデンサ、櫛歯型コンデンサ、インダクタ、および他のトリミング可能な部品からなる部品グループから選択される、ことを特徴とする請求項14に記載のモジュール。

**【請求項 1 7】**

前記第1の導電性接点が配置される前記空洞は内部空洞であり、ここにおいて、前記第2導電性接点が配置される、前記内部空洞を取り囲む前記基板の表面は内部表面であり、ここにおいて、

20

前記基板は、前記少なくとも1つの第2の電子部品を含み、そして前記基板の外部表面に取り囲まれるように構成される外部空洞を有し、前記外部表面の上に第3の導電性接点が配置され、前記第3の導電性接点は前記外部空洞の上をまたいで搭載される少なくとも1つの第3の電子部品と接触するように構成される、

ことを特徴とする請求項1-16のいずれかに記載のモジュール。

**【請求項 1 8】**

前記空洞は前記基板の第1の側に形成され、そして前記基板は、前記基板の前記第1の側とは反対側の第2の側の上に1つまたはそれ以上の第3の電子部品を搭載するように構成される、ことを特徴とする請求項1-17のいずれかに記載のモジュール。

30

**【請求項 1 9】**

前記基板の前記第1の側に形成された空洞は第1の空洞であり、そして第2の空洞は、前記基板の第2の側に形成され、前記第2の空洞内に搭載される少なくとも1つの前記第3の電子部品を含むように構成される、ことを特徴とする請求項18に記載のモジュール。

**【請求項 2 0】**

前記基板の前記第2の側は、少なくとも別の1つの前記第3の電子部品が前記第2の空洞の上をまたいで搭載されるように構成される、ことを特徴とする請求項19に記載のモジュール。

40

**【請求項 2 1】**

電気的および機械的に結合した少なくとも第1と第2のモジュールを含む電子組立体であって、それぞれの前記モジュールは：

空洞を内包する絶縁材料からなる基板と；

前記空洞内に搭載された少なくとも1つの第1の電子部品と接触するように構成された前記空洞内の第1の導電性接点と；

前記空洞の上をまたいで搭載される少なくとも1つの第2の電子部品に接触するように構成される、前記空洞を取り囲む前記基板の表面上の第2の導電性接点と；そして

前記第1と第2の導電性接点と電気通信する前記基板内の導電性トレースと；

を有する、ことを特徴とする組立体。

**【請求項 2 2】**

少なくとも前記第1と第2のモジュールは前記モジュールの外部表面にそれぞれ接点パッドを有し、前記接点パッドは、前記導電性トレースと接続しそして少なくとも前記第1

50

と第2のモジュール間の電気通信を提供するため前記組立体内で結合されている、ことを特徴とする請求項21に記載の組立体。

【請求項23】

少なくとも前記第1のモジュールは前記組立体内で前記第2のモジュールの上に積み重ねられている、ことを特徴とする請求項21または22に記載の組立体。

【請求項24】

前記第1のモジュールは、前記第1のモジュール内の前記空洞とは反対側の、前記第1のモジュールの基板の下面が、前記第2のモジュール内に形成された前記空洞の上をまたぎそして塞ぐように積み重ねられる、ことを特徴とする請求項23に記載の組立体。

【請求項25】

前記第1のモジュールは、前記第1のモジュール内の前記空洞が前記第2のモジュール内に形成された前記空洞に対面するように積み重ねられる、ことを特徴とする請求項23に記載の組立体。

【請求項26】

前記第1のモジュールは、前記第1のモジュール内の前記空洞を取り囲む前記第1のモジュールの前記基板の前記表面上に直角な、前記第1のモジュールの側面上の接点パッドにより、前記第2のモジュールに接続される、ことを特徴とする請求項23に記載の組立体。

【請求項27】

前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が相互に平行なそれぞれの向きに開口するように、前記第1のモジュールが配向する、ことを特徴とする請求項26に記載の組立体。

【請求項28】

前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が相互に直角なそれぞれの向きに開口するように、前記第1のモジュールが配向する、ことを特徴とする請求項26に記載の組立体。

【請求項29】

絶縁性ベースを有し、ここにおいて少なくとも前記第1と第2のモジュールが前記絶縁ベースの表面上に並んで搭載され、前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が前記表面に直角な向きに開口する、ことを特徴とする請求項21または22に記載の組立体。

【請求項30】

電子モジュールを作成する方法であって、

空洞を内包する絶縁材料からなる基板であって、前記空洞内の第1の導電性接点と、前記空洞を取り囲む前記基板の表面上の第2の導電性接点と、そして前記第1と第2の導電性接点と電気的に通信する前記基板内の導電性トレースと、を有する基板を提供するステップと；

少なくとも1つの第1の電子部品を前記第1の導電性接点と接触して前記空洞内に搭載するステップと；そして

少なくとも1つの第2の電子部品を、前記空洞の上をまたいで前記空洞を取り囲む前記基板の前記表面上に前記第2の導電性接点と接触して搭載するステップと；

を有することを特徴とする方法。

【請求項31】

前記基板を提供するステップは、前記基板上に第1の接点パッドを形成するステップを有し、前記第1の接点パッドは物理的および電気的に前記電子部品の下面上の第2の接点パッドに接触するように構成される、ことを特徴とする請求項30に記載の方法。

【請求項32】

前記第2の電子部品は、集積回路チップおよびインターポーザからなる部品のグループから選択される、ことを特徴とする請求項30または31に記載の方法。

【請求項33】

10

20

30

40

50

前記少なくとも 1 つの第 1 の電子部品はさらなる集積回路チップおよびディスクリート部品からなるさらなる部品のグループから選択される、ことを特徴とする請求項 3 2 に記載の方法。

【請求項 3 4】

前記導電性トレースは、前記空洞を取り囲む前記基板の表面に直角な方向に前記基板を貫通するピアを有する、ことを特徴とする請求項 3 0 - 3 3 のいずれかに記載の方法。

【請求項 3 5】

前記ピアは事前設定された格子の上にレイアウトされる、ことを特徴とする請求項 3 4 に記載の方法。

【請求項 3 6】

前記ピアはそれぞれの前記接点に対して 1 組の事前に設定された角度で配置される、ことを特徴とする請求項 3 4 に記載の方法。

【請求項 3 7】

少なくとも 1 つの前記ピアは前記第 1 の導電性接点と前記第 2 の導電性接点とを接続するように構成される、ことを特徴とする請求項 3 4 に記載の方法。

【請求項 3 8】

前記基板を提供するステップは、前記基板の外部表面上にプリント回路基板に接觸するための複数の接点パッドを形成するステップを有し、ここにおいて少なくとも 1 つの前記ピアは、前記導電性接点の 1 つと前記外部表面上の前記接点パッドの 1 つとを接続するように構成される、ことを特徴とする請求項 3 4 に記載の方法。

【請求項 3 9】

前記導電性トレースは、前記空洞を取り囲む前記基板の表面に平行な 1 つまたはそれ以上の平面に配置される導電線を有する、ことを特徴とする請求項 3 0 - 3 8 のいずれかに記載の方法。

【請求項 4 0】

前記導電線は均一でない厚みを有する、ことを特徴とする請求項 3 9 に記載の方法。

【請求項 4 1】

前記基板を提供するステップは、前記空洞を取り囲む前記基板の表面に直角な前記基板の側面に複数の接点パッドを形成するステップを有し、ここにおいて少なくとも 1 つの前記導電線は、前記導電性接点の 1 つと前記基板の側面上の前記接点パッドの 1 つとを接続するように構成される、ことを特徴とする請求項 3 9 に記載の方法。

【請求項 4 2】

前記導電線は少なくとも、前記空洞の内部表面により画定される第 1 の平面に配置される第 1 の線と、前記空洞を取り囲む前記基板の前記表面を含む第 2 の平面に配置される第 2 の線と、を有することを特徴とする請求項 3 9 に記載の方法。

【請求項 4 3】

前記基板を提供するステップは、前記基板の外部表面の中または上に 1 つまたはそれ以上のディスクリート電子部品を埋め込むステップを有する、ことを特徴とする請求項 3 0 - 4 2 のいずれかに記載の方法。

【請求項 4 4】

前記 1 つまたはそれ以上のディスクリート電子部品を埋め込むステップは、前記部品または前記モジュール全体が事前設定の動作特性に適合するように前記埋め込まれた部品の少なくとも 1 つをトリミングするステップを有する、ことを特徴とする請求項 4 3 に記載の方法。

【請求項 4 5】

前記基板の外部表面の中または上に埋め込まれた前記部品は、抵抗、フラットコンデンサ、櫛歯型コンデンサ、インダクタ、および他のトリミング可能な部品からなる部品グループから選択される、ことを特徴とする請求項 4 3 に記載の方法。

【請求項 4 6】

前記第 1 の導電性接点が配置される前記空洞は内部空洞であり、ここにおいて、前記第

10

20

30

40

50

2導電性接点が配置される、前記内部空洞を取り囲む前記基板の前記表面は内部表面であり、ここにおいて、

前記基板を提供するステップは、前記少なくとも1つの第2の電子部品を含み、そして前記基板の外部表面に取り囲まれるように構成される外部空洞を形成するステップを有し、前記外部表面の上に第3の導電性接点が配置され、前記第3の導電性接点は前記外部空洞の上をまたいで搭載される少なくとも1つの第3の電子部品と接触するように構成される、

ことを特徴とする請求項30-45のいずれかに記載の方法。

【請求項47】

前記空洞は前記基板の第1の側に形成され、そして前記方法は、前記基板の前記第1の側とは反対側の第2の側の上に1つまたはそれ以上の第3の電子部品を搭載するステップを有する、ことを特徴とする請求項30-46のいずれかに記載の方法。

【請求項48】

前記基板の前記第1の側に形成された空洞は第1の空洞であり、そして前記基板を提供するステップは、少なくとも1つの前記第3の電子部品を含むように構成される第2の空洞を前記基板の第2の側に形成するステップを有し、ここに前記第3の電子部品は前記第2の空洞内に搭載されることを特徴とする請求項47に記載の方法。

【請求項49】

前記1つまたはそれ以上の第3の電子部品を搭載するステップは、少なくとも1つの別の前記第3の電子部品を前記第2の空洞の上をまたいで搭載するステップを有する、ことを特徴とする請求項48に記載の方法。

【請求項50】

電子組立体を作成する方法であって、請求項30-49のいずれかの方法に従って作成された、少なくとも第1と第2のモジュールを電気的および機械的に結合させるステップを有する、ことを特徴とする方法。

【請求項51】

前記少なくとも第1と第2のモジュールを結合させるステップは、前記モジュールの外部表面上のそれぞれの接点パッドを使用して少なくとも前記第1と第2のモジュールを結合させるステップを有し、前記接点パッドは、前記導電性トレースと接続し、そして少なくとも前記第1と第2のモジュール間の電気通信を提供するため前記組立体内で結合されている、ことを特徴とする請求項50に記載の方法。

【請求項52】

前記少なくとも前記第1と第2のモジュールを結合させるステップは、少なくとも前記第1のモジュールを前記組立体内の前記第2のモジュールの上に積み重ねるステップを有する、ことを特徴とする請求項50または51に記載の方法。

【請求項53】

前記第1のモジュールは、前記第1のモジュール内の前記空洞と反対側の、前記第1のモジュールの基板の下面が、前記第2のモジュール内に形成された前記空洞の上をまたぎそしてふさぐように積み重ねられる、ことを特徴とする請求項52に記載の方法。

【請求項54】

前記第1のモジュールは、前記第1のモジュール内の空洞が前記第2のモジュール内に形成された空洞に対面するように積み重ねられる、ことを特徴とする請求項52に記載の方法。

【請求項55】

前記少なくとも前記第1のモジュールを前記第2のモジュールの上に積み重ねるステップは、前記第1のモジュール内の前記空洞を取り囲む前記第1のモジュールの基板の表面に直角な、前記第1のモジュールの側面の上の接点パッドにより、前記第1のモジュールを前記第2のモジュールに接続するステップを有する、ことを特徴とする請求項52に記載の方法。

【請求項56】

10

20

30

40

50

前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が相互に平行なそれぞれの向きに開口するように、前記第1のモジュールが配向する、ことを特徴とする請求項55に記載の方法。

【請求項57】

前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が相互に直角なそれぞれの向きに開口するように、前記第1のモジュールが配向する、ことを特徴とする請求項55に記載の方法。

【請求項58】

前記少なくとも第1と第2のモジュールを結合させるステップは、少なくとも前記第1と第2のモジュールを前記絶縁ベースの表面上に並んで搭載するステップを有し、一方で前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞は前記表面上に直角な向きに開口する、ことを特徴とする請求項50または51に記載の方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的に電子回路およびシステムに関し、特にこのような回路およびシステムにおける集積回路および他の部品の組み立てに関するものである。

【0002】

(関連出願の参照)

本出願は2012年5月17日出願の米国暫定特許出願61/648,098(特許文献1)；2012年6月3日出願の米国暫定特許出願61/654,888(特許文献2)；および2012年7月12日出願の米国暫定特許出願61/670,616(特許文献3)の恩恵を主張する。これら全ての暫定出願はここに参照として採り入れられる。

20

【背景技術】

【0003】

現代の電子デバイスは常に増加する数の部品と増加する複雑度を含んでいる。同時に設計者はこれらの部品を常に小型化する最終製品に適合させるように求められている。

これらの矛盾する要求はチップ設計やパッケージに対する高度に集積したアプローチの開発へと導いた。例えばマルチチップモジュール(MCMs)は一般的に単一基板上に多重の集積回路(ICS)または半導体ダイスを含み、場合によってはさらにディスクリート部品を含む。マルチチップモジュール(MCMs)基板はその後プリント回路基板上に単一部品として組み立てられる。いくつかの先進MCMは「チップスタック」パッケージを使用し、その中では半導体ダイスは垂直構造に積み重ねられ、それによりMCM足跡のサイズを減少させている(高さ増加のコストを払って)。この種の設計のいくつかは「システムインパッケージ」とも呼ばれる。

30

【0004】

この種の設計の事例として、米国特許5,905,635(特許文献4)は支持構造による電子モジュールの組み立てについて記載している。各電子モジュールは中間層により分離された少なくとも2つのレベルに積み重ねられた電子部品の形態を有している。各電子モジュールは中間層に形成された少なくとも1つの孔を有し、一方支持構造は連続するモジュールのそれぞれの孔の中に導入される少なくとも1つのロッド要素を有している。

40

【0005】

ICチップは通常MCMまたはプリント回路基板の表面上に搭載されるが、設計によってICは基板の後背に搭載される。例えば、米国特許7,116,557(特許文献5)は埋め込み部品IC組立体について記載しており、そこではIC部品は熱シンクを提供する熱伝導性コア上に配置された積層基板内に埋め込まれる。回路部品はフレキシブルワイヤボンディングなどのフレキシブルな電気的相互配線を介してICに電気的に接続されている。フレキシブルな電気的相互配線および露出したIC組立体の表面の上には電気絶縁性被膜が施された。熱伝導性封入材料が回路部品およびフレキシブルな電気的相互配線を

50

固体または半固体のマトリックス内に収納する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国暫定特許出願61/648,098

【特許文献2】米国暫定特許出願61/654,888

【特許文献3】米国暫定特許出願61/670,616

【特許文献4】米国特許5,905,635

【特許文献5】米国特許7,116,557

【発明の概要】

【0007】

以下に記載される本発明の実施形態は、電子集積のための新規の3次元(3D)設計アプローチを提供する。

従って本発明の1実施形態によれば、空洞を内包する絶縁材料からなる基板を含む電子モジュールが提供される。空洞内の第1の導電性接点は空洞内に搭載された少なくとも1つの第1の電子部品と接触するように構成される。空洞を取り囲む基板の表面上の第2の導電性接点は、空洞の上をまたいで搭載される少なくとも1つの第2の電子部品に接触するように構成される。基板内の導電性トレースは第1と第2の導電性接点と電気通信する。

【0008】

開示された実施形態では、導電性接点は、物理的および電気的に電子部品の下面上の第2の接点パッドに接触するように構成される、基板上の第1の接点パッドを有する。典型的に第2の電子部品は、集積回路チップおよびインターポーラからなる部品のグループから選択され、一方少なくとも1つの第1の電子部品はさらなる集積回路チップおよびディスクリート部品からなるさらなる部品のグループから選択される。

【0009】

ある実施形態では、導電性トレースは、空洞を取り囲む基板の表面に直角な方向に基板を貫通するビアを有する。ビアは事前設定された格子の上にレイアウトされるか、またはビアはそれぞれの接点に対して1組の事前に設定された角度で配置される。一般的に少なくとも1つのビアは第1の導電性接点と第2の導電性接点とを接続するように構成される。さらにあるいは、基板の外部表面上にプリント回路基板に接触するための複数の接点パッドを有し、ここにおいて少なくとも1つのビアは、導電性接点の1つと外部表面上の接点パッドの1つとを接続するように構成される。

【0010】

ある実施形態では導電性トレースは、空洞を取り囲む基板の表面に平行な、1つまたはそれ以上の平面に配置される導電線を有する。導電線は均一でない厚みを有する。空洞を取り囲む基板の表面に直角な、基板の側面に複数の接点パッドを有し、ここにおいて少なくとも1つの導電線は、導電性接点の1つと基板のその側面上の接点パッドの1つとを接続するように構成される。さらにあるいは、導電線は少なくとも、空洞の内部表面により画定される第1の平面に配置される第1の線と、空洞を取り囲む基板の表面を含む第2の平面に配置される第2の線と、を有する。

【0011】

開示された実施形態では、モジュールは基板の外部表面の中または上に埋め込まれた1つまたはそれ以上のディスクリート電子部品を有する。ディスクリート電子部品または前記モジュール全体が事前設定の動作特性に適合するように構成されそしてトリミングされる。一般的に、基板の外部表面の中または上に埋め込まれた部品は、抵抗、フラットコンデンサ、櫛歯型コンデンサおよびインダクタからなる部品グループから選択される。

【0012】

いくつかの実施形態では、第1の導電性接点が配置される空洞は内部空洞であり、ここにおいて、第2導電性接点が配置される、内部空洞を取り囲む基板の表面は内部表面であ

10

20

30

40

50

り、一方基板は、少なくとも1つの第2の電子部品を含み、そして基板の外部表面に取り囲まれるように構成される外部空洞を有し、外部表面の上に第3の導電性接点が配置され、第3の導電性接点は外部空洞の上をまたいで搭載される少なくとも1つの第3の電子部品と接触するように構成される。

【0013】

代替的な実施形態では、空洞は基板の第1の側に形成され、そして基板は、基板の第1の側とは反対側の第2の側の上に1つまたはそれ以上の第3の電子部品を搭載するように構成される。このような1つの実施形態では、基板の第1の側に形成された空洞は第1の空洞であり、そして第2の空洞は、基板の第2の側に形成され、第2の空洞内に搭載される少なくとも1つの第3の電子部品を含むように構成される。基板の第2の側は、少なくとも別の1つの第3の電子部品が第2の空洞の上をまたいで搭載されるように構成されてもよい。

10

【0014】

本発明の1実施形態によれば、電気的および機械的に結合した少なくとも第1と第2のモジュールを含む電子組立体が提供される。それぞれのモジュールは、中に空洞が形成された絶縁材料を含む基板を有する。空洞内の第1の導電性接点は空洞内に搭載された少なくとも1つの第1の電子部品と接触するように構成され、一方空洞を取り囲む基板の表面上の第2の導電性接点は、空洞の上をまたいで搭載される少なくとも1つの第2の電子部品と接触するように構成される。基板内の導電性トレースは第1および第2の導電性接点と電気通信する。

20

【0015】

開示された実施形態では、少なくとも前記第1と第2のモジュールはモジュールの外部表面にそれぞれ接点パッドを有し、接点パッドは、導電性トレースと接続しそして少なくとも第1と第2のモジュール間の電気通信を提供するため組立体内で結合されている。

【0016】

いくつかの実施形態では、少なくとも第1のモジュールは組立体内で第2のモジュールの上に積み重ねられている。第1のモジュールは、第1のモジュール内の空洞とは反対側の第1のモジュールの基板の下面が、第2のモジュール内に形成された空洞の上をまたぎそして塞ぐように積み重ねられる。あるいは第1のモジュールは、第1のモジュール内の空洞が第2のモジュール内に形成された空洞に対面するように積み重ねられる。

30

【0017】

さらにあるいは、第1のモジュールは、第1のモジュール内の空洞を取り囲む第1のモジュールの基板の表面に直角な、第1のモジュールの側面上の接点パッドにより、第2のモジュールに接続される。この場合第1のモジュール内の空洞と第2のモジュール内の空洞が相互に平行または相互に直角なそれぞれの向きに開口するように、第1のモジュールが配向させられてもよい。

40

【0018】

他の1つの実施形態では、組立体は絶縁性ベースを有し、少なくとも第1と第2のモジュールが絶縁ベースの表面上に並んで搭載され、第1のモジュール内の空洞と第2のモジュール内の空洞がその表面に直角な向きに開口する。

40

【0019】

本発明の1実施形態によればさらに電子モジュールを作成する方法が提供される。その方法は、内部に形成された空洞を有し、空洞内の第1の導電性接点と、空洞を取り囲む基板の表面上の第2の導電性接点と、そして第1と第2の導電性接点と電気的に通信する基板内の導電性トレースと、を有する絶縁材料からなる基板を提供するステップを有する。第1の導電性接点と接触する少なくとも1つの第1の電子部品がその空洞内に搭載される。

少なくとも1つの第2の電子部品が、その空洞の上をまたいで、その空洞を取り囲む基板の表面上に、第2の導電性接点と接触して搭載される。

【図面の簡単な説明】

50

## 【0020】

本発明は以下の図面を伴う実施形態の詳細な記載により、より十分に理解されよう。

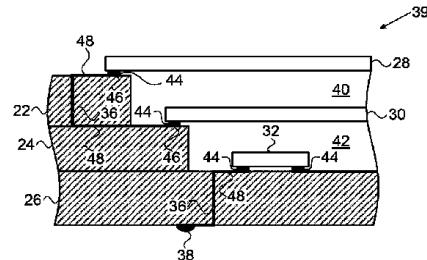

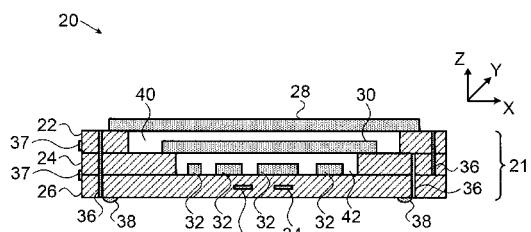

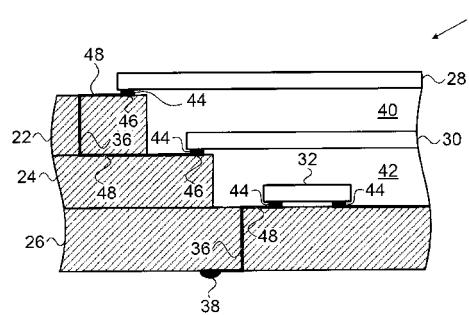

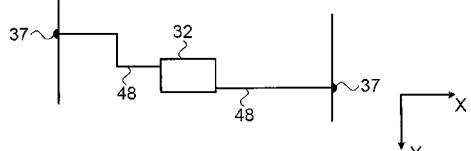

【図1】本発明の1実施形態による多重レベル電子モジュールの図解的断面図である。

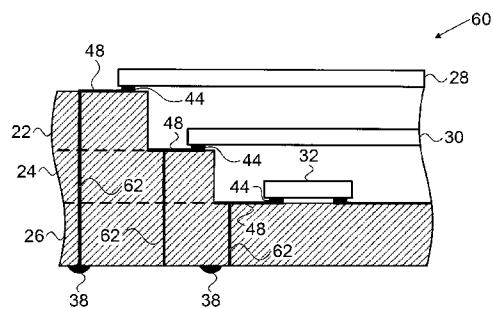

【図2】本発明の1実施形態による多重レベル電子モジュールの図解的詳細図である。

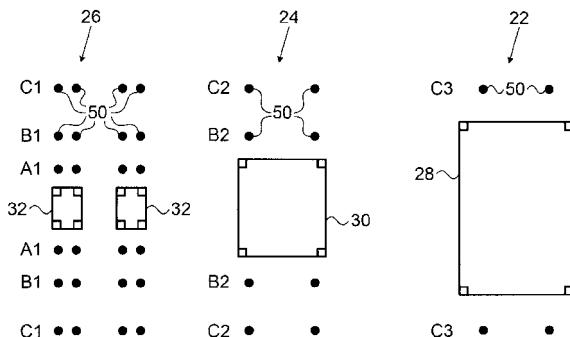

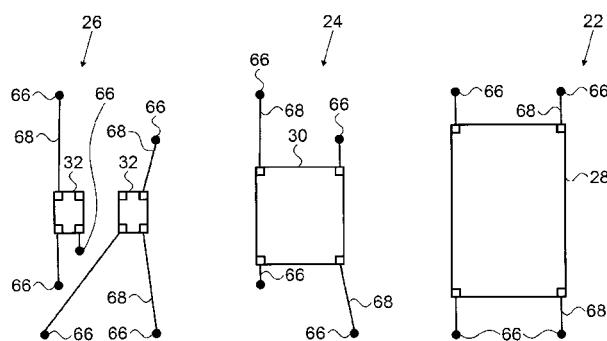

【図3A-C】本発明の1実施形態による多重レベル電子モジュールの連続する層の図解的上面図である。

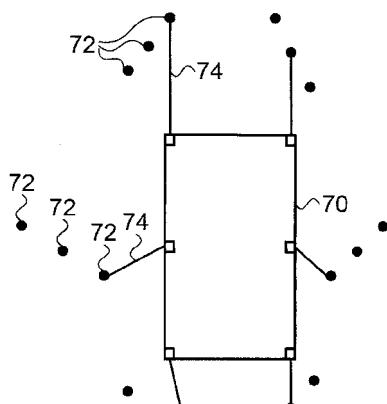

【図4】本発明の1実施形態による多重レベル電子モジュールの1つの層の図解的上面図である。

【図5】本発明の他の1つの実施形態による多重レベル電子モジュールの図解的詳細図である。

【図6A-C】本発明の代替的1実施形態による多重レベル電子モジュールの連続する層の図解的上面図である。

【図7】本発明のさらに別の1実施形態による多重レベル電子モジュールの1つの層の図解的上面図である。

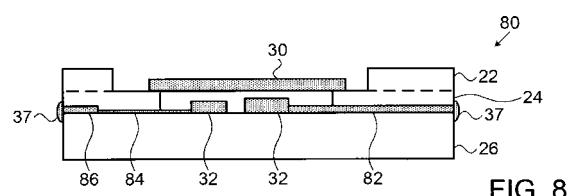

【図8】本発明のさらなる1実施形態による多重レベル電子モジュールの図解的断面図である。

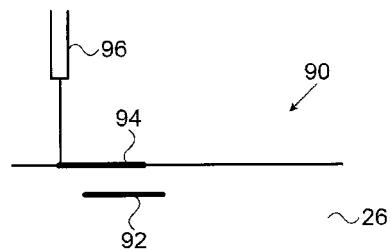

【図9】本発明の1実施形態による多重レベル電子モジュールの図解的断面図であり、埋め込みコンデンサのレーザトリミングを示す。

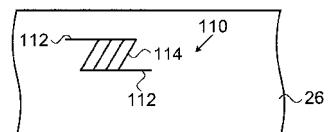

【図10】本発明の1実施形態による多重レベル電子モジュールの1つの層の図解的上面図であり、埋め込み抵抗を示す。

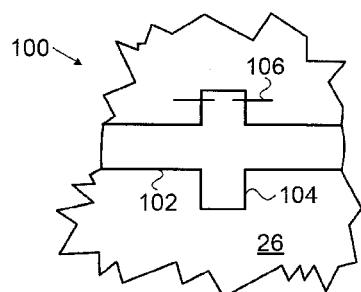

【図11】本発明の1実施形態による多重レベル電子モジュールの図解的断面図であり、埋め込み平面コンデンサを示す。

【図12】本発明の1実施形態による多重レベル電子モジュールの図解的断面図であり、埋め込み櫛歯型コンデンサを示す。

【図13】本発明の1実施形態による多重レベル電子モジュールの1つの層の図解的上面図であり、埋め込みインダクタを示す。

【図14A-C】本発明の代替的実施形態による多重レベル電子モジュールの図解的断面図である。

【図15】本発明の1実施形態による多重レベル電子モジュールの積み重ねの図解的断面図である。

【図16】本発明の1実施形態による、多重の多重レベル電子モジュールからなる組立体の図解的側面図である。

【図17】本発明の代替的実施形態による、多重の多重レベル電子モジュールからなる組立体の図解的側面図である。

【図18】本発明の代替的実施形態による、多重の多重レベル電子モジュールからなる組立体の図解的側面図である。

【図19】本発明の代替的実施形態による、多重の多重レベル電子モジュールからなる組立体の図解的側面図である。

【図20】本発明のさらなる実施形態による、多重の多重レベル電子モジュールからなる組立体の図解的側面図である。

## 【発明を実施するための形態】

## 【0021】

## (概要)

本明細書に記載される本発明の実施形態は新規のタイプの電子モジュールを提供する。それは多重のICチップおよび他の部品（受動ディスクリート部品および微小電気機械部品、光学部品および他の多機能部品を含む）が高い部品密度で3次元（3D）組立体の中に一緒に搭載されることを可能にする。このようなモジュールは異なる制作工程で生産される部品に適したプラットフォームを形成し、そして特殊材料の3D設計の中への組み込みをサポートする。このモジュール設計はまた熱拡散を最適化し、したがってシステムの電力特性を向上させ、一方で集積した相互配線は高いレベルの信頼性を確実にする。本発

10

20

30

40

50

明の実施形態によるモジュールはシステムの性能の最適化および製品の市場までのコストと時間の削減に有用である。

【0022】

開示された実施形態では、電子モジュールは空洞を有する絶縁基板からなる。（1つまたはそれ以上の空洞を有するこのような基板は本明細書では「フレーム」と等価で呼ばれる。）空洞の中の導電性接点は1つまたはそれ以上の電子部品、ディスクリート部品またはIC、が空洞内の基板表面上に搭載することを可能にする。空洞の周囲の基板表面上の追加の導電性接点はICまたはインターポーラのようないつまたはそれ以上の追加の電子部品を空洞の上をまたいで搭載するのに使用されてもよい。空洞は2つまたはそれ以上の入れ子の層を有してもよく、それにより部品が3つまたはそれ以上のレベルに搭載可能である。ディスクリート部品はまた、基板それ自体の内部に埋め込まれてもよい。

10

【0023】

基板内の導電性トレースは基板の表面上の導電性接点（空洞内および空洞周辺の表面上の）に接続する。トレースは部品間の、そして基板の外部表面上の接点パッドへの適切な接続を提供するように所望にレイアウト可能である。これらの外部接点パッドは、モジュールをプリント配線基板上に搭載し、また多重のモジュールを一緒に接続してより大きな組立体にするのに使用できる。

【0024】

本発明の実施形態は以下の設計原則を満たす：

20

- ・異なる機能、材料および生産工程の部品を分離する。

- ・各部品の性能およびコストの最適化。

- ・多機能部品の3D絶縁フレーム上での容易な組立て。

- ・最小の数の信頼できる標準相互配線。

- ・改良された熱拡散と向上した信頼性。

【0025】

開示された実施形態で使用される絶縁フレームは以下の点を含む多くの利点がある：

1. 広範囲の絶縁材料が使用可能であり、それには例えば、積層板およびセラミック（低温同時焼成セラミックス-LTCC）の両方を含む。

2. フレームの生産にコスト効率のよい生産技術が使用可能である。

30

3. フレームが、無線周波数（RF）回路の用途で使用される優れた高周波特性を持つ。

4. フレーム上に部品を組み立てる際に既存組立技術が使用可能である。

5. フレームの開口空洞設計により電子部品のみならず微小電気機械システム（MEMS）および光学部品の使用に適している。

6. 以下の実施例に示されるような異なるサイズの開口空洞により、高い部品密度の真の3D多重層構造を構築するための、底部層の小さな部品からトップ層の大きめのICおよびインターポーラまでのチップの同時搭載が、高コストのチップ埋め込みの必要なく可能である。

7. 接地面がフレームの裏面に形成できる。

40

8. 部品組み立ての後、選択肢としてフレームが既存の技術および材料を使用してカプセル封入されてもよい。

9. 柔軟な設計原則により、各部品（ディスクリート部品およびICを両方含む）が最適な材料および製造技術を使用して生産されることが可能になり、それによりモジュール性能の最適化が可能になる。従って各部品の性能は設計の初期段階で最適化される。内部の、非誘導性接続は部品の高速、低損失の相互配線を可能にする。

10. フレーム設計が高い信頼性をサポートする。各部品は事前試験が可能である。その設計は組み立てられたモジュール全体のトリミングを可能にし、そしてそれによりモジュールの性能を向上させることができる。熱拡散が適切な相互配線および高い熱伝導率の特殊材料を使用して最適化できる。フリップチップまたはチップスケール形状因子のICがコスト効率化および信頼性のために使用可能である。モジュールは前述のようにカプセ

50

ル封入できる。

11. 以下に記載するように、単一のフレームが3D構築ブロックとして機能できる。これらの構築ブロックは大きめの、より複雑な、高ハイアラーキの多次元構造の構築と組立を可能にする。

12. これら実施形態のモジュール性は、コスト、電力経費、機械的応力除去、速度の向上、および試験プログラムの標準化などのシステム特性に関して他の多くの利点を提供する。

#### 【0026】

図1は本発明の1実施形態による多重レベル電子モジュール20の図解的断面図である。モジュールは絶縁基板21の上に構築され、基板21はこの事例では3層、22、24、26からなり、それらは全体としてモジュール20のフレームを画定している。層22、24は中心部が空いており、それにより外部空洞40と入れ子の内部空洞42を含む。モジュール20の特定の幾何学形状は、例示のためであり、他の形状のモジュールは以下の他の図に示される。便宜的に図1は1組のデカルト座標を示し、X軸とY軸は部品が搭載される層22、24および26の表面に平行な横方向に走り、一方Z軸はこれら表面に直角に走る。

#### 【0027】

基板21は任意の適合する電気的絶縁性の材料からなる。例えば、LTCC(セラミック)は優れた熱伝導を提供し、従って部品の冷却を促進し、一方積層は特に多重積層構造を生成するのにコスト効率がよい。あるいは、弾性ポリマーが改良された機械的振動吸収を提供するために使用可能であり、またはシステム要求に基づいて他の適切な既存技術で既知の絶縁材料が使用可能である。

#### 【0028】

電子部品はモジュール20内に3D配列で搭載される。部品32(典型的にはディスクリート部品またはIC)は空洞42内で層26の表面上に搭載される。ICのようなもう1つの部品30は空洞42の上をまたいで空洞を取り囲む層24の表面上に搭載される。(層24、および層22も同様に、対応する空洞42および40をその全ての側面で、または2つまたは3つの側面で取り囲んでもよい。)さらにICまたはインターポーラのような別の1つの部品28は空洞40の上をまたいで層22の表面上に搭載される。(一般的にインターポーラは適合する相互配線を持つ単純なICチップからなる。)モジュール20のICおよびディスクリート部品はフリップチップまたはチップスケールパッケージ内に包含され、またはベアダイスとして組み立てられてもよい。いくつかのディスクリート部品34はまた、下記でさらに記載されるように、基板21内に埋め込まれてもよい。

#### 【0029】

モジュール上または内に搭載された電子部品は、以下の図に示されるように、基板21上または基板を貫通して走る伝導性トレースにより接続される。これらトレースは一般的にビア36を有し、それは例えば図2に示されるように、空洞40と42の内部のまたは周辺の、部品が搭載される表面に直角に(即ち、Z軸方向に)基板21を貫通する。トレースはまた部品搭載面に平行なX-Y平面に配置される導電線を有する。導電性トレースおよび接点は銅に対する標準的銀塩印刷または光化学技術を使用して形成可能であり、さらにあるいはそれらは、他の金属および導電性ポリマーおよび接着剤からなってもよい。

#### 【0030】

モジュール20は基板21の外側表面上の接点パッド37および/または38を使用して、プリント回路基板(PCB)のようなより大きな下方に横たわる基板の上に搭載されるように構成される。あるいは、またはさらに、例えば図15-20に示すように、接点パッド37および/または38はモジュール20を他のモジュールに接続させるのに使用できる。外部接点パッド37および38はボールグリッドアレイ(BGA)、ランドグリッドアレイ(LGA)あるいは表面実装デバイス(SMD)の接点のような任意の適合するタイプでよい。図1に示すように、接点37は空洞40と42の内部のまたは周辺にある部品搭載表面に直角な基板21の側面に位置し、一方接点38は部品搭載表面に平行な

10

20

30

40

50

、基板の底面（またはトップ面 この選択肢は図1には記載されていないが）にある。一般的に接点38はモジュール20内の電子部品にビア36により接続され、一方接点37は例えば図4と図8に示すように、部品搭載表面に平行に走る横方向導電線により接続される。

【0031】

図2は本発明のもう1つの実施形態による多重レベル電子モジュール39の図解的詳細図である。この図はビア36および横方向導電線48および、それらの部品28, 30および32への接続の詳細を示す。前述のように導電線48は一般的に層22, 24および26の表面に沿って走り、そして空洞42の内部表面上（層26の上）と空洞40と42周辺の層22と24の表面上との両方に形成される。ビアと導電線は一般的に低抵抗および低インダクタンスまたはゼロインダクタンスに設計される。

10

【0032】

ビア36と導電線48は基板21の層22, 24および26の表面上に形成された導電性接点パッド46により部品に接続される。接点パッド46は適切な半田付けまたは他の接合技術を使用して部品28, 30および32上の導電性パッド44と物理的および電気的に接触する。従ってこれら部品は、基板の同一レベルまたは異なるレベルのいずれかにある接点パッド46の間に伸長するビア36および導電線48の手段により、部品同士のみならず、モジュール39の外部接点パッド（パッド38のような）に接続される。

20

【0033】

（導電性ビアおよび導電線の設計）

ビアのパターンはそれぞれの特定のモジュールに対して特別に設計されそして生産されるが、しかし類似のパッケージに対し標準ビアパターンを提供することにより設計工程は簡略化でき、生産コストは低減できる。このような標準パターンに対しては使用可能な全てのビアが形成されるが、しかしそれらのいくつかだけがモジュールの電気スキームに依存して導電線で接続される。

30

【0034】

図3A-Cは本発明の1実施形態による、モジュール20のような多重レベル電子モジュールの連続する層26, 24, 22の図解的上面図である。この実施形態では、ビア50はXおよびY方向に沿った事前設定の格子の中にレイアウトされる。実際に使用されるビアの数は部品の数、部品の端末接点の数、および電気的スキームに依存する。

30

【0035】

図3A-Cに示されるスキームでは、部品32, 30および28は概略それらの物理的寸法に従って配置される（底部からトップ方向で最小から最大に）。従ってビア50のパターンは層ごとに異なり、Cと表示されるビア（C1, C2とC3）は3つの層22-24-26全てを貫通し；Bと表示されるビアは層24と26を貫通し；そしてAと表示されるビアは層26のみ、すなわち部品32が搭載される表面とパッド38が位置する底部表面との間を貫通する。従って横方向導電線48のレイアウト（これらの図には図示されない）に依存して、ビア‘C’は任意の層の部品を相互接続し、あるいはこれらの部品を外部接点パッドに接続する。ビア‘B’と‘A’は接続性においてより限定されるが、図示されるモジュールにおいて使用可能なビアの格子は全体として、部品間および外部接続の実質的に任意の所望のパターンを提供するのに使用可能である。

40

【0036】

図4は本発明の1実施形態による多重レベル電子モジュールの1つの層の図解的上面図であり、横方向導電線48を示す。導電線48は図3A-Cのビア50のように、直線構成のパターンでレイアウトされる。図4に示す事例では、導電線48は部品32をモジュールの両側面の接点パッド37に接続する。あるいは、同じ種類の線がビアおよび同一層内の他の部品に接続されてもよい。

【0037】

図5は本発明の他の1つの実施形態による多重レベル電子モジュール60の図解的詳細図である。この図は横方向導電線48およびビア62が、いかに部品28, 30, 32を

50

基板の層 2 6 の底面上の接点パッド 3 8 に接続するかを示す。同じ種類の線およびビアが図 2 に示されたスキームにおいて、そして実質的に任意の他の種類の相互配線シナリオにおいて使用可能である。

【 0 0 3 8 】

図 6 A - C は本発明の代替的 1 実施形態による多重レベル電子モジュールの連続する層 2 6 , 2 4 , 2 2 の図解的上面図である。従前の実施形態と異なり、この設計はビアの固定された配列に基づかず、むしろ必要な場所において適切な層を貫通する特定のビア 6 6 のみを使用し、また横方向導電線 6 8 はこれらビアを部品 2 8 , 3 0 および 3 2 に接続する。このアプローチはより少ない金属を使用し、より大きな設計柔軟性を提供し、いくつかの用途でのモジュール内の部品をより密接に充填できる可能性がある。

10

【 0 0 3 9 】

図 7 は本発明のさらに別の 1 実施形態による多重レベル電子モジュールの 1 つの層の図解的上面図である。この実施形態では、ビア 7 2 は部品 7 0 が搭載される接点に対して 1 組の事前設定の角度で配置される。横方向導電線 7 4 がその後部品接点と実際に使用されるビアの間に形成される。この種の設計アプローチは図 3 A - C に示される格子ベースの設計と図 6 A - C の「自由型」設計の間の有用な妥協を提供するかもしれない。

【 0 0 4 0 】

選択されたレイアウトの種類に関係なく、穿孔と金属メッキは一般的に積層基板内に垂直ビアを形成する最も適切な技術である。穿孔は機械的にまたはレーザにより実行可能であり、その後既知の既存技術を使用して銅メッキされる。ビア信頼性の高い非誘導性接点は一般的に、このようにしてビア直径が 5 0 - 3 5 0 ミクロンの範囲で獲得可能である（これより大きなまたは小さなビアもまた可能であるが）。

20

【 0 0 4 1 】

セラミック基板に対しては圧膜技術が一般的に最も適している。この場合、ビアの開孔は基板の生産に使用されるセラミックグリーンテープの各層の中で機械的に準備される。銀、パラジウム - 銀、または他の金属ペーストのスクリーン印刷がこれら開口部を導電性材料で充満させるのに使用される。セラミックグリーンテープからなる多層構造は、その後一緒に加圧され、そして焼結される。部品を側面の端末と接続するため、厚い導電線（トレース）がビアの代わりにまたはビアと共に使用可能である。

30

【 0 0 4 2 】

図 8 は本発明のさらなる 1 実施形態による多重レベル電子モジュール 8 0 の図解的断面図であり、横方向導電線 8 2 , 8 4 を示す。この図に示すように、部品 3 2 を外部接点パッド 3 7 に接続するため、厚い金属トレースがビアの穿孔の代わりに、またはビアの穿孔と共に使用されてもよい。この種のトレースは垂直ビアに接続する水平断片を形成するため使用されてもよい。

【 0 0 4 3 】

積層基板については、一般的に厚い金属被覆（一般に 1 5 0 - 6 0 0 ミクロンの範囲、しかしそれより大きなおよび小さな厚さも選択肢として使用できる）が、トレース 8 2 , 8 4 を製造するための最も適切な技術である。銅で最大 2 5 0 ミル厚まで、アルミニウムで最大 5 0 0 ミル厚までの金属トレースが当該分野で公知の金属被覆技術を用いて製造できる。このような厚さは、上記で定義された範囲の厚さの、高信頼性で無誘導性のトレースを生成するのに十分以上である。光化学、微小機械、レーザーベース技術などの当技術分野で知られている様々な技術が、（積層フレーム用の）厚い金属のパターニングに使用することができる。

40

【 0 0 4 4 】

横方向導電線 8 2 , 8 4 は、均一または不均一な厚さであってよい。例えば、側面接点 3 7 での横方向導電線 8 4 の終端は、接点 3 7 近くに厚い部分 8 6 を含んでもよい。この厚い部分は、2 5 0 ミクロンの厚さでトレースの終端接触を改善することができる。この種のトレースの可変厚さは、垂直ビアの横方向の接続に対し有用であり得る。最小の金属厚は、信頼性および非誘導性接触、多層構造の製造の容易さ、および費用効率の高い金属パ

50

ターニングを提供するために、他の場所で使用されてもよい。

【0045】

要約すると、3Dモジュールを積層基板で生産する一連のステップは上述したように以下を含むことができる：

1. 個々の層の調製（空洞を含む）。

2. 導電線と接点パッドの必要なパターンを作るための各層に対する金属パターニング。

3. 積み重ね。

4. 垂直ビアの掘削とメッキ。

5. 外部終端の追加。

6. 部品の組み立て。

【0046】

セラミック基板については、（側面接点又はビアに接続する）厚い金属トレースは導電性厚膜ペーストのマルチスクリーン印刷によって構築することができ、それは同時にトレースのパターニングを可能にする。この種のモジュールでは、150-250ミクロンの範囲のトレース厚が一般的に望ましい。

【0047】

要約するとこの場合、セラミック技術では、3Dモジュールの製造における一連のステップは以下のようである：

1. すべての層に対しグリーンセラミックテープの調製（必要な空洞及びビアを有する）- すべての層に対する導電線、ビアおよび接点パッドのスクリーン印刷を含む。

2. 個々の層を押圧し多層構造を形成する。

3. 焼結。

4. 外部端末の追加。

5. 部品の組み立て。

【0048】

新しい3D印刷技術（追加的製造）もまたフレームの製造に適している。この場合、3Dフレームはパッド、導電線およびビア用の導電性材料と残部用の絶縁材料との所望の組み合わせで単に層ごとに印刷される。この製造技術は、複雑なパターンの厚い水平導電性トレースと垂直ビアに対して費用効率がよい。

【0049】

（埋め込み部品の組み込み）

図1で図解されたように、基板21は、抵抗器、コンデンサ、およびインダクタなどの埋め込みコンポーネント34を含んでもよい。このような部品は、実質的に任意の種類の電子モジュールで使用可能であるが、しかしそれらはフィルタ、バラン及び変圧器のような様々なタイプのRF回路やチップの構築に特に有用である。埋め込まれた部品は、部品32（図1）のような基板の実装面の上に配置された他のディスクリート部品と組み合わせて使用することができる。この組み合わせは、フィルタやマルチブレクサのようなより複雑な種類のRF（およびその他の）モジュールの構築を可能にする。

【0050】

埋め込み部品34の特性を向上させ、改良するために追加の技術が使用されてもよい。例えば、レーザトリミングのようなトリミング技術は、生産において部品の数値を微調整するために使用可能である。さらにあるいは、フェライトおよび強誘電体のような特殊な材料が、性能改善のために基板内または外部表面上に埋め込まれた部品に組み込むことができる。これらの選択肢は、以下の図面に示されている。多くの特定の部品は以下に記載されるが、本実施形態によって提供されるトリミングの原理は、このようにして基板の中または上に埋め込むことができる実質的に任意の種類のトリミング可能な部品に適用することができる。

【0051】

図9は、本発明の実施形態による、埋め込みコンデンサ90のレーザトリミングを示す

10

20

30

40

50

、マルチレベル電子モジュールの図解的断面図である。この実施形態の絶縁層26は、それ自体多層構造である。このようにコンデンサ90は、トリミングを可能にするために、層26の1つの内部層の表面に形成された内部導電性プレート92、および層26の上面に形成された外側導電性プレート94を有する。コンデンサ90の特性が測定され、そしてレーザ96が、モジュールの設計周波数で所望の動作特性を与えるための適切な部品の数値に到達するのに十分な材料を、プレート94から除去する。例えば、フィルタおよびマルチプレクサを製造する際には、特定された周波数帯域における挿入損失およびノイズ除去が測定され、そして必要なトリミング値を計算するために電磁界シミュレーションが（当技術分野で知られているように）適用される。同様の技術は他のタイプのモジュールにおいても使用することができる。

10

## 【0052】

図10は、本発明の実施形態による、埋め込み抵抗100を示すマルチレベル電子モジュールの1つの層の図解的上面図である。抵抗100は抵抗パッド104に接続する導電性トレース102を含む。抵抗100の抵抗値はパッドの幅によって決定される。したがって抵抗は、例えばライン106に沿ってパッド104を切断することによって、上述の技術を用いて、トリミングされてもよい。

20

## 【0053】

同様に、抵抗器、インダクタ、および櫛歯型コンデンサがモジュールの層の1つの外部面に形成され、その後、同様の技術によってトリミングされてもよい。例えば、抵抗値とインダクタンス値は導電線を狭くすることによってトリミングすることができ、一方静電容量は、電極の一部を除去することによってトリミングされる。このアプローチは、モジュールの部品が組み立てられた前または後のいずれかにおける、モジュール全体の試験およびトリミングを可能にする。このようなモジュールは自動機器により高度に標準化されたテストプログラムで個別に試験しトリミングすることができる。

30

## 【0054】

さらにあるいは、トリミングが必要とされない場合、埋め込み部品34は、それらに接続する適切な導電性トレースと共に、基板の絶縁層の1つの内に完全に含まれ得る。それでも回路修正は、例えばフレームに搭載されたディスクリート部品32の手段により依然として達成可能である。

## 【0055】

種々の技術がモジュール基板の1つの層内（およびモジュールの絶縁フレーム内の他の層内に、部品表面がその後のトリミング用に利用可能であるかなかろうが、）に部品32を埋め込むために使用できる。基板が積層からなる場合、部品を構成する導体及び他の要素（例えば、強誘電要素及び／又は磁気要素など）は、単に積層プロセスの適切な段階で埋め込むことができる。一方、セラミック基板は一般に、高温焼結を必要とし、それは埋め込み部品に損傷を与える可能性がある。したがってセラミック基板が使用される場合、穴は、その後埋め込み部品を挿入するために、焼結段階で基板中に残してもよい。部品が挿入された後、穴は、選択肢として任意の適切な封入材料で充填されてもよい。

40

## 【0056】

図11は、本発明の実施形態による、埋め込み平坦コンデンサ110を示す多重レベル電子モジュールの図解的断面図である。強誘電体材料114は、基板層26内のコンデンサ電極112の間に埋め込まれている。

## 【0057】

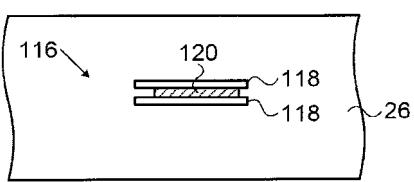

図12は、本発明の別の実施形態による埋め込み櫛歯型コンデンサ116を示す多重レベル電子モジュールの図解的断面図である。この場合、コンデンサの1組のインターリーブされた電極120が1つまたはそれ以上の埋め込み強誘電体層118に沿って、または間に、埋め込まれていてもよい。

## 【0058】

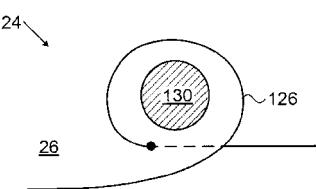

図13は、本発明のさらに別の実施形態による、埋め込まれたインダクタ124を示す多重レベル電子モジュール内の1つの層の図解的上面図である。ここでは、フェライト13

50

0 または他の磁気材料が、インダクタンスを増加させるために、層 2 6 内のインダクタのワイヤコイル 1 2 6 内に埋め込まれている。

【 0 0 5 9 】

(他の代替的フレーム設計および多重フレームモジュール)

図 1 に示され、そしてそれに続くいくつかの図に繰り返されるフレーム外形は、本発明の原理に基づいて形成できる構造を代表しているが、それらは例示のためだけに示され、そして制限するものではない。以下の図では多くのさらなる事例が示される。他の代替的な空洞ベースの、多重レベルのモジュール設計は本明細書を読んだ後の当業者には明白であり、それらは本発明の範囲内にあると見做される。

【 0 0 6 0 】

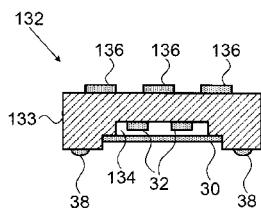

図 1 4 A は本発明の代替的実施形態による多重レベル電子モジュール 1 3 2 の図解的断面図である。ここでは空洞 1 3 4 は基板の一方の側に形成され、そして部品 3 0 と 3 2 はそれぞれ空洞の上をまたいで、そして空洞の中に搭載されている。追加のトレース(不図示)がモジュール 1 3 2 の基板の他方の側、空洞 1 3 4 の反対側に提供され、この反対側にもさらなる部品 1 3 6 の搭載を可能にしている。この実施形態では、接点パッド 3 8 は基板の空洞 1 3 4 と同じ側に形成され(従前の実施形態とは反対側)、それによりモジュール 1 3 2 を P C B または、当該基板に対向する空洞を有する下方の他の基板上に搭載可能にしている。

【 0 0 6 1 】

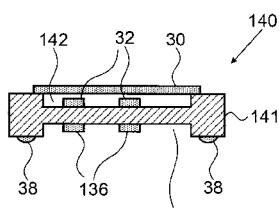

図 1 4 B は本発明のもう 1 つの実施形態による多重レベル電子モジュール 1 4 0 の図解的断面図である。この場合、基板は両側に形成された空洞 1 3 4 と 1 4 2 と、空洞 1 3 4 に沿った接点パッド 3 8 を有する。部品 1 3 6 は空洞 1 3 4 内に搭載され、一方部品 3 0 と 3 2 は空洞 1 4 2 の上をまたいで、そして空洞 1 4 2 の中に搭載される。

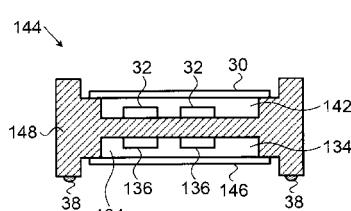

【 0 0 6 2 】

図 1 4 C は本発明の他の 1 つの実施形態による多重レベル電子モジュール 1 4 4 の図解的断面図である。この実施形態はモジュール 1 4 0 に似ているが、しかし空洞 1 3 4 と空洞 1 4 2 の両方の端部の周辺に搭載面をさらに提供し、それにより部品 1 4 6 と 3 0 はそれぞれこれら空洞の上をまたいで搭載可能である。

【 0 0 6 3 】

従前の図は全て単一の基板フレームからなるモジュールを示したが、以下に記載される実施形態では 2 つまたはそれ以上のモジュールが電気的および機械的に接合されて単一の集積電子組立体を形成する。この接合は一般的にモジュールの外部表面上の適切な接点パッドを結合することにより達成される。例えば、基板の任意の側のフリップチップ端末がこの目的に使用できる。このアプローチはフレームを互いに半田付けまたは接着することにより単一のモジュールを複雑な 3 D 構造およびアレイ内に組み込むことを可能にする。これは電子回路のみならず光学的および電子機械的デバイスにも、またある種の「システムインパッケージ」にも有用である。

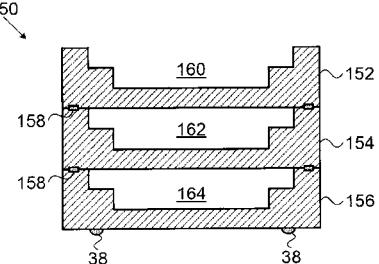

【 0 0 6 4 】

図 1 5 は本発明の 1 実施形態によるこの種の組立体 1 5 0 の図解的断面図である。組立体 1 5 0 は多重レベル電子モジュール 1 5 2 , 1 5 4 , 1 5 6 の積み重ねからなる。これらモジュールは一般的に以前の図に示されたものと類似の内部導電性接点およびトレースを有する。モジュール 1 5 2 , 1 5 4 , 1 5 6 は上方および/または下方表面上のそれぞれの接点パッド 1 5 8 により互いに接続され、接点パッドはそれぞれのモジュール内のトレースに接続し、それによりモジュール間の電気的通信を提供する。

【 0 0 6 5 】

モジュール 1 5 2 , 1 5 4 , 1 5 6 はそれぞれ空洞 1 6 0 , 1 6 2 , 1 6 4 を含む。この実施形態ではモジュールは積み重ねられ、モジュール 1 5 2 の基板の下面(空洞 1 6 0 の反対側)はモジュール 1 5 4 の空洞 1 6 2 を覆いそして囲い込み、一方モジュール 1 5 4 の基板の下面はモジュール 1 5 6 の空洞 1 6 4 を覆いそして囲い込む。

【 0 0 6 6 】

10

20

30

40

50

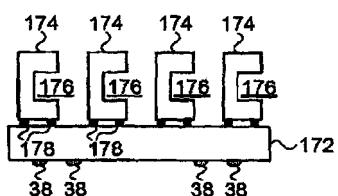

図16は本発明のもう1つ実施形態による、多重の多重レベル電子モジュール174からなる組立体170の図解的側面図である。この実施形態では、それぞれのモジュール174はそれぞれ空洞176を有し、そして空洞を取り囲むモジュール基板の表面に直角なモジュールの側面に接点パッド178を有する。モジュール174はこのように絶縁ベース172の上面の上に並べて搭載される。ベース172それ自体が接点パッド38の手段によりPCBまたは他の基板に搭載されてもよい。この構成は高い部品密度の多重モジュール組立体を形成するのに特に有用である。

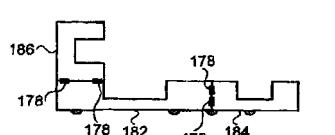

【0067】

図17は本発明の代替的実施形態による、多重の多重レベル電子モジュール182, 184, 186からなる組立体180の図解的側面図である。それぞれのモジュール182, 184, 186はそれぞれの空洞を取り囲むモジュール基板の表面に直角な、モジュールの側面に接点パッド178により、少なくとも1つの他のモジュールに接合されている。この設定はモジュール182と184が1つの方向に接合されることを可能にし、それによりそれぞれの空洞が互いに平行に開口する。一方モジュール182の上面の接点パッドは、モジュール186が、図に示すように、その空洞がモジュール182と184の空洞の開口方向と直交する方向に開口することを可能にする。

【0068】

モジュールの相互接合のための接点パッド配置のこの柔軟性は、組立体が多種多様な形状および構成で形成されることを可能にする。

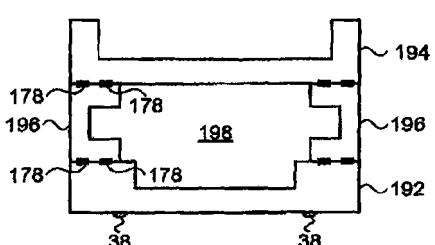

例えば図18は本発明の代替的実施形態による、多重の多重レベル電子モジュール192, 194, 196からなる組立体190の図解的側面図である。この場合、モジュール196は、モジュール196の側面とそれぞれモジュール192と194のそれぞれトップ面と底面にある接点パッド178を使用して、モジュール192と194の間に垂直に搭載される。この配置はモジュールにより囲まれた中央空洞198を画定する。

【0069】

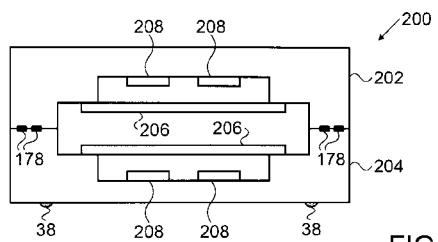

図19は本発明のさらに別の実施形態による、多重の多重レベル電子モジュール202, 204からなる組立体200の図解的側面図である。この場合、モジュール202, 204は、モジュール202の空洞がモジュール204の対応する空洞に面するように積み重ねられる。部品206はモジュール202, 204のそれぞれの空洞の上をまたいで搭載され、一方部品208は内部空洞内に搭載される。モジュールはそれぞれの上面にある接点パッドにより接合される。したがってこの実施形態では上述のタイプの単一のモジュール設計を使用して、組立体が搭載されるPCB上の面積に対しておよそ2倍の部品密度を達成できる。

【0070】

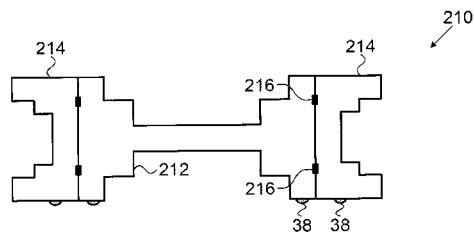

図20は本発明のさらなる実施形態による、多重の多重レベル電子モジュール212, 214からなる組立体210の図解的側面図である。モジュール212は上方および下方空洞を持つ図14Cに似たタイプである。モジュール214はモジュール20(図1)に似た形状を持ち、接点パッド216によりモジュール212の側面に直角構成で接合する。

【0071】

上記の実施形態は事例として引用され、本発明は上記で特に示されそして記載されたものに限定されない。むしろ、本発明の範囲は、本明細書を読んだ当業者に想起される、従来技術にない、上記に記載された種々の特徴の組み合わせおよび準組み合わせの両方を含み、またその変形および修正形を含む、ことを理解されたい。

10

20

30

40

【図1】

FIG. 1

【図2】

FIG. 2

【図3A - C】

FIG. 3A

FIG. 3B

FIG. 3C

【図4】

FIG. 4

【図5】

FIG. 5

【図7】

FIG. 7

【図6A - C】

FIG. 6A

FIG. 6B

FIG. 6C

【図8】

FIG. 8

【図 9】

FIG. 9

【図 11】

FIG. 11

【図 10】

FIG. 10

【図 12】

FIG. 12

【図 13】

FIG. 13

【図 14 A - C】

FIG. 14A

FIG. 14B

【図 16】

FIG. 16

FIG. 14C

【図 17】

FIG. 17

【図 15】

FIG. 15

【図 18】

FIG. 18

【図19】

FIG. 19

【図20】

FIG. 20

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                       | International application No.<br>PCT/IB2013/053749                |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------|-----------------------|---|---------------------------------------------------------------------------------------|------|---|------------------------------------------------------------------------------|------|---|-----------------------------------------------------------------------------|------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC (2013.01) H01L 21/00<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                       |                                                                   |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC (2013.01) H01L 21/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                       |                                                                   |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                       |                                                                   |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>Databases consulted: PATENTSCOPE, USPTO, Esp@cenet, PamPat database<br>Search terms used: electronic module, cavity, trace, dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                       |                                                                   |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category*</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="text-align: center; padding: 2px;">X</td> <td style="padding: 2px;">US 2012104623 A1 PAGAILA REZA A. et al.<br/>03 Mar 2012 (2012/03/03)<br/>Whole Document</td> <td style="text-align: center; padding: 2px;">1-58</td> </tr> <tr> <td style="text-align: center; padding: 2px;">X</td> <td style="padding: 2px;">US 2009279268 A1 SON KYUNG JOO<br/>12 Nov 2009 (2009/11/12)<br/>Whole document</td> <td style="text-align: center; padding: 2px;">1-58</td> </tr> <tr> <td style="text-align: center; padding: 2px;">A</td> <td style="padding: 2px;">US 2002053727 A1 KIMURA NAOTO<br/>09 May 2002 (2002/05/09)<br/>Whole document</td> <td style="text-align: center; padding: 2px;">1-58</td> </tr> </tbody> </table> |                                                                                       |                                                                   | Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | X | US 2012104623 A1 PAGAILA REZA A. et al.<br>03 Mar 2012 (2012/03/03)<br>Whole Document | 1-58 | X | US 2009279268 A1 SON KYUNG JOO<br>12 Nov 2009 (2009/11/12)<br>Whole document | 1-58 | A | US 2002053727 A1 KIMURA NAOTO<br>09 May 2002 (2002/05/09)<br>Whole document | 1-58 |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Citation of document, with indication, where appropriate, of the relevant passages    | Relevant to claim No.                                             |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 2012104623 A1 PAGAILA REZA A. et al.<br>03 Mar 2012 (2012/03/03)<br>Whole Document | 1-58                                                              |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 2009279268 A1 SON KYUNG JOO<br>12 Nov 2009 (2009/11/12)<br>Whole document          | 1-58                                                              |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 2002053727 A1 KIMURA NAOTO<br>09 May 2002 (2002/05/09)<br>Whole document           | 1-58                                                              |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input checked="" type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |                                                                   |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                       |                                                                   |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| Date of the actual completion of the international search<br>11 Sep 2013                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                       | Date of mailing of the international search report<br>11 Sep 2013 |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

| Name and mailing address of the ISA:<br>Israel Patent Office<br>Technology Park, Bldg.5, Malcha, Jerusalem, 9695101, Israel<br>Facsimile No. 972-2-5651616                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                       | Authorized officer<br>DAVIDI Ariel<br>Telephone No. 972-2-5651727 |           |                                                                                    |                       |   |                                                                                       |      |   |                                                                              |      |   |                                                                             |      |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No.

PCT/IB2013/053749

| Patent document cited search report | Publication date | Patent family member(s) |    | Publication Date |

|-------------------------------------|------------------|-------------------------|----|------------------|

| US 2012104623 A1                    | 03 Mar 2012      | US 2012104623           | A1 | 03 May 2012      |

| US 2009279268 A1                    | 12 Nov 2009      | CN 101421834            | A  | 29 Apr 2009      |

|                                     |                  | CN 101421834            | B  | 28 Mar 2012      |

|                                     |                  | KR 20070101579          | A  | 17 Oct 2007      |

|                                     |                  | US 2009279268           | A1 | 12 Nov 2009      |

|                                     |                  | WO 2007117097           | A1 | 18 Oct 2007      |

| US 2002053727 A1                    | 09 May 2002      | JP 2002076252           | A  | 15 Mar 2002      |

|                                     |                  | KR 20020018058          | A  | 07 Mar 2002      |

|                                     |                  | US 2002053727           | A1 | 09 May 2002      |

|                                     |                  | US 6600221              | B2 | 29 Jul 2003      |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LA,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC