(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.<sup>6</sup>

H01L 27/108

(45) 공고일자 1999년08월02일

(11) 등록번호 10-0214915

(24) 등록일자 1999년05월20일

(21) 출원번호 10-1996-0038200

(65) 공개번호 특 1997-0024220

(22) 출원일자 1996년09월04일

(43) 공개일자 1997년05월30일

(30) 우선권주장 8/540,387 1995년10월06일 미국(US)

(73) 특허권자 인터내셔널 비지네스 머신즈 코포레이션 포만 제프리 엘

미국 10504 뉴욕주 아몬크

(72) 발명자 크로닌 존 애드워드

미국 버몬트주 05468 밀頓 로드 #3 박스 3254

데브로제 존 케네스

미국 버몬트주 05401 버링تون 품 애비뉴 59

횡 원

미국 코넥티컷주 06850 놀워크 #제이 4 베드포드 애비뉴 11

(74) 대리인 김영, 김창세, 장성구

**심사관 : 신양환****(54) 반도체 구조체와 동적 랜덤 액세스 메모리 장치와 전기적 절연 방법 및 반도체 구조체 준비 방법****요약**

서로간에 겹쳐서 위치된 전도체를 전기적으로 절연하는 개선된 방법이 개시된다. 이들 전도체는, 예를 들면 고밀도 반도체 구조체에서, 복수의 전도 소자를 제조하는데 사용되는 다소 불명확한 패터닝 및 에칭 단계 때문에, 보통 서로 접촉되게 된다. 본 발명의 방법은 하위 전도체의 상위 표면에 흙을 형성하여 옥사이드형 재료로 적어도 부분적으로 흙을 채우는 단계를 포함한다. 이 방법은 적층 캐퍼시터 셀 (stacked capacitor cell)을 구성하는데 있어 특히 유용하다. 이 기법을 사용하여 준비된 셀이 또한 본 발명의 일부를 형성한다.

**대표도****명세서****도면의 간단한 설명**

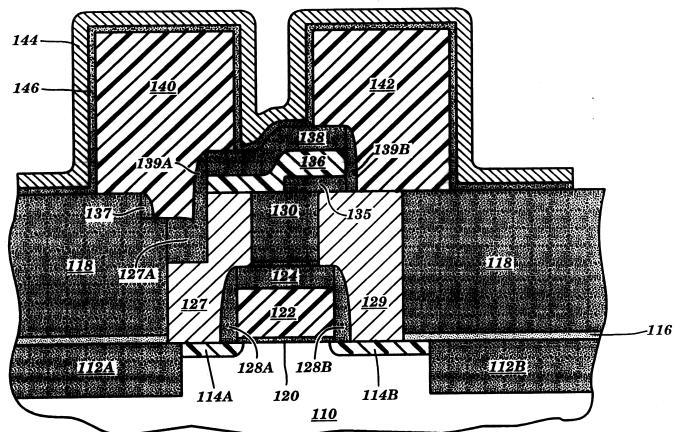

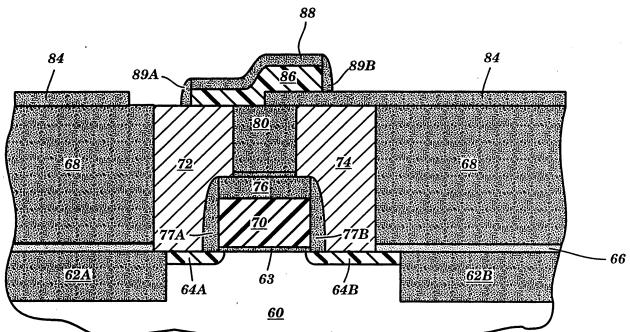

제1도는 비트-라인 스터드와 저장 캐퍼시터 노드간의 오버랩을 방지하기 위한 단계들이 취해지지 않은 경우의 적층 캐퍼시터 셀에 대한 단면도 .

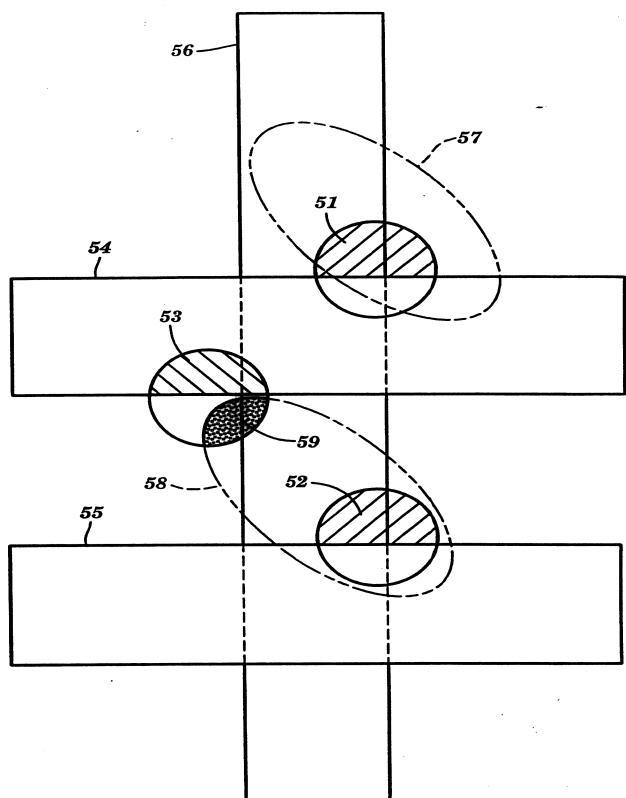

제2도는 적층 캐퍼시터 셀에 있어서 저장 캐퍼시터 노드와 비트-라인 스터드간의 잠재적인 오버랩 영역을 묘사하는 그래픽 평면도 .

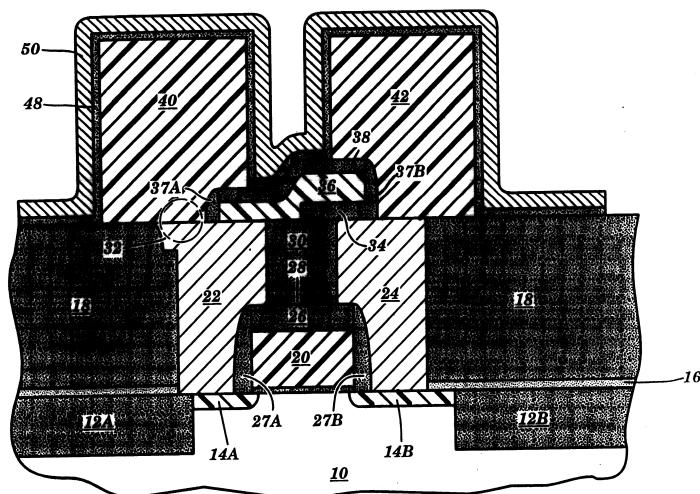

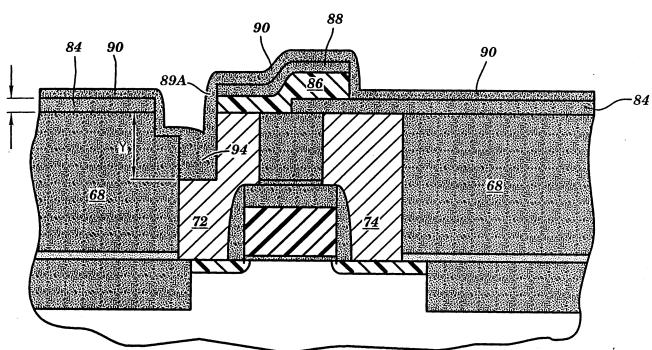

제3도는 예비적 준비 단계에 있어서, 본 발명에 근거한 적층 캐퍼시터 셀을 묘사한 도면 .

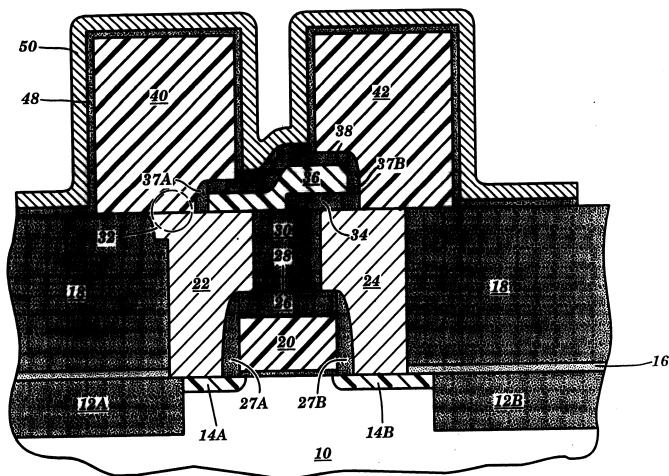

제4도는 본 발명에 근거하여, 계속해서 준비 단계중에 있는 도3의 적층 캐패시터 셀을 묘사한 도면.

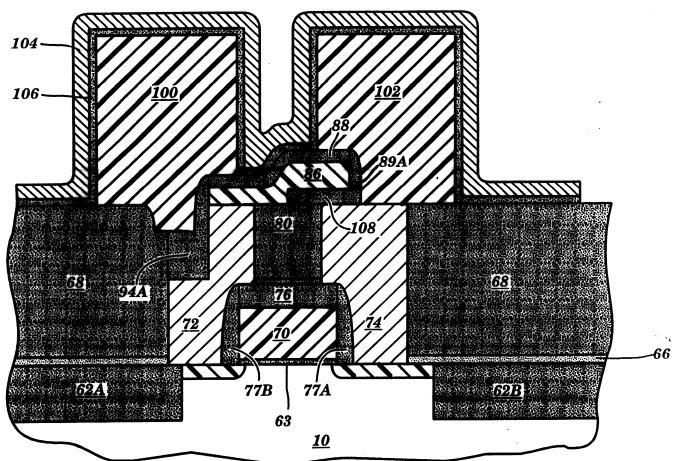

제5도는 본 발명에 근거한 완전한 적층 캐패시터 셀을 묘사한 도면.

제6도는 본 발명에 근거한 적층 캐패시터 셀에 대한 다른 실시예를 묘사한 도면.

#### \* 도면의 주요부분에 대한 부호의 설명

|                      |                        |

|----------------------|------------------------|

| 10 : 실리콘 기판          | 12A, 12B : 트렌치 옥사이드 영역 |

| 14A, 14B : 불순물 확산 영역 | 16 : 에칭 억제 층           |

| 18 : 절연 영역           | 20 : 워드 라인             |

| 24 : 캐패시터 스터드        | 26 : 절연 캡 층            |

| 28 : 옥사이드 층          | 30 : 절연 영역의 일부         |

| 34 : 스터드 차별 층        | 36 : 비트-라인             |

| 38 : 비트-라인 캡 층       | 40, 42 : 저장 캐패시터 노드    |

| 48 : 노드 유전체 층        | 50 : 전도 층              |

#### 발명의 상세한 설명

##### 발명의 목적

##### 발명이 속하는 기술분야 및 그 분야의 종래기술

본 발명은 전반적으로 반도체 장치, 더욱 상세히 설명하면, 서로 근접한채 불연속적인 전기적 절연 영역 및 전기적 접촉을 요구하는 고 집적 복수-레벨 장치(hightly integrated multi-level devices)에 관한 것이다.

반도체 장치의 집적 밀도는 단기간에 4배씩 증가해 왔다. 이러한 성과는 공정에 요구되는 기본 규칙에 따라, 장치 크기를 최소화하므로써 수행되었다. 전기 스터드(studs), 절연 트렌치(isolation trenches) 및, 와이어링 패턴과 같은 전형적인 장치 내 또는 장치 상의 일반적 요소들은 서로 비정상적으로 근접한 채 위치되어야만 했다.

전도 소자가 극도로 근접하면 소자가 서로 절연되도록 설계되는 경우 심각한 문제를 야기할 수도 있다. 예기치 않은 접촉은 반도체 장치의 고장 및 전기 단락으로 이어질 수 있다. 각 레벨이 여러 전도 소자를 포함하는 복수-레벨 장치에 있어서, 이러한 문제는 특히 어려울 수 있다. 예를 들면, 주어진 장치에서, 하위 레벨상의 전도 소자중 몇몇이 인접 상위 레벨상의 전도 소자와 접촉하도록 설계되는 반면, 다른 하위 레벨 전도 소자는 공교롭게 그들 바로위에 위치된 상위 레벨 소자로부터 절연된 채 다른 기능을 수행하여야 한다. 그러나, 장치를 준비하는 데 있어, 종래의 패터닝 및 에칭 단계(예를 들면, 방향성 리액티브 이온 에칭(reactive ion etching; RIE)는, 서로 접촉하도록 설계된 소자들과, 매개된 절연층에 의해 분리될 필요가 있는 소자들을 구별하지 못할 수 있다. 물론, 여러 마스킹 단계가 채택되어, 하나의 특정 전도 소자가 다른 전도 소자에 바람직하지 않게 노출되는 것을 방지할 수도 있다. 그러나 마스킹 및 패턴 단계의 수가 증가하면 자주 전반적인 장치 제조 공정의 복잡성이 증가한다. 따라서 제조 생산성이 줄어들고 전반적인 비용이 증가할 수 있다.

이러한 문제에 영향을 받기 쉬운 반도체 구조의 일례로서 동적 랜덤 액세스 메모리(dynamic random access memory; DRAM)장치가 있다. 고 밀도 DRAM은 종종 엄청난 저장 용량을 제공하는 적층 캐패시터(stacked capacitor; STC) 셀을 활용한다. STC 기법의 몇몇 형태를 활용하는 DRAM 장치에 대한 설명이 <sup>2</sup>와이 카와모토등(Y. Kawamoto et al)에 의한 A 1.28um bit-Line Shielded Memory Cell Technology for 64Mb DRAMs 1990 Syposium on VLSI Technology, page 13-14이라는 명칭의 기사에서 뿐 아니라 미합중국 특히 제5,196,910호 및 제5,140,389호에서 발견된다. 랜덤 액세스 메모리에 활용되는 STC 셀의 일반적인 설계 및 기능이 당 기술분야에서 알려져 있다. 이들 셀은 64Mb 클래스의 고속, 저전력 DRAM의 설계에서 핵심적인 소자가 된다.

상기 언급된 카와모토(Kawamoto)에 의한 기사는 이러한 저장 캐패시터(원통형 노드 또는 침니(chimney))가 비트 라인 위에 형성되는 비트-라인 차폐된 STC 셀을 기술한다. 이 셀은 또한 메모리에 대해 필수적인 다른 기능적 터미널, 즉 워드 라인을 포함한다. 이 기사는 또한 저장 셀 공정 방법에 대한 설명을 포함한다.

전형적인 STC 셀의 예가 도1에서 제공된다. 비록 이 STC 셀의 예가 비트-라인 스터드와 캐패시터 스터드를 활용하지만, 이 도면의 많은 요소들이 카와모토에 의한 기사의 장치의 요소들과 유사하다. 스터드를 사용하면 보다 조밀하고 보다 집적된 셀을 형성할 수 있다. 이러한 셀은 자주 보다 낮은 비트-라인 및 워드 라인 캐패시터스로 기능할 수 있으며, 이러한 것은 대개의 경우 매우 바람직하다. 또한, 스터드-구조 타입의 셀을 형성하는데 관여하는 전반적인 프로세스가 보다 편평한 중간 표면(즉, 형성된 대로의 표면)을 활용한다. 반면에 카와모토에 의한 기사에서 기술된 유형의 셀은 덜 편평한, 즉, 보다 컨포멀(conformal)한 중간표면을 포함한다. 보다 편평할수록 포토리소그래픽(photolithographic) 단계 동안 프린팅 기구의 포커싱을 더욱 쉽게 한다.

이러한 셀을 형성하기 위한 대부분의 기법이 도 3내지 도 6을 참조하여 본 발명에 근거한 상세한 설명에서 보다 더 기술될 것이다. 도 1을 참조하면, 이러한 유형의 셀은 통상적으로 얕은 트렌치 옥사이드(shallow trench oxide; STI) 영역(12A,12B)이 형성된 실리콘 기판(10) 상에 배치된다. 불순물 확산 영

역(14A, 14B)은 STI영역에 인접해 있다.

에칭 억제 층(etch stop layer)(16)이 대개 STI 영역 위에 형성되고, 절연 영역(18)이 층(16) 위에 형성된다. (이하 기술되는 바와 같이 형성될)워드 라인(20)은 절연 캡 층(insulating cap layer)(26)과 캡 층 스페이서(cap layer spacer)(27A, 27B)에 의해 둘러싸여 있다. 비트-라인 스터드(22)와 캐패시터 스터드(24)는 영역(18)내에 위치되어 옥사이드 층(28)과 절연 영역(18)의 일부(30)에 의해 분리된다. 이 스터드는 모두 전도 재료로 만들어 진다. 스터드 차별 층(stud differentiation layer)(34)은 절연 영역(18)의 노출된 표면의 일부상에 침착되거나 형성된다. 비트-라인(36)은 아래에 기술되는 바와 같이 형성될 수 있으며, 비트-라인 스터드(22)의 상위 표면의 일부와 접촉한다. 비트-라인은 대개 절연 비트-라인 캡 층(38)에 의해 커버된다.

저장 캐패시터 노드(40, 42)는 STC내에서 주 저장 소자를 구성한다. 이는 카와모토에 의한 기사에 기술된 것과 같은, 다양한 기법으로 준비될 수 있다. 이 노드는 대개 플리실리콘과 같은 재료로 형성되며 노드 유전체 층(48)에 의해 둘러싸여 있다. 전도 플레이트 또는 층(50)이 각각의 노드를 커버한다.

이와 같은 고 집적 장치에서는, 전도 소자가 서로 매우 밀착되지만 매우 상이한 기능을 수행할 수도 있으며, 동일 장치의 매우 상이한 부분 또는 집적 회로내의 다른 장치에 사실상 독립적으로 접속될 수 있다. 따라서, 이러한 근접성에도 불구하고, 때때로 두 소자간의 전기적 접촉이 방지되어 결과적으로 이 장치의 고장 및 단락이 방지되어야 한다.

특정 실례로서, 도 1의 STC 셀과 같은 몇가지 타입의 STC 셀은 보다 적절한 동작을 위해 저장 노드(42)와 캐패시터 스터드(24)간의 접촉을 필요로 한다. 그러나, 동시에, 이러한 타입의 셀은 저장 노드(40)가 비트-라인 스터드(22)로부터 분리, 즉, 전기적으로 절연될 것을 필요로 한다. (노드(40)는 셀내의 전적으로 상이한 형상부 또는 상이한 장치에 전기적으로 접속될 수도 있다).

고 집적 STC 셀내에서 인접한 전도체를 상호간에 전기적으로 절연된 상태로 유지하는 것은 이러한 셀을 생산하는데 요구되는 단계 때문에 매우 어려운 일이 된다. 도 1의 예에서, 워드 라인(20), 캡 층(26) 및 스터드(22, 24)가 별개의 통상적인 단계에 의해 절연 영역(18)내에서 형성된다. 스터드들은 실질적으로 동일 평면상에 있다. 이러한 모든 형상부에 요구되는 구멍(opening)은 대개, 적당한 포토레지스트 층(도시되지 않음)을 도포한 후 이 포토레지스트를 패터닝하여 구멍의 크기를 한정하므로써 준비된다.

한정된 지역은, 예를 들면 리액티브 이온 에칭(RIE) 기법을 이용하여 방향성을 가지고 예칭된다. 동일 유형의 과정이 비트-라인(36)을 형성하는데 사용된다. 비트-라인(36)은, 초기에는 절연 영역(18) 위의 연속적인 층이었던, 스터드-차별 층(34)에 의해 캐패시터 스터드(24)로부터 절연된다. 비트-라인(36)은 스페이서(37A, 37B)와 캡 옥사이드 층(38)에 의해 후속형성된 저장 캐패시터 노드(40, 42)로부터 절연된다. 저장 노드는 대개, 카와모토의 기사에서 설명된 바와 같은 기법으로, 동시에 형성된다. 스터드의 경우에서와 같이 원하는 크기의 노드를 원하는 위치에 형성하는 것은 대개 적절한 위치에 도포된 레지스트를 정확히 패터닝한후 이 한정된 패턴을 예칭할 것을 필요로 한다.

그러나, 노드 형성에 포함된 단계는 노드(40)와 비트-라인 스터드(22) 사이의 바람직하지 못한 오버랩으로 이어질 수 있다. 스터드 차별 층(34)이 먼저 예칭되어 비트-라인(36)을 비트-라인 스터드(22)에는 접촉시키지만 캐패시터 스터드(24)에는 접촉시키지 않도록 하는 경우, 이러한 정렬이 보다 멀 정확할 수도 있다. 이것은 스터드(22)의 상위 표면 일부를 노출시킨 채 내버려두어, 결과적으로, 노드(40)와 비트-라인 스터드(22)(영역(32) 참조) 사이에 바람직하지 않은 접촉을 초래한다. 상기 언급된 바와 같이, 이러한 접촉은, 극히 작은 경우라도, 전기적 단락을 야기할 수 있다.

현재의 포토리소그래피적 이미징 기법을 사용하여 다수의 밀착-위치된 형상부를 정의하는 경우, 이 기법은 기판상의 패턴에 대해 주어진 마스크를 정렬하는데 있어서 일정한 최소 허용오차(tolerance)를 필요로 하기 때문에, 오버랩 문제의 제거는 일반적으로 가능하지 않다. 사실상, 고 밀도 집적에 대한 지나친 강조가 이러한 오버랩 문제를 더욱 심각하게 만들었다.

도 2는 포토리소그래피적 이미징의 여러 순차적 단계가 수행됨에 따라 STC 셀의 평면 표면상(및 셀 자체내)의 여러 영역간에 발생하는 잠재적인 바람직하지 못한 오버랩을 단순화한 도면이다. 이 도면은 구조체의 상부로부터 취해진 평면도이며, 캐패시터 스터드(52), 비트-라인 스터드(53), 제1비트-라인(54), 제2비트-라인(55), 워드 라인(56), 제1캐패시터 노드(57) 및, 제2캐패시터 노드(58)의 상대적 위치를 포함한다. 간단히 설명하면, 이미징 동안 완벽한 정렬을 보장할 수 없기 때문에, 한정된 후 예칭된 영역간에 원치 않는 오버랩이 발생한다. 이러한 오버랩을 나타내는 지역은 영역(59)으로서 표시된다.

### 발명이 이루고자 하는 기술적 과제

상기 지적된 오버랩과 바람직하지 못한 결과를 처리하는 하나의 기법으로, 캐패시터 노드를 형성하기 전에, 비트-라인 스터드(22)(도 1)의 상부 표면상에 특히 도포되고 패턴된 부가의 마스크를 사용한다. 그러나, 상기 지적된 바와 같이, 부가의 마스크를 사용하면 대개 제조 공정상의 비용과 복잡성이 증가한다. 사실상, 이러한 목적을 위해 마스크를 사용하는 것은, 반도체 구조체의 크기가 극도로 감소됨에 따라 현실적으로 불가능하게 되었다.

따라서 공교롭게도 서로 매우 밀착하여 위치되고, 표준 패터닝 및 에칭 기법에 의해 형성되는 전도체를 효율적으로 절연하는 방법에 대한 필요성이 명백하다.

이 방법은, 장치의 밀도를 감소시키거나 리소그래피적 역량의 한계를 초과하지 않으면서도, 적층 캐패시터와 같은 매우 고밀도로 집적된 복수-레벨 장치에 적용 가능하여야 한다.

또한, 이러한 방법으로 준비된 장치는 자신의 수행 능력을 유지하여야 한다. STC 셀의 경우를 예로 들면, 큰 저장 용량이 유지되어야 한다.

### 발명의 구성 및 작용

상기 논의된 필요성은 개선된 반도체 구조체의 발견에 의해 만족되어졌으며, 이 반도체 구조체는 (a) 상위 표면과 하위 표면을 가지며, 절연 영역에 배치된 제1하위 전도체 (b) 상위 표면과 하위 표면을 가지며, 제1하위 전도체로부터 전기적으로 절연되어, 절연 영역 내에 배치된 제2하위 전도체 (c) 적어도 제1하위 전도체의 일부상에 배치되며, 그로부터 전기적으로 절연된 제1상위 전도체 (d) 적어도 제2하위 전도체의 상위 표면의 일부상에 배치되며, 그에 전기적으로 접속된 제2상위 전도체를 포함한다.

이 장치에 있어서, 제1하위 전도체는 자신의 상위 표면 내에 제1상위 전도체에 대해 자기-정렬된 흙(self-aligned recess)을 갖는다. 이 흙은 적어도 부분적으로 절연체로 채워져 있어서, 제1상위 전도체로부터 제1하위 전도체를 전기적으로 절연시킨다.

이러한 타입의 구조체에 근거한 장치의 예로서, 상위 전도체가 저장 캐퍼시터 노드이며, 하위 전도체 중 하나가 비트-라인 스터드이고 다른 하위전도체는 캐퍼시터 스터드인 적층 캐퍼시터 셀이 있다. 본 발명의 독특한 특징은 비트 라인 스터드와 다른 저장 노드와의 전기적 접촉은 억제하지만, 캐퍼시터 스터드와 위에 놓인 저장 노드 사이에 적당한 전기적 접촉을 허용한다는 것이다.

본 발명의 다른 특징은, 제2하위 전도체와 제2상위 전도체가 존재하는 상태에서, 절연 영역 내에 배치된 제1하위 전도체를 제1하위 전도체의 적어도 일부상에 배치된 제1상위 전도체로부터 전기적으로 절연하는 개선된 방법에 근거한다.

이 방법은, 서로로부터 전기적으로 절연되었으나, 서로 극도로 밀착되도록 설계된 소자를 형성하기 위한 복수의 리소그래피적 단계 및 애칭 단계를 포함하는 제조 공정에 있어 특히 유용하다. 이하 기술되는 바와 같이, 이 방법은 하위 전도체 중 하나의 상위 표면내에 자기-정렬된 흙을 형성하여 절연체 재료로 이 흙을 적어도 부분적으로 채우는 것을 포함한다.

본 발명의 다른 특징 및 세부사항은 첨부 도면을 참조하여, 바람직한 실시예에 대한 다음의 실시예로부터 명백해질 것이다.

도 3은, 초기 단계에 있는, 본 발명에 따른 STC 셀을 묘사하는 단면도이다. 도시된 모든 형상부는, 특히 언급되는 경우를 제외하고는, 실질적으로 도 1의 유사 형상부와 기능 및 형태에 있어 동일하다. STC의 준비는, 대부분의 경우, 종래의 기법에 의해 수행될 수 있다. 같은 트렌치 절연(STI) 영역(62A, 62B)이 (대개 그 자체가 실리콘 재료인)기판(60)내의 바람직한 지역내에 제1애칭 트렌치에 의해 준비될 수 있다. 뛰어어, 이 트렌치는 CVD-침착된 실리콘 다이옥사이드와 같은 옥사이드 재료로 채워져 표면에 대해 평탄화될 수 있다.

STI의 특정 세부사항을 다루는 정보는 당 기술분야(예를 들면, 비.데버리(B.Davar i)등에 의한 1988 IEDM 88 Technical Digest, cat. No.88 CH2528-8, p.92-95의 기사 참조)에서 쉽게 이용 가능하다. 그러나, 본 기술분야의 당업자라면 다른 종래의 절연 유형이 STC 베이스에 대해 가능하다는 것을 알 것이다. LOCOS 절연은 이러한 대안적 실시예중 하나이다.

다음에 게이트 옥사이드 층(63)이 대개 기판의 열적 산화에 의해 형성된다. 이 옥사이드 층은 전형적으로 약 50Å 내지 약 200Å 범위내의 두께를 갖는다.

게이트 옥사이드 층의 형성에 뛰어어 워드 라인(70)이 형성된다. 워드 라인은 종종 폴리실리콘으로 제작되지만, 대안적으로, 예를 들면 텅스텐이나 몰리브덴과 같은 내화 금속(refractory metal) 또는, 텅스텐(tungsten), 탄탈륨(tantalum)이나, 몰리브덴(molibdenum)의 디실리사이드(disilicide)와 같은 임의의 종래 재료와 내화 금속의 합금인 다른 재료로 형성될 수도 있다. 워드 라인은, 예를 들면 화학 증착(chemical deposition; CVD), 저온-CVD, 플라즈마-증강 CVD(plasma-enhanced CVD; PECVD), 증발 증착(evaporation) 및 그 유사기법과 같은 임의의 종래 기법에 의해 형성될 수 있다. 워드 라인은 또한, 이하에서 언급되는 바와 같이 트랜지스터 내에서의 그 기능 때문에 게이트 전극 전도체로서 칭해질 수도 있다.

워드 라인(70)의 형성에 뛰어어, 절연 캡 층(76)이 형성된다. 이 층은 노출된 모든 표면을 덮는 블랭킷 재료로서 (예를 들면 CVD에 의해)침착되는 것이 유리하며, 적당한 형상으로 마스크되고 애칭된다. 예를 들어, RIE에 의한 방향성 애칭은 캡 층 스페이서(77A, 77B)를 남긴다. 따라서, 캡 층과 스페이서에 의해 형성된 연속 층이, 구조체의 다른 전도 영역, 예를 들면 이하에서 언급되는 스터드로부터 워드 라인을 절연시킨다.

다음에, 확산 영역(64A, 64B)이 형성된다. 이 영역은 종종 통상적인 금속 옥사이드 반도체 전계 효과 트랜지스터(metal oxide semiconductor field effect transistor; MOSFET)의 소스 및 드레인 소자로서 작용하며, 워드 라인(70)이 게이트로서 작용한다. 확산 영역을 형성하는 기법은 당 기술분야에 알려져 있다. 대개, 적당한 도핑요소(dopant)가 확산 영역이 될 기판의 일부에 이식된다. 도핑요소의 선택은 물론 형성될 장치의 특정 유형에 의존하게 된다. 예를 들면, p-채널 유형의 FET 장치가 요구되는 경우에는 대개 봉소가 도핑요소로서 채택된다. n-채널 유형의 FET 장치가 요구되는 경우에는 대개 비소나 인이 도핑요소이다.

도핑요소를 이식하는 방법은 당 기술분야에서 잘 알려져 있다(예를 들면, 다음의 참고 문헌 Microelectronics, by J. Millman, McGraw-Hill, 1979; Fundamentals of Semiconductor Device, by E.S. Yang, McGraw-Hill, 1978; 및 VLSI Technology, S. M. Sze(Ed.), McGraw-Hill, 1988참조). 이온 이식기(ion implanter)가 실질적인 이식을 위해 전형적으로 채택된다. 니트로젠과 같은 불활성 캐리어 가스는 대개, 예를 들어 디보란(diborane), 포스핀(phosphine) 또는, 아르신(arsine)과 같은 불순물 소스를 형성하는데에 일반적으로 사용된다.

다음에 패시베이션 층(passivation layer)(66)이 도포된다. 이 층은 실리콘 니트라이드(silicon nitride)와 같은 니트라이드-유형의 재료로서, 예를 들면 약 50Å 내지 약 1000Å 정도로 비교적 얇은 것이 바람직하다. 패시베이션 층은 이온 물질이 STI-옥사이드 영역으로 진입하는 것을 방지한다. 패시베이션 층은 또한 애칭 억제물로서 작용한다. 패시베이션 층을 도포하는데에는 CVD 또는 저온 CVD 와 같은

일반적인 방법이 사용될 수 있다.

도 3에 나타낸 바와 같이, 절연 영역(68) 역시 종래의 기법에 의해 침착될 수 있다. 예를 들면, 실레인(silane)과 같은 반응 선도물질(reactive precursor)이나 실리콘 다이옥사이드가 CVD 또는 저온 CVD에 의해 침착될 수도 있다. 침착된 후, 절연 영역(68)은 대개, 본 명세서에서 참고 문헌으로 인용된 미합중국 특허 제5,292,689호, 제5,234,868호, 제4,944,836호 및 제4,910,155호에서 기술되는 화학-기계적 연마(chemical-mechanical polishing; CMP)등에 의해 평탄화될 수 있다. 평탄화될 경우, 영역(68)은, 비록 부분적으로는 STC 셀의 설계 크기에 의존하겠지만, 대개 약 3000 Å 내지 약 15000 Å의 두께를 갖는다.

뒤이어, 비트-라인 스터드(72)와 캐패시터 스터드(74)가 제조된다. 이들은 프로세스 효율성을 위해, 대개 동일 단계 동안 형성된다. 전형적으로, 마스크가 절연 영역(68)을 관통하는 적당한 비아를 형성하는데 사용되며, 그리고 난 후 종래의 에칭 과정에 의해 비아를 패시베이션 층(66)의 깊이로 가져오게 한다. 마스크를 제거한 후, 전도 재료가 침작되어 비아를 동시에 채운다. 전도체는 대개 도핑된 폴리실리콘등의 재료이거나, 몰리브덴, 텅스텐, 플라티늄, 탄탈륨, 디실리사이드 또는 티타늄 디실리사이드같은 내화 금속이나 내화 금속 합금이다.

금속 스터드 등의 형상부를 준비하는 금속화(metalization) 기법이 당 기술분야에 잘 알려져 있으며, 예를 들면 에스.엠.제(S.M.Sze) VLSI Technology, 2nd Edition, 1988, McGraw-Hill Publishing Company에 기술되어 있다. (이 참고문헌의 제9장이 이 주제에 특히 관련되어 있지만, 제(Sze)의 문헌은 그 전체 내용이 전반적으로 이 주제에 관련되어 있으며, 여기서 참고문헌으로 인용되었다). 금속 침착이, 예를 들면 CVD, 스퍼터링, 증착등의 상기 언급된 것과 같은 알려진 기법에 의해 수행될 수 있다. 침착을 위한 특정 설비 및 공정 파라미터의 선택은 과도한 노력 없이도 반도체 공정 분야의 당업자에 의해 결정될 수 있다.

스터드의 특정 크기는 생산되는 특정 STC 셀의 크기등의 다양한 요인에 의존하게 된다. 일반적으로, 각 스터드는 제조되는 특정 세대의 셀 어레이의 최소 특징부 크기에 근사한다. 스터드가 지나치게 길면 캐패시턴스가 너무 크게 되고, 반면 스터드가 지나치게 짧으면 캐패시턴스가 불충분하게 된다. 바람직하기로는 256 메가비트의 DRAM의 STC 셀에 대한 스터드의 길이가 보통 약 3000 Å 내지 약 10,000 Å의 범위내에 있는 반면, 그 폭은 보통 약 2000 Å 내지 약 4000 Å의 범위내에 있게 된다. 스터드(72,74)의 상위 표면은, 예를 들면 상기 언급된 CMP 기법에 의해 보통 평탄화된다.

이어서, 도 3의 스터드 차별 층(84)이 노출된 스터드 표면과 절연 영역(68) 위에 도포되며, 스터드 차별 마스크(도시되지 않음)로 패턴된다. 패턴되는 동안, 이 층은 비트-라인(이하에서 기술됨)이 비트라인 스터드(72)에는 접촉하지만, 캐패시터 스터드(74)에는 접촉하지 않도록 보장한다. 스터드 차별 층(84)은 캐패시터 스터드에 대한 기생 캐패시턴스(parasitic capacitance)를 감소하는데 충분할 정도로 두꺼우면서도 쉽게 에칭할 수 있을 정도로 얇아야 한다. 층(84)의 두께 역시 이하에서 기술되는 캡 옥사이드 층(88)의 두께보다 얇게하여, 스페이서(89A)가 이하 언급될 흠-에칭 단계 동안 약화되어 비트-라인이 노출되는 것을 방지한다. 스터드 차별 층의 두께는 보통, 상기 언급된 DRAM 크기에 대해 약 200 Å 내지 약 1000 Å이다.

층(84)은 대표적으로 실리콘 다이옥사이드(silicon dioxide)로 형성되지만, 대신에 여러 가지 다른 재료, 예를 들면 실리콘 니트라이드(silicon nitride) 또는 실리콘 옥사이드(silicon oxide)와 실리콘 니트라이드의 합성물로 형성될 수도 있다. 이 층은 통상적인 기법, 예를 들면, 몇몇 형태의 CVD에 의해 침착될 수도 있다.

다음에, 도 3의 비트-라인(86)이 형성된다. 실질적으로 전도적인 재료(substantially conductive material)가 비트-라인을 형성하는데 사용된다. 예로서 텅스텐같은 내화 금속 또는 내화 금속-실리사이드 합성물(refractory metal-silicide composite)이 있다. 비트-라인은 대개, 예를 들면, 블랭킷 재료가 전 표면 위에 침착된 후 패턴되어 바람직한 치수로 에칭되는 CVD 기법을 사용함으로써, 컨포멀하게(conformally) 침착된다. STC 셀 내의 비트-라인의 기능 역시 당 기술분야 잘 알려져 있다.

캡 옥사이드 층(88)은, 예를 들면 CVD에 의해 블랭킷모양의 컨포멀한 층을 초기 침착한 후 패터닝하고 적당한 치수로 에칭하므로써 역시 형성된다. 캡 옥사이드 재료로된 블랭킷 층이 실질적으로 기판 표면에 수직한 방향으로 에칭될 때 스페이서(89A,89B)가 형성된다. 캡 옥사이드 층은 상기 비트-라인 위에 순차적으로 세워지게 되는 저장 캐패시터 노드로부터 비트-라인(86)을 절연한다. 다른 절연 재료 또는 재료 합합물이 이용될 수도 있지만 대개는 실리콘 다이옥사이드로 만들어진다.

비트-라인(86)과 캡 옥사이드 층(88)이 패턴되는 동안, 비트-라인 스터드 흠(94)이 의도적으로 형성된다. 이 스터드 흠은 도 4에서 묘사되며, 순차적 단계 후 옥사이드로 채워진다. 흠이 있다는 사실이 본 발명의 주요한 특징이다. 본 기술 분야의 당업자라면 흠을 형성하는데 상이한 방법이 이용가능하며, 특정 기법의 선택이 중요하지 않음을 알 것이다. 예시적으로, 이 흠(또는 트렌치)은 비트-라인(86)과 캡 옥사이드 층(88)을 에칭하는데 사용되는 마스크(도시되지 않음)를 재거하기전에 형성될 수도 있다. 비트-라인 스터드(72)(예를 들면, 상기 언급된 바와 같은 내화 금속 또는 도핑된 폴리실리콘)를 형성하는 물질에 선택적인 부식액으로 과도-에칭(over-etching)하므로써 이 흠을 생성하게 된다.

흡의 깊이(도 4의 Y)는 스터드 차별 층(84)의 두께(도 4의 X)보다 더 커야한다. 이렇게 하므로써, 이하 기술된 비트-라인 스페이서 층과 층(84)이 순차적으로 제거되는 경우, 보호 절연 층이 이 흠내에 남게되는 것이 보장된다. 이러한 절연 층은 순차적인 생산 단계 동안 비트-라인 스터드와 위에 놓인 저장 캐패시터 노드 사이가 바람직하지 않게 접촉하는 것을 방지한다. 바람직한 실시예에서, 이 흠의 깊이는 층(84)의 두께보다 적어도 100% 더 크다.

비트-라인 스터드 흠(94)이 형성된 후, 비트-라인/캡 옥사이드 마스크가 제거되고, 비트-라인 스페이서 층(90)이 노출된 모든 영역 위, 예를 들면 스터드 차별 층(84)과 캡 옥사이드 층(88) 위에 도포된다. 스페이서 층(90)은 보통 옥사이드 재료로 형성되며, CVD 등의 종래 방법에 의해 침착될 수 있다. 스페이서 층은 보통, 앞에서 특정된 예시적인 DRAM 크기에 비해 비교적 얇은데, 예를 들면 약 200 Å 내지 약 1500 Å이다.

이어서 비트-라인 스페이서 층(90)이 RIE 등의 적절한 기법에 의해 방향성(즉, 기판 표면에 수직으로)에 칭된다. 스페이서 층(90)의 남은 부분은 두 가지 기능을 수행한다. 첫째로, 스페이서 층(90)은 비트-라인(86)의 측면을 보호한다. 둘째로, 상기 언급한 바와 같이 스페이서 층(90)은 흄(94)을 채워(또는 부분적으로 채워), 위에 놓인 저장 캐패시터 노드로부터 아래에 놓인 비트-라인 스타드를 절연한다. 따라서, 노드 형성 동안 스타드를 보호하는데 분리 마스크가 사용될 필요가 없다. 유사한 방식으로, 스타드 차별 층(84) 역시 방향성에 칭을 통해 제거되어, 캐패시터 스타드(74)는 노출시키지만, 비트-라인 스타드(72)는 노출시키지 않는다.

본 발명의 몇몇 실시예에서, 상기 기술된 몇 단계에 대해 대안적 시퀀스가 바람직하다. 이 경우에는, 흄을 형성하기 위한 과도-에칭 단계 다음에 상기 기술된 방식으로 스타드 차별 층이 제거된다. 뒤이어 비트-라인 스페이스 층(90)이 침착되며 방향성-에칭에 의해 제거된다. 이러한 대안적 기법에서, 최종-언급된 단계는 스페이서 층의 두께의 제거만을 포함하며, 스페이서 층과 스타드 차별 층 둘다의 두께 제거는 포함하지 않는다. 따라서, 흄-에칭 단계 동안 스페이서(89A)를 부주의하게 약화시켜 비트-라인을 노출시킬 염려가 있다. 층(84)의 두께가 캡 옥사이드 층(88)의 두께보다 얇아야 한다는 필요성 역시 이 대안적 실시예에서는 제거된다. 도 6 및 이에 관련된 설명으로 이 실시예가 명확해 질 것이다.

이제 그 이상의 STC 셀 구성을 위해 매우 바람직한 중간-구조체이 준비되었다. 비트-라인 스타드와 캐패시터 스타드와 마찬가지로, 워드 라인 및 비트-라인이 적소에 위치되어 있으며, 여러 소자들 사이가 적절히 절연되어 있다. 구조체의 표면 또한 실질적으로 평탄화된다. 또한, 비트-라인 스타드가, 옥사이드로 부분적으로 채워지거나 완전히 채워진 자가-정렬된 흄의 존재에 의해 보호되는 반면, 캐패시터 스타드는 종국적으로 위에 놓인 저장 노드에 접속하기 위해 노출된다.

이제 도 5에서 묘사된 저장 캐패시터 노드가 형성될 수 있다. 캐패시터 노드의 형상 및 디자인이 본 발명에서 중요하지 않다는 것을 이해하여야 한다. 이와 같이 잘 알려진 구조는 여러 참고문헌, 예를 들면 본 명세서에서 참고 문헌으로 인용된 미합중국 특허 제5,140,389호에 기술되어 있다. 이와 유사하게, 저장 캐패시터 노드를 형성하기 위한 여러 기법이 당 기술분야에서 잘 알려져 있다.

도 5는 본 발명에 근거한 예시적인 STC 구조체(또는 어레이)를 묘사한다. 이것은 두 개의 저장 캐패시터 노드를 포함한다. 이 노드는 먼저 CVD 등의 종래 기법에 의해 폴리실리콘 재료로 블랭킷 층을 매우 두껍게 침착하므로써 형성될 수 있다. 이어서, 에칭에 의해 블랭킷 층이 각 노드(100, 102)의 최종 크기로 형성된 두 개의 미가공 덩어리(rough chunks)로 패턴된다. 부가의 패터닝 단계가 수행되어 노드를 도 5에서 묘사된 보다-균일한 크기로 만들 수 있다.

이어서, 노드 유전체 재료(106)가 전 어레이 표면 위에 침착된다. 이러한 재료 층은 저장 캐패시터에 필수적인 요소인 것으로 당 기술분야에 알려져 있다. 이것은 실리콘 다이옥사이드, 실리콘 니트라이드, 탄탈륨 옥사이드같은 내화 금속 옥사이드 필름 또는, 합성 재료같은 여러 재료로 형성될 수 있다. 종래의 기법, 예를 들면, CVD, 스퍼터링 또는 스피닝(spinning) 기법의 방식이 이러한 층을 도포하는데 사용될 수 있다. 물론 어느 기법을 선택하는 것이 최선이냐는 것은 침착되는 재료에 부분적으로 의존한다.

몇몇 실시예에 대한 바람직한 유전체 재료로서 실리콘 니트라이드와 실리콘 옥사이드의 합성물이 있다. 이것은, 예를 들면 리액션 챔버(reaction chamber)를 통해 두 성분의 선도물질을 흘려보내므로써, CVD에 의해 단독으로 침착될 수 있다. 이와 달리, 이 층은, 폴리 실리콘과 같이 아래에 놓인 캐패시터 노드를 형성하는 재료의 열적 산화와 함께 니트라이드 재료의 CVD를 행하는 등, CVD 및 다른 프로세스를 결합하므로써 형성될 수도 있다. 이러한 기법은 당 기술분야에서 알려져 있다.

침착 후, 유전체 층(106)이 표준 기법에 의해 패턴되고 에칭되어 통상적으로 캐패시터 노드(100과 102)의 형성에 컨포밀하게 된다. 최종적으로 한정된 바와 같이, 층(106)은, 예를 들면 상기 언급된 DRAM의 크기에 대해 약 50Å 내지 약 500Å 으로서 비교적 얇다.

이어서, 플레이트 전도체 재료가 유전체 층(106) 위에 정합적으로 침착되어 층(104)을 형성하므로써, 사실상 캐패시터 자체의 구조를 완성한다. 플레이트는 내화 금속이나 도핑된 폴리실리콘, 예를 들면, n-도핑된 폴리실리콘 같은 여러 전도 재료로 형성될 수도 있다. 이것은 예를 들면, CVD에 의해 침착된 후 패턴되어 전반적으로 아래에 놓인 유전체 층(106) 표면에 컨포밀하게 될 수 있다. 상기 언급된 DRAM 크기에 대해 플레이트의 두께는 보통 약 500Å 내지 약 3000Å 의 범위내에 있다.

많은 다른 유형의 캐패시터 저장 노드가 본 발명에 활용될 수 있음이 다시 강조되어야 한다. 한 유형이 본 명세서에서 참고문헌으로 인용된 와이. 카와모토 등에 의한 상기 언급된 기사(1990 Symposium on VLSI Technology)에 기술되어 있다. 이 유형의 캐패시터 노드를 제작하는 세부사항은 여기서 다룰 필요가 없다. 간략하게, 비트-라인, 워드 라인 및 위에 놓인 옥사이드 코팅을 포함하는 표준 캐패시터 구조가 묘사된다(카와모토의 구조체에서는 스타드가 사용되지 않는다, 이는 캐패시터 노드가 기판내의 액티브 영역에 직접적으로 접속되기 때문이다).

저장 노드의 역 패턴(reverse pattern)이 스핀-코팅된 폴리아미드 층내에 그려진다. 이어서, 폴리실리콘 층이, 예를 들면 CVD 방식으로 노출 표면상에 침착된다(카와모토의 기사내의 도면이 이러한 제조 시퀀스를 기술하는데 도움이 된다). 이어서, 폴리실리콘 층이, 구조체의 트렌치 영역내의 재보충된 레지스트 마스크를 사용해 에칭되어, 폴리아미드 트렌치 패턴의 측벽 및 하부상에만 폴리실리콘이 남도록 한다. 뒤이어, 이 레지스트 및 폴리아미드 재료는, 애싱(ashing) 등에 의해 제거되며, 탄탈륨 옥사이드(tantalum oxide)같은 절연 재료가 CVD같은 적당한 기법에 의해 노출 표면 위에 침착된다. 이어서, 텅스텐 등의 재료로부터 형성된 전도 플레이트가 절연체 재료 위에 도포되어 STC 셀 구조체를 완성한다.

카와모토의 참고문헌에 기술된 기법의 핵심적 특징은 저장 노드 형성을 위한 희생 층(sacrificial layer)으로서 폴리아미드같은 합성 재료를 사용하는 것이다. 이러한 방온(temperature-resistant) 유형의 폴리머가 폴리실리콘의 CVD 침착에 포함된 열처리를 보장할 수 있다. DRAM 제조 기술분야의 당업자라면, 여전히 일반적인 유형의 STC를 생산하더라도, 매우 다양한 재료, 공정 단계 및, 카와모토 조건이 가능함을 이해할 것이다.

역시 본 발명의 범주내에 있는 다른 대안으로서 U-형상인 캐패시터 노드 구조를 사용하는 것이 있다. 환언하면, 도 5의 구성요소(100, 102)같이 실질적으로 사각형인 캐패시터 노드가, 베이스 영역, 즉 U형 수평부분내에서 서로 접속된 적어도 두 개의 침니 혹은 확장부(extention)를 포함하는 캐패시터 노드로 대체될 수도 있다. 이러한 유형의 노드 형상은 특정 경우, 예를 들면 상당히 큰 저장 용량이 필요한 경우 바람직할 수도 있다. 이 구조는, 표준 제조 기법을 이용하는 도 5에서 상기 기술된 것과 매우 유사할 수도 있다.

노드 구조체가 완전히 형성(도 5참조)된 후, STC셀에 대한 여러 가지 다른 표준 접속이 형성될 수 있다. 예를 들면, 몇 개의 와이어링 레벨이 직접 또는 간접으로 셀 어레이에 접속될 수 있다. 본 기술분야의 당업자라면, 여러 주변 구조에 대한 특정 유형의 접속이 전반적인 DRAM 디자인 뿐 아니라 STC 셀에 대해 의도된 디자인 및 기능에도 의존하게 됨을 이해할 것이다.

도 6은 본 발명에 근거한 STC 셀의 다른 실시예를 나타낸다. 대부분의 형상부는 도 5의 것과 동일하다. 환언하면, 이 대안적 구조는 기판(110), STI 영역(112A, 112B), 소스/드레인 확산 영역(114A, 114B), 패시베이션 층(116), 절연 영역(118), 게이트 옥사이드 층(120), 워드 라인(122), 절연 캡 층(124), 비트-라인 스터드(127), 캐패시터 스터드(129), 절연 영역(118)의 일부(130), 스터드 확산 층의 나머지 부분(135), 비트-라인(136), 캡 옥사이드 층(138), 스페이서(139A, 139B), 제1저장 캐패시터 노드(140), 제2저장 캐패시터 노드(142), 플레이트 전도체(144) 및 노드 유전체 층(146)을 포함한다.

도 6의 STC 구조는 이미 언급된 몇몇 단계의 시퀀스내를 변화시킨 결과이다. 환언하면, 비트-라인 스터드 흄(127A)(이 지점에서 옥사이드 또는 다른 절연 재료도 완전히 또는 부분적으로 채워짐)을 형성하는데 사용된 과도-에칭 단계 다음에, 요소(135)로서 남는 부분인 스터드 차별 층이 제거되었다. 이어서 비트-라인 스페이서 층(도 6의 구조가 완성되자마자 실질적으로 제거됨)이 침착되고 방향성 에칭에 의해 제거되었다.

도 6의 구조와 도 5의 구조에 있어서 차이점은 별로 중요하지 않다. 비트-라인 스페이서 층의 소형 견부(shoulder)(137)가 흄(127A)에 인접한 절연 영역(118)의 일부상에 존재한다. 또한, 비트-라인 캡(138)은 도 5의 유사 형상부, 즉 비트-라인 캡(88)보다 두껍다. 또한, 스페이서(139B)가 도 5에서와 같이, 나머지 스터드 확산 층(135)에서 끝나지 않고, 캐패시터 스터드(129)의 상위 표면에 직접 접촉한다. 그러나, 역시 이 대안적 실시예의 주요한 잇점은 프로세싱에 관련되어 있다. 즉, 이미 언급된 바와 같이, 흄-에칭 단계 동안 스페이서(139A)를 약화(따라서 비트-라인을 노출시킴)시킬 염려가 적다. 비트-라인 스터드 흄은 여전히 그 기능, 즉 위에 놓인 저장 캐패시터 노드(140)로부터 비트-라인 스터드를 절연하는 기능을 수행하도록 위치된다.

본 발명의 응용가능성은 STC로 제한되지 않는다는 것이 명백하다. 따라서, (a) 상위 표면과 하위 표면을 가지며, 절연 영역내에 침착된 제1하위 전도체 (b) 상위 표면과 하위 표면을 가지며, 1하위 전도체로부터 전기적으로 절연되어, 절연 영역내에 침착된 제2하위 전도체 (c) 제1하위 전도체의 상위 표면의 적어도 일부상에 침착되며, 그로부터 전기적으로 절연된 제1상위 전도체 (d) 제2하위 전도체의 상위 표면의 적어도 일부상에 침착되며, 그에 전기적으로 접속된 제2상위 전도체를 포함하는 반도체 구조체의 다른 특징이 지적된다.

이미 언급된 특정 실시예로부터 명백한 바와 같이, 제1하위 전도체는 자신의 상위 표면상에 제1상위 전도체에 대해 자기-정렬된 흄을 갖는다. 이 흄은 절연체로 적어도 부분적으로 채워져 있으므로, 제1상위 전도체로부터 제1하위 전도체를 전기적으로 절연한다. 이러한 절연 구조는, 상기 기술된 바와 같이, 전도체가 리소그래피적 기법에 근거한 패터닝 및 에칭 기법에 의해 형성된 경우 매우 가치가 있다.

본 발명의 바람직한 실시예가 기술되었지만, 여러 변형이 있을 수도 있음이 이해되어야 한다. 다음의 특허청구범위는 본 발명의 사상 및 범주를 벗어나지 않는 이러한 모든 변형을 커버하는 것으로 이해된다.

상기 참조된 모든 특허, 기사 및 문헌은 본 명세서에서 참고문헌으로서 인용된다.

## 발명의 효과

### (57) 청구의 범위

#### 청구항 1

반도체 구조체(semiconductor structure)에 있어서, (a) 상위 표면과 하위 표면을 가지며, 절연 영역에 침착된 제1하위 전도체; (b) 상기 제1하위 전도체로부터 전기적으로 절연되고, 상위 표면과 하위 표면을 가지며, 상기 절연 영역에 침착된 제2하위 전도체; (c) 상기 제1하위 전도체의 적어도 일부상에 침착되며, 그로부터 전기적으로 절연된 제1상위 전도체; (d) 상기 제2하위 전도체의 적어도 일부상에 침착되며, 그에 전기적으로 접속된 제2상위 전도체를 포함하되, 상기 제1하위 전도체는 상기 제1상위 전도체의 상위 표면내의 흄(recess)에 의해 상기 제1상위 전도체로부터 절연되며, 상기 흄은 상기 제1상위 전도체에 대해 자기-정렬(self-aligned)되고 절연체(insulator)로 적어도 부분적으로 채워진 반도체 구조체.

#### 청구항 2

제1항에 있어서, 절연 층(insulating layer)이 상기 절연 영역의 표면의 일부상에 침착되는 반도체 구조체.

#### 청구항 3

제2항에 있어서, 상기 절연 층의 두께는 상기 제1하위 전도체내 흄의 깊이보다 작은 반도체 구조체.

**청구항 4**

제1항에 있어서, 상기 제1 및 제2상위 전도체중 적어도 하나가 저장 캐패시터 노드인 반도체 구조체.

**청구항 5**

제1항에 있어서, 상기 제1하위 전도체는 비트-라인 스터드인 반도체 구조체.

**청구항 6**

제5항에 있어서, 상기 제2하위 전도체는 저장 캐패시터 스터드인 반도체 구조체.

**청구항 7**

제6항에 있어서, 상기 제1 및 제2상위 전도체는 저장 캐패시터 노드인 반도체 구조체.

**청구항 8**

제7항에 있어서, 상기 캐패시터 노드는 폴리실리콘을 포함하는 재료로 형성된 반도체 구조체.

**청구항 9**

제7항에 있어서, 상기 캐패시터 노드는 전도 층에 의해 커버된 반도체 구조체.

**청구항 10**

제1항에 의한 적층 캐패시터 셀(a stacked capacitor cell)로서, 상기 제1하위 전도체는 비트-라인 스터드이고, 상기 제2하위 전도체는 캐패시터 스터드이며, 상기 제1 및 제2상위 전도체는 저장 캐패시터 노드이되, 상기 캐패시터 셀은 상기 캐패시터 노드 사이에 배치되고 그들로부터 절연된 비트-라인과 절연 영역내에 위치된 워드 라인을 더 포함하는 적층 캐패시터 셀.

**청구항 11**

동적 랜덤 액세스 메모리(a dynamic random access memory; DRAM) 장치에 있어서, 제10항에 따른 적층 캐패시터 셀을 적어도 하나 포함하는 동적 랜덤 액세스 메모리 장치.

**청구항 12**

제1상위 전도체는 제1하위 전도체의 적어도 일부상에 배치되고 상기 제1하위 전도체는 절연 영역내에 배치되며, 제2하위 전도체는 절연 영역내에 위치되어 상기 제1하위 전도체로부터 전기적으로 절연되고, 제2상위 전도체는 상기 제2하위 전도체의 적어도 일부상에 배치되어 그것에 전기적으로 접속될 때 상기 제1상위 전도체로부터 상기 제1하위 전도체를 전기적으로 절연하는 방법에 있어서, 상기 순차적으로-형성된 상기 제1상위 전도체에 대해 자기-정렬된 상기 제1하위 전도체의 상위 표면내에 적어도 부분적으로 절연체로 채워진 흙을 형성하여 상기 제1상위 전도체로부터 상기 제1하위 전도체를 전기적으로 절연하는 단계를 포함하는 전기적 절연 방법.

**청구항 13**

제12항에 있어서, 상기 제1 및 제2상위 전도체는 리소그래피적 단계, 패터닝 단계 및, 에칭 단계를 포함하는 기법에 의해 형성되는 전기적 절연 방법.

**청구항 14**

제12항에 있어서, 상기 제1하위 전도체는 비트-라인 스터드이고, 상기 제1상위 전도체 및 제2상위 전도체는 저장 캐패시터 노드이며, 상기 제2하위 전도체는 캐패시터 스터드이되, 상기 전도체 및 스터드는 적층 캐패시터 셀의 소자를 포함하는 전기적 절연 방법.

**청구항 15**

제12항에 있어서, 상기 흙은 에칭에 의해 형성되는 전기적 절연 방법.

**청구항 16**

상위 레벨에 있는 적어도 두 개의 전도체와 하위 레벨에 있는 적어도 두 개의 전도체를 포함하되, 제1상위 전도체는 제1하위 전도체상에 적어도 부분적으로 배치되고, 제2상위 전도체는 제2하위 전도체상에 적어도 부분적으로 배치되며, 상기 제2상위 전도체와 상기 제2하위 전도체 사이에 전기적 접속을 형성하는데 사용되는 단계는 통상적으로 상기 제1상위 전도체와 상기 제1하위 전도체 사이에 바람직하지 않은 전기적 접속을 또한 초래하는 반도체 구조체 준비 방법에 있어서, 상기 제1상위 전도체에 대해 자기-정렬된 상기 제1하위 전도체의 상위 표면내에 적어도 부분적으로 절연체로 채워진 흙을 형성하여 상기 제1상위 전도체로부터 상기 제1하위 전도체를 전기적으로 절연하는 단계를 포함하는 반도체 구조체 준비 방법.

**청구항 17**

제16항에 있어서, 상기 제2상위 전도체와 상기 제2하위 전도체 사이에 전기적 접속을 형성하는데 사용되는 상기 단계는 리소그래피적 단계, 패터닝 단계 및, 에칭 단계를 포함하는 반도체 구조체 준비 방법.

**청구항 18**

제16항에 있어서, 상기 반도체 구조체는 적층 캐패시터 셀인 반도체 구조체 준비 방법.

도면

도면1

도면2

도면3

도면4

도면5

## 도면6