(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6553057号

(P6553057)

(45) 発行日 令和1年7月31日(2019.7.31)

(24) 登録日 令和1年7月12日(2019.7.12)

|              |                                     |

|--------------|-------------------------------------|

| (51) Int.Cl. | F 1                                 |

| H03K 19/00   | (2006.01)      H03K 19/00      210  |

| G01R 27/26   | (2006.01)      G01R 27/26      C    |

| H02J 1/00    | (2006.01)      H02J 1/00      303   |

| G06F 17/50   | (2006.01)      G06F 17/50      662G |

請求項の数 15 (全 28 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-546845 (P2016-546845)  |

| (86) (22) 出願日 | 平成27年1月15日 (2015.1.15)        |

| (65) 公表番号     | 特表2017-506328 (P2017-506328A) |

| (43) 公表日      | 平成29年3月2日 (2017.3.2)          |

| (86) 國際出願番号   | PCT/US2015/011658             |

| (87) 國際公開番号   | W02015/109125                 |

| (87) 國際公開日    | 平成27年7月23日 (2015.7.23)        |

| 審査請求日         | 平成29年12月19日 (2017.12.19)      |

| (31) 優先権主張番号  | 14/157,451                    |

| (32) 優先日      | 平成26年1月16日 (2014.1.16)        |

| (33) 優先権主張国   | 米国 (US)                       |

|           |                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                         |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                         |

| (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                         |

| (74) 代理人  | 100112807<br>弁理士 岡田 貴志                                                                                         |

最終頁に続く

(54) 【発明の名称】システムレベルの電力分配ネットワークに関する電圧依存ダイRCモデリング

## (57) 【特許請求の範囲】

## 【請求項1】

回路と、前記回路の電源レイルと電力供給源の間に結合された電力スイッチとを備えるシステムにおけるパワーゲーティングのための方法であって、

前記回路が不活性状態から起動されるべきときに前記電力スイッチをオンにすることを備え、ここにおいて、前記電力スイッチをオンにすることは、

第1の時間間隔のあいだに第1の平均速度で前記電力スイッチの抵抗を減少させること、

前記第1の時間間隔のすぐ後に続く第2の時間間隔のあいだに第2の平均速度で前記電力スイッチの前記抵抗を減少させること、ここにおいて、前記第1の平均速度は前記第2の平均速度よりも大きく、前記第1の時間間隔と前記第2の時間間隔との間の境界は、前記回路の前記電源レイルの電圧が前記回路内のトランジスタのしきい値電圧にほぼ達する時刻と一致する、と、

を備える、方法。

## 【請求項2】

前記第1の平均速度は前記第2の平均速度より少なくとも2倍大きい、請求項1に記載の方法。

## 【請求項3】

前記第2の時間間隔の後に続く第3の時間間隔のあいだに第3の平均速度で前記電力スイッチの前記抵抗を減少させること、ここにおいて、前記第3の平均速度は前記第1およ

10

20

び第 2 の 平均速度よりも大きい、

をさらに備える、請求項 1 に記載の方法。

**【請求項 4】**

前記第 2 の時間間隔と前記第 3 の時間間隔との間の境界は、前記回路の電圧が前記電力供給源の基準の供給電圧の 90 パーセント以上になる時刻と一致する、請求項 3 に記載の方法。

**【請求項 5】**

前記電力スイッチは第 1 の複数のスイッチと、第 2 の複数のスイッチとを備え、前記方法はさらに、

前記第 1 の時間間隔のあいだに前記第 1 の複数のスイッチをオンにすることと、

10

前記第 2 の時間間隔のあいだに前記第 2 の複数のスイッチをオンにすることと、

を備える、請求項 1 に記載の方法。

**【請求項 6】**

前記第 1 の複数のスイッチは前記第 2 の複数のスイッチよりも速い速度でオンにされる、請求項 5 に記載の方法。

**【請求項 7】**

前記第 1 の複数のスイッチ中の少なくとも 2 つのスイッチは並行してオンにされる、請求項 5 に記載の方法。

**【請求項 8】**

前記第 1 の複数のスイッチのそれぞれは、前記第 2 の複数のスイッチのそれよりも低い抵抗を有する、請求項 5 に記載の方法。

20

**【請求項 9】**

回路と、前記回路の電源レイルと電力供給源の間に結合された電力スイッチとを備えるシステムにおけるパワーゲーティングのための装置であって、前記装置は、

前記回路が不活性状態から起動されるべきときに前記電力スイッチをオンにするための手段を備え、ここにおいて、前記電力スイッチをオンにするための前記手段は、

第 1 の時間間隔のあいだに第 1 の 平均速度で前記電力スイッチの抵抗を減少させるための手段と、

前記第 1 の時間間隔のすぐ後に続く第 2 の時間間隔のあいだに第 2 の 平均速度で前記電力スイッチの前記抵抗を減少させるための手段、ここにおいて、前記第 1 の 平均速度は前記第 2 の 平均速度よりも大きく、前記第 1 の時間間隔と前記第 2 の時間間隔との間の境界は、前記回路の前記電源レイルの電圧が前記回路内のトランジスタのしきい値電圧にほぼ達する時刻と一致する、と、

30

を備える、装置。

**【請求項 10】**

前記第 1 の 平均速度は前記第 2 の 平均速度より少なくとも 2 倍大きい、請求項 9 に記載の装置。

**【請求項 11】**

前記第 2 の時間間隔の後に続く第 3 の時間間隔のあいだに第 3 の 平均速度で前記電力スイッチの前記抵抗を減少させるための手段、ここにおいて、前記第 3 の 平均速度は前記第 1 および第 2 の 平均速度よりも大きい、

40

をさらに備える、請求項 9 に記載の装置。

**【請求項 12】**

前記第 2 の時間間隔と前記第 3 の時間間隔との間の境界は、前記回路の電圧が前記電力供給源の基準の供給電圧の 90 パーセント以上になる時刻と一致する、請求項 11 に記載の装置。

**【請求項 13】**

前記電力スイッチは第 1 の複数のスイッチと、第 2 の複数のスイッチとを備え、前記装置はさらに、

前記第 1 の時間間隔のあいだに前記第 1 の複数のスイッチをオンにするための手段と、

50

前記第2の時間間隔のあいだに前記第2の複数のスイッチをオンにするための手段と、を備える、請求項9に記載の装置。

【請求項14】

前記第1の複数のスイッチは前記第2の複数のスイッチよりも速い速度でオンにされる、または、

前記第1の複数のスイッチ中の少なくとも2つのスイッチは並行してオンにされる、請求項13に記載の装置。

【請求項15】

前記第1の複数のスイッチのそれぞれは、前記第2の複数のスイッチのそれよりも低い抵抗を有する、請求項13に記載の装置。 10

【発明の詳細な説明】

【技術分野】

【0001】

[0001]本開示の態様は、一般に電力分配ネットワークに関し、より詳細には電力分配ネットワークのための電圧依存ダイRCモデルリングに関する。

【背景技術】

【0002】

[0002]電力分配ネットワーク(PDN)は、電力供給源(たとえば、電池)から電力をダイ上の様々な回路に分配するために使用することができる。電力を保存するために、PDNは、給電ゲーティングを使用し得、回路が非活性のときに回路からの電力漏れを防止するためにPDNが電力供給源から回路を切り離す。回路の大きさが深ナノメートル領域までにも小さくなるにつれて、電力漏れが著しく増大する。したがって、モバイルデバイスの電力消費を減らし、電池寿命を延ばすために、パワーゲーティングがますます重要になっている。 20

【発明の概要】

【0003】

[0003]以下では、1つまたは複数の実施形態の簡略化した概要を、そのような実施形態の基本的な理解が得られるようにするために提示する。この概要は、企図されるすべての実施形態の広範な概説ではなく、またすべての実施形態の重要な要素を特定するものでも、どれかまたはすべての実施形態の範囲を描写するものでもない。その唯一の目的は、後で提示されるより詳細な説明の前置きとして、1つまたは複数の実施形態のいくつかの概念を簡略化された形で提示することである。 30

【0004】

[0004]一態様によれば、回路の電圧に依存する静電容量を決定するための方法が本明細書で説明される。この方法は、複数の電圧のそれぞれにおいて回路のパラメータを測定することと、電圧ごとに、その電圧での回路の測定されたパラメータに回路の抵抗-キャパシタ(RC)モデルをフィッティングすることによって、その電圧での回路の静電容量を決定することとを備える。

【0005】

[0005]第2の態様は、回路および電力スイッチを備えるシステムに関する。この電力スイッチは、回路と、回路が活性状態にあるときに回路を電力供給源に接続するように、ならびに回路が不活性状態にあるときに回路を電力供給源から切り離すように構成され、ここにおいて、電力スイッチは可変抵抗を有する。システムはさらに、第1の時間間隔のあいだに第1の速度で電力スイッチの抵抗を減少させ、第1の時間間隔のすぐ後に続く第2の時間間隔のあいだに第2の速度で電力スイッチの抵抗を減少させることによって、不活性状態から活性状態へ回路の電力が増加するように電源回路の抵抗を制御するように構成されたスイッチ制御回路を備え、ここにおいて、第1の速度は第2の速度よりも大きく、第1と第2の時間間隔との間の境界は、回路の電圧が回路内のトランジスタのしきい値電圧にほぼ達する時刻と一致する。 40

【0006】

10

20

30

40

50

[0006]第3の態様は、回路と、その回路と電力供給源の間に結合された電力スイッチとを備えるシステムにおけるパワーゲーティングのための方法に関する。この方法は、回路が不活性状態から起動されるべきときに電力スイッチをオンにすることを備える。電力スイッチをオンにすることは、第1の時間のあいだに第1の速度で電力スイッチの抵抗を減少させることと、第1の時間間隔のすぐ後に続く第2の時間間隔のあいだに第2の速度で電力スイッチの抵抗を減少させることとを備え、ここにおいて、第1の速度は第2の速度よりも大きく、第1と第2の時間間隔との間の境界は、回路の電圧が回路内のトランジスタのしきい値電圧にほぼ達する時刻と一致する。

#### 【0007】

[0007]第4の態様は、回路と、その回路と電力供給源の間に結合された電力スイッチとを備えるシステムにおけるパワーゲーティングのための装置に関する。この装置は、回路が不活性状態から起動されるべきときに電力スイッチをオンにするための手段を備える。電力スイッチをオンにするための手段は、第1の時間間隔のあいだに第1の速度で電力スイッチの抵抗を減少させるための手段と、第1の時間間隔のすぐ後に続く第2の時間間隔のあいだに第2の速度で電力スイッチの抵抗を減少させるための手段とを備え、ここにおいて、第1の速度は第2の速度よりも大きく、第1と第2の時間間隔との間の境界は、回路の電圧が回路内のトランジスタのしきい値電圧にほぼ達する時刻と一致する。

10

#### 【0008】

[0008]前述の目的および関連した目的の達成のために、1つまたは複数の実施形態は、後で十分に説明される、また特許請求の範囲で具体的に指示される特徴を備える。以下の説明および添付の図面では、1つまたは複数の実施形態のいくつかの説明的な態様を詳細に示す。しかし、これらの態様は、様々な実施形態の原理が使用され得る様々な様式のほんのいくつかだけを示すにすぎず、説明される実施形態は、このような態様およびその同等物すべてを含むものである。

20

#### 【図面の簡単な説明】

#### 【0009】

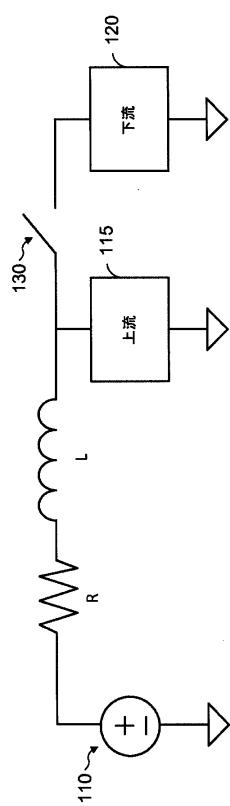

【図1】[0009]電力を上流回路および下流回路に分配するための電力分配ネットワーク(PDN)の一例を示す図。

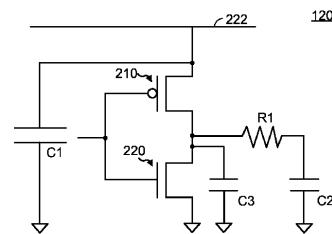

【図2】[0010]PDNから見た電圧に依存する静電容量を有するインバータの一例を示す図。

30

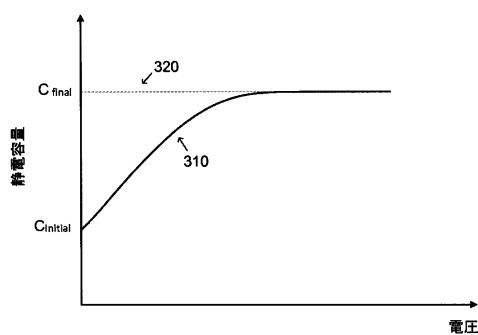

【図3】[0011]電圧の関数としてのインバータの静電容量の一例を示す図。

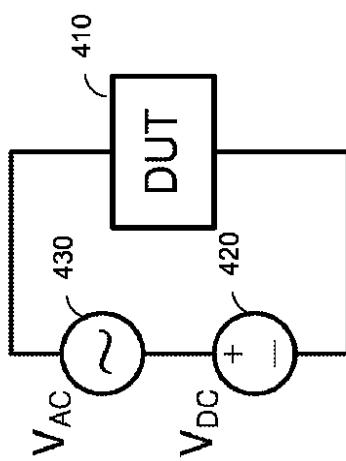

【図4】[0012]本開示の実施形態によるデバイスの電圧に依存する静電容量と抵抗とを決定するための試験セットアップを示す図。

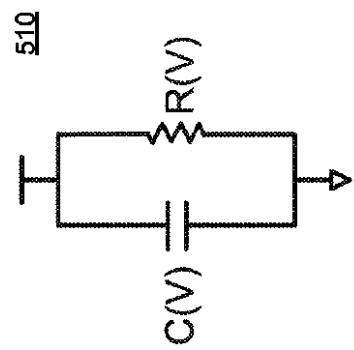

【図5】[0013]本開示の実施形態による並列抵抗 - キャパシタ(RC)モデルの一例を示す図。

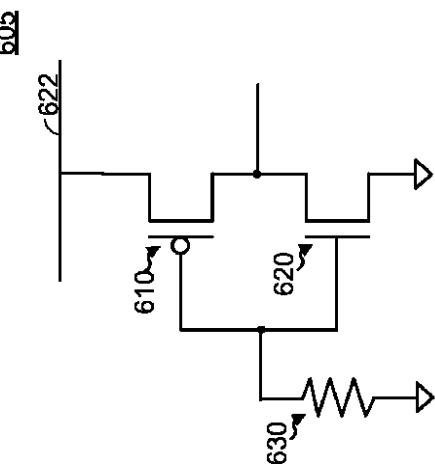

【図6A】[0014]本開示の実施形態による2つの異なる入力状態でのインバータの電圧に依存する静電容量を決定するための構成を示す図。

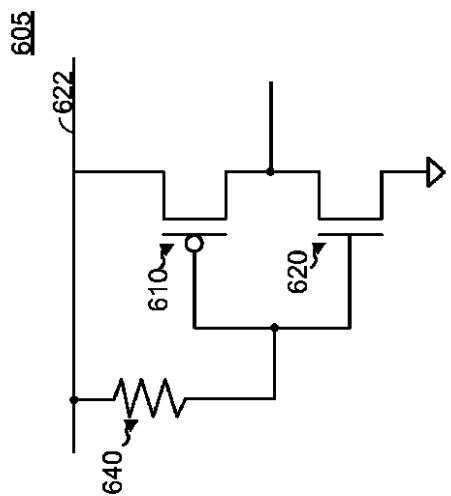

【図6B】本開示の実施形態による2つの異なる入力状態でのインバータの電圧に依存する静電容量を決定するための構成を示す図。

【図7】[0015]本開示の実施形態による2つの異なる入力状態でのインバータの電圧に依存する静電容量を示す図。

40

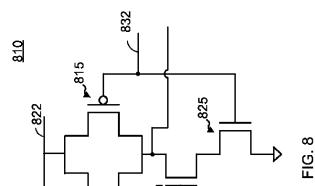

【図8】[0016]本開示の実施形態による2入力NANDゲートを示す図。

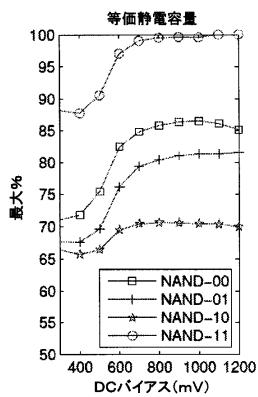

【図9】[0017]本開示の実施形態による4つの異なる入力状態での2入力NANDゲートの電圧に依存する静電容量を示す図。

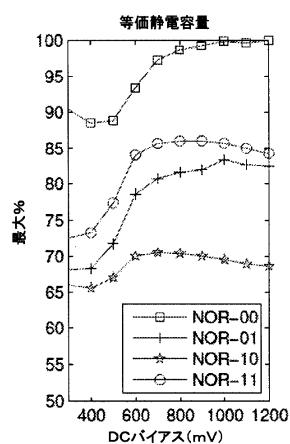

【図10】[0018]本開示の実施形態による2入力NORゲートを示す図。

【図11】[0019]本開示の実施形態による4つの異なる入力状態での2入力NORゲートの電圧に依存する静電容量を示す図。

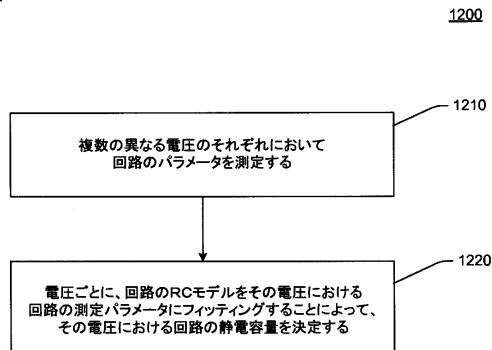

【図12】[0020]本開示の実施形態による下流回路の電圧に依存する静電容量を決定するための方法を示す図。

【図13】[0021]本開示の実施形態による、下流回路に結合されたPDNのインパルス応

50

答を測定することによって下流回路の電圧に依存する静電容量を決定するための試験セットアップを示す図。

【図14】[0022]本開示の別の実施形態による下流回路の電圧に依存する静電容量を決定するための方法を示す図。

【図15】[0023]本開示の実施形態による電力スイッチの抵抗プロファイルを示す図。

【図16】[0024]本開示の実施形態による電力スイッチを示す図。

【図17】[0025]本開示の別の実施形態による電力スイッチを示す図。

【図18A】[0026]本開示の実施形態によるパワーゲーティングのための方法を示す図。

【図18B】本開示の実施形態によるパワーゲーティングのための方法を示す図。

【発明を実施するための形態】

10

【0010】

[0027]添付の図面に関して以下で示される詳細な説明は、様々な構成についての説明が意図されており、本明細書に記載の概念が実践され得る構成だけを表すものではない。この説明は、様々な概念についての完全な理解が得られることを目的として具体的な詳細を含む。しかし、これらの概念は、これらの具体的な詳細がなくても実践され得ることが当業者には明らかであろう。場合によっては、そのような概念を不明瞭にすることを避けるために、良く知られている構造物および構成要素はブロック図の形で示される。

【0011】

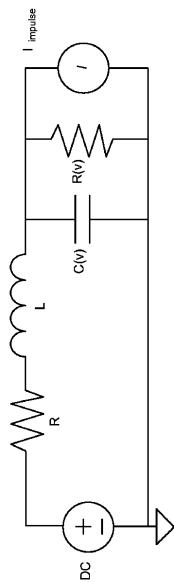

[0028]図1は、電力をDC電力供給源110から上流回路115および下流回路120に分配するための電力分配ネットワーク(PDN)の一例を示す。図1のインダクタLおよび抵抗Rはそれぞれ、電力供給源110と回路115および120との間のボードおよびパッケージの接続のインダクタンスと抵抗とをモデル化している。上流回路115および下流回路120は、同じダイ上に配置され得る。

20

【0012】

[0029]PDNは、電力を保存するためにパワーゲーティングを使用し得る。この関連で、PDNは、下流回路120を電力供給源110に選択的に接続するための電力スイッチ130を含む。下流回路120が活性であるとき、電力管理回路(図示せず)は、電力を下流回路120に供給するために電力スイッチ130をオンにする。下流回路120が非活性であるとき、電力管理回路は、電力供給源110を下流回路120から切り離すために電力スイッチ130をオフにする。これは、下流回路120が非活性のときの電力消費を低減させる。

30

【0013】

[0030]下流回路120が活性のときに電力スイッチ130の両端のIR(電流(I)×抵抗(R))電圧降下を最小限にするためには、電力スイッチ130の有する抵抗が非常に小さいことが望ましい。しかし、これは、下流回路120が初めて起動されたときの上流回路115における供給電圧の大きい降下につながる。大きな電圧降下は、下流回路120内のキャパシタによって引き起こされ、それらは、下流回路120が非活性状態から初めて起動されたときに(電力スイッチ130が初めて閉じられたときに)は、ほとんど電荷を有していない。その結果、上流回路115と下流回路120が電力スイッチ130によって最初に接続されたときに、大量の電流が上流回路115内のキャパシタから下流回路120内のキャパシタへと急に流れ、上流回路115における供給電圧を降下させることになる。PDNは、電力供給源110と回路115および120との間のインダクタLのため、その大きい電圧降下を防止するのに十分なだけ速く反応することができない。

40

【0014】

[0031]電圧降下の大きさは、下流回路120の静電容量の関数になる。下流回路120の静電容量が大きければ大きいほど、電圧降下が大きくなる。抵抗がゼロである理想電力スイッチ130では、電圧降下は次式で近似され得る。

## 【数1】

$$\text{降下} = \left(1 - \frac{C_{up}}{C_{up} + C_{down}}\right) \cdot 100\% \quad (1)$$

ここで、 $C_{up}$ は上流回路115の静電容量であり、 $C_{down}$ は下流回路120の静電容量である。式(1)はオン抵抗がゼロである理想スイッチを仮定しているが、現実のスイッチにはいくらかのオン抵抗があるので、式(1)は実際の電圧降下よりも大きい電圧降下を予測している。しかし、オン抵抗が非常に小さいスイッチについては、式(1)は電圧降下のよい近似値を与える。式(1)から分かるように、下流回路120の静電容量が上流回路115の静電容量に比べて大きいとき、電圧降下は大きくなり得る。たとえば、 $C_{up}$ と $C_{down}$ がほぼ等しいとき、電圧降下は、約50%になり、それは、ほとんどの場合で受容できない強さである。

## 【0015】

[0032]大きい電圧降下は、上流回路115内の論理回路を誤動作させ得るので望ましくない。大きい電圧降下はまた、上流回路115内の伝搬遅延を引き起こし得、上流回路115内のタイミング問題につながり得る。したがって、上流回路115が適正に機能することを保証するために、電圧降下を受容可能な限度(たとえば、5%)以内に保つことが重要である。

## 【0016】

[0033]電圧降下を受容可能な限度内に保つための1つの手法は、可変抵抗電力スイッチを使用して電力スイッチ130を実施することである。下流回路120が初めて起動されるとき、電力スイッチ130は、上流回路115から下流回路120への電荷移動の速度を制限するために比較的高い抵抗を有し、従って電圧降下を低減させる。電力スイッチ130の抵抗は時間が経つにつれ減少して、電力供給源110からの電荷がインダクタLを通って下流回路120の電力を供給するための時間が与えられる。下流回路120の電源レイル(rail)の電圧が基準の供給電圧に近い電圧に落ち着くと、スイッチの抵抗は低くなる。

## 【0017】

[0034]可変抵抗電力スイッチ130は、並列に結合された複数のスイッチ(たとえば、トランジスタスイッチ)を使用して実施され得る。下流回路120が起動されると、これらのスイッチは、ある時間の期間にわたってオンにされ得、より多くのスイッチがオンにされるにつれて電力スイッチ130の抵抗が減少する。1つの例では、スイッチは、1つまたは複数の弱いスイッチ(高抵抗スイッチ)と、1つまたは複数の強いスイッチ(低抵抗スイッチ)とを含み得る。弱いスイッチは、強いスイッチの抵抗より10~20倍高い抵抗を有し得る。この例では、弱いスイッチは、大きい電圧降下を防止するために初めにオンにされ得、強いスイッチは、下流回路120の電源レイルの電圧が基準の供給電圧に近い電圧に落ち着いたときに回転させることができる。

## 【0018】

[0035]すなわち、電力スイッチ130の抵抗は、下流回路120が初めに起動されたときの上流回路115における大きい電圧降下を防止するように調整することができる。上流回路115における電圧降下の大きさと、下流回路120の起動時間との間にはトレードオフがある。電力スイッチ130の初期抵抗を大きくすることは、起動時間が増大することを代償にして電圧降下を低減する。したがって、電圧降下と起動時間の両方を最適化する電力スイッチ130を設計するためには、下流回路120の静電容量を正確にモデル化することが重要である。

## 【0019】

10

20

30

40

50

[0036]従来のモデリング技法では、下流回路120の静電容量を固定容量としてモデル化し、静電容量の電圧依存性を無視する。この過剰に簡略化されたモデルは、電力スイッチ130が最初にオンにされたときの下流回路120の静電容量の大きな過大推定値、したがって電圧降下の大きな過大推定値につながり得る。これは、以下の例によって説明され得る。

#### 【0020】

[0037]図2は、P型電界効果トランジスタ(PFET)210およびN型電界効果トランジスタ(NFET)220によって形成されたインバータを備える下流回路120の一例を示す。回路120はまた、第1のキャパシタC1と、第2のキャパシタC2と、第3のキャパシタC3とを備える。この例では、第1のキャパシタC1は、PFET210の本的な静電容量(たとえば、PFET210のNウェル静電容量)を表し、第2の静電容量C2は、インバータの出力部に接続された線の寄生静電容量を表し、第3の静電容量C3は、NFET220の本的な静電容量(たとえば、NFET220のドレイン-ボディ間の静電容量)を表す。図2の抵抗R1は線の抵抗を表す。図を簡単にするために図2には1つのインバータが示されているが、下流回路120は多くのインバータおよび/または他の論理デバイスを含み得ることを理解されたい。10

#### 【0021】

[0038]下流回路120が非活性状態において電力供給源110から切り離されると、下流回路120内のキャパシタは漏れ電流により放電され、下流回路120の供給レイル222の電圧がほぼ0ボルトになる。下流回路120の電力を供給するために電力スイッチ130が最初にオンにされたとき、PFET210およびNFET220のゲートがローに駆動されていると仮定すると、PFET210は最初オフされている。これは、PFET210のソース-ゲート間の電圧が最初はPFET210の絶対しきい値電圧 $V_{th}$ よりも十分に低いからである。結果として、第2のキャパシタC2および第3のキャパシタC3は、最初はPDNから分離されており、したがって、最初にPDNから見た下流回路120の静電容量には寄与しない。20

#### 【0022】

[0039]供給レイル222の電圧が上昇すると、PFET210がオンになる。これがPFET210のソースとドレインの間にチャネルを生成し、それによって、PDNと第2および第3のキャパシタC2およびC3との間の経路が開通する。すなわち、供給レイル222の電圧が上昇するにつれて、PDNからは、第2および第3のキャパシタC2およびC3のより多くの静電容量が見える。結果として、PDNから見た下流回路120の静電容量は増大する。30

#### 【0023】

[0040]このことが、図3で例示され、それは、供給レイル222の電圧の関数としての、PDNから見た下流回路120の静電容量310を示している。電力スイッチ130が最初にオンにされるとき、供給レイル222の電圧はほぼ0ボルトであり、静電容量310は $C_{initial}$ であり、それは、第1のキャパシタC1の静電容量を含む。電圧が上昇すると、PFET210はオンになって、PDNと第2および第3のキャパシタC2およびC3との間の経路が開通する。結果として、PDNから見た静電容量310は、増大する電圧とともに増大する。電圧がPFET210の絶対しきい値電圧 $V_{th}$ に達すると、PFET210は完全にオンになり、PDNから見た静電容量310は、 $C_{final}$ に近づき、それは、下流回路120の十分に電力が供給されたときの下流回路120の静電容量である。40

#### 【0024】

[0041]第2のキャパシタC2の静電容量は、必ずしもそれ自体が電圧依存性ではないことを理解されたい。PDNから見た第2のキャパシタC2の静電容量は、PFET210を通るPDNと第2のキャパシタC2との間の経路が電圧依存性である(したがって、PDNの能力は、第2のキャパシタC2の静電容量を見るは、電圧依存性である)ので、この例では電圧依存性である。同じことが第3のキャパシタC3にも言える。50

## 【0025】

[0042]図3の例に示されたキャパシタ以外に、他のキャパシタもまた下流回路120の電圧に依存する静電容量に寄与し得ることを理解されたい。図3の例は、下流回路120の静電容量が電圧依存性であり得る多くの様式のうちの単に1つを示しているにすぎないこともまた理解されたい。一般に、PDNから見た下流回路120の静電容量は、増大する電圧とともに増大する。これは、下流回路120内のトランジスタが増大する電圧によりオンになって、トランジスタが下流回路120内のPDNとキャパシタの間の経路を開通することになるからである。

## 【0026】

[0043]上記の例で、従来のモデリング技法では下流回路120の静電容量を、ほぼ $C_{f,i}_{na}$ に等しい固定された静電容量として単純にモデル化している。これは、図3の破線320で表されている。したがって、この例の従来のモデリング技法では、PDNから最初に見える静電容量を大幅に過大推定し、これは電圧降下を大きく過大推定することにつながる。

## 【0027】

[0044]すなわち、従来のモデリング技法では、電力スイッチ130が最初にオンにされたときのPDNから見た静電容量を大幅に過大推定する可能性がある。これにより回路設計者が電圧降下を過大推定し、したがって、電圧降下限度内にとどまるために必要とされるよりもずっと大きい電力スイッチ130の初期抵抗を決定することになる。これには、下流回路120の起動時間を不必要に延ばすという望ましくない効果がある。

## 【0028】

[0045]本開示の実施形態は、下流回路の電圧に依存する静電容量をモデル化し、それによって回路設計者が電力スイッチの抵抗を、下流回路120の静電容量を固定された静電容量としてモデル化するモデリング技法と比較して、よりよく最適化することを可能にするための技法を提供する。本開示の実施形態はまた、下流回路の電圧依存性の抵抗をモデル化するための技法も提供する。

## 【0029】

[0046]1つの実施形態では、下流回路120の電圧に依存する静電容量および抵抗は、下流回路120の電圧に依存するRC回路モデルを、たとえばコンピュータシミュレータ（たとえば、集積回路エンファシスによるシミュレーションプログラム（SPICE）シミュレータ）を使用して得られた下流回路120の測定インピーダンスにフィッティングすることによって推定される。本明細書では「測定」という用語は、デバイスのコンピュータシミュレーションで実行された測定を指すことも物理的デバイスの測定を指すこともある。

## 【0030】

[0047]この実施形態では、下流回路120のインピーダンスは、複数の異なるDC電圧のそれそれぞれにおいて測定され、それらは、0ボルトとPDNの供給電圧の間のいずれでの電圧範囲にもわたり得る。それぞれのDC電圧について、下流回路120のRCモデルは、そのDC電圧での下流回路120の静電容量と抵抗とを決定するために、そのDC電圧での測定インピーダンスにフィッティングされる。すなわち、下流回路120の静電容量および抵抗は、複数の異なるDC電圧のそれぞれにおいて決定され、それによって、これらのDC電圧の電圧範囲にわたって下流回路120の静電容量および抵抗の電圧依存性の特性を明らかにする。

## 【0031】

[0048]下方の図4は、たとえばコンピュータシミュレータを使用して下流回路120のインピーダンスを測定するための、例示的な試験セットアップを示し、ここにおいては、下流回路120は非線形の被試験デバイス（DUT）410として扱われる。DUT410は、DC電圧源420によってDCバイアスがかけられ、ある周波数範囲（たとえば、0から100MHzまで）にわたって、小さいAC電圧源430によって励起される。DC電圧源420は、複数の異なるDC電圧のそれぞれに順次に設定され得、この設定に

10

20

30

40

50

おいて、以下でさらに論じられるように、DUT 410 のインピーダンスが、その周波数範囲にわたってそれぞれのDC電圧で測定される。

【0032】

[0049]この例のコンピュータシミュレータでは、DUT 410 の S パラメータを、その周波数範囲にわたってそれぞれのDC電圧で測定する。次に、それぞれのDC電圧でのSパラメータは、次式を使用してインピーダンスに変換される。

【数2】

$$Z = \frac{Z_p(S_{11} + 1)}{1 - S_{11}} \quad (2)$$

10

ここで、 $S_{11}$  は入力ポート電圧係数であり、 $Z$  は入力インピーダンスであり、 $Z_p$  は非線形デバイスモデルの特性インピーダンスである。すなわち、コンピュータシミュレータは、その周波数範囲にわたってそれぞれのDC電圧でのDUT 410 のインピーダンス  $Z$  の測定を行う。

【0033】

[0050]各々のDC電圧について、DUT 410 のRC回路モデルが、そのDC電圧でのDUT 410 の抵抗と静電容量とを決定するために、そのDC電圧でのDUT 410 の測定されたインピーダンス  $Z$  にフィッティングされる。この関連で、図5は、使用され得る並列RC回路モデル510の一例を示す。RCモデル510は、電圧依存性の抵抗  $R(V)$  と並列に電圧依存性のキャパシタ  $C(V)$  を備え、単一の極を有する。並列RCモデル510は、DUT 410 が対象の周波数範囲内に支配的な極を有するときに適切に機能し、したがって、並列RC回路として正確にモデル化ができる。それぞれのDC電圧において、RCモデル610のインピーダンスは、ラプラス領域で次式によつて与えられる。

20

【数3】

30

$$Z = \frac{R}{1+sCR} \quad (3)$$

ここで、 $s = j 2\pi f$  であり、ラプラス領域の複素角周波数を表し、 $R$  はそれぞれのDC電圧での抵抗であり、 $C$  はそれぞれのDC電圧での静電容量である。

【0034】

[0051]特定のDC電圧でのDUT 410 の静電容量と抵抗とを、そのDC電圧でのDUT 410 の測定インピーダンス  $Z$  と、RCモデルとを使用して決定するための方法がここで、1つの実施形態によって説明される。

40

【0035】

[0052]そのDC電圧でのDUT 410 の抵抗は、そのDC電圧およびゼロの周波数におけるDUT 410 の測定インピーダンス  $Z$  に等しい。これは、周波数がゼロのときのRCモデルのインピーダンスは抵抗に等しいからである。この場合、DUT 410 の抵抗は  $Z|_{s=0}$  で表し得る。

【0036】

[0053]次に、DUT 410 の静電容量は、そのDC電圧での測定されたインピーダンスとRCモデルのインピーダンスとの間の誤差を対象の周波数範囲にわたって最小にする最適な静電容量  $C_{opt}$  を次式に基づいて見つけることによって、そのDC電圧で推定され

50

得る。

【数4】

$$C_{opt} = \arg \min_c \left| Z_{meas}(s) - \frac{Z|_{s=0}}{1 + sCZ|_{s=0}} \right| \quad (4)$$

10

ここで  $Z_{meas}(s)$  は、その DC 電圧での測定されたインピーダンスを周波数の関数として表し、

【数5】

$$\frac{Z|_{s=0}}{1 + sCZ|_{s=0}}$$

は、周波数の関数としての RC モデルのインピーダンスを表し、 $Z|_{s=0}$  は、その DC 電圧での RC モデルの抵抗を表す（上で論じられたように）。上の式は、その DC 電圧での測定インピーダンスと RC モデルのインピーダンスとの間の誤差をその周波数範囲にわたって最小にする最適な静電容量  $C_{opt}$  を決定する。この誤差は、勾配降下アルゴリズムまたは他の種類のアルゴリズムを使用して最小化することができる。最適な静電容量  $C_{opt}$  は、その DC 電圧での DUT 410 の静電容量の推定値を与える。

20

【0037】

[0054] 上述の方法は、それぞれの DC 電圧での DUT 410 の抵抗と静電容量とを決定するために、したがって、DC 電圧の電圧範囲にわたる DUT 410 の抵抗および静電容量の電圧依存性をキャラクタライズするために、複数の DC 電圧のそれについて繰り返され得る。

30

【0038】

[0055] 特定の DC 電圧での DUT 410 の抵抗および静電容量はまた、直接極フィッティング法を使用して決定することもできる。この実施形態では、その DC 電圧での DUT の測定されたインピーダンスは、測定されたインピーダンスを次の単極の式に変換する極フィッティングアルゴリズムに、入力され得る。

【数6】

$$Z = \frac{C'}{s+A'} \quad (5)$$

40

ここで、 $s = j 2\pi f$  であり、ラプラス領域の複素角周波数を表し、 $C'$  および  $A'$  は单極の式の値である。式(3)で与えられた RC モデルのインピーダンス  $Z$  は、RC モデルのインピーダンス  $Z$  が極の式(5)に対応するように、次式に書き直すことができる。

【数7】

$$Z = \frac{1/C}{s+1/(CR)} \quad (6)$$

そのDC電圧でのDUT 410の抵抗および静電容量は、次式によって決定される。

【数8】

10

$$C = \frac{1}{C'} \quad (7)$$

および

【数9】

20

$$R = \frac{C'}{A'} \quad (8)$$

【0039】

[0056] 上述の極フィッティング法は、それぞれのDC電圧でのDUT 410の抵抗と静電容量とを決定するために、したがって、DC電圧の電圧範囲にわたるDUT 410の抵抗および静電容量の電圧依存性をキャラクタライズするために、複数のDC電圧のそれぞれについて繰り返され得る。

30

【0040】

[0057] 本開示の実施形態による上述のモデリング技法は、インバータ、NANDゲート、NORゲート、および他の論理デバイスを含む様々な種類の論理デバイスの電圧に依存する静電容量をモデル化するために使用され得る。

【0041】

[0058] この関連で、図6Aは、ローに駆動されているインバータ605の入力を伴うインバータ605の電圧に依存する静電容量を決定するために上述のモデリング技法のいずれの1つも使用され得る一例を示す。この例で、PFET 610およびNFET 620のゲートは、抵抗器630を介してグランドに結合されている。抵抗器630は、下流回路内のインバータ605の入力をローに駆動するドライバの抵抗以上の抵抗を有し得る。次に、インバータ605の電圧に依存する静電容量は、DUT 4110として動作するインバータ605を用いて上述のモデリング技法の1つを実行することによって決定することができる。

40

【0042】

[0059] 図6Bは、ハイに駆動されたインバータ605の入力を伴うインバータ605の電圧に依存する静電容量を決定するために上述のモデリング技法のいずれの1つも使用され得る一例を示す。この例では、PFET 610およびNFET 620のゲートは、抵抗器640を介して供給レイル622に結合されている。結果として、インバータ605の入力の電圧は、供給レイル622の電圧が上昇するにつれて上昇する。抵抗器640

50

は、下流回路内のインバータ 605 の入力をハイに駆動するドライバの抵抗以上の抵抗を有し得る。次に、インバータ 605 の電圧に依存する静電容量は、D U T 410として動作するインバータ 605 を用いて上述のモデリング技法の 1 つを実行することによって決定することができる。

#### 【0043】

[0060]したがって、インバータ 605 の電圧に依存する静電容量は 2 つの異なる入力論理状態、すなわち、インバータ 605 の入力がロー（論理 0）に駆動される 1 つと、インバータ 605 の入力がハイ（論理 1）に駆動されるもう 1 つと、についてキャラクタライズされ得る。図 7 は、2 つの入力論理状態についてのインバータ 605 の電圧に依存する静電容量の一例を示すグラフである。図 7 に示されるように、入力論理状態 0 でのインバータ 605 の静電容量は、P F E T 610 が絶対しきい値電圧（たとえば、500 mV）に達した後に劇的に増大し、また入力論理状態 1 でのインバータ 605 の静電容量は、N F E T 620 が絶対しきい値電圧（たとえば、450 mV）に達した後に劇的に増大する。両方の状態での静電容量は、電圧が基準の供給電圧に近づくと、ほぼ一定のままになる。10

#### 【0044】

[0061]下流回路 120 が不活性状態から初めて起動されるとき、下流回路 120 への入力は一般に既定値に設定される。結果として、電力供給時の下流回路 120 内の各ノードの状態は知られており、したがってインバータ 605 の入力論理状態は知られている。これは、以下でさらに論じられるように、回路設計者が、電力スイッチ 130 の初期抵抗を決定するためにインバータ 605 の適切な電圧に依存する静電容量モデルを選択することを可能にする。20

#### 【0045】

[0062]上記の例では、2 つの異なる状態でのインバータ 605 の電圧に依存する静電容量は、インバータ 605 の出力に結合された寄生の配線容量の負荷なしで決定される。しかし、上述のモデリング技法のうちのいずれの 1 つもまた、寄生の配線容量の影響を明らかにするために、インバータ 605 の出力部に結合された寄生の配線容量の負荷付きのインバータ 605 に対して実行され得ることを理解されたい。

#### 【0046】

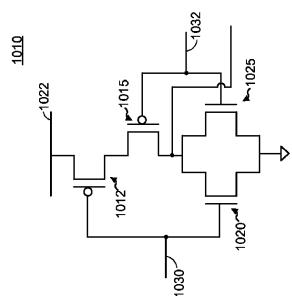

[0063]上で論じられたように、上述のモデリング技法はまた、N A N D ゲートおよびN O R ゲートの電圧に依存する静電容量をモデル化するために使用することもできる。この関連で、図 8 は、2 つのP F E T 812 および 815 と、2 つのN F E T 820 および 825 とを備える 2 入力N A N D ゲート 810 の一例を示す。この例では、N A N D ゲート 810 は 4 つの異なる入力論理状態、すなわち、入力 830 と 832 の両方がローに駆動される 1 つ（論理 00）と、入力 830 と 832 の両方がハイに駆動される 1 つ（論理 11）と、入力 830 と 832 が反対に駆動される 2 つ（論理 01 および 10）とを有する。入力は、抵抗を介してその入力をグランドに結合することによってローに駆動され得、また入力は、抵抗を介してその入力を供給レイル 822 に結合することによってハイに駆動され得る。30

#### 【0047】

[0064]上述のモデリング技法のうちのいずれの 1 つも、それぞれの状態でのN A N D ゲート 810 の電圧に依存する静電容量を決定するために、N A N D ゲート 810 に対して 4 つの論理状態のうちのそれぞれについて実行され得る。図 9 は、4 つの異なる入力論理状態でのN A N D ゲート 810 の電圧に依存する静電容量の一例を示すグラフである。40

#### 【0048】

[0065]図 10 は、2 つのP F E T 1012 および 1015 と、2 つのN F E T 1020 および 1025 とを備える 2 入力N O R ゲート 1010 の一例を示す。この例では、N O R ゲート 1010 は、入力 1030 と 1032 の両方がローに駆動される 1 つ（論理 00）、入力 1030 と 1032 の両方がハイに駆動される 1 つ（論理 11）、ならびに入力 1030 と 1032 が反対に駆動される 2 つ（論理 01 および 10）の、4 つの異な50

る入力論理状態を有する。入力は、抵抗を介してその入力をグランドに結合することによってローに駆動され得、また入力は、抵抗を介してその入力を供給レール 1022 に結合することによってハイに駆動され得る。

#### 【0049】

[0066] 上述のモデリング技法のうちのいずれか 1 つが、それぞれの状態での N O R ゲート 1010 の電圧に依存する静電容量を決定するために、N A N D ゲート 1010 に対して 4 つの論理状態のそれぞれについて実行され得る。図 11 は、4 つの異なる入力論理状態での N O R ゲート 1010 の電圧に依存する静電容量の一例を示すグラフである。

#### 【0050】

[0067] したがって、上述のモデリング技法は、下流回路 120 内の、インバータ、N A N D ゲート、および N O R ゲートを含む様々な論理デバイスの電圧に依存する静電容量を決定するために使用することができる。インバータ、N A N D ゲートおよび N O R ゲートは、下流回路内で様々な論理関数を実施するのに使用されることがある汎用論理回路セットを形成する。

#### 【0051】

[0068] 1 つの実施形態では、複数の論理デバイスの電圧に依存する静電容量は、複数の論理デバイスを備える下流回路 120 の電圧に依存する静電容量を決定するために、別々に決定され一緒に合計され得る。これは、本開示の実施形態では並列 R C 回路モデルを使用してそれぞれの論理デバイスをモデル化するので、可能である。結果として、論理デバイスの電圧依存の性静電容量は並列になり、したがって合計されることがある。デバイスごとに、下流回路 120 の最初に電力が供給されたときのデバイスの入力論理状態が決定され、決定された入力論理状態でのデバイスの電圧に依存する静電容量が、下流回路の電圧に依存する静電容量を決定するために使用される。すなわち、この実施形態は、多くの論理デバイスを備えるシステムの電圧に依存する静電容量を決定するための、計算効率のよい方法を提供する。

#### 【0052】

[0069] 別の実施形態では、複数の論理デバイスを備える回路の電圧に依存する静電容量は、上述のモデリング技法のうちのいずれか 1 つを下流回路全体に対して実行することによって決定することができる。この実施形態では、それぞれの論理デバイスの入力論理状態は、回路が最初に電力が供給されたときのデバイスの入力論理状態設定される。

#### 【0053】

[0070] 図 12 は、本開示の実施形態による回路の電圧に依存する静電容量を決定するための方法 1200 を示す。ステップ 1210 で、回路のパラメータが複数の異なる電圧のそれぞれにおいて測定される。たとえば、ある周波数範囲にわたる回路のインピーダンスが、それぞれの電圧において測定され得る。ステップ 1220 で、電圧ごとに、回路の R C モデルをその電圧での回路の測定されたパラメータにフィッティングすることによって、その電圧での回路の静電容量が決定される。たとえば、電圧ごとに回路の R C モデルが、その電圧での回路の測定インピーダンスにフィッティングされ得る。

#### 【0054】

[0071] 別の実施形態では、下流回路 120 の電圧に依存する静電容量は、下流回路に結合された P D N のインパルス応答を測定することによって推定される。この関連で、図 13 は、例示的な試験セットアップを示し、下流回路 120 は P D N の抵抗器 R およびインダクタ L を介して D C 電力供給源によってバイアスがかけられ図 13 において、下流回路 120 は電圧に依存する R C 回路として描かれている。この実施形態では、D C 電力供給源は、複数の異なる D C 電圧を下流回路に印加する。それぞれの D C 電圧において、試験デバイスが P D N をインパルス信号  $I_{impulse}$  で励起し、結果となるインパルス応答を測定する。次に、下流回路 120 の静電容量は、次式を使用して D C 電圧ごとに推定され得る。

10

20

30

40

【数10】

$$C = \frac{1}{L\omega_0^2} \quad (9)$$

ここで、 $\omega_0$ はそのDC電圧での測定されたインパルス応答の共振周波数であり、LはPDNのインダクタンスであり、CはそのDC電圧での下流回路120の静電容量である。共振周波数は、測定されたインパルス応答のフーリエ変換を行うことによって決定され得る。

10

【0055】

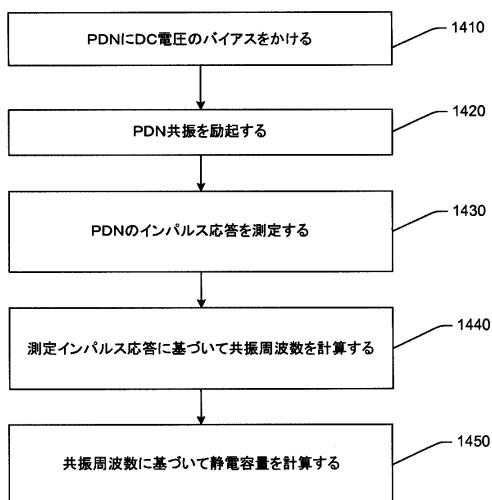

[0072]図14は、ある特定のDC電圧での下流回路120の静電容量を決定するための方法1400を示し、下流回路120はPDNに結合されている。ステップ1410で、PDNはそのDC電圧のバイアスがかけられる。ステップ1420で、PDN共振が励起される。これは、PDNをインパルス信号で励起することによって行われる。ステップ1430で、PDNのインパルス応答が測定される。ステップ1440で、測定されたインパルス応答に基づいて共振周波数が計算される。ステップ1450で、そのDC電圧での下流回路120の静電容量が共振周波数に基づいて計算される。たとえば、静電容量は式(9)を使用して計算される。方法1400は、複数のDC電圧のそれぞれにおける下流回路120の静電容量を決定するために、したがって、下流回路120の電圧に依存する静電容量をキャラクタライズするために、複数の異なるDC電圧のそれについて繰り返され得る。

20

【0056】

[0073]すなわち、本開示の実施形態によるモデリング技法では、下流回路の電圧に依存する静電容量をモデル化する。これは、回路設計者が、下流回路120が初めて起動されたときの下流回路120の静電容量をより正確に決定することを可能にし、したがって、上流回路115における電圧降下をある特定の電圧降下限度（たとえば、5%）以内にお保ちながら起動時間を低減させるように電力スイッチ130をよりよく最適化することを可能にする。たとえば、本開示の実施形態によるモデリング技法では、電力スイッチ130が初めてオンにされたときにPDNから見た下流回路120の静電容量は、従来のモデリング技法と比較して小さいと決定する。この知識を用いて、電力スイッチ130の初期抵抗は、電圧降下を電圧降下限度（たとえば、5%）以内にお保ちながら、起動時間を低減させるために小さくされることができる。

30

【0057】

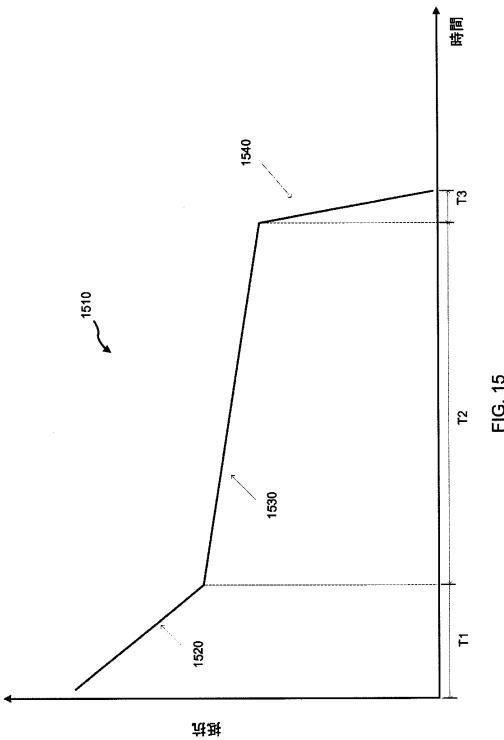

[0074]この関連で、図15は、本開示の実施形態によるモデリング技法を用いて決定することができる、電力スイッチ130の抵抗プロファイル1510の一例を示す。この実施形態で、抵抗プロファイル1510は、電力スイッチ130の抵抗を時間の関数として表す。抵抗プロファイル1510は第1の時間間隔T1と、第2の時間間隔T2と、第3の時間間隔T3とに分割され得る。

40

【0058】

[0075]第1の時間間隔T1は、下流回路120の電力を供給するために電力スイッチ130が初めてオンにされた時刻に始まる。第1の時間間隔のあいだ、電力スイッチ130の抵抗は、比較的速度1520で減少する。たとえば、所定の電圧降下限度（たとえば、5%）に対し、電力スイッチ130の抵抗は、従来のモデリング技法を用いて決定されたであろう速度よりもずっと速い速度で減少し得る。これは、本開示の実施形態では、電力スイッチが初めてオンにされたときにPDNから見た下流回路120の静電容量が小さく、したがって電力スイッチ130の抵抗が電圧降下限度以内におとどまりながら、より速い速度で減少できることを正確に決定するからである。上で論じられたように、下流回路120の静電容量は、電力スイッチ130が初めてオンにされたとき、下流回路120の電源レイルが下流回路120内のトランジスタがオンになる電圧に達するのに十分

50

なだけ長く電力スイッチがオンにされていたときより、小さい。

**【0059】**

[0076]第1の時間間隔T1は、下流回路120の電源レイルが、下流回路内のトランジスタのしきい値電圧にほぼ等しい電圧に達した時刻に終わり得る。上で論じられたように、下流回路の静電容量は、PDNからみて、下流回路120内のトランジスタがオンになり、下流回路内のキャパシタまでの経路を開通するにつれて増大する。トランジスタのしきい値電圧は、トランジスタの絶対しきい値電圧の平均値を指し得る。

**【0060】**

[0077]第2の時間間隔T2のあいだ、電力スイッチ130の抵抗は、第1の時間間隔T1と比較して遅い速度1530で減少する。たとえば、電力スイッチ130の抵抗は、50%以上遅い速度で減少し得る。これは、下流回路の静電容量が、PDNから見て、第2の時間間隔T2のあいだ、第1の時間間隔T1と比較して大きいからである。たとえば、第2の時間間隔T2のほとんどまたは全部でのあいだ、下流回路120の電源レイルの電圧は、下流回路内のトランジスタのしきい値電圧を超える可能性があり、そのような場合において、トランジスタがオンにされる。結果として、下流回路の静電容量は、PDNから見て、第2の時間間隔T2のほとんどまたは全部のあいだ、その最終値に近くなり得る。

**【0061】**

[0078]第2の時間間隔T2は、下流回路120の電源レイルの電圧が基準の供給電圧に近い電圧に落ち着いた時刻に終わり得る。たとえば、第2の時間間隔T2は、下流回路120の供給電圧と基準の供給電圧との間の電圧差がほぼ電圧降下限度以下になったときに終わり得る。

**【0062】**

[0079]第3の時間間隔T3のあいだ、電力スイッチ130の抵抗は、第2の時間間隔T2および第1の時間間隔T1よりも速い速度1540で減少し得る。これは、電圧降下が下流回路120の供給電圧と基準の供給電圧との間の電圧差に制限されるからである。すなわち、電圧差が小さいときは、電力スイッチ130の抵抗の低下が大きくても、小さい電圧降下しか生じない。

**【0063】**

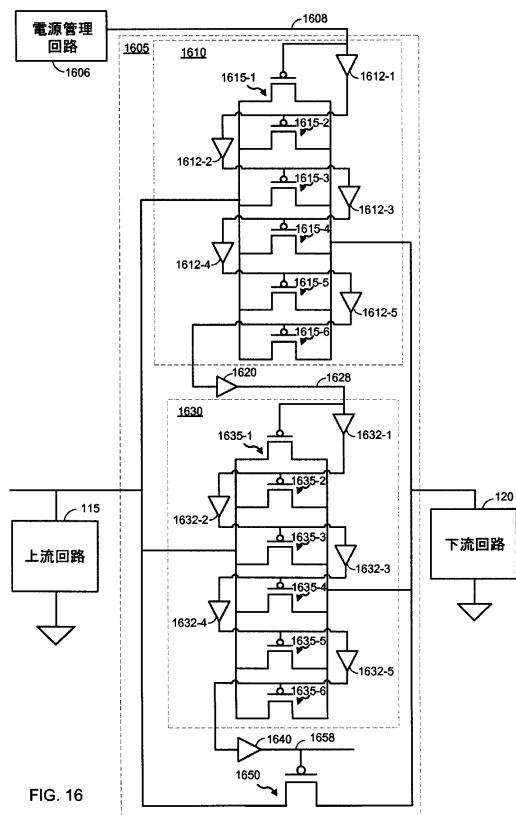

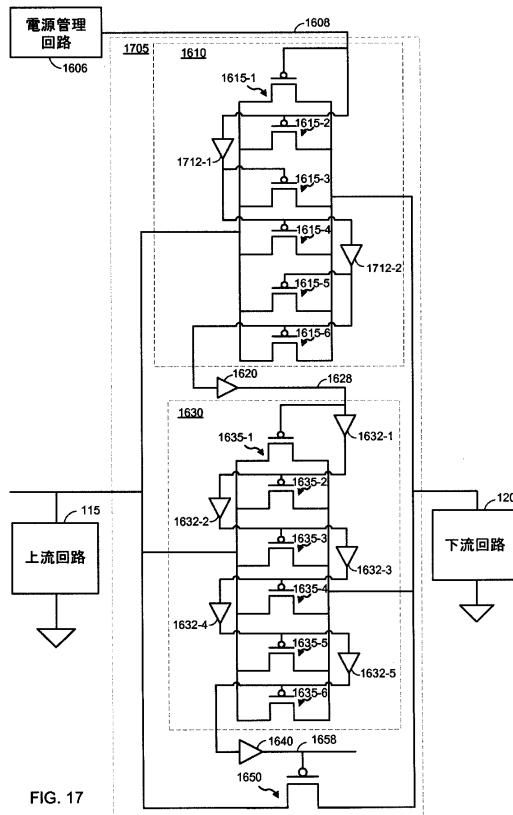

[0080]図16は、本開示の実施形態による、図15に示された抵抗プロファイル1510を実施するための電力スイッチ1605の一例を示す。電力スイッチ1605は、第1のスイッチ回路1610と、第2のスイッチ回路1630と、第3のスイッチ1650とを備える。

**【0064】**

[0081]第1のスイッチ回路1610は、抵抗プロファイル1510の第1の時間間隔T1に対応する部分を実施し、スイッチ1615-1から1615-6の第1の組と、遅延要素1612-1から1612-5の第1の組とを備える。図を簡単にするために図16には6つのスイッチが示されているが、スイッチ1615-1から1615-6の第1の組はもっと多くのスイッチ（たとえば、数百または数千のスイッチ）を備え得ることを理解されたい。スイッチ1615-1から1615-6のそれぞれは、上流回路115と下流回路120の間に結合される。図16は原寸に比例して描かれていない、スイッチのサイズは、図を簡単にするために上流回路115および下流回路120に対して誇張されていることを理解されたい。図16に示された例では、スイッチ1615-1から1615-6のそれぞれは、PFETを用いて実施される。遅延要素1612-1から1612-5は直列に結合され、それぞれの遅延要素1612-1から1612-5は、スイッチ1615-1から1615-6のうちの1つのゲートに結合される。

**【0065】**

[0082]下流回路120の電力を供給するために電力スイッチ1605がオンにされるべきとき、電源管理回路1606が、スイッチ1615-1から1615-6の第1の組をオンにし始めるために、遅延要素1612-1から1612-5の第1の組に信号160

10

20

30

40

50

8を入力する。信号が延要素1612-1から1612-5の第1の組を通って伝わるについて、遅延要素1612-1から1612-5は、スイッチ1615-1から1615-6を順次オンにする。オンになる隣接スイッチ間の遅延は、その隣接スイッチ間の遅延要素の遅延にほぼ等しい。たとえば、オンになるスイッチ1615-1と1615-2の間の遅延は、遅延要素1612-1の遅延にほぼ等しい。図を簡単にするために図16の例では、一度に1つのスイッチがオンにされるとして示されているが、多数のスイッチを一度にオンにできることを理解されたい(たとえば、第1のスイッチ回路1610が数百または数千のスイッチを備える場合)。

#### 【0066】

[0083]第2のスイッチ回路1630は、抵抗プロファイル1510の第2の時間間隔T2に対応する部分を実施し、スイッチ1635-1から1635-6の第2の組と、遅延要素1632-1から1632-5の第2の組とを備える。図を簡単にするために図16には6つのスイッチが示されているが、スイッチ1635-1から1635-6の第2の組はもっと多くのスイッチ(たとえば、数百または数千のスイッチ)を備え得ることを理解されたい。また、スイッチの第1および第2の組は異なる数のスイッチを有し得ることも理解されたい。スイッチ1635-1から1635-6のそれぞれは、上流回路115と下流回路120の間に結合される。図16に示された例では、スイッチ1635-1から1635-6のそれぞれは、P F E Tを用いて実施される。遅延要素1632-1から1632-5は直列に結合され、それぞれの遅延要素1632-1から1632-5の出力は、スイッチ1635-1から1635-6のうちの1つのゲートに結合される。

10

#### 【0067】

[0084]スイッチ1615-1から1615-6の第1の組がオンにされた後で、スイッチ1635-1から1635-6の第2の組をオンにし始めるために、信号1628が遅延要素1632-1から1632-5の第2の組に入力される。信号1628は、スイッチ1612-1から1612-5の第1の組によって出力される信号の遅延されたバージョンであり得る。たとえば、遅延要素1612-1から1612-5の第1の組によって出力された信号は、遅延要素1620によって遅延された後に、遅延要素1632-1から1632-5の第2の組に入力され得る。あるいは、遅延要素1612-1から1612-5の第1の組によって出力された信号は、スイッチ1615-1から1615-6の第1の組がオンにされたことの確認として電源管理回路1606へ戻して入力され得、電源管理回路1606は、スイッチ1635-1から1635-6の第2の組をオンにし始めるために、時間設定した遅延の後に信号1628を立ち上げ得る。信号1628が遅延要素1632-1から1632-5の第2の組を通して伝わるについて、遅延要素1632-1から1632-5は、スイッチ1635-1から1635-6を順次オンにする。

30

#### 【0068】

[0085]第3のスイッチ1650は、抵抗プロファイル1510の第3の時間間隔T3に対応する部分を実施する。第3のスイッチ1650は、上流回路115と下流回路120の間に結合される。第3のスイッチ1650は、1つまたは複数の強いスイッチ(低抵抗スイッチ)を使用して実施することができ、それぞれの強いスイッチは、スイッチの第1および第2の組内のスイッチそれよりもずっと低い抵抗(すなわち、ずっと高いコンダクタンス)を有し得る。

40

#### 【0069】

[0086]スイッチ1635-1から1635-6の第2の組がオンにされた後、信号1658が、第3のスイッチ1650をオンにするために、第3のスイッチ1650に入力される。信号1658は、遅延要素1632-1から1632-5の第2の組によって出力される信号の遅延されたバージョンであり得る。たとえば、遅延要素1632-1から1632-5の第2の組によって出力される信号は、遅延要素1640によって遅延された後に、第3のスイッチ1650に入力され得る。あるいは、遅延要素1632-1から1632-5の第2の組によって出力された信号は、スイッチ1635-1から1635-6の第2の組がオンにされたことの確認として電源管理回路1606へ戻して入力され得

50

、電源管理回路 1606 は、第 3 のスイッチ 1650 をオンにするための時間設定した遅延の後に信号 1658 を立ち上げることができる。第 3 のスイッチ 1650 が複数の強いスイッチを有する例では、強いスイッチはほぼ同時に転じられ得、あるいは強いスイッチは、遅延要素の組を使用して順次にオンにされ得る。

#### 【0070】

[0087] すなわち、電力スイッチ 1605 は可変抵抗を有し、所定の時刻における電力スイッチ 1605 の抵抗は、所定の時刻にオンにされるスイッチ 1615-1 から 1615-6 と、1635-1 から 1635-6 と、1650 とに依存する。この抵抗は、スイッチのすべてがオンにされたときに最小になる。遅延要素 1612-1 から 1612-5、1620、1632-1 から 1632-5、および 1640 は、電力供給のあいだスイッチ 1615-1 から 1615-6 と、1635-1 から 1635-6 と、1650 とをオンにするためのタイミングシーケンスを制御し、したがって、電力供給のあいだ電力スイッチ 1605 の抵抗を制御する。すなわち、遅延要素 1612-1 から 1612-5、1620、1632-1 から 1632-5、および 1640 は、電力供給のあいだ電力スイッチ 1605 の抵抗を制御するように構成されたスイッチ制御回路を形成し得る。10

#### 【0071】

[0088] 上で論じられたように、第 1 の時間間隔 T1 のあいだ、電力スイッチ 130 の抵抗は、第 2 の時間間隔 T2 と比較して速い速度で減少する。これは、本開示の様々な実施形態による図 16 の電力スイッチ 1605 を使用して実施され得る。

#### 【0072】

[0089] 1 つの実施形態では、スイッチ 1615-1 および 1615-6 の第 1 の組内の各スイッチの抵抗は、スイッチ 1635-1 から 1635-6 の第 2 の組内の各スイッチの抵抗よりも低くされ得る。結果として、スイッチ 1615-1 から 1615-6 の第 1 の組内のスイッチのうちの 1 つがオンになると、電力スイッチ 1605 の抵抗は、スイッチ 1635-1 から 1635-6 の第 2 の組内のスイッチのうちの 1 つがオンになるとよりも大きく低下する。20

#### 【0073】

[0090] 別の実施形態では、遅延要素 1612-1 から 1612-5 の第 1 の組内の各遅延要素の遅延は、遅延要素 1632-1 から 1632-5 の第 2 の組内の各遅延要素の遅延よりも短いことがあり得る。これは、スイッチ 1615-1 から 1615-6 の第 1 の組内のスイッチを、スイッチ 1635-1 から 1635-6 の第 2 の組内のスイッチと比較して速い速度でオンにさせ、したがって、電力スイッチ 1605 の抵抗を速い速度で低下させる。この実施形態では、スイッチ 1615-1 から 1615-6 の第 1 の組内のスイッチのそれぞれが、スイッチ 1635-1 から 1635-6 の第 2 の組内のスイッチのそれぞれとほぼ同じ抵抗を有し得る。30

#### 【0074】

[0091] 別の実施形態では、スイッチ 1615-1 から 1615-6 の第 1 の組内の 2 つ以上のスイッチは、並行して一度にオンされ得、その一例が図 17 に示されている。この例では、第 1 のスイッチ回路 1710 が遅延要素 1712-1 から 1712-2 の組を備え、それぞれの遅延要素の出力がスイッチのうちの 2 つを並行してオンにする。第 1 の時間間隔 T1 のあいだにスイッチのうちの 2 つ以上を並行して一度にオンにすることによって、電力スイッチ 1705 の抵抗は、より速い速度で第 1 の時間間隔 T1 のあいだに減少する。この実施形態では、スイッチ 1615-1 から 1615-6 の第 1 の組内のスイッチのそれぞれは、スイッチ 1635-1 から 1635-6 の第 2 の組内のスイッチのそれぞれとほぼ同じ抵抗を有し得る。40

#### 【0075】

[0092] スイッチ 1635-1 から 1635-6 の第 2 の組内の 2 つ以上のスイッチはまた、並行して一度にオンにされ得ることを理解されたい。この場合、スイッチ 1635-1 から 1635-6 の第 2 の組と比較して、スイッチ 1615-1 から 1615-6 の第 1 の組内により多数のスイッチが一度にオンにされ得る。たとえば、スイッチ 1635-50

1から1635-6の第2の組と比較して2倍も多い、スイッチ1615-1から1615-6の第1の組内のスイッチを一度にオンにされ得る。

【0076】

[0093]上で論じられた実施形態のうちの任意の2つ以上が、第2の時間間隔T2と比較して、第1の時間間隔T1のあいだにより速い速度で電力スイッチの抵抗を減少させるために、組み合わせて使用される得ることを理解されたい。たとえば、スイッチ1615-1から1615-6の第1の組内のスイッチは、スイッチ1635-1から1615-6の第2の組内のスイッチよりも低い抵抗を有することも、速い速度でオンになることもできる。

【0077】

[0094]抵抗プロファイル1510は、図を簡単にするために図15では区分線形であるとして示されているが、抵抗プロファイル1510はこの例に限定されないことを理解されたい。たとえば、電力スイッチ130の抵抗は、各時間間隔のうちの1つの中で一定の速度で減少する必要がない。この例では、ある時間間隔のあいだに電力スイッチ130の抵抗が減少する速度は、その抵抗が減少する平均速度によって与え得、それは次式の通りに表すことができる。

【数11】

$$r_{avg} = \frac{\Delta R}{\Delta T} \quad (10)$$

10

20

ここで、 $r_{avg}$ はその時間間隔のあいだに抵抗が減少する平均速度であり、Rはその時間間隔全体にわたる抵抗の低下であり、Tは時間間隔の継続時間である。第1の時間間隔T1では、抵抗の低下Rは、第1の時間間隔T1中の最初のスイッチがオンになった後の電力スイッチの抵抗と、第1の時間間隔T1のあいだに最後のスイッチがオンになった後の電力スイッチの抵抗との差によって与えられ得る。これは、電力スイッチ130のオフ抵抗が計算に含まれないように行われ得る。

【0078】

[0095]第2の時間間隔T2について、抵抗の低下Rは、第2の時間間隔T2のあいだに最初のスイッチがオンになった後の電力スイッチの抵抗と、第2の時間間隔T2のあいだに最後のスイッチがオンになった後の電力スイッチの抵抗との差によって与えられ得る。あるいは、第2の時間間隔T2について、抵抗の低下Rは、第1の時間間隔T1のあいだに最後のスイッチがオンになった後の電力スイッチの抵抗と、第2の時間間隔T2のあいだに最後のスイッチがオンになった後の電力スイッチの抵抗との差によって与えられ得る。

30

【0079】

[0096]第3の時間間隔T3について、抵抗の低下Rは、第3の時間間隔T3のあいだに最初のスイッチがオンになった後の電力スイッチの抵抗と、第3時間間隔T3のあいだに最後のスイッチがオンになった後の電力スイッチの抵抗との差によって与えられ得る。あるいは、第3の時間間隔T3では、抵抗の低下Rは、第2の時間間隔T2のあいだに最後のスイッチがオンになった後の電力スイッチの抵抗と、第3の時間間隔T3のあいだに最後のスイッチがオンになった後の電力スイッチの抵抗との差によって与えられ得る。

40

【0080】

[0097]上で論じられたように、第1の時間間隔T1と第2の時間間隔T2との間の境界は、下流回路120の電圧が下流回路120内のトランジスタのしきい値電圧にほぼ等しくなる時刻と一致し得る。一般に、この境界は、電圧がしきい値電圧のある百分率（たとえば、しきい値電圧の70%以上、しきい値電圧の80%以上、またはしきい値電圧の90%以上）になる時刻と一致し得る。

【0081】

50

[0098]上で論じられたように、第2の時間間隔T2と第3の時間間隔T3との間の境界は、下流回路120の電圧が基準の供給電圧に近い電圧に落ち着く時刻に一致し得る。一般に、この境界は、電圧がしきい値電圧基準の供給電圧のある百分率（たとえば、基準の供給電圧の90%以上）になる時刻と一致し得る。

#### 【0082】

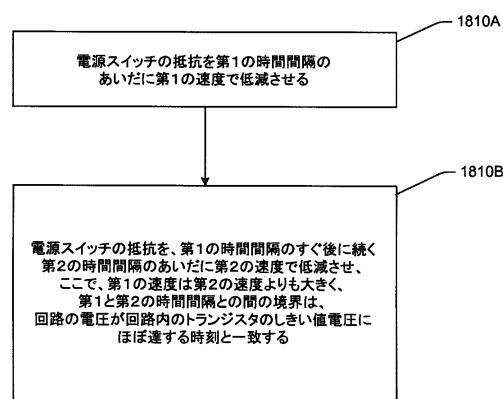

[0099]図18Aおよび図18Bは、本開示の実施形態によるシステムにおけるパワーゲーティングのための方法1800を示す。回路（たとえば、下流回路120）と、この回路と電力供給源の間に結合された電力スイッチ（たとえば、電力スイッチ130）とを備えるシステム。

#### 【0083】

[0100]図18Aに示されるように、ステップ1810で、電力スイッチは回路が不活性状態から起動されるべきときにオンにされる。ステップ1810はさらに、図18Bに示されるステップ1810Aおよび1810Bを備える。ステップ1810Aで、電力スイッチの抵抗は、第1の時間間隔のあいだに第1の速度で減少させる。ステップ1810Bで、電力スイッチの抵抗は、第1の時間間隔のすぐ後に続く第2の時間間隔のあいだに第2の速度で減少させられ、ここにおいて、第1の速度は第2の速度よりも大きく、第1と第2の時間間隔との間の境界は、回路の電圧が回路内のトランジスタのしきい値電圧にほぼ達する時刻と一致する。上で論じられたように、トランジスタのしきい値電圧は、トランジスタの絶対閾値電圧の平均値を指し得る。

#### 【0084】

[0101]当業者には、本明細書に記載の回路が多様なトランジスタタイプを使用して実現され得ること、したがって、図に示された特定のトランジスタタイプに限定されないことが理解されよう。たとえば、バイポーラ接合トランジスタ、接合電界効果トランジスタ、または他の任意のトランジスタタイプを使用することができる。当業者にはまた、本明細書に記載の回路が、CMOS、バイポーラ接合トランジスタ（BJT）、バイポーラCMOS（BiCMOS）、シリコンゲルマニウム（SiGe）、ガリウムひ素（GaAs）などの様々なIC製法技術を用いて製造され得ることが理解されよう。

#### 【0085】

[0102]当業者にはまた、本明細書に記載の方法（たとえば、回路の電圧に依存する静電容量をモデル化するための方法）が、その方法を実行するためのプロセッサ（たとえば、汎用プロセッサ）によって実行可能であるコード（命令）をコンピュータプログラムが備える、コンピュータ可読媒体に格納されているコンピュータプログラム（たとえば、ソフトウェア）の形で具現化され得ることが理解されよう。コンピュータ可読媒体は、RAMメモリ、フラッシュメモリ、ハードディスク、取外し可能ディスク、CD-ROM、もしくは他の光ディスク記憶装置、または当技術分野で知られているコンピュータ可読媒体の他の任意の形を備えることができる。

#### 【0086】

[0103]本開示の前記の説明は、当技術分野の当業者が本開示を作製または使用できるようにするために提供されている。本開示に対する様々な修正が当業者には容易に明らかになるであろうし、本明細書において定義された一般的な原理は、本開示の趣旨および範囲から逸脱することなく、他の変形形態に適用することができる。すなわち、本開示は、本明細書に記載された例に限定されるものではなく、本明細書において開示された原理および新規の特徴と一致する最も広い範囲が与えられるものである。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

#### [C1]

回路の電圧に依存する静電容量を決定するための方法であって、

複数の電圧のそれぞれにおいて前記回路のパラメータを測定することと、

それぞれの電圧について、前記回路の抵抗 - キャパシタ（RC）モデルを前記電圧における前記回路の測定されたパラメータにフィッティングすることによって、前記電圧における前記回路の静電容量を決定することと、

10

20

30

40

50

を備える、方法。

[ C 2 ]

それぞれの電圧における前記回路の前記パラメータが、前記電圧における前記回路のインピーダンスを備える、C 1 に記載の方法。

[ C 3 ]

それぞれの電圧における前記回路の前記静電容量を決定することが、前記電圧における前記回路の測定されたインピーダンスと前記 R C モデルのインピーダンスとの間の誤差を最小にする静電容量を決定することを備える、C 2 に記載の方法。

[ C 4 ]

それぞれの電圧における前記回路の前記パラメータを測定することが、

前記電圧における前記回路の S パラメータを測定することと、

前記電圧における前記回路の前記 S パラメータを前記電圧における前記回路の前記インピーダンスに変換することと、

を備える、C 2 に記載の方法。

[ C 5 ]

それぞれの電圧における前記回路の前記静電容量を決定することが、

前記電圧における前記測定されたパラメータを極の式に変換することと、

前記 R C モデルの極を前記極の式にフィッティングすることと、

を備える、C 1 に記載の方法。

[ C 6 ]

システムであって、

回路と、

前記回路が活性状態にあるときに前記回路を電力供給源に接続するように、および前記回路が不活性状態にあるときに前記回路を前記電力供給源から切り離すように構成された電力スイッチ、ここにおいて、前記電力スイッチが可変な抵抗を有する、と、

第 1 の時間間隔のあいだに第 1 の速度で前記電力スイッチの前記抵抗を減少させ、前記第 1 の時間間隔のすぐ後に続く第 2 の時間間隔のあいだに第 2 の速度で前記電力スイッチの前記抵抗を減少させることによって、前記不活性状態から前記活性状態へと前記回路の電力が増加するように電源回路の抵抗を制御するように構成されたスイッチ制御回路、ここにおいて、前記第 1 の速度が前記第 2 の速度よりも大きく、前記第 1 と第 2 の時間間隔との間の境界が、前記回路の電圧が前記回路内のトランジスタのしきい値電圧にほぼ達する時刻と一致する、と、

を備えるシステム。

[ C 7 ]

前記第 1 の速度が前記第 2 の速度の少なくとも 2 倍である、C 6 に記載のシステム。

[ C 8 ]

前記スイッチ制御回路が、前記第 2 の時間間隔の後に続く第 3 の時間間隔のあいだに第 3 の速度で前記電力スイッチの前記抵抗を減少させるように構成され、前記第 3 の速度が前記第 1 および第 2 の速度よりも大きい、C 6 に記載のシステム。

[ C 9 ]

前記第 2 と第 3 の時間間隔との間の境界が、前記回路の電圧が前記電力供給源の基準の供給電圧の 90 パーセント以上になる時刻と一致する、C 8 に記載のシステム。

[ C 10 ]

前記電力スイッチが第 1 の複数のスイッチと、第 2 の複数のスイッチとを備え、前記スイッチ制御回路が、前記第 1 の時間間隔のあいだに前記第 1 の複数のスイッチをオンにするように、ならびに前記第 2 の時間間隔のあいだに前記第 2 の複数のスイッチをオンにするように構成される、C 6 に記載のシステム。

[ C 11 ]

前記第 1 の複数のスイッチが前記第 2 の複数のスイッチよりも速い速度でオンにされる、C 10 に記載のシステム。

10

20

30

40

50

[ C 1 2 ]

前記第1の複数のスイッチ中の少なくとも2つのスイッチが並行してオンにされる、C 1 0に記載のシステム。

[ C 1 3 ]

前記第1の複数のスイッチのそれぞれが、前記第2の複数のスイッチのそれよりも低い抵抗を有する、C 1 0に記載のシステム。

[ C 1 4 ]

回路と、前記回路と電力供給源の間に結合された電力スイッチとを備えるシステムにおけるパワーゲーティングのための方法であって、

前記回路が不活性状態から起動されるべきときに前記電力スイッチをオンにすることを備え、ここにおいて、前記電力スイッチをオンにすることが、

第1の時間間隔のあいだに第1の速度で前記電力スイッチの抵抗を減少させることと、

前記第1の時間間隔のすぐ後に続く第2の時間間隔のあいだに第2の速度で前記電力スイッチの前記抵抗を減少させること、ここにおいて、前記第1の速度が前記第2の速度よりも大きく、前記第1と第2の時間間隔との間の境界が、前記回路の電圧が前記回路内のトランジスタのしきい値電圧にほぼ達する時刻と一致する、と、

を備える、方法。

[ C 1 5 ]

前記第1の速度が前記第2の速度の少なくとも2倍である、C 1 4に記載の方法。

20

[ C 1 6 ]

前記第2の時間間隔の後に続く第3の時間間隔のあいだに第3の速度で前記電力スイッチの前記抵抗を減少させること、ここにおいて、前記第3の速度が前記第1および第2の速度よりも大きい、

をさらに備える、C 1 4に記載の方法。

[ C 1 7 ]

前記第2と第3の時間間隔との間の境界が、前記回路の電圧が前記電力供給源の基準の供給電圧の90パーセント以上になる時刻と一致する、C 1 6に記載の方法。

[ C 1 8 ]

前記電力スイッチが第1の複数のスイッチと、第2の複数のスイッチとを備え、前記方法がさらに、

30

前記第1の時間間隔のあいだに前記第1の複数のスイッチをオンにすることと、

前記第2の時間間隔のあいだに前記第2の複数のスイッチをオンにすることと、

を備える、C 1 4に記載の方法。

[ C 1 9 ]

前記第1の複数のスイッチが前記第2の複数のスイッチよりも速い速度でオンにされる、C 1 8に記載の方法。

[ C 2 0 ]

前記第1の複数のスイッチ中の少なくとも2つのスイッチが並行してオンにされる、C 1 8に記載の方法。

40

[ C 2 1 ]

前記第1の複数のスイッチのそれぞれが、前記第2の複数のスイッチのそれよりも低い抵抗を有する、C 1 8に記載の方法。

[ C 2 2 ]

回路と、前記回路と電力供給源の間に結合された電力スイッチとを備えるシステムにおけるパワーゲーティングのための装置であって、前記装置は、

前記回路が不活性状態から起動されるべきときに前記電力スイッチをオンにするための手段を備え、ここにおいて、前記電力スイッチをオンにするための前記手段が、

第1の時間間隔のあいだに第1の速度で前記電力スイッチの抵抗を減少させるための手段と、

50

前記第1の時間間隔のすぐ後に続く第2の時間間隔のあいだに第2の速度で前記電力スイッチの前記抵抗を減少させるための手段、ここにおいて、前記第1の速度が前記第2の速度よりも大きく、前記第1と第2の時間間隔との間の境界が、前記回路の電圧が前記回路内のトランジスタのしきい値電圧にほぼ達する時刻と一致する、と、

を備える、装置。

[ C 2 3 ]

前記第1の速度が前記第2の速度の少なくとも2倍である、C 2 2に記載の装置。

[ C 2 4 ]

前記第2の時間間隔の後に続く第3の時間間隔のあいだに第3の速度で前記電力スイッチの前記抵抗を減少させるための手段、ここにおいて、前記第3の速度が前記第1および第2の速度よりも大きい、

をさらに備える、C 2 2に記載の装置。

[ C 2 5 ]

前記第2と第3の時間間隔との間の境界が、前記回路の電圧が前記電力供給源の基準の供給電圧の90パーセント以上になる時刻と一致する、C 2 4に記載の装置。

[ C 2 6 ]

前記電力スイッチが第1の複数のスイッチと、第2の複数のスイッチとを備え、前記装置がさらに、

前記第1の時間間隔のあいだに前記第1の複数のスイッチをオンにするための手段と、前記第2の時間間隔のあいだに前記第2の複数のスイッチをオンにするための手段と、を備える、C 2 2に記載の装置。

[ C 2 7 ]

前記第1の複数のスイッチが前記第2の複数のスイッチよりも速い速度でオンにされる、C 2 6に記載の装置。

[ C 2 8 ]

前記第1の複数のスイッチ中の少なくとも2つのスイッチが並行してオンにされる、C 2 6に記載の装置。

[ C 2 9 ]

前記第1の複数のスイッチのそれぞれが、前記第2の複数のスイッチのそれぞれよりも低い抵抗を有する、C 2 6に記載の装置。

10

20

30

【図 1】

図 1

FIG. 1

【図 2】

FIG. 2

【図 3】

図 3

FIG. 3

【図 4】

FIG. 4

【図5】

FIG. 5

【図6A】

FIG. 6A

【図6B】

FIG. 6B

【図7】

図7

FIG. 7

【図 8】

FIG. 8

【図 9】

図 9

FIG. 9

【図 10】

FIG. 10

【図 11】

図 11

FIG. 11

【図 1 2】

図 12

【図 1 3】

FIG. 13

【図 1 4】

図 14

【図 1 5】

図 15

【図16】

図16

【図17】

図17

【図18A】

図18A

1800

FIG. 18A

【図18B】

図18B

FIG. 18B

---

フロントページの続き

(72)発明者 コーツ、ライアン・マイケル

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 及川 尚人

(56)参考文献 特開2008-065732(JP,A)

特開2010-010920(JP,A)

特開2008-034667(JP,A)

特開2012-134321(JP,A)

特開2009-170651(JP,A)

特開2009-105221(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/00

G01R 27/26

G06F 17/50

H02J 1/00