(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3987163号

(P3987163)

(45) 発行日 平成19年10月3日(2007.10.3)

(24) 登録日 平成19年7月20日(2007.7.20)

(51) Int.C1.

F 1

G 06 F 1/18 (2006.01)

H 04 L 25/02 (2006.01)G 06 F 1/00

H 04 L 25/02320 J

V

請求項の数 8 (全 18 頁)

(21) 出願番号

特願平9-215806

(22) 出願日

平成9年7月25日(1997.7.25)

(65) 公開番号

特開平11-45130

(43) 公開日

平成11年2月16日(1999.2.16)

審査請求日

平成16年7月8日(2004.7.8)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(74) 代理人 100086564

弁理士 佐々木 聖孝

(72) 発明者 斎藤 比斗志

東京都港区北青山3丁目6番12号 青山

富士ビル 日本テキサス・インスツルメン

ツ株式会社内

審査官 石井 茂和

最終頁に続く

(54) 【発明の名称】データ通信システム

## (57) 【特許請求の範囲】

## 【請求項1】

第1および第2の装置間で少なくとも一対の信号線が着脱可能に接続され、各々の前記装置は前記一対の信号線を差動式で駆動することによって信号を相手側の前記装置に送信し、

前記第1の装置には、アクティブモード中に前記一対の信号線に共通に印加するための前記差動式駆動法に応じた第1のバイアス電圧を発生し、かつパワーダウンモード中は前記第1のバイアス電圧の発生を止める第1のバイアス発生手段と、パワーダウンモード中に前記一対の信号線の片方に印加するための前記差動式駆動法に依存しない第2のバイアス電圧を発生し、かつアクティブモード中に前記第2のバイアス電圧の発生を止める第2のバイアス発生手段とが設けられ、

前記第2の装置には、前記信号線上に前記第1または第2のバイアス電圧が印加されているか否かを検出するためのバイアス検出手段が設けられているデータ通信システム。

## 【請求項2】

前記第1および第2の装置間で第1および第2の信号線対が着脱可能に接続され、前記第1の信号線対について前記第1の装置に前記第1および第2のバイアス発生手段が設けられるとともに前記第2の装置に前記バイアス検出手段が設けられ、前記第2の信号線対について前記第2の装置に前記第1のバイアス発生手段が設けられるとともに前記第1の装置に前記バイアス検出手段が設けられている請求項1に記載のデータ通信システム。

## 【請求項3】

10

20

請求項 2 に記載のデータ通信システムにおけるシステム起動方法において、前記第 1 および第 2 の装置が共にパワーダウンモード中で、かつ両装置間に前記第 1 および第 2 の信号線対が接続されていない時に前記第 1 の装置側で前記第 2 のバイアス発生手段より前記第 2 のバイアス電圧の発生を開始する第 1 のステップと、

前記第 1 のステップの後に、前記第 1 および第 2 の装置間における前記第 1 および第 2 の信号線対の接続に応答して、前記第 2 の装置側で前記バイアス検出手段により前記第 1 の対の信号線を介して前記第 2 のバイアス電圧を検出する第 2 のステップと、

前記第 2 のステップの直後に前記第 2 の装置側がアクティブモードになって前記第 1 のバイアス電圧発生手段より前記第 2 の信号線対に対して前記第 1 のバイアス電圧の発生を開始する第 3 のステップと、

前記第 3 のステップの直後に前記第 1 の装置側で前記バイアス検出手段により前記第 2 の信号線対を介して前記第 1 のバイアス電圧を検出する第 4 のステップと、

前記第 4 のステップの直後に前記第 1 の装置側がアクティブモードになる第 5 のステップと、

前記第 5 のステップの直後に前記第 1 および第 2 の装置間で初期化のためのデータ通信を行う第 6 のステップと

を有するシステム起動方法。

#### 【請求項 4】

請求項 2 に記載のデータ通信システムにおけるシステム起動方法において、

前記第 1 および第 2 の装置が共にパワーダウンモード中で、かつ両装置間に前記第 1 および第 2 の信号線が接続されている時に前記第 1 の装置側で前記第 2 のバイアス発生手段より前記第 2 のバイアス電圧の発生を開始する第 1 のステップと、

前記第 1 のステップの後に前記第 2 の装置で前記バイアス検出手段により前記第 1 の信号線対を介して前記第 2 のバイアス電圧を検出する第 2 のステップと、

前記第 2 のステップの直後に前記第 2 の装置側がアクティブモードになって前記第 1 のバイアス電圧発生手段より前記第 2 の信号線対に対して前記第 1 のバイアス電圧の発生を開始する第 3 のステップと、

前記第 3 のステップの直後に前記第 1 の装置側で前記バイアス検出手段により前記第 2 の信号線対を介して前記第 1 のバイアス電圧を検出する第 4 のステップと、

前記第 4 のステップの直後に前記第 1 の装置側がアクティブモードになる第 5 のステップと、

前記第 5 のステップの直後に前記第 1 および第 2 の装置間で初期化のためのデータ通信を行う第 6 のステップと

を有するシステム起動方法。

#### 【請求項 5】

前記第 1 および第 2 の装置間で第 1 および第 2 の信号線対が着脱可能に接続され、前記第 1 の信号線対について前記第 1 の装置に前記第 1 および第 2 のバイアス発生手段が設けられるとともに前記第 2 の装置に前記バイアス検出手段が設けられ、前記第 2 の信号線対について前記第 2 の装置に前記第 1 および第 2 のバイアス発生手段が設けられるとともに前記第 1 の装置に前記バイアス検出手段が設けられる請求項 1 に記載のデータ通信システム。

#### 【請求項 6】

請求項 5 に記載のデータ通信システムにおけるシステム起動方法において、

前記第 1 および第 2 の装置が共にパワーダウンモード中で、かつ両装置間に前記第 1 および第 2 の信号線が接続されていない時に前記第 1 の装置側で前記第 2 のバイアス発生手段より前記第 2 のバイアス電圧の発生を開始する第 1 のステップと、

前記第 1 のステップの後に、前記第 1 および第 2 の装置間における前記第 1 および第 2 の信号線対の接続に応答して、前記第 2 の装置側で前記バイアス検出手段により前記第 1 の信号線対を介して前記第 2 のバイアス電圧を検出するとともに前記第 1 の装置側で前記バイアス検出手段により前記第 2 の信号線対を介して前記第 2 のバイアス電圧を検出する

第2のステップと、

前記第2のステップの直後に前記第1および第2の装置がそれぞれアクティブモードになる第3のステップと、

前記第3のステップの直後に前記第1および第2の装置間で初期化のためのデータ通信を行う第4のステップと

を有するシステム起動方法。

【請求項7】

請求項5に記載のデータ通信システムにおけるシステム起動方法において、

前記第1および第2の装置が共にパワーダウンモード中で、かつ両装置間に前記第1および第2の信号線対が接続されている時に両装置側でそれぞれ前記第2のバイアス発生手段より前記第2のバイアス電圧の発生を開始する第1のステップと、

前記第1のステップの直後に前記第2の装置側で前記バイアス検出手段により前記第1の信号線対を介して前記第2のバイアス電圧を検出するとともに前記第1の装置側で前記バイアス検出手段により前記第2の信号線対を介して前記第2のバイアス電圧を検出する第2のステップと、

前記第2のステップの直後に前記第1および第2の装置がそれぞれアクティブモードになる第3のステップと、

前記第3のステップの直後に前記第1および第2の装置間で初期化のためのデータ通信を行う第4のステップと

を有するシステム起動方法。

【請求項8】

前記第2のバイアス発生手段が、前記第2のバイアス電圧に対応した電源電圧を供給する電源電圧端子に電気的に接続されたソース端子と、前記片側の信号線に電気的に接続されるドレイン端子とを有するMOSトランジスタと、前記MOSトランジスタのゲート端子に電気的に接続され、パワーダウンモード中は前記MOSトランジスタをオンにし、アクティブモード中は前記MOSトランジスタをオフにする制御手段とを含む請求項1または5に記載のデータ通信システム。

【発明の詳細な説明】

【0010】

【発明の属する技術分野】

本発明は、2つの装置間で一対の信号線に所定の共通バイアス電圧を印加しながら差動方式で両信号線を駆動することによって信号を伝送するデータ通信システムに関する。

【0020】

【従来の技術】

この種のデータ通信システムの例として、IEEE1394と規定されたインターフェースを挙げることができる。このIEEE1394は、マルチメディア向けのパソコン用周辺装置インターフェース規格であり、同一のネットワーク上で100Mbps, 200Mbps, 400Mbpsの3種類のデータ転送速度が可能であり、周辺装置同士間のデータ転送も可能となっている。

【0030】

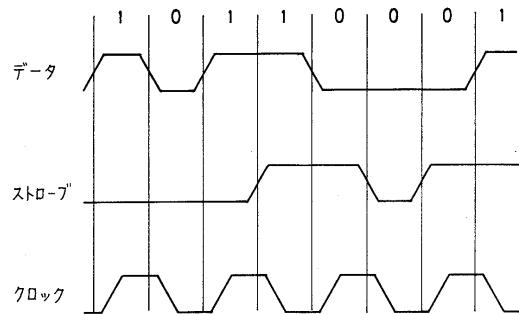

IEEE1394では、2組の信号線対からなるケーブル上でシリアルバスを構築し、DS-Link符号化方式によってデータを伝送する。ここで、DS-Link符号化方式とは、図11に示すように、送信側より一系統の信号線上でデータ信号を送ると同時にもう一つの系統の信号線上でストローブ信号を送り、受信側で両信号の排他的論理和をとって同期用のクロック信号を再生する方式である。この方式は、スタートビットやストップビットを用いる一般的のシリアル転送フォーマットと比べて伝送効率が高いうえ、スキュー・マージンが大きいためクロック周波数またはデータ転送速度を向上できるという利点がある。

【0040】

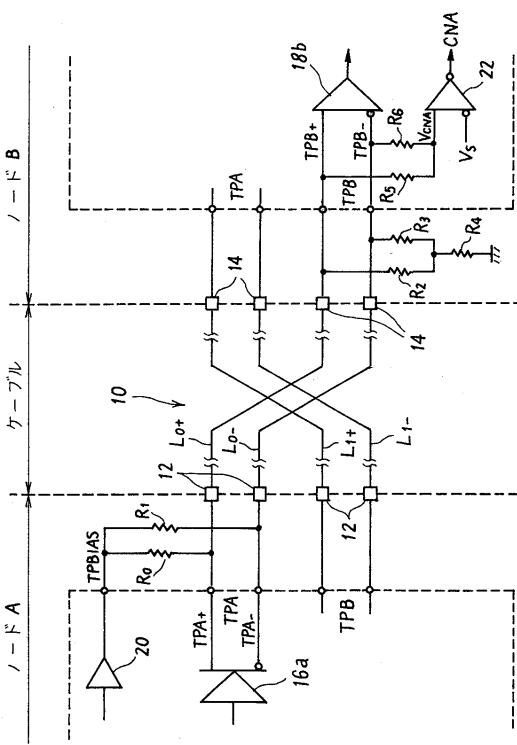

図12に、IEEE1394規格に基づく従来のデータ通信システムにおけるケーブル周

10

20

30

40

50

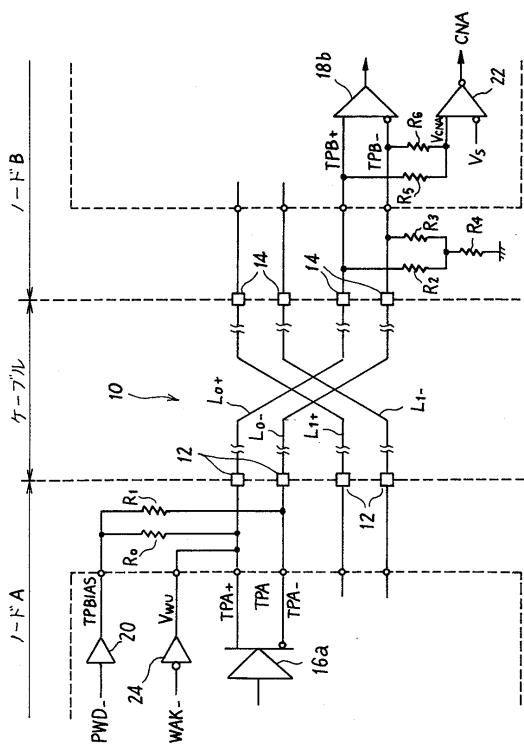

りの要部の構成を示す。IEEE1394インタフェースを有する2つの装置またはノードA, B間には、ケーブル10の2組の信号線対[L0+, L0-]、[L1+, L1-]がコネクタ12, 14を介して着脱可能に接続される。

#### 【0050】

各々のノードA, Bには2組のポートTPA, TPBが備えられ、櫛掛け式で自ノードのポートTPAが相手ノードのポートTPBに電気的に接続され、自ノードのポートTPBが相手ノードのポートTPAに電気的に接続される。

#### 【0060】

より詳細には、第1の信号線対L0+, L0-を介してノードAのポートTPAのドライバ16aからノードBのポートTPBのレシーバ18bへストローブ信号が伝送されるとともに、第2の信号線対L1+, L1-を介してノードAのポートTPBのドライバ(図示せず)からノードBのポートTPAのレシーバ(図示せず)へデータ信号が伝送されるようになっている。

#### 【0070】

一方、第2の信号線対L1+, L1-を介してノードBのポートTPAのドライバ(図示せず)からノードAのポートTPBのレシーバ(図示せず)へストローブ信号が伝送されるとともに、第1の信号線対L0+, L0-を介してノードBのポートTPBのドライバ(図示せず)からノードAのポートTPAのレシーバ(図示せず)へデータ信号が伝送されるようになっている。

#### 【0080】

各ノードA, BのポートTPAでは、アクティブな動作状態の下で増幅器20よりDS-LINK符号化方式の差動駆動法に基づく一定電圧値(たとえば1.8V)を有するコモンモード電圧TPBIASを抵抗R0, R1を介してノード内信号線TPA+, TPA-に印加する。ドライバ16aより出力される振幅値がたとえば200mVの差動信号はこのコモンモード電圧TPBIASに重畠してケーブル10の信号線対[L0+, L0-]上を伝送され、相手ノードのポートTPBで終端抵抗[R2, R3, R4]を介してレシーバ18bに受信される。

#### 【0090】

一方、各ノードA, BのポートTPBでは、コンパレータ22が抵抗R5, R6を介してラインTPB+, TPB-に接続されている。両ノードA, B間にケーブル10が接続されているときは、ノードAからのコモンモード電圧TPBIASがケーブル10の信号線対[L0+, L0-]を介してノードBのポートTPBに伝達されることにより、コンパレータ22には比較基準電圧VSよりも高い入力電圧VCNAが入力され、所定の論理値たとえば論理値Lのコンパレータ出力CNAが得られる。

#### 【0100】

このように、各ノードA, Bは、コンパレータ22で相手ノードからのコモンモード電圧TPBIASの有無を検出することにより、ケーブル10が接続されているか否か、および相手ノードがアクティブな動作状態にあるか否かを判別するようにしている。

#### 【0110】

【発明が解決しようとする課題】

ところで、IEEE1394インタフェースを組み込む装置の中でも、ディジタルカメラのようなバッテリ駆動型のアプリケーションでは、通常、消費電力を抑えるために、データ転送を行わない間はこの規格のインターフェース回路(デバイス)をパワーダウンモードに設定している。パワーダウンモードの期間中、デバイス内ではケーブル接続状態検出用のコンパレータ22を除いてほとんどの回路(特にコモンモード電圧発生用の増幅器20)がシャットダウン状態に置かれる。

#### 【0120】

したがって、ユーザがデータ転送のためにケーブル10を接続した時に、両ノードA, Bの双方がパワーダウンモードになっている場合には、どちらからもケーブル10にコモンモード電圧TPBIASが供給されないため、どちらもコモンモード電圧TPBIASを検出すること

10

20

30

40

50

ができず、自動的にアクティブモードに切り替わることができない。つまり、周辺装置をケーブルでつなぐと直ちに使える状態にするプラグ・アンド・プレイ機能が保証できない。

#### 【0130】

この問題を回避するために、パワーダウンモード中も増幅器20を動作させてコモンモード電圧TPBIASを出力させるようにすると、この増幅器20内で多くの電力が消費され、ケーブル未接続時の消費電力が増加してしまう。コモンモード電圧TPBIASは、差動駆動式のデータ転送を実現するためのバイアス電圧である。このような差動駆動式データ転送用のバイアス電圧を発生するための増幅器20は、不可避的に相当の電力を消費する回路構成を有している。

10

#### 【0140】

本発明は、上記の問題点に鑑みてなされたもので、パワーダウンモード中に電力消費を抑えながらケーブル接続状態を直ちに検出できるようにしたデータ通信システムを提供することを目的とする。

#### 【0150】

また、本発明は、マルチメディア・システムにおいて効率的かつ確実なプラグ・アンド・プレイ機能を保証できるようにしたデータ通信システムを提供することを目的とする。

#### 【0160】

##### 【課題を解決するための手段】

上記の目的を達成するために、本発明のうち請求項1に記載のデータ通信システムは、第1および第2の装置間で少なくとも一対の信号線が着脱可能に接続され、各々の前記装置は前記一対の信号線を差動式で駆動することによって信号を相手側の前記装置に送信し、前記第1の装置には、アクティブモード中に前記一対の信号線に共通に印加するための前記差動式駆動法に応じた第1のバイアス電圧を発生し、かつパワーダウンモード中は前記第1のバイアス電圧の発生を止める第1のバイアス発生手段と、パワーダウンモード中に前記一対の信号線の片方に印加するための前記差動式駆動法に依存しない第2のバイアス電圧を発生し、かつアクティブモード中に前記第2のバイアス電圧の発生を止める第2のバイアス発生手段とが設けられ、前記第2の装置には、前記信号線上に前記第1または第2のバイアス電圧が印加されているか否かを検出するためのバイアス検出手段が設けられている構成とした。

20

#### 【0170】

また、請求項2に記載のデータ通信システムは、請求項1に記載のシステムにおいて、前記第1および第2の装置間で第1および第2の信号線対が着脱可能に接続され、前記第1の信号線対について前記第1の装置に前記第1および第2のバイアス発生手段が設けられるとともに前記第2の装置に前記バイアス検出手段が設けられ、前記第2の信号線対について前記第2の装置に前記第1のバイアス発生手段が設けられるとともに前記第1の装置に前記バイアス検出手段が設けられている構成とした。

30

#### 【0180】

また、請求項3に記載のシステム起動方法は、請求項2に記載のデータ通信システムにおけるシステム起動方法において、前記第1および第2の装置が共にパワーダウンモード中で、かつ両装置間に前記第1および第2の信号線対が接続されていない時に前記第1の装置側で前記第2のバイアス発生手段より前記第2のバイアス電圧の発生を開始する第1のステップと、前記第1のステップの後に、前記第1および第2の装置間ににおける前記第1および第2の信号線対の接続に応答して、前記第2の装置側で前記バイアス検出手段により前記第1の対の信号線を介して前記第2のバイアス電圧を検出する第2のステップと、前記第2のステップの直後に前記第2の装置側がアクティブモードになって前記第1のバイアス電圧発生手段より前記第2の信号線対に対して前記第1のバイアス電圧の発生を開始する第3のステップと、前記第3のステップの直後に前記第1の装置側で前記バイアス検出手段により前記第2の信号線対を介して前記第1のバイアス電圧を検出する第4のステップと、前記第4のステップの直後に前記第1の装置側がアクティブモードになる第50

40

5のステップと、前記第5のステップの直後に前記第1および第2の装置間で初期化のためのデータ通信を行う第6のステップとを有する方法とした。

【0190】

また、請求項4に記載のシステム起動方法は、請求項2に記載のデータ通信システムにおけるシステム起動方法において、前記第1および第2の装置が共にパワーダウンモード中で、かつ両装置間に前記第1および第2の信号線が接続されている時に前記第1の装置側で前記第2のバイアス発生手段より前記第2のバイアス電圧の発生を開始する第1のステップと、前記第1のステップの後に前記第2の装置で前記バイアス検出手段により前記第1の信号線対を介して前記第2のバイアス電圧を検出する第2のステップと、前記第2のステップの直後に前記第2の装置側がアクティブモードになって前記第1のバイアス発生手段より前記第2の信号線対に対して前記第1のバイアス電圧の発生を開始する第3のステップと、前記第3のステップの直後に前記第1の装置側で前記バイアス検出手段により前記第2の信号線対を介して前記第1のバイアス電圧を検出する第4のステップと、前記第4のステップの直後に前記第1の装置側がアクティブモードになる第5のステップと、前記第5のステップの直後に前記第1および第2の装置間で初期化のためのデータ通信を行う第6のステップとを有する方法とした。 10

【0200】

また、請求項5に記載のデータ通信システムは、請求項1に記載のシステムにおいて、前記第1および第2の装置間で第1および第2の信号線対が着脱可能に接続され、前記第1の信号線対について前記第1の装置に前記第1および第2のバイアス発生手段が設けられるとともに前記第2の装置に前記バイアス検出手段が設けられ、前記第2の信号線対について前記第2の装置に前記第1および第2のバイアス発生手段が設けられるとともに前記第1の装置に前記バイアス検出手段が設けられる構成とした。 20

【0210】

また、請求項6に記載のシステム起動方法は、請求項5に記載のデータ通信システムにおけるシステム起動方法において、前記第1および第2の装置が共にパワーダウンモード中で、かつ両装置間に前記第1および第2の信号線が接続されていない時に前記第1の装置側で前記第2のバイアス発生手段より前記第2のバイアス電圧の発生を開始する第1のステップと、前記第1のステップの後に、前記第1および第2の装置間ににおける前記第1および第2の信号線対の接続に応答して、前記第2の装置側で前記バイアス検出手段により前記第1の信号線対を介して前記第2のバイアス電圧を検出するとともに前記第1の装置側で前記バイアス検出手段により前記第2の信号線対を介して前記第2のバイアス電圧を検出する第2のステップと、前記第2のステップの直後に前記第1および第2の装置がそれぞれアクティブモードになる第3のステップと、前記第3のステップの直後に前記第1および第2の装置間で初期化のためのデータ通信を行う第4のステップとを有するシステム起動方法とした。 30

【0220】

また、請求項7に記載のシステム起動方法は、請求項5に記載のデータ通信システムにおけるシステム起動方法において、前記第1および第2の装置が共にパワーダウンモード中で、かつ両装置間に前記第1および第2の信号線対が接続されている時に両装置側でそれぞれ前記第2のバイアス発生手段より前記第2のバイアス電圧の発生を開始する第1のステップと、前記第1のステップの直後に前記第2の装置側で前記バイアス検出手段により前記第1の信号線対を介して前記第2のバイアス電圧を検出するとともに前記第1の装置側で前記バイアス検出手段により前記第2の信号線対を介して前記第2のバイアス電圧を検出する第2のステップと、前記第2のステップの直後に前記第1および第2の装置がそれぞれアクティブモードになる第3のステップと、前記第3のステップの直後に前記第1および第2の装置間で初期化のためのデータ通信を行う第4のステップとを有する方法とした。 40

【0230】

また、請求項8に記載のデータ通信システムは、請求項1または5に記載のシステムにお

いて、前記第2のバイアス発生手段が、前記第2のバイアス電圧に対応した電源電圧を供給する電源電圧端子に電気的に接続されたソース端子と、前記片側の信号線に電気的に接続されるドレイン端子とを有するMOSトランジスタと、前記MOSトランジスタのゲート端子に電気的に接続され、パワーダウンモード中は前記MOSトランジスタをオンにし、アクティブモード中は前記MOSトランジスタをオフにする制御手段とを含む構成とした。

#### 【0240】

##### 【発明の実施の形態】

以下、図1～図10を参照して本発明の実施例を説明する。

#### 【0250】

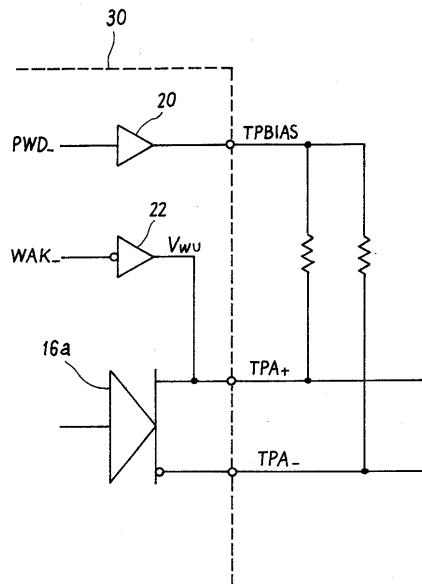

図1に、本発明の一実施例によるデータ通信システムにおけるケーブル周りの要部の構成を示す。この実施例のシステムは、IEEE1394規格に適合するものであり、従来システム(図12)と共通する構成・機能を有する部分には同一の符号を付している。

#### 【0260】

このシステムにおいて、従来システムと相違する主要な点は、少なくとも一方のノード(装置または機器)たとえばノードAより、パワーダウンモード中にケーブル接続状態モニタ用またはウェイクアップ用のバイアス電圧V<sub>WU</sub>が outputされることである。このバイアス電圧V<sub>WU</sub>を発生するために、ノードAにはウェイクアップ・バッファ24が設けられる。

#### 【0270】

このウェイクアップ・バッファ24はたとえばP型MOSトランジスタからなり、その出力端子(ドレイン端子)はオープンドレイン接続方式でプリント配線を介してポートTPAの片側の信号線たとえばTPA+に接続されている。

#### 【0280】

両ノードA, B間にケーブル10が接続され、かつノードAのウェイクアップ・バッファ24がオン状態になっていると、その出力端子よりバイアス電圧V<sub>WU</sub>がケーブル10の信号線対[L0+, L0-]を介して相手ノードBのポートTPBへ伝達され、ノードBのケーブル接続状態検出用のコンパレータ22がバイアス電圧V<sub>WU</sub>を検出するようになっている。

#### 【0290】

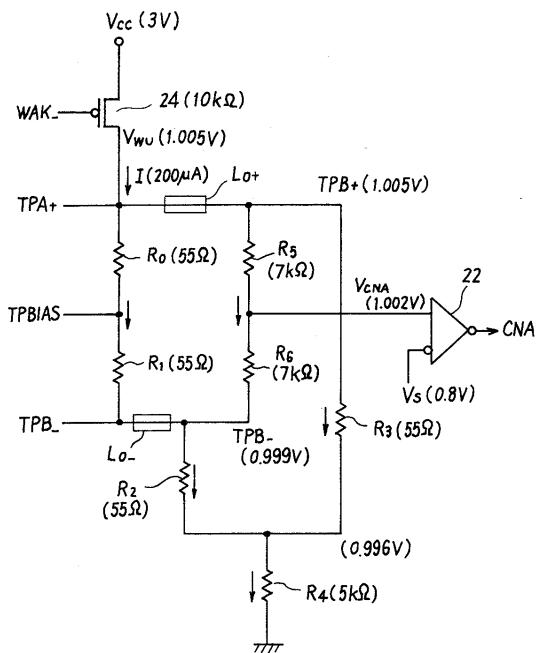

図2に、ウェイクアップ・バッファ24がオン状態になっている時の電流および電位分布を等価回路で示す。なお、この等価回路では、ケーブル10[L0+, L0-]の抵抗を無視している。また、パワーダウンモード中なので、増幅器20はシャットダウン状態になり、その出力(TPBIAS)はハイインピーダンスになっている。

#### 【0300】

ウェイクアップ・バッファ24を構成するP型MOSトランジスタのソース端子にはたとえば3Vの電源電圧V<sub>cc</sub>が供給され、ゲート端子には制御部からのウェイクアップ制御信号WAK+が与えられる。ウェイクアップ制御信号WAK+が論理値L(たとえば0.0V)になっている時に、このP型MOSトランジスタ24はオンになる。

#### 【0310】

一方、IEEE1394にしたがいTPBIAS用のバイアス抵抗[R0, R1]、ケーブル終端抵抗[R2, R3, R4]およびコンパレータ入力抵抗[R5, R6]はそれぞれ規定の抵抗値を有している。すなわち、[R0, R1]は[55, 55]、[R2, R3, R4]は[55, 55, 5k]、[R5, R6]は[7k, 7k]に選ばれている。また、コンパレータ22に与えられる比較基準電圧Vsも規格で0.8Vに設定されている。

#### 【0320】

したがって、オン状態のトランジスタ24の抵抗つまりオン抵抗をたとえば10kに選ぶと、そのドレイン電圧(バイアス電圧)V<sub>WU</sub>が1.005V、ドレイン電流Iが200μAになり、相手ノードBにおけるコンパレータ22の入力電圧V<sub>CNA</sub>は基準値Vs(0.8V)よりも十分に高い値(約1.002V)になる。これによって、コモンモード電

10

20

30

40

50

圧TPBIASが検出されるときと同様に、コンパレータ22の出力CNAが論理値Lとなり、ケーブル10が接続されているというモニタ情報が得られる。

#### 【0340】

このように、パワーダウンモード中でも、一方のノードAのウェイクアップ・バッファ24がアクティブ状態でポートTPAに所要のバイアス電圧VWUを供給することにより、両ノードA,B間にケーブル10が接続されれば、該バイアス電圧VWUがケーブル10を介して相手ノードBのポートTPBに伝達されてケーブル接続状態検出用コンパレータ22で検出される。これによって、ノードBはケーブル10が接続されていることを認識できる。

#### 【0350】

後述するように、ノードBにウェイクアップ・バッファ24が設けられていなくても、上記のようなノードAからのウェイクアップ用バイアス電圧VWUに応動してノードBはアクティブな動作状態に切り替わり、ノードB側の増幅器20よりコモンモード電圧TPBIASを出力することができる。そして、このノードBからのコモンモード電圧TPBIASがケーブル10を介してノードAに伝達されることにより、ノードAも自己のコンパレータ22によってケーブル10が接続されていることを認識し、アクティブ動作状態に切り替わることができる。すなわち、パワーダウンモード中でも、ケーブル10が接続されたなら、両ノードA,Bが速やかにアクティブな動作状態に切り替わるようになっており、プラグ・アンド・プレイ機能が保証されている。

#### 【0360】

本実施例によれば、ウェイクアップ・バッファ24がアクティブ状態になっている間、ケーブル10が接続されていない場合には、電源電圧端子Vccとグランドとの間で電流バスが形成されないため、電力の消費はない。なお、この時のウェイクアップ・バッファ24の出力電圧またはバイアス電圧VWUは電源電圧Vcc(3V)にほぼ等しい電圧値になっている。

#### 【0370】

ケーブル10が接続されると、図2に示すように、電源電圧端子Vccとグランド間で各部に電流バスが形成され、各抵抗である程度の電力が消費される。しかし、ウェイクアップ・バッファ24の出力電圧(バイアス電圧)VWUは、コモンモード電圧TPBIASとは異なり、データ伝送の規格(差動駆動方式)には拘束されず、相手ノードBのコンパレータ22に検出可能な最低限の電圧値で足りる。このため、単位時間当たりの電力消費量が少ない。しかも、上記のように、ケーブル10が接続された直後に、両ノードA,Bが自動的かつ速やかにパワーダウンモードからアクティブモードに切り替わるので、ウェイクアップ機能に伴う消費電力は時間的にも非常に少ない。

#### 【0380】

また、通常のデータ転送時には、ウェイクアップ・バッファ24がシャットダウンされるため、本来のIEEE1394規格には何の影響も与えなくて済む。

#### 【0390】

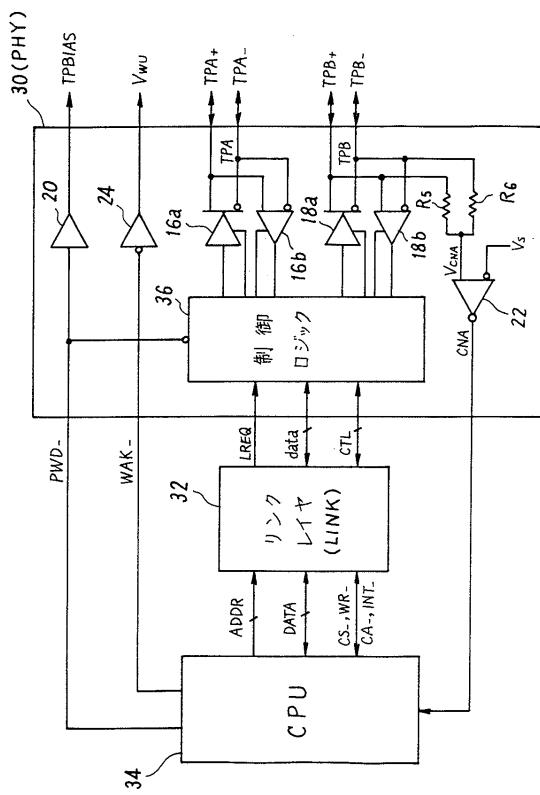

図3に、本実施例におけるノードA内のインターフェース部の構成を示す。このインターフェース部は、フィジカル・レイヤ(物理層またはPHY)30、リンク・レイヤ(リンク層またはLINK)32およびマイクロプロセッサ(CPU)34の3個のチップから構成される。これらのチップのうち、フィジカル・レイヤ30およびリンク・レイヤ32がIEEE規格のインターフェース回路(デバイス)である。

#### 【0400】

ウェイクアップ・バッファ24は、フィジカル・レイヤ30内に設けられ、CPU34よりウェイクアップ制御信号WAK\_を受け取る。また、コモンモード電圧TPBIASを発生するための増幅器20も、フィジカル・レイヤ30内に設けられ、CPU34よりパワーダウン信号PWD\_を受け取る。

#### 【0410】

フィジカル・レイヤ30内には、IEEE1394規格にしたがい、2つの差動式トラン

10

20

30

40

50

シーバ [ 16 a , 16 b ] 、 [ 18 a , 18 b ] と、ケーブル接続状態検出用コンパレータ 22 および制御ロジック 36 も設けられている。相手ノード B でも、IEEE1394 規格にしたがい同様のコモンモード電圧発生用増幅器 20 、 2 つの差動式トランシーバ [ 16 a , 16 b ] 、 [ 18 a , 18 b ] 、ケーブル接続状態検出用コンパレータ 22 および制御ロジック 36 が設けられている。もちろん、ノード B も、本実施例によるウェイクアップ・バッファ 24 を有していてよい。

#### 【 0420 】

ノード A の両トランシーバ [ 16 a , 16 b ] 、 [ 18 a , 18 b ] は、ケーブル 10 を介して繋掛けでノード B の両トランシーバ [ 16 a , 16 b ] 、 [ 18 a , 18 b ] と電気的に接続される。

10

#### 【 0430 】

つまり、両ノード A , B 間にケーブル 10 が接続されると、ノード A のポート TPA のトランシーバ [ 16 a , 16 b ] は第 1 の信号線対 [ L0+ , L0- ] を介してノード B のポート TPB のトランシーバ [ 18 a , 18 b ] と電気的に接続され、ノード A のポート TPB のトランシーバ [ 18 a , 18 b ] は第 2 の信号線対 [ L1+ , L1- ] を介してノード B のポート TPA のトランシーバ [ 16 a , 16 b ] と電気的に接続される。

#### 【 0440 】

そして、データ通信時には、第 1 の信号線対 L0+ , L0- を介してノード A のポート TPA のドライバ 16 a からノード B のポート TPB のレシーバ 18 b ヘストローブ信号がシリアル伝送されるとともに、第 2 の信号線対 L1+ , L1- を介してノード A のポート TPB のドライバ 18 a からノード B のポート TPA のレシーバ 16 b ヘデータ信号がシリアル伝送される。

20

#### 【 0450 】

一方、第 2 の信号線対 L1+ , L1- を介してノード B のポート TPB のドライバ 18 a からノード A のポート TPA のレシーバ 16 b ヘデータ信号がシリアル伝送されるとともに、第 1 の信号線対 L0+ , L0- を介してノード B のポート TPA のドライバ 16 a からノード A のポート TPB のレシーバ 18 b ヘストローブ信号がシリアル伝送される。

#### 【 0460 】

増幅器 20 は、CPU34 からのパワーダウン信号 PWD\_ が論理値 H レベルのときにアクティブ状態となって、差動式ライン駆動のためのコモンモード電圧 TPBIAS ( 1 . 8 V ) を出力する。この増幅器 20 からのコモンモード電圧 TPBIAS は、バイアス抵抗 R0 , R1 を介してポート TPA の信号線 TPA+ , TPA- に印加される。上記したように、ケーブル 10 が接続されているときは、ノード A 側からのコモンモード電圧 TPBIAS はケーブル 10 の信号線対 [ L0+ , L0- ] を介して相手ノード B のポート TPB に伝達され、ケーブル接続状態検出用のコンパレータ 22 によって検出される。

30

#### 【 0470 】

パワーダウン信号 PWD\_ が論理値 L レベルになると、増幅器 20 はシャットダウン状態となり、消費電力を発生しない。

#### 【 0480 】

ノード A のコンパレータ 22 は、相手ノード B よりケーブル 10 の信号線対 [ L1+ , L1- ] を介してポート TPB に送られてきたコモンモード電圧 TPBIAS を検出する。また、相手ノード B にもウェイクアップ・バッファ 24 が設けられている場合、ノード A のコンパレータ 22 は、ノード B よりケーブル 10 の信号線対 [ L1+ , L1- ] を介してポート TPB に送られてきたウェイクアップ用バイアス電圧 V\_WU をも検出することになる。コンパレータ 22 の出力信号 CNA は CPU34 に与えられる。

40

#### 【 0490 】

コンパレータ 22 は、CPU34 からのパワーダウン信号 PWD\_ とは無関係に、当該ノードに電源が入っている限り継続的に動作する。また、コンパレータ 22 に対する比較基準電圧 VS も、当該ノードに電源が入っている限り図示しない基準電圧発生器より継続的に与えられる。

50

**【0500】**

フィジカル・レイヤ30内の制御ロジック36は、両トランシーバ[16a, 16b], [18a, 18b]におけるドライバ/レシーバの切替制御、送信データの符号化処理、受信データの復調処理等を行うほか、後述するバス初期化のためのロジックやバス・アビトレーションのためのロジック等を有している。

**【0510】**

制御ロジック36は、CPU34からのパワーダウン信号PWD\_が論理値Hレベルのときにアクティブな動作状態となり、パワーダウン信号PWD\_が論理値Lレベルのときはパワーダウン状態またはシャットダウン状態となる。制御ロジック36がシャットダウン状態にある間は、両トランシーバ[16a, 16b], [18a, 18b]もシャットダウン状態に置かれる。10

**【0520】**

リンク・レイヤ32は、フィジカル・レイヤ30とCPU34との間に介在するインターフェースであり、データ転送モードの制御、パケット処理、CRC(巡回冗長検査)生成・検査処理等を行う。リンク・レイヤ32とフィジカル・レイヤ30の制御ロジック36との間では、割込み信号LREQ、制御信号CTL、2ビット・データdata等がやりとりされる。リンク・レイヤ32とCPU34との間では、アドレス信号ADDR、各種制御信号(チップ選択信号CS\_、書込み/読み出し制御信号WR\_等)、割込み信号INT\_および8ビット・データDATA等がやりとりされる。

**【0530】**

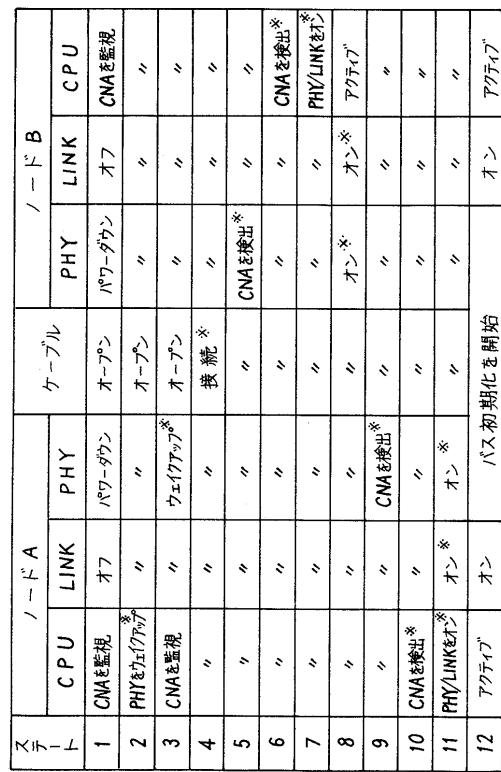

次に、図4～図8につき本実施例のシステムにおいて両ノードA, Bがパワーダウンモードからバス全体を起動させるまでのシーケンスを説明する。また、図9には、比較例として、従来システムにおいて問題となる場合を示す。なお、これらの図において、記号\*は当該遷移状態が発生したことを示す。20

**【0540】**

先ず、従来システムでは、本発明によるウェイクアップ・バッファ24に相当するものがない。したがって、図9に示すように、両ノードA, Bがパワーダウンモードになっている最中に、ケーブル10が接続されても(ステート4)、両ノードA, Bのどちらもそのことに気付かず、プラグ・アンド・プレイ機能が働くかない。

**【0550】**

これに対して、本実施例では、以下に説明するように、両ノードA, Bがパワーダウンモード中にあっても、ケーブル10が接続された時は、直ちに両ノードがアクティブノードに切り替わり、プラグ・アンド・プレイ機能が働くようになっている。しかも、消費電力の増大を招くことなく実現できる。30

**【0560】**

本実施例において、図4の例は、ウェイクアップ・バッファ24が一方のノードAにのみ設けられており、他方のノードBには設けられていない場合である。

**【0570】**

図4において、初期状態では、ケーブル10が接続されておらず、かつ両ノードA, Bがパワーダウンモードになっている(ステート1)。もっとも、上記したように、パワーダウンモード中でも、各ノードA, Bにおいてフィジカル・レイヤ30内のケーブル接続状態検出用のコンパレータ22はアクティブ状態にあり、CPU34はコンパレータ22の出力CNAの状態または論理値を監視している。40

**【0580】**

次に、ノードAのCPU34は、フィジカル・レイヤ30に対してウェイクアップ制御信号WAK\_をアクティブ(論理値L)にする(ステート2)。たとえば、ノードAでデータ転送のための何らかのボタン操作が行われた時に、このウェイクアップ制御が実行されてよい。

**【0590】**

これにより、ノードA内では、CPU34からのウェイクアップ制御信号WAK\_に応動50

してフィジカル・レイヤ30のウェイクアップ・バッファ24がオン状態になり、ウェイクアップ用のバイアス電圧VWUを発生する(ステート3)。しかし、未だケーブル10が接続されていないため、ウェイクアップ・バッファ24の出力(オープンコレクタ出力)はハイインピーダンス状態になっている。したがって、このステート3の期間がいくら長く続いても、電力の消費はほとんどない。

#### 【0600】

その後、両ノードA,B間にケーブル10が接続される(ステート4)。そうすると、ノードAのウェイクアップ・バッファ24からのバイアス電圧VWUがケーブル10の信号線対[L0+, L0-]を介して相手ノードBのポートTPBへ伝達され、ノードBのコンパレータ22がバイアス電圧VWUまたはVCNAを検出する(ステート5)。

10

#### 【0610】

次いで、ノードB内では、CPU34がコンパレータ22の出力(論理値LのCNA)を認識する(ステート6)。これによって、ノードBは起動シーケンスに入り、CPU34がフィジカル・レイヤ30およびリンク・レイヤ32をアクティブ状態に切り替える(ステート7)。すなわち、フィジカル・レイヤ30に対してはパワーダウン信号PWD\_を非アクティブ(論理値H)に切り替え、リンク・レイヤ32に対しては所定の制御信号たとえばチップ選択信号CS\_をアクティブ(論理値L)にする。

#### 【0620】

これにより、ノードB内では、3つのチップ30, 32, 34が全てアクティブな動作状態になり(ステート8)、フィジカル・レイヤ30の増幅器20よりコモンモード電圧TPBIASが発生される。

20

#### 【0630】

ノードBからのコモンモード電圧TPBIASは、ケーブル10の信号線対[L1+, L1-]を介してノードAのポートTPBに伝えられ、ノードAのコンパレータ22にバイアス電圧VCNAとして検出される(ステート9)。

30

#### 【0640】

次いで、ノードA内では、CPU34がコンパレータ22の出力(論理値LのCNA)を認識する(ステート10)。これによって、ノードAも起動シーケンスに入り、CPU34がフィジカル・レイヤ30およびリンク・レイヤ32をアクティブ状態に切り替える(ステート11)。

#### 【0650】

この際、フィジカル・レイヤ30に対しては、パワーダウン信号PWD\_が非アクティブ(論理値H)に切り替わると同時に(入れ代わりに)、ウェイクアップ信号WAK\_が非アクティブ(論理値H)に切り替わる。これによって、ウェイクアップ・バッファ24はオフ状態になる。

#### 【0660】

こうして、両ノードA,B間でケーブル10が接続され、かつ各ノードのインターフェース部がオン状態になったことで、バス・リセットが行われ、それぞれのフィジカル・レイヤ30, 30の間でIEEE1394規格に基づいた所定の手順でバス初期化が実行される(ステート12)。

40

#### 【0670】

このように、この例では、ノードBにウェイクアップ・バッファ24が設けられていないくとも、ケーブル10が接続された時点で、ノードAからのウェイクアップ用バイアス電圧VWUに応動してノードBがパワーダウンモードからアクティブモードに切り替わることができる。そして、このアクティブ状態になったノードBの起動シーケンスを利用して、ノードAもパワーダウンモードからアクティブモードに切り替わることができ、バス全体の起動が速やかに行われる。

#### 【0680】

図5の例は、ケーブル10が最初から接続されている場合であり、他の条件は図4の例と同じである。この場合は、ノードAでウェイクアップ・バッファ24が作動するや否や、

50

そのウェイクアップ用バイアス電圧VWUがケーブル10を介して相手ノードBに伝達され、ノードBのコンパレータ22に検出される。したがって、ノードAでウェイクアップを開始してからノードBがそれに気付くまでの待ち時間(ステート4)が実質的に省かれる。それ以外の動作は図4の例と同じである。

#### 【0690】

図6の例は、両ノードA,Bの双方にウェイクアップ・バッファ24が設けられている場合である。この場合は、パワーダウンモード中に両ノードA,Bがそれぞれのウェイクアップ・バッファ24をオン状態にする(ステート2,3)。この間、ケーブル10が未接続でも、各ノードでウェイクアップ・バッファ24が電力を消費することはない。そして、ケーブル10が接続されると(ステート4)、両ノードA,Bは互いに相手ノードからのバイアス電圧VWUを検出して(ステート5,6)、同時または並列的にアクティブ状態に切り替わり(ステート7,8)、直ちにバス初期化を開始することができる(ステート12)。

10

#### 【0700】

なお、最初からケーブル10が接続されている場合で、両ノードA,Bがほぼ同時にそれぞれのウェイクアップ・バッファ24をオンにしたときは、ケーブル接続までの待機時間(ステート3)が省かれる。それ以外は、図6と同様の動作が行われる。また、パワーダウンモード中に両ノードA,Bの一方が先にウェイクアップ・バッファ24をオンにしたときは、図4または図5と同様の動作が行われる。

#### 【0710】

20

図7は、上記した図4の例でノードBに他のノードCが別のケーブルを介して接続されている場合である。ノードAの動作は、図7では省略しているが、図4と同じである。

#### 【0720】

この場合、ノードBは、IEEE1394対応の2つのポート#1,#2を有し、ポート#1でノードAと接続され、ポート#2でノードCに接続される。各ポート#1,#2には個別のフィジカル・レイヤ30が充てられ、各フィジカル・レイヤ30は独立して動作する。しかし、いずれかのポート(図7では#1)が他のノード(A)とつながると、全てのポート(#1,#2)で一斉にバス初期化が行われる(ステート12)。

#### 【0730】

30

IEEE1394規格では、デイジチーン方式またはノード分岐方式により同一のネットワーク上に多数のノードを接続することが可能であり、いずれかのノードでケーブルの抜き差しが行われる度にバス・リセットないしバス初期化が行われ、新たなネットワーク・トポロジが構築される。

#### 【0740】

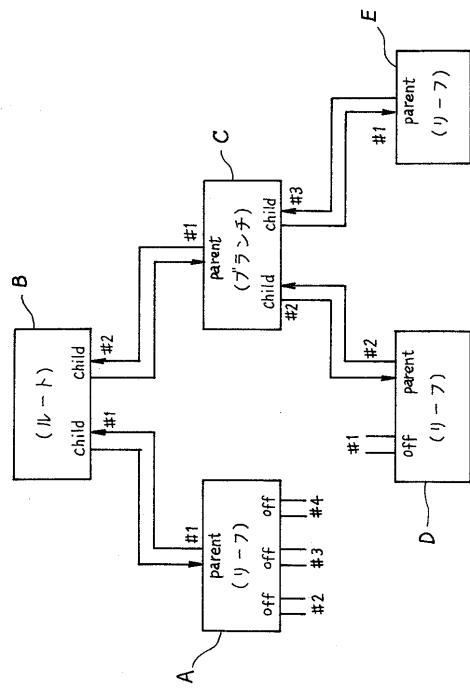

図8に、IEEE1394におけるネットワーク・トポロジの一例を示す。図8において、ケーブル接続されたポート#を1本しか持たないノードA,D,Eは、それぞれがネットワークの端にあるノード(リーフ)であることを認識し、その接続先つまり親(parent)であるノードB,Cに対して問い合わせを行う。そうすると、ノードB,Cは、その問い合わせを受けた自己のポート#1,(#2,#3)で親子関係を確認すると同時に、それ以外にケーブル接続されている他のポート#2,#1から接続先のノード(C,B)に対してさらに問い合わせを行う。こうして順次親子関係が決まっていく。

40

#### 【0750】

この例では、ノードB,Cが互いに問い合わせを出し合う。この場合は、両ノードB,C間でルートを決定するためのやりとりが所定の手順で行われる。その結果、図8の例では、ノードBがルートとなり、ノードCがブランチになる。ルート(ノードB)は、ネットワークの中心となり、バス・アビトリエーションの判定等を行う。

#### 【0760】

以上好適な実施例について説明したが、本発明の技術思想の範囲内で種々の変形・変更が可能である。

#### 【0770】

50

たとえば、上記した実施例では、ウェイクアップ・バッファ24の出力端子をデバイス（フィジカル・レイヤ30）の外のプリント基板上でポートT P A+に接続した。しかし、この配線は一例であり、たとえば図10に示すように、デバイスの内部で配線を行ってもよい。また、ウェイクアップ・バッファ24の出力端子を他方のポートT P A-に接続しても同様の作用効果が得られる。ウェイクアップ・バッファ24の構成も種々の変形が可能であり、たとえばユニポーラ・トランジスタで構成することもできる。

#### 【0780】

また、他の回路要素も種々の変形が可能である。たとえば、上記実施例では、コモンモード電圧発生用の増幅器20は個別の回路として構成されている。しかし、この増幅器20と同等の機能を有する増幅回路をドライバ16a, 18aに内蔵させることも可能である。

。

10

#### 【0790】

上記した実施例はIEEE1394規格に適合するシステムに係るものであったが、本発明の一適用例であり、本発明はコモンモード電圧を必要とする任意の差動駆動式データ通信システムに適用可能である。

#### 【0800】

##### 【発明の効果】

以上説明したように、本発明によれば、パワーダウンモード中に電力消費を抑えながらケーブル接続状態を直ちに検出することが可能である。したがって、マルチメディア・システムにおいて効率的かつ確実なプラグ・アンド・プレイ機能を保証することができる。

20

##### 【図面の簡単な説明】

【図1】本発明の一実施例によるデータ通信システムにおけるケーブル周りの要部の構成を示す回路図である。

【図2】実施例のシステムでウェイクアップ・バッファがオン状態になっている時の電流および電位分布を等価回路で示す回路図である。

##### 【図3】実施例におけるノード内のインターフェース部の構成を示すブロック図である。

【図4】実施例において2つのノードがパワーダウンモードからバス全体を起動させるまでのシーケンスの一例を示す図である。

【図5】実施例において2つのノードがパワーダウンモードからバス全体を起動させるまでのシーケンスの別の例を示す図である。

30

【図6】実施例において2つのノードがパワーダウンモードからバス全体を起動させるまでのシーケンスの別の例を示す図である。

【図7】図4の例において一方のノードに第3のノードが接続されている場合のシーケンスを例を示す図である。

【図8】IEEE1394規格におけるネットワーク・トポロジの一例を示すブロック図である。

【図9】実施例におけるシーケンスの比較例として従来システムにおいて問題となる場合を示す図である。

【図10】実施例におけるウェイクアップ・バッファの出力の配線の変形例を示す要部の回路図である。

40

【図11】IEEE1394規格で採用するD S - L i n k 符号化方式を説明するための信号波形図である。

【図12】IEEE1394規格にしたがう従来のデータ通信システムにおけるケーブル周りの要部の構成を示す回路図である。

##### 【符号の説明】

A, B ノード

10 ケーブル

16a, 18a ドライバ

16b, 18b レシーバ

20 コモンモード電圧発生用増幅器

50

2 2 ケーブル接続状態検出用コンパレータ

2 4 ウェイクアップ・バッファ

3 0 フィジカル・レイヤ

3 2 リンク・レイヤ

3 4 C P U

【図1】

【図2】

【図3】

【 义 5 】

| スケート<br>ト | ノード A       |      |       | ノード B  |       |      |             |

|-----------|-------------|------|-------|--------|-------|------|-------------|

|           | CPU         | LINK | PHY   | ケーブル   | PHY   | LINK | CPU         |

| 1         | CNAを監視      | オフ   | バワタウン | 接続     | バワダウン | オフ   | CNAを監視      |

| 2         | PHYを立ち上げる   | オフ   | オフ    | オフ     | オフ    | オフ   | オフ          |

| 3         | CNAを監視      | オフ   | オフ    | オフ     | オフ    | オフ   | オフ          |

| 5         | オフ          | オフ   | オフ    | オフ     | オフ    | オフ   | CNAを検出*     |

| 6         | オフ          | オフ   | オフ    | オフ     | オフ    | オフ   | CNAを検出*     |

| 7         | オフ          | オフ   | オフ    | オフ     | オフ    | オフ   | PHY/LINKをオフ |

| 8         | オフ          | オフ   | オフ    | オフ     | オフ    | オフ   | オン*         |

| 9         | オフ          | オフ   | オフ    | CNAを検出 | オフ    | オフ   | アラート        |

| 10        | CNAを検出      | *    | オフ    | オフ     | オフ    | オフ   | オフ          |

| 11        | PHY/LINKをオフ | *    | オン*   | オン*    | オフ    | オフ   | オフ          |

| 12        | アラート        | オン   | オフ    | オフ     | オフ    | オフ   | オン          |

【 図 4 】

【 义 6 】

| スティート         | ノードA |           |        |           | ノードB   |       |             |         |

|---------------|------|-----------|--------|-----------|--------|-------|-------------|---------|

|               | CPU  | LINK      | PHY    | ケーブル      | PHY    | LINK  | CPU         |         |

| 1 CNA監視       | オフ   | ハーフダブル    | オーバン   | ハーフダブル    | オフ     | CNA監視 |             |         |

| 2 PHYをACKする   | "    | "         | "      | "         | "      | "     | PHYをACKする   |         |

| 3 CNA監視       | "    | ワイヤレスアダプタ | "      | ワイヤレスアダプタ | "      | "     | CNA監視       |         |

| 4             | "    | "         | "      | 接続        | "      | "     | "           | "       |

| 5             | "    | "         | CNAを検出 | "         | CNAを検出 | "     | "           | "       |

| 6 CNAを検出      | "    | "         | "      | "         | "      | "     | CNAを検出      |         |

| 7 PHY LINKをオフ | "    | "         | "      | "         | "      | "     | PHY/LINKをオフ |         |

| 8 アクティベート     | オン*  | オン*       | オン*    | "         | オン*    | オン*   | オン*         | アクティベート |

| 12 アクティベート    | オフ   | バス初期化を開始  |        |           |        |       | オン          | アクティベート |

【図 7】

| ステップ | J - D A |       |                   | J - D B  |       |     | J - D C           |                   |      |

|------|---------|-------|-------------------|----------|-------|-----|-------------------|-------------------|------|

|      | CPU     | LINK  | PHY               | ケーブル     | LINK  | CPU | PHYポート#1          | PHYポート#2          | ケーブル |

| 1    | CNA監視   | オフ    | アワーサン             | アワーサン    | アワーサン | オフ  | ポート#1に接続<br>CNA監視 | ポート#2に接続<br>CNA監視 | 接続   |

| 4    | "       | "     | "                 | "        | "     | "   | アクティブ             | アクティブ             | オン   |

| 4    | "       | "     | "                 | "        | "     | "   | "                 | "                 | "    |

| 5    | CNA監視*  | "     | CNA監視*            | "        | "     | "   | "                 | "                 | "    |

| 6    | "       | "     | PHY(リ)オフ*         | "        | "     | "   | "                 | "                 | "    |

| 7    | "       | "     | 高ボルト#1, #2に<br>接続 | "        | "     | "   | "                 | "                 | "    |

| 8    | オン*     | "     | "                 | "        | "     | "   | "                 | "                 | "    |

| 9    | "       | "     | "                 | "        | "     | "   | "                 | "                 | "    |

| 10   | "       | "     | "                 | "        | "     | "   | "                 | "                 | "    |

| 11   | "       | "     | "                 | "        | "     | "   | "                 | "                 | "    |

| 12   | バス初期化   | バスセット | 待機                | バス初期化を開始 | "     | "   | "                 | "                 | "    |

【図 8】

【図 9】

| ステップ | J - D A |      |       | J - D B |       |     |

|------|---------|------|-------|---------|-------|-----|

|      | CPU     | LINK | PHY   | CPU     | LINK  | PHY |

| 1    | CNA監視   | オフ   | アワーサン | アワーサン   | アワーサン | オフ  |

| 4    | "       | "    | "     | "       | "     | "   |

| 4    | "       | "    | "     | "       | "     | "   |

【図 10】

【図 1 1】

【図 1 2】

---

フロントページの続き

(56)参考文献 特開平08-221163(JP,A)

特開平08-095687(JP,A)

特開平04-186411(JP,A)

特開平07-261880(JP,A)

特開平08-087360(JP,A)

(58)調査した分野(Int.Cl., DB名)

WPI(DIALOG)

G06F 1/18

H04L 25/02