(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5357063号

(P5357063)

(45) 発行日 平成25年12月4日(2013.12.4)

(24) 登録日 平成25年9月6日(2013.9.6)

(51) Int.Cl.

F 1

H01L 27/146 (2006.01)

H01L 27/14 A

H04N 5/369 (2011.01)

H04N 5/335 690

H04N 5/374 (2011.01)

H04N 5/335 740

請求項の数 4 (全 9 頁)

(21) 出願番号 特願2009-553578 (P2009-553578)

(86) (22) 出願日 平成20年2月20日 (2008.2.20)

(65) 公表番号 特表2010-521812 (P2010-521812A)

(43) 公表日 平成22年6月24日 (2010.6.24)

(86) 國際出願番号 PCT/US2008/002235

(87) 國際公開番号 WO2008/115331

(87) 國際公開日 平成20年9月25日 (2008.9.25)

審査請求日 平成23年2月17日 (2011.2.17)

(31) 優先権主張番号 11/686,573

(32) 優先日 平成19年3月15日 (2007.3.15)

(33) 優先権主張国 米国(US)

(73) 特許権者 510215606

オムニヴィジョン テクノロジーズ イン

コーポレイテッド

アメリカ合衆国 カリフォルニア州 95

054 サンタ クララ バートン ドラ

イヴ 4275

(74) 代理人 110001210

特許業務法人 YKI 国際特許事務所

(72) 発明者 パークス クリストファー

アメリカ合衆国 ニューヨーク ロチェス

ター ケンタッキー クロッシング 11

3

審査官 石坂 博明

最終頁に続く

(54) 【発明の名称】 画像センサ

## (57) 【特許請求の範囲】

## 【請求項 1】

画像センサであって、

(a) 基板上に行および列に配置された複数の画素を備えており、

各画素が、

(i) 入射光に反応して電荷を収集する少なくとも一つの感光性領域と、

(ii) 前記少なくとも一つの感光性領域から前記電荷を感知し、前記電荷を電圧に変換する電荷・電圧変換ノードと、

(iii) 出力ノードに接続されたソースを有し、前記電荷・電圧変換ノードに接続されたゲートを有し、電源ノードの一部に接続されたドレインを有する増幅器トランジスタであって、隣接する列の画素は前記電源ノードの残りの部分に接続されたドレインを有する増幅器トランジスタを含む、増幅器トランジスタと、

(iv) 前記出力ノードと前記電荷・電圧変換ノードとを接続するリセットトランジスタと、

を備え、

1つの列内の各画素に含まれる、前記電荷・電圧変換ノード、前記リセットトランジスタのリセットゲート、前記出力ノード、前記増幅器トランジスタのゲート、および前記電源ノードの一部は、

前記隣接する列に向かう方向に、前記電荷・電圧変換ノード、前記リセットトランジスタのリセットゲート、前記出力ノード、前記増幅器トランジスタのゲート、および前記電

10

20

源ノードの一部、という空間的順序で配置されており、

前記隣接する列内の各画素に含まれる、前記電源ノードの残りの部分、前記増幅器トランジスタのゲート、前記出力ノード、前記リセットトランジスタのリセットゲート、および前記電荷・電圧変換ノードは、

前記1つの列から離れる方向に、前記電源ノードの残りの部分、前記増幅器トランジスタのゲート、前記出力ノード、前記リセットトランジスタのリセットゲート、および前記電荷・電圧変換ノード、という空間的順序で配置されている、

画素センサ。

**【請求項2】**

各画素が、各感光性領域から前記電荷・電圧変換ノードへ電荷を転送する転送ゲートを含む、請求項1に記載の画像センサ。 10

**【請求項3】**

前記1つの列内の各画素、および前記隣接する列内の各画素は、

隣接する二つの感光性領域を備え、

前記二つの感光性領域のそれぞれは、転送ゲートを備え、

各転送ゲートは、前記二つの感光性領域に共有される前記電荷・電圧変換ノードに接続

されている、請求項1に記載の画像センサ。 20

**【請求項4】**

前記画素センサは撮像装置内に設けられる、請求項1から3のいずれか1項に記載の画像センサ。 20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、一般的にはCMOSアクティブ画素画像センサの分野に関しており、より具体的には、画素のサイズの低減に関する。 30

**【背景技術】**

**【0002】**

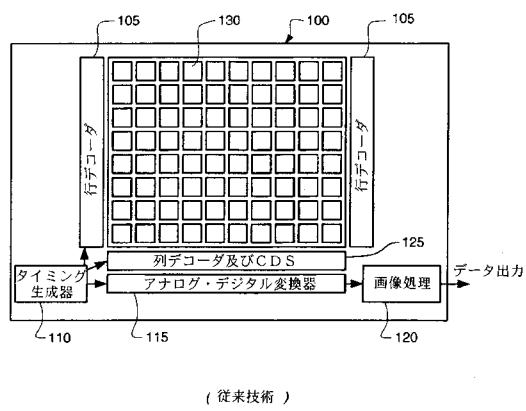

図1は、典型的なCMOSアクティブ画素画像センサ100を示す。画像センサ100の基本的な構成要素は、感光性画素130のアレイである。行デコーダ回路105が、相関二重サンプリング(CDS)回路125によってサンプリングされるべき画素130の行全体を選択する。アナログ・デジタル変換器115が列デコーダを走査し、CDS125に記憶された信号をデジタル化する。アナログ・デジタル変換器115は、各列に一つの変換器を有するタイプ(並列)であっても、各列をシリアルにデジタル化する一つの高速変換器であってもよい。デジタル化されたデータは、画像センサ100から直接的に出力されてもよく、あるいは、欠陥補正、カラーフィルタ補間、画像スケーリング、及びその他の特殊効果のための集積された画像処理120があってもよい。タイミング生成器110が行及び列デコーダを制御して、画素アレイ全体又は画素アレイの一部のみをサンプリングする。 30

**【0003】**

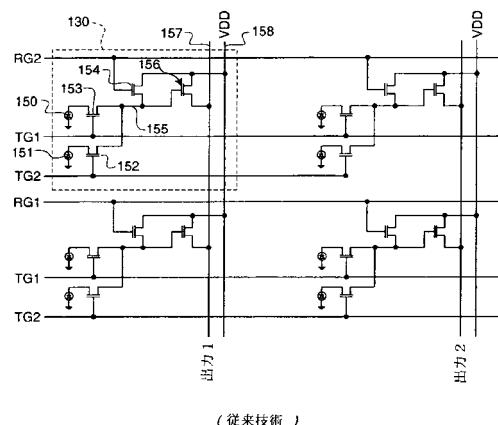

図2は、CMOS画像センサのための多くの異なる可能な模式図の一つを示す。画素アレイのうちの4つの画素130(明瞭化のために一つのみがラベルされている)が示されている。各画素130は、2つのフォトダイオード150及び151の間で共有される回路を有している。このタイプの画素は、他の変形とともに、米国特許第5,625,210号、第5,841,159号、5,949,061号、第6,107,655号、第6,160,281号、第6,423,994号、及び第6,657,665号に見出される。 40

**【0004】**

フォトダイオード150及び151は、それぞれ転送ゲート152及び153によって共通の共有された浮遊拡散部155に接続されている。フォトダイオード150をサンプリングするプロセスは、電源(VDD)158をオンし、リセットトランジスタ154も 50

またオンして、浮遊拡散部 155 の電圧を電源 158 の電圧に設定することによって始まる。リセットトランジスタ 154 はそれからオフして、出力トランジスタ 156 によってサンプリングされた信号レベルが出力信号線 157 の上にドライブされる。次に、転送ゲート 153 がオンして、光生成された信号電荷をフォトダイオード 150 から浮遊拡散部 155 に転送する。ここで、出力トランジスタ 156 は、信号レベル電圧を出力信号線 157 の上にドライブする。リセット直後の第1の信号マイナス転送ゲート 153 がパルスされた後の信号の差は、フォトダイオード 150 内にあった電子の数に比例する。

### 【0005】

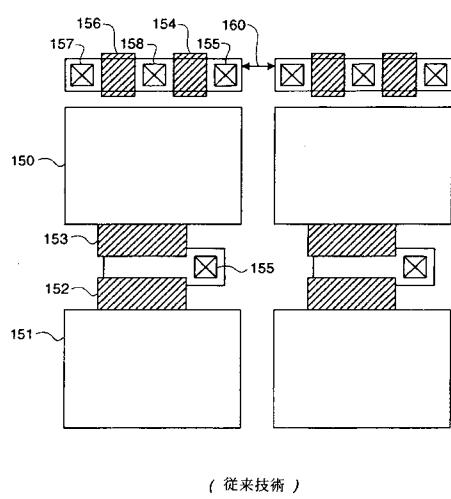

第2のフォトダイオード 151 は、転送ゲート 152 を通して同じ方法でサンプリングされる。この画素 130 は2つの共有された画素として示されているが、これは、2つのフォトダイオード 150 及び 151 が共通の浮遊拡散部 155 を共有しているからである。2つの共有された画素が物理的にどのようにしてシリコン基板上に製造され得るかの一例が、図3に示されている。図3で番号が付けられた構成要素は、図2の模式的な記号に対応している。ポリシリコントランジスタ転送ゲートが 152 及び 153 であり、リセットトランジスタゲートが 154 であり、出力トランジスタゲートが 156 である。浮遊拡散部コンタクト 155 は、金属ワイヤによって共通に接続されている。リセット 154 及び出力 156 のトランジスタは、電源線まで共通の拡散接続部 158 を共有している。

10

### 【発明の概要】

### 【発明が解決しようとする課題】

### 【0006】

20

図3の画素レイアウトの欠点は、画素のサイズをどのように低減するかという点である。2つの隣接する画素の間のギャップ 160 は、隣接する画素の間での電子のリークというリスク無しに、さらに縮減されることはない。トランジスタゲート 154 及び 156 のサイズは、電源の動作電圧がそれらのサイズを決定するので、縮減できない。電源電圧を低減することは、それが、フォトダイオードによって収集されることができる光電子の最大数もまた減らすことになるので、魅力的なオプションではない。

### 【0007】

本発明は、リセット及び出力トランジスタのゲートのサイズを低減する必要なしに画素サイズを低減する方策を開示することで、この欠点及びその他に対応する。

### 【課題を解決するための手段】

30

### 【0008】

本発明は、上述の問題の一つ又はそれ以上を克服することに向けられている。本発明の一つの局面によれば、本発明は基板上に配置された複数の画素を含む画像センサについており、各画素が、入射光に反応して電荷を収集する少なくとも一つの感光性領域と、前記少なくとも一つの感光性領域から前記電荷を感知し、前記電荷を電圧に変換する電荷・電圧変換ノードと、出力ノードに接続されたソースを有し、前記電荷・電圧変換ノードに接続されたゲートを有し、電源ノードの一部に接続されたドレインを有する増幅器トランジスタであって、隣接する列の画素は前記電源ノードの残りの部分に接続されたドレインを有する増幅器トランジスタを含む、増幅器トランジスタと、前記出力ノードと前記電荷・電圧変換ノードとを接続するリセットトランジスタと、を含み、1つの列内の各画素に含まれる、前記電荷・電圧変換ノード、前記リセットトランジスタのリセットゲート、前記出力ノード、前記増幅器トランジスタのゲート、および前記電源ノードの一部は、前記隣接する列に向かう方向に、前記電荷・電圧変換ノード、前記リセットトランジスタのリセットゲート、前記出力ノード、前記増幅器トランジスタのゲート、および前記電源ノードの一部、という空間的順序で配置されており、前記隣接する列内の各画素に含まれる、前記電源ノードの残りの部分、前記増幅器トランジスタのゲート、前記出力ノード、前記リセットトランジスタのリセットゲート、および前記電荷・電圧変換ノードは、前記1つの列から離れる方向に、前記電源ノードの残りの部分、前記増幅器トランジスタのゲート、前記出力ノード、前記リセットトランジスタのリセットゲート、および前記電荷・電圧変換ノード、という空間的順序で配置されている。

40

50

**【発明の効果】****【0009】**

本発明は、トランジスタ配置のサイズを低減することなく、画像センサの画素サイズを低減することを許容する。

**【図面の簡単な説明】****【0010】**

【図1】従来技術のアクティブ画素画像センサである。

【図2】図1の画素の模式図である。

【図3】図1の平面図(上面図)である。

【図4】本発明の複数の画素の模式図である。

10

【図5】図4の平面図(上面図)である。

【図6】図5のトランジスタを通る水平断面図である。

【図7】図4の画素を有する本発明の画像センサである。

【図8】本発明の画像センサを有するカメラである。

**【発明を実施するための形態】****【0011】**

本発明を詳細に議論する前に、本発明が好ましくはCMOSアクティブ画素センサで使用されるが、これに限定されるものではないことを指摘することは、有益である。アクティブ画素センサは、画素内のアクティブな電気的要素、より具体的には増幅器を指しており、CMOSは、画素に関連しているが典型的には画素内には無いトランジスタのような相補的な金属・酸化物・シリコン形の電気的要素を指しており、一つのトランジスタのソース／ドレインが一つのドーパントタイプ(例えばp形)であり、その対向するトランジスタが反対のドーパントタイプ(n形)であるように形成されている。CMOS装置はいくつかの効果を含み、その一つは、消費電力が少ないとある。

20

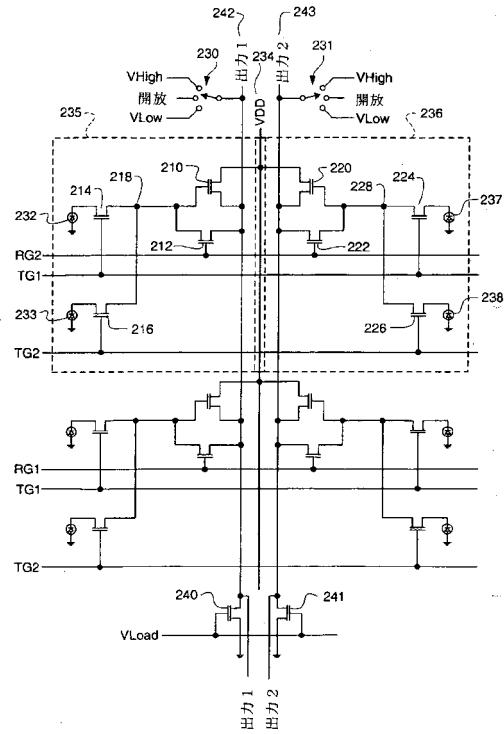

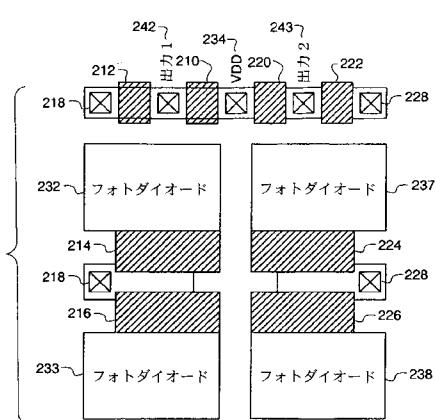

**【0012】**

画素サイズを低減するために、画素内のトランジスタの動作を変える必要がある。本発明の画素の模式図が、図4に示されている。この画素235の従来技術からの主な相違点は、リセットトランジスタ212が浮遊拡散部218と出力信号線242との間に接続されている点である。従来技術では、リセットトランジスタは電源線(VDD)234に接続されている。この模式図はトランジスタの全体数を低減しないが、電源線(VDD)234拡散部が2つの画素235及び236の間で共有されることを許容する。これは、図5に、より明瞭に示されている。

30

**【0013】**

図4に戻ると、ここで各画素が詳細に説明される。画素235が、代表的な画素として使用される。これに関して、画素235は2つの感光性領域又はフォトダイオード232及び233を含み、その各々は入射光に反応して電荷を収集する。この特徴が主に光に反応して電荷を単に収集することを必要としていることが理解されると、ピン・フォトダイオードもまた使用されることができる点が、明瞭化のために指摘される。転送ゲート214は、フォトダイオード232から電荷・電圧変換ノード又はセンスノード218に電荷を転送する。出力トランジスタ又は増幅器210、好ましくはソースフォロワは、そのゲートを介してセンスノード218に接続されており、増幅器210は、センスノード218上の信号を感知し、その信号をソースを介して出力バス242に出力する。増幅器210のドレインは、電源(VDD)234に接続されている。この接続は、ドレインを電源ノード234の少なくとも一部に接続することを含む。この部分は、好ましくは、電源ノード234の1/2を含み、又は実質的に1/2を含む。増幅器220は同じ方法で接続されており、電源234の残りの部分に接続されている。画素235は、センスノード218、増幅器210、及びリセットトランジスタ212を共有しているが、入射光に反応して電荷を収集する別個のフォトダイオード233とその電荷をセンスノード218に転送する転送ゲート216とを含んでいる。

40

**【0014】**

50

隣接する画素 236 は画素 235 と同じ構成要素を含んでいるが、明瞭化のために異なって番号が付けられている。この点に関して、画素 236 は、フォトダイオード 237、転送ゲート 224、センスノード又は浮遊拡散部 228、増幅器 220、及びリセットトランジスタ 222 を含む。画素 236 は、浮遊拡散部 228、増幅器 220、及びリセットトランジスタ 222 を共有しているが、別個のフォトダイオード 238 と転送ゲート 226 とを含んでいる。

【0015】

図 5において、参照番号は図 4 の数字に対応している。VDD 拡散部 234 は、2つの出力トランジスタ 210 及び 220 の間で共有されている。リセットトランジスタゲート 212 及び 222 は、浮遊拡散部 218 及び 228 が output 242 及び 243 を通した電圧にリセットされることを許容する。画素 235 (図 4 に示されている) は、電荷・電圧変換ノード 218、リセットトランジスタ 212 のリセットゲート、出力ノード 242、増幅器トランジスタ 210 のゲート、及び電源ノード 234 の少なくとも一部を、連続的なこのような空間順で含む。隣接する画素 236 (やはり図 4 に示されている) は、電源ノード 234 の残りの部分、増幅器トランジスタ 220 のゲート、出力ノード 243、リセットトランジスタ 222 のリセットゲート、及び電荷・電圧変換ノード 228 を、連続的なこのような空間順で含む。

【0016】

図 4 に戻ると、フォトダイオード 232 及び 237 の行から電荷を読み出すプロセスは、浮遊拡散部 218 及び 228 を活性化することによって始まる。これは、定電流シンク負荷トランジスタ 240 及び 241 (図 4 の下部を参照) をオフすることによって行われる。負荷トランジスタ 240 及び 241 をオフすると、スイッチ 230 及び 231 は、VHigh 電圧設定に設定される。ここで、リセットトランジスタ 212 及び 222 がオンされると、浮遊拡散部 218 及び 228 は VHigh 電圧に設定される。次に、リセットトランジスタ 212 及び 222 はオフされて、スイッチ 230 及び 231 が開放設定に設定される。それから、電流シンク負荷トランジスタ 240 及び 241 がオンされて、出力トランジスタ 210 及び 220 が、出力線 242 及び 243 を、光信号の零電子に対応する浮遊リセットレベルを表す電圧にドライブする。次に、転送ゲート 214 及び 224 がパルスでオン・オフされて、光生成された電荷をフォトダイオード 232 及び 237 から浮遊拡散部 218 及び 228 に転送する。ここで、出力トランジスタ 210 及び 220 は、出力線 242 及び 243 を、フォトダイオード 232 及び 237 で生成された電子数に対応する電圧レベルにドライブする。この電圧レベルとリセット電圧レベルとの間の差は、フォトダイオード内の電荷量に比例する。

【0017】

フォトダイオード 233 及び 238 の次の行を読み出すために、浮遊拡散部 218 及び 228 を活性化することによってプロセスが反復される。これは、定電流シンク負荷トランジスタ 240 及び 241 をオフすることによって行われる。負荷トランジスタ 240 及び 241 がオフすると、スイッチ 230 及び 231 は、VHigh 電圧設定に設定される。ここで、リセットトランジスタ 212 及び 222 がオンされると、浮遊拡散部 218 及び 228 は VHigh 電圧に設定される。次に、リセットトランジスタ 212 及び 222 はオフされて、スイッチ 230 及び 231 が開放設定に設定される。それから、電流シンク負荷トランジスタ 240 及び 241 がオンされ、出力トランジスタ 210 及び 220 が、出力線 242 及び 243 を、光信号の零電子に対応する浮遊リセットレベルを表す電圧にドライブする。次に、転送ゲート 216 及び 226 がパルスでオン・オフされて、光生成された電荷をフォトダイオード 233 及び 238 から浮遊拡散部 218 及び 228 に転送する。ここで、出力トランジスタ 210 及び 220 は、出力線 242 及び 243 を、フォトダイオード 233 及び 238 で生成された電子数に対応する電圧レベルにドライブする。この電圧レベルとリセット電圧レベルとの間の差は、フォトダイオード内の電荷量に比例する。

【0018】

10

20

30

40

50

次に、画素 235 及び 236 内のトランジスタは、画素の別の行を読み出しに動く前に、非活性化されなければならない。リセットトランジスタ 212 及び 222 をオン状態に保持することで、出力トランジスタ 210 及び 220 のゲート及びソース電圧が等しく設定される。表面チャンネルトランジスタでゲート及びソース電圧が等しいと、トランジスタはオフ状態にある。出力トランジスタ 210 及び 220 がオフ状態にあるとき、それらは、他の画像センサ行のフォトダイオードの読み出しには干渉しない。

【0019】

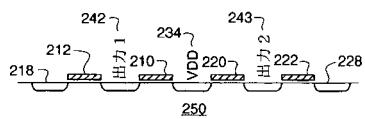

共通電源 (VDD) 拡散部 234 を共有することによって、図 5 において、トランジスタによって占有される面積量が低減される。図 3 の従来技術に比べて、コンタクトが一つ少なく、トランジスタ間の分離領域が一つ少ない。このことは、同じトランジスタゲート寸法を維持し且つ適正なサイズのフォトダイオードを維持しながら、画素の全体サイズが低減されることを許容する。

【0020】

図 6 は、トランジスタゲート 212、210、220、及び 222 の線を通る断面を示す。これらのトランジスタは、シリコン基板 250 に製造されている。

【0021】

図 4 の画素 235 は、共通浮遊拡散部 218 を共有する 2 つのフォトダイオード 232 及び 233 を示している。CMOS 画像センサの当業者は、本発明が、共有されるフォトダイオードが無い場合を含めて、任意の数のフォトダイオードを共有すること又は共通浮遊拡散部を共有しないことに適用されることができますことを、容易に認識するであろう。

【0022】

図 4 はまた、垂直方向に向いた VDD 電源線 234 を示す。電源線 234 はまた、水平に、あるいは方形グリッドとして両方向に向けられることもできる。さらに、VDD 電源線 234 が水平に向けられると、米国特許第 5,949,061 号及び第 6,323,476 号にあるように、読み出しのために行を選択又は非選択するために使用することができる。

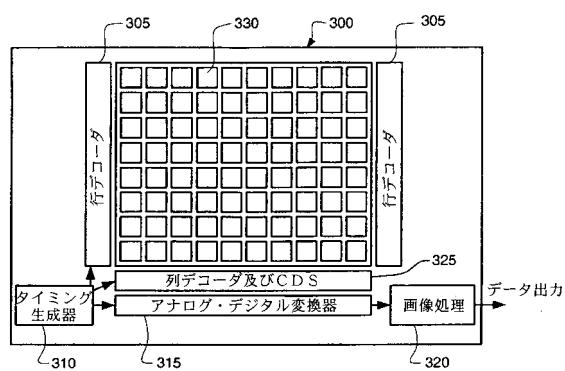

【0023】

図 7 は、画像センサ 300 に組み込まれた本発明 330 の画素を示す。画像センサ 300 は、読み出しのために行を選択又は非選択する行デコーダ 305 を有する。これはまた、各列の出力線をサンプリングする列デコーダ 325、及び出力線上の信号をデジタル化するアナログ・デジタル変換器 315 も有する。タイミング生成器 310 は、行 305 及び列 325 デコーダの走査を制御する。画像プロセッサ 320 は、行及び列のゲイン及びオフセットの補正、ならびに欠陥補正、及びカラーフィルタ補間、又はその他の画像処理機能のために使用される。

【0024】

図 8 は、本発明の画像センサ 300 を有するデジタルカメラ 400 である。

【符号の説明】

【0025】

100 画像センサ、105 行デコーダ回路、110 タイミング生成器、115 アナログ・デジタル変換器、120 画像処理、125 相関二重サンプリング (CDS) 回路、130 感光性画素、150 フォトダイオード、151 フォトダイオード、152 転送ゲート、153 転送ゲート、154 リセットトランジスタゲート、155 浮遊拡散部、156 出力トランジスタゲート、157 出力信号線、158 電源線 (VDD)、160 ギャップ、210 出力トランジスタ又は増幅器、212 リセットトランジスタゲート、214 転送ゲート、216 転送ゲート、218 浮遊拡散部又はセンスノード、220 出力トランジスタ又は増幅器、222 リセットトランジスタゲート、224 転送ゲート、226 転送ゲート、228 浮遊拡散部又はセンスノード、230 スイッチ、231 スイッチ、232 フォトダイオード、233 フォトダイオード、234 電源線 (VDD)、235 画素、236 画素、237 フォトダイオード、238 フォトダイオード、240 シンク負荷トランジスタ、241

10

20

30

40

50

シンク負荷トランジスタ、242 出力信号線、243 出力信号線、250 シリコン基板、300 画像センサ、305 行デコーダ、310 タイミング生成器、315 アナログ・デジタル変換器、320 画像プロセッサ、325 列デコーダ、330 感光性画素、400 デジタルカメラ。

【図1】

【図2】

【図3】

【 図 4 】

【図5】

【図6】

【 四 7 】

〔 8 〕

**FIG. 8**

---

フロントページの続き

(56)参考文献 特開2000-232218(JP,A)

特開平11-112018(JP,A)

特開2006-319951(JP,A)

特開2006-302970(JP,A)

特開平10-256521(JP,A)

特開2000-209504(JP,A)

特表2004-508716(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/339、27/14、

27/144-27/148、29/762

H04N 5/335- 5/378