(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6502176号

(P6502176)

(45) 発行日 平成31年4月17日(2019.4.17)

(24) 登録日 平成31年3月29日(2019.3.29)

(51) Int.Cl.

F 1

|      |         |           |

|------|---------|-----------|

| HO1L | 21/8238 | (2006.01) |

| HO1L | 27/092  | (2006.01) |

| HO1L | 21/28   | (2006.01) |

| HO1L | 21/822  | (2006.01) |

| HO1L | 27/04   | (2006.01) |

|      |        |      |

|------|--------|------|

| HO1L | 27/092 | F    |

| HO1L | 21/28  | 301B |

| HO1L | 27/04  | A    |

| HO1L | 21/90  | A    |

| HO1L | 21/88  | Z    |

請求項の数 4 (全 69 頁) 最終頁に続く

(21) 出願番号

特願2015-108074 (P2015-108074)

(22) 出願日

平成27年5月28日 (2015.5.28)

(65) 公開番号

特開2016-6871 (P2016-6871A)

(43) 公開日

平成28年1月14日 (2016.1.14)

審査請求日

平成30年5月21日 (2018.5.21)

(31) 優先権主張番号

特願2014-112744 (P2014-112744)

(32) 優先日

平成26年5月30日 (2014.5.30)

(33) 優先権主張国

日本国 (JP)

特許法第30条第2項適用 (集会名) 第61回応用物理学会春季学術講演会、(開催日) 平成26年3月19日、(公開者) 山崎舜平

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 笹川 慎也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 宮入 秀和

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 倉田 求

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタと、第2のトランジスタと、コンタクトプラグを有する半導体装置であって、

前記第1のトランジスタはシリコン基板に活性領域を有し、

前記第2のトランジスタは酸化物半導体を活性層に有し、

前記第1のトランジスタと前記第2のトランジスタはそれぞれ重なる領域を有し、

前記第1のトランジスタと前記第2のトランジスタの間に第1の絶縁層を有し、

前記第2のトランジスタ上に第2の絶縁層を有し、

前記第1のトランジスタのソース電極またはドレイン電極の一方は、前記第2のトランジスタのソース電極またはドレイン電極の一方と前記コンタクトプラグを介して電気的に接続されており、

前記酸化物半導体は、第1の酸化物半導体層と、前記第1の酸化物半導体層上の第2の酸化物半導体層と、前記第2の酸化物半導体層上の第3の酸化物半導体層と、を有し、

前記第3の酸化物半導体層は、前記第2のトランジスタのソース電極及びドレイン電極の側面に接する領域を有し、

前記コンタクトプラグは、前記第1の絶縁層、前記第2のトランジスタのソース電極またはドレイン電極の一方、および前記第2の絶縁層を貫通しており、前記コンタクトプラグは、前記第2の絶縁層から前記第1の絶縁層に向かう深さ方向において、前記第2の絶縁層と前記第2のトランジスタのソース電極またはドレイン電極の一方との界面を境に径

10

20

が小さくなる領域を有することを特徴とする半導体装置。

**【請求項 2】**

請求項1において、

前記第1のトランジスタおよび前記第2のトランジスタは、CMOS回路を構成していることを特徴とする半導体装置。

**【請求項 3】**

請求項1または2において、

前記酸化物半導体は、Inと、Znと、M(MはAl、Ti、Ga、Sn、Y、Zr、La、Ce、NdまたはHf)を有することを特徴とする半導体装置。

**【請求項 4】**

請求項1乃至3のいずれか一項において、

前記コントラクトプラグは、前記第2のトランジスタが有する酸化物半導体層を貫通していることを特徴とする半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の一態様は、酸化物半導体を用いた半導体装置に関する。

**【0002】**

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、液晶表示装置、発光装置、照明装置、蓄電装置、記憶装置、撮像装置、それらの駆動方法、または、それらの製造方法、を一例として挙げることができる。

**【0003】**

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。トランジスタ、半導体回路は半導体装置の一態様である。また、記憶装置、表示装置、撮像装置、電子機器は、半導体装置を有する場合がある。

**【背景技術】**

**【0004】**

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。当該トランジスタは集積回路(I.C.)や画像表示装置(単に表示装置とも表記する)のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜として、シリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

**【0005】**

酸化物半導体を用いたトランジスタは、非導通状態において極めてリーク電流が小さいことが知られている。例えば、特許文献1には酸化物半導体を用いたトランジスタの低いリーク電流特性を応用した低消費電力のCPUなどが開示されている。

**【先行技術文献】**

**【特許文献】**

**【0006】**

【特許文献1】特開2012-257187号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0007】**

本発明の一態様では、占有面積の小さい半導体装置を提供することを目的の一つとする。または、集積度の高い半導体装置を提供することを目的の一つとする。または、動作速度の速い半導体装置を提供することを目的の一つとする。または、消費電力の小さい半導体

10

20

30

40

50

装置を提供することを目的の一つとする。または、生産性の高い半導体装置を提供することを目的の一つとする。または、歩留まりの高い半導体装置を提供することを目的の一つとする。または、新規な半導体装置を提供することを目的の一つとする。または、上記半導体装置の作製方法を提供することを目的の一つとする。

【0008】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

10

【0009】

本発明の一態様は、酸化物半導体を用いて形成されたトランジスタおよびシリコンを用いて形成されたトランジスタを有する半導体装置に関する。

【0010】

本発明の一態様は、第1の絶縁層と、導電層と、第2の絶縁層と、コンタクトプラグを有し、導電層は第1の絶縁層と第2の絶縁層との間に設けられ、第1の絶縁層、導電層および第2の絶縁層は、互いに重なる領域を有し、コンタクトプラグは、第1の絶縁層と、導電層と、第2の絶縁層を貫通するように設けられ、コンタクトプラグは、第2の絶縁層から第1の絶縁層に向かう深さ方向において、第2の絶縁層と導電層との界面を境に径が小さくなる領域を有することを特徴とする半導体装置である。

20

【0011】

本発明の他の一態様は、第1のトランジスタと、第2のトランジスタと、コンタクトプラグを有する半導体装置であって、第1のトランジスタはシリコン基板に活性領域を有し、第2のトランジスタは酸化物半導体を活性層に有し、第1のトランジスタと第2のトランジスタはそれぞれ重なる領域を有し、第1のトランジスタと第2のトランジスタの間に第1の絶縁層を有し、第2のトランジスタ上に第2の絶縁層を有し、第1のトランジスタのソース電極またはドレイン電極の一方は、第2のトランジスタのソース電極またはドレイン電極の一方とコンタクトプラグを介して電気的に接続されており、コンタクトプラグは、第1の絶縁層、第2のトランジスタのソース電極またはドレイン電極の一方、および第2の絶縁層を貫通しており、コンタクトプラグは、第2の絶縁層から第1の絶縁層に向かう深さ方向において、第2の絶縁層と第2のトランジスタのソース電極またはドレイン電極の一方との界面を境に径が小さくなる領域を有することを特徴とする半導体装置である。

30

【0012】

第1のトランジスタおよび第2のトランジスタは、CMOS回路を構成することができる。

【0013】

酸化物半導体は、Inと、Znと、M(MはAl、Ti、Ga、Sn、Y、Zr、La、Ce、NdまたはHf)を有することが好ましい。

【0014】

40

また、コンタクトプラグは、第2のトランジスタが有する酸化物半導体層を貫通する構成とすることもできる。

【0015】

本発明の他の一態様は、第1の絶縁層を形成し、第1の絶縁層上に導電膜を形成し、第1のマスクを用いて導電膜を選択的にエッチングすることによって、導電層および当該導電層を膜厚方向に貫通する貫通口を形成し、導電層および貫通口を覆うように第2の絶縁層を形成し、第2のマスクを用いて第2の絶縁層を選択的にエッチングすることによって、貫通口の径よりも大きい径の開口部を形成して貫通口を露出させ、導電層をマスクとして第1の絶縁層を選択的にエッチングすることを特徴とする半導体装置の作製方法である。

【発明の効果】

50

**【 0 0 1 6 】**

本発明の一態様により、占有面積の小さい半導体装置を提供することができる。または、集積度の高い半導体装置を提供することができる。または、動作速度の速い半導体装置を提供することができる。または、消費電力の小さい半導体装置を提供することができる。または、生産性の高い半導体装置を提供することができる。または、歩留まりの高い半導体装置を提供することができる。または、新規な半導体装置を提供することができる。または、上記半導体装置の作製方法を提供することができる。

**【 0 0 1 7 】**

なお、本発明の一態様はこれらの効果に限定されるものではない。例えば、本発明の一態様は、場合によっては、または、状況に応じて、これらの効果以外の効果を有する場合もある。または、例えば、本発明の一態様は、場合によっては、または、状況に応じて、これらの効果を有さない場合もある。

10

**【図面の簡単な説明】****【 0 0 1 8 】**

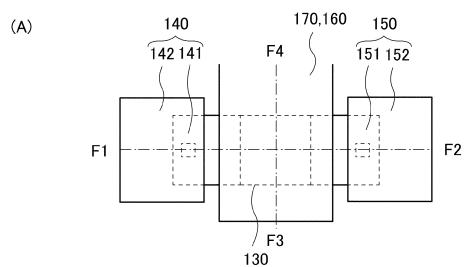

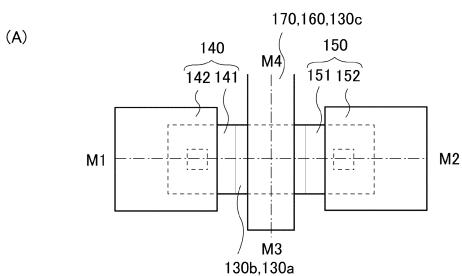

【図 1】半導体装置を説明する断面図および回路図。

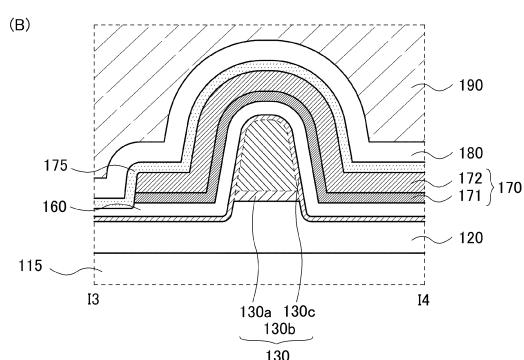

【図 2】コンタクトプラグの作製方法を説明する断面図。

【図 3】コンタクトプラグの作製方法を説明する断面図。

【図 4】半導体装置を説明する断面図。

【図 5】コンタクトプラグの作製方法を説明する断面図。

【図 6】半導体装置を説明する上面図。

20

【図 7】半導体装置を説明する断面図および回路図。

【図 8】半導体装置を説明する断面図。

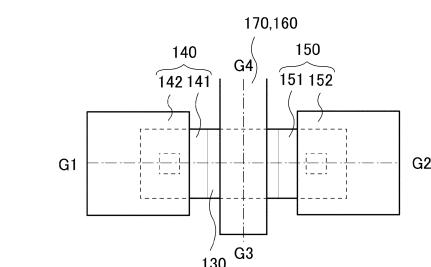

【図 9】半導体装置を説明する上面図。

【図 10】トランジスタを説明する上面図および断面図。

【図 11】トランジスタを説明する上面図および断面図。

【図 12】トランジスタを説明する上面図および断面図。

【図 13】トランジスタを説明する上面図および断面図。

【図 14】トランジスタを説明する上面図および断面図。

【図 15】トランジスタを説明する上面図および断面図。

【図 16】トランジスタのチャネル幅方向の断面を説明する図。

30

【図 17】トランジスタのチャネル長方向の断面を説明する図。

【図 18】トランジスタのチャネル幅方向の断面を説明する図。

【図 19】半導体層を説明する上面図および断面図。

【図 20】半導体層を説明する上面図および断面図。

【図 21】トランジスタを説明する上面図および断面図。

【図 22】トランジスタを説明する上面図および断面図。

【図 23】トランジスタを説明する上面図および断面図。

【図 24】トランジスタを説明する上面図および断面図。

【図 25】トランジスタを説明する上面図および断面図。

【図 26】トランジスタを説明する上面図および断面図。

40

【図 27】トランジスタのチャネル幅方向の断面を説明する図。

【図 28】トランジスタのチャネル長方向の断面を説明する図。

【図 29】トランジスタのチャネル幅方向の断面を説明する図。

【図 30】トランジスタを説明する上面図。

【図 31】トランジスタの作製方法を説明する図。

【図 32】トランジスタの作製方法を説明する図。

【図 33】トランジスタの作製方法を説明する図。

【図 34】トランジスタの作製方法を説明する図。

【図 35】トランジスタの作製方法を説明する図。

【図 36】トランジスタの作製方法を説明する図。

50

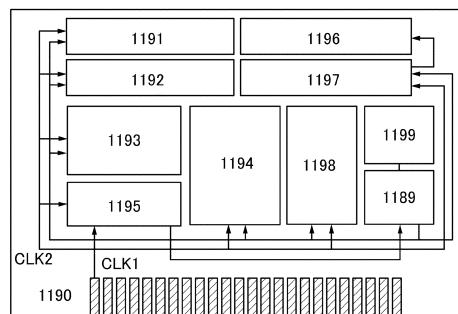

【図37】C P Uの構成例を説明する図。

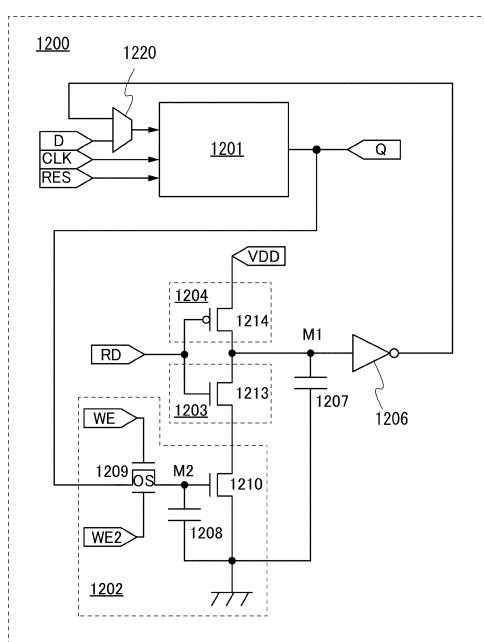

【図38】記憶素子の回路図。

【図39】電子機器を説明する図。

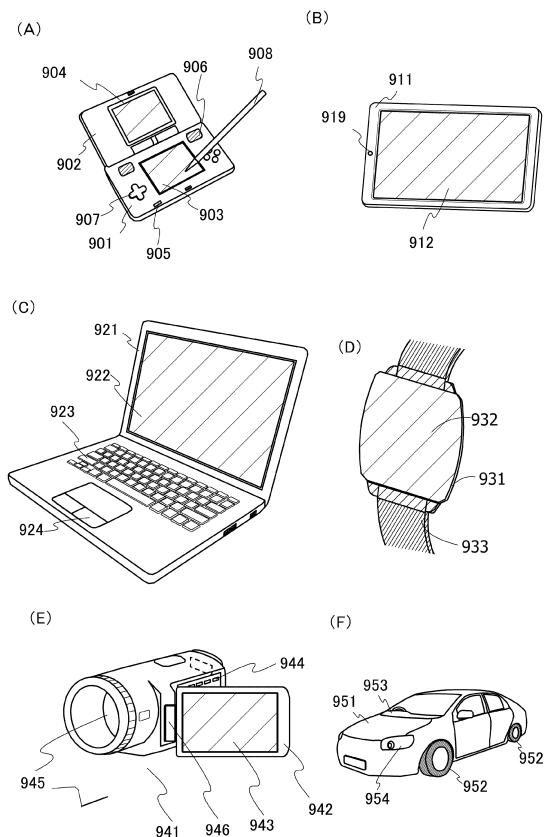

【図40】半導体装置の拡大断面図。

【図41】半導体装置の拡大断面図。

【図42】エッチング装置を説明する図。

【図43】C A A C - O Sの断面におけるC s補正高分解能TEM像、およびC A A C - O Sの断面模式図。

【図44】C A A C - O Sの平面におけるC s補正高分解能TEM像。

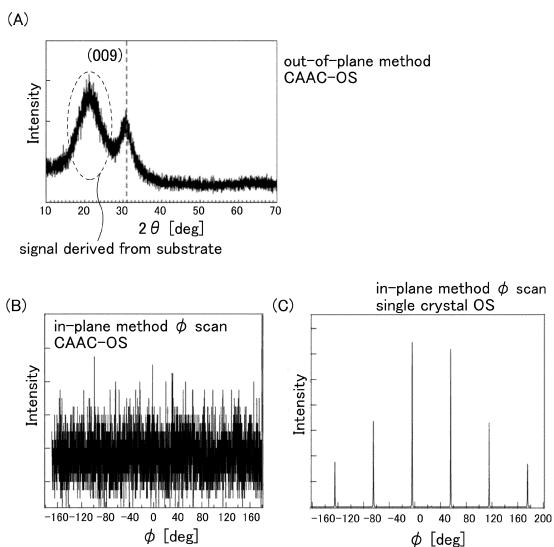

【図45】C A A C - O Sおよび単結晶酸化物半導体のXRDによる構造解析を説明する図。 10

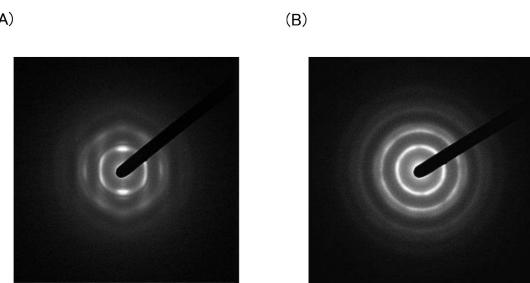

【図46】C A A C - O Sの電子回折パターンを示す図。

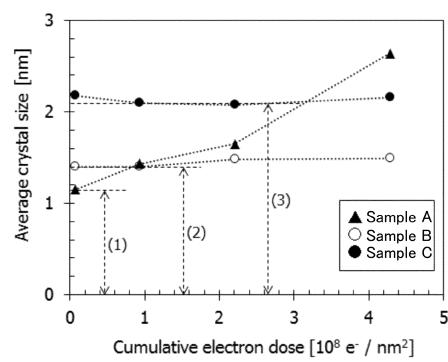

【図47】In-Ga-Zn酸化物の電子照射による結晶部の変化を示す図。

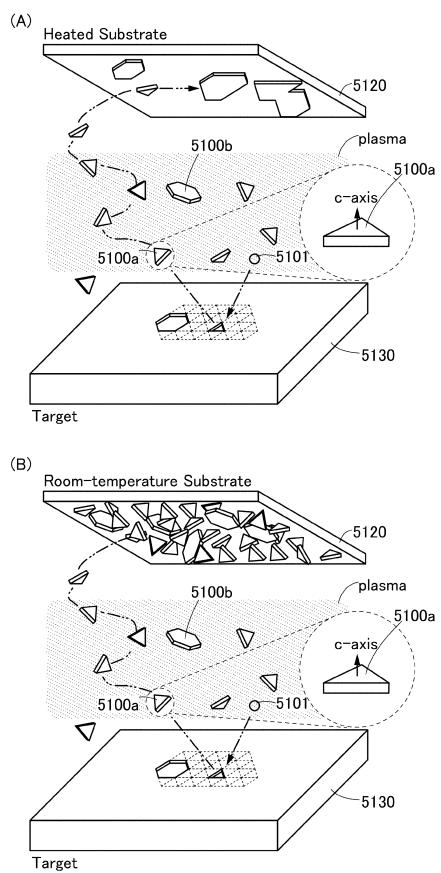

【図48】C A A C - O Sおよびn c - O Sの成膜モデルを説明する模式図。

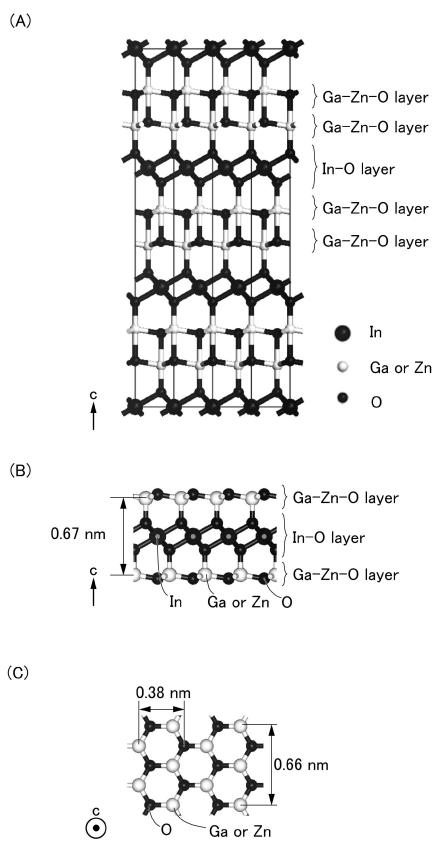

【図49】InGaZnO<sub>4</sub>の結晶、およびペレットを説明する図。

【図50】C A A C - O Sの成膜モデルを説明する模式図。

#### 【発明を実施するための形態】

##### 【0019】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。なお、図を構成する同じ要素のハッチングを異なる図面間で適宜省略または変更する場合もある。 20

##### 【0020】

例えば、本明細書等において、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。 30

##### 【0021】

ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

##### 【0022】

XとYとが直接的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に接続されていない場合であり、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）を介さずに、XとYとが、接続されている場合である。 40

##### 【0023】

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。なお、XとYとが電気的に接続されている場合は、Xと 50

Yとが直接的に接続されている場合を含むものとする。

**【0024】**

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（DA変換回路、AD変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動増幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。なお、XとYとが機能的に接続されている場合は、XとYとが直接的に接続されている場合と、XとYとが電気的に接続されている場合とを含むものとする。10

**【0025】**

なお、XとYとが電気的に接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟んで接続されている場合）と、XとYとが機能的に接続されている場合（つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合）と、XとYとが直接接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟まずに接続されている場合）とが、本明細書等に開示されているものとする。つまり、電気的に接続されている、と明示的に記載されている場合は、単に、接続されている、とのみ明示的に記載されている場合と同様な内容が、本明細書等に開示されているものとする。20

**【0026】**

なお、例えば、トランジスタのソース（又は第1の端子など）が、Z1を介して（又は介さず）、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2を介して（又は介さず）、Yと電気的に接続されている場合や、トランジスタのソース（又は第1の端子など）が、Z1の一部と直接的に接続され、Z1の別の一部がXと直接的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2の一部と直接的に接続され、Z2の別の一部がYと直接的に接続されている場合では、以下のように表現することが出来る。30

**【0027】**

例えば、「XとYとトランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とは、互いに電気的に接続されており、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yの順序で電気的に接続されている。」と表現することができる。または、「トランジスタのソース（又は第1の端子など）は、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）はYと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この順序で電気的に接続されている」と表現することができる。または、「Xは、トランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とを介して、Yと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース（又は第1の端子など）と、ドレイン（又は第2の端子など）とを、区別して、技術的範囲を決定することができる。40

**【0028】**

または、別の表現方法として、例えば、「トランジスタのソース（又は第1の端子など）は、少なくとも第1の接続経路を介して、Xと電気的に接続され、前記第1の接続経路は、第2の接続経路を有しておらず、前記第2の接続経路は、トランジスタを介した、トランジスタのソース（又は第1の端子など）とトランジスタのドレイン（又は第2の端子など）50

ど)との間の経路であり、前記第1の接続経路は、Z1を介した経路であり、トランジスタのドレイン(又は第2の端子など)は、少なくとも第3の接続経路を介して、Yと電気的に接続され、前記第3の接続経路は、前記第2の接続経路を有しておらず、前記第3の接続経路は、Z2を介した経路である。」と表現することができる。または、「トランジスタのソース(又は第1の端子など)は、少なくとも第1の接続経路によって、Z1を介して、Xと電気的に接続され、前記第1の接続経路は、第2の接続経路を有しておらず、前記第2の接続経路は、トランジスタを介した接続経路を有し、トランジスタのドレイン(又は第2の端子など)は、少なくとも第3の接続経路によって、Z2を介して、Yと電気的に接続され、前記第3の接続経路は、前記第2の接続経路を有していない。」と表現することができる。または、「トランジスタのソース(又は第1の端子など)は、少なくとも第1の電気的バスによって、Z1を介して、Xと電気的に接続され、前記第1の電気的バスは、第2の電気的バスを有しておらず、前記第2の電気的バスは、トランジスタのソース(又は第1の端子など)からトランジスタのドレイン(又は第2の端子など)への電気的バスであり、トランジスタのドレイン(又は第2の端子など)は、少なくとも第3の電気的バスによって、Z2を介して、Yと電気的に接続され、前記第3の接続経路は、前記第4の接続経路を有しておらず、前記第4の電気的バスは、トランジスタのドレイン(又は第2の端子など)からトランジスタのソース(又は第1の端子など)への電気的バスである。」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続経路について規定することにより、トランジスタのソース(又は第1の端子など)と、ドレイン(又は第2の端子など)とを、区別して、技術的範囲を決定することができる。

#### 【0029】

なお、これらの表現方法は、一例であり、これらの表現方法に限定されない。ここで、X、Y、Z1、Z2は、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとする。

#### 【0030】

なお、回路図上は独立している構成要素同士が電気的に接続しているように図示されている場合であっても、1つの構成要素が、複数の構成要素の機能を併せ持っている場合もある。例えば配線の一部が電極としても機能する場合は、一の導電膜が、配線の機能、及び電極の機能の両方の構成要素の機能を併せ持っている。したがって、本明細書における電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

#### 【0031】

なお、「膜」という言葉と、「層」という言葉とは、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

#### 【0032】

##### (実施の形態1)

本実施の形態では、本発明の一態様である半導体装置について、図面を参照して説明する。

#### 【0033】

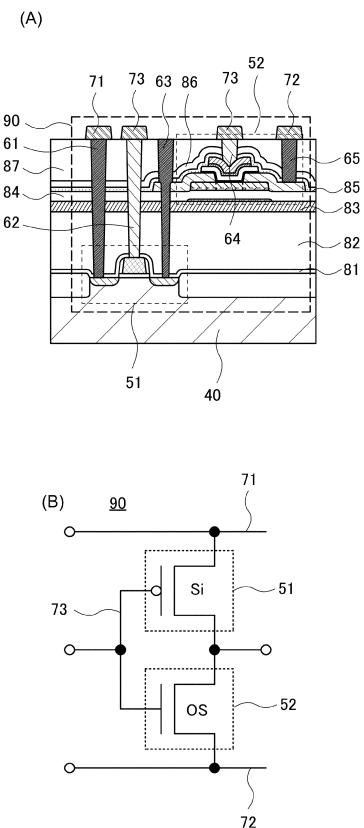

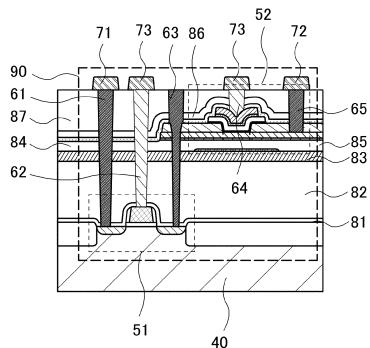

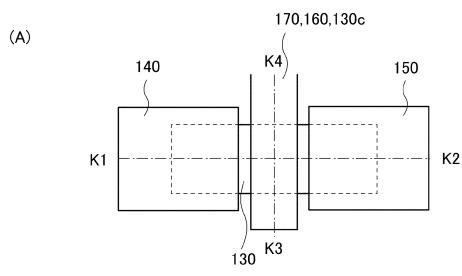

図1(A)は、本発明の一態様の半導体装置の構成を示す断面図である。図1(A)に示す半導体装置は、シリコン基板40に活性領域を有するトランジスタ51と、酸化物半導体層を活性層とするトランジスタ52を有する。トランジスタ51をp-ch型、トランジスタ52をn-ch型とすることでCMOS回路を形成することができる。図1(A)に示すトランジスタの51、52は、インバータ回路90を形成している(図1(B)参照)。

#### 【0034】

トランジスタ51はチャネルが形成される活性領域、ソース領域、ドレイン領域、ゲート

10

20

30

40

50

絶縁膜およびゲート電極を基本構成とする。また、トランジスタ 5 2 はチャネルが形成される活性層、ソース電極、ドレイン電極、ゲート絶縁膜およびゲート電極を基本構成とする。図 1 ( A ) に示すように、トランジスタ 5 1 およびトランジスタ 5 2 のそれぞれが有する上記構成要素の一部が重なることで回路の占有面積を縮小することができる。

【 0 0 3 5 】

また、インバータ回路 9 0 においては、シリコン基板 4 0 に活性領域を有する n - c h 型のトランジスタの工程が不要となるため、p ウェルおよび n 型不純物領域などの形成工程を省くことができ、工程を大幅に削減することができる。

【 0 0 3 6 】

トランジスタ 5 1 上には絶縁層 8 1 、絶縁層 8 2 、絶縁層 8 3 および絶縁層 8 4 が設けられる。ここで、説明の便宜上、絶縁層 8 1 乃至絶縁層 8 4 をまとめて第 1 の絶縁層とする。

【 0 0 3 7 】

また、第 1 の絶縁層上にはトランジスタ 5 2 が設けられ、トランジスタ 5 2 上には絶縁層 8 5 、絶縁層 8 6 および絶縁層 8 7 が設けられる。ここで、説明の便宜上、絶縁層 8 5 乃至絶縁層 8 7 をまとめて第 2 の絶縁層とする。

【 0 0 3 8 】

なお、第 1 の絶縁層および第 2 の絶縁層を構成する絶縁層は上記形態に限らず、上記絶縁層の一部が省かれる場合や、他の絶縁層が付加される場合もある。

【 0 0 3 9 】

トランジスタ 5 1 のソース領域またはドレイン領域の一方は、第 1 の絶縁層および第 2 の絶縁層を貫通するコンタクトプラグ 6 1 と電気的に接続する。また、コンタクトプラグ 6 1 は、第 2 の絶縁層上で配線 7 1 と電気的に接続する。

【 0 0 4 0 】

また、トランジスタ 5 1 のゲート電極は、第 1 の絶縁層および第 2 の絶縁層を貫通するコンタクトプラグ 6 2 と電気的に接続する。また、コンタクトプラグ 6 2 は、第 2 の絶縁層上で配線 7 3 と電気的に接続する。

【 0 0 4 1 】

また、トランジスタ 5 1 のソース領域またはドレイン領域の他方は、第 1 の絶縁層、トランジスタ 5 2 のソース電極またはドレイン電極の一方、および第 2 の絶縁層を貫通するコンタクトプラグ 6 3 と電気的に接続する。ここで、トランジスタ 5 1 のソース領域またはドレイン領域の他方と、トランジスタ 5 2 のソース電極またはドレイン電極の一方とは、コンタクトプラグ 6 3 を介して電気的に接続されることになる。

【 0 0 4 2 】

また、トランジスタ 5 2 のゲート電極は、第 2 の絶縁層を貫通するコンタクトプラグ 6 4 と電気的に接続する。また、コンタクトプラグ 6 4 は、第 2 の絶縁層上で配線 7 3 と電気的に接続する。すなわち、トランジスタ 5 1 のゲート電極とトランジスタ 5 2 のゲート電極とは、コンタクトプラグ 6 2 、配線 7 3 およびコンタクトプラグ 6 4 を介して電気的に接続されることになる。

【 0 0 4 3 】

なお、図 1 ( A ) において、コンタクトプラグ 6 2 、 6 4 は、存在する奥行き方向の位置が他のコンタクトプラグと異なるため、ハッチングを変えて記してある。

【 0 0 4 4 】

また、トランジスタ 5 2 のソース電極またはドレイン電極の他方は、第 2 の絶縁層を貫通するコンタクトプラグ 6 5 と電気的に接続する。また、コンタクトプラグ 6 5 は、第 2 の絶縁層上で配線 7 2 と電気的に接続する。

【 0 0 4 5 】

本発明の一態様の半導体装置においては、互いに重なる領域を有する複数のトランジスタを形成した後にコンタクトプラグを形成し、複数のトランジスタの電気的な接続および当該コンタクトプラグと配線等との接続を行う。このような構成とすることで、工程を簡略

10

20

30

40

50

化することができる。また、トランジスタを形成後に配線を自由に行えるようになるため、工程の一部を変更することで機能の異なる半導体装置を形成することができ、設計および製造のコストを削減することができる。

#### 【0046】

ここで、コンタクトプラグは、まずコンタクトホールを形成し、当該コンタクトホールにCVD (Chemical Vapor Deposition) 法等で導電体を埋め込むように形成する。この工程においては、占有面積を小さくするためにアスペクト比の大きいコンタクトホールを形成することが好ましいが、複数の層を貫通し、かつアスペクト比の大きいコンタクトホールの形成は難度が高い。

#### 【0047】

図1(A)に示すコンタクトプラグ61、62を設けるためのコンタクトホールは、第1の絶縁層および第2の絶縁層をエッチングして形成するため、比較的難度が低い。例えば、酸化物絶縁層や窒化物絶縁層などでは、種類が異なっても同じエッチング条件で処理できる場合が多いのである。

#### 【0048】

一方、コンタクトプラグ63を設けるためのコンタクトホールは、絶縁層のエッチングのほかにトランジスタ52のソース電極またはドレイン電極(代表的には金属層)のエッチングを行わなければならない。絶縁層と金属層ではエッチング条件が異なるため、エッチングガスやエッチャントの切り替えなどをを行わなければならない、実質的に工程増加となる。また、エッチング工程中に堆積物、プラズマダメージ、オーバーエッチングなどによって不良を誘発することもある。

#### 【0049】

したがって、本発明の一態様では、コンタクトプラグ63を設けるためのコンタクトホールの形成を工程増加および不良の誘発をすることなく行うために、予めトランジスタ52のソース電極またはドレイン電極の一方に貫通口を形成する方法を用いる。

#### 【0050】

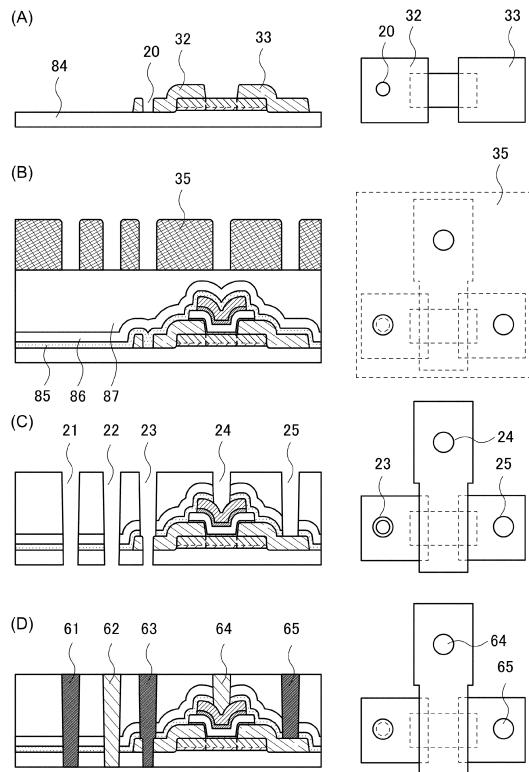

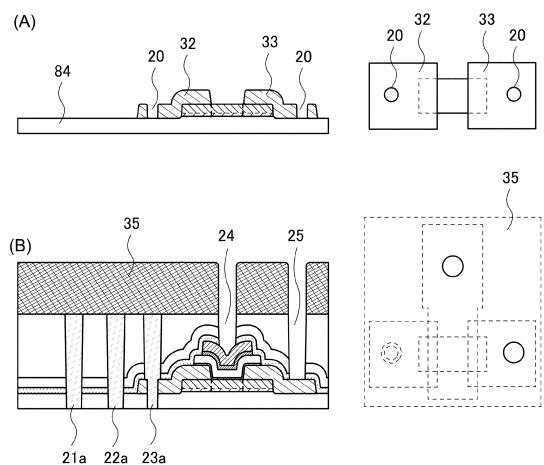

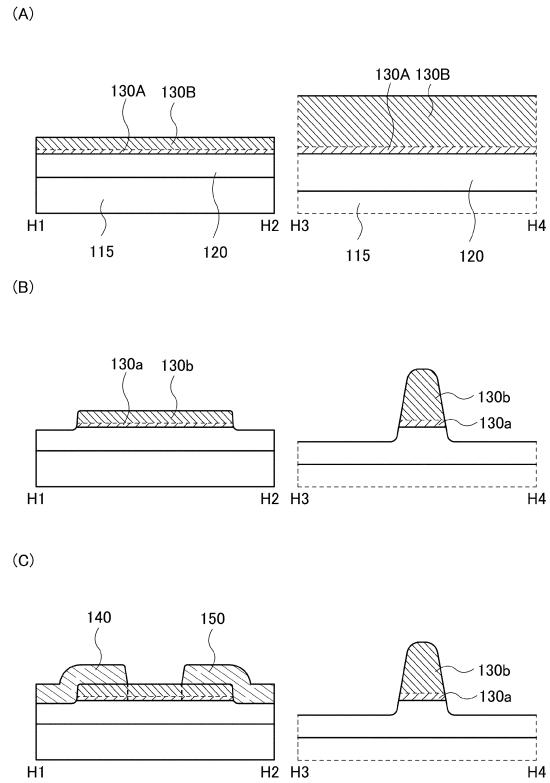

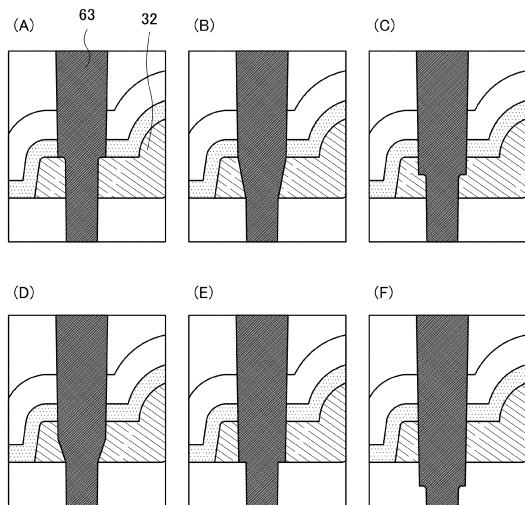

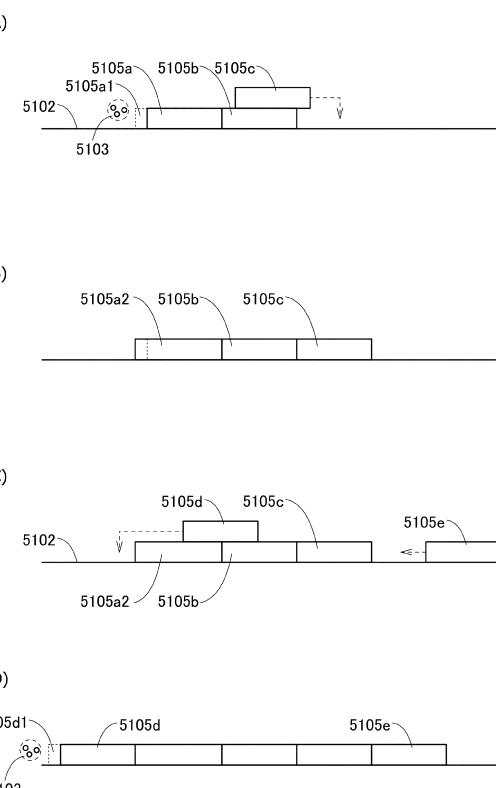

図2(A)乃至図2(D)にコンタクトプラグ63を形成するための工程図を示す。なお、トランジスタ51、およびトランジスタ51上に設けられる絶縁層の一部は図示していない。また、図の左側には断面図を示し、右側には上面図を示す。

#### 【0051】

まず、絶縁層84上に三層構造の酸化物半導体層の二層を形成し、当該酸化物半導体層と接するようにソース電極層32およびドレイン電極層33を形成する(図2(A)参照)。ここで、ソース電極層32に貫通口20を設けておく。貫通口20はソース電極層32およびドレイン電極層33のパターン形成と同一工程で形成することができる。

#### 【0052】

なお、図3(A)に示すように貫通口20はドレイン電極層33にも設けてよい。ドレイン電極層33に設けた貫通口20を使用しない場合は、後の工程で当該貫通口を含まない領域でコンタクトプラグ等とドレイン電極層33を接続すればよい。なお、ソースおよびドレインの名称はトランジスタの動作によって入れ替わるものであり、ソース電極層32およびドレイン電極層33の名称は入れ替えることができる。

#### 【0053】

次に、酸化物半導体層の残りの一層、ゲート絶縁膜およびゲート電極層を形成し、トランジスタ52の基本構成を完成させる。そして、トランジスタ52上に第2の絶縁層を設ける。このとき、貫通口20には第2の絶縁層の一部が形成されている状態となっている。さらに第2の絶縁層上に複数のコンタクトホールを形成するためのレジストマスク35を形成する(図2(B)参照)。

#### 【0054】

そして、エッチング工程を行うことにより、コンタクトホール21乃至コンタクトホール25を形成する(図2(C)参照)。このとき、ソース電極層32には貫通口20が設かれているため、絶縁層のエッチング条件から金属層のエッチング条件に変更することな

10

20

30

40

50

くエッティング工程を容易に行うことができる。

【0055】

なお、エッティング工程においてコンタクトホール23と貫通口20とのずれを生じさせないためには、第2の絶縁層の領域におけるコンタクトホール23の径を貫通口20の径よりも大きくすることが好ましい。したがって、コンタクトホール23は、第2の絶縁層から第1の絶縁層に向かう深さ方向において、トランジスタ52のソース電極層32と第2の絶縁層との界面を境に径が小さくなる形状となる。

【0056】

なお、図2(B)では全てのコンタクトホールを同時に形成するレジストマスクの例を示したが、深さの異なるコンタクトホールを順次形成する手段を用いてもよい。例えば、図3(B)に示すように、相対的に深いコンタクトホールを先に形成した後、当該コンタクトホールに一時的に有機樹脂を充填し、相対的に浅いコンタクトホールを形成する方法を用いてもよい。逆に、相対的に浅いコンタクトホールを先に形成した後、相対的に深いコンタクトホールを形成する方法を用いてもよい。

10

【0057】

そして、上記コンタクトホールに導電層を充填することによりコンタクトプラグ61乃至コンタクトプラグ65を形成する(図2(D)参照)。コンタクトプラグ63においては、コンタクトホール23の形状に従って、トランジスタ52のソース電極層32と前記第2の絶縁層との界面を境に径が変化する形状となる。

【0058】

20

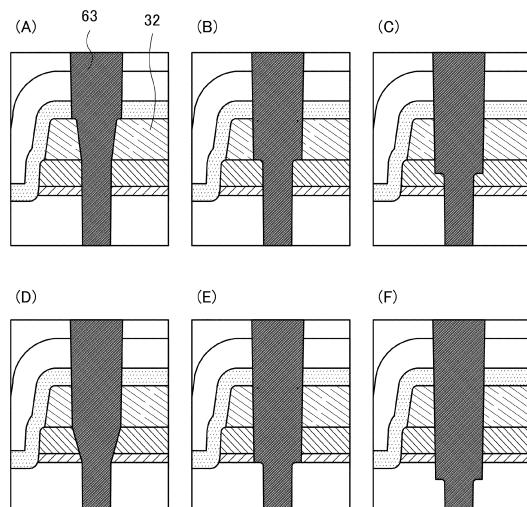

図40(A)乃至図40(F)に、図1(A)に示すトランジスタ52のソース電極層32と前記第2の絶縁層との界面近傍の拡大図を示す。図40(A)は図2(D)の拡大図であるが、本発明の一態様はこれに限らない。エッティング条件を調整することで、貫通口20およびその周辺の形状は様々に変化させることができる。

【0059】

例えば、図40(B)のように貫通口20に形成されたコンタクトプラグ63の側壁の角度がコンタクトプラグ63の他の部位の側壁の角度と異なる形状であってもよい。また、図40(C)のようにソース電極層32の内部でコンタクトプラグ63の径が変化する形状であってもよい。また、図40(D)のようにソース電極層32の内部でコンタクトプラグ63の側壁の角度が変化する形状であってもよい。また、図40(E)のようにソース電極層32と第1の絶縁層との界面を境にコンタクトプラグ63の径が変化する形状であってもよい。また、図40(F)のように、第1の絶縁層の内部でコンタクトプラグ63の径が変化する形状であってもよい。

30

【0060】

なお、コンタクトプラグの側壁は若干のテーパー角を有することから、コンタクトプラグは、深さ方向のいずれの部分においても径が変化しているといえる。一方で、本発明の一態様においては、これらの径の変化とは関係なく、コンタクトプラグが顕著な径の変化がある領域を有することを特徴とする。

【0061】

なお、本発明の一態様の半導体装置に用いるトランジスタ52の形態は酸化物半導体層上にソース電極およびドレイン電極が形成され、当該ソース電極および当該ドレイン電極が絶縁層84と接しない構成としてもよい。このような構成においては、絶縁層84に含まれる酸素がソース電極およびドレイン電極を構成する金属層に奪われることがない。したがって、当該酸素を酸化物半導体層に効率よく供給することができ、トランジスタ52の電気特性および信頼性を向上させることができる。

40

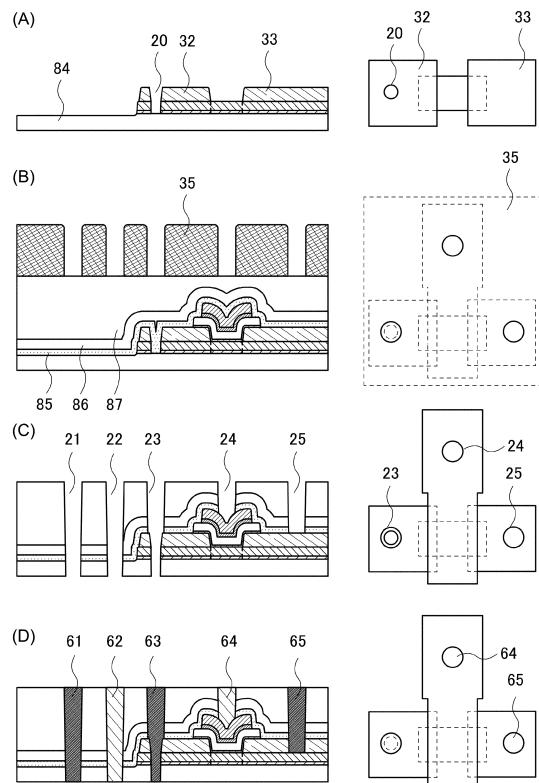

【0062】

上記構成の場合、本発明の一態様の半導体装置は、図4に示すようになる。当該構成においても、トランジスタ52のソース電極またはドレイン電極の一方には貫通口を設けることにより、コンタクトプラグ63を設けるためのコンタクトホールを形成しやすくなる。

【0063】

50

この場合、コンタクトプラグ 6 3 を設けるためのコンタクトホールの形成時においては、酸化物半導体層もエッティングすることになる。酸化物半導体層は絶縁層とエッティング条件が異なる場合があるため、酸化物半導体層にも貫通口を設けておいてもよい。

#### 【 0 0 6 4 】

酸化物半導体層にも貫通口を設ける構成におけるコンタクトプラグ 6 3 を形成するための工程図を図 5 ( A ) 乃至図 5 ( D ) に示す。酸化物半導体層にも貫通口を設ける構成以外は図 2 ( A ) 乃至図 2 ( D ) の工程と同じであり、説明は省略する。

#### 【 0 0 6 5 】

図 4 1 ( A ) 乃至図 4 1 ( F ) に、図 4 に示すトランジスタ 5 2 のソース電極層 3 2 と前記第 2 の絶縁層との界面近傍の拡大図を示す。図 4 1 ( A ) は図 5 ( D ) の拡大図であるが、本発明の一態様はこれに限らない。エッティング条件を調整することで、貫通口 2 0 およびその周辺の形状は様々に変化させることができる。10

#### 【 0 0 6 6 】

例えば、図 4 1 ( B ) のようにソース電極層 3 2 と酸化物半導体層との界面を境にコンタクトプラグ 6 3 の径が変化する形状であってもよい。また、図 4 1 ( C ) のように酸化物半導体層の内部でコンタクトプラグ 6 3 の径が変化する形状であってもよい。また、図 4 1 ( D ) のように酸化物半導体層における貫通口 2 0 に形成されたコンタクトプラグ 6 3 の側壁の角度がコンタクトプラグ 6 3 の他の部位の側壁の角度と異なる形状であってもよい。また、図 4 1 ( E ) のように酸化物半導体層と第 1 の絶縁層との界面を境にコンタクトプラグ 6 3 径が変化する形状であってもよい。また、図 4 1 ( F ) のように、第 1 の絶縁層の内部でコンタクトプラグ 6 3 の径が変化する形状であってもよい。また、図 4 0 に示すコンタクトプラグ 6 3 の形状が組み合わされた形状であってもよい。20

#### 【 0 0 6 7 】

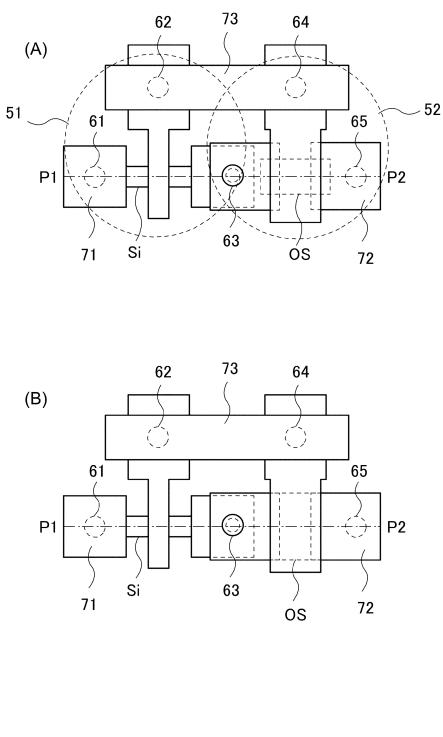

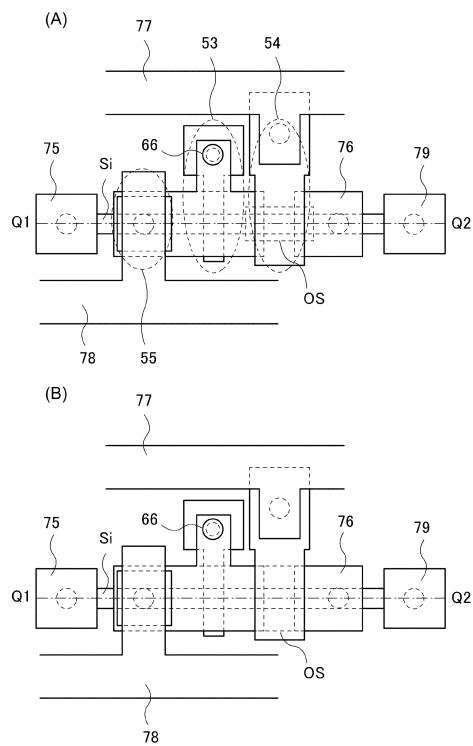

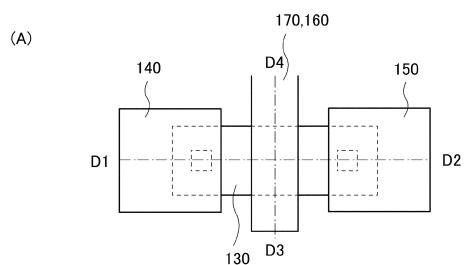

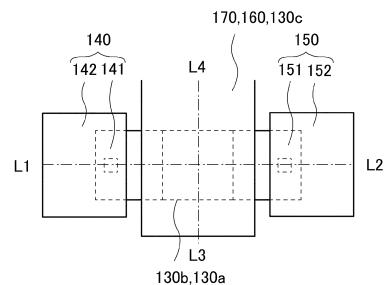

図 6 ( A )、( B ) は、本発明の一態様の半導体装置の上面図である。図 6 ( A ) は図 1 ( A ) に示す半導体装置の上面図であり、図 6 ( B ) は図 4 に示す半導体装置の上面図である。なお、図 1 ( A ) および図 4 は、図 6 ( A )、( B ) に示す P 1 - P 2 の断面に相当する。なお、図中 O S は酸化物半導体で形成された活性層を示し、S i はシリコンの活性領域を示す。

#### 【 0 0 6 8 】

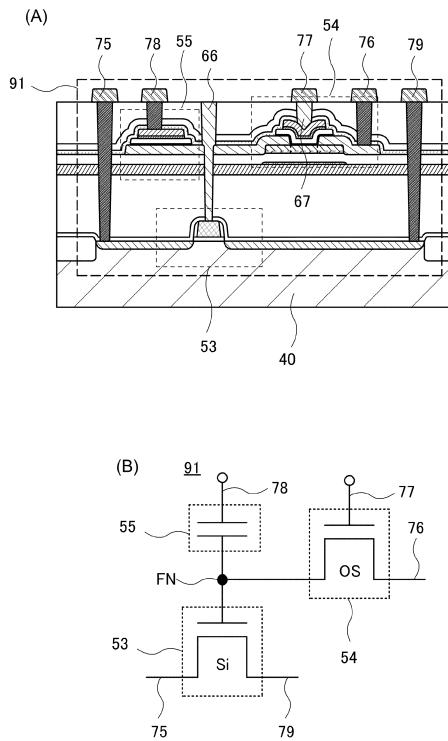

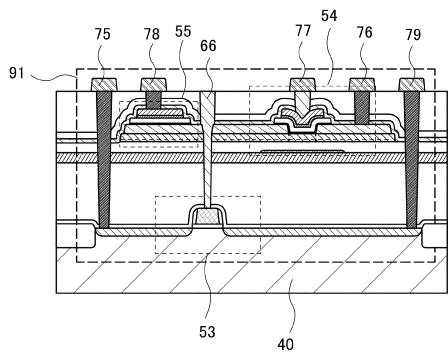

また、本発明の他の一態様を図 7 ( A ) に示す。図 7 ( A ) に示す半導体装置は、シリコン基板 4 0 に活性領域を有するトランジスタ 5 3 と、酸化物半導体層を活性層とするトランジスタ 5 4 および容量素子 5 5 を有する。図 7 ( A ) に示すトランジスタ 5 3、5 4 および容量素子 5 5 の接続形態において、図 7 ( B ) の回路図に示す回路 9 1 を形成している。図 7 ( A ) に示す半導体装置は、容量素子 5 5 を有する点および各要素の接続形態を除き、図 1 ( A ) に示す半導体装置と同等の構成とすることができます。30

#### 【 0 0 6 9 】

ここでは、トランジスタ 5 3 のゲート電極層と、トランジスタ 5 4 のソース電極層またはドレイン電極層の一方と、容量素子 5 5 の一方の電極層を電気的に接続するためにコンタクトプラグ 6 6 を利用する。コンタクトプラグ 6 6 は、トランジスタ 5 4 のソース電極層またはドレイン電極層の一方（容量素子 5 5 の一方の電極層と共に）に設けられた貫通口を通して設けられる。したがって、図 1 ( A ) に示すコンタクトプラグ 6 3 と同様に第 2 の絶縁層から第 1 の絶縁層に向かう深さ方向において、トランジスタ 5 4 のソース電極層またはドレイン電極層の一方と第 2 の絶縁層との界面を境に径が小さくなる形状となる。40

#### 【 0 0 7 0 】

なお、図 7 ( A ) において、コンタクトプラグ 6 6、6 7 は、存在する奥行き方向の位置が他のコンタクトプラグと異なるため、ハッチングを変えて記してある。

#### 【 0 0 7 1 】

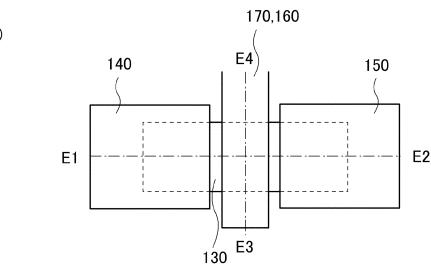

なお、図 4 に示すトランジスタ 5 2 の構造をトランジスタ 5 4 に適用した場合は、図 8 に示す形態となる。また、図 9 ( A ) は、図 7 ( A ) に示す半導体装置の上面図の一例である。また、図 9 ( B ) は図 8 に示す半導体装置の上面図の一例である。なお、図 7 ( A )50

および図8は、図9(A)、(B)に示すQ1-Q2の断面に相当する。

**【0072】**

図7(B)に示す回路91は電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶回路)の一例である。

**【0073】**

酸化物半導体を用いたトランジスタ54は、オフ電流が極めて低い電気特性を有するため、長時間の電荷保持を可能とする。例えば、ソースとドレインとの間の電圧を0.1V、5V、または、10V程度とした場合、トランジスタのチャネル幅で規格化したオフ電流は、数yA/ $\mu$ mから数zA/ $\mu$ mにまで低減することができる。一方、酸化物半導体以外の材料、例えば結晶シリコンなどを用いたトランジスタは、高速動作が容易である。したがって、両者を組み合わせることにより、データの保持能力が高く、動作が高速な記憶装置を構成することができる。10

**【0074】**

図7(B)に示す半導体装置では、トランジスタ53のゲート電極の電位が保持可能という特徴を活かすこと、次のように、情報の書き込み、保持、読み出しが可能である。

**【0075】**

情報の書き込みおよび保持について説明する。まず、配線77の電位をトランジスタ54がオン状態となる電位にして、トランジスタ54をオン状態とする。

**【0076】**

上記動作により、配線76の電位が、トランジスタ53のゲート電極、および容量素子55に与えられる。すなわち、ノードFNには、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下Lowレベル電荷、Highレベル電荷という)のいずれかが与えられるものとする。20

**【0077】**

その後、配線77の電位をトランジスタ54がオフ状態となる電位にして、トランジスタ54をオフ状態とすることにより、ノードFNに与えられた電荷が保持される(保持)。トランジスタ54のオフ電流は極めて小さいため、ノードFNの電荷は長時間にわたって保持される。

**【0078】**

次に情報の読み出しについて説明する。配線75に所定の電位(定電位)を与えた状態で、配線78に適切な電位(読み出し電位)を与えると、ノードFNに保持された電荷量に応じて、配線79は異なる電位をとる。30

**【0079】**

一般に、トランジスタ53をnチャネル型とすると、トランジスタ53のゲート電極(ノードFN)にHighレベル電荷が与えられている場合の見かけのしきい値電圧 $V_{th\_H}$ は、トランジスタ53のゲート電極(ノードFN)にLowレベル電荷が与えられている場合の見かけのしきい値電圧 $V_{th\_L}$ より低くなる。

**【0080】**

ここで、見かけのしきい値電圧とは、トランジスタ53を「オン状態」とするために必要な配線78の電位をいうものとする。したがって、配線78の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ53のゲート電極(ノードFN)に与えられた電荷を判別できる。40

**【0081】**

例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、配線78の電位が $V_0$ ( $> V_{th\_H}$ )となれば、トランジスタ53は「オン状態」となる。Lowレベル電荷が与えられていた場合には、配線78の電位が $V_0$ ( $< V_{th\_L}$ )となっても、トランジスタ53は「オフ状態」のままである。このため、配線79の電位を判別することで、保持されている情報を読み出すことができる。

**【0082】**

なお、メモリセルをアレイ状に配置して用いる場合は、所望のメモリセルの情報をのみを読50

み出せることになる。このように情報を読み出さないメモリセルにおいては、ゲート電極に与えられている電位にかかわらず、トランジスタ53が「オフ状態」となるような電位、つまり、 $V_{t h\_H}$ より小さい電位を配線78に与えればよい。または、ゲート電極に与えられている電位にかかわらず、トランジスタ53が「オン状態」となるような電位、つまり、 $V_{t h\_L}$ より大きい電位を配線78に与えればよい。

#### 【0083】

図7(B)に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合(ただし、電位は固定されていることが望ましい)であっても、長期にわたって記憶内容を保持することが可能である。なお、記憶内容の保持期間中に電力を供給する動作を行ってもよい。

10

#### 【0084】

また、上述した駆動方法においては、ノードFNへの情報の書き込みに高い電圧を必要とせず、トランジスタ53の劣化の問題もない。例えば、従来の不揮発性メモリのような高電圧印加によるフローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う動作がないため、トランジスタ53のゲート絶縁膜の劣化などの問題が生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。

20

#### 【0085】

上述した本発明の一態様の半導体装置の構成要素について説明する。なお、以下においては、図1(A)に示す半導体装置を対象として説明するが、本実施の形態に示す他の半導体装置も同様である。

#### 【0086】

シリコン基板40はバルクのシリコン基板に限らず、SOI基板であってもよい。また、シリコン基板40に替えて、ゲルマニウム、シリコングルマニウム、炭化シリコン、ガリウムヒ素、アルミニウムガリウムヒ素、インジウムリン、窒化ガリウム、有機半導体を材料とする基板を用いることもできる。

30

#### 【0087】

なお、トランジスタ51は、プレーナ型のトランジスタだけでなく、様々なタイプのトランジスタとすることができます。例えば、FIN(フィン)型、TRI-GATE(トライゲート)型などのトランジスタなどとすることができます。

#### 【0088】

絶縁層81は保護膜として機能させることができ、代表的には窒化シリコン膜や酸化アルミニウム膜を用いることができる。また絶縁層82および絶縁層87は平坦化膜として機能させることができ、代表的には酸化シリコン膜、酸化窒化シリコン膜などを用いることができる。

40

#### 【0089】

絶縁層83は、水素プロック膜として機能させることができる。トランジスタ51の活性領域近傍に設けられる絶縁層中の水素はシリコンのダンギングボンドを終端し、トランジスタ51の信頼性を向上させる効果がある。一方、上層に設けられるトランジスタ52の活性層である酸化物半導体層の近傍に設けられる絶縁層中の水素は、酸化物半導体中にキャリアを生成する要因の一つとなるため、トランジスタ52の信頼性を低下させる要因となる場合がある。したがって、シリコン系半導体材料を用いたトランジスタの上層に酸化物半導体を用いたトランジスタを積層して設ける場合、これらの間に水素の拡散を防止する機能を有する絶縁層83を設けることが好ましい。絶縁層83により、下層に水素を閉じ込めてトランジスタ51の信頼性が向上することに加え、下層から上層に水素

50

が拡散することが抑制されることでトランジスタ 5 2 の信頼性も同時に向上させることができる。

#### 【 0 0 9 0 】

絶縁層 8 3 としては、例えば、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、イットリア安定化ジルコニア(YSZ)等を用いることができる。なお、絶縁層 8 5 もこれらの材料で形成することができる。

#### 【 0 0 9 1 】

絶縁層 8 4 はトランジスタ 5 2 の酸化物半導体層に対する酸素の供給源として機能する。

したがって、絶縁層 8 4 は酸素を含む絶縁層であり、化学量論組成よりも酸素が多い組成

であることが好ましい。また、絶縁層 8 4 は、トランジスタ 5 2 のバックゲート側のゲー

ト絶縁膜としても機能させることができるために、酸化物半導体層との界面において、欠陥

を生成しにくい膜であることが好ましい。

10

#### 【 0 0 9 2 】

絶縁層 8 4 としては、代表的には酸化シリコン膜、酸化窒化シリコン膜を用いることができる。また、窒化シリコン膜または窒化酸化シリコン膜と上記絶縁層との積層であってもよい。なお、絶縁層 8 6 もこれらの材料で形成することができる。

#### 【 0 0 9 3 】

コンタクトプラグ 6 1 乃至コンタクトプラグ 6 5 は代表的には金属材料で形成することができる。具体的には、タンゲステンを用いることができる。また、コンタクトプラグは、

壁面に窒化チタンを設け、その内部にタンゲステンを設ける構成としてもよい。なお、絶

縁層およびコンタクトプラグ上面の平坦化には CMP (Chemical Mechanical

Polishing) 法を用いることができる。

20

#### 【 0 0 9 4 】

本実施の形態では、本発明の一態様をインバータ回路および記憶回路の構成を例として説明したが、他の回路に応用することも可能である。また、二つのトランジスタが重なる例に限らず、3個以上のトランジスタ等の要素を電気的に接続する場合においても応用する

ことが可能である。

#### 【 0 0 9 5 】

また、本実施の形態では、シリコンを活性領域に有するトランジスタと酸化物半導体を活

性層に有するトランジスタを積層する例を示したが、これに限らない。シリコンを有する

トランジスタを複数積層する場合にも適用することができる。また、酸化物半導体を有す

るトランジスタを複数積層する場合にも適用することができる。

30

#### 【 0 0 9 6 】

また、本発明の一態様は、重なる配線の電気的な接続にも適用することができる。

#### 【 0 0 9 7 】

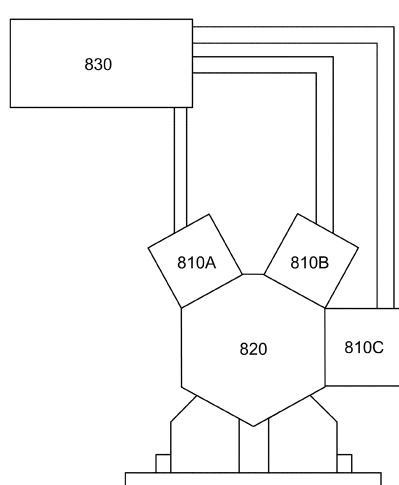

図 4 2 に複数の膜種を有する多層膜をエッティングするためのエッティング装置の一例を示す。

図 4 2 に示したエッティング装置は、エッティングチャンバー 8 1 0 A、8 1 0 B、8 1 0

C と、基板を各エッティングチャンバーへ移動する際に一時的に基板を待機させることを目的

としたトランスファー・チャンバー 8 2 0 と、各エッティングチャンバーへエッティングガス

等を供給するガス供給システム 8 3 0 と、を有する。また、図示していないが、各電源供

給システム、ポンプシステム、およびガス除害システム等を有する。

40

#### 【 0 0 9 8 】

複数の膜種を有する多層膜に微細な開口部を形成するには、平行平板型のエッティング装置

を用いることが好ましい。特に、高密度プラズマ発生源などを有するエッティング装置を用

いることが好ましい。または、各層のエッティングにおいて、適宜最適なエッティングガスを

選択できるガス供給システムを有することが好ましい。特に、複数のガスを組み合わせる

事ができるガス供給システムを有することが好ましい。

#### 【 0 0 9 9 】

例えば、複数の膜種を有する多層膜への微細な開口部の形成を、一つのエッティングチャン

50

バーで行ってもよい。この方法では、各層において最適なエッティングガスを用いればよい。図42のように、3つのエッティングチャンバーを有するエッティング装置であれば、複数の基板を同時並行的に処理することが可能である。そのため、生産効率を高めることができる。

#### 【0100】

一つのエッティングチャンバーで複数の膜種を有する多層膜をエッティングする場合、エッティングチャンバーでは、エッティングする膜種に応じて最適なガスに切り替える。そのため、様々なエッティング生成物がエッティングチャンバー壁に堆積することがある。これが、エッティングチャンバー壁から剥がれ、パーティクルとなることがある。パーティクルが基板上に付着するとエッティング不良を引き起こすことがある。

10

#### 【0101】

このようなパーティクルの発生を防止する方法としては、膜種毎にエッティングチャンバーを決めて、エッティングする方法がある。以下では、図42に示したエッティング装置を用いて、複数の膜種を有する多層膜をエッティングする場合の一例を示す。ここで用いるエッティングの対象物は、第1の絶縁膜と、第2の絶縁膜と、第3の絶縁膜と、酸化物半導体膜と、導電膜と、第4の絶縁膜と、有機樹脂膜と、フォトレジストと、が基板上にこの順に形成されている積層物とする。なお、フォトレジストは、露光および現像を経て、所定の形状を有する。

#### 【0102】

まず、基板をエッティングチャンバー810Aに配置し、有機樹脂膜および第4の絶縁膜のエッティングを行う。次に基板を、エッティングチャンバー810Aから、トランスマスター・チャンバー820を介して、エッティングチャンバー810Bに移動させ、導電膜をエッティングする。次に基板を、エッティングチャンバー810Bから、トランスマスター・チャンバー820を介して、エッティングチャンバー810Aに移動させ、酸化物半導体膜、第3の絶縁膜および第2の絶縁膜をエッティングする。次に基板を、エッティングチャンバー810Aから、トランスマスター・チャンバー820を介して、エッティングチャンバー810Cに移動させ、アッショングすることでこれまでのエッティングで生じた生成物を除去する。次に基板を、エッティングチャンバー810Cから、トランスマスター・チャンバー820を介して、エッティングチャンバー810Aに移動させ、第1の絶縁膜をエッティングする。次に基板を、エッティングチャンバー810Aから、トランスマスター・チャンバー820を介して、エッティングチャンバー810Cへ移動させ、アッショングすることでフォトレジストおよび有機樹脂膜を除去する。

20

30

40

#### 【0103】

上記一例より、さらに多層膜となっている構成であっても、上記手順を繰り返すことにより、微細な開口部を形成することができる。

#### 【0104】

上記の一例の場合は、複数の膜種を有する多層膜をエッティングするために複数のエッティングチャンバーを用いる。このとき、基板は、真空中で移動され、大気雰囲気にさらされることがないので、再現性のよいエッティングができる。また、各エッティングチャンバーにおいては、膜種毎にエッティングガスを切り替えることがない。そのため、処理時間が短くなり、生産効率を高くすることができる。

#### 【0105】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

#### 【0106】

##### (実施の形態2)

本実施の形態では、本発明の一態様に用いることのできる酸化物半導体を有するトランジスタについて図面を用いて説明する。なお、本実施の形態における図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。

#### 【0107】

50

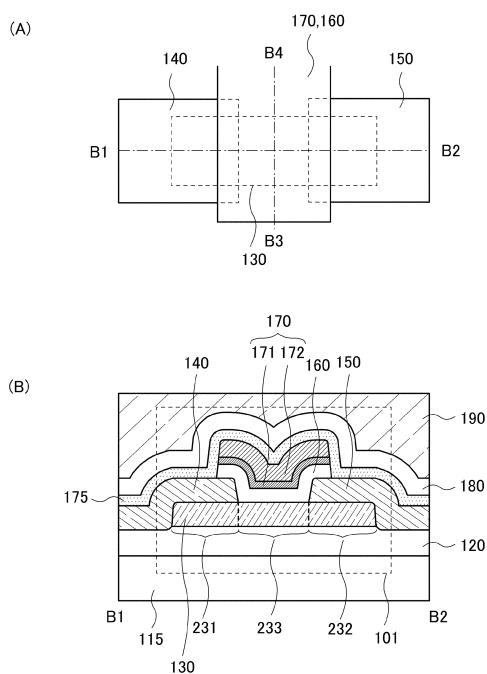

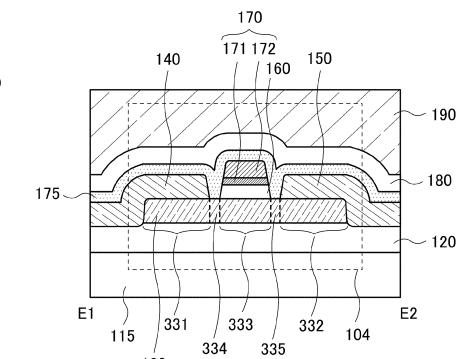

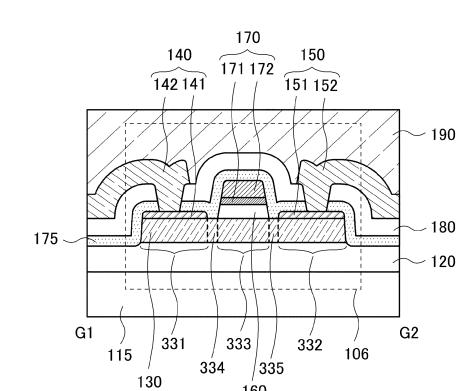

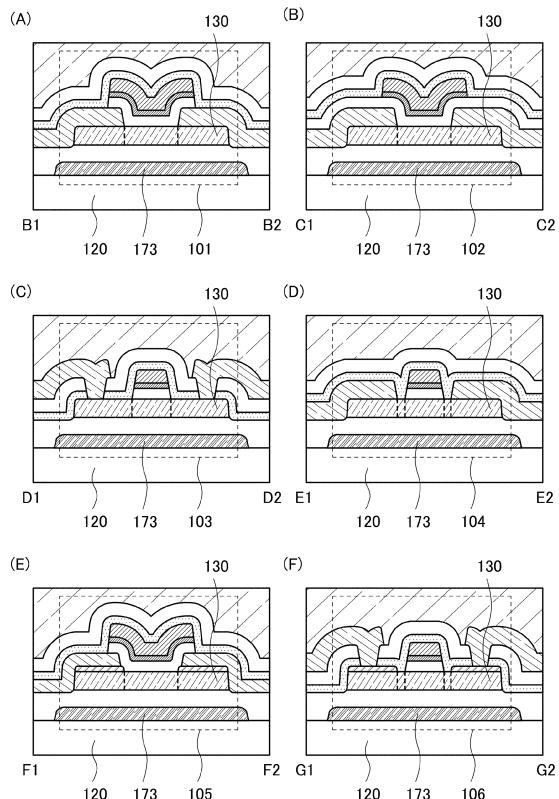

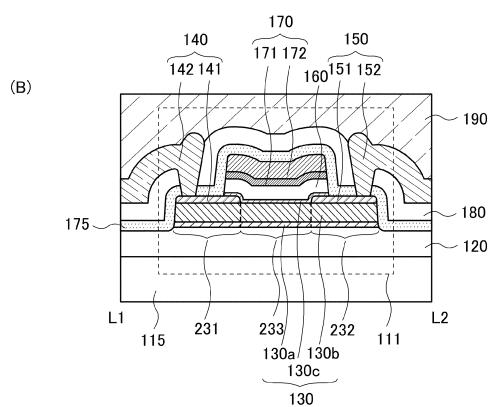

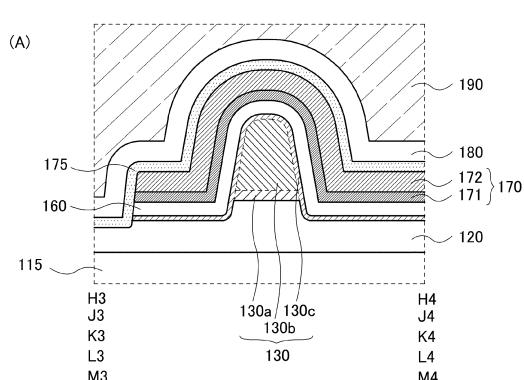

図10( A )、( B )は、本発明の一態様のトランジスタ101の上面図および断面図である。図10( A )は上面図であり、図10( A )に示す一点鎖線B1-B2方向の断面が図10( B )に相当する。また、図10( A )に示す一点鎖線B3-B4方向の断面が図16( A )に相当する。また、一点鎖線B1-B2方向をチャネル長方向、一点鎖線B3-B4方向をチャネル幅方向と呼称する場合がある。

#### 【0108】

トランジスタ101は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130と、酸化物半導体層130と電気的に接続する導電層140および導電層150と、酸化物半導体層130、導電層140および導電層150と接する絶縁層160と、絶縁層160と接する導電層170と、導電層140、導電層150、絶縁層160および導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、を有する。また、必要に応じて絶縁層180に接する絶縁層190(平坦化膜)などを有していてもよい。

#### 【0109】

ここで、導電層140はソース電極層、導電層150はドレイン電極層、絶縁層160はゲート絶縁膜、導電層170はゲート電極層としてそれぞれ機能することができる。

#### 【0110】

また、図10( B )に示す領域231はソース領域、領域232はドレイン領域、領域233はチャネル形成領域として機能することができる。領域231および領域232は導電層140および導電層150とそれぞれ接しており、例えば導電層140および導電層150として酸素と結合しやすい導電材料を用いれば領域231および領域232を低抵抗化することができる。

#### 【0111】

具体的には、酸化物半導体層130と導電層140および導電層150とが接することで酸化物半導体層130内に酸素欠損が生じ、当該酸素欠損と酸化物半導体層130内に残留または外部から拡散する水素との相互作用により、領域231および領域232は低抵抗のn型となる。

#### 【0112】

なお、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。また、「電極層」は、「配線」と言い換えることもできる。

#### 【0113】

また、導電層170は、導電層171および導電層172の二層で形成される例を図示しているが、一層または三層以上の積層であってもよい。当該構成は本実施の形態で説明する他のトランジスタにも適用できる。

#### 【0114】

また、導電層140および導電層150は単層で形成される例を図示しているが、二層以上の積層であってもよい。当該構成は本実施の形態で説明する他のトランジスタにも適用できる。

#### 【0115】

また、本発明の一態様のトランジスタは、図11( A )、( B )に示す構成であってもよい。図11( A )はトランジスタ102の上面図であり、図11( A )に示す一点鎖線C1-C2方向の断面が図11( B )に相当する。また、図11( A )に示す一点鎖線C3-C4方向の断面は、図16( B )に相当する。また、一点鎖線C1-C2方向をチャネル長方向、一点鎖線C3-C4方向をチャネル幅方向と呼称する場合がある。

#### 【0116】

トランジスタ102は、ゲート絶縁膜として作用する絶縁層160がゲート電極層として作用する導電層170と端部を一致させない点を除き、トランジスタ101と同様の構成

10

20

30

40

50

を有する。トランジスタ 102 の構造は、導電層 140 および導電層 150 が絶縁層 160 で広く覆われているため、導電層 140 および導電層 150 と導電層 170 との間の抵抗が高く、ゲートリーク電流の少ない特徴を有している。

#### 【0117】

トランジスタ 101 およびトランジスタ 102 は、導電層 170 と導電層 140 および導電層 150 が重なる領域を有するトップゲート構造である。当該領域のチャネル長方向の幅は、寄生容量を小さくするために 3 nm 以上 300 nm 未満とすることが好ましい。一方で、酸化物半導体層 130 にオフセット領域が形成されないため、オン電流の高いトランジスタを形成しやすい。

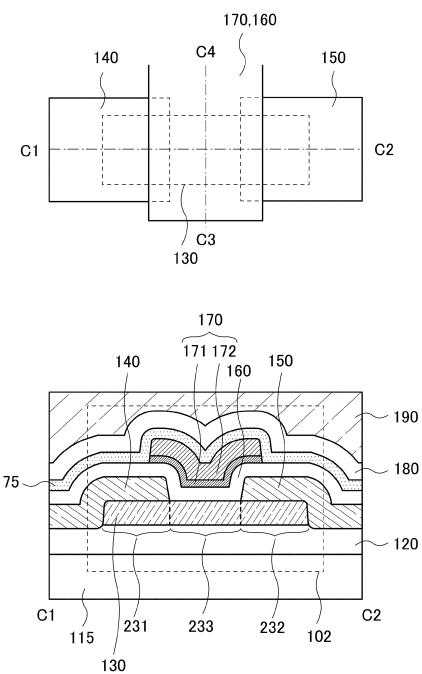

#### 【0118】

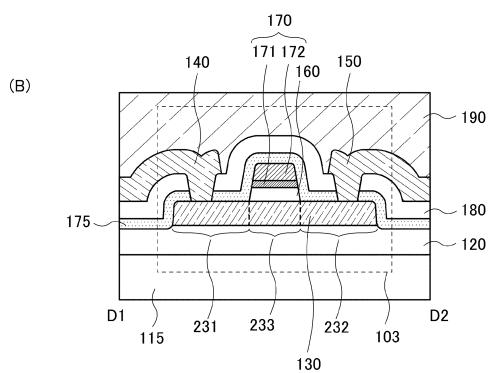

また、本発明の一態様のトランジスタは、図 12 (A)、(B) に示す構成であってもよい。図 12 (A) はトランジスタ 103 の上面図であり、図 12 (A) に示す一点鎖線 D1 - D2 方向の断面が図 12 (B) に相当する。また、図 12 (A) に示す一点鎖線 D3 - D4 方向の断面は、図 16 (A) に相当する。また、一点鎖線 D1 - D2 方向をチャネル長方向、一点鎖線 D3 - D4 方向をチャネル幅方向と呼称する場合がある。

#### 【0119】

トランジスタ 103 は、基板 115 と接する絶縁層 120 と、絶縁層 120 と接する酸化物半導体層 130 と、酸化物半導体層 130 と接する絶縁層 160 と、絶縁層 160 と接する導電層 170 と、酸化物半導体層 130 、絶縁層 160 および導電層 170 を覆う絶縁層 175 と、絶縁層 175 と接する絶縁層 180 と、絶縁層 175 および絶縁層 180 に設けられた開口部を通じて酸化物半導体層 130 と電気的に接続する導電層 140 および導電層 150 を有する。また、必要に応じて絶縁層 180 、導電層 140 および導電層 150 に接する絶縁層 190 (平坦化膜)などを有していてもよい。

#### 【0120】

ここで、導電層 140 はソース電極層、導電層 150 はドレイン電極層、絶縁層 160 はゲート絶縁膜、導電層 170 はゲート電極層としてそれぞれ機能することができる。

#### 【0121】

また、図 12 (B) に示す領域 231 はソース領域、領域 232 はドレイン領域、領域 233 はチャネル形成領域として機能することができる。領域 231 および領域 232 は絶縁層 175 と接しており、例えば絶縁層 175 として水素を含む絶縁材料を用いれば領域 231 および領域 232 を低抵抗化することができる。

#### 【0122】

具体的には、絶縁層 175 を形成するまでの工程により領域 231 および領域 232 に生じる酸素欠損と、絶縁層 175 から領域 231 および領域 232 に拡散する水素との相互作用により、領域 231 および領域 232 は低抵抗の n 型となる。なお、水素を含む絶縁材料としては、例えば窒化シリコンや窒化アルミニウムなどを用いることができる。

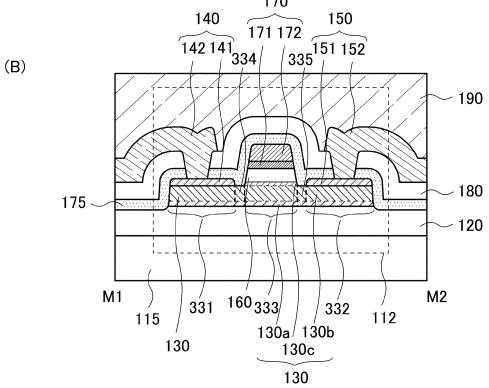

#### 【0123】

また、本発明の一態様のトランジスタは、図 13 (A)、(B) に示す構成であってもよい。図 13 (A) はトランジスタ 104 の上面図であり、図 13 (A) に示す一点鎖線 E1 - E2 方向の断面が図 13 (B) に相当する。また、図 13 (A) に示す一点鎖線 E3 - E4 方向の断面は、図 16 (A) に相当する。また、一点鎖線 E1 - E2 方向をチャネル長方向、一点鎖線 E3 - E4 方向をチャネル幅方向と呼称する場合がある。

#### 【0124】

トランジスタ 104 は、導電層 140 および導電層 150 が酸化物半導体層 130 の端部を覆うように接している点を除き、トランジスタ 103 と同様の構成を有する。

#### 【0125】

また、図 13 (B) に示す領域 331 および領域 334 はソース領域、領域 332 および領域 335 はドレイン領域、領域 333 はチャネル形成領域として機能することができる。領域 331 および領域 332 はトランジスタ 101 における領域 231 および領域 232 と同様に低抵抗化することができる。また、領域 334 および領域 335 はトランジス

タ103における領域231および領域232と同様に低抵抗化することができる。なお、チャネル長方向における領域334および領域335の幅が100nm以下、好ましくは50nm以下の場合には、ゲート電界の寄与によりオン電流は大きく低下しないため、上述したような低抵抗化を行わない構成とすることもできる。

#### 【0126】

トランジスタ103およびトランジスタ104は、導電層170と導電層140および導電層150が重なる領域を有さないセルファーライン構造である。セルファーライン構造のトランジスタはゲート電極層とソース電極層およびドレイン電極層間の寄生容量が極めて小さいため、高速動作用途に適している。

#### 【0127】

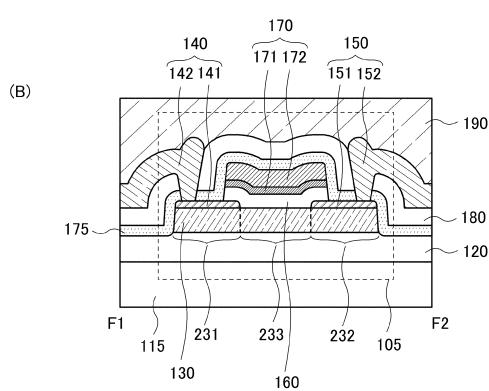

また、本発明の一態様のトランジスタは、図14(A)、(B)に示す構成であってもよい。図14(A)はトランジスタ105の上面図であり、図14(A)に示す一点鎖線F1-F2方向の断面が図14(B)に相当する。また、図14(A)に示す一点鎖線F3-F4方向の断面は、図16(A)に相当する。また、一点鎖線F1-F2方向をチャネル長方向、一点鎖線F3-F4方向をチャネル幅方向と呼称する場合がある。

#### 【0128】

トランジスタ105は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130と、酸化物半導体層130と電気的に接続する導電層141および導電層151と、酸化物半導体層130、導電層141、導電層151と接する絶縁層160と、絶縁層160と接する導電層170と、酸化物半導体層130、導電層141、導電層151、絶縁層160および導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する。また、必要に応じて絶縁層180、導電層142および導電層152に接する絶縁層190(平坦化膜)などを有してもよい。

#### 【0129】

ここで、導電層141および導電層151は、酸化物半導体層130の上面と接し、側面には接しない構成となっている。

#### 【0130】

トランジスタ105は、導電層141および導電層151を有する点、および絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する点を除き、トランジスタ101と同様の構成を有する。導電層140(導電層141および導電層142)はソース電極層として作用させることができ、導電層150(導電層151および導電層152)はドレイン電極層として作用させることができる。

#### 【0131】

また、本発明の一態様のトランジスタは、図15(A)、(B)に示す構成であってもよい。図15(A)はトランジスタ106の上面図であり、図15(A)に示す一点鎖線G1-G2方向の断面が図15(B)に相当する。また、図15(A)に示す一点鎖線G3-G4方向の断面は、図16(A)に相当する。また、一点鎖線G1-G2方向をチャネル長方向、一点鎖線G3-G4方向をチャネル幅方向と呼称する場合がある。

#### 【0132】

トランジスタ106は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130と、酸化物半導体層130と電気的に接続する導電層141および導電層151と、酸化物半導体層130と接する絶縁層160と、絶縁層160と接する導電層170と、絶縁層120、酸化物半導体層130、導電層141、導電層151、絶縁層160、導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する。また、必要に応じて絶縁層180、導電層142および導電層152に接する絶縁層190(平

10

20

30

40

50

坦化膜)などを有していてもよい。

**【0133】**

ここで、導電層141および導電層151は、酸化物半導体層130の上面と接し、側面には接しない構成となっている。

**【0134】**

トランジスタ106は、導電層141および導電層151を有する点を除き、トランジスタ103と同様の構成を有する。導電層140(導電層141および導電層142)はソース電極層として作用させることができ、導電層150(導電層151および導電層152)はドレイン電極層として作用させることができる。

**【0135】**

トランジスタ105およびトランジスタ106の構成では、導電層140および導電層150が絶縁層120と接しない構成であるため、絶縁層120中の酸素が導電層140および導電層150に奪われにくくなり、絶縁層120から酸化物半導体層130中への酸素の供給を容易とすることができます。

**【0136】**

なお、トランジスタ103における領域231および領域232、トランジスタ104およびトランジスタ106における領域334および領域335には、酸素欠損を形成し導電率を高めるための不純物を添加してもよい。酸化物半導体層に酸素欠損を形成する不純物としては、例えば、リン、砒素、アンチモン、ホウ素、アルミニウム、シリコン、窒素、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、インジウム、フッ素、塩素、チタン、亜鉛、および炭素のいずれかから選択される一つ以上を用いることができる。当該不純物の添加方法としては、プラズマ処理法、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。

**【0137】**

不純物元素として、上記元素が酸化物半導体層に添加されると、酸化物半導体層中の金属元素および酸素の結合が切断され、酸素欠損が形成される。酸化物半導体層に含まれる酸素欠損と酸化物半導体層中に残存または後から添加される水素の相互作用により、酸化物半導体層の導電率を高くすることができる。

**【0138】**

なお、不純物元素の添加により酸素欠損が形成された酸化物半導体に水素を添加すると、酸素欠損サイトに水素が入り伝導帯近傍にドナー準位が形成される。その結果、酸化物導電体を形成することができる。このため、酸化物導電体は透光性を有する。なお、ここでは、導電体化された酸化物半導体を酸化物導電体という。

**【0139】**

酸化物導電体は、縮退半導体であり、伝導帯端とフェルミ準位とが一致または略一致していると推定される。このため、酸化物導電体層とソース電極層およびドレイン電極層として機能する導電層との接触はオーミック接触であり、酸化物導電体層とソース電極層およびドレイン電極層として機能する導電層との接触抵抗を低減することができる。

**【0140】**

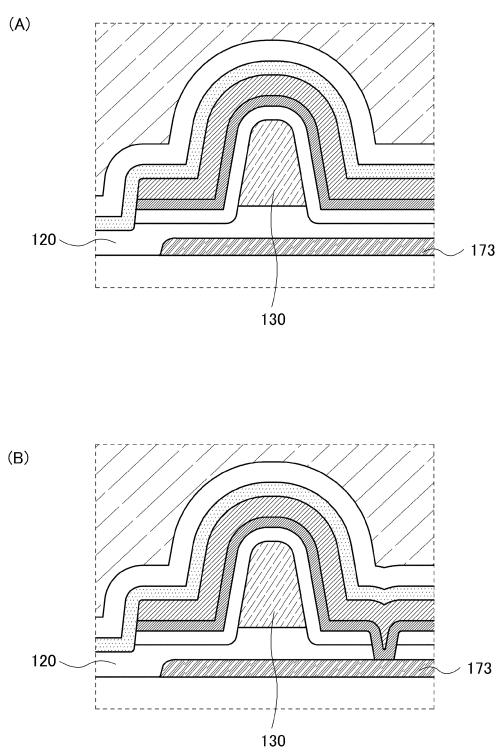

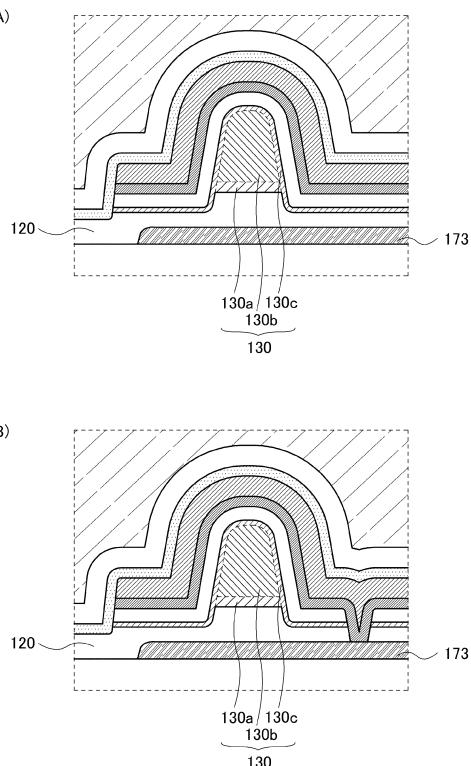

また、本発明の一態様のトランジスタは、図17(A)、(B)、(C)、(D)、(E)、(F)に示すチャネル長方向の断面図、ならびに図18(A)、(B)に示すチャネル幅方向の断面図のように、酸化物半導体層130と基板115との間に導電層173を備えていてもよい。当該導電層を第2のゲート電極層(バックゲート)として用いることで、オン電流の増加や、しきい値電圧の制御を行うことができる。なお、図17(A)、(B)、(C)、(D)、(E)、(F)に示す断面図において、導電層173の幅を酸化物半導体層130よりも短くしてもよい。さらに、導電層173の幅を導電層170の幅よりも短くしてもよい。

**【0141】**

オン電流を増加させるには、例えば、導電層170と導電層173を同電位とし、ダブルゲートトランジスタとして駆動させればよい。また、しきい値電圧の制御を行うには、導

10

20

30

40

50

電層 170 とは異なる定電位を導電層 173 に供給すればよい。導電層 170 と導電層 173 を同電位とするには、例えば、図 18 (B) に示すように、導電層 170 と導電層 173 とをコンタクトホールを介して電気的に接続すればよい。

#### 【0142】

また、図 10 乃至図 15 におけるトランジスタ 101 乃至トランジスタ 106 では、酸化物半導体層 130 が単層である例を図示したが、酸化物半導体層 130 は積層であってもよい。トランジスタ 101 乃至トランジスタ 106 の酸化物半導体層 130 は、図 19 または図 20 に示す酸化物半導体層 130 に入れ替えることができる。

#### 【0143】

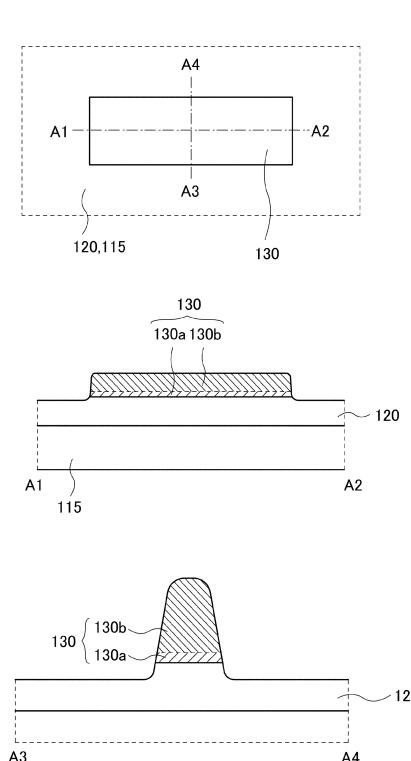

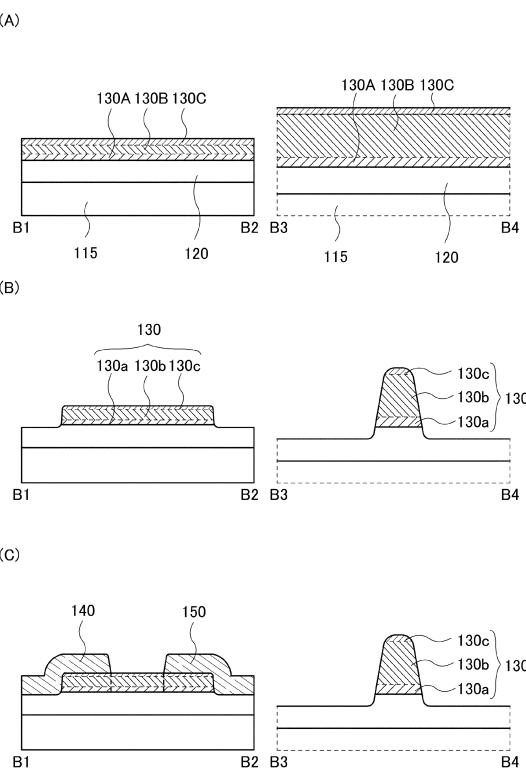

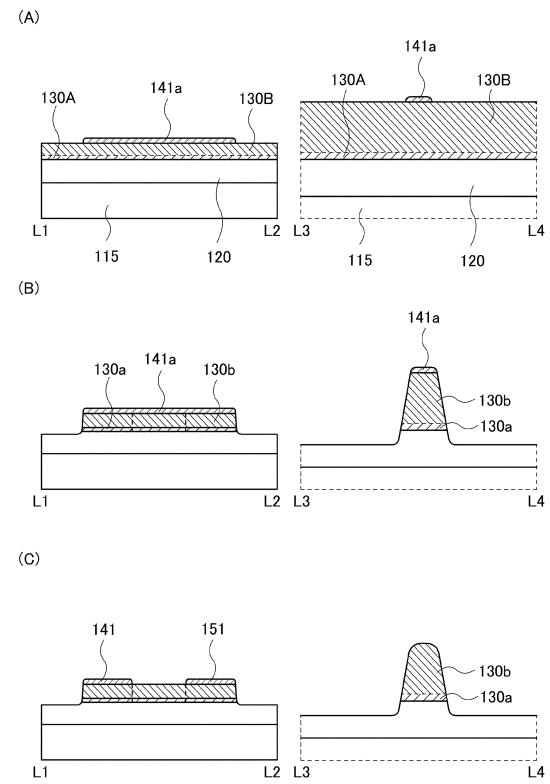

図 19 (A)、(B)、(C) は、二層構造である酸化物半導体層 130 の上面図および断面図である。図 19 (A) は上面図であり、図 19 (A) に示す一点鎖線 A1 - A2 方向の断面が図 19 (B) に相当する。また、図 19 (A) に示す一点鎖線 A3 - A4 方向の断面が図 19 (C) に相当する。

#### 【0144】

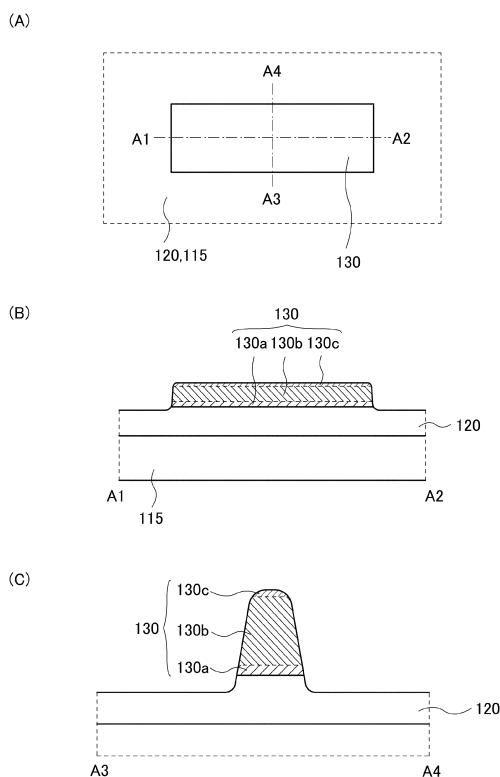

また、図 20 (A)、(B)、(C) は、三層構造である酸化物半導体層 130 の上面図および断面図である。図 20 (A) は上面図であり、図 20 (A) に示す一点鎖線 A1 - A2 方向の断面が図 20 (B) に相当する。また、図 20 (A) に示す一点鎖線 A3 - A4 方向の断面が図 20 (C) に相当する。

#### 【0145】

酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c には、それぞれ組成の異なる酸化物半導体層などを用いることができる。

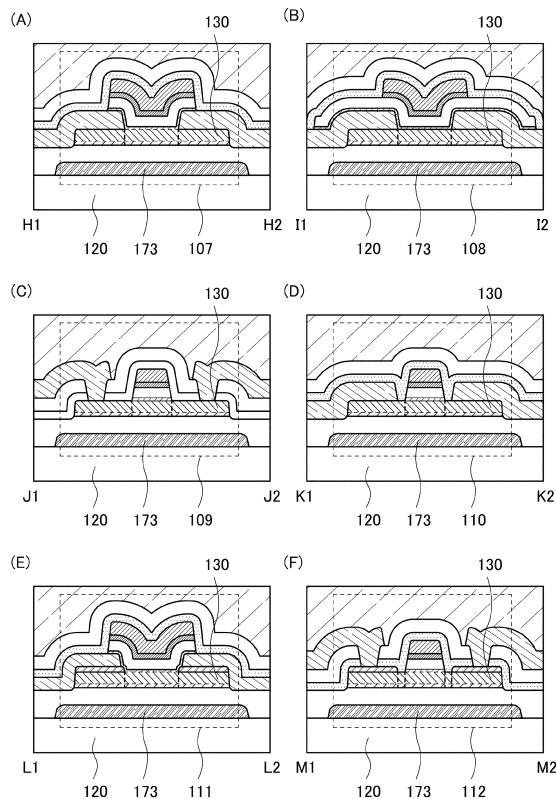

#### 【0146】

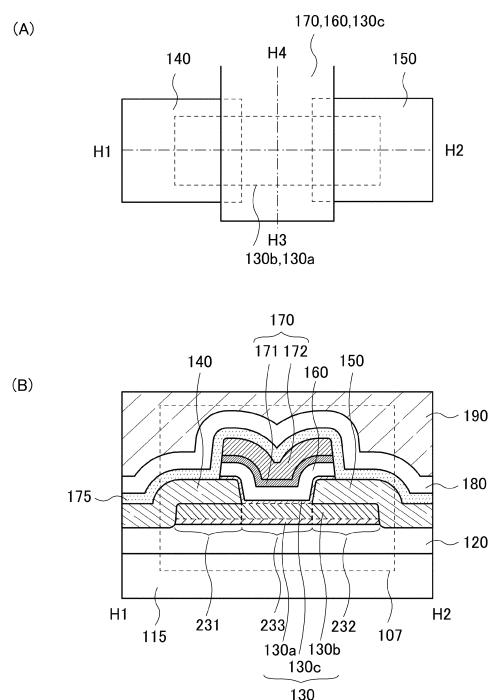

また、本発明の一態様のトランジスタは、図 21 (A)、(B) に示す構成であってよい。図 21 (A) はトランジスタ 107 の上面図であり、図 21 (A) に示す一点鎖線 H1 - H2 方向の断面が図 21 (B) に相当する。また、図 21 (A) に示す一点鎖線 H3 - H4 方向の断面が図 27 (A) に相当する。また、一点鎖線 H1 - H2 方向をチャネル長方向、一点鎖線 H3 - H4 方向をチャネル幅方向と呼称する場合がある。

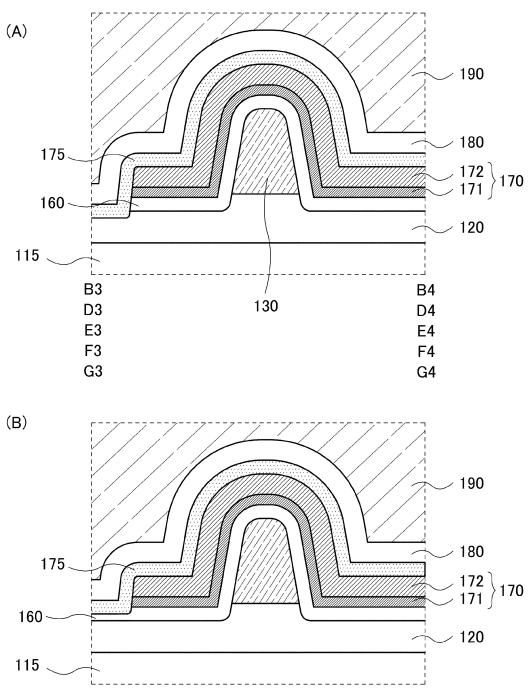

#### 【0147】

トランジスタ 107 は、基板 115 と接する絶縁層 120 と、絶縁層 120 と接する酸化物半導体層 130a および酸化物半導体層 130b からなる積層と、当該積層と電気的に接続する導電層 140 および導電層 150 と、当該積層、導電層 140 および導電層 150 と接する酸化物半導体層 130c と、酸化物半導体層 130c と接する絶縁層 160 と、絶縁層 160 と接する導電層 170 と、導電層 140、導電層 150、酸化物半導体層 130c、絶縁層 160 および導電層 170 と接する絶縁層 175 と、絶縁層 175 と接する絶縁層 180 と、を有する。また、必要に応じて絶縁層 180 に接する絶縁層 190 (平坦化膜) などを有していてよい。

#### 【0148】

トランジスタ 107 は、領域 231 および領域 232 において酸化物半導体層 130 が二層 (酸化物半導体層 130a、酸化物半導体層 130b) である点、領域 233 において酸化物半導体層 130 が三層 (酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c) である点、および導電層 140 および導電層 150 と絶縁層 160 との間に酸化物半導体層の一部 (酸化物半導体層 130c) が介在している点を除き、トランジスタ 101 と同様の構成を有する。

#### 【0149】

また、本発明の一態様のトランジスタは、図 22 (A)、(B) に示す構成であってよい。図 22 (A) はトランジスタ 108 の上面図であり、図 22 (A) に示す一点鎖線 I1 - I2 方向の断面が図 22 (B) に相当する。また、図 22 (A) に示す一点鎖線 I3 - I4 方向の断面が図 27 (B) に相当する。また、一点鎖線 I1 - I2 方向をチャネル長方向、一点鎖線 I3 - I4 方向をチャネル幅方向と呼称する場合がある。

#### 【0150】

10

20

30

40

50

トランジスタ108は、領域231および領域232において酸化物半導体層130が二層（酸化物半導体層130a、酸化物半導体層130b）である点、領域233において酸化物半導体層130が三層（酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c）である点、および導電層140および導電層150と絶縁層160との間に酸化物半導体層の一部（酸化物半導体層130c）が介在している点を除き、トランジスタ102と同様の構成を有する。

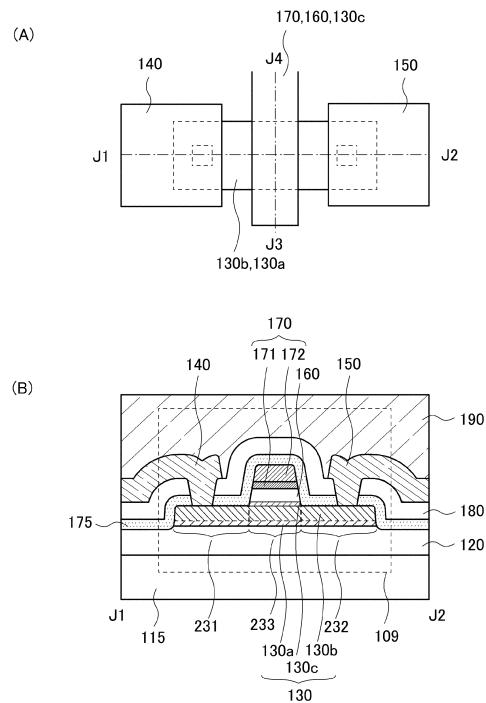

#### 【0151】

また、本発明の一態様のトランジスタは、図23(A)、(B)に示す構成であってもよい。図23(A)はトランジスタ109の上面図であり、図23(A)に示す一点鎖線J1-J2方向の断面が図23(B)に相当する。また、図23(A)に示す一点鎖線J3-J4方向の断面が図27(A)に相当する。また、一点鎖線J1-J2方向をチャネル長方向、一点鎖線J3-J4方向をチャネル幅方向と呼称する場合がある。

10

#### 【0152】

トランジスタ109は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130aおよび酸化物半導体層130bからなる積層と、当該積層と接する酸化物半導体層130cと、酸化物半導体層130cと接する絶縁層160と、絶縁層160と接する導電層170と、当該積層、酸化物半導体層130c、絶縁層160および導電層170を覆う絶縁層175と、絶縁層175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて当該積層と電気的に接続する導電層140および導電層150を有する。また、必要に応じて絶縁層180、導電層140および導電層150に接する絶縁層190（平坦化膜）などを有していてもよい。

20

#### 【0153】

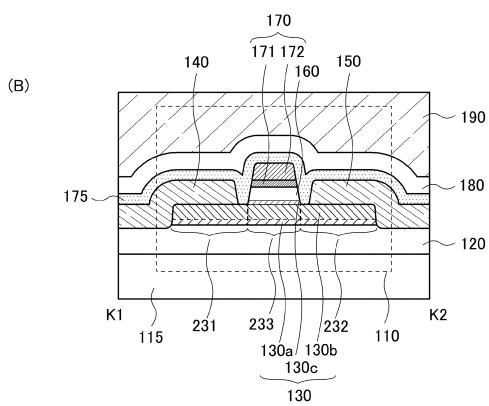

トランジスタ109は、領域231および領域232において酸化物半導体層130が二層（酸化物半導体層130a、酸化物半導体層130b）である点、領域233において酸化物半導体層130が三層（酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c）である点を除き、トランジスタ103と同様の構成を有する。

#### 【0154】

また、本発明の一態様のトランジスタは、図24(A)、(B)に示す構成であってもよい。図24(A)はトランジスタ110の上面図であり、図24(A)に示す一点鎖線K1-K2方向の断面が図24(B)に相当する。また、図24(A)に示す一点鎖線K3-K4方向の断面が図27(A)に相当する。また、一点鎖線K1-K2方向をチャネル長方向、一点鎖線K3-K4方向をチャネル幅方向と呼称する場合がある。

30

#### 【0155】

トランジスタ110は、領域231および領域232において酸化物半導体層130が二層（酸化物半導体層130a、酸化物半導体層130b）である点、領域233において酸化物半導体層130が三層（酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c）である点を除き、トランジスタ104と同様の構成を有する。

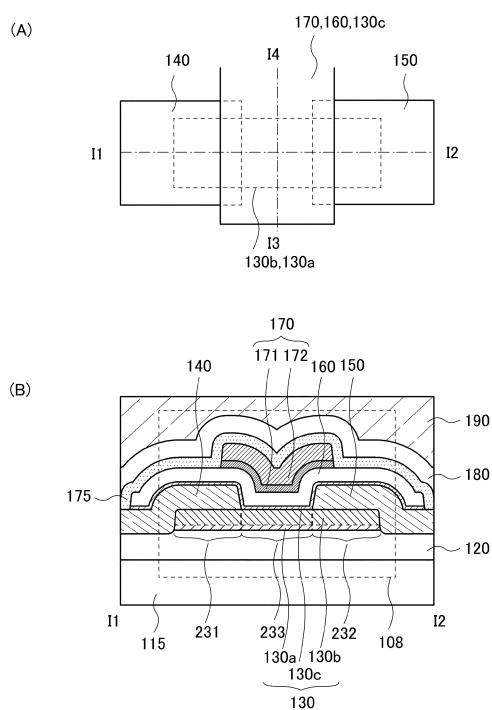

#### 【0156】

また、本発明の一態様のトランジスタは、図25(A)、(B)に示す構成であってもよい。図25(A)はトランジスタ111の上面図であり、図25(A)に示す一点鎖線L1-L2方向の断面が図25(B)に相当する。また、図25(A)に示す一点鎖線L3-L4方向の断面が図27(A)に相当する。また、一点鎖線L1-L2方向をチャネル長方向、一点鎖線L3-L4方向をチャネル幅方向と呼称する場合がある。

40

#### 【0157】

トランジスタ111は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130aおよび酸化物半導体層130bからなる積層と、当該積層と電気的に接続する導電層141および導電層151と、当該積層、導電層141および導電層151と接する酸化物半導体層130cと、酸化物半導体層130cと接する絶縁層160と、絶縁層160と接する導電層170と、当該積層、導電層141、導電層151、酸化物半導体層130c、絶縁層160および導電層170と接する絶縁層175と、絶縁層

50

175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する。また、必要に応じて絶縁層180、導電層142および導電層152に接する絶縁層190(平坦化膜)などを有していてもよい。

#### 【0158】

トランジスタ111は、領域231および領域232において酸化物半導体層130が二層(酸化物半導体層130a、酸化物半導体層130b)である点、領域233において酸化物半導体層130が三層(酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c)である点、および導電層141および導電層151と絶縁層160との間に酸化物半導体層の一部(酸化物半導体層130c)が介在している点を除き、トランジスタ105と同様の構成を有する。10

#### 【0159】

また、本発明の一態様のトランジスタは、図26(A)、(B)に示す構成であってよい。図26(A)はトランジスタ112の上面図であり、図26(A)に示す一点鎖線M1-M2方向の断面が図26(B)に相当する。また、図26(A)に示す一点鎖線M3-M4方向の断面が図27(A)に相当する。また、一点鎖線M1-M2方向をチャネル長方向、一点鎖線M3-M4方向をチャネル幅方向と呼称する場合がある。

#### 【0160】

トランジスタ112は、領域331、領域332、領域334および領域335において酸化物半導体層130が二層(酸化物半導体層130a、酸化物半導体層130b)である点、領域333において酸化物半導体層130が三層(酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c)である点を除き、トランジスタ106と同様の構成を有する。20

#### 【0161】

また、本発明の一態様のトランジスタは、図28(A)、(B)、(C)、(D)、(E)、(F)に示すチャネル長方向の断面図、ならびに図29(A)、(B)に示すチャネル幅方向の断面図のように、酸化物半導体層130と基板115との間に導電層173を備えていてよい。当該導電層を第2のゲート電極層(バックゲート)として用いることで、オン電流の増加や、しきい値電圧の制御を行うことができる。なお、図28(A)、(B)、(C)、(D)、(E)、(F)に示す断面図において、導電層173の幅を酸化物半導体層130よりも短くしてもよい。さらに、導電層173の幅を導電層170の幅よりも短くしてもよい。30

#### 【0162】

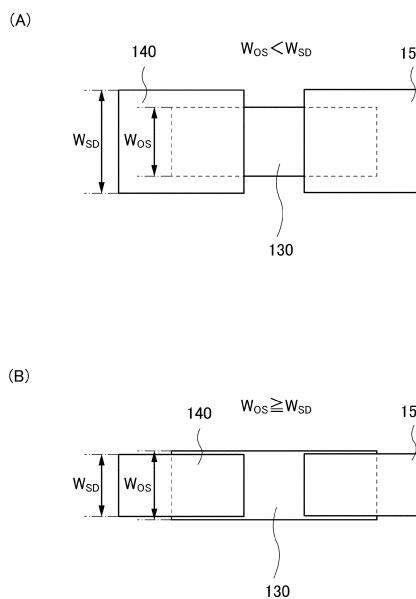

また、本発明の一態様のトランジスタにおける導電層140(ソース電極層)および導電層150(ドレイン電極層)は、図30(A)、(B)に示す上面図(酸化物半導体層130、導電層140および導電層150のみを図示)のように酸化物半導体層130の幅( $W_{o,s}$ )よりも導電層140および導電層150の幅( $W_{s,d}$ )が長く形成されていてよいし、短く形成されていてよい。 $W_{o,s} > W_{s,d}$ ( $W_{s,d}$ は $W_{o,s}$ 以下)とすることで、ゲート電界が酸化物半導体層130全体にかかりやすくなり、トランジスタの電気特性を向上させることができる。40

#### 【0163】

本発明の一態様のトランジスタ(トランジスタ101乃至トランジスタ112)では、いずれの構成においても、ゲート電極層である導電層170は、ゲート絶縁膜である絶縁層160を介して酸化物半導体層130のチャネル幅方向を電気的に取り囲み、オン電流が高められる。このようなトランジスタの構造を、surrounded channel(s-channel)構造とよぶ。

#### 【0164】

また、酸化物半導体層130aおよび酸化物半導体層130bを有するトランジスタ、ならびに酸化物半導体層130a、酸化物半導体層130bおよび酸化物半導体層130cを有するトランジスタにおいては、酸化物半導体層130を構成する二層または三層の材50

料を適切に選択することで酸化物半導体層 130b に電流を流すことができる。酸化物半導体層 130b に電流が流れることで、界面散乱の影響を受けにくく、高いオン電流を得ることができる。なお、酸化物半導体層 130b を厚くすると、オン電流を向上させることができる。例えば、酸化物半導体層 130b の膜厚を 100 nm 乃至 200 nm としてもよい。

#### 【0165】

以上の構成のトランジスタを用いることにより、半導体装置に良好な電気特性を付与することができる。

#### 【0166】

なお、本明細書において、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレイン領域またはドレイン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

10

#### 【0167】

また、チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

20

#### 【0168】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（以下、実効的なチャネル幅と呼ぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅と呼ぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の上面に形成されるチャネル領域の割合に対して、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。

30

#### 【0169】

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためにには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

40

#### 【0170】

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅（SCW：Surrounded Channel Width）」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面 TEM 像などを取得して、その画像を解析することなどによって、値を決定することができる。

50

**【 0 1 7 1 】**

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

**【 0 1 7 2 】**

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

**【 0 1 7 3 】****( 実施の形態 3 )**

本実施の形態では、実施の形態 2 に示したトランジスタの構成要素について詳細を説明する。

10

**【 0 1 7 4 】**

基板 115 は、図 1 ( A ) におけるシリコン基板 40 、絶縁層 81 、絶縁層 82 および絶縁層 83 を含む構成に相当する。なお、シリコン基板には p - c h 型のトランジスタのみを形成するため、 n - 型の導電型を有するシリコン基板を用いることが好ましい。または、 n - 型または i 型のシリコン層を有する S O I 基板であってもよい。また、当該シリコン基板におけるトランジスタを形成する面の面方位は、 ( 110 ) 面であることが好ましい。表面に ( 110 ) 面を有するシリコン基板に p - c h 型トランジスタを形成することで、移動度を高くすることができる。

**【 0 1 7 5 】**

20

絶縁層 120 は図 1 ( A ) における絶縁層 84 に相当する。絶縁層 120 は、基板 115 からの不純物の拡散を防止する役割を有するほか、酸化物半導体層 130 に酸素を供給する役割を担うことができる。したがって、絶縁層 120 は酸素を含む絶縁膜であることが好ましく、化学量論組成よりも多い酸素を含む絶縁膜であることがより好ましい。例えば、昇温脱離ガス分析法 ( T D S ( Thermal Desorption Spectroscopy ) ) にて、酸素原子に換算しての酸素の放出量が  $1.0 \times 10^{19}$  atom s / cm<sup>3</sup> 以上である膜とする。なお、上記 T D S 分析時における膜の表面温度としては 100 以上 700 以下、または 100 以上 500 以下の範囲が好ましい。また、上述のように基板 115 が他のデバイスが形成された基板である場合、絶縁層 120 は、層間絶縁膜としての機能も有する。その場合は、表面が平坦になるように C M P ( Chemical Mechanical Mechanical Polishing ) 法等で平坦化処理を行うことが好ましい。

30

**【 0 1 7 6 】**

例えば、絶縁層 120 には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、またはこれらの混合材料を用いることができる。また、上記材料の積層であつてもよい。

**【 0 1 7 7 】**

40

なお、本実施の形態では、トランジスタが有する酸化物半導体層 130 が酸化物半導体層 130a 、酸化物半導体層 130b および酸化物半導体層 130c を絶縁層 120 側から順に積んだ三層構造である場合を主として詳細を説明する。

**【 0 1 7 8 】**

なお、酸化物半導体層 130 が单層の場合は、上記酸化物半導体層 130b に相当する層を用いればよい。

**【 0 1 7 9 】**

また、酸化物半導体層 130 が二層の場合は、酸化物半導体層 130a に相当する層および酸化物半導体層 130b に相当する層を絶縁層 120 側から順に積んだ積層を用いればよい。この構成の場合、酸化物半導体層 130a と酸化物半導体層 130b とを入れ替え

50

ることもできる。

**【0180】**

また、酸化物半導体層130が四層以上である場合は、例えば、本実施の形態で説明する三層構造の酸化物半導体層130に対して他の酸化物半導体層を積む構成や当該三層構造におけるいずれかの界面に他の酸化物半導体層を挿入する構成とすることができる。

**【0181】**

一例としては、酸化物半導体層130bには、酸化物半導体層130aおよび酸化物半導体層130cよりも電子親和力（真空準位から伝導帯下端までのエネルギー）が大きい酸化物半導体を用いる。電子親和力は、真空準位と価電子帶上端とのエネルギー差（イオン化ポテンシャル）から、伝導帯下端と価電子帶上端とのエネルギー差（エネルギーギャップ）を差し引いた値として求めることができる。10

**【0182】**

酸化物半導体層130aおよび酸化物半導体層130cは、酸化物半導体層130bを構成する金属元素を一種以上含み、例えば、伝導帯下端のエネルギーが酸化物半導体層130bよりも、0.05eV、0.07eV、0.1eV、0.15eVのいずれか以上であって、2eV、1eV、0.5eV、0.4eVのいずれか以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。

**【0183】**

このような構造において、導電層170に電界を印加すると、酸化物半導体層130のうち、伝導帯下端のエネルギーが最も小さい酸化物半導体層130bにチャネルが形成される。20

**【0184】**

また、酸化物半導体層130aは、酸化物半導体層130bを構成する金属元素を一種以上含んで構成されるため、酸化物半導体層130bと絶縁層120が接した場合の界面と比較して、酸化物半導体層130bと酸化物半導体層130aとの界面には界面準位が形成されにくくなる。該界面準位はチャネルを形成することができるため、トランジスタのしきい値電圧が変動することができる。したがって、酸化物半導体層130aを設けることにより、トランジスタのしきい値電圧などの電気特性のばらつきを低減することができる。また、当該トランジスタの信頼性を向上させることができる。

**【0185】**

また、酸化物半導体層130cは、酸化物半導体層130bを構成する金属元素を一種以上含んで構成されるため、酸化物半導体層130bとゲート絶縁膜（絶縁層160）が接した場合の界面と比較して、酸化物半導体層130bと酸化物半導体層130cとの界面ではキャリアの散乱が起こりにくくなる。したがって、酸化物半導体層130cを設けることにより、トランジスタの電界効果移動度を高くすることができます。30

**【0186】**

酸化物半導体層130aおよび酸化物半導体層130cには、例えば、Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHfを酸化物半導体層130bよりも高い原子数比で含む材料を用いることができる。具体的には、当該原子数比を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。前述の元素は酸素と強く結合するため、酸素欠損が酸化物半導体層に生じることを抑制する機能を有する。すなわち、酸化物半導体層130aおよび酸化物半導体層130cは、酸化物半導体層130bよりも酸素欠損が生じにくいということができる。40

**【0187】**

また、酸化物半導体層130a、酸化物半導体層130b、および酸化物半導体層130cとして用いることのできる酸化物半導体は、少なくともインジウム（In）もしくは亜鉛（Zn）を含むことが好ましい。または、InとZnの双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

**【0188】**

10

20

30

40

50

スタビライザーとしては、ガリウム (Ga)、スズ (Sn)、ハフニウム (Hf)、アルミニウム (Al)、またはジルコニウム (Zr) 等がある。また、他のスタビライザーとしては、ランタノイドである、ランタン (La)、セリウム (Ce)、プラセオジム (Pr)、ネオジム (Nd)、サマリウム (Sm)、ユウロピウム (Eu)、ガドリニウム (Gd)、テルビウム (Tb)、ジスプロシウム (Dy)、ホルミウム (Ho)、エルビウム (Er)、ツリウム (Tm)、イッテルビウム (Yb)、ルテチウム (Lu) 等がある。

#### 【0189】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化ガリウム、酸化亜鉛、In-Zn酸化物、Sn-Zn酸化物、Al-Zn酸化物、Zn-Mg酸化物、Sn-Mg酸化物、In-Mg酸化物、In-Ga酸化物、In-Ga-Zn酸化物、In-Al-Zn酸化物、In-Sn-Zn酸化物、Sn-Ga-Zn酸化物、Al-Ga-Zn酸化物、Sn-Al-Zn酸化物、In-Hf-Zn酸化物、In-La-Zn酸化物、In-Ce-Zn酸化物、In-Pr-Zn酸化物、In-Nd-Zn酸化物、In-Sm-Zn酸化物、In-Eu-Zn酸化物、In-Gd-Zn酸化物、In-Tb-Zn酸化物、In-Dy-Zn酸化物、In-Ho-Zn酸化物、In-Er-Zn酸化物、In-Tm-Zn酸化物、In-Yb-Zn酸化物、In-Lu-Zn酸化物、In-Sn-Ga-Zn酸化物、In-Hf-Ga-Zn酸化物、In-Al-Ga-Zn酸化物、In-Sn-Al-Zn酸化物、In-Sn-Hf-Zn酸化物、In-Hf-Al-Zn酸化物を用いることができる。

#### 【0190】

なお、ここで、例えば、In-Ga-Zn酸化物とは、InとGaとZnを主成分として有する酸化物という意味である。また、InとGaとZn以外の金属元素が入っていてもよい。また、本明細書においては、In-Ga-Zn酸化物で構成した膜をIGZO膜とも呼ぶ。

#### 【0191】

また、 $InMO_3 (ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Y、Zr、La、Ce、またはNdから選ばれた一つの金属元素または複数の金属元素を示す。また、 $In_2SnO_5 (ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数) で表記される材料を用いてもよい。

#### 【0192】

なお、酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130cが、少なくともインジウム、亜鉛およびM (Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属) を含むIn-M-Zn酸化物であるとき、酸化物半導体層130aを $In : M : Zn = x_1 : y_1 : z_1$  [原子数比]、酸化物半導体層130bを $In : M : Zn = x_2 : y_2 : z_2$  [原子数比]、酸化物半導体層130cを $In : M : Zn = x_3 : y_3 : z_3$  [原子数比] とすると、 $y_1 / x_1$  および  $y_3 / x_3$  が  $y_2 / x_2$  よりも大きくなることが好ましい。 $y_1 / x_1$  および  $y_3 / x_3$  は  $y_2 / x_2$  よりも1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。このとき、酸化物半導体層130bにおいて、 $y_2$  が  $x_2$  以上であるとトランジスタの電気特性を安定させることができる。ただし、 $y_2$  が  $x_2$  の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_2$  は  $x_2$  の3倍未満であることが好ましい。

#### 【0193】

酸化物半導体層130aおよび酸化物半導体層130cにおけるZnおよびOを除いた場合において、InおよびMの原子数比率は、好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが75atomic%以上とする。また、酸化物半導体層130bのZnおよびOを除いてのInおよびMの原子数比率は、好ましくはInが25atomic%以上、Mが75atomic%未満、さらに好ましくはInが34atomic%以上、Mが66atomic%未満とする。

10

20

30

40

50

## 【0194】

また、酸化物半導体層130bは、酸化物半導体層130aおよび酸化物半導体層130cよりもインジウムの含有量を多くするとよい。酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることにより、より多くのs軌道が重なるため、InがMよりも多い組成となる酸化物はInがMと同等または少ない組成となる酸化物と比較して移動度が高くなる。そのため、酸化物半導体層130bにインジウムの含有量が多い酸化物を用いることで、高い電界効果移動度のトランジスタを実現することができる。

## 【0195】

酸化物半導体層130aの厚さは、3nm以上100nm以下、好ましくは5nm以上50nm以下、さらに好ましくは5nm以上25nm以下とする。また、酸化物半導体層130bの厚さは、3nm以上200nm以下、好ましくは10nm以上150nm以下、さらに好ましくは15nm以上100nm以下とする。また、酸化物半導体層130cの厚さは、1nm以上50nm以下、好ましくは2nm以上30nm以下、さらに好ましくは3nm以上15nm以下とする。また、酸化物半導体層130bは、酸化物半導体層130aおよび酸化物半導体層130cより厚い方が好ましい。

## 【0196】

なお、酸化物半導体層をチャネルとするトランジスタに安定した電気特性を付与するためには、酸化物半導体層中の不純物濃度を低減し、酸化物半導体層を真性(i型)または実質的に真性にすることが有効である。ここで、実質的に真性とは、酸化物半導体層のキャリア密度が、 $1 \times 10^{17} / \text{cm}^3$ 未満であること、好ましくは $1 \times 10^{15} / \text{cm}^3$ 未満であること、さらに好ましくは $1 \times 10^{13} / \text{cm}^3$ 未満であることを指す。

## 【0197】

また、酸化物半導体層において、水素、窒素、炭素、シリコン、および主成分以外の金属元素は不純物となる。例えば、水素および窒素はドナー準位の形成に寄与し、キャリア密度を増大させてしまう。また、シリコンは酸化物半導体層中で不純物準位の形成に寄与する。当該不純物準位はトラップとなり、トランジスタの電気特性を劣化させることがある。したがって、酸化物半導体層130a、酸化物半導体層130bおよび酸化物半導体層130cの層中や、それぞれの界面において不純物濃度を低減させることが好ましい。

## 【0198】

酸化物半導体層を真性または実質的に真性とするためにには、SIMS(Secondary Ion Mass Spectrometry)分析において、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 未満とする。また、水素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $2 \times 10^{20} \text{ atoms/cm}^3$ 以下、好ましくは $5 \times 10^{19} \text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{19} \text{ atoms/cm}^3$ 以下、さらに好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 以下とする。また、窒素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $5 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 以下、さらに好ましくは $5 \times 10^{17} \text{ atoms/cm}^3$ 以下とする。

## 【0199】

また、酸化物半導体層が結晶を含む場合、シリコンや炭素が高濃度で含まれると、酸化物半導体層の結晶性を低下させことがある。酸化物半導体層の結晶性を低下させないためには、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 未満とする部分を有していればよい。また、例えば、酸化物半導体層のある深さにおいて、または

10

20

30

40

50

、酸化物半導体層のある領域において、炭素濃度を  $1 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、好ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 未満、さらに好ましくは  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 未満とする部分を有していればよい。

#### 【0200】

また、上述のように高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタのオフ電流は極めて小さい。例えば、ソースとドレインとの間の電圧を 0.1 V、5 V、または、10 V 程度とした場合に、トランジスタのチャネル幅で規格化したオフ電流を数 y A / μm 乃至数 z A / μm にまで低減することが可能となる。

#### 【0201】

なお、トランジスタのゲート絶縁膜としては、シリコンを含む絶縁膜が多く用いられるため、上記理由により酸化物半導体層のチャネルとなる領域は、本発明の一態様のトランジスタのようにゲート絶縁膜と接しない構造が好ましいということができる。また、ゲート絶縁膜と酸化物半導体層との界面にチャネルが形成される場合、該界面でキャリアの散乱が起り、トランジスタの電界効果移動度が低くなることがある。このような観点からも、酸化物半導体層のチャネルとなる領域はゲート絶縁膜から離すことが好ましいといえる。

#### 【0202】

したがって、酸化物半導体層 130 を酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c の積層構造とすることで、酸化物半導体層 130b にチャネルを形成することができ、高い電界効果移動度および安定した電気特性を有したトランジスタを形成することができる。

#### 【0203】

酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c のバンド構造においては、伝導帯下端のエネルギーが連続的に変化する。これは、酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c の組成が近似することにより、酸素が相互に拡散しやすい点からも理解される。したがって、酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c は組成が異なる層の積層体ではあるが、物性的に連続であるということもでき、図面において、当該積層体のそれぞれの界面は点線で表している。

#### 【0204】

主成分を共通として積層された酸化物半導体層 130 は、各層を単に積層するのではなく連続接合（ここでは特に伝導帯下端のエネルギーが各層の間で連続的に変化する U 字型の井戸構造（U Shape Well））が形成されるように作製する。すなわち、各層の界面にトラップ中心や再結合中心のような欠陥準位を形成するような不純物が存在しないように積層構造を形成する。仮に、積層された酸化物半導体層の層間に不純物が混在していると、エネルギー・バンドの連続性が失われ、界面でキャリアがトラップあるいは再結合により消滅してしまう。

#### 【0205】

例えば、酸化物半導体層 130a および酸化物半導体層 130c には In : Ga : Zn = 1 : 3 : 2、1 : 3 : 3、1 : 3 : 4、1 : 3 : 6、1 : 4 : 5、1 : 6 : 4 または 1 : 9 : 6（原子数比）、酸化物半導体層 130b には In : Ga : Zn = 1 : 1 : 1、2 : 1 : 3、5 : 5 : 6、3 : 1 : 2、または 4 : 2 : 4 : 1（原子数比）などの In - Ga - Zn 酸化物などを用いることができる。なお、酸化物半導体層 130a、酸化物半導体層 130b、および酸化物半導体層 130c の原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス 40 % の変動を含む。

#### 【0206】

酸化物半導体層 130 における酸化物半導体層 130b はウェル（井戸）となり、酸化物半導体層 130 を用いたトランジスタにおいて、チャネルは酸化物半導体層 130b に形成される。なお、酸化物半導体層 130 は伝導帯下端のエネルギーが連続的に変化しているため、U 字型井戸とも呼ぶことができる。また、このような構成で形成されたチャネル

10

20

30

40

50

を埋め込みチャネルということもできる。

**【0207】**

また、酸化物半導体層130aおよび酸化物半導体層130cと、酸化シリコン膜などの絶縁層との界面近傍には、不純物や欠陥に起因したトラップ準位が形成され得る。酸化物半導体層130aおよび酸化物半導体層130cがあることにより、酸化物半導体層130bと当該トラップ準位とを遠ざけることができる。

**【0208】**

ただし、酸化物半導体層130aおよび酸化物半導体層130cの伝導帯下端のエネルギーと、酸化物半導体層130bの伝導帯下端のエネルギーとの差が小さい場合、酸化物半導体層130bの電子が該エネルギー差を越えてトラップ準位に達することができる。電子がトラップ準位に捕獲されることで、絶縁層界面にマイナスの電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。10

**【0209】**

したがって、トランジスタのしきい値電圧の変動を低減するには、酸化物半導体層130aおよび酸化物半導体層130cの伝導帯下端のエネルギーと、酸化物半導体層130bの伝導帯下端のエネルギーとの間に一定以上の差を設けることが必要となる。それぞれの当該エネルギー差は、0.1eV以上が好ましく、0.15eV以上がより好ましい。

**【0210】**

酸化物半導体層130a、酸化物半導体層130bおよび酸化物半導体層130cには、結晶部が含まれることが好ましい。特にc軸に配向した結晶を用いることでトランジスタに安定した電気特性を付与することができる。また、c軸に配向した結晶は歪曲に強く、フレキシブル基板を用いた半導体装置の信頼性を向上させることができる。20

**【0211】**

ソース電極層として作用する導電層140およびドレイン電極層として作用する導電層150には、例えば、Al、Cr、Cu、Ta、Ti、Mo、W、Ni、Mn、Nd、Sc、および当該金属材料の合金から選ばれた材料の単層、または積層を用いることができる。代表的には、特に酸素と結合しやすいTiや、後のプロセス温度が比較的高くできることなどから、融点の高いWを用いることがより好ましい。また、低抵抗のCuやCu-Mnなどの合金と上記材料との積層を用いてもよい。なお、トランジスタ105、トランジスタ106、トランジスタ111、トランジスタ112においては、例えば、導電層141および導電層151にW、導電層142および導電層152にTiとAlとの積層膜などを用いることができる。30

**【0212】**

上記材料は酸化物半導体膜から酸素を引き抜く性質を有する。そのため、上記材料と接した酸化物半導体層の一部の領域では酸化物半導体層中の酸素が脱離し、酸素欠損が形成される。膜中に僅かに含まれる水素と当該酸素欠損が結合することにより当該領域は顕著にn型化する。したがって、n型化した当該領域はトランジスタのソースまたはドレインとして作用させることができる。

**【0213】**

また、導電層140および導電層150にWを用いる場合には、窒素をドーピングしてもよい。窒素をドーピングすることで酸素を引き抜く性質を適度に弱めることができ、n型化した領域がチャネル領域まで拡大することを防ぐことができる。また、上記の導電層をn型の半導体層との積層とし、n型の半導体層と酸化物半導体層を接触させることによってもn型化した領域がチャネル領域まで拡大することを防ぐことができる。n型の半導体層としては、窒素が添加されたIn-Ga-Zn酸化物、酸化亜鉛、酸化インジウム、酸化スズ、酸化インジウムスズなどを用いることができる。40

**【0214】**

ゲート絶縁膜として作用する絶縁層160には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、50

酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、絶縁層160は上記材料の積層であってもよい。なお、絶縁層160に、ランタン(La)、窒素、ジルコニウム(Zr)などを、不純物として含んでいてもよい。

#### 【0215】

また、絶縁層160の積層構造の一例について説明する。絶縁層160は、例えば、酸素、窒素、シリコン、ハフニウムなどを有する。具体的には、酸化ハフニウム、および酸化シリコンまたは酸化窒化シリコンを含むと好ましい。

#### 【0216】

酸化ハフニウムおよび酸化アルミニウムは、酸化シリコンや酸化窒化シリコンと比べて比誘電率が高い。したがって、等価酸化膜厚に対して物理的な膜厚を大きくできるため、等価酸化膜厚を10nm以下または5nm以下とした場合でも、トンネル電流によるリーク電流を小さくすることができる。即ち、オフ電流の小さいトランジスタを実現することができる。さらに、結晶構造を有する酸化ハフニウムは、非晶質構造を有する酸化ハフニウムと比べて高い比誘電率を備える。したがって、オフ電流の小さいトランジスタとするためには、結晶構造を有する酸化ハフニウムを用いることが好ましい。結晶構造の例としては、単斜晶系や立方晶系などが挙げられる。ただし、本発明の一態様は、これらに限定されない。

10

#### 【0217】

また、酸化物半導体層130と接する絶縁層120および絶縁層160は、窒素酸化物の放出量の少ない膜を用いることが好ましい。窒素酸化物の放出量の多い絶縁層と酸化物半導体が接した場合、酸化物半導体のエネルギーギャップ内における窒素酸化物の準位密度が高くなることがある。絶縁層120および絶縁層160には、例えば、窒素酸化物の放出量の少ない酸化窒化シリコン膜または酸化窒化アルミニウム膜等の酸化物絶縁層を用いることができる。

20

#### 【0218】

なお、窒素酸化物の放出量の少ない酸化窒化シリコン膜は、TDSにおいて、窒素酸化物の放出量よりアンモニアの放出量が多い膜であり、代表的にはアンモニアの放出量が $1 \times 10^{18}$ 個/cm<sup>3</sup>以上 $5 \times 10^{19}$ 個/cm<sup>3</sup>以下である。なお、上記TDS分析時ににおける膜の表面温度としては50以上650以下、または50以上550以下の範囲が好ましい。

30

#### 【0219】

絶縁層120および絶縁層160として、上記酸化物絶縁層を用いることで、トランジスタのしきい値電圧のシフトを低減することが可能であり、トランジスタの電気特性の変動を低減することができる。

#### 【0220】

ゲート電極層として作用する導電層170には、例えば、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Mn、Nd、Sc、TaおよびWなどの導電膜を用いることができる。また、上記材料の合金や上記材料の導電性窒化物を用いてもよい。また、上記材料、上記材料の合金、および上記材料の導電性窒化物から選ばれた複数の材料の積層であってもよい。代表的には、タングステン、タングステンと窒化チタンの積層、タングステンと窒化タンタルの積層などを用いることができる。また、低抵抗のCuまたはCu-Mnなどの合金や上記材料とCuまたはCu-Mnなどの合金との積層を用いてもよい。本実施の形態では、導電層171に窒化タンタル、導電層172にタングステンを用いて導電層170を形成する。

40

#### 【0221】

絶縁層175には、水素を含む窒化シリコン膜または窒化アルミニウム膜などを用いることができる。実施の形態2に示したトランジスタ103、トランジスタ104、トランジスタ106、トランジスタ109、トランジスタ110、およびトランジスタ112では、絶縁層175として水素を含む絶縁膜を用いることで酸化物半導体層の一部をn型化することができる。また、窒化絶縁膜は水分などのプロッキング膜としての作用も有し、ト

50

ランジスタの信頼性を向上させることができる。

【0222】

また、絶縁層175としては酸化アルミニウム膜を用いることもできる。特に、実施の形態2に示したトランジスタ101、トランジスタ102、トランジスタ105、トランジスタ107、トランジスタ108、およびトランジスタ111では絶縁層175に酸化アルミニウム膜を用いることが好ましい。酸化アルミニウム膜は、水素、水分などの不純物、および酸素の両方に対して膜を透過させない遮断効果が高い。したがって、酸化アルミニウム膜は、トランジスタの作製工程中および作製後において、トランジスタの電気特性の変動要因となる水素、水分などの不純物の酸化物半導体層130への混入防止、酸化物半導体層130を構成する主成分材料である酸素の酸化物半導体層からの放出防止、絶縁層120からの酸素の不必要的放出防止の効果を有する保護膜として用いることに適している。また、酸化アルミニウム膜に含まれる酸素を酸化物半導体層中に拡散させることもできる。

10

【0223】

また、絶縁層175上には絶縁層180が形成されていることが好ましい。当該絶縁層には、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、当該絶縁層は上記材料の積層であってもよい。

【0224】

ここで、絶縁層180は絶縁層120と同様に化学量論組成よりも多くの酸素を有することが好ましい。絶縁層180から放出される酸素は絶縁層160を経由して酸化物半導体層130のチャネル形成領域に拡散させることができることから、チャネル形成領域に形成された酸素欠損に酸素を補填することができる。したがって、安定したトランジスタの電気特性を得ることができる。

20

【0225】

半導体装置を高集積化するにはトランジスタの微細化が必須である。一方、トランジスタの微細化によりトランジスタの電気特性が悪化することが知られており、チャネル幅が縮小するとオン電流は低下する。

【0226】

本発明の一態様のトランジスタ107乃至トランジスタ112では、チャネルが形成される酸化物半導体層130bを覆うように酸化物半導体層130cが形成されており、チャネル形成層とゲート絶縁膜が接しない構成となっている。そのため、チャネル形成層とゲート絶縁膜との界面で生じるキャリアの散乱を抑えることができ、トランジスタのオン電流を大きくすることができます。

30

【0227】

また、本発明の一態様のトランジスタでは、前述したように酸化物半導体層130のチャネル幅方向を電気的に取り囲むようにゲート電極層（導電層170）が形成されているため、酸化物半導体層130に対しては垂直方向からのゲート電界に加えて、側面方向からのゲート電界が印加される。すなわち、チャネル形成層に対して全体的にゲート電界が印加されることになり実効チャネル幅が拡大するため、さらにオン電流を高められる。

40

【0228】

また、本発明の一態様における酸化物半導体層130が二層または三層のトランジスタでは、チャネルが形成される酸化物半導体層130bを酸化物半導体層130a上に形成することで界面準位を形成しにくくする効果を有する。また、本発明の一態様における酸化物半導体層130が三層のトランジスタでは、酸化物半導体層130bを三層構造の中間に位置する層とすることで上下からの不純物混入の影響を排除できる効果などを併せて有する。そのため、上述したトランジスタのオン電流の向上に加えて、しきい値電圧の安定化や、S値（サブスレッショルド値）を低減させることができる。したがって、I<sub>c</sub>ut（ゲート電圧V<sub>G</sub>が0V時の電流）を下げることができ、消費電力を低減させることができます。

50

きる。また、トランジスタのしきい値電圧が安定化することから、半導体装置の長期信頼性を向上させることができる。また、本発明の一態様のトランジスタは、微細化にともなう電気特性の劣化が抑えられることから、集積度の高い半導体装置の形成に適しているといえる。

#### 【0229】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

#### 【0230】

(実施の形態4)

本実施の形態では、実施の形態2で説明したトランジスタ101、トランジスタ107、およびトランジスタ111の作製方法を説明する。

10

#### 【0231】

まず、基板115に含まれるシリコントランジスタの作製方法の一例を説明する。シリコン基板としては、n<sup>-</sup>型の単結晶シリコン基板を用い、表面に絶縁層(フィールド酸化膜とも言う)で分離した素子形成領域を形成する。素子形成領域の形成は、LOCOS法(Local Oxidation of Silicon)法)やSTI法(Shallow Trench Isolation)等を用いることができる。

#### 【0232】

ここで基板は単結晶シリコン基板に限らず、SOI(Silicon on Insulator)基板等を用いることもできる。

20

#### 【0233】

次に、素子形成領域を覆うようにゲート絶縁膜を形成する。例えば、熱処理を行い素子形成領域の表面を酸化させることにより酸化シリコン膜を形成する。また、酸化シリコン膜を形成した後に窒化処理を行うことによって酸化シリコン膜の表面を窒化させてもよい。

#### 【0234】

次に、ゲート絶縁膜を覆うように導電膜を形成する。導電膜としては、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素またはこれらの元素を主成分とする合金材料若しくは化合物材料で形成することができる。また、これらの元素を窒化した金属窒化膜で形成することもできる。他にも、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体材料により形成することもできる。

30

#### 【0235】

次に、導電膜を選択的にエッチングすることによって、ゲート絶縁膜上にゲート電極層を形成する。

#### 【0236】

次に、ゲート電極層を覆うように酸化シリコン膜または窒化シリコン膜等の絶縁膜を形成し、エッチバックを行ってゲート電極層の側面にサイドウォールを形成する。

#### 【0237】

次に、素子形成領域以外を覆うようにレジストマスクを選択的に形成し、当該レジストマスクおよびゲート電極層をマスクとして不純物元素を導入することによってp<sup>+</sup>型の不純物領域を形成する。ここでは、p-ch型のトランジスタを形成するため、不純物元素としては、p型を付与する不純物元素であるホウ素(B)やガリウム(Ga)等を用いることができる。

40

#### 【0238】

以上でシリコン基板に活性領域を有するp-ch型のトランジスタが完成する。なお、当該トランジスタ上には窒化シリコン膜や酸化アルミニウム膜などのパッシベーション膜を形成することが好ましい。

#### 【0239】

次に、トランジスタを形成したシリコン基板上に層間絶縁膜を形成し、各種コンタクトブルグおよび各種配線を形成する。また、実施の形態1で説明したように水素の拡散を防止

50

する酸化アルミニウム等の絶縁層を形成する。基板 115 には、上述したトランジスタが形成されたシリコン基板、当該シリコン基板上に形成された層間絶縁膜等が含まれる。

#### 【 0 2 4 0 】

続いて、図 3 1 および図 3 2 を用いてトランジスタ 101 の作製方法を説明する。なお、図面の左側にはトランジスタのチャネル長方向の断面を示し、右側にはチャネル幅方向の断面を示す。また、チャネル幅方向の図面は拡大図のため、各要素の見かけ上の膜厚は左右の図面で異なる。

#### 【 0 2 4 1 】

酸化物半導体層 130 は、酸化物半導体層 130 a、酸化物半導体層 130 b および酸化物半導体層 130 c の三層構造である場合を例示する。酸化物半導体層 130 が二層構造の場合は、酸化物半導体層 130 a および酸化物半導体層 130 b の二層とし、酸化物半導体層 130 が単層構造の場合は、酸化物半導体層 130 b の一層とすればよい。10

#### 【 0 2 4 2 】

まず、基板 115 上に絶縁層 120 を形成する。基板 115 の種類および絶縁層 120 の材質は実施の形態 3 の説明を参照することができる。なお、絶縁層 120 は、スパッタ法、CVD 法、MBE (Molecular Beam Epitaxy) 法などを用いて形成することができる。

#### 【 0 2 4 3 】

また、絶縁層 120 にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理法などを用いて酸素を添加してもよい。酸素を添加することによって、絶縁層 120 から酸化物半導体層 130 への酸素の供給をさらに容易にすることができます。20

#### 【 0 2 4 4 】

なお、基板 115 の表面が絶縁体であり、後に設ける酸化物半導体層 130 への不純物拡散の影響が無い場合は、絶縁層 120 を設けない構成とすることができる。

#### 【 0 2 4 5 】

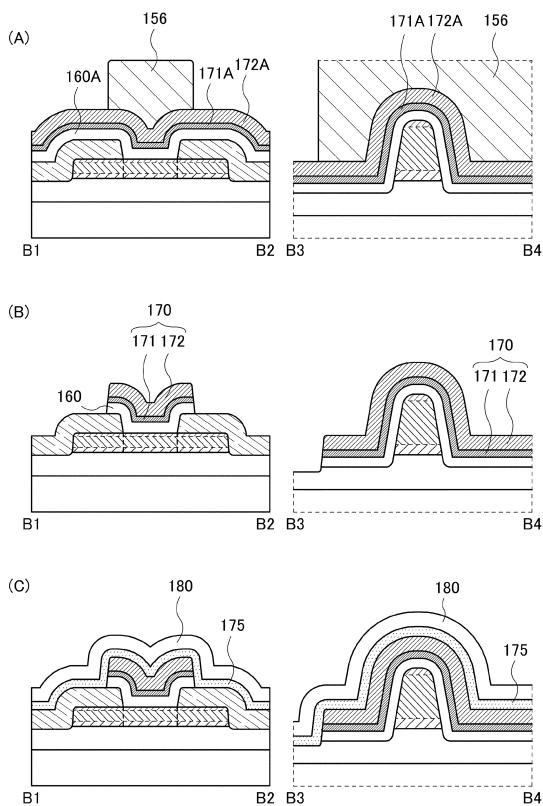

次に、絶縁層 120 上に酸化物半導体層 130 a となる酸化物半導体膜 130 A、酸化物半導体層 130 b となる酸化物半導体膜 130 B、および酸化物半導体層 130 c となる酸化物半導体膜 130 C をスパッタ法、CVD 法、MBE 法などを用いて成膜する（図 3 1 (A) 参照）。30

#### 【 0 2 4 6 】

酸化物半導体層 130 が積層構造である場合、酸化物半導体膜はロードロック室を備えたマルチチャンバー方式の成膜装置（例えばスパッタ装置）を用いて各層を大気に触れさせることなく連続して積層することが好ましい。スパッタ装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべく、クライオポンプのような吸着式の真空排気ポンプを用いて高真空排気 ( $5 \times 10^{-7}$  Pa 乃至  $1 \times 10^{-4}$  Pa 程度まで) できること、かつ、成膜される基板を 100 以上、好ましくは 500 以上に加熱できることが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に炭素成分や水分等を含む気体が逆流しないようにしておくことが好ましい。また、ターボ分子ポンプとクライオポンプを組み合わせた排気系を用いてもよい。40

#### 【 0 2 4 7 】

高純度真性酸化物半導体を得るために、チャンバー内を高真空排気するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が -40 以下、好ましくは -80 以下、より好ましくは -100 以下にまで高純度化したガスを用いることで酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。

#### 【 0 2 4 8 】

酸化物半導体膜 130 A、酸化物半導体膜 130 B、および酸化物半導体膜 130 C には、実施の形態 3 で説明した材料を用いることができる。例えば、酸化物半導体膜 130 A50

に  $In : Ga : Zn = 1 : 3 : 6$ 、 $1 : 3 : 4$ 、 $1 : 3 : 3$  または  $1 : 3 : 2$  [ 原子数比 ] の  $In - Ga - Zn$  酸化物、酸化物半導体膜 130B に  $In : Ga : Zn = 1 : 1 : 1$ 、 $3 : 1 : 2$ 、 $5 : 5 : 6$  または  $4 : 2 : 4 . 1$  [ 原子数比 ] の  $In - Ga - Zn$  酸化物、酸化物半導体膜 130C に  $In : Ga : Zn = 1 : 3 : 6$ 、 $1 : 3 : 4$ 、 $1 : 3 : 3$  または  $1 : 3 : 2$  [ 原子数比 ] の  $In - Ga - Zn$  酸化物を用いることができる。また、酸化物半導体膜 130A、および酸化物半導体膜 130C には、酸化ガリウムのような酸化物半導体を用いてもよい。また、成膜法にスパッタ法を用いる場合は、上記材料をターゲットとして成膜することができる。なお、酸化物半導体膜 130A、酸化物半導体膜 130B、および酸化物半導体膜 130C の原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス 40 % の変動を含む。例えば、 $In : Ga : Zn = 4 : 2 : 4 . 1$  の材料をターゲットに用いてスパッタ法で成膜した膜の原子数比は、 $In : Ga : Zn = 4 : 2 : 3$  になることがある。

10

#### 【 0249 】

ただし、実施の形態 3 に詳細を記したように、酸化物半導体膜 130B には酸化物半導体膜 130A および酸化物半導体膜 130C よりも電子親和力が大きい材料を用いる。

#### 【 0250 】

なお、酸化物半導体膜の成膜には、スパッタ法を用いることが好ましい。スパッタ法としては、RFスパッタ法、DCスパッタ法、ACスパッタ法等を用いることができる。

#### 【 0251 】

酸化物半導体膜 130C の形成後に、第 1 の加熱処理を行ってもよい。第 1 の加熱処理は、250 以上 650 以下、好ましくは 300 以上 500 以下の温度で、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上含む雰囲気、または減圧状態で行えばよい。また、第 1 の加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを 10 ppm 以上含む雰囲気で行ってもよい。第 1 の加熱処理によって、酸化物半導体膜 130A、酸化物半導体膜 130B、および酸化物半導体膜 130C の結晶性を高め、さらに絶縁層 120、酸化物半導体膜 130A、酸化物半導体膜 130B、および酸化物半導体膜 130C から水素や水などの不純物を除去することができる。なお、第 1 の加熱処理は、後述する酸化物半導体層 130a、酸化物半導体層 130b、および酸化物半導体層 130c を形成するエッチングの後に行ってもよい。

20

#### 【 0252 】

次に、酸化物半導体膜 130C 上に導電層を形成する。導電層は、例えば、次の方法を用いて形成することができる。

#### 【 0253 】

まず、酸化物半導体膜 130C 上に第 1 の導電膜を形成する。第 1 の導電膜としては、Al、Cr、Cu、Ta、Ti、Mo、W、Ni、Mn、Nd、Sc、および当該金属材料の合金から選ばれた材料の単層、または積層を用いることができる。

#### 【 0254 】

次に、第 1 の導電膜上にネガ型のレジスト膜を形成し、当該レジスト膜に対して電子ビーム露光、液浸露光、EUV 露光などの方法を用いて露光し、現像処理を行うことで第 1 のレジストマスクを形成する。なお、第 1 の導電膜とレジスト膜の間には密着剤として有機塗布膜を形成することが好ましい。また、ナノインプリントリソグラフィ法を用いて第 1 のレジストマスクを形成してもよい。

40

#### 【 0255 】

次に、第 1 のレジストマスクを用いて、第 1 の導電膜を選択的にエッチングし、第 1 のレジストマスクをアッシングすることにより導電層を形成する。

#### 【 0256 】

次に、上記導電層をハードマスクとして用い、酸化物半導体膜 130A、酸化物半導体膜 130B、および酸化物半導体膜 130C を選択的にエッティングして上記導電層を取り除き、酸化物半導体層 130a、酸化物半導体層 130b、および酸化物半導体層 130c の積層からなる酸化物半導体層 130 を形成する（図 31 (B) 参照）。なお、上記導電

50

層を形成せずに、第1のレジストマスクを用いて酸化物半導体層130を形成してもよい。ここで、酸化物半導体層130に対して酸素イオンを注入してもよい。

#### 【0257】

次に、酸化物半導体層130を覆うように第2の導電膜を形成する。第2の導電膜としては、実施の形態3で説明した導電層140および導電層150に用いることのできる材料で形成すればよい。第2の導電膜の形成には、スパッタ法、CVD法、MBE法などを用いることができる。

#### 【0258】

次に、ソース領域およびドレイン領域となる部分の上に第2のレジストマスクを形成する。そして、第2の導電膜の一部をエッチングし、導電層140および導電層150を形成する(図31(C)参照)。10

#### 【0259】

次に、酸化物半導体層130、導電層140および導電層150上に絶縁膜160Aを形成する。絶縁膜160Aは、実施の形態3で説明した絶縁層160に用いることのできる材料で形成すればよい。絶縁膜160Aの形成には、スパッタ法、CVD法、MBE法などを用いることができる。

#### 【0260】

次に、第2の加熱処理を行ってもよい。第2の加熱処理は、第1の加熱処理と同様の条件で行うことができる。第2の加熱処理により、絶縁層120から酸素を酸化物半導体層130の全体に拡散させることができる。なお、第2の加熱処理を行わずに、第3の加熱処理で上記効果を得てもよい。20

#### 【0261】

次に、絶縁膜160A上に導電層170となる第3の導電膜171Aおよび第4の導電膜172Aを形成する。第3の導電膜171Aおよび第4の導電膜172Aは、実施の形態3で説明した導電層171および導電層172に用いることのできる材料で形成すればよい。第3の導電膜171Aおよび第4の導電膜172Aの形成には、スパッタ法、CVD法、MBE法などを用いることができる。

#### 【0262】

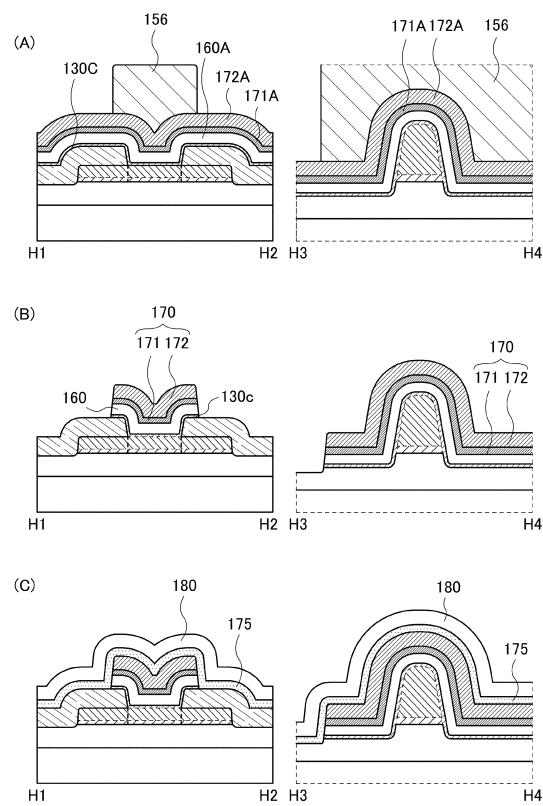

次に、第4の導電膜172A上に第3のレジストマスク156を形成する(図32(A)参照)。そして、当該レジストマスクを用いて、第3の導電膜171A、第4の導電膜172Aおよび絶縁膜160Aを選択的にエッチングし、導電層171および導電層172からなる導電層170、および絶縁層160を形成する(図32(B)参照)。なお、絶縁膜160Aをエッチングしない構造とすれば、トランジスタ102を作製することができる。

#### 【0263】

次に、酸化物半導体層130、導電層140、導電層150、絶縁層160および導電層170上に絶縁層175を形成する。絶縁層175の材質は、実施の形態3の説明を参照することができる。トランジスタ101の場合は、酸化アルミニウム膜を用いることが好ましい。絶縁層175は、スパッタ法、CVD法、MBE法などで形成することができる。40

#### 【0264】

次に、絶縁層175上に絶縁層180を形成する(図32(C)参照)。絶縁層180の材質は、実施の形態3の説明を参照することができる。また、絶縁層180は、スパッタ法、CVD法、MBE法などで形成することができる。

#### 【0265】

また、絶縁層175および/または絶縁層180にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理法などを用いて酸素を添加してもよい。酸素を添加することによって、絶縁層175および/または絶縁層180から酸化物半導体層130への酸素の供給をさらに容易にすることができます。

#### 【0266】

10

20

30

40

50

次に、第3の加熱処理を行ってもよい。第3の加熱処理は、第1の加熱処理と同様の条件で行うことができる。第3の加熱処理により、絶縁層120、絶縁層175、絶縁層180から過剰酸素が放出されやすくなり、酸化物半導体層130の酸素欠損を低減することができる。

#### 【0267】

次に、トランジスタ107の作製方法について説明する。なお、上述したトランジスタ101の作製方法と重複する工程の詳細な説明は省略する。

#### 【0268】

基板115上に絶縁層120を形成し、当該絶縁層120上に酸化物半導体層130aとなる酸化物半導体膜130A、および酸化物半導体層130bとなる酸化物半導体膜130Bをスパッタ法、CVD法、MBE法などを用いて成膜する（図33（A）参照）。 10

#### 【0269】

次に、第1の導電膜を酸化物半導体膜130B上に形成し、前述した方法と同様に第1のレジストマスクを用いて導電層を形成する。そして、当該導電層をハードマスクとして酸化物半導体膜130Aおよび酸化物半導体膜130Bを選択的にエッチングし、上記導電層を取り除いて酸化物半導体層130aおよび酸化物半導体層130bからなる積層を形成する（図33（B）参照）。なお、ハードマスクを形成せずに、第1のレジストマスクを用いて当該積層を形成してもよい。ここで、酸化物半導体層130aおよび酸化物半導体層130bに対して酸素イオンを注入してもよい。

#### 【0270】

次に、上記積層を覆うように第2の導電膜を形成する。そして、ソース領域およびドレイン領域となる部分の上に第2のレジストマスクを形成し、当該第2のレジストマスクを用いて第2の導電膜の一部をエッチングし、導電層140および導電層150を形成する（図33（C）参照）。 20

#### 【0271】

次に、酸化物半導体層130aおよび酸化物半導体層130bの積層上、ならびに導電層140および導電層150上に酸化物半導体層130cとなる酸化物半導体膜130Cを形成する。さらに、酸化物半導体膜130C上に絶縁膜160A、第3の導電膜171Aおよび第4の導電膜172Aを形成する。 30

#### 【0272】

次に、第4の導電膜172A上に第3のレジストマスク156を形成する（図34（A）参照）。そして、当該レジストマスクを用いて、第3の導電膜171A、第4の導電膜172A、絶縁膜160A、および酸化物半導体膜130Cを選択的にエッチングし、導電層171および導電層172からなる導電層170、絶縁層160、および酸化物半導体層130cを形成する（図34（B）参照）。なお、絶縁膜160Aおよび酸化物半導体膜130Cを第4のレジストマスクを用いてエッチングすることで、トランジスタ108を作製することができる。

#### 【0273】

次に、絶縁層120、酸化物半導体層130（酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c）、導電層140、導電層150、絶縁層160および導電層170上に絶縁層175および絶縁層180を形成する（図34（C）参照）。 40

#### 【0274】

以上の工程において、トランジスタ107を作製することができる。

#### 【0275】

次に、トランジスタ111の作製方法について説明する。なお、上述したトランジスタ101の作製方法と重複する工程の詳細な説明は省略する。

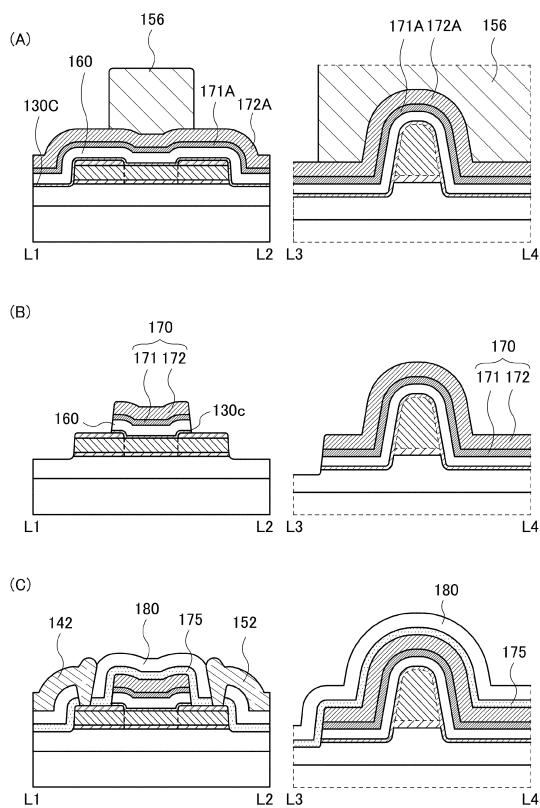

#### 【0276】

基板115上に絶縁層120を形成し、当該絶縁層120上に酸化物半導体層130aとなる酸化物半導体膜130A、および酸化物半導体層130bとなる酸化物半導体膜130Bをスパッタ法、CVD法、MBE法などを用いて成膜する。そして、第1の導電膜を 50

酸化物半導体膜 130B 上に形成し、第 1 のレジストマスクを用いて導電層 141a を形成する（図 35（A）参照）。

#### 【0277】

そして、導電層 141a をハーデマスクとして酸化物半導体膜 130A および酸化物半導体膜 130B を選択的にエッチングし、酸化物半導体層 130a、酸化物半導体層 130b および導電層 141a からなる積層を形成する（図 35（B）参照）。ここで、酸化物半導体層 130a および酸化物半導体層 130b に対して酸素イオンを注入してもよい。

#### 【0278】

次に、ソース領域およびドレイン領域となる部分の上に第 2 のレジストマスクを形成し、当該第 2 のレジストマスクを用いて導電層 141a の一部をエッチングし、導電層 141 および導電層 151 を形成する（図 35（C）参照）。

#### 【0279】

次に、酸化物半導体層 130a および酸化物半導体層 130b の積層上、ならびに導電層 141 および導電層 151 上に酸化物半導体層 130c となる酸化物半導体膜 130C を形成する。さらに、酸化物半導体膜 130C 上に絶縁膜 160A、第 3 の導電膜 171A および第 4 の導電膜 172A を形成する。

#### 【0280】

次に、第 4 の導電膜 172A 上に第 3 のレジストマスク 156 を形成する（図 36（A）参照）。そして、当該レジストマスクを用いて、第 3 の導電膜 171A、第 4 の導電膜 172A、絶縁膜 160A、および酸化物半導体膜 130C を選択的にエッチングし、導電層 171 および導電層 172 からなる導電層 170、絶縁層 160、および酸化物半導体層 130c を形成する（図 36（B）参照）。

#### 【0281】

次に、絶縁層 120、酸化物半導体層 130（酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c）、導電層 141、導電層 151、絶縁層 160 および導電層 170 上に絶縁層 175 および絶縁層 180 を形成する。

#### 【0282】

次に、絶縁層 175 および絶縁層 180 に導電層 141 および導電層 151 に達する開口部を設け、当該開口部を覆うように第 5 の導電膜を形成する。そして、第 5 の導電膜上に第 4 のレジストマスクを設け、当該レジストマスクを用いて、第 5 の導電膜を選択的にエッチングし、導電層 142 および導電層 152 を形成する（図 36（C）参照）。

#### 【0283】

以上の工程において、トランジスタ 111 を作製することができる。

#### 【0284】

なお、本実施の形態で説明した金属膜、半導体膜、無機絶縁膜など様々な膜は、代表的にはスパッタ法やプラズマ CVD 法により形成することができるが、他の方法、例えば、熱 CVD 法により形成してもよい。熱 CVD 法の例としては、MOCVD（Metal Organic Chemical Vapor Deposition）法や ALD（Atomic Layer Deposition）法などがある。

#### 【0285】

熱 CVD 法は、プラズマを使わない成膜方法のため、プラズマダメージにより欠陥が生成されることが無いという利点を有する。

#### 【0286】

また、熱 CVD 法では、原料ガスと酸化剤を同時にチャンバー内に送り、チャンバー内を大気圧または減圧下とし、基板近傍または基板上で反応させて基板上に堆積させることで成膜を行ってもよい。

#### 【0287】

ALD 法は、チャンバー内を大気圧または減圧下とし、反応のための原料ガスが順次にチャンバーに導入され、そのガス導入の順序を繰り返すことで成膜を行ってもよい。例えば、それぞれのスイッチングバルブ（高速バルブとも呼ぶ）を切り替えて 2 種類以上の原料

10

20

30

40

50

ガスを順番にチャンバーに供給し、複数種の原料ガスが混ざらないように第1の原料ガスと同時に不活性ガス（アルゴン、或いは窒素など）などを導入し、第2の原料ガスを導入する。なお、同時に不活性ガスを導入する場合には、不活性ガスはキャリアガスとなり、また、第2の原料ガスの導入時にも同時に不活性ガスを導入してもよい。また、不活性ガスを導入する代わりに真空排気によって第1の原料ガスを排出した後、第2の原料ガスを導入してもよい。第1の原料ガスが基板の表面に吸着して第1の層を成膜し、後から導入される第2の原料ガスと反応して、第2の層が第1の層上に積層されて薄膜が形成される。このガス導入順序を制御しつつ所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、ガス導入順序を繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なFETを作製する場合に適している。10

#### 【0288】

MOCVD法やALD法などの熱CVD法は、これまでに記載した実施形態に開示された金属膜、半導体膜、無機絶縁膜など様々な膜を形成することができ、例えば、In-Ga-Zn-O膜を成膜する場合には、トリメチルインジウム、トリメチルガリウム、およびジメチル亜鉛を用いることができる。なお、トリメチルインジウムの化学式は、In(CH<sub>3</sub>)<sub>3</sub>である。また、トリメチルガリウムの化学式は、Ga(CH<sub>3</sub>)<sub>3</sub>である。また、ジメチル亜鉛の化学式は、Zn(CH<sub>3</sub>)<sub>2</sub>である。また、これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム（化学式Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>）を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛（化学式Zn(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>）を用いることもできる。20

#### 【0289】

例えば、ALDを利用する成膜装置により酸化ハフニウム膜を形成する場合には、溶媒とハフニウム前駆体化合物を含む液体（ハフニウムアルコキシド溶液、代表的にはテトラキスジメチルアミドハフニウム（TDMAH））を気化させた原料ガスと、酸化剤としてオゾン(O<sub>3</sub>)の2種類のガスを用いる。なお、テトラキスジメチルアミドハフニウムの化学式はHf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>である。また、他の材料液としては、テトラキス（エチルメチルアミド）ハフニウムなどがある。

#### 【0290】

例えば、ALDを利用する成膜装置により酸化アルミニウム膜を形成する場合には、溶媒とアルミニウム前駆体化合物を含む液体（トリメチルアルミニウム（TMA）など）を気化させた原料ガスと、酸化剤としてH<sub>2</sub>Oの2種類のガスを用いる。なお、トリメチルアルミニウムの化学式はAl(CH<sub>3</sub>)<sub>3</sub>である。また、他の材料液としては、トリス（ジメチルアミド）アルミニウム、トリイソブチルアルミニウム、アルミニウムトリス（2,2,6,6-テトラメチル-3,5-ヘプタンジオナート）などがある。30

#### 【0291】

例えば、ALDを利用する成膜装置により酸化シリコン膜を形成する場合には、ヘキサクロロジシランを被成膜面に吸着させ、吸着物に含まれる塩素を除去し、酸化性ガス(O<sub>2</sub>、一酸化二窒素)のラジカルを供給して吸着物と反応させる。

#### 【0292】

例えば、ALDを利用する成膜装置によりタンゲステン膜を成膜する場合には、WF<sub>6</sub>ガスとB<sub>2</sub>H<sub>6</sub>ガスを順次繰り返し導入して初期タンゲステン膜を形成し、その後、WF<sub>6</sub>ガスとH<sub>2</sub>ガスを同時に導入してタンゲステン膜を形成する。なお、B<sub>2</sub>H<sub>6</sub>ガスに代えてSiH<sub>4</sub>ガスを用いてもよい。40

#### 【0293】

例えば、ALDを利用する成膜装置により酸化物半導体膜、例えばIn-Ga-Zn-O膜を成膜する場合には、In(CH<sub>3</sub>)<sub>3</sub>ガスとO<sub>3</sub>ガスを順次繰り返し導入してIn-O層を形成し、その後、Ga(CH<sub>3</sub>)<sub>3</sub>ガスとO<sub>3</sub>ガスを同時に導入してGa-O層を形成し、更にその後Zn(CH<sub>3</sub>)<sub>2</sub>とO<sub>3</sub>ガスを同時に導入してZn-O層を形成する。なお、これらの層の順番はこの例に限らない。また、これらのガスを混ぜてIn-Ga50

- O層やIn-Zn-O層、Ga-Zn-O層などの混合化合物層を形成しても良い。なお、O<sub>3</sub>ガスに変えてAr等の不活性ガスでバーリングして得られたH<sub>2</sub>Oガスを用いても良いが、Hを含まないO<sub>3</sub>ガスを用いる方が好ましい。また、In(CH<sub>3</sub>)<sub>3</sub>ガスにかえて、In(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いても良い。また、Ga(CH<sub>3</sub>)<sub>3</sub>ガスにかえて、Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いても良い。また、Zn(CH<sub>3</sub>)<sub>2</sub>ガスを用いても良い。

#### 【0294】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

#### 【0295】

(実施の形態5)

<酸化物半導体の構造について>

以下では、酸化物半導体の構造について説明する。

#### 【0296】

本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「略平行」とは、二つの直線が-30°以上30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。

#### 【0297】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

#### 【0298】

酸化物半導体は、例えば、非単結晶酸化物半導体と単結晶酸化物半導体とに分けられる。または、酸化物半導体は、例えば、結晶性酸化物半導体と非晶質酸化物半導体とに分けられる。

#### 【0299】

なお、非単結晶酸化物半導体としては、C AAC - OS (C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体などがある。また、結晶性酸化物半導体としては、単結晶酸化物半導体、C AAC - OS、多結晶酸化物半導体、微結晶酸化物半導体などがある。

#### 【0300】

まずは、C AAC - OSについて説明する。

#### 【0301】

C AAC - OSは、c軸配向した複数の結晶部(ペレットともいう。)を有する酸化物半導体の一つである。

#### 【0302】

透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって、C AAC - OSの明視野像および回折パターンの複合解析像(高分解能TEM像ともいう。)を観察することで複数のペレットを確認することができる。一方、高分解能TEM像によっても明確なペレット同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、C AAC - OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

#### 【0303】

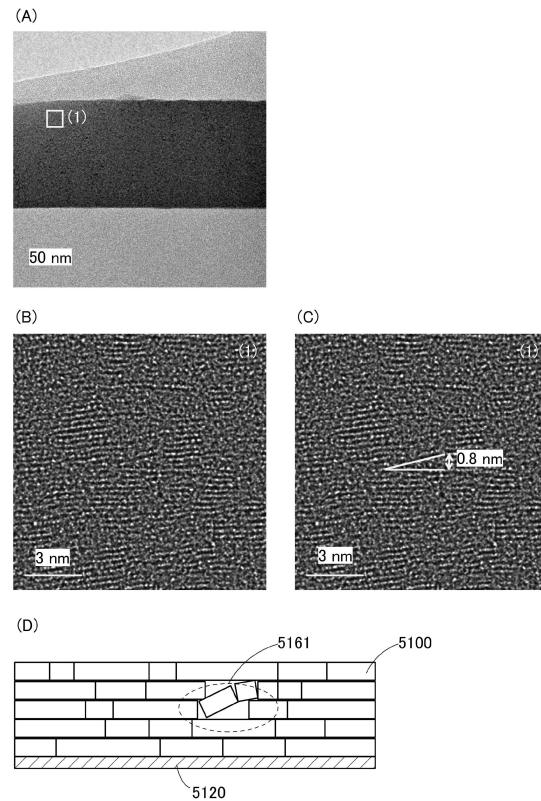

例えば、図43(A)に示すように、試料面と略平行な方向から、C AAC - OSの断面の高分解能TEM像を観察する。ここでは、球面収差補正(Spherical Aberration Corrector)機能を用いてTEM像を観察する。なお、球面収差補正機能を用いた高分解能TEM像を、以下では、特にCs補正高分解能TEM像と呼

10

20

30

40

50

ぶ。なお、Cs補正高分解能TEM像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡JEM-ARM200Fなどによって行うことができる。

#### 【0304】

図43(A)の領域(1)を拡大したCs補正高分解能TEM像を図43(B)に示す。図43(B)より、ペレットにおいて、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OSの膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAAC-OSの被形成面または上面と平行に配列する。

#### 【0305】

図43(B)において、CAAC-OSは特徴的な原子配列を有する。図43(C)は、特徴的な原子配列を、補助線で示したものである。図43(B)および図43(C)より、ペレット一つの大きさは1nm以上3nm以下程度であり、ペレットとペレットとの傾きにより生じる隙間の大きさは0.8nm程度であることがわかる。したがって、ペレットを、ナノ結晶(nc:nanocrystal)と呼ぶこともできる。

#### 【0306】

ここで、Cs補正高分解能TEM像から、基板5120上のCAAC-OSのペレット5100の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる(図43(D)参照。)。図43(C)で観察されたペレットとペレットとの間で傾きが生じている箇所は、図43(D)に示す領域5161に相当する。

#### 【0307】

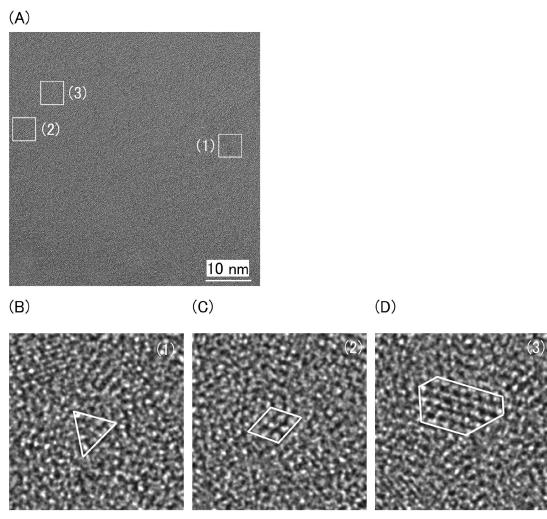

また、例えば、図44(A)に示すように、試料面と略垂直な方向から、CAAC-OSの平面のCs補正高分解能TEM像を観察する。図44(A)の領域(1)、領域(2)および領域(3)を拡大したCs補正高分解能TEM像を、それぞれ図44(B)、図44(C)および図44(D)に示す。図44(B)、図44(C)および図44(D)より、ペレットは、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なるペレット間で、金属原子の配列に規則性は見られない。

#### 【0308】

例えば、InGaZnO<sub>4</sub>の結晶を有するCAAC-OSに対し、X線回折(XRD:X-Ray Diffraction)装置を用いてout-of-plane法による構造解析を行うと、図45(A)に示すように回折角(2)が31°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の(009)面に帰属されることから、CAAC-OSの結晶がc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

#### 【0309】

なお、InGaZnO<sub>4</sub>の結晶を有するCAAC-OSのout-of-plane法による構造解析では、2が31°近傍のピークの他に、2が36°近傍にもピークが現れる場合がある。2が36°近傍のピークは、CAAC-OS中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAAC-OSは、2が31°近傍にピークを示し、2が36°近傍にピークを示さないことが好ましい。

#### 【0310】

一方、CAAC-OSに対し、c軸に略垂直な方向からX線を入射させるin-plane法による構造解析を行うと、2が56°近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub>の結晶の(110)面に帰属される。CAAC-OSの場合は、2を56°近傍に固定し、試料面の法線ベクトルを軸(c軸)として試料を回転させながら分析(スキャン)を行っても、図45(B)に示すように明瞭なピークは現れない。これに対し、InGaZnO<sub>4</sub>の単結晶酸化物半導体であれば、2を56°近傍に固定してスキャンした場合、図45(C)に示すように(110)面と等価な結晶面に帰属されるピークが6本観察される。したがって、XRDを用いた構造解析から、CAAC-OSは、a軸およびb軸の配向が不規則であることが確認できる。

#### 【0311】

10

20

30

40

50

次に、C A A C - O S である I n - G a - Z n 酸化物に対し、試料面に平行な方向からプローブ径が 3 0 0 nm の電子線を入射させたときの回折パターン（制限視野透過電子回折パターンともいう。）を図 4 6 (A) に示す。図 4 6 (A) より、例えば、I n G a Z n O<sub>4</sub> の結晶の (0 0 9) 面に起因するスポットが確認される。したがって、電子回折によつても、C A A C - O S に含まれるペレットが c 軸配向性を有し、c 軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直な方向からプローブ径が 3 0 0 nm の電子線を入射させたときの回折パターンを図 4 6 (B) に示す。図 4 6 (B) より、リング状の回折パターンが確認される。したがって、電子回折によつても、C A A C - O S に含まれるペレットの a 軸および b 軸は配向性を有さないことがわかる。なお、図 4 6 (B) における第 1 リングは、I n G a Z n O<sub>4</sub> の結晶の (0 1 0) 面および (1 0 0) 面などに起因すると考えられる。また、図 4 6 (B) における第 2 リングは (1 1 0) 面などに起因すると考えられる。

### 【0312】

このように、それぞれのペレット（ナノ結晶）の c 軸が、被形成面または上面に略垂直な方向を向いていることから、C A A C - O S を C A N C ( C - A x i s A l i g n e d n a n o c r y s t a l s ) を有する酸化物半導体と呼ぶこともできる。

### 【0313】

C A A C - O S は、不純物濃度の低い酸化物半導体である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体の主成分以外の元素である。特に、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体内部に含まれると、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

### 【0314】

また、C A A C - O S は、欠陥準位密度の低い酸化物半導体である。例えば、酸化物半導体中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

### 【0315】

また、C A A C - O S を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

### 【0316】

次に、微結晶酸化物半導体について説明する。

### 【0317】

微結晶酸化物半導体は、高分解能 TEM 像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。微結晶酸化物半導体に含まれる結晶部は、1 nm 以上 1 0 0 nm 以下、または 1 nm 以上 1 0 nm 以下の大きさであることが多い。特に、1 nm 以上 1 0 nm 以下、または 1 nm 以上 3 nm 以下の微結晶であるナノ結晶を有する酸化物半導体を、n c - O S ( n a n o c r y s t a l l i n e O x i d e S e m i c o n d u c t o r ) と呼ぶ。また、n c - O S は、例えば、高分解能 TEM 像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、C A A C - O S におけるペレットと同じ起源を有する可能性がある。そのため、以下では n c - O S の結晶部をペレットと呼ぶ場合がある。

### 【0318】

n c - O S は、微小な領域（例えば、1 nm 以上 1 0 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S は、分析方法によっては、非晶質酸化物半導体と区別が付かない場合がある。例えば、n c - O S に対し、ペレットよりも大きい径の X 線を用いる X R D 装置

10

20

30

40

50

を用いて構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、n c - O Sに対し、ペレットよりも大きいプローブ径（例えば50nm以上）の電子線を用いる電子回折（制限視野電子回折ともいう。）を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O Sに対し、ペレットの大きさと近いペレットより小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O Sに対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。また、n c - O Sに対しナノビーム電子回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

## 【0319】

10

このように、それぞれのペレット（ナノ結晶）の結晶方位が規則性を有さないことから、n c - O SをNANC（Non-Aligned nanocrystals）を有する酸化物半導体と呼ぶこともできる。

## 【0320】

n c - O Sは、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、n c - O Sは、非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、n c - O Sは、異なるペレット間で結晶方位に規則性が見られない。そのため、n c - O Sは、C AAC - O Sと比べて欠陥準位密度が高くなる。

## 【0321】

次に、非晶質酸化物半導体について説明する。

20

## 【0322】

非晶質酸化物半導体は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体である。石英のような無定形状態を有する酸化物半導体が一例である。

## 【0323】

非晶質酸化物半導体は、高分解能TEM像において結晶部を確認することができない。

## 【0324】

非晶質酸化物半導体に対し、XRD装置を用いた構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、非晶質酸化物半導体に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンが観測される。

30

## 【0325】

非晶質構造については、様々な見解が示されている。例えば、原子配列に全く秩序性を有さない構造を完全な非晶質構造（completely amorphous structure）と呼ぶ場合がある。また、最近接原子間距離または第2近接原子間距離まで秩序性を有し、かつ長距離秩序性を有さない構造を非晶質構造と呼ぶ場合もある。したがって、最も厳格な定義によれば、僅かでも原子配列に秩序性を有する酸化物半導体を非晶質酸化物半導体と呼ぶことはできない。また、少なくとも、長距離秩序性を有する酸化物半導体を非晶質酸化物半導体と呼ぶことはできない。よって、結晶部を有することから、例えば、C AAC - O Sおよびn c - O Sを、非晶質酸化物半導体または完全な非晶質酸化物半導体と呼ぶことはできない。

40

## 【0326】

なお、酸化物半導体は、n c - O Sと非晶質酸化物半導体との間の物性を示す構造を有する場合がある。そのような構造を有する酸化物半導体を、特に非晶質ライク酸化物半導体（a-like OS: amorphous-like Oxide Semiconductor）と呼ぶ。

## 【0327】

a - like OSは、高分解能TEM像において鬆（ボイドともいう。）が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することができる領域と、結晶部を確認することのできない領域と、を有する。

50

**【0328】**

以下では、酸化物半導体の構造による電子照射の影響の違いについて説明する。

**【0329】**

a - l i k e O S、n c - O S および C A A C - O S を準備する。いずれの試料も In - Ga - Zn 酸化物である。

**【0330】**

まず、各試料の高分解能断面 TEM 像を取得する。高分解能断面 TEM 像により、各試料は、いずれも結晶部を有することがわかる。

**【0331】**

さらに、各試料の結晶部の大きさを計測する。図 47 は、各試料の結晶部（22箇所から 10 45 箇所）の平均の大きさの変化を調査した例である。図 47 より、a - l i k e O S は、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、図 47 中に（1）で示すように、TEM による観察初期においては 1.2 nm 程度の大きさだった結晶部（初期核ともいう。）が、累積照射量が  $4.2 \times 10^8 e^- / nm^2$  においては 2.6 nm 程度の大きさまで成長していることがわかる。一方、n c - O S および C A A C - O S は、電子照射開始時から電子の累積照射量が  $4.2 \times 10^8 e^- / nm^2$  になるまでの範囲で、電子の累積照射量によらず結晶部の大きさに変化が見られないことがわかる。具体的には、図 47 中の（2）で示すように、TEM による観察の経過によらず、結晶部の大きさは 1.4 nm 程度であることがわかる。また、図 47 中の（3）で示すように、TEM による観察の経過によらず、結晶部の大きさは 2.1 nm 程度であることがわかる。 20

**【0332】**

このように、a - l i k e O S は、TEM による観察程度の微量な電子照射によって、結晶化が起こり、結晶部の成長が見られる場合がある。一方、良質な n c - O S、および C A A C - O S であれば、TEM による観察程度の微量な電子照射による結晶化はほとんど見られないことがわかる。

**【0333】**

なお、a - l i k e O S および n c - O S の結晶部の大きさの計測は、高分解能 TEM 像を用いて行うことができる。例えば、InGaZnO<sub>4</sub> の結晶は層状構造を有し、In - O 層の間に、Ga - Zn - O 層を 2 層有する。InGaZnO<sub>4</sub> の結晶の単位格子は、In - O 層を 3 層有し、また Ga - Zn - O 層を 6 層有する、計 9 層が c 軸方向に層状に重なった構造を有する。よって、これらの近接する層同士の間隔は、（009）面の格子面間隔（d 値ともいう。）と同程度であり、結晶構造解析からその値は 0.29 nm と求められている。そのため、高分解能 TEM 像における格子縞に着目し、格子縞の間隔が 0.28 nm 以上 0.30 nm 以下である箇所においては、それぞれの格子縞が InGaZnO<sub>4</sub> の結晶の a - b 面に対応する。 30

**【0334】**

また、酸化物半導体は、構造ごとに密度が異なる場合がある。例えば、ある酸化物半導体の組成がわかれれば、該組成と同じ組成における単結晶の密度と比較することにより、その酸化物半導体の構造を推定することができる。例えば、単結晶の密度に対し、a - l i k e O S の密度は 78.6% 以上 92.3% 未満となる。また、例えば、単結晶の密度に対し、n c - O S の密度および C A A C - O S の密度は 92.3% 以上 100% 未満となる。なお、単結晶の密度に対し密度が 78% 未満となる酸化物半導体は、成膜すること 자체が困難である。 40

**【0335】**