(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6361171号

(P6361171)

(45) 発行日 平成30年7月25日(2018.7.25)

(24) 登録日 平成30年7月6日(2018.7.6)

(51) Int.Cl.

G06F 17/50 (2006.01)

F 1

G 06 F 17/50 6 6 2 G

請求項の数 5 (全 17 頁)

(21) 出願番号 特願2014-42726 (P2014-42726)

(22) 出願日 平成26年3月5日 (2014.3.5)

(65) 公開番号 特開2015-170004 (P2015-170004A)

(43) 公開日 平成27年9月28日 (2015.9.28)

審査請求日 平成28年11月21日 (2016.11.21)

(73) 特許権者 000003067

TDK株式会社

東京都港区芝浦三丁目9番1号

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100113435

弁理士 黒木 義樹

(74) 代理人 100124062

弁理士 三上 敬史

(74) 代理人 100145012

弁理士 石坂 泰紀

(72) 発明者 江畠 克史

東京都港区芝浦三丁目9番1号 TDK-EPC株式会社内

最終頁に続く

(54) 【発明の名称】等価回路

## (57) 【特許請求の範囲】

## 【請求項 1】

積層型コンデンサのシミュレーション用の等価回路が設定されているプログラムを、コンピュータが実行してシミュレーションを行う方法であって、

前記プログラムに設定されている前記等価回路は、

前記積層型コンデンサの内部電極を示す第1回路部と、

前記積層型コンデンサの静電容量を示す第2回路部と、を有し、

前記第1回路部は、3つ以上設けられており、その少なくとも2つ以上においてインダクタンス成分を有しており、

前記第2回路部は、一の前記第1回路部と他の前記第1回路部との間に接続されており、

前記第1回路部の前記インダクタンス成分の間に相互インダクタンスが設定されるよう 10

に、前記等価回路が作成されており、

前記等価回路を用いてシミュレーションを行うことを特徴とするシミュレーション方法。

## 【請求項 2】

前記第1回路部は抵抗成分を有し、

前記抵抗成分は、

直列に接続された複数のインダクタンス素子と、

各前記インダクタンス素子それぞれの両端部に対して一端が接続され、互いに並列に 20

接続された複数の抵抗素子と、を有することを特徴とする請求項 1 記載のシミュレーション方法。

【請求項 3】

前記第 2 回路部は、

第 1 容量素子と、

第 2 容量素子と抵抗素子とが直列に接続された直列回路と、を有し、

前記直列回路は、1 以上設けられており、

前記第 1 容量素子と前記直列回路とが並列に接続されていることを特徴とする請求項 1 又は 2 記載のシミュレーション方法。

【請求項 4】

10

前記等価回路は、第 1 ~ 第 4 の端子を有し、

前記第 1 端子及び前記 3 端子は、前記第 1 回路部により電気的に接続されており、

前記第 2 端子及び前記 4 端子は、前記第 1 端子及び前記第 3 端子に接続された前記第 1 回路部とは異なる前記第 1 回路部により電気的に接続されていることを特徴とする請求項 1 ~ 3 のいずれか一項記載のシミュレーション方法。

【請求項 5】

コンピュータに、積層型コンデンサのシミュレーション用の等価回路を用いてシミュレーションを実行させるプログラムであって、

前記等価回路は、

前記積層型コンデンサの内部電極を示す第 1 回路部と、

20

前記積層型コンデンサの静電容量を示す第 2 回路部と、を有し、

前記第 1 回路部は、3 つ以上設けられており、その少なくとも 2 つ以上においてインダクタンス成分を有するように設定されており、

前記第 2 回路部は、一の前記第 1 回路部と他の前記第 1 回路部との間に接続されるよう設定されており、

前記第 1 回路部の前記インダクタンス成分の間に相互インダクタンスが設定されるよう、前記等価回路が作成されていることを特徴とするプログラム。

【発明の詳細な説明】

【技術分野】

【0001】

30

本発明は、積層型コンデンサのシミュレーション用の等価回路に関する。

【背景技術】

【0002】

この種の分野の従来技術として、例えば特許文献 1 に記載されたものが知られている。特許文献 1 に記載の積層チップコンデンサの等価回路モデルでは、基本等価回路の等価直列キャパシタンスと等価直列レジスタンスの一部を、スタティックキャパシタンスと、積層チップコンデンサ内における内部電極の角や端の近くに発生する電磁場分布の異常特性に関する回路素子として、キャパシタンス及びレジスタンスを設けている。このような構成により、この等価回路モデルでは、実際の回路性能との誤差の発生の抑制を図っている。

40

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2012-3409 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記のように、等価回路では、実製品の積層型コンデンサの特性との誤差を抑制し、実製品の積層型コンデンサの特性に近似する特性を得ることが求められている。

【0005】

50

本発明は、実製品の積層型コンデンサの特性に近似する特性を得ることができる等価回路を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明に係る等価回路は、積層型コンデンサのシミュレーション用の等価回路であって、積層型コンデンサの内部電極を示す第1回路部と、積層型コンデンサの静電容量を示す第2回路部と、を有し、第1回路部は、3つ以上設けられており、その少なくとも2つ以上においてインダクタンス成分を有しており、第2回路部は、一の第1回路部と他の第1回路部との間に接続されており、第1回路部のインダクタンス成分の間に相互インダクタンスが設定されていることを特徴とする。

10

【0007】

この等価回路は、内部電極を示す第1回路部が3つ以上設けられている。このように、等価回路では、第1回路部を3つ以上設けることにより、ある所定の周波数において内部共振現象が生じる。このとき、各第1回路部には、通常よりも大きい電流（共振電流）が流れることになる。共振電流が損失を有する第1回路部に流れると、等価回路全体のインピーダンス特性において損失のピークとして現れる。このピークは、実製品の積層型コンデンサにおいて発生する。したがって、等価回路では、実製品の積層型コンデンサの特性に近づけることができる。また、等価回路では、インダクタンス成分の間に相互インダクタンスが設定されている。これにより、等価回路では、実製品の積層型コンデンサにおいて生じる物理現象（内部電極間の電流のアンバランスや内部電極間で生じる共振現象）が実現可能となる。したがって、等価回路では、実製品の積層型コンデンサの特性に近似する特性を得ることができる。

20

【0008】

一実施形態においては、第1回路部は抵抗成分を有し、抵抗成分は、直列に接続された複数のインダクタンス素子と、各インダクタンス素子それぞれの両端部に対して一端が接続され、互いに並列に接続された複数の抵抗素子と、を有していてもよい。このように第1回路部の抵抗成分をインダクタンス素子及び抵抗素子により構成することにより、表皮効果を考慮することが可能となり、高周波帯域における抵抗成分（ESR：等価直列抵抗）が大きくなる。したがって、実製品の積層型コンデンサの特性に更に近似する特性を得ることができる。

30

【0009】

一実施形態においては、第2回路部は、第1容量素子と、第2容量素子と抵抗素子とが直列に接続された直列回路と、を有し、直列回路は、1以上設けられており、第1容量素子と直列回路とが並列に接続されていてもよい。このように第2回路部を第1容量素子と直列回路とにより構成することにより、誘電損失を考慮することが可能となり、低周波側における静電容量の成分を大きく且つ抵抗成分を小さくできる。したがって、実製品の積層型コンデンサの特性に更に近似する特性を得ることができる。

【0010】

一実施形態においては、第1～第4の端子を有し、第1端子及び3端子は、第1回路部により電気的に接続されており、第2端子及び4端子は、第1端子及び第3端子に接続された第1回路部とは異なる第1回路部により電気的に接続されていてもよい。このような構成により、等価回路は、貫通コンデンサとして構成されている。ここで、貫通型コンデンサでは、4つの端子電極のうち、内部電極で電気的に接続された第2端子電極及び第4端子電極をグランドに接続すると、内部電極では、第2端子電極と第4端子電極とに向かって、同じ大きさで互いに逆方向のノイズ電流が流れる。このとき、第2端子電極に向かう電流により生じる磁束と、第4端子電極に向かう電流により生じる磁束とは、互いに打ち消し合う。これにより、貫通型コンデンサでは、ESL（等価直列インダクタンス）を低減することができる。等価回路は、貫通型コンデンサの構成をモデル化しており、インダクタンス成分間において相互インダクタンスを設定している。これにより、等価回路では、貫通型コンデンサと同等の特性を得ることができ、貫通型コンデンサにおける磁束の

40

50

打ち消しの効果のモデル化を図れる。

【発明の効果】

【0011】

本発明によれば、実製品の積層型コンデンサの特性に近似する特性を得ることができる。

【図面の簡単な説明】

【0012】

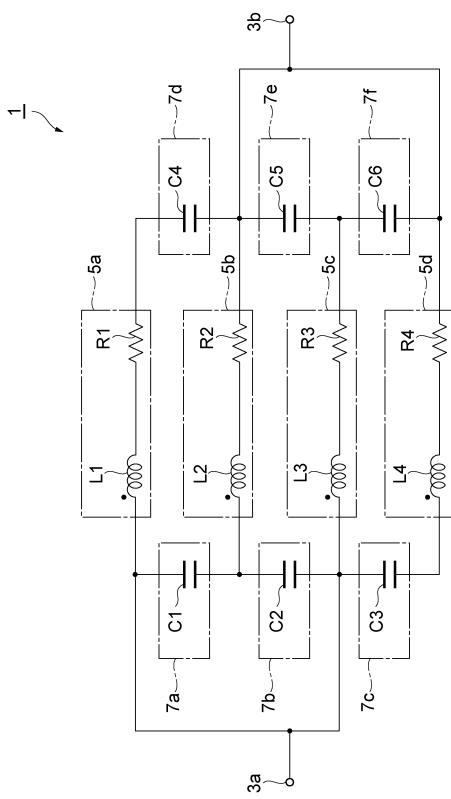

【図1】第1実施形態に係る等価回路を示す図である。

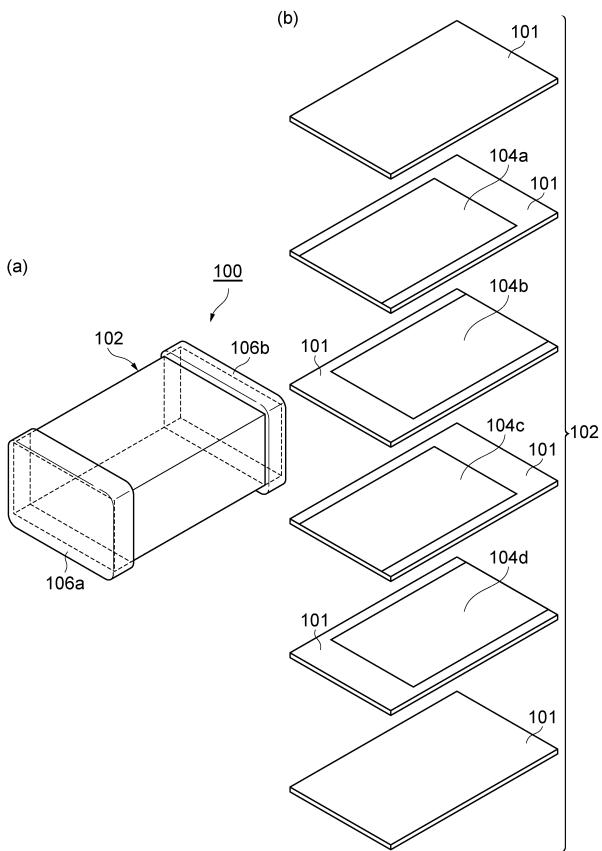

【図2】図1に示す等価回路を有する積層型コンデンサの構成を示す図である。

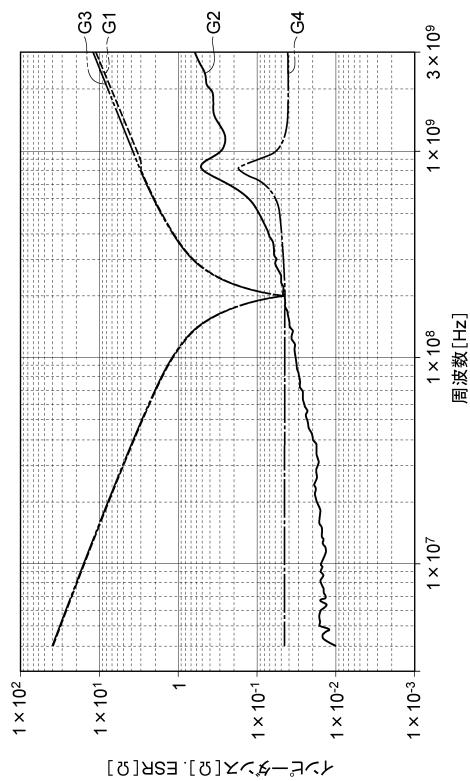

【図3】図1に示す等価回路におけるインピーダンス及びESRの周波数特性のシミュレーション結果を示す図である。 10

【図4】比較例の等価回路におけるインピーダンス及びESRの周波数特性のシミュレーション結果を示す図である。

【図5】第2実施形態に係る等価回路における内部電極部の抵抗部の構成を示す回路図である。

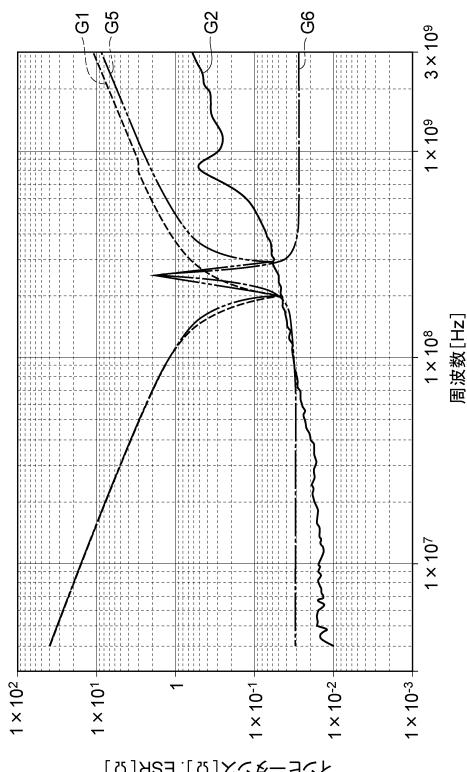

【図6】図5に示す抵抗部を備えた等価回路におけるインピーダンス及びESRの周波数特性のシミュレーション結果を示す図である。

【図7】第3実施形態に係る等価回路における静電容量部の静電容量回路の構成を示す回路図である。

【図8】図7に示す静電容量回路を備えた等価回路におけるインピーダンス及びESRの周波数特性のシミュレーション結果を示す図である。 20

【図9】第4実施形態に係る等価回路を示す図である。

【図10】図9に示す等価回路を有する貫通型コンデンサの構成を示す図である。

【図11】抵抗素子の構成を示す図である。

【図12】図9に示す等価回路のSパラメータの周波数特性のシミュレーション結果を示す図である。

【図13】Sパラメータの測定回路を示す図である。

【図14】図9に示す等価回路におけるインピーダンス及びESRの周波数特性のシミュレーション結果を示す図である。

【図15】インピーダンス及びESRの測定回路を示す図である。 30

【発明を実施するための形態】

【0013】

以下、添付図面を参照して、本発明の好適な実施形態について詳細に説明する。なお、図面の説明において同一又は相当要素には同一符号を付し、重複する説明は省略する。

【0014】

[第1実施形態]

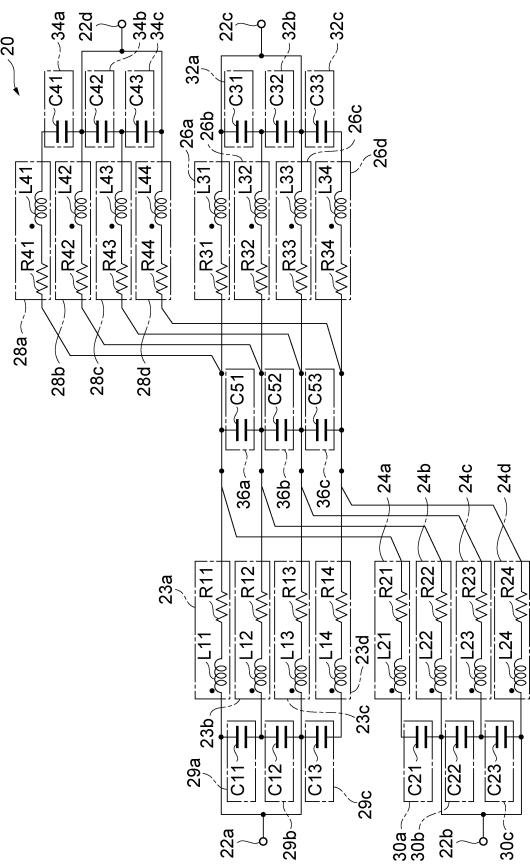

図1は、第1実施形態に係る等価回路を示す図である。図1に示す等価回路1は、例えば、電子部品を用いた回路設計や分析のシミュレーションに用いられる回路であり、コンピュータにおいて実行される回路設計(分析)プログラムに適用される。

【0015】

図1に示すように、等価回路1は、第1端子3a及び第2端子3bと、内部電極部(第1回路部)5a～5dと、静電容量部(第2回路部)7a～7fと、を備えている。図1に示す等価回路1は、図2に示すように、誘電体層101が積層されてなる素体102と、素体102内に配置された2層の第1内部電極104a, 104c及び2層の第2内部電極104b, 104dと、第1内部電極104a, 104cに接続された第1端子電極106aと、第2内部電極104b, 104dに接続された第2端子電極106bと、を備える積層型コンデンサ100の等価回路である。第1内部電極104a, 104cと第2内部電極104b, 104dとは、交互に配置されている。第1端子3aは、第1端子電極106aに相当し、第2端子3bは、第2端子電極106bに相当する。内部電極部5a～5dは、第1内部電極104a, 104c及び第2内部電極104b, 104dに 40

相当する。

【0016】

内部電極部 5 a ~ 5 d は、積層型コンデンサ 100 の内部電極 104 a ~ 104 d を示している。内部電極部 5 a ~ 5 d は、4 つ設けられている。これは、積層型コンデンサ 100 において、内部電極 104 a ~ 104 d が 4 層配置されていることを示している。内部電極部 5 a, 5 c は、第 1 端子 3 a に接続されている。つまり、内部電極部 5 a, 5 c は、第 1 内部電極 104 a, 104 c に相当する。内部電極部 5 b, 5 d は、第 2 端子 3 b に接続されている。つまり、内部電極部 5 b, 5 d は、第 2 内部電極 104 b, 104 d に相当する。

【0017】

内部電極部 5 a は、インダクタンス素子（インダクタンス成分）L 1 と、抵抗素子 R 1 と、を有している。インダクタンス素子 L 1 と抵抗素子 R 1 とは、直列に接続されており、R L 直列回路を構成している。インダクタンス素子 L 1 は、内部電極や接続導体などによる寄生インダクタンスを表している。抵抗素子 R 1 は、内部電極や接続導体などの導体損失を表している。

【0018】

内部電極部 5 b は、インダクタンス素子 L 2 と、抵抗素子 R 2 と、を有している。内部電極部 5 c は、インダクタンス素子 L 3 と、抵抗素子 R 3 と、を有している。内部電極部 5 d は、インダクタンス素子 L 4 と、抵抗素子 R 4 と、を有している。

【0019】

静電容量部 7 a ~ 7 f は、積層型コンデンサ 100 の静電容量を示している。静電容量部 7 a ~ 7 f は、内部電極部 5 a ~ 5 d の間に配置されている。具体的には、内部電極部 5 a と内部電極部 5 b との間には、静電容量部 7 a と静電容量部 7 d とが配置されている。すなわち、静電容量部 7 a, 7 d は、内部電極部 5 a, 5 b により発生する静電容量を表している。

【0020】

同様に、内部電極部 5 b と内部電極部 5 c との間には、静電容量部 7 b と静電容量部 7 e とが配置されている。すなわち、静電容量部 7 b, 7 e は、内部電極部 5 b, 5 c により発生する静電容量を表している。内部電極部 5 c と内部電極部 5 d との間には、静電容量部 7 c と静電容量部 7 f とが配置されている。すなわち、静電容量部 7 c, 7 f は、内部電極部 5 c, 5 d により発生する静電容量を表している。各静電容量部 7 a ~ 7 f は、キャパシタンス素子 C 1, C 2, C 3, C 4, C 5, C 6 をそれぞれ有している。

【0021】

本実施形態では、内部電極部 5 a ~ 5 d において、インダクタンス素子 L 1 ~ L 4 間に相互インダクタンスが設定されている。詳細には、インダクタンス素子 L 1 とインダクタンス素子 L 2 との結合係数 K 1、インダクタンス素子 L 1 とインダクタンス素子 L 3 との結合係数 K 2、インダクタンス素子 L 1 とインダクタンス素子 L 4 との結合係数 K 3、インダクタンス素子 L 2 とインダクタンス素子 L 3 との結合係数 K 4、インダクタンス素子 L 2 とインダクタンス素子 L 4 との結合係数 K 5、及び、インダクタンス素子 L 3 とインダクタンス素子 L 4 との結合係数 K 6 が設定されている。各結合係数 K 1 ~ K 6 は、実製品の積層型コンデンサの特性に応じて適宜設定される。

【0022】

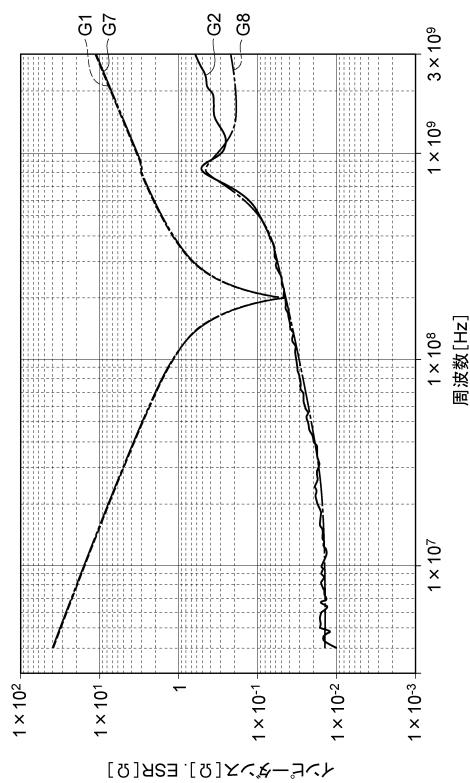

図 3 は、図 1 に示す等価回路におけるインピーダンス及び ESR の周波数特性のシミュレーション結果を示す図である。図 4 は、比較例の等価回路におけるインピーダンス及び ESR の周波数特性のシミュレーション結果を示す図である。図 3 及び図 4 では、縦軸はインピーダンス [ ]、ESR (等価直列抵抗) [ ] を示し、横軸は周波数 [ Hz ] を示している。また、図 3 及び図 4 では、実製品の積層型コンデンサのインピーダンスの実測値を G 1、ESR の実測値を G 2 で示し、本実施形態の等価回路 1 におけるインピーダンスを G 3, G 5、ESR を G 4, G 6 で示している。

【0023】

10

20

30

40

50

図3に示すように、実製品の積層型コンデンサでは、グラフG1で示されるように、周波数が200MHz付近でインピーダンスが極小値となっている。これは、コンデンサの静電容量によるリアクタンスと等価直列インダクタンスによるインダクタンスとが打ち消し合い、合計のリアクタンス値がゼロになるためである。また、実製品の積層型コンデンサでは、グラフG2で示されるように、周波数が800MHz付近でESRのピークが発生している。これは、内部共振によるものである。これに対して、等価回路1では、グラフG3で示されるように、周波数が200MHz付近でインピーダンスが極小値となっており、グラフG4で示されるように、周波数800MHz付近でESRのピークが発生している。つまり、等価回路1では、実製品の積層型コンデンサの実測値と略同等の特性を得ることができる。

10

#### 【0024】

一方、図4に示すように、インダクタンス素子L1～L4において相互インダクタンスを設定していない（結合係数K1～K6を0に設定した）回路では、グラフG5、G6で示されるように、実製品の積層型コンデンサの特性（グラフG1、G2）とは異なる特性を示している。比較例の等価回路では、実製品の積層型コンデンサで生じる内部共振現象が適切に再現されないため、実製品の積層型コンデンサとは異なる特性を示している。したがって、等価回路1のインダクタンス素子L1～L4において相互インダクタンス（結合係数K1～K6）を設定することの有効性が確認された。

#### 【0025】

以上説明したように、本実施形態に係る等価回路1は、内部電極部5a～5dを備えている。このように、等価回路1では、内部電極部（内部電極）を3以上（本実施形態では4個）備えることにより、ある所定の周波数において内部共振現象が生じる。このとき、各内部電極部5a～5dには、通常よりも大きい電流（共振電流）が流れることになる。共振電流が損失を有する内部電極に流れると、等価回路1全体のインピーダンス特性において損失のピークとして現れる。したがって、図2に示すように、等価回路1では、実製品の積層型コンデンサの特性に近づけることができる。

20

#### 【0026】

また、本実施形態の等価回路1では、インダクタンス素子L1～L4の間に相互インダクタンスが設定されている。これにより、等価回路1では、実製品の積層コンデンサにおいて生じる物理現象（内部電極間の電流のアンバランスや内部電極間で生じる共振現象）が実現可能となる。したがって、等価回路1では、実製品の積層型コンデンサの特性に近似する特性を得ることができる。

30

#### 【0027】

##### [第2実施形態]

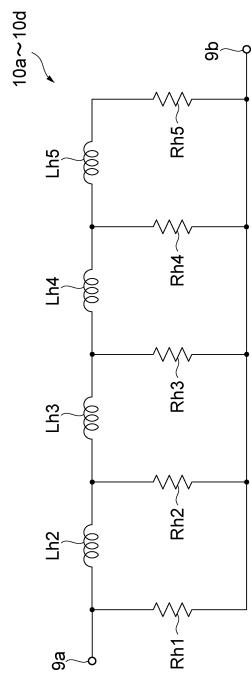

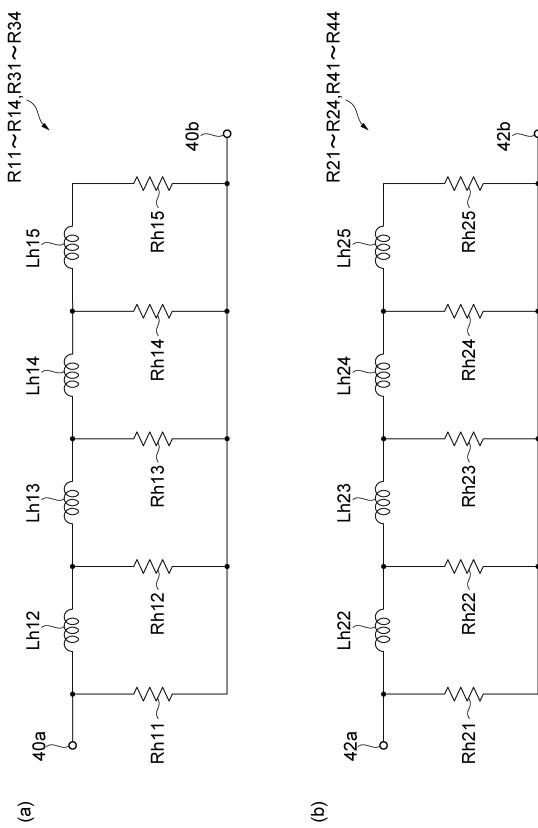

続いて、第2実施形態について説明する。第2実施形態に係る等価回路は、内部電極部5a～5dの抵抗素子R1～R4に替えて抵抗部（抵抗成分）10a～10dを備える点で第1実施形態と異なっている。図5は、第2実施形態に係る等価回路における内部電極部の抵抗部の構成を示す回路図である。

#### 【0028】

図5に示すように、抵抗部（抵抗成分）10aは、インダクタンス素子Lh2～Lh5と、抵抗素子Rh1～Rh5と、を備えている。インダクタンス素子Lh2、Lh3、Lh4、Lh5は、この順番に直列に接続されている。インダクタンス素子Lh2の一端は、端子9aに接続されている。本実施形態では、インダクタンス素子Lh2～Lh5を4個、抵抗素子Rh1～Rh5を5個用いているが、インダクタンス素子及び抵抗素子の数は、設計に応じて適宜設定されればよい。

40

#### 【0029】

抵抗素子Rh1は、その一端がインダクタンス素子Lh2の一端（端子9a）に接続され、その他端が端子9bに接続されている。抵抗素子Rh2は、その一端がインダクタンス素子Lh2の他端で且つインダクタンス素子Lh3の一端に接続され、その他端が端子9bに接続されている。すなわち、インダクタンス素子Lh2の両端部に対して、抵抗素

50

子 R h 1 及び抵抗素子 R h 2 の一端が接続されている。抵抗素子 R h 3 は、その一端がインダクタンス素子 L h 3 の他端で且つインダクタンス素子 L h 4 の一端に接続され、その他端が端子 9 b に接続されている。抵抗素子 R h 4 は、その一端がインダクタンス素子 L h 4 の他端で且つインダクタンス素子 L h 5 の一端に接続され、その他端が端子 9 b に接続されている。抵抗素子 R h 5 は、その一端がインダクタンス素子 L h 5 の他端に接続され、その他端が端子 9 b に接続されている。2つのインダクタンス素子と1つの抵抗素子は、T型回路を構成している。抵抗部 10 b ~ 10 d についても、抵抗部 10 a と同様の構成を有している。

#### 【 0 0 3 0 】

図 6 は、図 5 に示す抵抗部を備えた等価回路におけるインピーダンス及び ESR の周波数特性のシミュレーション結果を示す図である。図 6 では、縦軸はインピーダンス [ ] 、 ESR (等価直列抵抗) [ ] を示し、横軸は周波数 [ Hz ] を示している。図 6 では、実製品の積層型コンデンサのインピーダンスの実測値を G 1 、 ESR の実測値を G 2 で示し、本実施形態の等価回路におけるインピーダンスを G 7 、 ESR を G 8 で示している。

#### 【 0 0 3 1 】

図 6 に示すように、内部電極部 5 a ~ 5 d において抵抗部 10 a ~ 10 d を備える等価回路では、グラフ G 7 , G 8 で示されるように、周波数が 1 GHz 以下の帯域において、実製品の積層型コンデンサの実測値 (グラフ G 1 , G 2 ) と略同等の特性を得られており、周波数 800 MHz 付近で生じる ESR のピークもモデル化が図られている。周波数が 1 GHz 以上の帯域において実測値と差異が生じている点について、実製品の積層型コンデンサでは、多数の内部電極が設けられており、内部電極間において高次の共振が生じている。本実施形態の等価回路では、内部電極部 5 a ~ 5 d により 4 層の内部電極を備えた構成となっているため、1次共振のみがモデル化されている。そのため、本実施形態の等価回路において内部電極部の数を増やすことにより、周波数が 1 GHz 以上の帯域においても実測値に近づけることが可能となる。

#### 【 0 0 3 2 】

以上説明したように、第 2 実施形態に係る等価回路では、抵抗部 10 a ~ 10 d は、直列に接続されたインダクタンス素子 L h 2 ~ L h 5 と、抵抗素子 R h 1 ~ R h 5 とから構成されている。実製品の積層型コンデンサでは、高周波になるほど、表皮効果により導体の抵抗が増加する。本実施形態では、内部電極で生じる損失をより詳細に実現するために、抵抗部 10 a ~ 10 d を、インダクタンス素子 L h 2 ~ L h 5 及び抵抗素子 R h 1 ~ R h 5 により構成している。これにより、表皮効果を考慮した等価回路を構成できる。したがって、高周波における抵抗成分が大きくなり、実製品の積層型コンデンサの特性に更に近似させることができる。

#### 【 0 0 3 3 】

##### [ 第 3 実施形態 ]

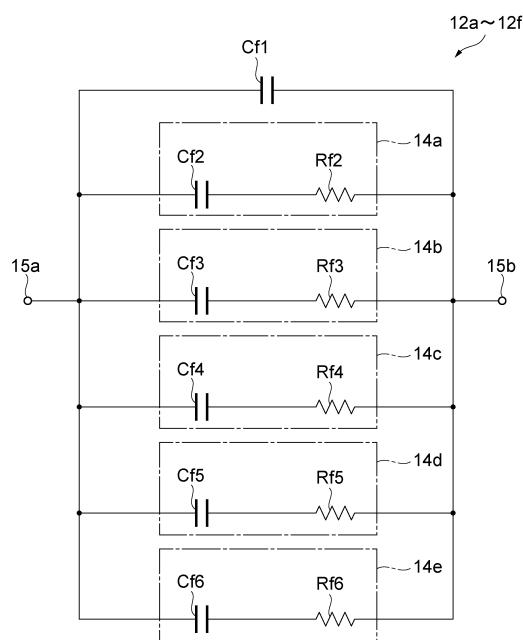

続いて、第 3 実施形態について説明する。第 3 実施形態に係る等価回路は、静電容量部 7 a ~ 7 f のキャパシタンス素子 C 1 ~ C 6 に替えて静電容量回路 12 a ~ 12 f を備える点で第 1 実施形態と異なっている。この等価回路において、内部電極部 5 a ~ 5 d の構成は、第 2 実施形態と同様である。すなわち、内部電極部 5 a ~ 5 d は、抵抗部 10 a ~ 10 d を備えている。図 7 は、第 3 実施形態に係る等価回路の静電容量部の静電容量回路の構成を示す回路図である。

#### 【 0 0 3 4 】

図 7 に示すように、静電容量回路 12 a ~ 12 f は、キャパシタンス素子 (第 1 容量素子) C f 1 と、CR 直列回路 14 a ~ 14 e と、を備えている。CR 直列回路 14 a は、キャパシタンス素子 (第 2 容量素子) C f 2 と、抵抗素子 R f 2 とが直列に接続されている。同様に、CR 直列回路 14 b ~ 14 e は、キャパシタンス素子 C f 3 ~ C f 6 と、抵抗素子 R f 3 ~ R f 6 とが直列に接続されている。CR 直列回路 14 a ~ 14 e は、1 以上設けられており、本実施形態では、5 個設けられている。CR 直列回路の数は、設計に

10

20

30

40

50

応じて適宜設定されればよい。

【0035】

キャパシタンス素子C f 1とCR直列回路14a～14eとは、並列に接続されている。詳細には、キャパシタンス素子C f 1は、その一端が端子15aに接続され、その他端が端子15bに接続されている。CR直列回路14aは、キャパシタンス素子C f 2の一端が端子15aに接続され、抵抗素子R f 2の他端が端子15bに接続されている。CR直列回路14b～14eについても同様である。

【0036】

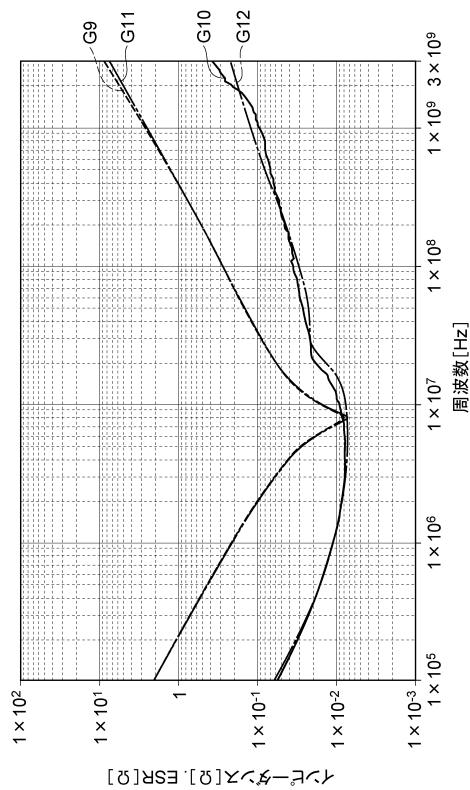

図8は、図7に示す静電容量回路を備えた等価回路におけるインピーダンス及びESRの周波数特性のシミュレーション結果を示す図である。図8では、縦軸はインピーダンス [ ]、ESR(等価直列抵抗) [ ]を示し、横軸は周波数 [ Hz ]を示している。図8では、実製品の積層型コンデンサのインピーダンスの実測値をG9、ESRの実測値をG10で示し、本実施形態の等価回路におけるインピーダンスをG11、ESRをG12で示している。

【0037】

図8に示すように、静電容量回路12a～12fを備える等価回路では、グラフG11、G12で示されるように、周波数が1GHzの以下の帯域において、実製品の積層型コンデンサの実測値(グラフG9、G10)と略同等の特性を得られている。実測値では、20MHz付近においてESRのピークが発生しているが、この等価回路においても、20MHz付近においてESRのピークが発生している。また、周波数が1MHz以下の帯域において、実製品の積層型コンデンサでは、誘電損失によりESRが周波数に反比例する特性を有しているが、この等価回路においても、実製品の積層型コンデンサと同様の特性が得られている。

【0038】

以上説明したように、第3実施形態に係る等価回路では、静電容量部7a～7fの静電容量回路12a～12fは、キャパシタンス素子C f 1とCR直列回路14a～14eとが並列に接続された構成を有している。このように静電容量回路12a～12fを構成することにより、誘電損失を考慮することが可能となり、低周波側における静電容量の成分を大きく且つ抵抗成分を小さくできる。また、この等価回路では、内部電極で生じる損失をより詳細に実現するために、抵抗部10a～10dを設けている。したがって、この等価回路では、内部電極において生じる表皮効果による損失と、誘電体によって生じる誘電体損の影響を考慮しているため、実製品の積層コンデンサの特性をより詳細にモデル化することができる。

【0039】

[第4実施形態]

続いて、第4実施形態について説明する。図9は、第4実施形態に係る等価回路を示す図である。図9に示すように、等価回路20は、第1端子22a、第2端子22b、第3端子22c及び第4端子22dと、内部電極部23a～23d、内部電極部24a～24d、内部電極部26a～26d及び内部電極部28a～28dと、静電容量部29a～29c、静電容量部30a～30c、静電容量部32a～32c、静電容量部34a～34c及び静電容量部36a～36cと、を備えている。

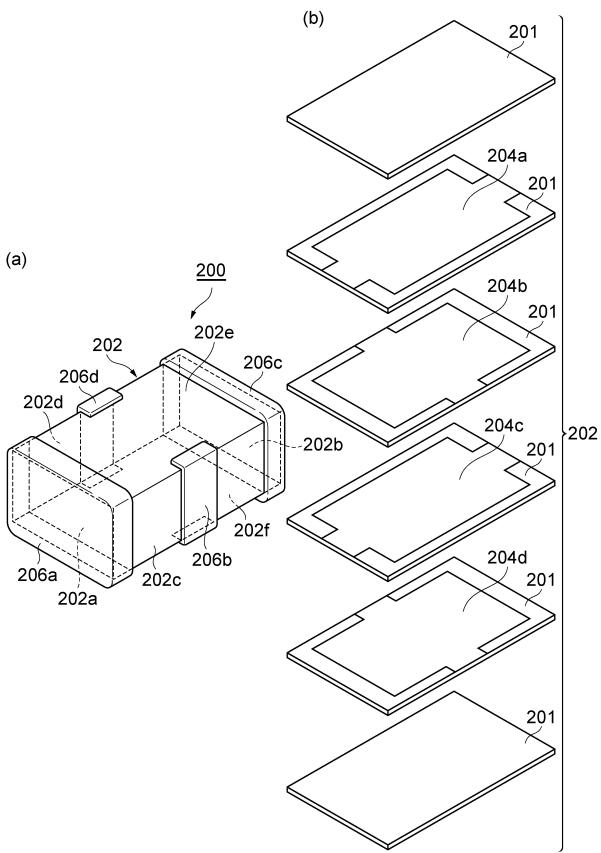

【0040】

図9に示す等価回路20は、図10に示すように、誘電体層201が積層されていると共に直方体形状を成し、長手方向で対向する一対の端面202a、202b、幅方向で対向する一対の側面202c、202d及び高さ方向で対向する一対の主面202e、202fを有する素体202と、素体202内に配置された第1～第4内部電極204a～204dと、第1内部電極204a及び第3内部電極204cに接続され且つ素体202の端面202a、202bにそれぞれ配置された第1端子電極206a及び第3端子電極206cと、第2内部電極204b及び第4内部電極204dに接続され且つ素体202の側面202c、202dにそれぞれ配置された第2端子電極206b及び第4端子電極206dと、

10

20

30

40

50

06dと、を備える貫通型コンデンサ200の等価回路である。第1端子22aは、第1端子電極206aに相当し、第2端子22bは、第2端子電極206bに相当する。第3端子22cは、第3端子電極206cに相当し、第4端子22dは、第4端子電極206dに相当する。

【0041】

この貫通型コンデンサ200では、第1端子電極206a及び第3端子電極206cが第1内部電極204a及び第3内部電極204cを介して導通しており、第2端子電極206b及び第4端子電極206dが第2内部電極204b及び第4内部電極204dを介して導通しており、第1端子電極206a及び第3端子電極206cと第2端子電極206b及び第4端子電極206dとの間に静電容量を有している。貫通型コンデンサ200は、第1端子電極206aと第3端子電極206cとの間に信号を通し、第2端子電極206bと第4端子電極206dを回路のグランドに接続して使用される。これにより、貫通型コンデンサ200では、第1端子電極206aと第3端子電極206cを通過する信号成分に含まれる高周波ノイズが第2端子電極206b及び第4端子電極206dを介してグランドに流れるため、第1端子電極206a及び第3端子電極206cを通過する高周波ノイズを除去できる。

【0042】

内部電極部23a～23d、内部電極部24a～24d、内部電極部26a～26d及び内部電極部28a～28dは、貫通型コンデンサ200の内部電極204a～204dを示している。内部電極部23a～23d、内部電極部24a～24d、内部電極部26a～26d及び内部電極部28a～28dは、それぞれ4つ設けられている。これは、貫通型コンデンサ200において、内部電極204a～204dが4層配置されていることを示している。

【0043】

内部電極部23a、内部電極部24a、内部電極部26a及び内部電極部28aは、第1内部電極204aに相当する。内部電極部23a及び内部電極部26aは、第1端子22a及び第3端子22cに接続されている。内部電極部23b、内部電極部24b、内部電極部26b及び内部電極部28bは、第2内部電極204bに相当する。内部電極部24b及び内部電極部28bは、第2端子22b及び第4端子22dに接続されている。

【0044】

内部電極部23c、内部電極部24c、内部電極部26c及び内部電極部28cは、第3内部電極204cに相当する。内部電極部23c及び内部電極部26cは、第1端子22a及び第3端子22cに接続されている。内部電極部23d、内部電極部24d、内部電極部26d及び内部電極部28dは、第4内部電極204dに相当する。内部電極部24d及び内部電極部28dは、第2端子22b及び第4端子22dに接続されている。

【0045】

内部電極部23aは、インダクタンス素子L11と、抵抗部R11と、を有している。インダクタンス素子L11と抵抗部R11とは、直列に接続されており、RL直列回路を構成している。内部電極部23bは、インダクタンス素子L12と、抵抗部R12と、を有している。内部電極部23cは、インダクタンス素子L13と、抵抗部R13と、を有している。内部電極部23dは、インダクタンス素子L14と、抵抗部R14と、を有している。

【0046】

内部電極部24aは、インダクタンス素子L21と、抵抗部R21と、を有している。インダクタンス素子L21と抵抗部R21とは、直列に接続されており、RL直列回路を構成している。内部電極部24bは、インダクタンス素子L22と、抵抗部R22と、を有している。内部電極部24cは、インダクタンス素子L23と、抵抗部R23と、を有している。内部電極部24dは、インダクタンス素子L24と、抵抗部R24と、を有している。

【0047】

10

20

30

40

50

内部電極部 26a は、インダクタンス素子 L31 と、抵抗部 R31 と、を有している。インダクタンス素子 L31 と抵抗部 R31 とは、直列に接続されており、RL 直列回路を構成している。内部電極部 26b は、インダクタンス素子 L32 と、抵抗部 R32 と、を有している。内部電極部 26c は、インダクタンス素子 L33 と、抵抗部 R33 と、を有している。内部電極部 26d は、インダクタンス素子 L34 と、抵抗部 R34 と、を有している。

#### 【0048】

内部電極部 28a は、インダクタンス素子 L41 と、抵抗部 R41 と、を有している。インダクタンス素子 L41 と抵抗部 R41 とは、直列に接続されており、RL 直列回路を構成している。内部電極部 28b は、インダクタンス素子 L42 と、抵抗部 R42 と、を有している。内部電極部 28c は、インダクタンス素子 L43 と、抵抗部 R43 と、を有している。内部電極部 28d は、インダクタンス素子 L44 と、抵抗部 R44 と、を有している。

#### 【0049】

図 11(a) に示すように、抵抗部 R11 ~ R14, R31 ~ R34 のそれぞれは、抵抗素子 Rh11 ~ Rh15 と、インダクタンス素子 Lh12 ~ Lh15 と、を備えている。インダクタンス素子 Lh12, Lh13, Lh14, Lh15 は、この順番に直列に接続されている。インダクタンス素子 Lh12 の一端は、端子 40a に接続されている。

#### 【0050】

抵抗素子 Rh11 は、その一端がインダクタンス素子 Lh12 の一端 (端子 40a) に接続され、その他端が端子 40b に接続されている。抵抗素子 Rh12 は、その一端がインダクタンス素子 Lh12 の他端で且つインダクタンス素子 Lh13 の一端に接続され、その他端が端子 40b に接続されている。抵抗素子 Rh13 は、その一端がインダクタンス素子 Lh13 の他端で且つインダクタンス素子 Lh14 の一端に接続され、その他端が端子 40b に接続されている。抵抗素子 Rh14 は、その一端がインダクタンス素子 Lh14 の他端で且つインダクタンス素子 Lh15 の一端に接続され、その他端が端子 40b に接続されている。抵抗素子 Rh15 は、その一端がインダクタンス素子 Lh15 の他端に接続され、その他端が端子 40b に接続されている。2つのインダクタンス素子と1つの抵抗素子は、T型回路を構成している。

#### 【0051】

図 11(b) に示すように、抵抗部 R21 ~ R24, R41 ~ R44 は、抵抗素子 Rh21 ~ Rh25 と、インダクタンス素子 Lh22 ~ Lh25 と、を備えている。インダクタンス素子 Lh22, Lh23, Lh24, Lh25 は、この順番に直列に接続されている。インダクタンス素子 Lh22 の一端は、端子 42a に接続されている。

#### 【0052】

抵抗素子 Rh21 は、その一端がインダクタンス素子 Lh22 の一端 (端子 42a) に接続され、その他端が端子 42b に接続されている。抵抗素子 Rh22 は、その一端がインダクタンス素子 Lh22 の他端で且つインダクタンス素子 Lh23 の一端に接続され、その他端が端子 42b に接続されている。抵抗素子 Rh23 は、その一端がインダクタンス素子 Lh23 の他端で且つインダクタンス素子 Lh24 の一端に接続され、その他端が端子 42b に接続されている。抵抗素子 Rh24 は、その一端がインダクタンス素子 Lh24 の他端で且つインダクタンス素子 Lh25 の一端に接続され、その他端が端子 42b に接続されている。抵抗素子 Rh25 は、その一端がインダクタンス素子 Lh25 の他端に接続され、その他端が端子 42b に接続されている。2つのインダクタンス素子と1つの抵抗素子は、T型回路を構成している。

#### 【0053】

ここで、貫通型コンデンサ 200 の内部電極 204a ~ 204d は、長方形形状を呈している。そのため、内部電極 204a ~ 204d の長手方向と幅方向とでは、回路パラメータが異なる。本実施形態では、内部電極部 23a ~ 23d 及び内部電極部 26a ~ 26d は、内部電極の長手方向 (横方向) に対する回路パラメータである。内部電極部 24a

10

20

30

40

50

～24d及び内部電極部28a～28dは、内部電極の幅方向（縦方向）に対する回路パラメータである。

【0054】

静電容量部29a～29c、静電容量部30a～30c、静電容量部32a～32c、静電容量部34a～34c及び静電容量部36a～36cは、貫通型コンデンサの静電容量を示している。静電容量部29a、静電容量部30a、静電容量部32a、静電容量部34a及び静電容量部36aは、第1内部電極と第2内部電極との静電容量を示している。静電容量部29b、静電容量部30b、静電容量部32b、静電容量部34b及び静電容量部36bは、第2内部電極と第3内部電極との静電容量を示している。静電容量部29c、静電容量部30c、静電容量部32c、静電容量部34c及び静電容量部36cは、第3内部電極と第4内部電極との静電容量を示している。10

【0055】

各静電容量部29a～29cは、静電容量回路C11、C12、C13をそれぞれ有している。各静電容量部30a～30cは、静電容量回路C21、C22、C23をそれぞれ有している。各静電容量部32a～32cは、静電容量回路C31、C32、C33をそれぞれ有している。各静電容量部34a～34cは、静電容量回路C41、C42、C43をそれぞれ有している。各静電容量部36a～36cは、静電容量回路C51、C52、C53をそれぞれ有している。

【0056】

静電容量回路C11～C13、静電容量回路C21～C23、静電容量回路C31～C33、静電容量回路C41～C43及び静電容量回路C51～53は、図7に示す静電容量回路12aと同様の構成を有している。すなわち、静電容量回路C11～C13、静電容量回路C21～C23、静電容量回路C31～C33、静電容量回路C41～C43及び静電容量回路C51～53のそれぞれは、キャパシタンス素子Cf1と、CR直列回路14a～14eと、を備えている。CR直列回路14aは、キャパシタンス素子Cf2と、抵抗素子Rf2とが直列に接続されている。同様に、CR直列回路14b～14eは、キャパシタンス素子Cf3～Cf6と、抵抗素子Rf3～Rf6とが直列に接続されている。20

【0057】

本実施形態では、内部電極部23a～23d及び内部電極部26a～26dにおいて、インダクタンス素子L11～L14及びL31～L34間に相互インダクタンスが設定されている。内部電極部24a～24d及び内部電極部28a～28dにおいて、インダクタンス素子L21～L24及びL41～L44間に相互インダクタンスが設定されている。各インダクタンス素子間の結合係数は、実製品の貫通型コンデンサの特性に応じて適宜設定される。30

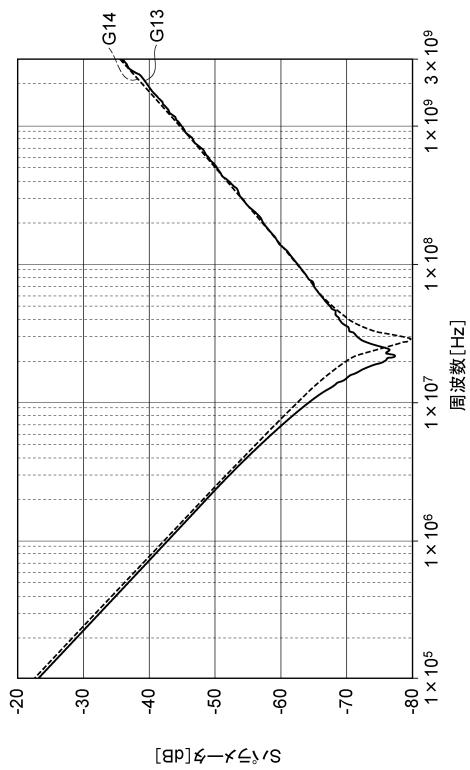

【0058】

図12は、図9に示す等価回路におけるSパラメータの周波数特性のシミュレーション結果を示す図である。図12では、縦軸はSパラメータ[dB]を示し、横軸は周波数[Hz]を示している。図12では、実製品の貫通型コンデンサのSパラメータの実測値をG13で示し、本実施形態の等価回路20におけるSパラメータをG14で示している。40

【0059】

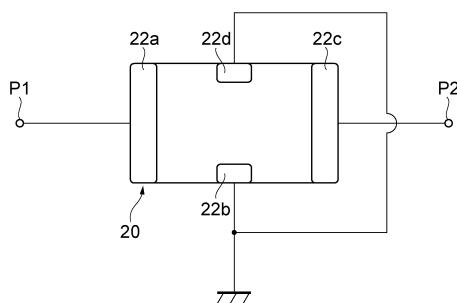

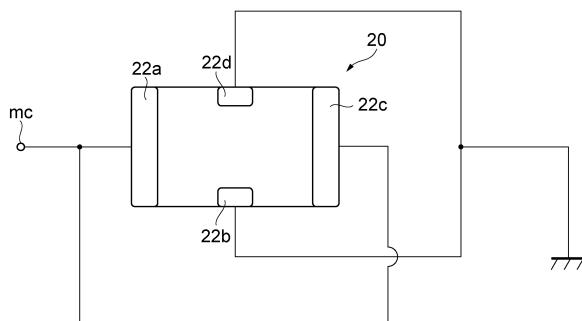

ここで、Sパラメータの測定方法について説明する。図13は、Sパラメータの測定回路を示す図である。図13では、等価回路20を貫通型コンデンサに適用した場合について示している。図13に示すように、貫通型コンデンサのSパラメータを測定する場合には、第1端子22aをポートP1に接続し、第3端子22cをポートP2に接続する。第2端子22b及び第4端子22dは、グラウンドに接続する。Sパラメータとして、ポートP1からポートP2への伝送特性S<sub>21</sub>を測定した。結果を図12に示す。

【0060】

図12に示すように、等価回路20では、グラフG14に示されるように、極小値において実製品の貫通型コンデンサ（グラフG13）と多少の差異はあるものの、実製品の貫50

通型コンデンサと近似する伝送特性が得られている。

【0061】

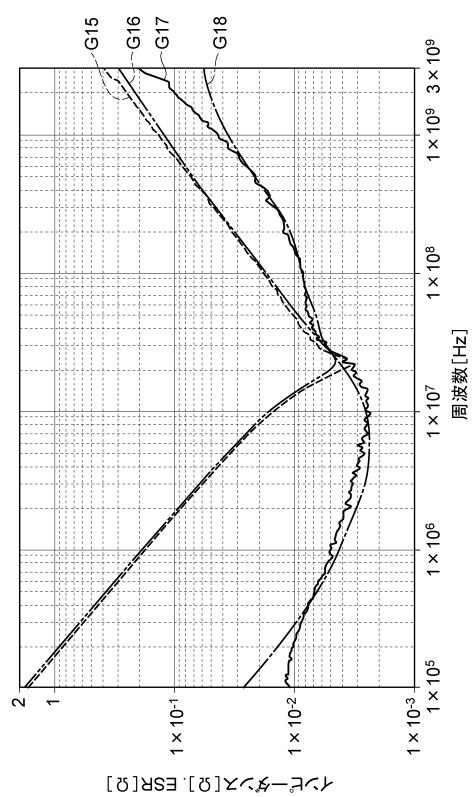

図14は、図9に示す等価回路におけるインピーダンス及びESRの周波数特性のシミュレーション結果を示す図である。図14では、縦軸はインピーダンス[ ]、ESR[ ]を示し、横軸は周波数[Hz]を示している。図14では、実製品の貫通型コンデンサのインピーダンスの実測値をG15、ESRの実測値をG16で示し、本実施形態の等価回路20におけるインピーダンスをG17、ESRをG18で示している。

【0062】

ここで、貫通型コンデンサのインピーダンス及びESR特性の測定方法について説明する。図15は、インピーダンス及びESRの測定回路を示す図である。図15では、等価回路20を貫通型コンデンサに適用した場合について示している。図15に示すように、インピーダンス及びESRを測定する場合には、第1端子22a及び第3端子22cを測定端子mcに接続し、第2端子22b及び第4端子22dをグランドに接続する。測定端子mcとグランドとの間のインピーダンス及びESRを測定した。

【0063】

図14に示すように、等価回路20では、グラフG17、G18で示されるように、1GHz以下の周波数帯域において、実製品の貫通型コンデンサの実測値(グラフG15、G16)に近似する特性を得られている。

【0064】

以上説明したように、本実施形態に係る等価回路20は、貫通型コンデンサ200の構成を有している。貫通型コンデンサ200では、第2端子電極206b及び第4端子電極206dをグランドに接続すると、第2端子電極206b及び第4端子電極206dに接続された第2内部電極204b及び第4内部電極204dでは、第2端子電極206bと第4端子電極206dに向かって、同じ大きさで互いに逆方向のノイズ電流が流れる。このとき、第2端子電極206bに向かう電流により生じる磁束と、第4端子電極206dに向かう電流により生じる磁束とは、互いに打ち消し合う。これにより、貫通型コンデンサ200では、ESL(等価直列インダクタンス)を低減することができる。本実施形態に係る等価回路20は、貫通型コンデンサ200の構成をモデル化しており、インダクタンス素子L11～L14、L21～L24、L31～L34、L41～L44において相互インダクタンスを設定している。これにより、等価回路20では、貫通型コンデンサ200と同等の特性を得ることができ、貫通型コンデンサ200における磁束の打ち消しの効果のモデル化を図れる。

【0065】

本発明は、上記実施形態に限定されるものではない。例えば、上記実施形態では、4層の内部電極を有する積層型コンデンサ(貫通型コンデンサ)の構成を一例に説明したが、内部電極の数は設計に応じて適宜設定されればよい。

【符号の説明】

【0066】

1, 20...等価回路、5a～5d, 23a～23d, 24a～24d, 26a～26d, 28a～28d...内部電極部(第1回路部)、7a～7f, 29a～29c, 30a～30c, 32a～32c, 34a～34c, 36a～36c...静電容量部(第2回路部)、10a～10d, R11～R14, R21～R24, R31～R34, R41～R44...抵抗部(抵抗成分)、14a～14e...CR直列回路(直列回路)、22a～22d...第1～第4端子、Cf1...キャパシタンス素子(第1容量素子)、Cf2～Cf6...キャパシタンス素子(第2容量素子)、L1～L4, L11～L14, L21～L24, L31～L34, L41～L44...インダクタンス素子(インダクタンス成分)、Lh2～Lh5, Lh12～Lh15, Lh22～Lh25...インダクタンス素子、Rh1～Rh5, Rh11～Rh15, Rh21～Rh25...抵抗素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

審査官 松田 直也

(56)参考文献 特開2013-186611(JP, A)

特開2013-228997(JP, A)

特開2002-259482(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 17 / 50