(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6014748号

(P6014748)

(45) 発行日 平成28年10月25日(2016.10.25)

(24) 登録日 平成28年9月30日(2016.9.30)

(51) Int.Cl.

F 1

G 11 C 16/02 (2006.01)

G 11 C 17/00 6 1 1 E

G 11 C 16/06 (2006.01)

G 11 C 17/00 6 1 4

G 11 C 17/00 6 3 9 C

G 11 C 17/00 6 4 1

請求項の数 20 (全 13 頁)

(21) 出願番号 特願2015-505779 (P2015-505779)

(86) (22) 出願日 平成25年3月27日 (2013.3.27)

(65) 公表番号 特表2015-516640 (P2015-516640A)

(43) 公表日 平成27年6月11日 (2015.6.11)

(86) 國際出願番号 PCT/US2013/034160

(87) 國際公開番号 WO2013/154836

(87) 國際公開日 平成25年10月17日 (2013.10.17)

審査請求日 平成27年8月27日 (2015.8.27)

(31) 優先権主張番号 13/446,206

(32) 優先日 平成24年4月13日 (2012.4.13)

(33) 優先権主張国 米国(US)

(73) 特許権者 511242535

サンディスク テクノロジーズ エルエル

シー

アメリカ合衆国 75024、テキサス州

、ブラー、ノース ダラス パークウェ

イ 6900 ツー レガシー タウン

センター

Two Legacy Town Cen

ter, 6900 North Dal

las Parkway, Plano,

Texas 75024 United

States of America

(74) 代理人 110000110

特許業務法人快友国際特許事務所

最終頁に続く

(54) 【発明の名称】メモリのブロックに対してプログラミングステップサイズを調整するシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項 1】

方法であって、

メモリ装置のブロックに対応する誤り数がしきい値を満たすか否かを判断するとともに、前記ブロックの最後の消去からの読み出し回数と前記ブロックの書き込み／消去サイクル数との比較に基づいて、その誤り数が、主として加齢による誤りを示しているか、又は、主として読み出しディスターブによる誤りを示しているのか、を判断することと、

前記誤り数が主として加齢による誤りを示しているとする判断に応答して、前記ブロックに対するプログラミングステップサイズを第1の値から第2の値へ低減することと、

前記誤り数が、主として読み出しディスターブによる誤りを示しているとする判断に応答して、前記ブロックに対してリフレッシュ操作を遂行すること、を含む方法。

## 【請求項 2】

請求項1記載の方法において、

前記プログラミングステップサイズを低減することにより、前記ブロックの蓄積素子に書き込まれるしきい値電圧の分布が引き締まり、前記ブロックにデータをプログラムする際に誤りを減らすことが可能となる方法。

## 【請求項 3】

請求項1又は2記載の方法において、

前記ブロックが複数のワード線を有し、各ワード線が複数の蓄積素子を有し、

前記誤り数は、前記ブロックのワード線内の蓄積素子から読み出されるデータの合計誤

り数を含む方法。

【請求項 4】

請求項 1 ~ 3 のいずれか一項記載の方法において、

第 2 の値を表から選択することをさらに含む方法。

【請求項 5】

請求項 4 記載の方法において、

前記表は、前記メモリ装置のメモリ内にある方法。

【請求項 6】

請求項 4 記載の方法において、

前記表は、前記メモリ装置のコントローラ内にある方法。

10

【請求項 7】

請求項 1 ~ 3 のいずれか一項記載の方法において、

第 1 の値に基づき第 2 の値を計算することをさらに含む方法。

【請求項 8】

請求項 1 ~ 7 のいずれか一項記載の方法において、

前記ブロックに対するリフレッシュ操作は、読み出し回数が書き込み / 消去サイクル数よりも大きいことを示す比較結果に基づいて遂行される方法。

【請求項 9】

請求項 1 ~ 8 のいずれか一項記載の方法において、

読み出し回数が書き込み / 消去サイクル数よりも小さいことを示す比較結果に少なくとも部分的にに基づいて、前記プログラミングステップサイズが第 1 の値から第 2 の値へ低減される方法。

20

【請求項 10】

請求項 1 ~ 9 のいずれか一項記載の方法において、

前記メモリ装置は、フラッシュメモリを含む方法。

【請求項 11】

データ蓄積装置であって、

メモリと、

コントローラと、を備え、

前記コントローラは、

30

前記メモリの或るブロックに対応する誤り数がしきい値を満たすか否かを判断するとともに、前記ブロックの最後の消去からの読み出し回数と前記ブロックの書き込み / 消去サイクル数との比較に基づいて、その誤り数が、主として加齢による誤りを示しているか、又は、主として読み出しディスクによる誤りを示しているのか、を判断し、

前記誤り数が主として加齢による誤りを示しているとする判断に応答して、前記ブロックに対するプログラミングステップサイズを第 1 の値から第 2 の値へ低減し、

前記誤り数が、主として読み出しディスクによる誤りを示しているとする判断に応答して、前記ブロックに対してリフレッシュ操作を遂行する、ように構成されるデータ蓄積装置。

【請求項 12】

請求項 11 記載のデータ蓄積装置において、

前記プログラミングステップサイズに従って前記ブロックにデータをプログラムするように構成された書き込み回路をさらに備えるデータ蓄積装置。

40

【請求項 13】

請求項 11 又は 12 記載のデータ蓄積装置において、

受信したしきい値データと受信した誤り数データに少なくとも部分的にに基づいて、前記プログラミングステップサイズを調整するように構成されたブロック単位プログラミング調整エンジンをさらに備えるデータ蓄積装置。

【請求項 14】

請求項 13 記載のデータ蓄積装置において、

50

前記ブロックから読み出されたデータに対して復号化操作を遂行し、かつ誤り数を前記ブロック単位プログラミング調整エンジンに提供するように構成された誤り訂正符号化エンジンをさらに備えるデータ蓄積装置。

【請求項 15】

請求項 13 又は 14 記載のデータ蓄積装置において、

誤り数は、前記ブロックの各ワード線のワード線誤り数の加算に基づく合計誤り数を含むデータ蓄積装置。

【請求項 16】

請求項 11 ~ 15 のいずれか一項記載のデータ蓄積装置において、

前記コントローラは、第 2 の値を表から選択するようにさらに構成されるデータ蓄積装置。 10

【請求項 17】

請求項 16 記載のデータ蓄積装置において、

前記表は、前記メモリ内にあるデータ蓄積装置。

【請求項 18】

請求項 16 記載のデータ蓄積装置において、

前記表は、前記コントローラ内にあるデータ蓄積装置。

【請求項 19】

請求項 11 ~ 18 のいずれか一項記載のデータ蓄積装置において、

前記コントローラは、読み出し回数が書き込み / 消去サイクル数よりも小さいことを示す比較結果に少なくとも部分的に基づいて、前記プログラミングステップサイズを第 1 の値から第 2 の値へ低減するように構成されるデータ蓄積装置。 20

【請求項 20】

請求項 11 ~ 19 のいずれか一項記載のデータ蓄積装置において、

前記コントローラは、読み出し回数が書き込み / 消去サイクル数よりも大きいことを示す比較結果に基づいて、前記ブロックに対してリフレッシュ操作を遂行するように構成されるデータ蓄積装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的に、メモリのブロックに対してプログラミングステップサイズを調整することに関する。

【背景技術】

【0002】

ユニバーサルシリアルバス (USB) フラッシュメモリ装置や取り外し可能なストレージカード等の不揮発性メモリ装置により、データやソフトウェアアプリケーションの可搬性は向上している。フラッシュメモリ装置は、個々のフラッシュメモリセルに複数のビットを蓄積することによってデータ蓄積密度と費用効率を向上させることができる。

【0003】

単一のフラッシュメモリセルで複数の情報ビットを蓄積することは、ビット列をフラッシュメモリセル状態にマップすることを通常含む。特定のフラッシュメモリセルにビット列を蓄積することが決定した後、フラッシュメモリセルはビット列に相当する状態までプログラムされ得る。小さいプログラミングステップサイズでフラッシュメモリセルをプログラムすると、プログラミングの精度は向上し得るが、プログラミングステップ数が増加し得るため、プログラミングの待ち時間が長くなる。大きいプログラミングステップサイズでフラッシュメモリセルをプログラムすると、プログラミングステップ数が減少し得るため、プログラミングの待ち時間は短くなるが、プログラミングの精度は低下する。一度メモリ装置内のメモリセルがプログラムされると、メモリセルのプログラミング状態を検知することにより、メモリセルからデータが読み出され得る。 40

【発明の概要】

10

20

30

40

50

## 【0004】

データ蓄積装置内のメモリの或るブロックに対するプログラミングステップのサイズは、そのブロックの誤り数がしきい値を満たすとする判断に少なくとも部分的に基づいて低減される。その結果、低減されたプログラミングステップサイズを用いてブロックの蓄積素子に書き込まれるしきい値電圧の分布を引き締めることができ、誤りを減らすとともにブロックにデータをプログラムすることが可能となる。「若い」メモリは通常、「老いた」メモリより誤りが少ない。このため、若いメモリのブロックは大きいプログラミングステップサイズでプログラムされ得る。

## 【0005】

大きいプログラミングステップサイズでブロックをプログラムすると、プログラミングステップ数が少なくなり得るため、プログラミングの待ち時間は短くなる。メモリの加齢にともない、ブロック内の蓄積素子から読み出されるデータの誤り数は通常増える。メモリの加齢にともない、誤り数がしきい値に達することに応じて低減されたプログラミングステップサイズでブロックをプログラムすれば、精度を向上させ、誤りを減らし、メモリの寿命を延ばし得る。

## 【図面の簡単な説明】

## 【0006】

【図1】メモリ装置の或るブロックに対して、そのブロックの誤り数に少なくとも部分的に基づいて、プログラミングステップサイズを第1の値から第2の値へ低減するシステムの第1の例証的な実施形態のブロック図である。

20

【図2】図1のメモリの或るブロックから読み出され得る1蓄積素子群の代表的な電圧特性を示し、かつプログラミングステップサイズの変更によるビット誤り訂正を示す概略図である。

【図3】メモリ装置の或るブロックに対して、そのブロックの誤り数に少なくとも部分的に基づいて、プログラミングステップサイズを第1の値から第2の値へ低減するシステムの第2の例証的な実施形態のブロック図である。

【図4】メモリ装置の或るブロックに対して、そのブロックの誤り数に少なくとも部分的に基づいて、プログラミングステップサイズを第1の値から第2の値へ低減する方法の一実施形態を示す流れ図である。

## 【発明を実施するための形態】

30

## 【0007】

データ蓄積装置内のメモリの或るブロックに対して、プログラミングステップサイズを第1の値から第2の値へ低減するシステムおよび方法が開示される。プログラミングステップサイズは、少なくとも部分的に、ブロックの誤り数がしきい値に達したという判断に応じて、低減される。（例えば、メモリの加齢にともない）プログラミングステップサイズを低減することにより、ブロックの蓄積素子に書き込まれるしきい値電圧の分布を引き締めることで、誤りを減らすとともにブロックにデータをプログラムすることが可能となり得る。

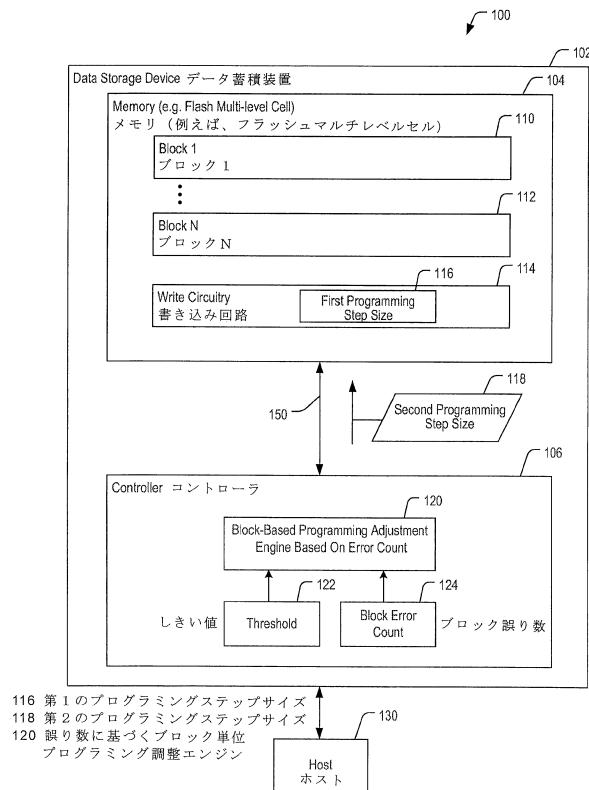

## 【0008】

図1を参照すると、メモリ装置の或るブロックに対して、そのブロックの誤り数に少なくとも部分的に基づいて、プログラミングステップサイズを第1の値から第2の値へ低減するように構成されたシステムの例証的な実施形態が示され、全体的に100と呼称されている。プログラミングステップサイズはまた、ブロックで行われたメモリ読み出し回数、ブロックの書き込み／消去サイクル数、またはこれらの組み合わせに基づき得る。システム100はホスト装置130へ結合されるデータ蓄積装置102を含む。データ蓄積装置102はバス150経由でコントローラ106へ結合されたメモリ104を含む。

40

## 【0009】

ホスト装置130は、メモリ104に蓄積されるべきデータを提供するように構成されるか、あるいはメモリ104から読み出すべきデータを要求するように構成され得る。例えば、ホスト装置130は、携帯電話機、音楽または映像再生機、ゲーム機、電子書籍リ

50

ーダ、個人用携帯情報端末（PDA）、ラップトップコンピュータ、ノートブックコンピュータ、タブレット等のコンピュータ、他の何らかの電子装置、またはこれらの組み合わせを含み得る。

#### 【0010】

データ蓄積装置102は、メモリカードであってよく、例えばSecure Digital（登録商標）（SD）カード、microSD（登録商標）カード、miniSD（登録商標）カード（デラウェア州ウィルミントンのSD-3CLLCの商標）、MultiMediaCard（登録商標）（MMC）カード（バージニア州アーリントンのJEDEC Solid State Technology Associationの商標）、またはCompactFlash（登録商標）（CF）カード（カリフォルニア州ミルピタスのサンディスクコーポレーションの商標）であってよい。別の例として、データ蓄積装置102は、ホスト装置130に組み込まれたメモリであってよく、例えば説明的な例として、eMMC（登録商標）（バージニア州アーリントンのJEDEC Solid State Technology Associationの商標）、ならびにeSDメモリであってよい。10

#### 【0011】

メモリ104は、フラッシュ装置（例えば、NANDフラッシュ装置、NORフラッシュ装置、またはその他の類のフラッシュ装置）の不揮発性メモリであってよい。メモリ104は、複数のブロック（例えば、第1の代表的なブロック110と第2の代表的なブロック112）を含む。メモリ104はまた、プログラミングステップサイズに従いブロック110、112のいずれか1つ以上にデータをプログラムするように構成された書き込み回路114を含む。例えば、書き込み回路114は、プログラミングステップサイズ（例えば、図2に関して詳述する第1のプログラミングステップサイズ116）を有する一連のプログラミングパルスにより、ブロック110、112のいずれか1つ以上にデータをプログラムし得る。書き込み回路114は、第1のプログラミングステップサイズ116をデフォルトのプログラミングステップサイズとして蓄積するように構成され得る。書き込み回路114は、別のプログラミングステップサイズ（例えば、第2のプログラミングステップサイズ118）をコントローラ106から受信し、デフォルトのプログラミングステップサイズの代わりに使用するように構成され得る。例えば、書き込み回路114は、第1のプログラミングステップサイズ116に従ってブロック110に第1のデータをプログラムするように構成され、かつ第2のプログラミングステップサイズ118に従ってブロック112に第2のデータをプログラムするように構成され得る（例えば、コントローラ106がブロック112にデータを書き込み、この書き込み操作を遂行するため、第2のプログラミングステップサイズ118を書き込み回路114へ送信する場合）。つまり、コントローラ106は、書き込み回路114を介してメモリへ書き込まれるデータについて、プログラミングステップサイズをブロック単位で選択し得る。20

#### 【0012】

コントローラ106は、ホスト装置130からメモリアクセス要請を受信し、かつメモリ104からのデータ読み出しを処理するように構成され得る。コントローラ106は、しきい値122とブロック誤り数124を受信するように構成されたブロック単位プログラミング調整エンジン120を含む。ブロック単位プログラミング調整エンジン120は、受信したしきい値122と受信したブロック誤り数124に少なくとも部分的に基づいて、書き込み回路114で使用するプログラミングステップサイズを調整するように構成され得る。ブロック単位プログラミング調整エンジン120はしきい値122とブロック誤り数124を比較し、その結果に基づき第2のプログラミングステップサイズ118を選択し得る。例えば、ブロック誤り数124がしきい値122に満たなければ、第2のプログラミングステップサイズ118が選択されない場合がある。ブロック誤り数124がしきい値122を上回るなら、第2のプログラミングステップサイズ118が選択され、メモリ104へ提供される場合がある。第2のプログラミングステップサイズ118は、第1のプログラミングステップサイズ116に基づき計算されてもよいし、あるいは図330

に関して説明するように表から選択されてもよい。

【0013】

コントローラ106は、メモリの或るブロックに対して、そのブロックの誤り数がしきい値を満たすとする判断に基づいて、プログラミングステップサイズを第1の値から第2の値へ低減するように構成され得る。例えば、ブロック110の誤り数は、ブロック110のメモリ読み出し回数またはブロック110の書き込み／消去サイクル数のため、メモリ104の加齢にともない増加し得る。ブロック110の誤り数（例えば、ブロック誤り数124）がしきい値（例えば、しきい値122）を満たすと、ブロック110に対するプログラミングステップのサイズは、第1のプログラミングステップサイズ116から第2のプログラミングステップサイズ118へ低減され得る。具体的に説明すると、ブロック単位プログラミング調整エンジン120は、受信したしきい値122と受信したブロック誤り数124を比較した結果に基づき、第1のプログラミングステップサイズ116から第2のプログラミングステップサイズ118にプログラミングステップサイズを調整することを判断し得る。コントローラ106は、ブロック110のプログラミング（データ書き込み）に使用する第2のプログラミングステップサイズ118を書き込み回路114へ送信し得る。10

【0014】

作動中、ホスト装置130はブロック110のデータを読み出すことをコントローラ106に指図し得る。コントローラ106は読み出されたデータに基づきブロック誤り数124を判断し、ブロック誤り数124をしきい値122と比較し得る。ブロック誤り数124がしきい値122を満たす場合（例えば、ブロック誤り数124がしきい値122を超過する場合）、プログラミングステップサイズは、第1のプログラミングステップサイズ116から第2のプログラミングステップサイズ118へ低減され得る。20

【0015】

メモリ装置の或るブロックに対して、プログラミングステップサイズを第1の値（例えば、第1のプログラミングステップサイズ116）から第2の値（例えば、第2のプログラミングステップサイズ118）へ低減すると、プログラミングステップ数が増加し得るため、プログラミングの待ち時間は長くなり得る。ただし、図2に関して説明するよう、低減されたプログラミングステップサイズを用いてブロックにプログラムされるデータで誤りは減るため、メモリ装置の寿命は延びる。通常、プログラミングステップサイズはメモリ装置の耐用寿命の終末に向けて低減されていき、メモリ装置の寿命の大半にわたり待ち時間は増加しない。30

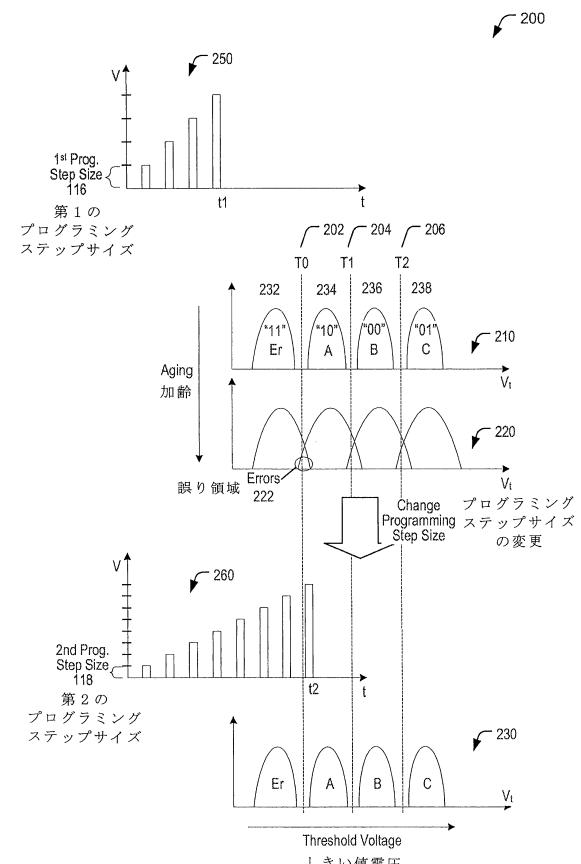

【0016】

図2は、メモリの或るブロック（例えば、図1のブロック110）から読み出され得る1蓄積素子群の代表的な電圧特性210、220、および230を示し、かつプログラミングステップサイズを低減することによって電圧しきい値分布の重なりによるデータ破損を軽減する効果を示す。例えば、第1のセル電圧分布（CVD）210には、2ビットセル等の1群のマルチレベルセルから読み出されるしきい値電圧特性が示されている。第1のCVD210は、第1のプログラミングステップサイズを用いて特定のしきい値電圧までプログラムされたセルの分布を示している。例えば、第1のグラフ表現250は、或るプログラミングステップサイズ（例えば、第1のプログラミングステップサイズ116）を有する一連のプログラミングパルスを示している。第1のプログラミングステップサイズ116は第1の電圧値を示している。一連のプログラミングパルスは、図1のメモリ104の1つ以上のブロック（例えば、ブロック110）をプログラムし得る。一例として、4つのプログラミングパルスが図に示されている。相続ぐ個々のプログラミングパルスの電圧値は、第1のプログラミングステップサイズ116の電圧値ずつ増加される。具体的に説明すると、第3のプログラミングパルスは、第2のプログラミングパルスの電圧値に加えた第1の電圧値に等しい電圧値を有し得る。図に示されているように、ブロック110のプログラミングは第1のプログラミング待ち時間、すなわち遅延t1を含み得る。40

【0017】

図に示されているように、第1のCVD210は4つの代表的なしきい値電圧範囲を含み、これらのしきい値電圧範囲は3つの読み出し電圧T0 202、T1 204、およびT2 206によって画定され、セル状態Er、A、B、およびCにそれぞれ相当する。例えば、2ビット値「11」は「Er」状態に相当する第1のしきい値電圧範囲232内のしきい値電圧に相当し、2ビット値「10」は「A」状態に相当する第2のしきい値電圧範囲234内のしきい値電圧に相当し、2ビット値「00」は「B」状態に相当する第3のしきい値電圧範囲236内のしきい値電圧に相当し、2ビット値「01」は「C」状態に相当する第4のしきい値電圧範囲238内のしきい値電圧に相当し得る。

#### 【0018】

データは、セルしきい値電圧を読み出し電圧T0 202～T2 206のいずれか1つ以上と比較することによって蓄積素子から読み出され得る。第1のCVD210は誤りがない（全てのセルが当初プログラムされた状態に保たれている）ものとして図に示されている。各セルはそれぞれのしきい値電圧範囲の中心にしきい値電圧を有するように当初プログラムされ得るが、様々な要因（例えば、蓄積素子を含むブロックのメモリ読み出し回数や書き込み／消去サイクル数）により、実際のセルしきい値電圧は中心電圧から「ずれる」場合があり、結果的に第2のCVD220になる。

#### 【0019】

第2のCVD220は、（例えば、メモリが加齢し）第1のCVD210から時間が経過した後にマルチレベルセル群から読み出され得る別のしきい値電圧特性を表している。CVD220は第1のプログラミングステップサイズ116を用いて特定のしきい値電圧までプログラムされたセルの分布を示している。誤り領域222は状態「Er」および「A」まで当初プログラムされたセルのブロックの蓄積素子で起こり得る誤りを含み、それらのしきい値電圧は読み出し電圧T0 202をまたいで別の状態にずれ込んでいる。具体的に説明すると、誤りはメモリの加齢にともない起こり、蓄積素子を含むブロックのメモリ読み出し回数や書き込み／消去サイクル数に一致し得る。誤りは、図に示されているように、「Er」状態まで当初プログラムされたセルのしきい値電圧が上がって、「Er」状態と「A」状態との間の読み出し電圧T0 202を越えることによって起こり得る。読み出し電圧T0 202を用いてこれらのセルを読み出すと、セルは「Er」状態ではなく「A」状態にあると誤認される。誤り領域222では「A」状態まで当初プログラムされたセルを含み、これらセルのしきい値電圧が読み出し電圧T0 202より下がっている。読み出し電圧T0 202を用いてこれらのセルを読み出すと、セルは「A」状態ではなく「Er」状態にあると誤認される。

#### 【0020】

第3のCVD230には第2のCVD220の2ビットマルチレベルセル群から読み出された別の代表的なしきい値電圧特性が示され、ここで、セルを特定のしきい値電圧までプログラムするのに使われるプログラミングステップサイズが、例えば図1のブロック単位プログラミング調整エンジン120によって低減されることにより、第2のCVD220の誤りが回避されている。例えば、第2のグラフ表現260は第2の一連のプログラミングパルスを示し、これらのプログラミングパルスは、第1のプログラミングステップサイズ116から低減された第2のプログラミングステップサイズ（例えば、第2のプログラミングステップサイズ118）を有する。第2のプログラミングステップサイズ118は第1の電圧値に満たない第2の電圧値に相当する。メモリ104の加齢にともない、ブロック110は第2のプログラミングステップサイズ118に従ってプログラムされ得る。一例として、8つのプログラミングパルスが図に示されている。相続ぐ個々のプログラミングパルスの電圧値は、第2のプログラミングステップサイズ118の電圧値ずつ増加される。図に示されているように、ブロック110のプログラミングは第2のプログラミング待ち時間t2を含み得る。プログラミングパルス数の増加のため、第2のプログラミング待ち時間t2は第1のプログラミング待ち時間t1より長い。

#### 【0021】

第2のCVD220において読み出し電圧T0 202で読み出されたときに「A」状

10

20

30

40

50

態と誤認された「E r」状態のセルは、プログラミングステップサイズの低減により、第3のCVD230では「E r」状態として正しく識別されている。第2のCVD220において読み出し電圧T0 202で読み出されたときに「E r」状態と誤認された「A」状態のセルは、プログラミングステップサイズの低減により、第3のCVD230では「A」状態として正しく識別されている。

【0022】

メモリの特定ブロック内の蓄積素子のプログラミングステップサイズを低減することにより、その特定のブロックの蓄積素子に書き込まれるしきい値電圧の分布を引き締めることができ、誤りを減らすとともにブロックにデータをプログラムすることおよびメモリの寿命を延ばすことが可能となる。

10

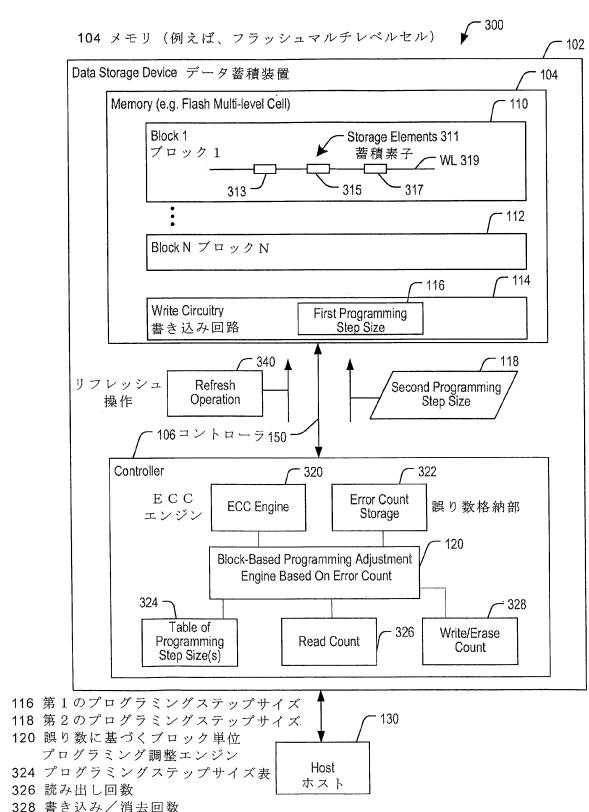

【0023】

図3を参照すると、システム構成品のさらなる詳細を示す図1のシステムの一例証的な実施形態が示され、全体的に300と呼称されている。システム300は、ホスト装置130へ結合されるデータ蓄積装置102を含む。データ蓄積装置102は、バス150経由でコントローラ106へ結合されたメモリ104を含む。

【0024】

メモリ104は、第1のブロック110とN番目のブロック112とを含む複数のブロックを含んでいる。第1のブロック110は、複数のワード線（例えば、代表的なワード線319）を含む。それぞれのワード線は1群の蓄積素子（例えば、1群の蓄積素子311）を含む。蓄積素子群311は複数のマルチレベルセル蓄積素子（例えば、フラッシュメモリ装置の代表的な蓄積素子313、315、および317）を含み得る。メモリ104は、書き込み回路114を含み、第1のプログラミングステップサイズ116の指示を蓄積する。例えば、書き込み回路114は、第1のプログラミングステップサイズ116に従ってブロック110に第1のデータをプログラムするように構成され、かつ第2のプログラミングステップサイズ118に従ってブロック112に第2のデータをプログラムするように構成され得る（例えば、コントローラ106がブロック112にデータを書き込み、この書き込み操作を遂行するため、第2のプログラミングステップサイズ118を書き込み回路114へ送信する場合）。つまり、コントローラ106は、書き込み回路114を介してメモリへ書き込まれるデータについて、プログラミングステップサイズをブロック単位で選択し得る。

20

【0025】

コントローラ106は、ブロック単位プログラミング調整エンジン120を含む。コントローラ106は誤り訂正符号化（ECC）エンジン320をさらに含み、ECCエンジン320は復号化操作を遂行し、かつ復号化操作で検出された誤り数に相当するデータを提供するように構成され、その提供されたデータは誤り数格納部322に蓄積される。例えば、ブロック110内の蓄積素子311から読み出されたデータはECCエンジン320によって受信され得る。ECCエンジン320は読み出されたデータに対して復号化操作を遂行し、復号化操作に基づいて誤り数をブロック単位プログラミング調整エンジン120に提供し得る。

30

【0026】

ブロック単位プログラミング調整エンジン120へ提供される、メモリ104のブロックの誤り数は、ブロック110の各ワード線のワード線誤り数の加算に基づく、ブロック110から読み出されるデータで検出される合計誤り数を含み得る。ブロック110の誤り数は、ブロック110のワード線319の読み出し回数、ブロック110のワード線319の書き込み／消去サイクル数、1つ以上の要因、またはこれらの組み合わせのため、メモリ104の加齢にともない増加し得る。読み出し回数326は、ブロック110の最後の消去以降にブロック110で行われたメモリ読み出しの回数に一致し得る。書き込み／消去回数328はブロック110の書き込み／消去サイクル数に一致し得る。

40

【0027】

ブロック110の誤り数がしきい値を満たすと、ブロック110にデータを書き込むと

50

きに使用されるプログラミングステップのサイズが第1のプログラミングステップサイズ116から第2のプログラミングステップサイズ118へ低減され得る。具体的に説明すると、ブロック単位プログラミング調整エンジン120は、受信したしきい値と受信したブロック誤り数に少なくとも部分的に基づいて、プログラミングステップサイズを第1の値（例えば、第1のプログラミングステップサイズ116）から第2の値（例えば、第2のプログラミングステップサイズ118）に調整し得る。

【0028】

コントローラ106は、第1の値に基づいて第2の値を計算するように構成され得る。例えば、第2のプログラミングステップサイズ118は、第1のプログラミングステップサイズ116に倍率を乗じることによって計算され得る。具体的に説明すると、第2のプログラミングステップサイズ118は、第1のプログラミングステップサイズ116に係数1.2を乗じることによって計算され得る（例えば、第2の値は第1の値より20%大きい）。別の実施例では、表、レジスタ、ラッチ等の格納域から第2のプログラミングステップサイズ118を引き出すためのインデックスとして第1のプログラミングステップサイズ116が使用され得る。

10

【0029】

コントローラ106は、プログラミングステップサイズ表324から第2の値を選択するように構成され得る。例えば、プログラミングステップサイズ表324から第2の値を引き出すためのインデックスとして第1の値が使用され得る。別の実施例では、図1のブロック誤り数124の値に少なくとも部分的に基づいて、プログラミングステップサイズ表324から第2の値が選択され得る。具体的に説明すると、ブロック誤り数124の値がしきい値122を大差で超過する場合には、第1の値からの低減を、ブロック誤り数124の値がしきい値122を小差で超過した場合の低減より大きくする、第2の値が、プログラミングステップサイズ表324から選択され得る。プログラミングステップサイズ表324はコントローラ106内にあるものとして図に示されているが、別の実施例では、メモリ104内にプログラミングステップサイズ表324があつてもよい。

20

【0030】

コントローラ106は、コントローラ106におけるブロック110の読み出し回数とブロック110の書き込み／消去サイクル数との比較に基づき、ブロック110のプログラミングステップサイズを低減するように構成され得る。例えば、「より新しい」メモリでは、ブロック110の書き込み／消去サイクル数によって誤りが生じるのではなく、むしろ消去状態（図2の「E<sub>r</sub>」状態）のセルがプログラム済み状態（図2の「A」状態）として読み出される、高い電圧ストレスを受け、読み出されていないセルから得られる読み出しディスターブによって誤りが生じ得る。誤りの主な原因が装置の加齢か読み出しディスターブなのかを判断するため、コントローラ106は読み出し回数326と書き込み／消去回数328を比較し、読み出し回数326と書き込み／消去回数328との比較結果がしきい値を満たす場合には、プログラミングステップサイズを第1の値から第2の値へ低減し得る。コントローラ106はまた、読み出し回数326と書き込み／消去回数328との比較結果が読み出しディスターブしきい値を満たす場合に、プログラミングステップサイズを調整する代わりにブロック110でリフレッシュ操作340を遂行するように構成され得る。例えば、読み出し回数326が比較的高く、かつ書き込み／消去回数328が比較的低く、かつ誤り数がしきい値を満たすなら、誤りの主な原因は読み出しディスターブにあるので、コントローラ106はプログラミングステップサイズを低減するのではなく、リフレッシュ操作340を遂行し得る（例えば、読み出し後にデータが再度書き換えられる）。

30

【0031】

作動中、ホスト装置130は、ブロック110のデータを読み出すことをコントローラ106に指図し得る。コントローラ106は、ワード線319から読み出された誤りを判断し、誤り数格納部322を更新し得る。例えば、コントローラは、ワード線319から読み出された以前の誤り数をワード線319から読み出された新しい誤り数に差し替え得

40

50

る。

【0032】

コントローラ106は、(例えば、図1のブロック誤り数124を判断するために)誤り数格納部322にあるブロック110のワード線誤りを合計し、ブロック誤り数124をしきい値122と比較し得る。この比較はバックグラウンドプロセスで遂行されるか、あるいはブロック110の書き込み要請を受けて遂行され得る。ブロック誤り数124がしきい値122を上回る場合は、誤りの原因が読み出しディスクラーブなのか否かを判断するため、読み出し回数326が書き込み/消去回数328と比較され得る。読み出し回数326と書き込み/消去回数328の比較が読み出し誤りの可能性を指摘するなら、コントローラはリフレッシュ操作340を遂行し得る。さもなくば、コントローラ106は、ブロック110に対する次の書き込み操作で使用する第2のプログラミングステップサイズ118をメモリ104へ送信し得る。

【0033】

メモリの特定ブロック内にある蓄積素子のプログラミングステップサイズを低減することにより、誤りを減らすとともにブロックにデータをプログラムすることおよびメモリの寿命を延ばすことが可能となる。

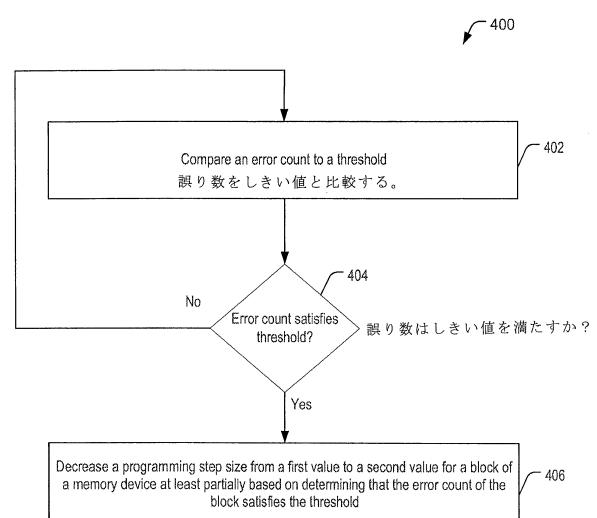

【0034】

メモリ装置の或るブロックに対してプログラミングステップサイズを第1の値から第2の値へ低減する方法400の一実施形態を示す流れ図を図4に示す。方法400は、図1および図3のデータ蓄積装置102によって遂行され得る。

【0035】

402では、誤り数をしきい値と比較する。具体的に説明すると、コントローラ106は、第1のプログラミングステップサイズ116に従って予めプログラムされていたブロック110のデータを読み出し得る。図3のECCエンジン320は読み出されたデータに対して復号化操作を遂行し、ワード線319の誤り数を提供し得る。ブロック誤り数124を判断するため、ブロック110の全ワード線の誤り数が合計され得る。ブロック誤り数124は、ブロック単位プログラミング調整エンジン120へ送信され、しきい値122と比較され得る。

【0036】

404では、誤り数がしきい値を満たすか否かが判断される。誤り数がしきい値を満たさない場合には、402へ戻る。誤り数がしきい値を満たす場合には、406で、メモリ装置の或るブロックに対して、そのブロックの誤り数がしきい値を満たすとする判断に少なくとも部分的に基づいて、プログラミングステップサイズを第1の値から第2の値へ低減し得る。具体的に説明すると、コントローラ106は、ブロック誤り数124をしきい値122と比較し、その比較結果に基づいてプログラミングステップサイズを低減し得る。コントローラ106はまた、読み出しディスクラーブしきい値を満たした比較結果を受けて、プログラミングステップサイズを調整する代わりにブロック110でリフレッシュ操作340を遂行し得る。例えば、ブロック誤り数124がしきい値122を上回る場合には、誤りの原因が読み出しディスクラーブなのか否かを判断するため、読み出し回数326を書き込み/消去回数328と比較し得る。読み出し回数326が書き込み/消去回数328を上回る場合には、コントローラは、プログラミングステップサイズを低減するのではなく、リフレッシュ操作340を遂行し得る。読み出し回数326が書き込み/消去回数328を下回る場合には、コントローラ106は、ブロック110に対する次の書き込み操作で使用する第2のプログラミングステップサイズ118をメモリ104へ送信し得る。

【0037】

大きいプログラミングステップサイズでブロック110をプログラムすると、プログラミングステップ数が減少し得るため、プログラミングの待ち時間は短くなる。通常、誤りの数はメモリの加齢にともない増加する。メモリの加齢にともない低減されたプログラミングステップサイズでブロックをプログラムすれば、精度を向上させ、誤りを減らし、メ

10

20

30

40

50

モリの寿命を延ばし得る。

【0038】

本願の図面に示された種々の構成品はブロック構成品として描かれ、一般的な用語で説明されているが、これらの構成品は、データ蓄積装置（例えば、図1および図3のデータ蓄積装置102）がこれらの構成品に起因する特定の機能を遂行することを可能にするよう構成された1つ以上のマイクロプロセッサ、状態マシン、または他の回路、またはこれらのいかなる組み合わせを含んでもよい。例えば、図1および図3のコントローラ106は、プログラミングステップサイズを第1の値（例えば、第1のプログラミングステップサイズ116）から第2の値（例えば、第2のプログラミングステップサイズ118）へ低減することをブロック単位プログラミング調整エンジン120に指図する物理的構成品であってよく、例えばコントローラ、プロセッサ、状態マシン、論理回路、または他の構造であってよい。

10

【0039】

コントローラ106は、制御情報を生成してブロック単位プログラミング調整エンジン120に指図するようにプログラムされたマイクロプロセッサまたはマイクロコントローラを用いて実装されてよい。一実施形態において、コントローラ106は、メモリ104に蓄積された命令を実行するプロセッサを含む。この代わりにまたはこれに加えて、プロセッサによって実行される実行可能命令が、不揮発性メモリ104とは別の独立したメモリ位置（例えば、読み出し専用メモリ（ROM））に蓄積されてもよい。

20

【0040】

一実施形態において、データ蓄積装置102は、1つ以上の外部装置に選択的に結合されるように構成された可搬型装置であってよい。例えば、データ蓄積装置102は、ユニバーサルシリアルバス（USB）フラッシュドライブや取り外し可能なメモリカード等の取り外し可能な装置であってよい。ただし、別の実施形態において、データ蓄積装置102は、1つ以上のホスト装置（例えば、可搬型通信装置の筐体）の中に取り付けられてよく、あるいは組み込まれてもよい。例えば、データ蓄積装置102はパッケージされた機器（例えば、無線電話機、個人用携帯情報端末（PDA）、ゲーム装置またはコンソール、可搬型ナビゲーション装置、コンピュータ、または内蔵型不揮発性メモリを使用する他の装置）の中にあってもよい。一実施形態において、データ蓄積装置102は、不揮発性メモリを含み、例えばフラッシュメモリ（例えば、NAND、NOR、マルチレベルセル（MLC）、分割ビット線NOR（DINOR）、AND、高容量結合比（HiCR）、非対称コンタクトレストランジスタ（ACT）、または他のフラッシュメモリ）、消去可能でプログラム可能な読み出し専用メモリ（EPROM）、電気的に消去可能でプログラム可能な読み出し専用メモリ（EEPROM）、読み出し専用メモリ（ROM）、ワンタイムプログラマブルメモリ（OTP）、またはその他の類のメモリを含む。

30

【0041】

ここに記載された実施形態の説明は、種々の実施形態を全般的に理解するためのものである。本願明細書の開示から別の実施形態を導き出し利用することもでき、本願明細書に開示された範囲から逸脱することなく、構造的および論理的な代替および変更を行うことができる。本願明細書の開示は、種々の実施形態のいかなるおよび全ての後続の適用または変形例を対象として含む。

40

【0042】

ここに開示された題材は制限的ではなく説明的とみなすべきものであり、添付の特許請求の範囲は本願明細書の範囲内にあるこのような全ての修正、改良、および他の実施形態を含むことを意図する。法律で許される最大限の範囲において、本発明の範囲は添付の特許請求の範囲およびその同等物の最も広義な解釈によって決定され、前述した詳細な説明によって制限または限定されない。

【図1】

FIG. 1

【 図 2 】

FIG. 2

【 図 3 】

FIG. 3

【 図 4 】

メモリ装置の或るブロックに対して、

そのブロックの誤り数がしきい値を満たすとする

判断に少なくとも部分的にに基づいて、

プログラムイングステップサイズを

第1の値から第2の値へ低減する。

FIG. 4

---

フロントページの続き

(72)発明者 ドブリュー , マヌエル アントニオ

アメリカ合衆国、95762、カリフォルニア州、エルドラドヒルズ、ハンティントン サークル

2166

(72)発明者 パンテラキス , ディミトリス

アメリカ合衆国、95054、カリフォルニア州、サンタクララ、ホープ ドライブ 1668、

#1734

(72)発明者 スカラ , スティーブン

アメリカ合衆国、94539、カリフォルニア州、フリーモント、パゴサ ウェイ 293

審査官 後藤 彰

(56)参考文献 特開2009-087509 (JP, A)

特開2003-242787 (JP, A)

特開2008-027511 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

G11C 16/02 - 16/06