(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6373991号

(P6373991)

(45) 発行日 平成30年8月15日(2018.8.15)

(24) 登録日 平成30年7月27日(2018.7.27)

(51) Int.Cl.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| GO6F 17/16 | (2006.01) | GO6F 17/16 | D    |

| GO6F 9/38  | (2006.01) | GO6F 9/38  | 310G |

| GO6F 9/30  | (2018.01) | GO6F 9/38  | 370A |

|            |           | GO6F 9/38  | 370C |

|            |           | GO6F 9/30  | 350A |

請求項の数 30 (全 119 頁)

(21) 出願番号 特願2016-530939 (P2016-530939)

(86) (22) 出願日 平成26年11月13日 (2014.11.13)

(65) 公表番号 特表2016-537722 (P2016-537722A)

(43) 公表日 平成28年12月1日 (2016.12.1)

(86) 國際出願番号 PCT/US2014/065557

(87) 國際公開番号 WO2015/073731

(87) 國際公開日 平成27年5月21日 (2015.5.21)

審査請求日 平成29年10月19日 (2017.10.19)

(31) 優先権主張番号 14/082,075

(32) 優先日 平成25年11月15日 (2013.11.15)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100112807

弁理士 岡田 貴志

最終頁に続く

(54) 【発明の名称】 フィルタベクトル処理動作のためのタップ付き遅延線を利用するベクトル処理エンジンと、関連するベクトル処理システムおよび方法

## (57) 【特許請求の範囲】

## 【請求項 1】

フィルタベクトル処理動作を供給するように構成されたベクトル処理エンジン(VPE)であって、

フィルタベクトル処理動作のための少なくとも1つの入力データフローパスにおいて入力ベクトルデータサンプルセットを供給することと、

少なくとも1つの出力データフローパスから結果として生じるフィルタ処理された出力ベクトルデータサンプルセットを受信すること、

前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットを記憶することと

を行うように構成された少なくとも1つのベクトルデータファイルと、

前記少なくとも1つの入力データフローパスにおいて少なくとも1つの実行ユニットと前記少なくとも1つのベクトルデータファイルとの間に設けられた少なくとも1つのタップ付き遅延線、前記少なくとも1つのタップ付き遅延線は、複数の処理ステージのうちの処理ステージごとに、シフトされた入力ベクトルデータサンプルセットを供給するよう、前記フィルタベクトル処理動作におけるフィルタタップの数に等しい前記複数の処理ステージのうちの処理ステージごとに、複数のパイプラインレジスタにおいて、ベクトルデータサンプル幅ぶん前記入力ベクトルデータサンプルセットをシフトするように構成される、と、

前記少なくとも1つの入力データフローパス中に設けられた前記少なくとも1つの実行

10

20

ユニット、前記少なくとも 1 つの実行ユニットは、

前記複数の処理ステージのうちの処理ステージごとに、前記シフトされた入力ベクトルデータサンプルセットと前記少なくとも 1 つの実行ユニット内のレジスタファイルから受信したフィルタ係数を乗算して、前記フィルタベクトル処理動作のフィルタタップごとに中間出力ベクトルデータサンプルセットを生成するように構成された少なくとも 1 つの乗算器と、

前記複数の処理ステージのうちの処理ステージごとに、少なくとも 1 つの累算器において前記中間出力ベクトルデータサンプルセットを累算するように構成された前記少なくとも 1 つの累算器と

を備える、と

を備え、

前記少なくとも 1 つの実行ユニットは、前記少なくとも 1 つの出力データフローパス上に前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットを供給するように構成される、

V P E。

#### 【請求項 2】

前記少なくとも 1 つの累算器は、前記入力ベクトルデータサンプルセットが前記少なくとも 1 つのベクトルデータファイルから再フェッチされることなく、前記複数の処理ステージのうちの処理ステージごとに前記中間出力ベクトルデータサンプルセットを累算するように構成される、

請求項 1 に記載の V P E。

#### 【請求項 3】

前記少なくとも 1 つの累算器は、前記入力ベクトルデータサンプルセット中の入力ベクトルデータサンプルの数が前記フィルタベクトル処理動作におけるフィルタタップの数より小さい場合、前記入力ベクトルデータサンプルセットが前記少なくとも 1 つのベクトルデータファイルから再フェッチされることなく、前記複数の処理ステージのうちの処理ステージごとに前記中間出力ベクトルデータサンプルセットを累算するように構成される、

請求項 1 に記載の V P E。

#### 【請求項 4】

前記少なくとも 1 つのタップ付き遅延線は、前記フィルタベクトル処理動作における前記フィルタタップの数が前記入力ベクトルデータサンプルセット中の入力ベクトルデータサンプルの数より大きい場合、前記少なくとも 1 つのベクトルデータファイルから前記少なくとも 1 つの入力データフローパス上に追加の入力ベクトルデータサンプルセットの別のフェッチを受信するようにさらに構成される、

請求項 1 に記載の V P E。

#### 【請求項 5】

前記少なくとも 1 つのベクトルデータファイルは、

前記フィルタベクトル処理動作のための前記少なくとも 1 つの入力データフローパス中に前記少なくとも 1 つのベクトルデータファイルの幅の前記入力ベクトルデータサンプルセットを供給することと、

記憶されるべき、前記少なくとも 1 つの出力データフローパスからの前記少なくとも 1 つのベクトルデータファイルの前記幅の前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットを受信することと

を行うように構成される、請求項 1 に記載の V P E。

#### 【請求項 6】

前記少なくとも 1 つのタップ付き遅延線は、

前記複数のパイプラインレジスタに、前記少なくとも 1 つのベクトルデータファイルから、前記少なくとも 1 つの入力データフローパスにおいて前記入力ベクトルデータサンプルセットを受信することと、

前記複数の処理ステージのうちの処理ステージごとに、前記少なくとも 1 つの実行ユ

10

20

30

40

50

ニットに、前記少なくとも 1 つの入力データフローパスにおいて前記シフトされた入力ベクトルデータサンプルセットの各々を供給することと

を行うようにさらに構成され、

前記少なくとも 1 つの実行ユニットは、前記複数の処理ステージのうちの処理ステージごとに、前記少なくとも 1 つのタップ付き遅延線から、前記少なくとも 1 つの入力データフローパスにおいて前記シフトされた入力ベクトルデータサンプルセットを受信するようさらに構成される、

請求項 1 に記載の V P E。

【請求項 7】

前記少なくとも 1 つのタップ付き遅延線は、

前記複数の処理ステージのうちの第 1 の処理ステージにおいて、前記少なくとも 1 つの実行ユニットに、前記少なくとも 1 つの入力データフローパスにおいて第 1 の入力ベクトルデータサンプルセットを供給することと、

前記複数の処理ステージのうちの後続の処理ステージにおいて、前記少なくとも 1 つの実行ユニットに、前記少なくとも 1 つの入力データフローパスにおいて前記シフトされた入力ベクトルデータサンプルセットを供給することと

を行うように構成され、

前記少なくとも 1 つの乗算器は、

前記第 1 の処理ステージにおいて第 1 の 中間出力ベクトルデータサンプルセットを生成するために、前記第 1 の入力ベクトルデータサンプルセットと第 1 のフィルタ係数を乗算することと、

前記後続の処理ステージにおいて後続の 中間出力ベクトルデータサンプルセットを生成するために、前記シフトされた入力ベクトルデータサンプルセットと後続のフィルタ係数を乗算することと

を行うように構成され、

前記少なくとも 1 つの累算器は、前記結果として生じる フィルタ処理された出力ベクトルデータサンプルセットを供給するために、前記少なくとも 1 つの累算器中の前記後続の 中間出力ベクトルデータサンプルセットと前記第 1 の 中間出力ベクトルデータサンプルセットとを累算するように構成される、

請求項 6 に記載の V P E。

【請求項 8】

前記少なくとも 1 つのベクトルデータファイルは、

前記少なくとも 1 つの入力データフローパス中の少なくとも 1 つのタップ付き遅延線入力における前記入力ベクトルデータサンプルセットとして、前記入力ベクトルデータサンプルセットを供給することと、

前記少なくとも 1 つの出力データフローパス中の少なくとも 1 つの実行ユニット出力における前記結果として生じる フィルタ処理された出力ベクトルデータサンプルセットを受信することと

を行うようにさらに構成され、

前記少なくとも 1 つのタップ付き遅延線は、

前記少なくとも 1 つのベクトルデータファイルから、前記少なくとも 1 つの入力データフローパス中の前記少なくとも 1 つのタップ付き遅延線入力において前記入力ベクトルデータサンプルセットを受信することと、

前記複数の処理ステージのうちの処理ステージごとに、前記少なくとも 1 つの実行ユニットに、前記少なくとも 1 つの入力データフローパス中の少なくとも 1 つの実行ユニット入力において前記シフトされた入力ベクトルデータサンプルセットの各々を供給することと

を行うようにさらに構成され、

前記少なくとも 1 つの実行ユニットは、

前記複数の処理ステージのうちの処理ステージごとに、前記少なくとも 1 つのタップ

10

20

30

40

50

付き遅延線から、前記少なくとも 1 つの入力データフローパス中の前記少なくとも 1 つの実行ユニット入力において前記シフトされた入力ベクトルデータサンプルセットを受信することと、

前記少なくとも 1 つの実行ユニット出力において前記少なくとも 1 つの出力データフローパス上に前記結果として生じる フィルタ処理された出力ベクトルデータサンプルセットを供給することと

を行うようにさらに構成される、請求項 6 に記載の VPE。

【請求項 9】

前記少なくとも 1 つのタップ付き遅延線は、

複数のシャドウパイプラインレジスタに、前記少なくとも 1 つの入力データフローパス中の前記少なくとも 1 つのベクトルデータファイルから、次の入力ベクトルデータサンプルセットを受信することと、

前記シフトされた入力ベクトルデータサンプルセットを供給するために、プライマリタップ付き遅延線に、処理ステージごとに前記複数のシャドウパイプラインレジスタにおいて前記ベクトルデータサンプル幅ぶん前記次の入力ベクトルデータサンプルセットをシフトすることと

を行うように構成されるシャドウタップ付き遅延線を備え、

前記プライマリタップ付き遅延線は、前記複数の処理ステージ中の処理ステージごとに、前記少なくとも 1 つの実行ユニットに、前記少なくとも 1 つの入力データフローパスにおいて前記シフトされた入力ベクトルデータサンプルセットを供給するように構成される

、

請求項 1 に記載の VPE。

【請求項 10】

複数の入力ベクトルデータサンプル選択器をさらに備え、前記複数の入力ベクトルデータサンプル選択器の各々は、前記少なくとも 1 つのタップ付き遅延線中の前記複数のパイプラインレジスタのうちの 1 つのパイプラインレジスタに割り当てられ、

前記複数の入力ベクトルデータサンプル選択器は各々、前記割り当てられたパイプラインレジスタに、シフトされた入力ベクトルデータサンプルを記憶するために、隣接パイプラインレジスタ中に記憶された入力ベクトルデータサンプルと前記少なくとも 1 つのベクトルデータファイルからの前記入力ベクトルデータサンプルセットからの入力ベクトルデータサンプルとの間で選択するように構成される、

請求項 1 に記載の VPE。

【請求項 11】

前記少なくとも 1 つのタップ付き遅延線は、前記少なくとも 1 つの実行ユニットによって実行されるベクトル命令に従って、前記少なくとも 1 つのタップ付き遅延線のためのプログラマブル入力データパス構成に基づいて、前記少なくとも 1 つの実行ユニットと前記少なくとも 1 つのベクトルデータファイルとの間の前記少なくとも 1 つの入力データフローパス中に選択的に供給されるように構成可能である、

請求項 1 に記載の VPE。

【請求項 12】

前記少なくとも 1 つのタップ付き遅延線は、前記少なくとも 1 つの実行ユニットによって実行される次のベクトル命令に従って、前記少なくとも 1 つのタップ付き遅延線のための前記プログラマブル入力データパス構成に基づいて、前記少なくとも 1 つの入力データフローパス中に選択的に供給されるように再構成されるように構成される、

請求項 1 に記載の VPE。

【請求項 13】

前記少なくとも 1 つのタップ付き遅延線は、前記少なくとも 1 つの実行ユニットによって実行される前記 VPE のクロックサイクルごとに前記少なくとも 1 つの入力データフローパス中に選択的に供給されるように再構成されるように構成される、

請求項 1 に記載の VPE。

10

20

30

40

50

## 【請求項 14】

前記少なくとも 1 つの実行ユニットは、前記少なくとも 1 つの実行ユニットのためのプログラム入力データフローパス構成に基づいて、前記入力ベクトルデータサンプルセットとは異なるビット幅の入力ベクトルデータサンプルを処理するように構成可能である、

請求項 1 に記載の V P E。

## 【請求項 15】

前記少なくとも 1 つの実行ユニットは、

前記少なくとも 1 つのベクトルデータファイル中に一緒に記憶される前記少なくとも 1 つの出力データフローパス中の前記結果として生じる フィルタ処理された出力ベクトルデータサンプルセット のうちの実数の、結果として生じるフィルタ処理された出力ベクトルデータサンプル を供給することと、

10

前記実数の、結果として生じるフィルタ処理された出力ベクトルデータサンプル と別個に、前記少なくとも 1 つのベクトルデータファイル中に一緒に記憶される前記少なくとも 1 つの出力データフローパス中の前記結果として生じる フィルタ処理された出力ベクトルデータサンプルセット のうちの虚数の、結果として生じるフィルタ処理された出力ベクトルデータサンプル を供給することと

を行うように構成される、請求項 1 に記載の V P E。

## 【請求項 16】

前記少なくとも 1 つの実行ユニットは、

20

前記少なくとも 1 つのベクトルデータファイル中に一緒に記憶される前記少なくとも 1 つの出力データフローパス中の前記結果として生じる フィルタ処理された出力ベクトルデータサンプルセット のうちの偶数の、結果として生じるフィルタ処理された出力ベクトルデータサンプル を供給することと、

前記偶数の、結果として生じるフィルタ処理された出力ベクトルデータサンプル と別個に、前記少なくとも 1 つのベクトルデータファイル中に一緒に記憶される前記少なくとも 1 つの出力データフローパス中の前記結果として生じる フィルタ処理された出力ベクトルデータサンプルセット のうちの奇数の、結果として生じるフィルタ処理された出力ベクトルデータサンプル を供給することと

を行うように構成される、請求項 1 に記載の V P E。

30

## 【請求項 17】

前記少なくとも 1 つの実行ユニットのためのフィルタ係数を記憶するように構成されたレジスタファイルをさらに備え、

前記少なくとも 1 つの実行ユニットは、処理ステージごとに前記フィルタベクトル処理動作のために前記レジスタファイルから フィルタ係数 を受信するようにさらに構成され、

前記少なくとも 1 つの乗算器は、処理ステージごとにそれぞれの 中間出力ベクトルデータサンプルセット を生成するために、処理ステージのための前記受信した フィルタ係数 と各受信した入力ベクトルデータサンプルセットを、前記少なくとも 1 つの乗算器中で乗算することによって、各処理ステージにおいて前記シフトされた入力ベクトルデータサンプルセットの各々 前記フィルタ係数を乗算する ようにさらに構成される、

40

請求項 1 に記載の V P E。

## 【請求項 18】

前記少なくとも 1 つの実行ユニットは、以下の式に従って、ディスクリート時間有限インパルス応答 (FIR) フィルタから成る前記フィルタベクトル処理動作を実行するように構成される、

## 【数 1】

$$y[n] = \sum_{l=0}^{l=Y-1} h(l) * x[n - l]$$

50

ここで、

$x[n]$  は、前記入力ベクトルデータサンプルセットを備え、

$y[n]$  は、前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットを備え、

$h(1)$  は、フィルタ係数から成り、

$Y$  は、前記フィルタ係数の数である、

請求項 1 に記載の VPE。

【請求項 19】

ベクトル処理エンジン (VPE) においてフィルタベクトル処理動作を実行するための装置であって、

フィルタベクトル処理動作のための少なくとも 1 つの入力データフローパス中に少なくとも 1 つのベクトルデータファイルから入力ベクトルデータサンプルセットをフェッチするための手段と、

前記少なくとも 1 つのベクトルデータファイルと少なくとも 1 つの実行ユニットとの間の前記少なくとも 1 つの入力データフローパスに設けられた少なくとも 1 つのタップ付き遅延線中に前記少なくとも 1 つの入力データフローパスにおける前記フェッチされた入力ベクトルデータサンプルセットを受信するための手段と、

複数の処理ステージの数が前記フィルタベクトル処理動作のフィルタタップの数に等しい、前記少なくとも 1 つの実行ユニット中の前記複数の処理ステージの処理ステージごとに、

前記入力ベクトルデータサンプルセットとして、シフトされた入力ベクトルデータサンプルセットを供給するように、前記入力ベクトルデータサンプルセット中の前記フィルタベクトル処理動作のための次のフィルタタップに前記少なくとも 1 つのタップ付き遅延線内の前記入力ベクトルデータサンプルセットをシフトするための手段、前記少なくとも 1 つのタップ付き遅延線は、前記フィルタベクトル処理動作におけるフィルタタップの数に等しい複数の処理ステージのうちの処理ステージごとに、複数のパイプラインレジスタにおいて、ベクトルデータサンプル幅ぶん前記入力ベクトルデータサンプルセットをシフトするように構成される、と、

現在の処理ステージにおいて、前記少なくとも 1 つの実行ユニットに、前記少なくとも 1 つの入力データフローパスにおいて前記少なくとも 1 つのタップ付き遅延線から前記シフトされた入力ベクトルデータサンプルセットを供給するための手段と、

中間出力ベクトルデータサンプルセットを生成するために、前記現在の処理ステージにおいて前記少なくとも 1 つの実行ユニット中の前記シフトされた入力ベクトルデータサンプルセットに前記少なくとも 1 つの実行ユニット内のレジスタファイルから受信したフィルタ係数を乗算するための手段と、

前記現在の処理ステージにおいて、前の結果として生じるフィルタ処理された出力ベクトルデータサンプルセットと前記中間出力ベクトルデータサンプルセットを累算するための手段と、

前記少なくとも 1 つのベクトルデータファイルに、前記少なくとも 1 つのベクトルデータファイルに記憶されるべき少なくとも 1 つの出力データフローパスにおける結果として生じるフィルタ処理された出力ベクトルデータサンプルセットとして、前記前の結果として生じるフィルタ処理された出力ベクトルデータサンプルセットを供給するための手段とを備える、装置。

【請求項 20】

ベクトル処理エンジン (VPE) においてフィルタベクトル処理動作を実行する方法であって、

前記フィルタベクトル処理動作のための少なくとも 1 つの入力データフローパス中に少なくとも 1 つのベクトルデータファイルから入力ベクトルデータサンプルセットをフェッチすることと、

前記少なくとも 1 つのベクトルデータファイルと少なくとも 1 つの実行ユニットとの間

10

20

30

40

50

の前記少なくとも 1 つの入力データフローパスに設けられた少なくとも 1 つのタップ付き遅延線中に前記少なくとも 1 つの入力データフローパスにおける前記フェッチされた入力ベクトルデータサンプルセットを受信することと、

複数の処理ステージの数が前記フィルタベクトル処理動作のフィルタタップの数に等しい、前記少なくとも 1 つの実行ユニット中の前記複数の処理ステージの処理ステージごとに、

前記入力ベクトルデータサンプルセットとして、シフトされた入力ベクトルデータサンプルセットを供給するように、前記入力ベクトルデータサンプルセット中の前記フィルタベクトル処理動作のための次のフィルタタップに前記少なくとも 1 つのタップ付き遅延線内の前記入力ベクトルデータサンプルセットをシフトすること、前記少なくとも 1 つのタップ付き遅延線は、前記フィルタベクトル処理動作におけるフィルタタップの数に等しい複数の処理ステージのうちの処理ステージごとに、複数のパイプラインレジスタにおいて、ベクトルデータサンプル幅ぶん前記入力ベクトルデータサンプルセットをシフトするように構成される、と、

現在の処理ステージにおいて、前記少なくとも 1 つの実行ユニットに、前記少なくとも 1 つの入力データフローパスにおいて前記少なくとも 1 つのタップ付き遅延線から前記シフトされた入力ベクトルデータサンプルセットを供給することと、

中間出力ベクトルデータサンプルセットを生成するために、前記現在の処理ステージにおいて前記少なくとも 1 つの実行ユニット中の前記シフトされた入力ベクトルデータサンプルセットに前記少なくとも 1 つの実行ユニット内のレジスタファイルから受信したフィルタ係数を乗算することと、

前記現在の処理ステージにおいて、前の結果として生じるフィルタ処理された出力ベクトルデータサンプルセットと前記中間出力ベクトルデータサンプルセットを累算することと、

前記少なくとも 1 つのベクトルデータファイルに、前記少なくとも 1 つのベクトルデータファイルに記憶されるべき少なくとも 1 つの出力データフローパスにおける結果として生じるフィルタ処理された出力ベクトルデータサンプルセットとして、前記前の結果として生じるフィルタ処理された出力ベクトルデータサンプルセットを供給することと

を備える、方法。

#### 【請求項 2 1】

前記入力ベクトルデータサンプルセット中の入力ベクトルデータサンプルの数が前記フィルタベクトル処理動作における前記フィルタタップの数より小さい場合、前記フィルタベクトル処理動作の間に前記少なくとも 1 つのベクトルデータファイルから前記入力ベクトルデータサンプルセットを再フェッチしないことを更に備える、

請求項 2 0 に記載の方法。

#### 【請求項 2 2】

前記入力ベクトルデータサンプルセット中の入力ベクトルデータサンプルの数が前記フィルタベクトル処理動作における前記フィルタタップの数より大きい場合、

前記フィルタベクトル処理動作のための前記少なくとも 1 つの入力データフローパス中に前記少なくとも 1 つのベクトルデータファイルから次の入力ベクトルデータサンプルセットをフェッチすることと、

前記少なくとも 1 つのタップ付き遅延線中に、前記少なくとも 1 つのベクトルデータファイルから、前記少なくとも 1 つの入力データフローパスにおける前記次のフェッチされた入力ベクトルデータサンプルセットを受信することと

をさらに備える、請求項 2 0 に記載の方法。

#### 【請求項 2 3】

複数のシャドウパイプラインレジスタ中に、前記少なくとも 1 つの入力データフローパス中の前記少なくとも 1 つのベクトルデータファイルから、次の入力ベクトルデータサンプルセットを受信することと、

前記シフトされた入力ベクトルデータサンプルセットを供給するために、プライマリタ

10

20

30

40

50

ップ付き遅延線に、処理ステージごとに前記複数のシャドウパイプラインレジスタにおいてベクトルデータサンプル幅ぶん前記次の入力ベクトルデータサンプルセットをシフトすることと

をさらに備え、

前記プライマリタップ付き遅延線は、前記複数の処理ステージ中の処理ステージごとに、前記少なくとも1つの実行ユニットに、前記少なくとも1つの入力データフローパスにおける前記シフトされた入力ベクトルデータサンプルセットを供給するように構成される

、

請求項20に記載の方法。

【請求項24】

10

前記少なくとも1つのタップ付き遅延線中の複数のパイプラインレジスタのうちの隣接パイプラインレジスタに前記シフトされた入力ベクトルデータサンプルセットを記憶するために、前記少なくとも1つのタップ付き遅延線中の前記隣接パイプラインレジスタ中に記憶された入力ベクトルデータサンプルと前記少なくとも1つのベクトルデータファイルからの前記入力ベクトルデータサンプルセットからの入力ベクトルデータサンプルとの間で選択することをさらに備える、

請求項20に記載の方法。

【請求項25】

20

前記少なくとも1つの実行ユニットによって実行されるベクトル命令に従って、前記少なくとも1つのタップ付き遅延線のためのプログラマブル入力データパス構成に基づいて、前記少なくとも1つの実行ユニットと前記少なくとも1つのベクトルデータファイルとの間の前記少なくとも1つの入力データフローパス中に前記少なくとも1つのタップ付き遅延線を選択的に供給することをさらに備える、

請求項20に記載の方法。

【請求項26】

前記少なくとも1つの実行ユニットによって実行される次のベクトル命令に従って、前記少なくとも1つのタップ付き遅延線のための前記プログラマブル入力データパス構成に基づいて、前記少なくとも1つの入力データフローパス中に選択的に供給されるように前記少なくとも1つのタップ付き遅延線を再構成することをさらに備える、

請求項25に記載の方法。

30

【請求項27】

前記少なくとも1つの実行ユニットによって実行される前記VPEのクロックサイクルごとに前記少なくとも1つの入力データフローパス中に選択的に供給されるように前記少なくとも1つのタップ付き遅延線を再構成することを備える、

請求項26に記載の方法。

【請求項28】

前記少なくとも1つの実行ユニットのためのプログラマブル入力データフローパス構成に基づいて、前記少なくとも1つの実行ユニット中の前記入力ベクトルデータサンプルセットとは異なるビット幅の入力ベクトルデータサンプルを処理することをさらに備える、

請求項20に記載の方法。

40

【請求項29】

前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットとして前記前の結果として生じるフィルタ処理された出力ベクトルデータサンプルセットを供給することは、

前記少なくとも1つのベクトルデータファイル中に一緒に記憶される前記少なくとも1つの出力データフローパス中の前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットのうちの実数の、結果として生じるフィルタ処理された出力ベクトルデータサンプルを供給すること、

前記実数の結果として生じるフィルタ処理された出力ベクトルデータサンプルと別個に、前記少なくとも1つのベクトルデータファイル中に一緒に記憶される前記少なくとも

50

1つの出力データフローパス中の前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットのうちの虚数の、結果として生じるフィルタ処理された出力ベクトルデータサンプルを供給することと

を備える、請求項20に記載の方法。

【請求項30】

前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットとして前記前の結果として生じるフィルタ処理された出力ベクトルデータサンプルセットを供給することは、

前記少なくとも1つのベクトルデータファイル中に一緒に記憶される前記少なくとも1つの出力データフローパス中の前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットのうちの偶数の、結果として生じるフィルタ処理された出力ベクトルデータサンプルを供給すること、10

前記偶数の、結果として生じるフィルタ処理された出力ベクトルデータサンプルと別個に、前記少なくとも1つのベクトルデータファイル中に一緒に記憶される前記少なくとも1つの出力データフローパス中の前記結果として生じるフィルタ処理された出力ベクトルデータサンプルセットのうちの奇数の、結果として生じるフィルタ処理された出力ベクトルデータサンプルを供給することと

を備える、請求項20に記載の方法。

【発明の詳細な説明】

【関連出願】

20

【0001】

[0001]本出願は、2013年3月13日に出願され、参照によりその全体が本明細書に組み込まれている、「VECTOR PROCESSING ENGINES HAVING PROGRAMMABLE DATA PATH CONFIGURATIONS FOR PROVIDING MULTI-MODE VECTOR PROCESSING, AND RELATED VECTOR PROCESSORS, SYSTEMS, AND METHODS」、123249と題する、米国特許出願第13/798,641号に関連する。

【0002】

[0002]本出願は、2013年3月13日に出願され、参照によりその全体が本明細書に組み込まれている、「VECTOR PROCESSING CARRY-SAVE ACCUMULATORS EMPLOYING REDUNDANT CARRY-SAVE FORMAT TO REDUCE CARRY PROPAGATION, AND RELATED VECTOR PROCESSORS, SYSTEMS, AND METHODS」、123248と題する、米国特許出願第13/798,618号に関連する。30

【0003】

[0003]本出願は、2013年11月15日に出願され、参照によりその全体が本明細書に組み込まれている、「VECTOR PROCESSING ENGINES (VPEs) EMPLOYING A TAPPED-DELAY LINE(S) FOR PROVIDING PRECISION FILTER VECTOR PROCESSING OPERATIONS WITH REDUCED SAMPLE REFETCHING AND POWER CONSUMPTION, AND RELATED VECTOR PROCESSOR SYSTEMS AND METHODS」、124362と題する、米国特許出願第14/082,075号にも関連する。40

【0004】

[0004]本出願は、2013年11月15日に出願され、参照によりその全体が本明細書に組み込まれている、「VECTOR PROCESSING ENGINES (VPEs) EMPLOYING TAPPED-DELAY LINE(S) FOR PROVIDING PRECISION CORRELATION/COVARIANCE

50

E VECTOR PROCESSING OPERATIONS WITH REDUCED SAMPLE RE-FETCHING AND POWER CONSUMPTION, AND RELATED VECTOR PROCESSOR SYSTEMS AND METHODS」、124364と題する、米国特許出願第14/082,079号にも関連する。

【0005】

[0005]本出願は、2013年11月15日に出願され、参照によりその全体が本明細書に組み込まれている、「VECTOR PROCESSING ENGINES (VPEs) EMPLOYING REORDERING CIRCUITRY IN DATA FLOW PATHS BETWEEN EXECUTION UNITS AND VECTOR DATA MEMORY TO PROVIDE IN-FLIGHT REORDERING OF OUTPUT VECTOR DATA STORED TO VECTOR DATA MEMORY, AND RELATED VECTOR PROCESSOR SYSTEMS AND METHODS」、124450と題する、米国特許出願第14/082,081号にも関連する。

【0006】

[0006]本出願は、2013年11月15日に出願され、参照によりその全体が本明細書に組み込まれている、「VECTOR PROCESSING ENGINES (VPEs) EMPLOYING MERGING CIRCUITRY IN DATA FLOW PATHS BETWEEN EXECUTION UNITS AND VECTOR DATA MEMORY TO PROVIDE IN-FLIGHT MERGING OF OUTPUT VECTOR DATA STORED TO VECTOR DATA MEMORY, AND RELATED VECTOR PROCESSING INSTRUCTIONS, SYSTEMS, AND METHODS」、124363U1と題する、米国特許出願第14/082,073号にも関連する。

【0007】

[0007]本出願は、2013年11月15日に出願され、参照によりその全体が本明細書に組み込まれている、「VECTOR PROCESSING ENGINES (VPEs) EMPLOYING DESPREADING CIRCUITRY IN DATA FLOW PATHS BETWEEN EXECUTION UNITS AND VECTOR DATA MEMORY TO PROVIDE IN-FLIGHT DESPREADING OF SPREAD-SPECTRUM SEQUENCES, AND RELATED VECTOR PROCESSING INSTRUCTIONS, SYSTEMS, AND METHODS」、124363U2と題する、米国特許出願第14/082,067号にも関連する。

【技術分野】

【0008】

[0008]本開示の分野は、単一命令多重データ(SIMD)プロセッサと多重命令多重データ(MIMD)プロセッサとを含む、ベクトル演算とスカラー演算とを処理するためのベクトルプロセッサおよび関連システムに関する。

【背景技術】

【0009】

[0009]ワイヤレスコンピューティングシステムは、デジタル情報領域において最も普及した技術の1つに急速になりつつある。技術における進歩により、ワイヤレス通信デバイスは、より小型でより強力になった。たとえば、ワイヤレスコンピューティングデバイスには、一般に、小型で軽量な、ユーザが容易に持ち運べるポータブルワイヤレス電話、携帯情報端末(PDA)、およびページングデバイスが含まれる。より具体的には、携帯電話およびインターネットプロトコル(IP)電話などのポータブルワイヤレス電話は、ワイヤレスネットワークを介して音声とデータパケットとを通信することができる。さらに

10

20

30

40

50

、多くのそのようなワイヤレス通信デバイスには、他のタイプのデバイスが含まれる。たとえば、ワイヤレス電話には、デジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダ、および／またはオーディオファイルプレーヤが含まれ得る。また、ワイヤレス電話は、インターネットにアクセスするために使用され得るウェブインターフェースを含むことができる。さらに、ワイヤレス通信デバイスは、設計されたワイヤレス通信技術規格（たとえば、符号分割多元接続（C D M A）、広帯域C D M A（W C D M A（登録商標））、およびロングタームエボリューション（L T E（登録商標）））に従って高速ワイヤレス通信データを処理するための複合処理リソースを含む場合がある。そのため、これらのワイヤレス通信デバイスはかなりのコンピューティング能力を含む。

【0010】

10

[0010]ワイヤレスコンピューティングデバイスは、より小型でより強力になるにつれて、ますますリソースの制約を受けるようになる。たとえば、画面サイズ、利用可能なメモリおよびファイルシステム空間の量、ならびに入出力能力の量は、デバイスの小さいサイズによって制限される場合がある。さらに、バッテリサイズ、バッテリによって供給される電力の量、およびバッテリの寿命も制限される。デバイスのバッテリ寿命を増やすための1つの方法は、より少ない電力を消費するプロセッサを設計することである。

【0011】

20

[0011]この関連で、ベクトルプロセッサを含むベースバンドプロセッサが、ワイヤレス通信デバイスに利用され得る。ベクトルプロセッサは、ベクトル、すなわちデータのアレイに働く高水準の演算を提供するベクトルアーキテクチャを有する。ベクトル処理は、1つのデータセットに対してベクトル命令を実行し、次いで、ベクトル内の後続要素のためにベクトル命令を再フェッチし復号することとは対照的に、ベクトル命令を1度フェッチし、次いで、データ要素のアレイ全体にわたってベクトル命令を複数回実行することを伴う。このプロセスにより、他の要因の中でも、各ベクトル命令はより少ない回数しかフェッチされる必要がないので、プログラムを実行するために必要とされるエネルギーの低減が可能になる。ベクトル命令は、同時に複数のクロック周期にわたって長いベクトルに対して動作するので、簡易な順序ベクトル命令ディスパッチを用いて、高度の並列性が達成可能である。

【0012】

30

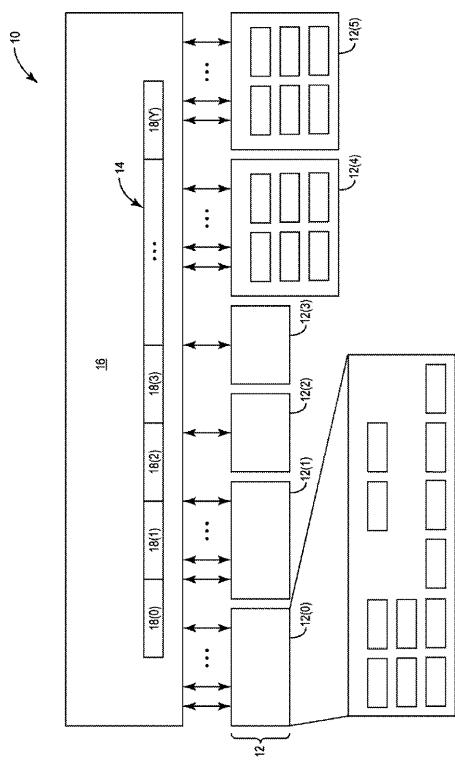

[0012]図1は、ワイヤレスコンピュータデバイスなどのコンピューティングデバイス内で利用され得る例示的なベースバンドプロセッサ10を示す。ベースバンドプロセッサ10は、特定のアプリケーションのための関数固有ベクトル処理を提供することに各々が専用化された複数の処理エンジン（P E）12を含む。この例では、6つの別個のP E12（0）～P E12（5）がベースバンドプロセッサ10内に設けられる。P E12（0）～P E12（5）は各々、共有メモリ16からP E12（0）～P E12（5）に供給される固定Xビット幅のベクトルデータ14に対してベクトル処理を提供するように構成される。たとえば、ベクトルデータ14は512ビット幅であり得る。ベクトルデータ14は、Xのより小さい倍数のビット幅のベクトルデータサンプルセット18（0）～18（Y）（たとえば、16ビットおよび32ビットのサンプルセット）内で定義され得る。このようにして、P E12（0）～P E12（5）は、高度の並列性を達成するために、P E12（0）～P E12（5）に並列に供給される複数のベクトルデータサンプルセット18に対するベクトル処理を提供することが可能である。各P E12（0）～P E12（5）は、ベクトルデータ14上で処理されるベクトル命令の結果を記憶するためのベクトルレジスタファイル（V R）を含む場合がある。

40

【0013】

[0013]図1のベースバンドプロセッサ10内の各P E12（0）～P E12（5）は、特定のタイプの固定演算を効率的に実行するように特に設計された、特定の専用回路とハードウェアとを含む。たとえば、図1のベースバンドプロセッサ10は、別個のW C D M AのP E12（0）、P E12（1）と、L T EのP E12（4）、P E12（5）とを含むが、これは、W C D M AおよびL T Eが異なるタイプの特殊な演算を伴うからである

50

。したがって、別個のWCDMA固有PE12(0)、PE12(1)とLTE固有PE12(4)、PE12(5)とを設けることによって、PE12(0)、PE12(1)、PE12(4)、PE12(5)の各々は、高効率演算のための、WCDMAおよびLTE用の頻繁に実行される関数に固有の特殊な専用回路を含むように設計され得る。この設計は、効率的でない方式ではあるが、より多数の無関係な演算をサポートするために柔軟であるように設計された、より一般的な回路とハードウェアとを含むスカラー処理エンジンとは対照的である。

#### 【0014】

[0014]特殊ベクトル処理動作の1つのタイプは、フィルタリングである。フィルタ動作は、サンプリングされた入力時間関数の重畠の量子化時間領域表現と、フィルタの重み付け関数の表現とを計算する。時間領域内の重畠は、周波数領域内の乗算に対応する。このように、デジタルフィルタは、間隔が均一なサンプル間隔で実行される乗算および加算の拡張シーケンスにより実現され得る。デジタル化入力信号は、加算器（アダー）、遅延サンプル、および乗算器にクロックされたデータをシフトする構造を通じてデジタル化入力信号サンプルを渡すことによってPEにおいてフィルタされ得る。

たとえば、有限インパルス応答（FIR）フィルタは、フィルタ関数を計算するために、「N」計算フィルタ係数を有する遅延線上の遅延タップの有限数（「N」）を使用して実施され得る。

#### 【0015】

[0015]しかしながら、フィルタリング演算は、ベクトルプロセッサにおいて供給される特殊データフローパスに起因して、ベクトルプロセッサにおいて並列化することは困難であり得る。フィルタリングされるべき入力ベクトルデータサンプルセットが、フィルタ遅延タップの間でシフトされると、入力ベクトルデータサンプルセットは、ベクトルデータファイルから再フェッチされ、したがって電力消費が増大し、スループットが低減される。メモリからの入力ベクトルデータサンプルセットの再フェッチを最小化するために、データフローパスは、効率的な並列化処理のために、遅延タップと同じ数の乗算器を設けるように構成される可能性がある。しかしながら、他のベクトル処理動作は、より少ない乗算器を要求し、その結果、データフローパス内の乗算器の非効率的なスケーリングおよび過少利用がもたらされる。スケーラビリティを供給するために、乗算器の数がフィルタ遅延タップの数よりも少なくなるように削減された場合、フィルタ処理の様々なフェーズに対して同じ入力ベクトルデータサンプルセットを取得するために、メモリにより多くの再フェッチが必要とされることによって、並列化が制限される。

#### 【発明の概要】

#### 【0016】

[0016]再フェッチおよび電力消費が低減される精度フィルタベクトル処理動作を供給するためのタップ付き遅延線を利用するベクトル処理エンジン（VPE）が開示される。関連するベクトル処理システムおよび方法がさらに開示される。本願に開示されるVPEは、フィルタ係数を持つ入力ベクトルデータサンプルセットの乗算および結果の累算を含む。電力消費を低減するために、メモリからの入力ベクトルデータサンプルの再フェッチを最小化するために、タップ付き遅延線は、ベクトルデータファイルとVPE中の実行ユニットとの間のデータフローパス中に含まれる。タップ付き遅延線は、フィルタベクトル処理動作を実行するための実行ユニットに入力ベクトルデータサンプルセットを受信し供給するように構成される。タップ付き遅延線は、各フィルタ遅延タップのための入力ベクトルデータサンプルをシフトすることと、実行ユニットにシフトされた入力ベクトルデータサンプルセットを供給することとを行うようにさらに構成され、シフトされた入力ベクトルデータサンプルセットは、フィルタベクトル処理動作の各処理ステージの間のベクトルデータファイルから再フェッチされることはない。この方法では、低減される再フェッチ動作は、電力消費を低減する。さらにVPE中のデータフローパスの効率は、メモリからの入力ベクトルデータサンプルセットの再フェッチ遅延によって制限されない。このシフトされた入力ベクトルデータサンプルセットは、実行ユニットに局在するように設けられ

10

20

30

40

50

る。実行ユニット中のベクトル処理は、データフローの制限ではなく、コンピュータリソースのみによって制限される。さらに、フィルタベクトル処理動作は、実行ユニットの中間フィルタステージのための累算がメモリ中に格納されないので、より正確であり、実行ユニットがメモリから再フェッチされるべきシフトされた入力フィルタサンプルデータを待つ間に、結果として丸められる。

【0017】

[0017]さらに、本願に開示されるタップ付き遅延線を利用するVPE中のフィルタベクトル処理動作は、フィルタ遅延タップと同じ数の乗算器を要求すること無しに完全に並列化することができる。これは、タップ付き遅延線がベクトルデータファイルからの入力ベクトルデータサンプルセットの再フェッチからの遅延を被ること無しにフィルタ処理のための実行ユニットに、シフトされた入力ベクトルデータサンプルを供給することができるからである。フィルタタップ遅延より少ない乗算器でフィルタベクトル処理動作の並列化を許容することによって、VPEのデータフローパスは、より少ない乗算器を要求するベクトル処理動作の他のタイプのために予約された乗算器の数を簡単にスケールダウンするように再プログラムすることができ、そのため、VPEの乗算器は、効率的な目的のために過少利用されることはない。例えば、VPE中のデータフローパスがベクトル処理動作の他のタイプのために要求されるより、フィルタベクトル処理動作のために多くの乗算器の数を利用するように構成される場合、追加の乗算器は、これらの他のベクトル処理動作の実行の間使用され得ず、その結果、VPEの乗算器処理リソースを過少利用することになる。

10

【0018】

[0018]この関連で、一実施形態では、フィルタベクトル処理動作を供給するように構成されたVPEが供給される。VPEは、少なくとも1つのベクトルデータファイルを備える。ベクトルデータファイルは、フィルタベクトル処理動作のための少なくとも1つの入力データフローパス中の入力ベクトルデータサンプルセットを供給するように構成される。ベクトルデータファイルはまた、少なくとも1つの出力データフローパスからの結果として生じるフィルタ化出力ベクトルデータサンプルセットを受信するように構成される。ベクトルデータファイルはまた、結果として生じるフィルタ化出力ベクトルデータサンプルセットを記憶するようにさらに構成される。VPEはまた、少なくとも1つの入力データフローパス中の少なくとも1つの実行ユニットと少なくとも1つのベクトルデータファイルとの間に供給される少なくとも1つのタップ付き遅延線を備える。タップ付き遅延線は、複数の処理ステージの中の各処理ステージのためのシフトされた入力ベクトルデータサンプルセットを供給するために、フィルタベクトル処理動作中のフィルタタップの数と等しい複数の処理ステージの中の各処理ステージのための複数のパイプラインレジスタ中のベクトルデータサンプルセットで入力ベクトルデータサンプルセットをシフトするように構成される。

20

【0019】

[0019]さらに、VPEはまた、少なくとも1つの入力データフローパス中に供給される少なくとも1つの実行ユニットを備える。実行ユニットは、フィルタベクトル処理動作の各フィルタタップのためのフィルタタップ出力ベクトルデータサンプルセットを生成するために、複数の処理ステージの中の各処理ステージのためのシフトされた入力ベクトルデータサンプルセット上にフィルタタップ動作を適用するように構成された少なくとも1つの乗算器を備える。実行ユニットはまた、複数の処理ステージの中の各処理ステージのための少なくとも1つの累算器中のフィルタタップ出力ベクトルデータサンプルセットを累算するように構成された少なくとも1つの累算器を備える。実行ユニットは、少なくとも1つの出力データフローパス上の結果として生じるフィルタ化出力ベクトルデータサンプルセットを供給するように構成される。この方法では、非限定的な例として、実行ユニットは、入力ベクトルデータサンプルセットがベクトルデータファイルからの再フェッチされずに、複数の処理ステージの中の各処理ステージのためのフィルタタップ出力ベクトルデータサンプルセットを累算するように構成される。

30

40

50

## 【0020】

[0020]別の実施形態では、フィルタベクトル処理動作を供給するように構成された VPE が供給される。VPE は、少なくとも 1 つのベクトルデータファイル手段を備える。ベクトルデータファイル手段は、フィルタベクトル処理動作のための少なくとも 1 つの入力データフローパス手段中に入力ベクトルデータサンプルセットを供給するための手段を備える。ベクトルデータファイル手段はさらに、記憶されるべき、少なくとも 1 つの出力データフローパス手段から結果として生じるフィルタ化出力ベクトルデータサンプルセットを受信するための手段を備える。VPE はさらに、少なくとも 1 つのベクトルデータファイル手段と少なくとも 1 つの入力データフロー手段中の少なくとも 1 つの実行ユニットとの間に設けられた少なくとも 1 つのタップ付き遅延線手段を備える。タップ付き遅延線手段は、複数の処理ステージの中の各処理ステージのためのシフトされた入力ベクトルベクトルデータサンプルセットを供給するために、フィルタベクトル処理動作中のフィルタタップの数に等しい、複数の処理ステージの中の各処理ステージのための複数のパイプラインレジスタ中のベクトルデータサンプル幅ぶん、入力ベクトルデータサンプルセットをシフトするための手段を備える。10

## 【0021】

[0021]さらに、VPE はまた、少なくとも 1 つの入力データフローパス中に供給される少なくとも 1 つの実行ユニット手段を備える。実行ユニット手段は、フィルタベクトル処理動作の各フィルタタップのためのフィルタタップ出力ベクトルデータサンプルセットを生成するために、複数の処理ステージの中の各処理ステージのためのシフトされた入力ベクトルデータサンプルセット上にフィルタタップ動作を適用するための手段を備える。実行ユニット手段は、複数の処理ステージの中の各処理ステージのための少なくとも 1 つの累算器においてフィルタタップ出力ベクトルデータサンプルセットを累算するための手段を備える。実行ユニット手段はさらに、フィルタベクトル処理動作ための少なくとも 1 つの出力データフローパス手段上に結果として生じるフィルタ化出力ベクトルデータサンプルを供給するための手段を備える。20

## 【0022】

[0022]別の実施形態では、VPE においてフィルタベクトル処理動作を実行する方法が供給される。方法は、フィルタベクトル処理動作のための少なくとも 1 つの入力データフローパス中に少なくとも 1 つのベクトルデータファイルからの入力ベクトルデータサンプルセットをフェッチすることを備える。方法はさらに、少なくとも 1 つのベクトルデータファイルと少なくとも 1 つの実行ユニットとの間の少なくとも 1 つの入力データフローパス中に設けられる少なくとも 1 つのタップ付き遅延線中に少なくとも 1 つの出力データフローパス中のフェッチされた入力ベクトルデータサンプルセットを受信することを備える。複数の処理ステージの数がフィルタベクトル処理動作のフィルタタップの数に等しい、少なくとも 1 つの実行ユニット中の複数の処理ステージの各処理ステージに対して、方法はさらに、現在の処理ステージ中の少なくとも 1 つの実行ユニットに、少なくとも 1 つの入力データフローパス中の少なくとも 1 つのタップ付き遅延線から入力ベクトルデータサンプルセットを供給することと、フィルタタップ出力ベクトルデータサンプルセットを生成するために、現在の処理ステージ中の少なくとも 1 つの実行ユニット中の入力ベクトルデータサンプルセット上にフィルタタップ動作を適用することと、現在の処理ステージ中の前の結果として生じるフィルタ化出力ベクトルデータサンプルセットとフィルタタップ出力ベクトルデータサンプルセットを累算することと、前の結果として生じるフィルタ化出力ベクトルデータサンプルセットを供給することと、入力ベクトルデータサンプルセットとしてシフトされた入力ベクトルデータサンプルセットを供給するために、入力ベクトルデータサンプルセット中のフィルタベクトル処理動作のための次のフィルタタップに少なくとも 1 つのタップ付き遅延線内の入力ベクトルデータサンプルセットをシフトすることとを備える。方法はさらに、少なくとも 1 つのベクトルデータファイル中に記憶されるべき少なくとも 1 つのベクトルデータファイルに、少なくとも 1 つの出力データフローパス中の結果として生じるフィルタ化出力ベクトルデータサンプルセットとして前の結果と304050

して生じるフィルタ化出力ベクトルデータサンプルセットを供給することを備える。

【図面の簡単な説明】

【0023】

【図1】特定のアプリケーション向けの関数固有ベクトル処理を提供するために各々が専用化された、複数のベクトル処理エンジン（VPE）を含む例示的なベクトルプロセッサの概略図。

【図2】VPE内に設けられた共通の回路およびハードウェアが、別個のVPEを設ける必要なしに複数のアプリケーションまたは技術のために、特定のタイプのベクトル演算を高効率な方式で実行するために複数のモードでプログラムされ得るように、プログラム可能なデータパス構成を有するVPEを含む例示的なベースバンドプロセッサの概略図。 10

【図3】VPEによってサポートされるフィルタベクトル処理動作において提供され得るディスクリート有限インパルス応答（FIR）フィルタの概略図。

【図4】再フェッチおよび電力消費が低減される精度フィルタベクトル処理動作を提供するためのフィルタ係数データを用いて処理されるべきシフトされた入力ベクトルデータサンプルセットを受信し、実行ユニットに供給するためにタップ付き遅延線を利用する例示的なVPEの概略図。

【図5】例示的なフィルタベクトル命令に従って図4のVPEにおいて実行され得る例示的なフィルタベクトル処理動作を示すフローチャート。

【図6A】図4のVPE内のレジスタファイルに記憶されたフィルタタップ係数の概略図。 20

【図6B】図4のVPE内のベクトルデータファイルに記憶された例示的な入力ベクトルデータサンプルセットの概略図。

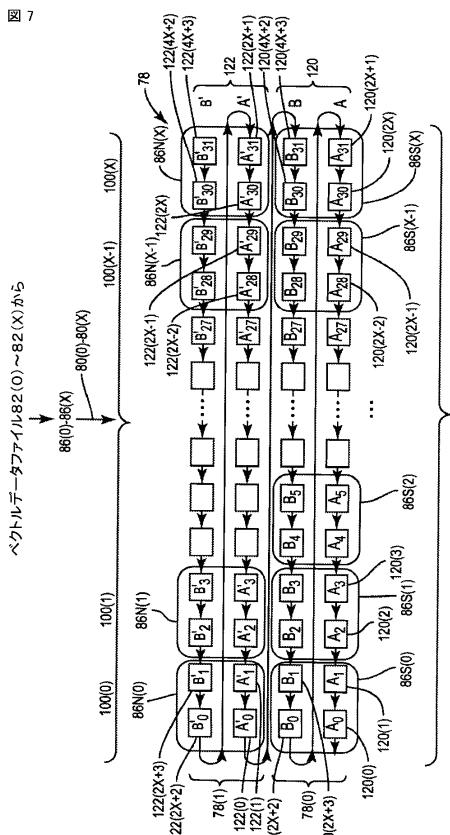

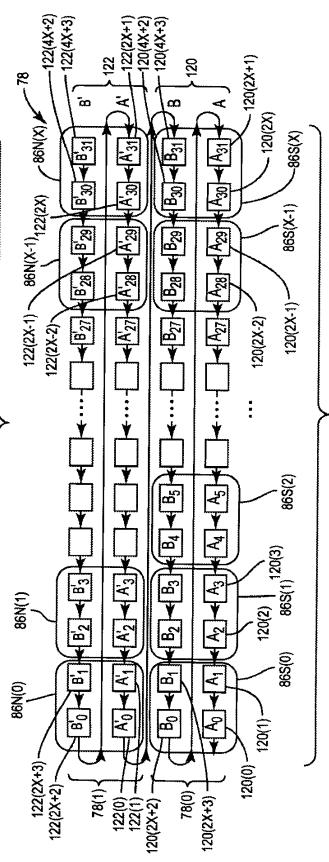

【図7】図4のVPEにおいて提供され得る例示的なタップ付き遅延線とオプションのシャドウタップ付き遅延線とを示す概略図であって、例示的なタップ付き遅延線が、各々、VPEによって実行されるフィルタベクトル処理動作の間に、ベクトルデータメモリからの入力ベクトルデータサンプルセットとシフトされた入力ベクトルデータサンプルセットとを受信し、実行ユニットに供給するための複数のパイプラインレジスタを備える、概略図。

【図8】フィルタベクトル処理動作の間に入力ベクトルデータサンプルセット内の入力ベクトルデータサンプルをシフトするためのパイプラインレジスタの中のレーン内およびレーン間のルーティングを含む、データレーン内のパイプラインレジスタの例示的な詳細を示す、図7のタップ付き遅延線のより例示的な詳細を示す概略図。 30

【図9A】例示的な8タップフィルタベクトル処理動作の第1のフィルタタップ実行の一部として、図4のVPE内のプライマリタップ付き遅延線に最初に記憶された入力ベクトルデータサンプルセットの概略図。

【図9B】レジスタファイルに記憶されたフィルタタップ係数、および図9Aに示された例示的な8タップフィルタベクトル処理動作フィルタベクトル処理動作の第1のフィルタタップ実行の一部として、図4のVPE内のシャドウタップ付き遅延線に最初に記憶されたシャドウ入力ベクトルデータサンプルセットの概略図。

【図9C】例示的な8タップフィルタベクトル処理動作の第2のフィルタタップ実行の一部として、図4のVPE内のプライマリタップ付き遅延線およびシャドウタップ付き遅延線に記憶された、シフトされた入力ベクトルデータサンプルセット、ならびにレジスタファイルに記憶されたフィルタタップ係数の概略図。 40

【図9D】例示的な8タップフィルタベクトル処理動作の第8のフィルタタップ実行の一部として、図4のVPE内のプライマリタップ付き遅延線およびシャドウタップ付き遅延線に記憶された、シフトされた入力ベクトルデータサンプルセット、ならびにレジスタファイルに記憶されたフィルタタップ係数の概略図。

【図10】例示的な8タップフィルタベクトル処理動作が完全に実行された後の図4のVPE内の実行ユニットの累算器のコンテンツの概略図。

【図11】再フェッチおよび電力消費が低減される精度相関／共分散ベクトル処理動作を 50

提供するために、シーケンス番号データを用いて処理されるべきシフトされた入力ベクトルデータサンプルセットを受信し、実行ユニットに供給するためにタップ付き遅延線を利用する例示的なVPEの概略図。

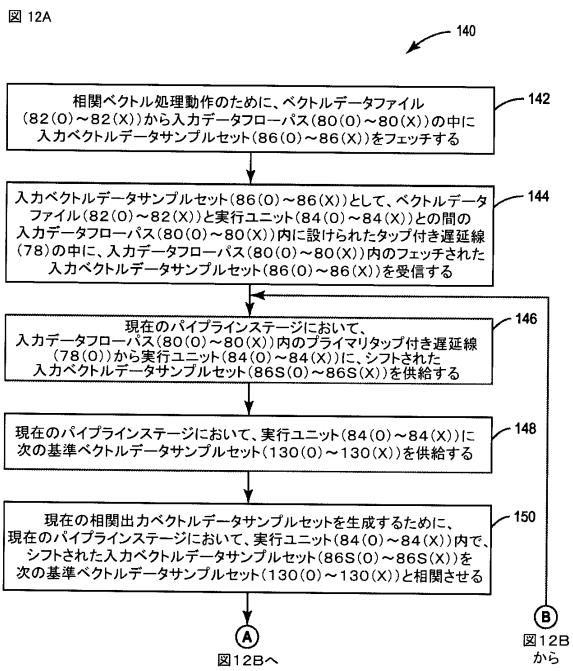

【図12A】例示的な相関／共分散ベクトル処理動作に従って、インターリープされたオンタイムおよび後発の入力ベクトルデータサンプルセットがフェッチされる、図11のVPE内で並列に実行され得る例示的な相関／共分散ベクトル処理動作を示すフローチャート。

【図12B】例示的な相関／共分散ベクトル処理動作に従って、インターリープされたオンタイムおよび後発の入力ベクトルデータサンプルセットがフェッチされる、図11のVPE内で並列に実行され得る例示的な相関／共分散ベクトル処理動作を示すフローチャート。10

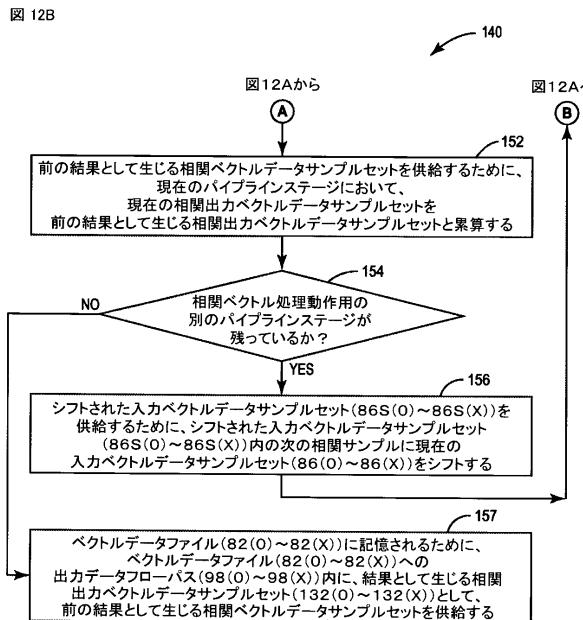

【図13】図11のVPE内のレジスタファイルに記憶された相関／共分散入力ベクトルデータサンプルセットの概略図。

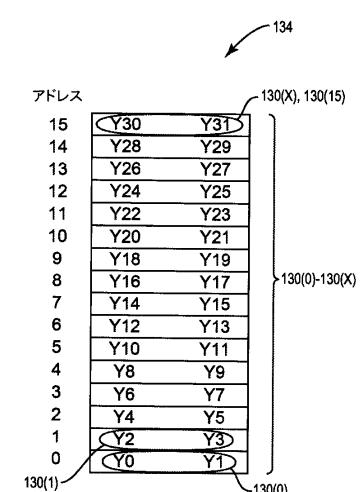

【図14】図11のVPE内に設けられ得る例示的なタップ付き遅延線とオプションのシャドウタップ付き遅延線とを示す概略図であって、例示的なタップ付き遅延線が、各々、VPEによって実行される相関／共分散ベクトル処理動作の間に、ベクトルデータメモリからの入力ベクトルデータサンプルセットとシフトされた入力ベクトルデータサンプルセットとを受信し、実行ユニットに供給するための複数のパイプラインレジスタを備える、概略図。

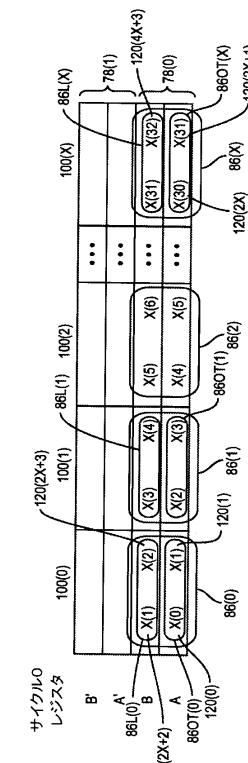

【図15A】相関／共分散ベクトル処理動作の第1の処理ステージの一部として、図11のVPE内のプライマリタップ付き遅延線に最初に供給されたベクトルデータファイルからの入力ベクトルデータサンプルセットの概略図。20

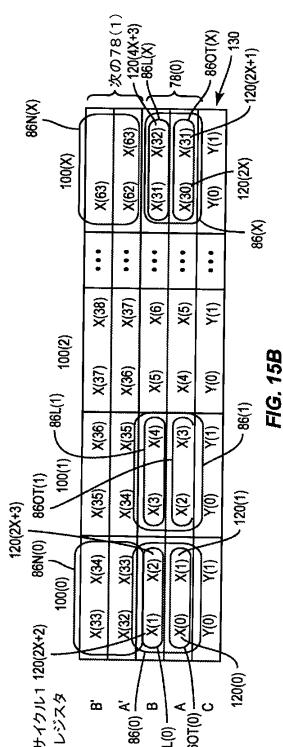

【図15B】相関／共分散ベクトル処理動作の第1の処理ステージの一部として、図11のVPE内のシャドウタップ付き遅延線に最初に供給されたベクトルデータファイルからのシャドウ入力ベクトルデータサンプルセットの概略図。

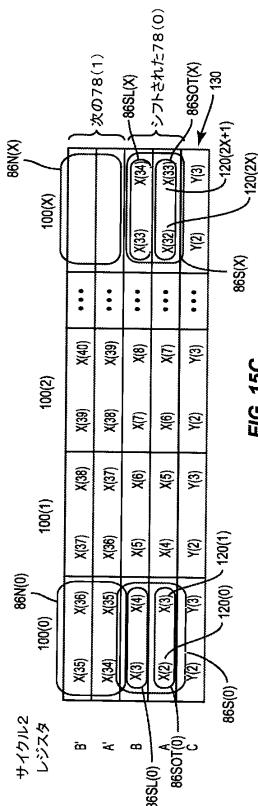

【図15C】相関／共分散ベクトル処理動作の第2の処理ステージの一部として、図11のVPE内のプライマリタップ付き遅延線およびシャドウタップ付き遅延線に記憶された、シフトされた入力ベクトルデータサンプルセット、ならびにレジスタファイルに記憶されたシフトされた入力ベクトルデータサンプルセットの概略図。

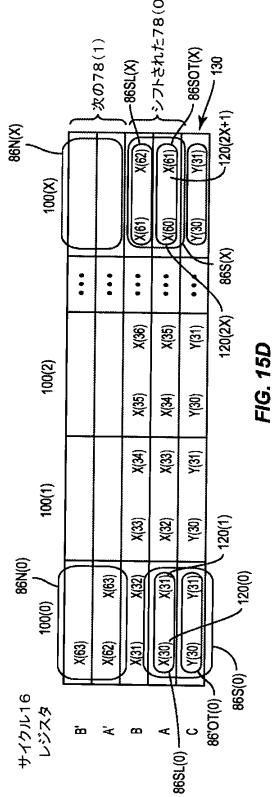

【図15D】相関／共分散ベクトル処理動作の第14の処理ステージの一部として、図11のVPE内のプライマリタップ付き遅延線およびシャドウタップ付き遅延線に記憶された、シフトされた入力ベクトルデータサンプルセット、ならびにレジスタファイルに記憶されたシフトされた入力ベクトルデータサンプルセットの概略図。30

【図16】例示的な相関／共分散ベクトル処理動作が完全に実行された後の図11のVPE内の実行ユニットの累算器のコンテンツの概略図。

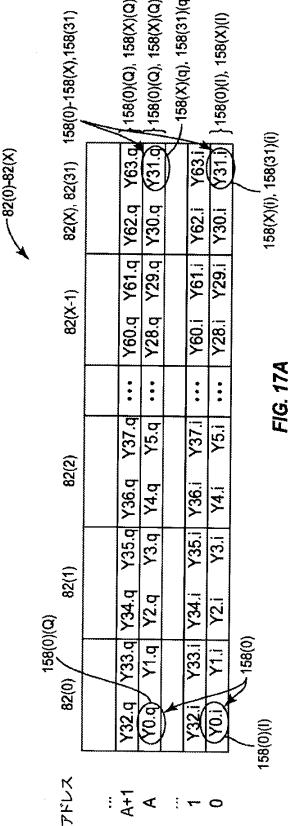

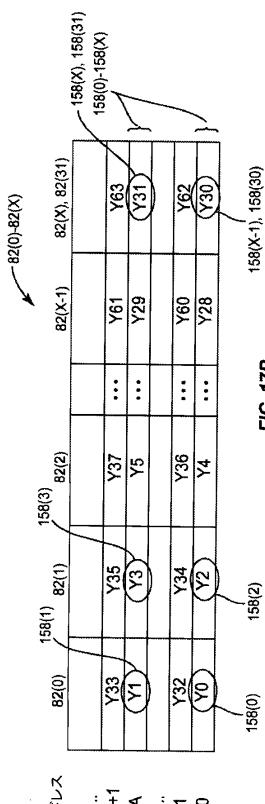

【図17A】別々に記憶された、結果として生じるフィルタ出力ベクトルデータサンプルの実数成分および虚数成分に記憶された、結果として生じるフィルタ出力ベクトルデータサンプルセットを示す例示的なベクトルデータファイルの図。

【図17B】別々に記憶されたその偶数および奇数の、結果として生じるフィルタ出力ベクトルデータサンプルとともに記憶された、結果として生じるフィルタ出力ベクトルデータサンプルセットを示す例示的なベクトルデータファイルの図。40

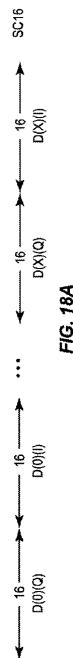

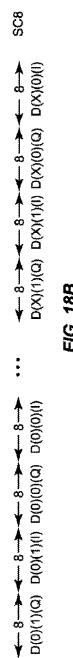

【図18A】符号付き複素数の16ビットフォーマットでVPEのベクトルデータファイルに記憶されたベクトルデータサンプルセットの例示的なインターリープされたベクトルデータサンプルの図。

【図18B】符号付き複素数の8ビットフォーマットでVPEのベクトルデータファイルに記憶されたベクトルデータサンプルセットの例示的なインターリープされたベクトルデータサンプルの図。

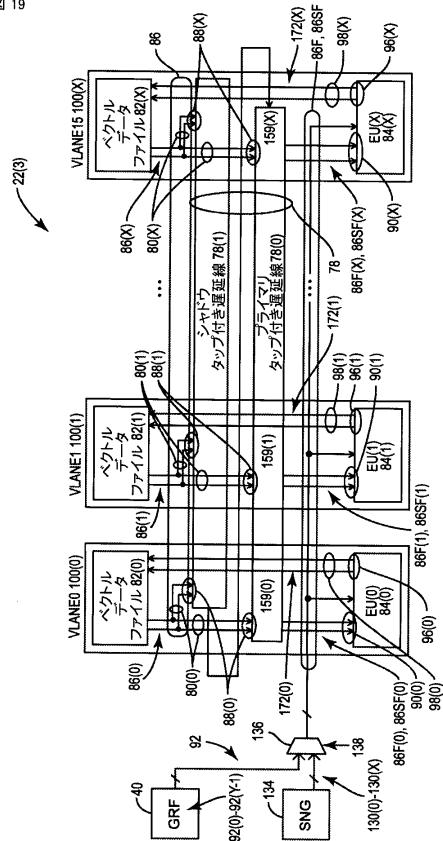

【図19】ベクトル処理動作を実行するための少なくとも1つの実行ユニットにフォーマット変換された入力ベクトルデータサンプルセットを供給するために、入力ベクトルデータサンプルセットがベクトルデータファイルから再フェッチされる必要なしに、ベクトル

データファイルと少なくとも 1 つの実行ユニットとの間の少なくとも 1 つの入力データフローパスにおいて、入力ベクトルデータサンプルセットのインフライトフォーマット変換を提供するように構成されたフォーマット変換回路を利用する例示的な VPE の概略図。

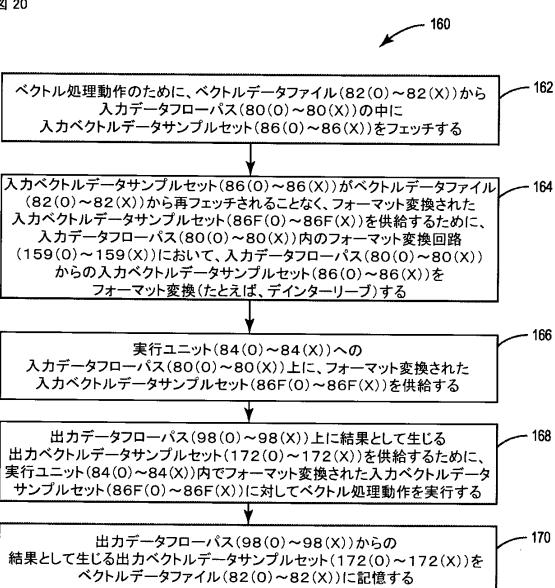

【図 20】図 19 の VPEにおいて実行され得る、ベクトルデータファイルと少なくとも 1 つの実行ユニットとの間の少なくとも 1 つの入力データフローパスにおける入力ベクトルデータサンプルセットの例示的なインフライトフォーマット変換を示すフローチャート。

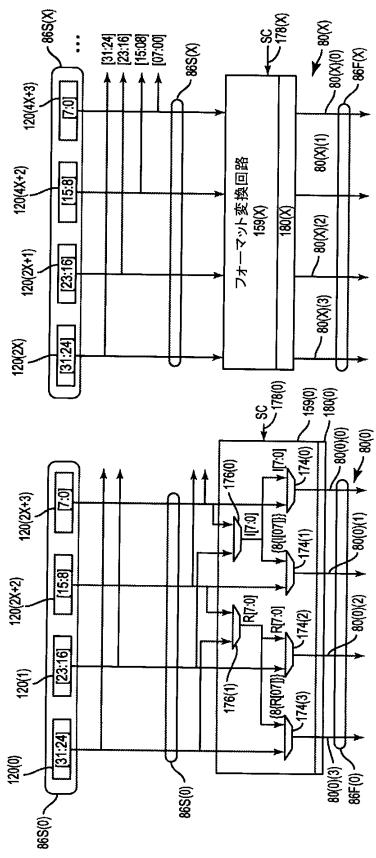

【図 21】図 19 の VPE 内のタップ付き遅延線と実行ユニットとの間に設けられた例示的なフォーマット変換回路の概略図であって、フォーマット変換回路が実行ユニットへの入力データフローパス内のタップ付き遅延線によって供給される入力ベクトルデータサンプルセットのインフライトフォーマット変換を提供するように構成される、概略図。 10

【図 22】実行ユニットにおける受信前に入力データフローパス内で入力ベクトルデータサンプルセットのインフライトフォーマット変換を提供するために、図 19 の VPE にプログラミングを提供する例示的なベクトル命令データフォーマットを示す図。

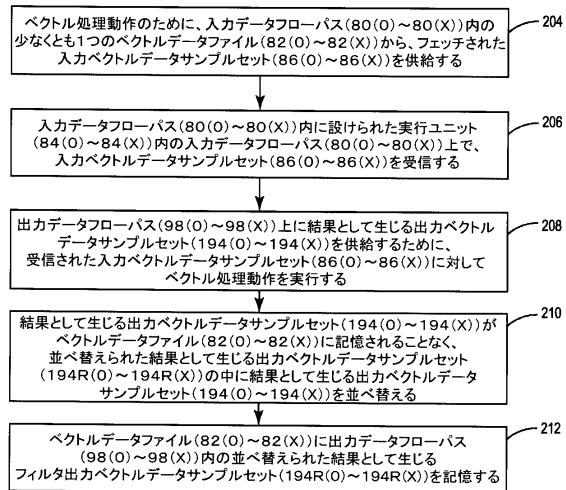

【図 23】並び替えられた、結果として生じる出力データサンプルセットを供給し記憶するために、結果として生じる出力ベクトルデータサンプルセットが少なくとも 1 つのベクトルデータファイルに記憶されずに、少なくとも 1 つの実行ユニットと少なくとも 1 つのベクトルデータファイルとの間の少なくとも 1 つの出力データフローパスにおいて、結果として生じる出力ベクトルデータサンプルセットのインフライト並び替えを提供するように構成された並び替え回路を利用する例示的な VPE の概略図。 20

【図 24】ベクトルデータファイルに並び替えた形式で記憶される図 23 の VPE 内のベクトルデータファイルと少なくとも 1 つの実行ユニットとの間の少なくとも 1 つの出力データフローパスにおける出力ベクトルデータサンプルセットの例示的なインフライトディンターリービングを示すフローチャート。

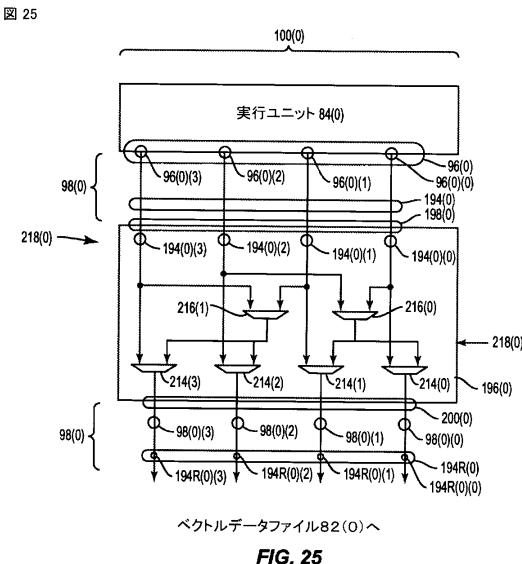

【図 25】ベクトルデータファイルに記憶された出力ベクトルデータサンプルセットのインフライト並び替えを提供するために、実行ユニットとベクトルデータファイルとの間の出力データフローパス内の並び替え回路を利用する例示的な VPE の概略図。

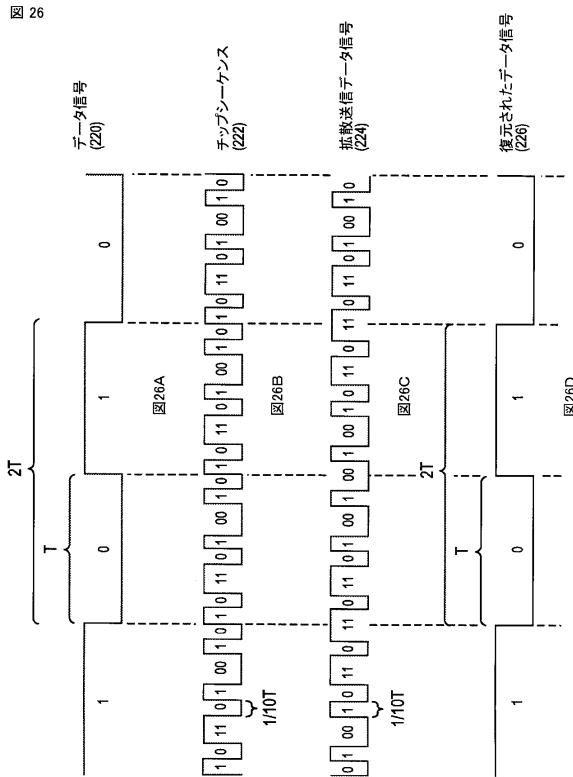

【図 26】図 26 A は、通信信号を表す例示的なベクトルデータサンプルシーケンスの図である。 図 26 B は、例示的な符号分割多元接続 (CDMA) チップシーケンスの図である。 図 26 C は、図 26 B の CDMA チップシーケンスで拡散された後の図 26 A のベクトルデータサンプルシーケンスの図である。 図 26 D は、図 26 A の元のベクトルデータサンプルシーケンスを復元するために、図 26 B の CDMA チップシーケンスで図 26 C の拡散されたベクトルデータサンプルシーケンスを逆拡散する図である。 30

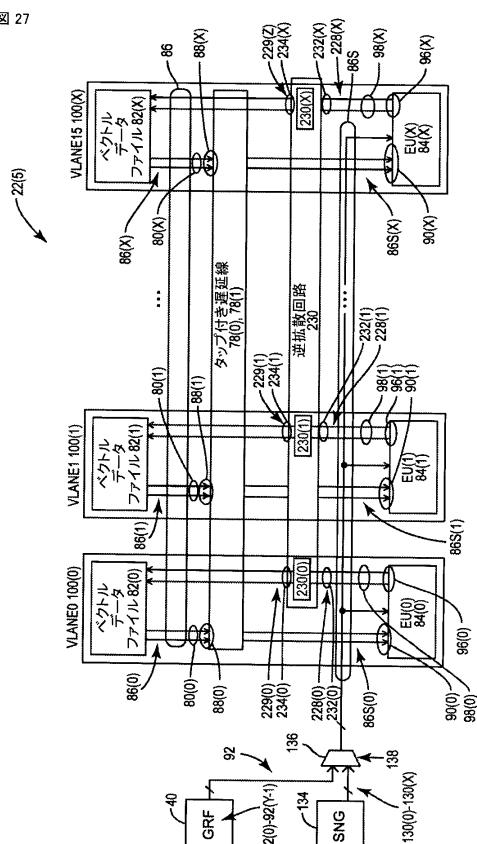

【図 27】逆拡散された、結果として生じる出力ベクトルデータサンプルセットを供給し記憶するために、結果として生じる出力ベクトルデータサンプルセットが少なくとも 1 つのベクトルデータファイルに記憶されずに、少なくとも 1 つの実行ユニットと少なくとも 1 つのベクトルデータファイルとの間の少なくとも 1 つの出力データフローパスにおいて、結果として生じる出力ベクトルデータサンプルセットの逆拡散を提供するように構成された逆拡散回路を利用する例示的な VPE の概略図。 40

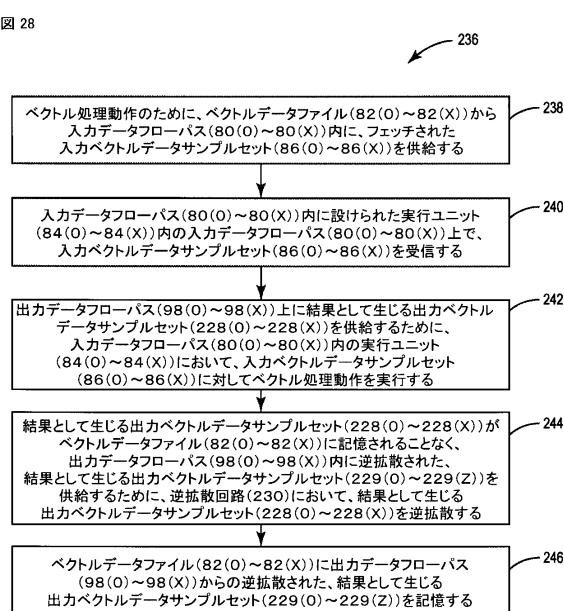

【図 28】少なくとも 1 つのベクトルデータファイル内に逆拡散された、結果として生じる出力ベクトルデータサンプルセットを供給し記憶するために、図 27 の VPE 内の少なくとも 1 つのベクトルデータファイルと少なくとも 1 つの実行ユニットとの間の少なくとも 1 つの出力データフローパスにおける、結果として生じる出力ベクトルデータサンプルセットの例示的な逆拡散を示すフローチャート。

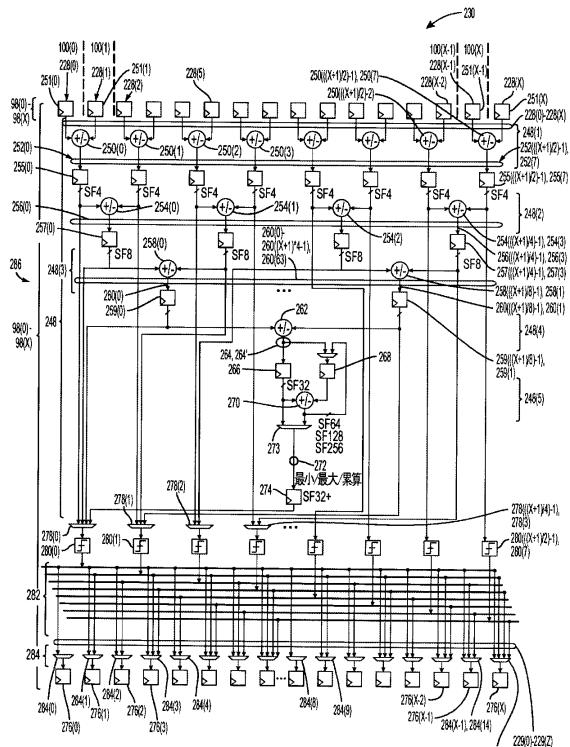

【図 29】少なくとも 1 つのベクトルデータファイル内に逆拡散された、結果として生じる出力ベクトルデータサンプルセットを供給し記憶するために、結果として生じる出力ベクトルデータサンプルセットの逆拡散を提供する、図 27 の VPE 内の少なくとも 1 つの実行ユニットと少なくとも 1 つのベクトルデータファイルとの間の出力データフローパス内の例示的な逆拡散回路の概略図。 50

【図30】マージされるべき例示的なベクトルデータサンプルとマージされた、結果として生じるベクトルデータサンプルとを示す図。

【図31】マージされた、結果として生じる出力ベクトルデータサンプルセットを供給し記憶するために、結果として生じる出力ベクトルデータサンプルセットが少なくとも1つのベクトルデータファイルに記憶されずに、少なくとも1つの実行ユニットと少なくとも1つのベクトルデータファイルとの間の少なくとも1つの出力データフローパスにおいて、結果として生じる出力ベクトルデータサンプルセットのマージングを提供するように構成されたマージ回路を利用する例示的なVPEの概略図。

【図32】ベクトルデータファイル内に加算マージされた、結果として生じる出力ベクトルデータサンプルセットを供給し記憶するために、図31のVPE内のベクトルデータファイルと少なくとも1つの実行ユニットとの間の少なくとも1つの出力データフローパスにおける、結果として生じる出力ベクトルデータサンプルセットの例示的な加算マージングを示すフローチャート。

【図33】結果として生じる出力ベクトルデータサンプルセットの加算マージングと、ベクトルデータファイル内への加算マージされた、結果として生じる出力ベクトルデータサンプルセットの記憶とを提供する、図31のVPE内の実行ユニットとベクトルデータファイルとの間の出力データフローパス内の例示的なマージ回路の概略図。

【図34】結果として生じる出力ベクトルデータサンプルセットの最大/最小マージングと、ベクトルデータファイル内への最大/最小マージされた、結果として生じる出力ベクトルデータサンプルセットの記憶とを提供する、図31のVPE内の実行ユニットとベクトルデータファイルとの間の出力データフローパス内の例示的なマージ回路の概略図。

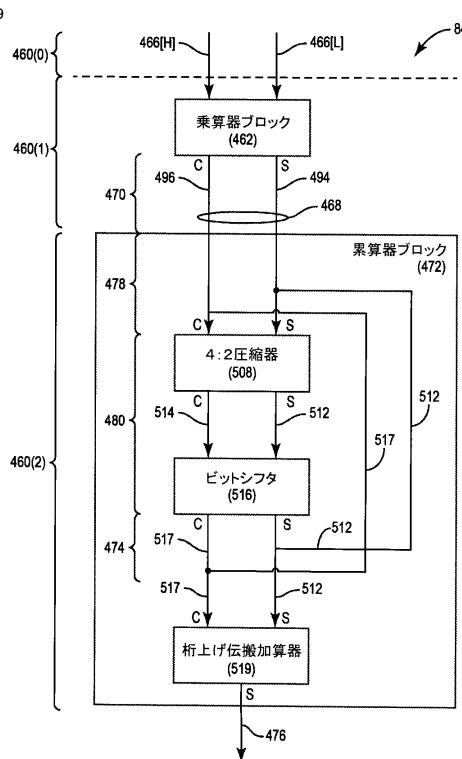

【図35】VPE内に設けられ得る例示的なベクトル処理ステージの概略図であって、ベクトル処理ステージのうちのいくつかがプログラム可能なデータパス構成を有する例示的なベクトル処理ブロックを含む、概略図。

【図36】各々がプログラム可能なデータパス構成を有し、図35の例示的なVPE内の様々なベクトル処理ステージ内に設けられる、乗算器ブロックおよび累算器ブロックの例示的なベクトル処理を示すフローチャート。

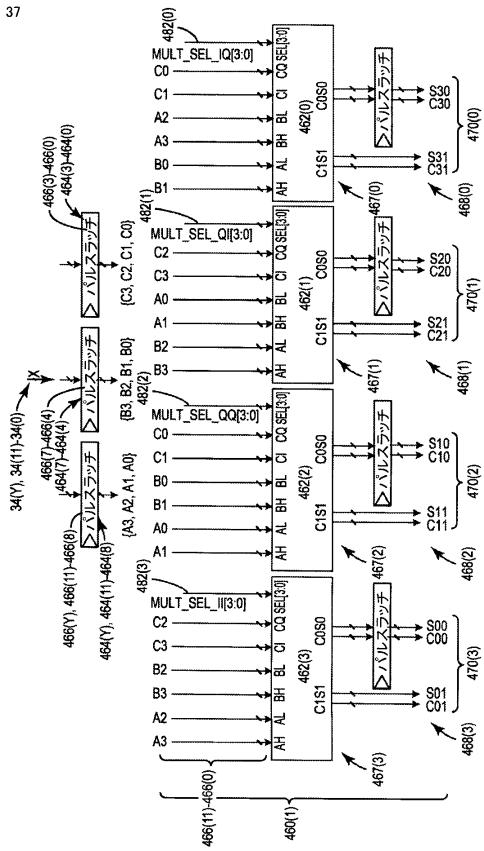

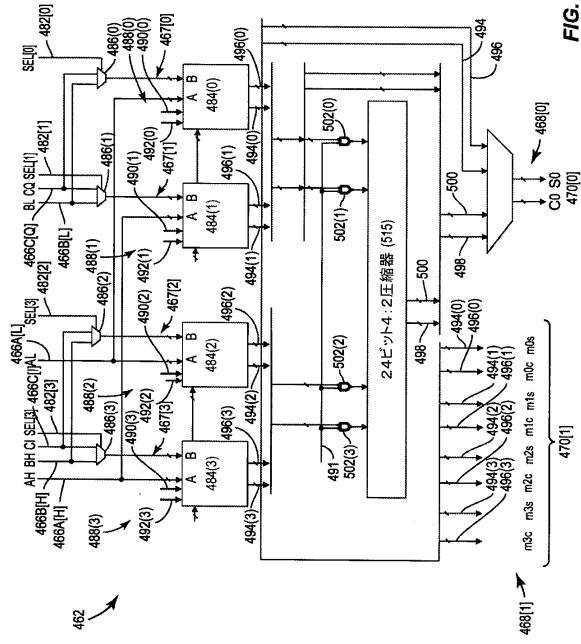

【図37】図35のVPEのベクトル処理ステージ内に設けられる複数の乗算器ブロックのより詳細な概略図であって、複数の乗算器ブロックが特定の様々なタイプのベクトル乗算演算を実行するために複数のモードでプログラムされ得るように、複数の乗算器ブロックが各々プログラム可能なデータパス構成を有する、概略図。

【図38】8ビット×8ビットの入力ベクトルデータサンプルセットおよび16ビット×16ビットの入力ベクトルデータサンプルセットについての乗算演算を提供するようにプログラムされ得ることが可能なプログラム可能なデータパス構成を有する、図37の複数の乗算器ブロックの中のある乗算器ブロックの内部構成要素の概略図。

【図39】図38のVPE内の乗算器ブロックおよび累算器ブロックの一般化された概略図であって、累算器ブロックが桁上げ伝搬を低減するために冗長桁上げ保存フォーマットを利用する桁上げ保存累算器構造を利用する、概略図。

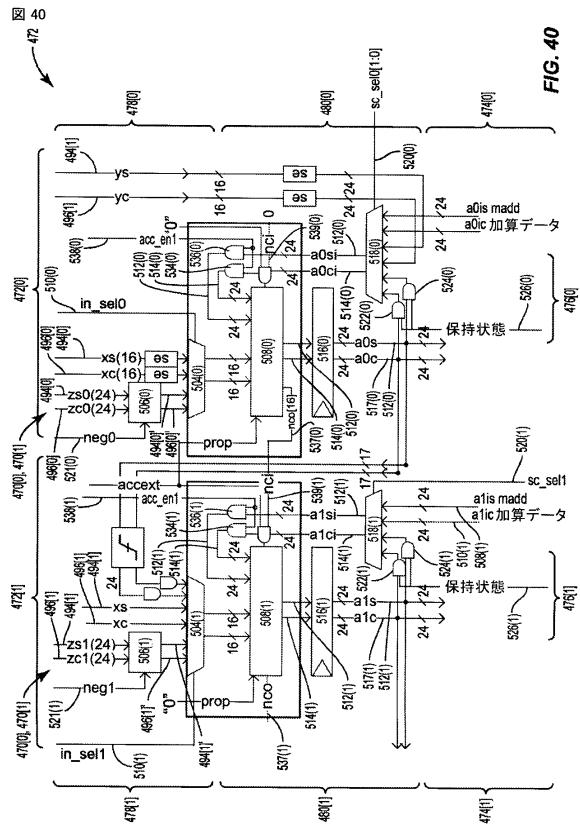

【図40】図35のVPE内に設けられた図39の累算器ブロックの例示的な内部構成要素の詳細な概略図であって、累算器ブロックが冗長桁上げ保存フォーマットを用いて特定の様々なタイプのベクトル累算演算を実行するために複数のモードでプログラムされ得るように、累算器ブロックがプログラム可能なデータパス構成を有する、概略図。

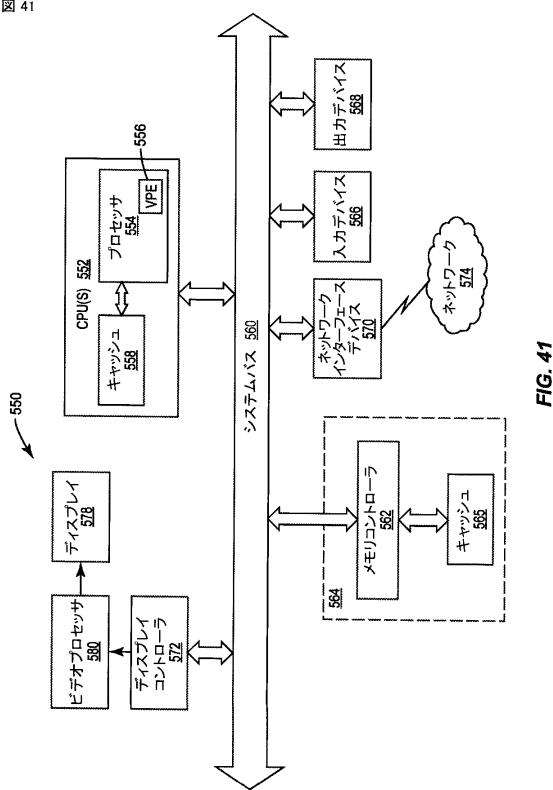

【図41】本明細書で開示された実施形態による、ベクトル処理回路とベクトル処理動作とを提供するために、本明細書で開示されたVPEを含むことができるベクトルプロセッサを含むことができる、例示的なプロセッサベースシステムのブロック図。

【発明を実施するための形態】

【0024】

[0075]ここで図面を参照すると、本開示のいくつかの例示的な実施形態が記載される。「例示的」という単語は、本明細書において、「例、事例、または例示として働くこと」を意味するために使用される。本明細書で「例示的」と記載されたいかなる実施形態も、

10

20

30

40

50

必ずしも他の実施形態より好ましいか、または有利であると解釈されるべきであるとは限らない。

【0025】

[0076]再フェッチおよび電力消費が低減される精度フィルタベクトル処理動作を供給するためのタップ付き遅延線を利用するベクトル処理エンジン（VPE）が開示される。関連するベクトル処理システムおよび方法がさらに開示される。本願に開示されるVPEは、フィルタ係数を持つ入力ベクトルデータサンプルセットの乗算および結果の累算を含む。電力消費を低減するために、メモリからの入力ベクトルデータサンプルの再フェッチを最小化するために、タップ付き遅延線は、ベクトルデータファイルとVPE中の実行ユニットとの間のデータフローパス中に含まれる。タップ付き遅延線は、フィルタベクトル処理動作を実行するための実行ユニットに入力ベクトルデータサンプルセットを受信し供給するように構成される。タップ付き遅延線は、各フィルタ遅延タップのための入力ベクトルデータサンプルをシフトすることと、実行ユニットにシフトされた入力ベクトルデータサンプルセットを供給することとを行うようにさらに構成され、シフトされた入力ベクトルデータサンプルセットは、フィルタベクトル処理動作の各処理ステージの間のベクトルデータファイルから再フェッチされることはない。この方法では、低減される再フェッチ動作は、電力消費を低減する。さらにVPE中のデータフローパスの効率は、メモリからの入力ベクトルデータサンプルセットの再フェッチ遅延によって制限されない。このシフトされた入力ベクトルデータサンプルセットは、実行ユニットに局在するように設けられる。実行ユニット中のベクトル処理は、データフローの制限ではなく、コンピュータリソースのみによって制限される。さらに、フィルタベクトル処理動作は、実行ユニット中の中間フィルタステージのための累算がメモリ中に格納されないので、より正確であり、実行ユニットがメモリから再フェッチされるべきシフトされた入力フィルタサンプルデータを待つ間に、結果として丸められる。10

【0026】

[0077]さらに、本願に開示されるタップ付き遅延線を利用するVPE中のフィルタベクトル処理動作は、フィルタ遅延タップと同じ数の乗算器を要求すること無しに完全に並列化することができる。これは、タップ付き遅延線がベクトルデータファイルからの入力ベクトルデータサンプルセットの再フェッチからの遅延をこうむること無しにフィルタ処理のための実行ユニットに、シフトされた入力ベクトルデータサンプルを供給することができるからである。フィルタタップ遅延より少ない乗算器でフィルタベクトル処理動作の並列化を許容することによって、VPEのデータフローパスは、より少ない乗算器を要求するベクトル処理動作の他のタイプのために予約された乗算器の数を簡単にスケールダウンするように再プログラムすることができ、そのため、VPEの乗算器は、効率的な目的的な目的のために過少利用されることはない。例えば、VPE中のデータフローパスがベクトル処理動作の他のタイプのために要求されるより、フィルタベクトル処理動作のためにより多くの乗算器の数を利用するように構成される場合、追加の乗算器は、これらの他のベクトル処理動作の実行の間使用され得ず、その結果、VPEの乗算器処理リソースを過少利用することになる。30

【0027】

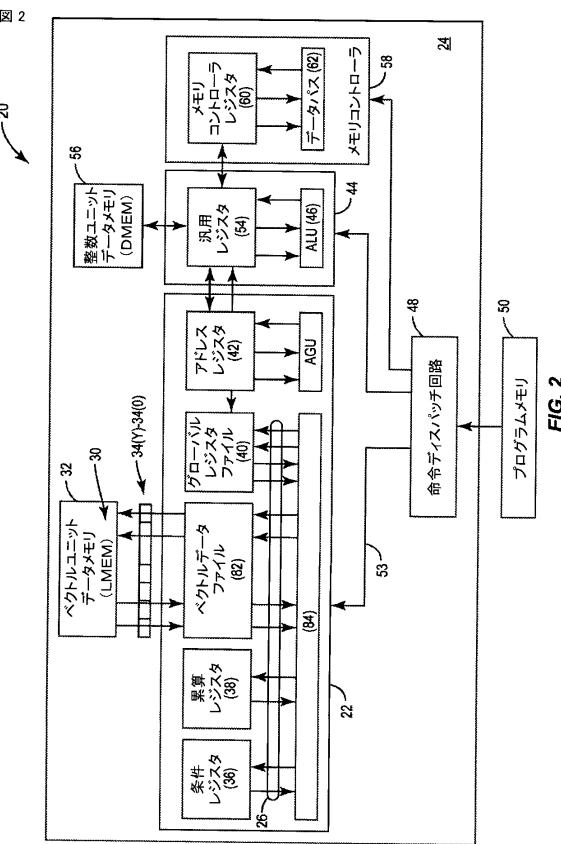

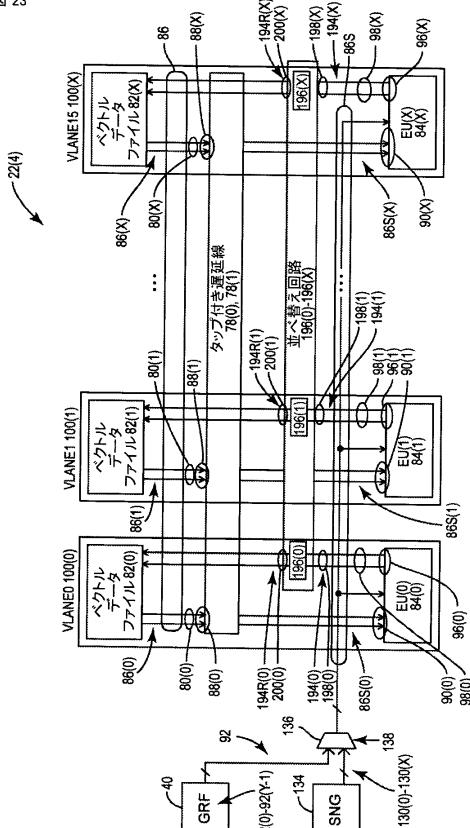

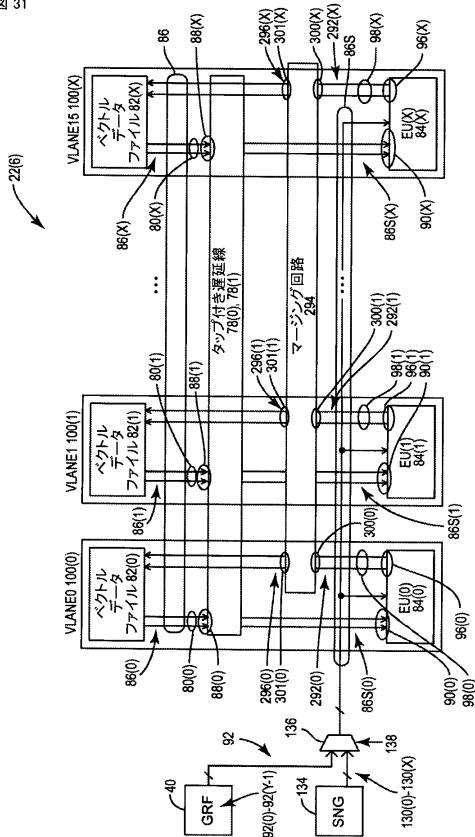

[0078]この関連で、図2は、ベクトル処理エンジン（VPE）22とも呼ばれる例示的なベクトル処理ユニット22を含むベースバンドプロセッサ20の概略図である。下記により詳細に説明されるように、VPE22は、実行ユニット84と、本明細書で開示される例示的なベクトル処理動作を含むベクトル処理動作を提供する他の特定の例示的な回路および機能とを含む。ベースバンドプロセッサ20およびそのVPE22は、半導体ダイ24内に設けられ得る。この実施形態では、下記により詳細に説明されるように、ベースバンドプロセッサ20は、様々なプログラム可能なデータバス構成を提供するためにプログラムされ得るプログラム可能なデータバス26を含む共通のVPE22を含む。このようにして、VPE22内の実行ユニット84とベクトルデータファイル82との間のプログラム可能なデータバス26は、ベースバンドプロセッサ20内に別々のVPE22を設4050

ける必要なしに、様々な動作モードで様々な特定のタイプのベクトル処理動作を提供するようにプログラムおよび再プログラムされ得る。

#### 【0028】

[0079]図3で始まる効率的な処理について、この開示におけるVPE22によって提供されるように構成された特定の回路とベクトル処理動作とを説明する前に、図2のベースバンドプロセッサ20の構成要素が最初に記載される。この非限定的な例におけるベースバンドプロセッサ20は、512ビットベクトルプロセッサである。ベースバンドプロセッサ20は、ベースバンドプロセッサ20内のベクトル処理を提供するVPE22をサポートするために、VPE22に加えて構成要素を含む。ベースバンドプロセッサ20は、ベクトルユニットデータメモリ(LMEM)32からベクトルデータ30を受信し記憶するように構成された、ベクトルデータファイル82としても知られる、ベクトルレジスタを含む。たとえば、ベクトルデータ30はXビット幅であり、「X」は設計選択に従って定義される(たとえば、512ビット)。ベクトルデータ30は、ベクトルデータサンプルセット34に分割され得る。非限定的な例として、ベクトルデータ30は256ビット幅であり得るし、より小さいベクトルデータサンプルセット34(Y)~34(0)を備える場合がある。いくつかのベクトルデータサンプルセット34(Y)~34(0)は、例として16ビット幅であり得るし、ベクトルデータサンプルセット34(Y)~34(0)の他は、32ビット幅であり得る。VPE22は、高度の並列性を達成するために、VPE22に並列に供給されるいくつかの選ばれたベクトルデータサンプルセット34(Y)~34(0)に対するベクトル処理を提供することが可能である。ベクトルデータファイル82はまた、VPE22がベクトルデータ30を処理するときに生成される結果を記憶するように構成される。いくつかの実施形態では、VPE22は、より速いベクトル命令実行時間を提供するようにレジスタ書き込みを低減するために、ベクトルデータファイル82内に中間ベクトル処理結果を記憶しないように構成される。この構成は、スカラー処理デジタル信号プロセッサ(DSP)などの、レジスタに中間結果を記憶するスカラー処理エンジンによって実行されるスカラー命令とは反対である。

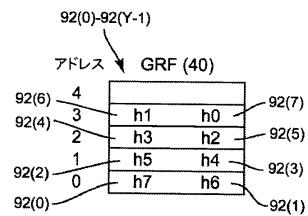

#### 【0029】

[0080]図2のベースバンドプロセッサ20は、ベクトル命令の条件付き実行において使用するためにVPE22に条件を与えるように、およびベクトル命令実行の結果として更新された条件を記憶するように構成された条件レジスタ36も含む。ベースバンドプロセッサ20はまた、累算レジスタ38と、グローバルレジスタを含むグローバルレジスタファイル40と、アドレスレジスタ42とを含む。累算レジスタ38は、ベクトルデータ30に対していくつかの特殊な演算を実行する結果として累算された結果を記憶するために、VPE22によって使用されるように構成される。グローバルレジスタファイル40は、VPE22によってサポートされるいくつかのベクトル命令のためのスカラーオペランドを記憶するように構成される。アドレスレジスタ42は、ベクトルユニットデータメモリ32からベクトルデータ30を取り出し、ベクトルユニットデータメモリ32にベクトル処理結果を記憶するために、ベクトルロードによってアドレス指定可能なアドレスを記憶し、VPE22によってサポートされる命令を記憶するように構成される。

#### 【0030】

[0081]引き続き図2を参照すると、この実施形態におけるベースバンドプロセッサ20は、VPE22によって提供されるベクトル処理に加えて、ベースバンドプロセッサ20においてスカラー処理を提供する(「整数ユニット」とも呼ばれる)スカラープロセッサ44も含む。高効率演算のために実行される命令のタイプに基づいて、ベクトル命令演算とスカラー命令演算の両方をサポートするように構成された中央処理装置(CPU)を設けることが望ましい場合がある。この実施形態では、スカラープロセッサ44は、非限定的な例として、32ビット縮小命令セットコンピューティング(RISC)スカラープロセッサである。スカラープロセッサ44は、この例では、スカラー命令処理をサポートするための算術論理ユニット(ALU)46を含む。ベースバンドプロセッサ20は、プログラムメモリ50から命令をフェッチし、フェッチされた命令を復号し、命令タイプに基

10

20

30

40

50

づいて、スカラープロセッサ 4 4 に、またはベクトルデータバス 5 3 を通って V P E 2 2 に、フェッチされた命令を向けるように構成された命令ディスパッチ回路 4 8 を含む。スカラープロセッサ 4 4 は、スカラー命令を実行するときにスカラープロセッサ 4 4 によって使用される汎用レジスタ 5 4 を含む。スカラー命令実行のためにスカラープロセッサ 4 4 によるアクセス用に、メインメモリから汎用レジスタ 5 4 にデータを供給するように、整数ユニットデータメモリ ( D M E M ) 5 6 がベースバンドプロセッサ 2 0 に含まれる。D M E M 5 6 は、非限定的な例としてキャッシュメモリであり得る。ベースバンドプロセッサ 2 0 は、メモリコントローラデータバス 6 2 を通ってメインメモリへのアクセスを求めるベクトル命令をスカラープロセッサ 4 4 が実行しているときに汎用レジスタ 5 4 からメモリアドレスを受信するように構成されたメモリコントローラレジスタ 6 0 を含むメモリコントローラ 5 8 も含む。

10

#### 【 0 0 3 1 】

[0082] V P E 2 2 によるベクトル命令処理によってサポートされることが望ましい場合がある特殊ベクトル処理動作の 1 つのタイプは、フィルタリングである。フィルタ動作は、サンプリングされた入力時間関数の重畠の量子化時間領域表現と、フィルタの重み付け関数の表現とを計算する。時間領域内の重畠は、周波数領域内の乗算に対応する。このように、デジタルフィルタは、間隔が均一なサンプル間隔で実行される乗算および加算の拡張シーケンスにより、V P E 2 2 において実現され得る。たとえば、ディスクリート有限インパルス応答 ( F I R ) フィルタは、フィルタ関数を計算するために、「 Y 」計算フィルタ係数を有する遅延線上の遅延タップの有限数 ( Y ) を使用して実施され得る。

20

#### 【 0 0 3 2 】

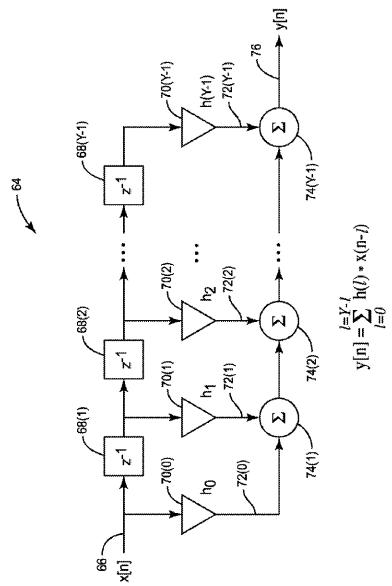

[0083] この関連で、図 3 は、図 2 の V P E 2 2 におけるフィルタベクトル処理動作を介してサポートされることが望ましい場合がある、例示的なディスクリート F I R フィルタ 6 4 の概略図である。デジタル化入力信号 6 6 (  $x[n]$  ) は、「フィルタ遅延タップ」 6 8 ( 1 ) ~ 6 8 ( Y - 1 ) と呼ばれる遅延構造を通ってデジタル化入力信号サンプル (  $x[0], x[1], \dots, x[n]$  ) を渡すことによってフィルタリングされ得る。フィルタ遅延タップ 6 8 ( 1 ) ~ 6 8 ( Y - 1 ) は、フィルタサンプル被乗数 7 2 ( 0 ) ~ 7 2 ( Y - 1 ) を供給するために、すべてのデジタル化入力信号サンプル ( すなわち、  $x[0], x[1], \dots, x[n]$  ) が各々フィルタ係数 (  $h[0] \sim h(Y-1)$  ) によって乗算される ( すなわち、  $h(1) * x[n-1]$  ) ために、クロックされたデジタル化入力信号サンプル ( すなわち、  $x[0], x[1], \dots, x[n]$  ) を乗算器 7 0 ( 0 ) ~ 7 0 ( Y - 1 ) の中にシフトする。フィルタサンプル被乗数 7 2 ( 0 ) ~ 7 2 ( Y - 1 ) は、結果として生じるフィルタ処理された出力信号 7 6 ( すなわち、  $y[n]$  ) を供給するために、加算器 ( すなわち、アダー ) 7 4 ( 1 ) ~ 7 4 ( Y - 1 ) によって一緒に加算される。このように、図 3 のディスクリート F I R フィルタ 6 4 は以下のように要約され得る。

30

#### 【 0 0 3 3 】

##### 【数 1】

$$y[n] = \sum_{l=0}^{l=Y-1} h(l) * x[n-l]$$

40

#### 【 0 0 3 4 】

ここで、

n は入力信号サンプルの数であり、

$x[n]$  はデジタル化入力信号 6 6 であり、

$y[n]$  は、結果として生じるフィルタ処理された出力信号 7 6 であり、

$h(l)$  はフィルタ係数であり、

Y はフィルタ係数の数である。

フィルタ係数  $h(l)$  は複素数であり得る。一態様では、V P E 2 2 は、( たとえば、グローバルレジスタファイル 4 0 から ) フィルタ係数を受信することができる。V P E 2 2

50

は、FIRフィルタ関数を実行するために受信されたフィルタ係数を直接使用することができ、その場合、上記の式におけるフィルタ係数  $h(1)$  は、受信されたフィルタ係数を表すことができる。代替として、VPE22は、FIRフィルタ関数を実行するためにそれらを使用する前に、受信されたフィルタ係数の複素共役を計算することができ、その場合、上記の式におけるフィルタ係数  $h(1)$  は、受信されたフィルタ係数の共役を表すことができる。

### 【0035】

[0084]図3の上記のディスクリートFIRフィルタ64は、以下のように書き直され得る。

$$y[n] = x[n] * h_0 + x[n-1] * h_1 + \dots + x[n-7] * h_7 \quad 10$$

### 【0036】

[0085]しかしながら、図3のディスクリートFIRフィルタ64などのフィルタリング演算は、ベクトルプロセッサにおいて提供される特殊データフローパスに起因して、ベクトルプロセッサにおいて並列化することは困難であり得る。フィルタリングされるべき入力ベクトルデータサンプルセット（たとえば、ベクトル化されたデジタル化入力信号66）が、フィルタ遅延タップ（たとえば、68(1)～68(Y-1)）の間でシフトされると、入力ベクトルデータサンプルセットはベクトルデータファイルから再フェッチされ、したがって電力消費が増大し、スループットが低減される。ベクトルデータファイルからの入力ベクトルデータサンプルセットの再フェッチを最小化するために、ベクトルプロセッサ内のデータフローパスは、効率的な並列化処理のために、フィルタ遅延タップ（たとえば、68(1)～68(Y-1)）と同じ数の乗算器（たとえば、70(0)～70(Y-1)）を設けるように構成される可能性がある。しかしながら、他のベクトル処理動作は、より少ない乗算器しか必要としない場合があり、それにより、データフローパス内の乗算器の非効率的なスケーリングおよび過少利用がもたらされる。スケーラビリティを提供するために、乗算器の数がフィルタ遅延タップの数よりも少なくなるように削減された場合、フィルタ処理の様々なフェーズに対して同じ入力ベクトルデータサンプルセットを取得するために、メモリにより多くの再フェッチが必要とされることによって、並列化が制限される。

### 【0037】

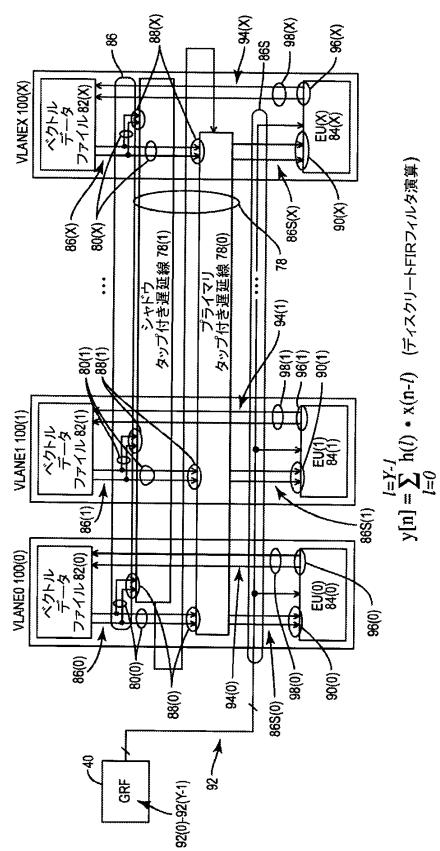

[0086]この関連で、図4は、図2のVPE22として提供され得る例示的なVPE22(1)の概略図である。下記でより詳細に記載されるように、図4のVPE22(1)は、ベクトルデータサンプルの再フェッチが除去または低減され、電力消費が低減される、VPE22(1)内の精度フィルタベクトル処理動作を提供する。精度フィルタベクトル処理動作は、ベクトルデータサンプルの再フェッチを必要とし、それにより結果として電力消費が増大する、中間結果の記憶を必要とするフィルタベクトル処理動作と比較して、VPE22(1)において提供され得る。ベクトルデータファイルからの入力ベクトルデータサンプルの再フェッチを除去または最小化して、電力消費を低減し、処理効率を改善するために、VPE22(1)内のベクトルデータファイル82(0)～82(X)と（「EÜ」とも標記される）実行ユニット84(0)～84(X)との間の入力データフローパス80(0)～80(X)にタップ付き遅延線78が含まれる。「X」+1は、この例におけるベクトルデータサンプルの処理用にVPE22(1)内に設けられる並列入力データレーンの最大数である。タップ付き遅延線78は、ベクトルデータファイル82(0)～82(X)の対応するサブセットまたはすべてから入力ベクトルデータサンプルセット86(0)～86(X)の入力ベクトルデータサンプル86のサブセットまたはすべてとして、タップ付き遅延線入力88(0)～88(X)上で入力ベクトルデータサンプルセット86(0)～86(X)を受信するように構成される。入力ベクトルデータサンプルセット86(0)～86(X)は、この例では86(0)、86(1)、...、および86(X)である、「X+1」個の入力ベクトルデータサンプル86から構成される。

### 【0038】

10

20

30

40

50

[0087]引き続き図4を参照すると、タップ付き遅延線78は、フィルタベクトル処理動作のために実行ユニット84(0)～84(X)によって処理されるべき、ベクトルデータファイル82(0)～82(X)からフェッチされた入力ベクトルデータサンプルセット86(0)～86(X)を記憶する。下記の図6および図7に関して下記でより詳細に説明されるように、タップ付き遅延線78は、実行ユニット84(0)～84(X)にシフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)を供給するために、VPE22(1)によって実行されるべきフィルタベクトル命令に従うフィルタベクトル処理動作のフィルタ遅延タップ(すなわち、フィルタ処理ステージ)ごとに、入力ベクトルデータサンプルセット86(0)～86(X)をシフトするように構成される。シフトされた入力ベクトルデータサンプル86Sのすべては、シフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)を備える。タップ付き遅延線78は、フィルタベクトル処理動作中、実行ユニット84(0)～84(X)の実行ユニット入力90(0)～90(X)にシフトされた入力ベクトルデータサンプル86S(0)～86S(X)を供給する。このようにして、フィルタベクトル処理動作のフィルタタップのためのシフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)に対して実行される動作に基づく中間フィルタ結果は、VPE22(1)によって実行されるフィルタベクトル処理動作の各処理ステージの間、記憶、シフト、およびベクトルデータファイル82(0)～82(X)から再フェッチされる必要がない。このように、タップ付き遅延線78は、VPE22(1)によって実行されるフィルタベクトル処理動作についての電力消費を低減し、処理効率を上げることができる。10 20

#### 【0039】

[0088]「ベクトル処理ステージ」とも呼ばれるVPE22(1)内の処理ステージは、特定のタスクまたは動作を実行するように設計された回路と関連するベクトルデータバスとを備える。ベクトル処理動作は、いくつかの異なる処理ステージにおいて、VPE22(1)によって実行される場合がある。各処理ステージは、VPE22(1)の1つまたは複数のクロックサイクルにわたって実行される場合がある。その結果、VPE22(1)内のベクトル処理動作の実行は、ベクトル処理動作の各処理ステージが各々1つまたは複数のクロックサイクルを消費する可能性があるので、完了するために多くのクロックサイクルを要する可能性がある。たとえば、処理ステージは、図4のVPE22(1)内のタップ付き遅延線78の中に入力ベクトルデータサンプルセット86(0)～86(X)をフェッチすることを含む場合がある。VPE22(1)内のベクトル処理ステージはパイプライン化され得る。30

#### 【0040】

[0089]実行ユニット84(0)～84(X)は、フェッチされた入力ベクトルデータサンプルセット86(0)～86(X)を処理する1つまたは複数のパイプラインステージを含む場合がある。たとえば、実行ユニット84(0)～84(X)内の1つのパイプラインステージは、累算演算を実行するように構成された累算器から構成される累算ステージを含む場合がある。別の例として、実行ユニット84(0)～84(X)内の別のパイプラインステージは、乗算演算を実行するように構成された乗算器から構成される乗算ステージを含む場合がある。40

#### 【0041】

[0090]引き続き図4を参照すると、実行ユニット84(0)～84(X)は、フィルタベクトル処理動作のための図2のグローバルレジスタファイル40に記憶されたフィルタ係数92(0)～92(Y-1)の中からフィルタ係数92を受信する、ここで、「Y」はフィルタベクトル処理動作のためのフィルタ係数の数に等しい場合がある。実行ユニット84(0)～84(X)は、各々、実行ユニット84(0)～84(X)内に中間フィルタベクトルデータ出力サンプルを供給するために、ベクトルフィルタ処理動作の各処理ステージの間に、受信されたフィルタ係数92(0)、90(1)、...、90(Y-1)のうちの1つを、シフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)のシフトされた入力ベクトルデータサンプル86S(0)、86S(1)、...50

. 8 6 S ( X ) と乗算するように構成される。中間フィルタベクトルデータ出力サンプルセットは、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) の各々において累算される（すなわち、前に累算されたフィルタ出力ベクトルデータサンプルが現在の累算されたフィルタ出力ベクトルデータサンプルに加算される）。これにより、シフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) 内のシフトされた入力ベクトルデータサンプル 8 6 S ( 0 )、8 6 S ( 1 )、. . . 8 6 S ( X ) ごとに、それぞれ、出力データフローパス 9 8 ( 0 ) ~ 9 8 ( X ) 上の実行ユニット出力 9 6 ( 0 ) ~ 9 6 ( X ) 上に実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) によって供給される、最終的な、結果として生じるフィルタ出力ベクトルデータサンプルセット 9 4 ( 0 ) ~ 9 4 ( X ) がもたらされる。結果として生じるフィルタ出力ベクトルデータサンプルセット 9 4 ( 0 ) ~ 9 4 ( X ) は、この例では 9 4 ( 0 )、9 4 ( 1 )、. . . および 9 4 ( X ) である、「X + 1」個の、結果として生じるフィルタ出力ベクトルデータサンプル 9 4 から構成される。実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) によって生成された中間フィルタベクトルデータ出力サンプルセットを記憶しシフトする必要なしに、結果として生じるフィルタ出力ベクトルデータサンプルセット 9 4 ( 0 ) ~ 9 4 ( X ) は、V P E 2 2 ( 1 ) によるさらなる使用および/または処理のために、それぞれのベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) に戻されて記憶される。

10

#### 【 0 0 4 2 】

[0091]引き続き図 4 を参照すると、下記でより詳細に説明されるように、タップ付き遅延線 7 8 は、処理されているベクトル命令に従って制御されるようにプログラム可能である。フィルタベクトル命令が処理されていない場合、タップ付き遅延線 7 8 は、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) と実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) との間の入力データフローパス 8 0 ( 0 ) ~ 8 0 ( X ) に含まれないようにプログラムされ得る。この実施形態では、タップ付き遅延線 7 8 は、フィルタベクトル処理動作のフィルタタップごとにシフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) を供給するために、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) から受信された入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) をロードしシフトするように構成される。このように、シフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) は、フィルタベクトル処理動作のフィルタタップの実行のために、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) に供給され得る。タップ付き遅延線 7 8 がないと、フィルタベクトル処理動作の次のフィルタタップのために、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) にシフトされた中間入力ベクトルデータサンプルセットを再び供給するために、別個のシフティングプロセスが実行される必要があるはずであり、それにより、遅延時間が増大し、さらなる電力が消費される。さらに、フィルタベクトル処理動作中、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) からのシフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) の再フェッチ遅延によって、V P E 2 2 ( 1 ) 内の入力データフローパス 8 0 ( 0 ) ~ 8 0 ( X ) および出力データフローパス 9 8 ( 0 ) ~ 9 8 ( X ) の効率が制限される。

20

30

#### 【 0 0 4 3 】

[0092]シフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) は、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) に局在するタップ付き遅延線 7 8 によって供給される。実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) におけるベクトル処理は、データフローの制限ではなく、コンピュータリソースのみによって制限される。これは、シフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) がベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) からフェッチされるまで待つ必要なしに、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) が、ベクトル処理動作を実行するためにシフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) を受信することに、連続して、または実質的に連続して忙しいことを意味する。

40

#### 【 0 0 4 4 】

[0093]さらに、図 4 の V P E 2 2 ( 1 ) によって実行されるフィルタベクトル処理動作

50

は、タップ付き遅延線 7 8 を利用することによってより精密になり得るが、これは、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) 内の中間フィルタ処理ステージのための出力累算がベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) に記憶される必要がないからである。実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) からベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) への中間出力ベクトルデータサンプルセットの記憶は、丸めをもたらす可能性がある。したがって、次の中間出力ベクトルデータサンプルセットがベクトル処理動作のために実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) に供給されるとき、ベクトル処理動作の各乗算フェーズの間に任意の丸め誤差が伝搬および加算される。対照的に、図 4 の V P E 2 2 ( 1 ) の例では、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) によって計算された中間出力ベクトルデータサンプルセットは、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) に記憶される必要がない。実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) は、前の中間出力ベクトルデータサンプルセットを次のフィルタ遅延タップのための中間出力ベクトルデータサンプルセットと累算することができるが、これは、タップ付き遅延線 7 8 が、処理されるべきベクトル処理動作の間に、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) にシフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) を供給するからであり、結果は前のフィルタ遅延タップのための前のベクトルデータサンプルセットと累算される。

10

#### 【 0 0 4 5 】

[0094]引き続き図 4 を参照すると、この実施形態における V P E 2 2 ( 1 ) は、並列化処理のための ( V L A N E 0 1 0 0 ( 0 ) ~ V L A N E X 1 0 0 ( X ) と標記された ) 複数のベクトルデータレーンから構成される。各ベクトルデータレーン 1 0 0 ( 0 ) ~ 20 1 0 0 ( X ) は、この実施形態では、ベクトルデータファイル 8 2 と実行ユニット 8 4 とを含んでいる。例としてベクトルデータレーン 1 0 0 ( 0 ) を取り上げると、その中のベクトルデータファイル 8 2 ( 0 ) は、フィルタベクトル処理のために実行ユニット 8 4 ( 0 ) によって受信されるように、入力データフローパス 8 0 ( 0 ) 上に入力ベクトルデータサンプル 8 6 ( 0 ) を供給するように構成される。上記で説明されたように、タップ付き遅延線 7 8 は、フィルタベクトル処理のために、入力ベクトルデータサンプル 8 6 ( 0 ) をシフトし、シフトされた入力ベクトルデータサンプル 8 6 S ( 0 ) を実行ユニット 8 4 ( 0 ) に供給するために、入力データフローパス 8 0 ( 0 ) 内に設けられる。ベクトルデータファイル 8 2 ( 0 ) はまた、V P E 2 2 ( 1 ) によって処理されるべき現在または次のベクトル命令に従って、必要または所望に応じて、次のベクトル処理動作のためにベクトルデータファイル 8 2 ( 0 ) に戻されて記憶されるべき、出力データフローパス 9 8 ( 0 ) からのフィルタベクトル処理の結果として、実行ユニット 8 4 ( 0 ) によって供給される、結果として生じるフィルタ出力ベクトルデータサンプル 9 4 ( 0 ) を受信するように構成される。

30

#### 【 0 0 4 6 】

[0095]必要に応じて、任意の数のベクトルデータレーン 1 0 0 ( 0 ) ~ 1 0 0 ( X ) が V P E 2 2 ( 1 ) 内に設けられる場合がある。V P E 2 2 ( 1 ) 内に設けられるベクトルデータレーン 1 0 0 ( 0 ) ~ 1 0 0 ( X ) の数は、効率目的のための並列化ベクトル処理対さらなるベクトルデータレーン 1 0 0 ( 0 ) ~ 1 0 0 ( X ) を設けることに伴うさらなる回路、空間、および電力消費についてのトレードオフに基づく場合がある。1つの非限定的な例として、16個のベクトルデータレーン 1 0 0 が V P E 2 2 ( 1 ) 内に設けられる場合があり、各ベクトルデータレーン 1 0 0 は、V P E 2 2 ( 1 ) 内の 5 1 2 ビットまでのベクトルデータの並列化処理を提供するために、32ビットのデータ幅能力を有する。

40

#### 【 0 0 4 7 】

[0096]引き続き図 4 を参照すると、すべてのベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) に適用可能であるが、例としてベクトルデータレーン 1 0 0 ( 0 ) 内のベクトルデータファイル 8 2 ( 0 ) を使用して、ベクトルデータファイル 8 2 ( 0 ) により、入力ベクトルデータサンプル 8 6 ( 0 ) の1つまたは複数のサンプルがベクトル処理のために記憶されることが可能になる。V P E 2 2 ( 1 ) によって実行されている特定のベクトル命

50

令に従う入力ベクトルデータサンプル 8 6 ( 0 ) のプログラミングに応じて、入力ベクトルデータサンプル 8 6 ( 0 ) の幅が設けられる。入力データフローパス 8 0 ( 0 ) の幅は、所与のベクトル命令がタップ付き遅延線 7 8 および実行ユニット 8 4 ( 0 ) に様々な幅の入力ベクトルデータサンプル 8 6 ( 0 ) を供給するために、クロックサイクルごとを含むベクトル命令ごとにプログラム可能および再プログラム可能である。このようにして、ベクトルデータレーン 1 0 0 ( 0 ) は、実行されているベクトル命令のタイプに応じて、入力ベクトルデータサンプル 8 6 ( 0 ) の様々な幅の処理を提供するように、プログラムおよび再プログラムされ得る。

#### 【 0 0 4 8 】

[0097]たとえば、ベクトルデータファイル 8 2 ( 0 ) は、32ビット幅であり、同様に 32ビットまでの幅である入力ベクトルデータサンプル 8 6 を記憶することが可能であり得る。入力ベクトルデータサンプル 8 6 ( 0 ) は、ベクトルデータファイル 8 2 ( 0 ) の幅全体（たとえば、32ビット）を消費する場合があるか、またはベクトルデータファイル 8 2 ( 0 ) の幅のより小さいサンプルサイズで供給される場合がある。入力ベクトルデータサンプル 8 6 ( 0 ) のサイズは、V P E 2 2 ( 1 ) によって実行されているベクトル命令に基づく、入力ベクトルデータサンプル 8 6 ( 0 ) のサイズ向けの入力データフローパス 8 0 ( 0 ) の構成のプログラミングに基づいて構成され得る。たとえば、入力ベクトルデータサンプル 8 6 ( 0 ) は、1つのベクトル命令のための2つの別々の16ビットベクトルデータサンプルを備える場合がある。別の例として、入力ベクトルデータサンプル 8 6 ( 0 ) は、1つの32ビットベクトルデータサンプルとは対照的に、別のベクトル命令のためのベクトルデータファイル 8 2 ( 0 ) 内の4つの8ビットベクトルデータサンプルを備える場合がある。別の例では、入力ベクトルデータサンプル 8 6 ( 0 ) は、1つの32ビットベクトルデータサンプルを備える場合がある。V P E 2 2 ( 1 ) はまた、ベクトル命令ごとに、および／または所与のベクトル命令のクロックサイクルごとに、実行ユニット 8 4 ( 0 ) によりベクトルデータファイル 8 2 ( 0 ) に供給される様々なサイズの、結果として生じるフィルタ出力ベクトルデータサンプル 9 4 ( 0 ) を受信するように、ベクトルデータファイル 8 2 ( 0 ) のための出力データフローパス 9 8 ( 0 ) をプログラムおよび再プログラムすることが可能である。

#### 【 0 0 4 9 】

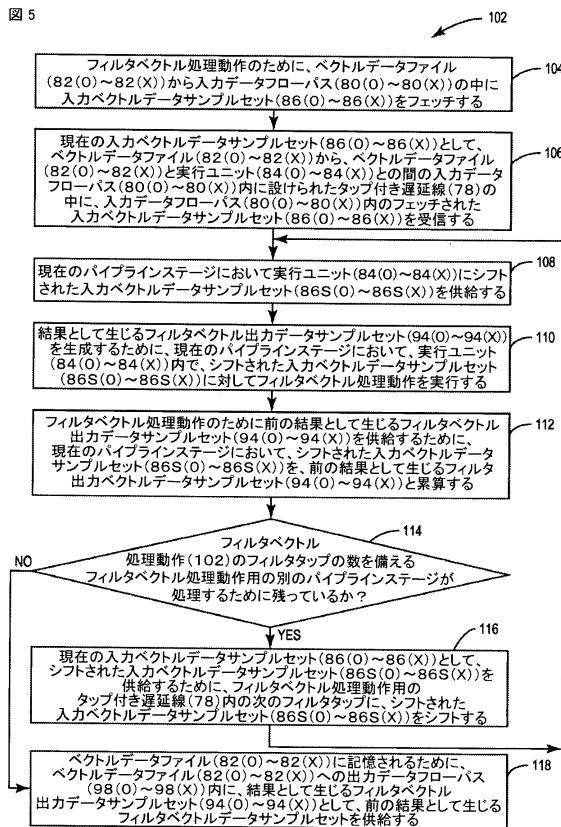

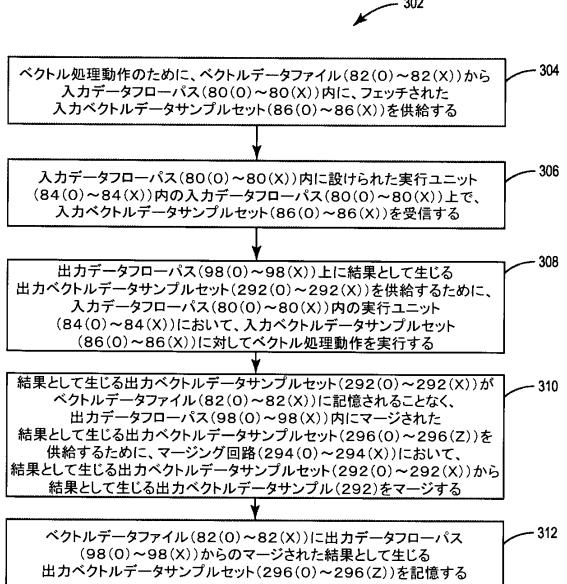

[0098]図4のV P E 2 2 ( 1 ) のさらなる詳細および特徴、ならびにこの実施形態における入力データフローパス 8 0 ( 0 ) ~ 8 0 ( X ) 内の実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) にシフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) を供給するためのタップ付き遅延線 7 8 のさらなる説明が次に記載される。この関連で、図5は、例示的なフィルタベクトル命令に従って、タップ付き遅延線 7 8 を利用する図4のV P E 2 2 ( 1 ) において実行され得る例示的なフィルタベクトル処理動作 1 0 2 を示すフローチャートである。図6 A ~ 図10において提供される例を参照して、図5のフィルタベクトル処理動作 1 0 2 において実行される例示的なタスクが記載される。

#### 【 0 0 5 0 】

[0099]図5を参照すると、フィルタベクトル命令に従ってフィルタベクトル処理動作 1 0 2 において処理されるべき入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) は、フィルタベクトル処理動作 1 0 2 のために、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) から入力データフローパス 8 0 ( 0 ) ~ 8 0 ( X ) の中にフェッチされる（プロック 1 0 4 ）。図4のV P E 2 2 ( 1 ) に関して上記で説明されたように、入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) は、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) 内のグローバルレジスタファイル 4 0 から受信されたフィルタ係数 9 2 ( 0 ) ~ 9 2 ( Y - 1 ) と乗算される。たとえば、図6 A は、グローバルレジスタファイル 4 0 内のフィルタ係数 9 2 ( 0 ) ~ 9 2 ( Y - 1 ) ( すなわち、h 7 ~ h 0 ) を示す。この例では、実行されるべきフィルタベクトル処理動作 1 0 2 において8個のフィルタタップを提供する、グローバルレジスタファイル 4 0 に記憶された8個のフィルタ係数 9 2 が存在する。この例では、上記で説明された図3のディスクリートF I R フィルタ 6 4 の式からのフィルタ

10

20

30

40

50

ベクトル処理動作 102 は、下記の通りであることに留意されたい。

$y[n] = x[n] * h_0 + x[n-1] * h_1 + \dots + x[n-7] * h_7$

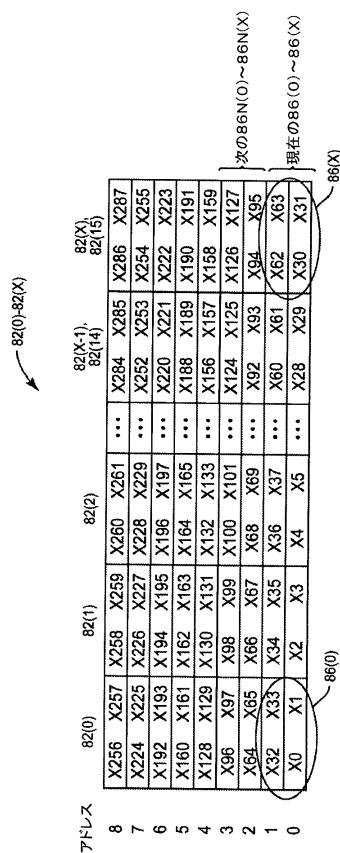

【0051】

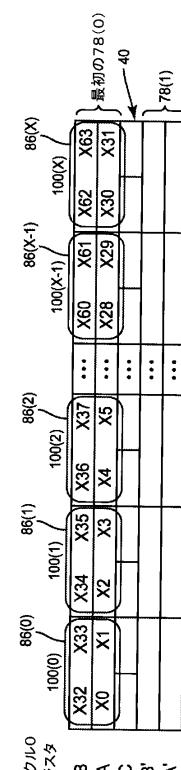

[00100] 図 6 B は、フィルタベクトル処理動作 102 によってフィルタリングされるべき入力信号を表す、図 4 の VPE22(1) 内のベクトルデータファイル 82(0) ~ 82(X) に記憶された例示的な入力ベクトルデータサンプルセット 86(0) ~ 86(X) を示す。この例では、サンプル X0 は最も古いサンプルであり、サンプル X63 はつい最近のサンプルである。言い換えれば、この例では、サンプル X63 は、時間的にサンプル X0 の後に発生する。ベクトルデータファイル 82(0) ~ 82(X) の各アドレスは 16 ビット幅であるので、ベクトルデータファイル 82(0) ~ 82(X) に記憶された最初の入力ベクトルデータサンプルセット 86(0) ~ 86(X) は、図 6 B に示されたように、ADDRESS0 および ADDRESS1 にまたがる。これにより、ベクトルデータファイル 82(0) ~ 82(X) が、図 4 の VPE22(1) の例における実行ユニット 84(0) ~ 84(X) の 32 ビット幅能力をサポートするために、32 ビット幅の入力ベクトルデータサンプル 86 を供給することが可能になる。この関連で、最初の入力ベクトルデータサンプルセット 86(0) ~ 86(X) を備える、合計 512 ビットの各々 8 ビットの幅である 64 個の合計入力ベクトルデータサンプルサブセット（すなわち、X0 ~ X63）が存在する。同様に、ADDRESS2 および ADDRESS3 は、ベクトルデータファイル 82(0) ~ 82(X) に記憶された別の 2 番目の入力ベクトルデータサンプルセット 86(0) ~ 86(X) を記憶する。図 6 B のこの例では、各ベクトルデータファイル 82(0) ~ 82(X) の 8 個のアドレス（ADDRESS0 ~ 7）が示され、256 個の合計入力ベクトルデータサンプル 86（すなわち、X0 ~ X255）を示すが、それは限定的でないことに留意されたい。

【0052】

[00101] フィルタベクトル処理動作 102 に関する入力ベクトルデータサンプルセット 86(0) ~ 86(X) の幅に応じて、ベクトル命令のプログラミングに従うフィルタベクトル処理動作 102 を提供するために、図 4 の VPE22(1) 内のベクトルデータレーン 100(0) ~ 100(X) の 1 つ、いくつか、またはすべてが利用され得る。ベクトルデータファイル 82(0) ~ 82(X) の幅全体が必要な場合、すべてのベクトルデータレーン 100(0) ~ 100(X) がフィルタベクトル処理動作 102 に利用され得る。フィルタベクトル処理動作 102 は、フィルタベクトル処理動作 102 に利用され得るベクトルデータレーン 100(0) ~ 100(X) のサブセットを必要とするにすぎない場合があることに留意されたい。これは、入力ベクトルデータサンプルセット 86(0) ~ 86(X) の幅がすべてのベクトルデータファイル 82(0) ~ 82(X) の幅よりも小さいからであり得るし、ここで、フィルタベクトル処理動作 102 と並列に実行されるべき他のベクトル処理動作にさらなるベクトルデータレーン 100 を利用することが望ましい。現在の例を説明する目的で、フィルタベクトル処理動作 102 において利用される入力ベクトルデータサンプルセット 86(0) ~ 86(X) が、すべてのベクトルデータレーン 100(0) ~ 100(X) を要すると想定する。

【0053】

[00102] 図 5 に戻って参照すると、現在の入力ベクトルデータサンプルセット 86(0) ~ 86(X) としてタップ付き遅延線 78 にロードされるために、フェッチされた入力ベクトルデータサンプルセット 86(0) ~ 86(X) が、ベクトルデータファイル 82(0) ~ 82(X) から入力データフローパス 80(0) ~ 80(X) に供給される（ロック 106）。入力ベクトルデータサンプルセット 86(0) ~ 86(X) は、フィルタベクトル処理動作 102 のために実行ユニット 84(0) ~ 84(X) によって処理されるべき入力ベクトルデータサンプルセット 86(0) ~ 86(X) として、プライマリタップ付き遅延線 78(0) の中にロードされる。プライマリタップ付き遅延線 78(0) の中にロードされた入力ベクトルデータサンプルセット 86(0) ~ 86(X) は、フィルタベクトル処理動作 102 の最初のフィルタタップ動作のためにシフトされない。し

かしながら、上記で説明され、図7に関して下記でさらに詳細に説明されるように、タップ付き遅延線78の目的は、フィルタベクトル処理動作102の次のフィルタタップ動作のために実行ユニット84(0)～84(X)にシフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)を供給するために、入力ベクトルデータサンプルセット86(0)～86(X)のシフトを提供することである。実行ユニット84(0)～84(X)によって実行されるフィルタベクトル処理動作102の各処理ステージの間、実行ユニット84(0)～84(X)にシフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)を供給するために、入力ベクトルデータサンプル86がプライマリタップ付き遅延線78(0)内でシフトされる。このようにして、入力ベクトルデータサンプルセット86(0)～86(X)は、フィルタベクトル処理動作102のフィルタタップ動作ごとに、記憶、ベクトルデータファイル82(0)～82(X)内でシフト、および再フェッチされる必要がない。10

#### 【0054】

[00103]オプションのシャドウタップ付き遅延線78(1)がVPE22(1)内に設けられた場合、次の入力ベクトルデータサンプルセット86N(0)～86N(X)も、ベクトルデータファイル82(0)～82(X)からシャドウタップ付き遅延線78(1)の中にロードされ得る。図7に関して下記でさらに詳細に説明されるように、次の入力ベクトルデータサンプルセット86N(0)～86N(X)は、シフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)の少なくとも一部になるために、フィルタベクトル処理動作102の間にプライマリタップ付き遅延線78(0)の中にシフトされる。このように、プライマリタップ付き遅延線78(0)は、フィルタベクトル処理動作102のために実行されるべき次の入力ベクトルデータサンプルセット86N(0)～86N(X)が、ベクトルデータファイル82(0)～82(X)からプライマリタップ付き遅延線78(0)の中にフェッチされるまで、実行ユニット84(0)～84(X)が待つ必要があった場合、場合によっては被る遅延をフェッチすることなく、フィルタベクトル処理動作102の間に利用可能なシフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)を有することができる。20

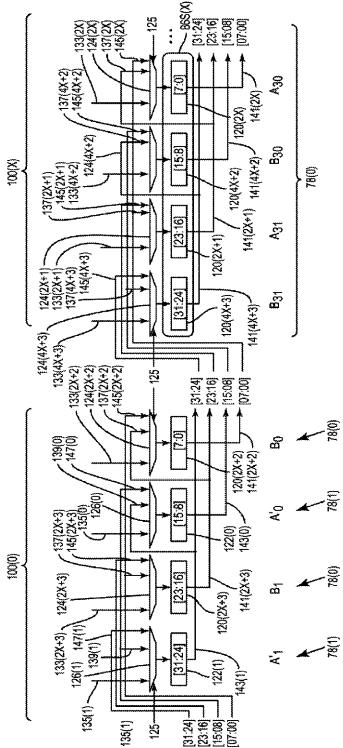

#### 【0055】

[00104]この関連で、図7は、図4のVPE22(1)内に設けられ得る例示的なタップ付き遅延線78を示す。この実施形態では、タップ付き遅延線78は、シャドウタップ付き遅延線78(1)とプライマリタップ付き遅延線78(0)とを備える。この例におけるプライマリタップ付き遅延線78(0)は、入力ベクトルデータサンプル86の解像度が8ビット長に落ちることを可能にするために、複数の8ビットプライマリパイプラインレジスタ120から構成される。実行ユニット84(0)～84(X)によって処理される最初の入力ベクトルデータサンプルセット86(0)～86(X)は、下記の図9Aに関して説明されるように、フィルタベクトル処理動作102の最初のフィルタタップのために、この例ではシフトされない。実行ユニット84(0)～84(X)がフィルタベクトル処理動作102のために次のフィルタタップを処理するとき、プライマリタップ付き遅延線78(0)に記憶された入力ベクトルデータサンプルセット86(0)～86(X)の中の入力ベクトルデータサンプル86は、シフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)になるために、図7の矢印によって示されたように、プライマリパイプラインレジスタ120(0)～120(4X+3)内でシフトされる。このようにして、実行ユニット84(0)～84(X)は、入力ベクトルデータサンプルセット86(0)～86(X)を記憶およびシフトする必要なしに、ならびにベクトルデータファイル82(0)～82(X)からシフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)を再フェッチすることなく、シフトされた入力ベクトルデータサンプルセット86S(0)～86S(X)を受信し、それらのフィルタベクトル処理動作102を実行することによって、十分利用される。3040

#### 【0056】

[00105]この実施形態では、プライマリパイプラインレジスタ120(0)～120(

50

4 X + 3 ) はまとめて、図 4 のベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) の幅である。15 に等しい「X」を有する幅が 512 ビットであるベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) の例では、512 ビット ( すなわち、64 個のレジスタ × 各 8 ビット ) の合計幅を提供するために、各々が 8 ビット幅である 64 個の合計プライマリパイプラインレジスタ 120 ( 0 ) ~ 120 ( 63 ) が存在する。したがって、この例では、プライマリタップ付き遅延線 78 ( 0 ) は、1 つの入力ベクトルデータサンプルセット 86 ( 0 ) ~ 86 ( X ) の幅全体を記憶することが可能である。この例では、8 ビット幅のプライマリパイプラインレジスタ 120 ( 0 ) ~ 120 ( 4 X + 3 ) を設けることによって、入力ベクトルデータサンプルセット 86 ( 0 ) ~ 86 ( X ) は、プライマリパイプラインレジスタ 120 ( 0 ) ~ 120 ( 4 X + 3 ) において、8 ビットフィルタベクトル処理動作のために 8 ビットのベクトルデータサンプルサイズにシフトダウンされ得る。たとえば、16 ビットまたは 32 ビットのサンプルなどにより大きいサイズの入力ベクトルデータサンプル 86 のサイズがフィルタベクトル処理動作のために望ましい場合、入力ベクトルデータサンプルセット 86 ( 0 ) ~ 86 ( X ) は、プライマリパイプラインレジスタ 120 ( 0 ) ~ 120 ( 4 X + 3 ) において、1 度に 2 つのプライマリパイプラインレジスタ 120 によってシフトされ得る。

10

#### 【0057】

[00106] 引き続き図 7 を参照すると、シャドウタップ付き遅延線 78 ( 1 ) もタップ付き遅延線 78 内に設けられる。シャドウタップ付き遅延線 78 ( 1 ) は、次のベクトル処理動作のためにベクトルデータファイル 82 ( 0 ) ~ 82 ( X ) から次の入力ベクトルデータサンプルセット 86N ( 0 ) ~ 86N ( X ) をラッチまたは輸送するために利用され得る。フィルタベクトル処理動作 102 のための各フィルタタップが実行ユニット 84 ( 0 ) ~ 84 ( X ) によって実行されるとき、次の入力ベクトルデータサンプルセット 86N ( 0 ) ~ 86N ( X ) からの次の入力ベクトルデータサンプル 86N は、シャドウタップ付き遅延線 78 ( 1 ) からプライマリタップ付き遅延線 78 ( 0 ) の中にシフトされる。シャドウタップ付き遅延線 78 ( 1 ) はまた、入力ベクトルデータサンプル 86 の解像度が、プライマリタップ付き遅延線 78 ( 0 ) と同様に 8 ビット長に落ちることを可能にするために、複数の 8 ビットシャドウパイプラインレジスタ 122 から構成される。プライマリパイプラインレジスタ 120 ( 0 ) ~ 120 ( 4 X + 3 ) のように、シャドウタップ付き遅延線 78 ( 1 ) 内に設けられたシャドウパイプラインレジスタ 122 ( 0 ) ~ 122 ( 4 X + 3 ) はまとめて、この例では 512 ビットである、ベクトルデータファイル 82 ( 0 ) ~ 82 ( X ) の幅である。したがって、シャドウタップ付き遅延線 78 ( 1 ) のシャドウパイプラインレジスタ 122 ( 0 ) ~ 122 ( 4 X + 3 ) も、1 つの入力ベクトルデータサンプルセット 86 ( 0 ) ~ 86 ( X ) の幅全体を記憶することが可能である。したがって、この実施形態では、プライマリタップ付き遅延線 78 ( 0 ) に含まれるシャドウパイプラインレジスタ 122 ( 0 ) ~ 122 ( 4 X + 3 ) の数は、この例では合計 16 である ( すなわち、X = 15 ) ベクトルデータレーン 100 ( 0 ) ~ 100 ( X ) の数の 4 倍である。したがって、シャドウパイプラインレジスタ 122 の数も、合計 512 ビット ( すなわち、64 個のレジスタ × 各 8 ビット ) 向けにこの例では合計 64 である。プライマリタップ付き遅延線 78 ( 0 ) に関して上記で説明されたように、この例では、8 ビット幅のシャドウパイプラインレジスタ 122 ( 0 ) ~ 122 ( 4 X + 3 ) を設けることによって、次の入力ベクトルデータサンプルセット 86N ( 0 ) ~ 86N ( X ) は、8 ビットフィルタベクトル処理動作のために 8 ビットのベクトルデータサンプルサイズにシフトダウンされ得る。

20

30

40

#### 【0058】

[00107] 図 8 は、図 7 のプライマリタップ付き遅延線 78 ( 0 ) およびシャドウタップ付き遅延線 78 ( 1 ) の中に存在する選択されたプライマリパイプラインレジスタ 120 とシャドウパイプラインレジスタ 122 とを示す概略図である。図 8 は、プライマリパイプラインレジスタ 120 とシャドウパイプラインレジスタ 122 との間の入力ベクトルデータサンプル 86 のシフトの例を説明することを容易にするために提供される。上記で説

50

明されたように、入力ベクトルデータサンプル 86 はまた、プライマリタップ付き遅延線 78(0) およびシャドウタップ付き遅延線 78(1) 内で、ならびにシャドウタップ付き遅延線 78(1) からプライマリタップ付き遅延線 78(0) にシフトされ得る。パイプラインレジスタ 120、122 は、入力ベクトルデータサンプル 86 が必要な場合 8 ビットの解像度でシフトすることを可能にするために、この例では各々 8 ビット幅である。これは下記でより詳細に説明される。プライマリタップ付き遅延線 78(0) およびシャドウタップ付き遅延線 78(1) はまた、同様に下記でより詳細に説明されるように、入力ベクトルデータサンプル 86 の解像度の 16 ビットシフトと 32 ビットシフトとを実行することが可能である。

#### 【0059】

10

[00108] この関連で、図 8 は、図 7 のプライマリタップ付き遅延線 78(0) 内に入力ベクトルデータサンプル 86S(X) のための記憶レジスタを形成する、プライマリパイプラインレジスタ 120(4X+3)、120(2X+1)、120(4X+2)、および 120(2X) の中への入力ベクトルデータサンプル 86 のシフトを示す。プライマリパイプラインレジスタ 120(4X+3) および 120(4X+2) は、それぞれ、図 7 のプライマリタップ付き遅延線 78(0) 内のレジスタ B<sub>31</sub> および B<sub>30</sub> である。プライマリパイプラインレジスタ 120(2X+1) および 120(2X) は、それぞれ、図 7 のプライマリタップ付き遅延線 78(0) 内のレジスタ A<sub>31</sub> および A<sub>30</sub> である。図 7 に示されたように、レジスタ B<sub>31</sub> および B<sub>30</sub> のためのプライマリパイプラインレジスタ 120(4X+3) および 120(4X+2) は、シャドウタップ付き遅延線 78(1) 内の隣接するシャドウパイプラインレジスタ 122 からシフトされた入力ベクトルデータサンプル 86 を受信するように構成される。したがって、図 8 の例では、それぞれ、レジスタ A<sub>0</sub> および A<sub>1</sub> のためのシャドウパイプラインレジスタ 122(0) および 122(1) は、B<sub>31</sub> および B<sub>30</sub> のためのプライマリパイプラインレジスタ 120(4X+3) および 120(4X+2) の中に入力ベクトルデータサンプル 86 をシフトするように構成されるものとして示される。同様に、図 8 の例では、プライマリタップ付き遅延線 78(0) 内の、それぞれ、レジスタ B<sub>1</sub> および B<sub>0</sub> のためのプライマリパイプラインレジスタ 120(2X+3) および 120(2X+2) は、レジスタ A<sub>31</sub> および A<sub>30</sub> のための隣接するプライマリパイプラインレジスタ 120(2X+1) および 120(2X) の中に入力ベクトルデータサンプル 86 をシフトするように構成されるものとして示される。これらのレジスタ間の入力ベクトルデータサンプル 86 の例示的なシフトが次に記載される。

20

#### 【0060】

30

[00109] 引き続き図 8 を参照すると、図 4 ならびに入力ベクトルデータサンプル 86 のシフトにおいて、ベクトルデータファイル 82(0) ~ 82(X) から新しい入力ベクトルデータサンプルセット 86(0) ~ 86(X) をロードするように、プライマリパイプラインレジスタ 120 とシャドウパイプラインレジスタ 122 とを構成する柔軟性を提供するために、入力ベクトルデータサンプル選択器がプライマリパイプラインレジスタ 120 およびシャドウパイプラインレジスタ 122 の各々に関連付けられる。この関連で、プライマリタップ付き遅延線 78(0) において、それぞれ、プライマリパイプラインレジスタ 120(0) ~ 120(4X+3) の中にロードまたはシフトされるベクトルデータに、入力ベクトルデータサンプル選択器 124(0) ~ 124(4X+3) が提供される。シャドウタップ付き遅延線 78(1) において、それぞれ、シャドウパイプラインレジスタ 122(0) ~ 122(4X+3) の中にロードまたはシフトされるベクトルデータに、入力ベクトルデータサンプル選択器 126(0) ~ 126(4X+3) が提供される。入力ベクトルデータサンプル選択器 124(0) ~ 124(4X+3) および入力ベクトルデータサンプル選択器 126(0) ~ 126(4X+3) は、この例では各々マルチプレクサである。下記でより詳細に説明されるように、入力ベクトルデータサンプル選択器 124(0) ~ 124(4X+3)、126(0) ~ 126(4X+3) は、各々、プライマリパイプラインレジスタ 120(0) ~ 120(4X+3) およびシャドウパイプラインレジスタ 122(0) ~ 122(4X+3) の中にロードまたはシフトされるべき

40

50

入力ベクトルデータを選択するために、データ幅シフト制御入力 125 によって制御され得る。

【0061】

[00110] 図 8 では、それぞれ、レジスタ  $B_{31}$ 、 $B_{30}$ 、 $A_{31}$ 、および  $A_{30}$  に対応する、それぞれ、プライマリパイプラインレジスタ 120 ( $4X + 3$ )、120 ( $4X + 2$ )、120 ( $2X + 1$ )、120 ( $2X$ ) のために、入力ベクトルデータサンプル選択器 124 ( $4X + 3$ )、124 ( $4X + 2$ )、124 ( $2X + 1$ )、124 ( $2X$ ) のみが示されていることに留意されたい。図 8 では、それぞれ、レジスタ  $A'_1$ 、 $A'_0$ 、 $B_1$ 、および  $B_0$  に対応する、それぞれ、パイプラインレジスタ 122 (1)、122 (0)、120 ( $2X + 3$ )、120 ( $2X + 2$ ) のために、入力ベクトルデータサンプル選択器 126 (1)、126 (0)、124 ( $2X + 3$ )、124 ( $2X + 2$ ) のみが示されている。

10

【0062】

[00111] 引き続き図 8 を参照すると、ベクトル処理動作のために、新しい入力ベクトルデータがプライマリタップ付き遅延線 78 (0) およびシャドウタップ付き遅延線 78 (1) の中にロードされるべき場合、データ幅シフト制御入力 125 は、入力ベクトルデータサンプル選択器 124 ( $4X + 3$ )、124 ( $4X + 2$ )、124 ( $2X + 1$ )、124 ( $2X$ ) に、ロードデータフローパス 133 ( $4X + 3$ )、133 ( $4X + 2$ )、133 ( $2X + 1$ )、133 ( $2X$ ) を選択させるように、図 4 の VPE22 (1) によって構成され得る。ロードデータフローパス 133 ( $4X + 3$ )、133 ( $4X + 2$ )、133 ( $2X + 1$ )、133 ( $2X$ ) を選択すると、ベクトルデータファイル 82 (0) ~ 82 (X) からの入力ベクトルデータがプライマリパイプラインレジスタ 120 ( $4X + 3$ )、120 ( $4X + 2$ )、120 ( $2X + 1$ )、120 ( $2X$ ) に記憶されることが可能になる。ベクトルデータファイル 82 (0) ~ 82 (X) から入力ベクトルデータをロードすることは、例として VPE22 (1) によって処理されるべき新しいまたは次のベクトル命令上で実行される場合がある。同様に、データ幅シフト制御入力 125 はまた、入力ベクトルデータサンプル選択器 126 (1)、124 ( $2X + 3$ )、126 (0)、124 ( $2X + 2$ ) に、入力データフローパス 135 (1)、133 ( $2X + 3$ )、135 (0)、133 ( $2X + 2$ ) を選択させるように、図 4 の VPE22 (1) によって構成され得る。ロードデータフローパス 135 (1)、133 ( $2X + 3$ )、135 (0)、133 ( $2X + 2$ ) を選択すると、ベクトルデータファイル 82 (0) ~ 82 (X) からの入力ベクトルデータがパイプラインレジスタ 122 (1)、120 ( $2X + 3$ )、124 (0)、120 ( $2X + 2$ ) に記憶されることが可能になる。

20

【0063】

[00112] 引き続き図 8 を参照すると、ベクトル処理動作のために、プライマリタップ付き遅延線 78 (0) およびシャドウタップ付き遅延線 78 (1) に記憶されたベクトルデータがシフトされる必要がある場合、データ幅シフト制御入力 125 は、入力ベクトルデータサンプル選択器 124 ( $4X + 3$ )、124 ( $4X + 2$ )、124 ( $2X + 1$ )、124 ( $2X$ ) に、ベクトルデータサンプルのシフトのための入力データフローパス 137 ( $4X + 3$ )、137 ( $4X + 2$ )、137 ( $2X + 1$ )、137 ( $2X$ ) を選択させるように、図 4 の VPE22 (1) によって構成され得る。データ幅シフト制御入力 125 はまた、入力ベクトルデータサンプル選択器 126 (1)、124 ( $2X + 3$ )、126 (0)、124 ( $2X + 2$ ) に、ベクトルデータサンプルのシフトのための入力データフローパス 139 (1)、137 ( $2X + 3$ )、139 (0)、137 ( $2X + 2$ ) を選択させる。そこに示されているように、入力ベクトルデータサンプル選択器 124 ( $4X + 3$ )、124 ( $4X + 2$ )、124 ( $2X + 1$ )、124 ( $2X$ ) および入力ベクトルデータサンプル選択器 126 (1)、124 ( $2X + 3$ )、126 (0)、124 ( $2X + 2$ ) は、各々、ベクトルデータが他のレジスタにシフトされることを可能にする、それぞれ、出力データフローパス 141 ( $4X + 3$ )、141 ( $4X + 2$ )、141 ( $2X + 1$ )、141 ( $2X$ ) および 143 (1)、141 ( $2X + 3$ )、143 (0)、124 ( $2X + 2$ ) を含む。図 8 に示された出力データフローパスは、次に全体が示される出力デ

40

50

ータフローパス 141(0) ~ 141(4X+3) および 143(0) ~ 143(4X+3) の一部であるが、それぞれ、プライマリタップ付き遅延線 78(0) 内の入力ベクトルデータサンプル選択器 124(0) ~ 124(4X+3) およびシャドウタップ付き遅延線 78(1) 内の入力ベクトルデータサンプル選択器 126(0) ~ 126(4X+3) のために含まれる。

#### 【0064】

[00113] 例として、8ビットベクトルデータのシフト中、入力ベクトルデータサンプル選択器 124(4X+3)、124(4X+2)、124(2X+1)、124(2X) および入力ベクトルデータサンプル選択器 126(1)、124(2X+3)、126(0)、124(2X+2) は、それぞれ、入力データフローパス 137(4X+3)、137(4X+2)、137(2X+1)、137(2X)、139(1)、137(2X+3)、139(0)、137(2X+2) を選択するように構成される。この関連で、例として、プライマリパイプラインレジスタ 120(2X+1) (すなわち、A<sub>31</sub>) 内のベクトルデータは、図 8 に示されたように、プライマリパイプラインレジスタ 120(2X) (すなわち、A<sub>30</sub>) に出力データフローパス 141(2X+1) 上でシフトされる。プライマリパイプラインレジスタ 120(4X+3) (すなわち、B<sub>31</sub>) 内のベクトルデータは、図 8 に示されたように、プライマリパイプラインレジスタ 120(4X+2) (すなわち、B<sub>30</sub>) に出力データフローパス 141(4X+3) 上でシフトされる。シャドウパイプラインレジスタ 122(0) (すなわち、A<sub>1</sub>) 内のベクトルデータは、図 8 に示されたように、プライマリパイプラインレジスタ 120(4X+3) (すなわち、B<sub>31</sub>) に出力データフローパス 143(0) 上でシフトされる。プライマリパイプラインレジスタ 120(2X+3) (すなわち、B<sub>1</sub>) 内のベクトルデータは、図 8 に示されたように、プライマリパイプラインレジスタ 120(4X+2) (すなわち、B<sub>30</sub>) に出力データフローパス 141(2X+3) 上でシフトされる。シャドウパイプラインレジスタ 122(1) (すなわち、A<sub>1</sub>) 内のベクトルデータは、図 8 に示されたように、シャドウパイプラインレジスタ 122(0) (すなわち、A<sub>0</sub>) に出力データフローパス 143(1) 上でシフトされる。プライマリパイプラインレジスタ 120(2X+2) (すなわち、B<sub>0</sub>) 内のベクトルデータは、図 8 に示されたように、プライマリパイプラインレジスタ 120(2X+1) (すなわち、A<sub>31</sub>) に出力データフローパス 141(2X+2) 上でシフトされる。

#### 【0065】

[00114] 引き続き図 8 を参照すると、16ビットベクトルデータのシフト中、入力ベクトルデータサンプル選択器 124(4X+3)、124(4X+2)、124(2X+1)、124(2X) および入力ベクトルデータサンプル選択器 126(1)、124(2X+3)、126(0)、124(2X+2) は、それぞれ、入力データフローパス 145(4X+3)、145(4X+2)、145(2X+1)、145(2X)、147(1)、145(2X+3)、147(0)、145(2X+2) を選択するように構成される。この関連で、例として、プライマリパイプラインレジスタ 120(2X+2) (すなわち、B<sub>0</sub>) 内のベクトルデータは、図 8 に示されたように、プライマリパイプラインレジスタ 120(2X) (すなわち、A<sub>30</sub>) に出力データフローパス 141(2X+2) 上でシフトされる。シャドウパイプラインレジスタ 122(0) (すなわち、A<sub>0</sub>) 内のベクトルデータは、図 8 に示されたように、プライマリパイプラインレジスタ 120(4X+2) (すなわち、B<sub>30</sub>) に出力データフローパス 143(0) 上でシフトされる。プライマリパイプラインレジスタ 120(2X+3) (すなわち、B<sub>1</sub>) 内のベクトルデータは、図 8 に示されたように、プライマリパイプラインレジスタ 120(2X+1) (すなわち、A<sub>31</sub>) に出力データフローパス 141(2X+3) 上でシフトされる。シャドウパイプラインレジスタ 122(1) (すなわち、A<sub>1</sub>) 内のベクトルデータは、図 8 に示されたように、プライマリパイプラインレジスタ 120(4X+3) (すなわち、B<sub>31</sub>) に出力データフローパス 143(1) 上でシフトされる。

#### 【0066】

10

20

30

40

50

[00115] プライマリタップ付き遅延線 7 8 ( 0 ) およびシャドウタップ付き遅延線 7 8 ( 1 )において 3 2 ビットベクトルデータのシフトが望ましい場合、プライマリパイプラインレジスタ 1 2 0 ( 0 ) ~ 1 2 0 ( 4 X + 3 ) およびシャドウパイプラインレジスタ 1 2 2 ( 0 ) ~ 1 2 2 ( 4 X + 3 ) に記憶されたベクトルデータは、必要な場合、2 つの 1 6 ビットベクトルデータのシフト動作においてシフトされ得る。

#### 【 0 0 6 7 】

[00116] 図 7 では、レジスタ B<sub>31</sub> および B<sub>30</sub> のためのプライマリパイプラインレジスタ 1 2 0 ( 4 X + 3 ) および 1 2 0 ( 4 X + 2 ) 、ならびにレジスタ A<sub>31</sub> および A<sub>30</sub> のためのプライマリパイプラインレジスタ 1 2 0 ( 2 X + 1 ) および 1 2 0 ( 2 X ) は、シフトされた入力ベクトルデータサンプル 8 6 S ( X ) に対して互いに論理的に関連付けられるが、図 8 に示されたように、互いに物理的に隣接していないことに留意されたい。この配置は、図 6 B に示されたように、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) 内の入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) の記憶パターンに起因して、この例において提供される。同様に図 6 B に示されたように、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) に記憶された入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) は、ADDRESS 0 および ADDRESS 1 をまたぐ。しかしながら、本明細書内の開示は、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) 内の入力ベクトルサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) のこの記憶パターンに限定されないことに留意されたい。

#### 【 0 0 6 8 】

[00117] さらに、図 8 に関して、タップ付き遅延線 7 8 ( 0 ) 、 7 8 ( 1 ) は、実行されるべきベクトル命令に従って、タップ付き遅延線 7 8 ( 0 ) 、 7 8 ( 1 ) のためのプログラム可能な入力データパス構成に基づいて、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) と実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) との間の入力データフローパス 8 0 ( 0 ) ~ 8 0 ( X ) 内に、選択的に設けられるか、または設けられないように構成可能である。たとえば、ベクトル命令がフィルタベクトル処理命令ではなく、および / または場合によっては入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) をシフトするためにタップ付き遅延線 7 8 ( 0 ) 、 7 8 ( 1 ) を必要としない場合、タップ付き遅延線 7 8 ( 0 ) 、 7 8 ( 1 ) は、入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) をラッチしないように構成され得る。入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) は、プライマリタップ付き遅延線 7 8 ( 0 ) とシャドウタップ付き遅延線 7 8 ( 1 ) とをバイパスすることによって、それぞれの実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) にベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) から供給され得る。このプログラム可能なデータパス構成により、さらに、プライマリタップ付き遅延線 7 8 ( 0 ) およびシャドウタップ付き遅延線 7 8 ( 1 ) が入力データフローパス 8 0 ( 0 ) ~ 8 0 ( X ) 内に設けられるか、または設けられないことが可能になる。プライマリタップ付き遅延線 7 8 ( 0 ) およびシャドウタップ付き遅延線 7 8 ( 1 ) は、必要に応じて、ベクトル命令ごとに、入力データフローパス 8 0 ( 0 ) ~ 8 0 ( X ) 内に設けられるか、または設けられないようにプログラムされ得る。

#### 【 0 0 6 9 】

[00118] 図 9 A は、フィルタベクトル処理命令の第 1 のクロックサイクル ( CYCLE 0 ) の間にプライマリタップ付き遅延線 7 8 ( 0 ) の中にベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) からロードされた入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) を示す。プライマリタップ付き遅延線 7 8 ( 0 ) およびシャドウタップ付き遅延線 7 8 ( 1 ) は、図 7 から簡略化された形式で示されている。グローバルレジスタファイル 4 0 も示されている。最初の入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) が入力ベクトルデータサンプル X 0 ~ X 6 3 としてプライマリタップ付き遅延線 7 8 ( 0 ) の中にロードされる。たとえば、プライマリタップ付き遅延線 7 8 ( 0 ) の中に ( および下記でより詳細に説明されるように、シャドウタップ付き遅延線 7 8 ( 1 ) の中にも ) 最初の入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) をロードするために、特殊ベクトル命令がサポートされる場合がある。この最初の入力ベクトルデータサンプル

10

20

30

40

50

セット 86(0)～86(X)は、図6Bに示されたように、ベクトルデータファイル82(0)～82(X)内のADDRESS0およびADDRESS1に記憶された。ひとえにこの例のための図4のVPE22(1)内のベクトルデータファイル82(0)～82(X)の記憶パターンのせいで、この例では、X0、X1、X32、およびX33が最初の入力ベクトルデータサンプル86(0)を形成することに留意されたい。他の入力ベクトルデータサンプル86は、同様に、図9Aに示されたように形成される(たとえば、86(1)、86(2)、...86(X))。入力ベクトルデータサンプル86を一緒にグループ化して、入力ベクトルデータサンプルセット86(0)～86(X)を形成するために、他のパターンが提供される可能性がある。

【0070】

10

[00119]図9Bは、フィルタベクトル処理命令の第2のクロックサイクル(CYCLE1)の間にシャドウタップ付き遅延線78(1)の中にロードされた次の入力ベクトルデータサンプルセット86N(0)～86N(X)を示す。フィルタ処理動作の実行をセットアップするために、ベクトルデータファイル82(0)～82(X)からの最初の入力ベクトルデータサンプルセット86(0)～86(X)がプライマリタップ付き遅延線78(0)の中にロードされた後に、次の入力ベクトルデータサンプルセット86N(0)～86N(X)がシャドウタップ付き遅延線78(1)の中にロードされる。この次の入力ベクトルデータサンプルセット86N(0)～86N(X)は、入力ベクトルデータサンプルX64～X127としてシャドウタップ付き遅延線78(1)の中にロードされる。この次の入力ベクトルデータサンプルセット86N(0)～86N(X)は、図6Bに示されたように、ベクトルデータファイル82(0)～82(X)内のADDRESS2およびADDRESS3に記憶された。ひとえにこの例のための図4のVPE22(1)内のベクトルデータファイル82(0)～82(X)の記憶パターンのせいで、この例では、X64、X65、X96、およびX97が最初の入力ベクトルデータサンプル86(0)を形成することに留意されたい。入力ベクトルデータサンプル86を一緒にグループ化して、入力ベクトルデータサンプルセット86(0)～86(X)を形成するために、他のパターンが提供される可能性がある。グローバルレジスタファイル40からの最初のフィルタ係数92(0)も、フィルタベクトル処理動作102において使用するために図9Bの実行ユニット84(0)～84(X)へのレジスタ(「C」)内に設けられるものとして示される。

20

【0071】

30

[00120]図7に戻って参照すると、フィルタベクトル処理動作102の各処理ステージの間に入力ベクトルデータサンプル86がプライマリタップ付き遅延線78(0)内でシフトされるとき、シャドウバイラインレジスタ122に記憶された次の入力ベクトルデータサンプル86Nも、シャドウタップ付き遅延線78(1)のシャドウバイラインレジスタ122内でシフトされる。図7の最初のシャドウバイラインレジスタ122(0)に記憶された入力ベクトルデータサンプル86は、各シフトの間にプライマリタップ付き遅延線78(0)の最後のプライマリバイラインレジスタ120(4X+3)の中にシフトされる。したがって、このようにして、フィルタベクトル処理動作102の処理ステージが実行ユニット84(0)～84(X)において進行するとき、シャドウタップ付き遅延線78(1)に最初に記憶された次の入力ベクトルデータサンプルセット86N(0)～86N(X)の少なくとも一部分は、処理のために実行ユニット84(0)～84(X)に供給されるために、プライマリタップ付き遅延線78(0)の中にシフトされる。シフトの回数は、この例ではフィルタベクトル処理動作102において提供されたフィルタタップの数に依存する。ベクトルデータファイル82(0)～82(X)からプライマリタップ付き遅延線78(0)およびシャドウタップ付き遅延線78(1)の中にフェッチされた入力ベクトルデータサンプルセット86(0)～86(X)内の入力ベクトルデータサンプル86の数が、フィルタベクトル処理動作102におけるフィルタタップの数よりも大きい場合、実行ユニット84(0)～84(X)は、任意のさらなる入力ベクトルデータサンプルセット86(0)～86(X)がベクトルデータファイル82(0)

40

50

~82(X)から再フェッチされることなく、フィルタベクトル処理動作102を実行することができる。しかしながら、フィルタベクトル処理動作102におけるフィルタタップの数が、ベクトルデータファイル82(0)~82(X)からプライマリタップ付き遅延線78(0)およびシャドウタップ付き遅延線78(1)の中にフェッチされた入力ベクトルデータサンプルセット86(0)~86(X)内の入力ベクトルデータサンプル86よりも大きい場合、フィルタベクトル処理動作102の一部として、さらなる入力ベクトルデータサンプルセット86(0)~86(X)がベクトルデータファイル82(0)~82(X)からフェッチされ得る。フィルタベクトル処理動作102がシフトされた入力ベクトルデータサンプルセット86S(0)~86S(X)に対して完了した後、タップ付き遅延線78(0)、78(1)内に未処理の入力ベクトルデータサンプル86Sが存在する場合、実行ユニット84(0)~84(X)は、次いで、次のフィルタベクトル処理動作のためのシフトされた入力ベクトルデータサンプルセット86S(0)~86S(X)として、プライマリタップ付き遅延線78(0)に記憶された前の次の入力ベクトルデータサンプルセット86N(0)~86N(X)を供給され得る。

10

#### 【0072】

[00121]シャドウタップ付き遅延線78(1)を提供するための別の例示的な論理的根拠は以下の通りである。現在のフィルタベクトル処理動作102が、ベクトルデータレン100(0)~100(X)の幅で提供され得るよりも多くの入力ベクトルデータサンプル86を要する場合、シャドウタップ付き遅延線78(1)の中にロードされたさらなる入力ベクトルデータサンプルセット86(0)~86(X)は、遅延がないフィルタベクトル処理動作102の間、実行ユニット84(0)~84(X)に利用可能である。フィルタベクトル処理動作102が、実行中シフトされた入力ベクトルデータサンプルセット86S(0)~86S(X)を通じて進行するとき、上記で説明されたように、シャドウタップ付き遅延線78(1)の中にロードされたさらなる次の入力ベクトルデータサンプルセット86N(0)~86N(X)が、プライマリタップ付き遅延線78(0)の中にシフトされる。したがって、このようにして、実行ユニット84(0)~84(X)によるベクトル処理において使用するための次の入力ベクトルデータサンプルセット86N(0)~86N(X)は、遅延なく利用可能である。ベクトルデータファイル82(0)~82(X)の幅の単一のフェッチされた入力ベクトルデータサンプルセット86(0)~86(X)が、フィルタベクトル処理動作102全体を実行するのに十分であるかどうかにかかわらず、実行ユニット84(0)~84(X)は、フィルタベクトル処理動作102の間、十分に利用され続けることができる。

20

#### 【0073】

[00122]最初の入力ベクトルデータサンプルセット86N(0)~86N(X)および次の入力ベクトルデータサンプルセット86N(0)~86N(X)が、それぞれ、プライマリタップ付き遅延線78(0)およびシャドウタップ付き遅延線78(1)の中にロードされた後、プライマリタップ付き遅延線78(0)に供給された最初の入力ベクトルデータサンプルセット86(0)~86(X)は、フィルタベクトル処理動作102の最初の処理ステージにおいて処理されるために、それぞれの実行ユニット84(0)~84(X)に供給される(図5のブロック108)。最初の入力ベクトルデータサンプルセット86(0)~86(X)が実行ユニット84(0)~84(X)によって処理された後、最初の入力ベクトルデータサンプルセット86(0)~86(X)は、実行ユニット84(0)~84(X)によって処理されるべきシフトされた入力ベクトルデータサンプルセット86S(0)~86S(X)になるために、プライマリタップ付き遅延線78(0)内でシフトされる。図4のVPE22(1)において示されたように、シフトされた入力ベクトルデータサンプル86S(0)は実行ユニット84(0)に供給され、シフトされた入力ベクトルデータサンプル86S(1)は実行ユニット84(1)に供給され、以下同様である。

40

#### 【0074】

[00123]次に、実行ユニット84(0)~84(X)は、フィルタベクトル処理動作1

10

20

30

40

50

0 2 を実行する (図 5 のブロック 110)。より詳細には、実行ユニット 84(0) ~ 84(X) は、この例では演算:  $y[n] = x[n-7] * h_7$  に従って、第 1 の繰返しにおいて最初の入力ベクトルデータサンプルセット 86(0) ~ 86(X) を現在のフィルタ係数 92(0) と乗算し、ここで、 $x[n-7]$  は、結果として生じるフィルタ出力ベクトルデータサンプルセット 94(0) ~ 94(X) を供給する最初の入力ベクトルデータサンプルセット 86(0) ~ 86(X) である。フィルタベクトル処理動作 102 の次の繰返し (図 5 のブロック 110) において、フィルタベクトル処理動作 102 のための次のシフトされた入力ベクトルデータサンプルセット 86S(0) ~ 86S(X) は、現在のフィルタ係数 92(1) ~ 92(Y-1) と乗算される。実行ユニット 84(0) ~ 84(X) は、新しい前の、結果として生じるフィルタ出力ベクトルデータサンプルセット 94(0) ~ 94(X) を供給するために、結果として生じるフィルタ出力ベクトルデータサンプルセット 94(0) ~ 94(X) を、実行ユニット 84(0) ~ 84(X) によって計算された前の、結果として生じるフィルタ出力ベクトルデータサンプルセット 94(0) ~ 94(X) と累算する (図 5 のブロック 112)。フィルタベクトル処理動作 102 の最初の処理ステージでは、前の、結果として生じるフィルタ出力ベクトルデータサンプルセットは存在しない。

10

#### 【0075】

[00124] フィルタベクトル処理動作 102 のすべての処理ステージが完了した場合 (図 5 のブロック 114)、ベクトルデータファイル 82(0) ~ 82(X) に供給され記憶されるために、出力データフローパス 98(0) ~ 98(X) 内の、結果として生じるフィルタ出力ベクトルデータサンプルセット 94(0) ~ 94(X) として、累算された前の、結果として生じるフィルタ出力ベクトルデータサンプルセット 94(0) ~ 94(X) が供給される (図 5 のブロック 116)。フィルタベクトル処理動作 102 のすべての処理ステージが完了していない場合 (図 5 のブロック 114)、フィルタベクトル処理動作 102 に次のシフトされた入力ベクトルデータサンプルセット 86S(0) ~ 86S(X) を供給するために、タップ付き遅延線 78(0) および 78(1) に記憶されたサンプルがタップ付き遅延線 78(0)、78(1) 内でシフトされる (図 5 のブロック 118)。シフトされた入力ベクトルデータサンプルセット 86S(0) ~ 86S(X) は、フィルタベクトル処理動作 102 が完了するまで、前の、結果として生じるフィルタ出力ベクトルデータサンプルセットと累算するために、中間結果として次の、結果として生じるフィルタ出力ベクトルデータサンプルセットを計算するために供給される。タップ付き遅延線 78(0)、78(1) 内にシフトされた入力ベクトルデータサンプルセット 86S(0) ~ 86S(X) を供給するために入力ベクトルデータサンプル 86 をシフトすることは、図 7 に関して詳細に上記で前述された。フィルタベクトル処理動作 102 に実行ユニット 84(0) ~ 84(X) によって供給された中間結果の最終的な累算は、図 4 に示されたように、実行ユニット 84(0) ~ 84(X) から、結果として生じるフィルタ出力ベクトルデータサンプルセット 94(0) ~ 94(X) として供給される。

20

30

#### 【0076】

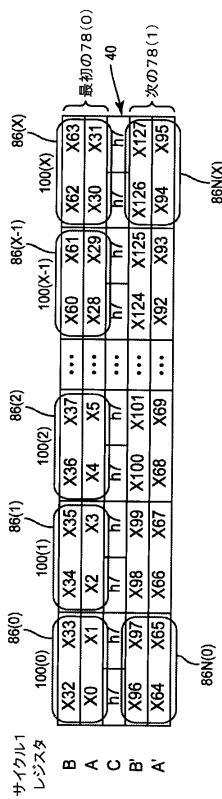

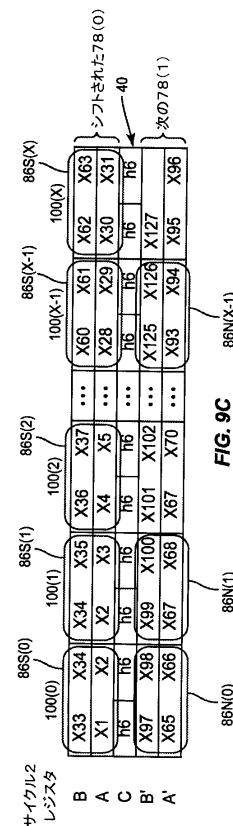

[00125] 図 9C は、次のフィルタ処理動作  $y[n] = x[n-6] * h_6$  のための次のシフトされた入力ベクトルデータサンプルセット 86S(0) ~ 86S(X) になるために、フィルタベクトル処理動作 102 の 2 番目の処理ステージにおいて、入力ベクトルデータサンプルセット 86(0) ~ 86(X) がシフトされたときのタップ付き遅延線 78 のコンテンツを示す。プライマリタップ付き遅延線 78(0) 内のシフトされた入力ベクトルデータサンプルセット 86S(0) ~ 86S(X) は、実行されているベクトル命令によって規定された入力ベクトルデータサンプルのシフト幅に従って、プライマリパイプラインレジスタ 120(0) ~ 120(4X+3) 内でシフトされる。たとえば、図 9C に示されたように、サンプル X2 はシフトされた入力ベクトルデータサンプル 86S(0) 内でシフトされる。新しいシフトされた入力ベクトルデータサンプルセット 86S(0) ~ 86S(X) は、フィルタベクトル処理動作 102 の次のフィルタタップのための実行のために、実行ユニット 84(0) ~ 84(X) に供給される。実行ユニット 84(0) ~ 84(X) に供給される。実行ユニット 84(0) ~ 84(X) に供給される。

40

50

) ~ 8 4 ( X ) に供給されたフィルタ係数 9 2 は、この例では「 h 6 」である次のフィルタ係数 9 2 である。

#### 【 0 0 7 7 】

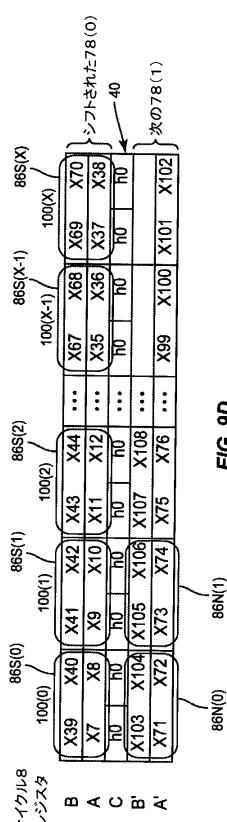

[00126]引き続き図 5 を参照すると、次のフィルタ係数 9 2 と乗算される（図 5 のブロック 1 1 0 ）ために、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) にプライマリタップ付き遅延線 7 8 ( 0 ) からシフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) を供給する（図 5 のブロック 1 0 8 ）ことによって、プロセスは繰り返す。結果として生じるフィルタ出力ベクトルデータサンプルセット 9 4 ( 0 ) ~ 9 4 ( X ) が前の、結果として生じるフィルタ出力ベクトルデータサンプルセット 9 4 ( 0 ) ~ 9 4 ( X ) と累算される（図 5 のブロック 1 1 2 ）。図 9 D は、例示的なフィルタベクトル処理動作 1 0 2 の最後の処理ステージの間、タップ付き遅延線 7 8 ( 0 ) 、 7 8 ( 1 ) 内に存在する入力ベクトルデータサンプル 8 6 の状態を示す。図 9 D に示されたこの例では、フィルタ係数 9 2 「 h 7 」 ~ 「 h 0 」（すなわち、 9 2 ( 0 ) ~ 9 2 ( Y - 1 ) ）のせいで、フィルタベクトル処理動作 1 0 2 において 8 個のフィルタタップ ( Y ) が存在した。図 9 D に示されたように、「 h 0 」はフィルタベクトル処理動作 1 0 2 における最後のフィルタ係数 9 2 である。シフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) は（フィルタタップの数よりも 1 回少ない） 7 回シフトされており、その結果、フィルタベクトル処理動作 1 0 2 のための最後の 8 番目の処理ステージにおいて、入力ベクトルデータサンプル X 3 9 がプライマリタップ付き遅延線 7 8 ( 0 ) 内のシフトされた入力ベクトルデータサンプル 8 6 S ( 0 ) に記憶される。

#### 【 0 0 7 8 】

[00127]上述されたフィルタベクトル処理動作 1 0 2 の例は、フィルタベクトル処理動作 1 0 2 を提供するために V P E 2 2 ( 1 ) 内のベクトルデータレーン 1 0 0 ( 0 ) ~ 1 0 0 ( X ) の各々を利用するが、それは必要でないことに留意されたい。フィルタベクトル処理動作 1 0 2 は、フィルタベクトル処理動作 1 0 2 に利用されるべきベクトルデータレーン 1 0 0 ( 0 ) ~ 1 0 0 ( X ) のサブセットを必要とするにすぎない場合がある。たとえば、入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) の幅がすべてのベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) の幅よりも小さい場合があり、ここで、フィルタベクトル処理動作 1 0 2 と並列に実行されるべき他のベクトル処理動作にさらなるベクトルデータレーン 1 0 0 を利用することが望ましい。このシナリオでは、図 7 のタップ付き遅延線 7 8 ( 0 ) 、 7 8 ( 1 ) は、最後のベクトルデータレーン 1 0 0 ( X ) に到達するより前に、ベクトルデータレーン 1 0 0 内のシフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) として、シャドウタップ付き遅延線 7 8 ( 1 ) からプライマリタップ付き遅延線 7 8 ( 0 ) に次の入力ベクトルデータサンプルセット 8 6 N ( 0 ) ~ 8 6 N ( X ) をシフトするように、修正される必要があり得る。

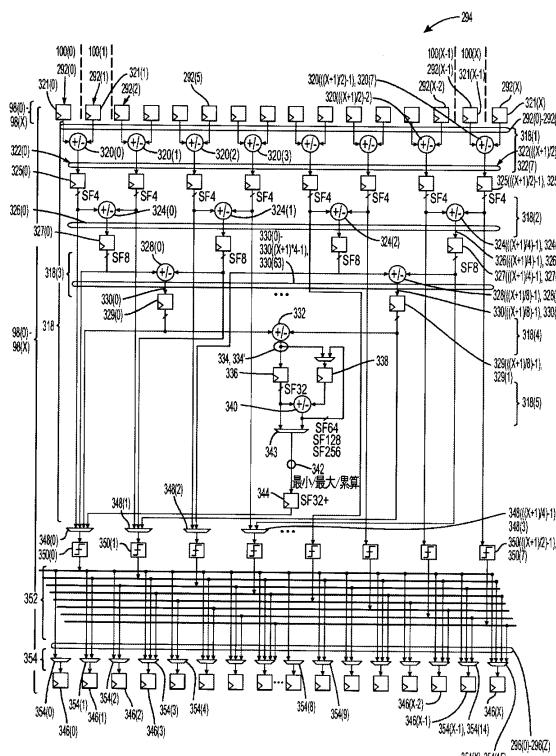

#### 【 0 0 7 9 】

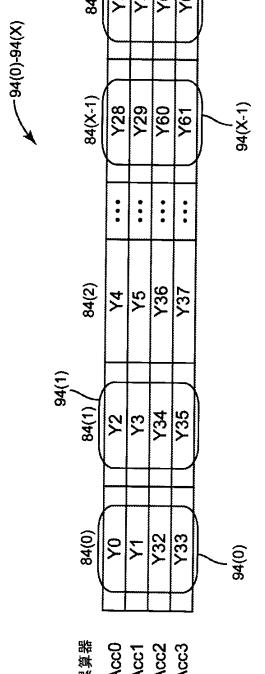

[00128]図 1 0 は、上記の例における例示的な 8 個のタップフィルタベクトル処理ステージが、  $y [ n ] = x [ n ] * h 0 + x [ n - 1 ] * h 1 + \dots + x [ n - 7 ] * h 7$  に従って完全に実行された後の、図 4 の V P E 2 2 ( 1 ) 内の実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) 内の累算器のコンテンツ（すなわち、結果として生じるフィルタ出力ベクトルデータサンプル 9 4 ）の概略図である。この例では、各実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) は、ベクトルデータレーン 1 0 0 ( 0 ) ~ 1 0 0 ( X ) ごとに並列に配置された 4 つの累算器を有するので、累算器 A c c 0 ~ A c c 3 が図 1 0 に示されている。累算された、結果として生じる出力ベクトルデータサンプルは、さらなる分析および / または処理のためにそこに記憶されるべき全体の、結果として生じるフィルタ出力ベクトルデータサンプルセット 9 4 ( 0 ) ~ 9 4 ( X ) として、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) に出力データフローパス 9 8 ( 0 ) ~ 9 8 ( X ) 上で供給され得る。必要な場合、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) から図 2 のベクトルユニットデータメモリ 3 2 に、結果として生じるフィルタ出力ベクトルデータサンプルセット 9 4 ( 0 ) ~ 9 4 ( X ) の行を移動するために、特殊なベクトル命令が V P E 2 2 ( 1 ) によってサポート

10

20

30

40

50

される場合がある。

【0080】

[00129] フィルタベクトル処理動作 102 以外の他のタイプのベクトル処理動作も、上記で説明された図 4 の VPE22(1) 内に設けられたタップ付き遅延線 78 と同じまたは同様のタップ付き遅延線 78 の使用による、VPE における処理効率を享受することができる。たとえば、VPE における入力ベクトルデータサンプルセット 86 のシフトを伴う別の特殊なベクトル処理動作は、( 本明細書では「相関ベクトル処理動作」と呼ばれる ) 相関 / 共分散ベクトル処理動作である。例として、CDMA システムにおいてユーザ信号と他のユーザの信号との間の良好な分離を提供するために、CDMA システムにおいてユーザ信号を復調するための直接スペクトル拡散コード ( DSSC ) ( すなわち、チップシーケンス ) を選ぶために相関演算を提供するようにベクトル処理を利用することが望ましい場合がある。信号の分離は、受信された信号を所望のユーザのローカルに生成されたチップシーケンスと相関させることによって行われる。信号が所望のユーザのチップシーケンスと一致する場合、相関関数は高くなり、CDMA システムはその信号を抽出することができる。所望のユーザのチップシーケンスが信号と共通する部分を少ししか、またはまったく有していない場合、相関は可能な限りゼロに近い ( したがって信号を除去する ) はずであり、これは相互相関と呼ばれる。チップシーケンスがゼロ以外の任意の時間オフセットで信号と相関される場合、相関は可能な限りゼロに近いはずである。これは自己相関と呼ばれ、マルチパス干渉を拒絶するために使用される。

【0081】

[00130] しかしながら、相関演算は、ベクトルプロセッサにおいて提供される特殊なデータフローパスに起因して、ベクトルプロセッサにおいて並列化することは困難であり得る。相関されるべき信号を表す入力ベクトルデータサンプルセットが遅延タップ間でシフトされると、入力ベクトルデータサンプルセットはベクトルデータファイルから再フェッチされ、したがって電力消費が増大し、スループットが低減される。メモリからの入力ベクトルデータサンプルセットの再フェッチを最小化するために、データフローパスは、効率的な並列化処理のために、遅延タップと同じ数の乗算器を設けるように構成される可能性がある。しかしながら、他のベクトル処理動作は、より少ない乗算器しか必要としない場合があり、それにより、データフローパス内の乗算器の非効率的なスケーリングおよび過少利用がもたらされる。スケーラビリティを提供するために、乗算器の数が遅延タップの数よりも少なくなるように削減された場合、相関処理の様々なフェーズに対して同じ入力ベクトルデータサンプルセットを取得するために、メモリにより多くの再フェッチが必要とされることによって、並列化が制限される。

【0082】

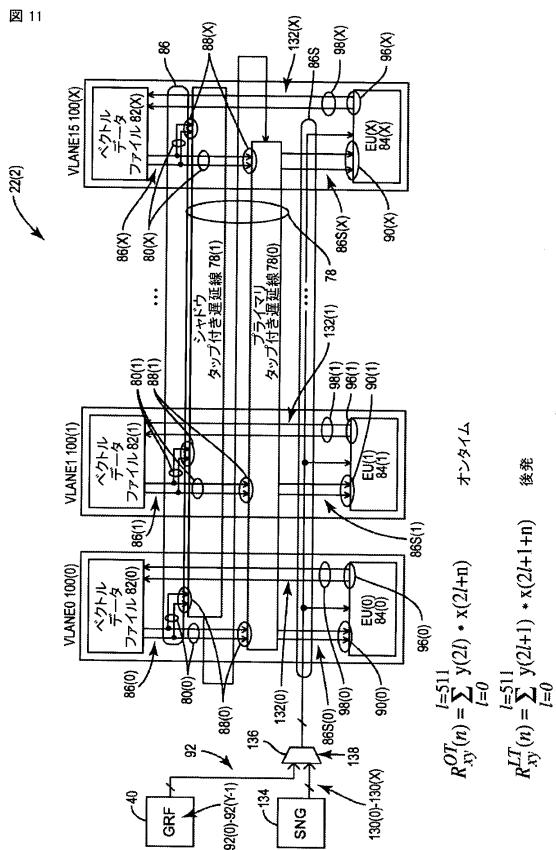

[00131] この関連で、図 11 は、図 2 の VPE22 として提供され得る別の例示的な VPE22(2) の概略図である。下記でより詳細に記載されるように、図 11 の VPE22(2) は、ベクトルデータサンプルの再フェッチが除去または低減され、電力消費が低減される、VPE22(2) 内の精度相関ベクトル処理動作を提供するように構成される。精度相関ベクトル処理動作は、ベクトルデータサンプルの再フェッチを必要とし、それにより結果として電力消費が増大する、中間結果の記憶を必要とする相関ベクトル処理動作と比較して、VPE22(2) において提供され得る。ベクトルデータファイルからの入力ベクトルデータサンプルの再フェッチを除去または最小化して、電力消費を低減し、処理効率を改善するために、図 4 の VPE22(1) に含まれるタップ付き遅延線 78 も、VPE22(2) 内のベクトルデータファイル 82(0) ~ 82(X) と ( 「 EU 」 とも標記される ) 実行ユニット 84(0) ~ 84(X) との間の入力データフローパス 80(0) ~ 80(X) に含まれる。「 X 」 + 1 は、この例におけるベクトルデータサンプルの処理用に VPE22(2) 内に設けられる並列入力データレーンの最大数である。上記で前に説明されたように、タップ付き遅延線 78 は、ベクトルデータファイル 82(0) ~ 82(X) の対応するサブセットまたはすべてから入力ベクトルデータサンプルセット 86(0) ~ 86(X) の入力ベクトルデータサンプル 86 のサブセットまたはすべてと

10

20

30

40

50

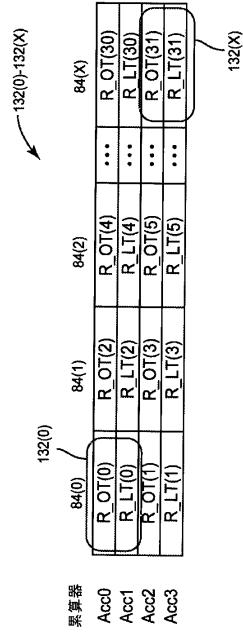

して、タップ付き遅延線入力 8 8 ( 0 ) ~ 8 8 ( X ) 上で入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) を受信するよう構成される。すべての入力ベクトルデータサンプル 8 6 は、入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) を備える。下記により詳細に説明されるように、ベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) からの入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) は、結果として生じる相関出力ベクトルデータサンプルセット 1 3 2 ( 0 ) ~ 1 3 2 ( X ) を供給するために、基準ベクトルデータサンプルセット 1 3 0 ( 0 ) ~ 1 3 0 ( X ) と V P E 2 2 ( 2 ) において相関される。基準ベクトルデータサンプルセット 1 3 0 ( 0 ) ~ 1 3 0 ( X ) は、この例では 1 3 0 ( 0 ) 、 1 3 0 ( 1 ) 、 . . . 、 および 1 3 0 ( X ) である、「 X + 1 」個の基準ベクトルデータサンプル 1 3 0 から構成される。結果として生じる相関出力ベクトルデータサンプルセット 1 3 2 ( 0 ) ~ 1 3 2 ( X ) は、この例では 1 3 2 ( 0 ) 、 1 3 2 ( 1 ) 、 . . . 、 および 1 3 2 ( X ) である、「 X + 1 」個の、結果として生じる相関出力ベクトルデータサンプル 1 3 2 から構成される。

10

#### 【 0 0 8 3 】

[00132]引き続き図 1 1 を参照すると、タップ付き遅延線 7 8 は、シフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) を供給するために、 V P E 2 2 ( 2 ) によって実行されるべき相関ベクトル命令に従う相関ベクトル処理動作の相関遅延タップ（すなわち、相関処理ステージ）ごとに、入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) をシフトする。シフトされた入力ベクトルデータサンプル 8 6 S のすべては、シフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) を備える。タップ付き遅延線 7 8 は、相関ベクトル処理動作中、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) の実行ユニット入力 9 0 ( 0 ) ~ 9 0 ( X ) にシフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) を供給するために、入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) をシフトする。このようにして、シフトされた入力ベクトルデータサンプルセット 8 6 S ( 0 ) ~ 8 6 S ( X ) に対して実行される動作に基づく中間相関結果は、 V P E 2 2 ( 2 ) によって実行される相関ベクトル処理動作の各処理ステージの間に、記憶、シフト、およびベクトルデータファイル 8 2 ( 0 ) ~ 8 2 ( X ) から再フェッチされる必要がない。このように、タップ付き遅延線 7 8 は、電力消費を低減し、 V P E 2 2 ( 2 ) によって実行される相関ベクトル処理動作についての処理効率を上げることができる。

20

#### 【 0 0 8 4 】

[00133]引き続き図 1 1 を参照すると、実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) は、相関ベクトル処理動作のためのシーケンス番号発生器 ( S N G ) 1 3 4 に記憶された基準ベクトルデータサンプルセット 1 3 0 ( 0 ) ~ 1 3 0 ( X ) の中から基準ベクトルデータサンプル 1 3 0 も受信する。実行ユニット 8 4 ( 0 ) ~ 8 4 ( X ) は、相関ベクトル処理動作の一部として、基準ベクトルデータサンプルセット 1 3 0 ( 0 ) ~ 1 3 0 ( X ) を入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) と相関させるように構成される。しかしながら、シーケンス番号発生器 ( S N G ) 1 3 4 はレジスタまたは他のファイルでもあり得ることに留意されたい。この例における相関ベクトル処理動作は C D M A 相関ベクトル命令向けなので、シーケンス番号発生器 1 3 4 は、基準ベクトルデータサンプルセット 1 3 0 ( 0 ) ~ 1 3 0 ( X ) を供給するために、この実施形態において提供される。基準ベクトルデータサンプルセット 1 3 0 ( 0 ) ~ 1 3 0 ( X ) と入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) との間の相関が高い場合、基準ベクトルデータサンプルセット 1 3 0 ( 0 ) ~ 1 3 0 ( X ) は、入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) からの信号抽出に使用するための生成されたチップシーケンスとして供給される。

40

#### 【 0 0 8 5 】

[00134]たとえば、 C D M A ベクトル相関命令向けの相関ベクトル処理動作は、入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) 内のオンタイム入力ベクトルデータサンプル 8 6 と、入力ベクトルデータサンプルセット 8 6 ( 0 ) ~ 8 6 ( X ) 内の後発入

50

カベクトルデータサンプルとの間の相関を提供する可能性がある。たとえば、入力ベクトルデータサンプルセット 86(0)～86(X)内のオンタイム入力ベクトルデータサンプル 86 は、入力ベクトルデータサンプルセット 86(0)～86(X)内の偶数の入力ベクトルデータサンプル 86(たとえば、86(0)、86(2)、86(4)、...、86(X-1))であり得る。入力ベクトルデータサンプルセット 86(0)～86(X)内の後発入力ベクトルデータサンプル 86 は、入力ベクトルデータサンプルセット 86(0)～86(X)内の奇数の入力ベクトルデータサンプル 86(たとえば、86(1)、86(3)、86(5)、...、86(X))であり得る。代替として、オンタイム入力ベクトルデータサンプル 86 は奇数の入力ベクトルデータサンプル 86 であり得るし、後発入力ベクトルデータサンプル 86 は偶数の入力ベクトルデータサンプル 86 であり得る。相関ベクトル処理動作の結果、オンタイム入力ベクトルデータサンプル 86 のための、結果として生じる相関出力ベクトルデータサンプルセット 132(0)～132(X)、および後発入力ベクトルデータサンプル 86 は、信号抽出に入力ベクトルデータサンプルセット 86(0)～86(X)からのオンタイム入力ベクトルデータサンプルを使用するべきか、または後発入力ベクトルデータサンプルを使用するべきかを決定するために使用され得る。たとえば、オンタイム相関ベクトル処理動作は、以下の式に従って供給される場合がある、

【0086】

【数2】

10

$$R_{xy}^{OT}[n] = \sum_{l=0}^{l=511} y[2l]^* x[2l+n]$$

【0087】

ここで、

n は入力信号サンプルの数であり、

$x[n]$  はデジタル化入力信号 66 であり、

$y[n]$  は基準信号であり、

$l$  はサンプル数である。

【0088】

30

[00135] 後発相関ベクトル処理動作は、以下の式に従って提供される場合がある、

【0089】

【数3】

$$R_{xy}^{LT}[n] = \sum_{l=0}^{l=511} y[2l+1]^* x[2l+1+n]$$

【0090】

ここで、

n は入力信号サンプルの数であり、