(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6674309号

(P6674309)

(45) 発行日 令和2年4月1日(2020.4.1)

(24) 登録日 令和2年3月10日(2020.3.10)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G 06 F 12/00 5 6 0 C

請求項の数 10 (全 39 頁)

(21) 出願番号 特願2016-82746 (P2016-82746)

(22) 出願日 平成28年4月18日 (2016.4.18)

(65) 公開番号 特開2017-194736 (P2017-194736A)

(43) 公開日 平成29年10月26日 (2017.10.26)

審査請求日 平成31年4月3日 (2019.4.3)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100101498

弁理士 越智 隆夫

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100128668

弁理士 斎藤 正巳

(72) 発明者 大輪 寧司

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】メモリ制御装置及びメモリ制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリに対する書き込み要求を出力し、

前記書き込み要求が許可されたことに応じて画像データを前記メモリへ書き込み、

1つの第1のブロックの書き込み動作が完了する毎に第1のイベントを発行する、

書き込み手段と、

前記書き込み手段によって前記メモリに書き込まれた画像データの読み出し要求を出力し、

前記読み出し要求が許可されたことに応じて前記メモリから前記画像データを読み出し、

1フレームの画像データが前記書き込み手段により前記メモリに書き込まれている間に、

前記メモリに書き込まれた前記1フレームの画像データの読み出し要求を出力し、

1つの第2のブロックの読み出し動作が完了する毎に第2のイベントを発行する、

読み出し手段と、

前記書き込み要求及び前記読み出し要求をそれぞれ許可するか否かを制御する制御手段と

を有し、

前記書き込み手段により前記メモリに書き込まれる画像データの1フレームに複数の前記第1のブロックが含まれ、

前記読み出し手段により前記メモリから読み出される画像データの1フレームに、前記

第 2 のブロックが含まれ、

前記制御手段は、

前記第 1 のイベントに応じて前記 1 フレームに含まれる前記第 2 のブロックの水平方向の数に基づく第 1 の値だけカウント値を増加させる処理を行い、

前記第 2 のイベントに応じて前記 1 フレームに含まれる前記第 1 のブロックの水平方向の数に基づく第 2 の値だけカウント値を低減させる処理を行い、

前記カウント値が第 1 閾値より大きい場合に前記書き込み要求を許可せず、

前記カウント値が前記第 1 閾値より小さい第 2 閾値より小さい場合に前記読み出し要求を許可しない、

ことを特徴とするメモリ制御装置。

10

#### 【請求項 2】

前記制御手段は、

前記カウント値と前記第 1 閾値とを比較する第 1 の比較部と、

前記カウント値と前記第 2 閾値とを比較する第 2 の比較部と、

前記第 1 の比較部による比較結果に応じて前記書き込み手段からの書き込み要求をマスクするか否かを制御する第 1 のマスク部と、

前記第 2 の比較部による比較結果に応じて前記読み出し手段からの読み出し要求をマスクするか否かを制御する第 2 のマスク部と

を有する

ことを特徴とする請求項 1 に記載のメモリ制御装置。

20

#### 【請求項 3】

前記書き込み手段は、書き込みアドレスが前記第 1 のブロックの最終アドレスに達したことに応じて前記第 1 のイベントを発行し、

前記読み出し手段は、読み出しアドレスが前記第 2 のブロックの最終アドレスに達したことに応じて前記第 2 のイベントを発行する

ことを特徴とする請求項 1 または 2 に記載のメモリ制御装置。

#### 【請求項 4】

前記制御手段は、前記読み出し手段により 1 フレームの前記画像データの読み出しが完了したことに応じて、前記カウント値を初期値に設定することを特徴とする請求項 1 から 3 のいずれか 1 項に記載のメモリ制御装置。

30

#### 【請求項 5】

前記第 1 のブロックと前記第 2 のブロックはそれぞれ 1 フレームの画像データを分割することにより決定され、

前記初期値は、前記第 1 のブロックと前記第 2 のブロックとの分割の態様に応じて設定されることを特徴とする請求項 4 に記載のメモリ制御装置。

#### 【請求項 6】

前記書き込み手段は、1 フレームの複数の前記第 1 のブロックを、第 1 の所定の順序で前記メモリに書き込み、

前記読み出し手段は、1 フレームの複数の前記第 2 のブロックを、前記第 1 の所定の順序に応じた第 2 の所定の順序で前記メモリから読み出す

40

ことを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載のメモリ制御装置。

#### 【請求項 7】

前記第 1 のブロックのサイズと前記第 2 のブロックのサイズとが異なることを特徴とする請求項 1 から 6 のいずれか 1 項に記載のメモリ制御装置。

#### 【請求項 8】

前記第 1 のブロックと前記第 2 のブロックはそれぞれ、最小のアクセス単位、複数の前記最小のアクセス単位を含む行、1 フレームを水平方向及び垂直方向に分割することにより決定される分割ブロック、水平方向に隣接する複数の前記分割ブロックを含むブロック行、及び、1 フレーム、の何れかであることを特徴とする請求項 1 から 7 のいずれか 1 項に記載のメモリ制御装置。

50

### 【請求項 9】

前記第2閾値は、前記1フレームに含まれる前記第1のブロックの垂直方向の数と前記1フレームに含まれる前記第2のブロックの垂直方向の数との差、前記1フレームに含まれる前記第2のブロックの水平方向の数、および前記1フレームに含まれる前記第1のブロックの水平方向の数を、乗算して得られた値であり、

前記第1閾値は、前記第2閾値よりも前記第1のブロックの水平方向の分割数、および前記第2のブロックの水平方向の分割数を加算した値に対応する量だけ大きい値である、ことを特徴とする請求項1から8のいずれか1項に記載のメモリ制御装置。

### 【請求項 10】

メモリに対する書き込み要求を出力し、前記書き込み要求が許可されたことに応じて画像データを前記メモリに書き込み、1つの第1のブロックの書き込み動作が完了する毎に第1のイベントを発行するステップと、10

前記メモリに書き込まれた画像データの読み出し要求を出力し、前記読み出し要求が許可されたことに応じて前記メモリから前記画像データを読み出し、1フレームの画像データが前記メモリに書き込まれている間に、前記メモリに書き込まれた前記1フレームの画像データの読み出し要求を出力し、1つの第2のブロックの書き込み動作が完了する毎に第2のイベントを発行するステップと、

前記書き込み要求と前記読み出し要求をそれぞれ許可するか否かを制御するステップと、11

を有し、20

前記メモリに書き込まれる画像データの1フレームには複数の前記第1のブロックが含まれ、

前記メモリから読み出される画像データの1フレームには、前記第2のブロックが含まれ、

前記制御するステップは、

前記第1のイベントに応じて前記1フレームに含まれる前記第2のブロックの水平方向の数に基づく第1の値だけカウント値を増加させる処理を行うステップと、

前記第2のイベントに応じて前記1フレームに含まれる前記第1のブロックの水平方向の数に基づく第2の値だけカウント値を低減させる処理を行うステップと、30

前記カウント値が第1閾値より大きい場合に前記書き込み要求を許可しないステップと、

前記カウント値が前記第1閾値より小さい第2閾値より小さい場合に前記読み出し要求を許可しないステップと、31

を含むことを特徴とするメモリ制御方法。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、メモリ制御装置及びメモリ制御方法に関する。

#### 【背景技術】

#### 【0002】

近年、デジタルカメラ等に用いられる撮像素子の画素数は、数千万画素にまでなっている。撮像素子の画素数の増加に伴い、撮像素子によって取得される画像データのメモリへの書き込みや読み出しに要する時間も長くなる。メモリへの書き込みや読み出しに要する時間を短縮させるために、例えば、撮像素子からの画像データをメモリに書き込んだ直後に、その画像データをメモリから読み出して画像処理等を行うことが提案されている。この場合、読み出しあドレスが書き込み中のアドレスを追い越さないような制御が行われる。また、画像データを分割して処理する場合においても、読み出しあドレスが書き込み中のアドレスを追い越さないように制御する技術が提案されている（特許文献1）。

#### 【先行技術文献】

#### 【特許文献】

10

20

30

40

50

**【0003】**

【特許文献1】特開2008-117135号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

しかしながら、従来の技術においては、メモリに対する書き込みのブロックと読み出しのブロックのサイズや数が異なる場合に、メモリに対する追いかけ制御を的確に行い得ない場合もあった。

**【0005】**

本発明の目的は、メモリに対する追いかけ制御を的確に行い得るメモリ制御装置及びメモリ制御方法を提供することにある。 10

**【課題を解決するための手段】****【0006】**

実施形態の一観点によれば、メモリに対する書き込み要求を出力し、前記書き込み要求が許可されたことに応じて画像データを前記メモリへ書き込み、1つの第1のブロックの書き込み動作が完了する毎に第1のイベントを発行する、書き込み手段と、前記書き込み手段によって前記メモリに書き込まれた画像データの読み出し要求を出力し、前記読み出し要求が許可されたことに応じて前記メモリから前記画像データを読み出し、1フレームの画像データが前記書き込み手段により前記メモリに書き込まれている間に、前記メモリに書き込まれた前記1フレームの画像データの読み出し要求を出力し、1つの第2のブロックの読み出し動作が完了する毎に第2のイベントを発行する、読み出し手段と、前記書き込み要求及び前記読み出し要求をそれぞれ許可するか否かを制御する制御手段とを有し、前記書き込み手段により前記メモリに書き込まれる画像データの1フレームに複数の前記第1のブロックが含まれ、前記読み出し手段により前記メモリから読み出される画像データの1フレームに、前記第2のブロックが含まれ、前記制御手段は、前記第1のイベントに応じて前記1フレームに含まれる前記第2のブロックの水平方向の数に基づく第1の値だけカウント値を増加させる処理を行い、前記第2のイベントに応じて前記1フレームに含まれる前記第1のブロックの水平方向の数に基づく第2の値だけカウント値を低減させる処理を行い、前記カウント値が第1閾値より大きい場合に前記書き込み要求を許可せず、前記カウント値が前記第1閾値より小さい第2閾値より小さい場合に前記読み出し要求を許可しないことを特徴とするメモリ制御装置が提供される。 20

**【発明の効果】****【0007】**

本発明によれば、メモリに対する追いかけ制御を的確に行い得るメモリ制御装置及びメモリ制御方法を提供することができる。 30

**【図面の簡単な説明】****【0008】**

【図1】第1実施形態によるメモリ制御装置を含む撮像装置の構成を示すブロック図である。

【図2】第1実施形態によるメモリ制御装置の構成を示すブロック図である。 40

【図3】書き込みアクセスや読み出しアクセスにおける走査の順序を概念的に示す図である。

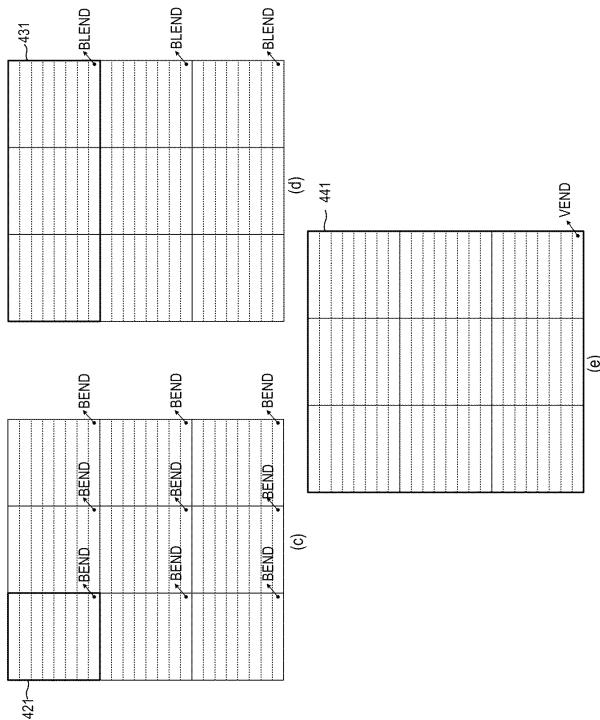

【図4-1】各イベントを示す図である。

【図4-2】各イベントを示す図である。

【図5】メモリアクセス制御部の構成を示す図である。

【図6-1】ブロック分割の例を概念的に示す図である。

【図6-2】ブロック分割の例を概念的に示す図である。

【図6-3】ブロック分割の例を概念的に示す図である。

【図7-1】メモリアクセス制御部の内部の状態を示すタイムチャートである。

【図7-2】メモリアクセス制御部の内部の状態を示すタイムチャートである。 50

【図7-3】メモリアクセス制御部の内部の状態を示すタイムチャートである。

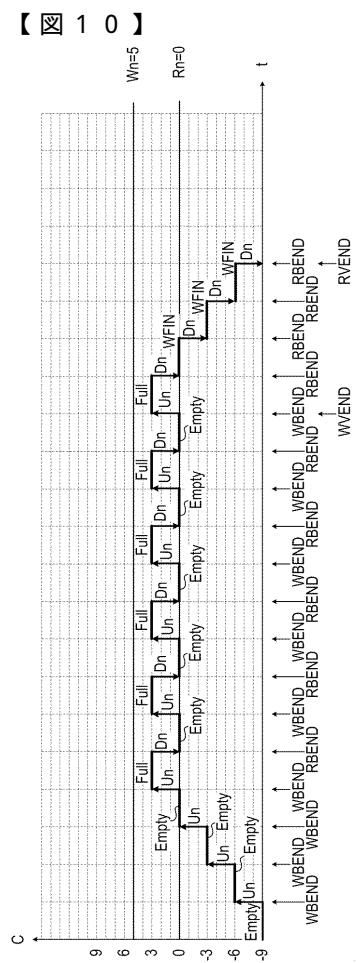

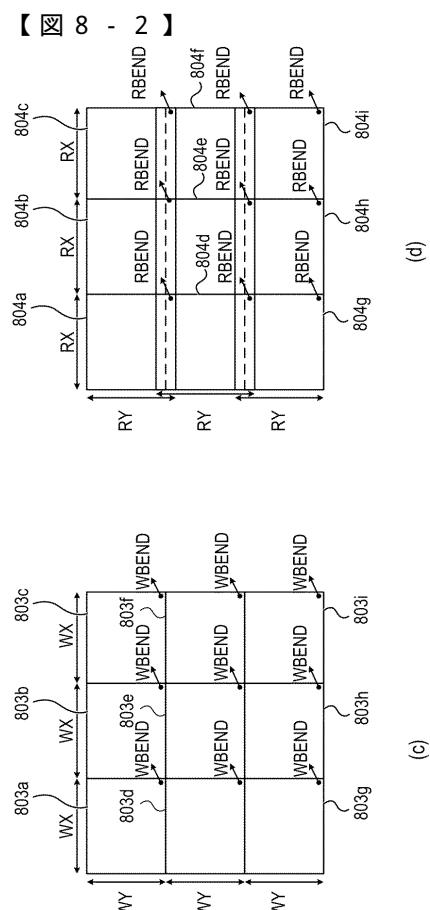

【図8-1】ブロック分割の例を概念的に示す図である。

【図8-2】ブロック分割の例を概念的に示す図である。

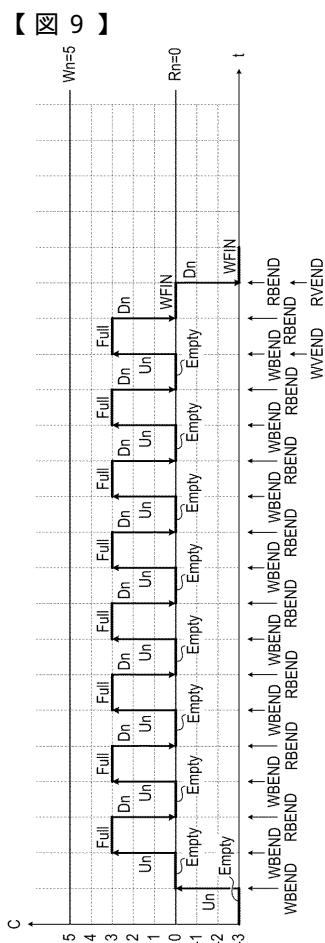

【図9】メモリアクセス制御部の内部の状態を示すタイムチャートである。

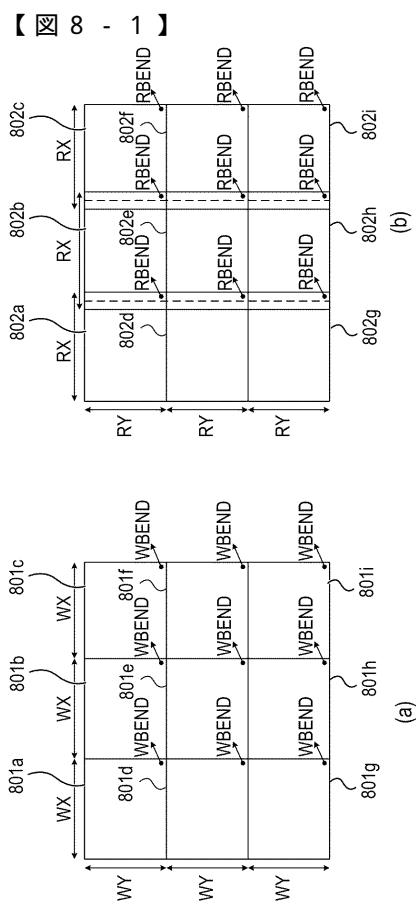

【図10】メモリアクセス制御部の内部の状態を示すタイムチャートである。

【図11】ブロック分割とフレームの例を概念的に示す図である。

【図12】書き込み処理及び読み出し処理を示すタイムチャートである。

【発明を実施するための形態】

【0009】

以下に、本発明の好ましい実施形態を、添付の図面に基づいて詳細に説明する。なお、

本発明は以下の実施形態に限定されるものではなく、その要旨を逸脱しない範囲において

適宜変更可能である。また、以下で説明する図面において、同じ機能を有するものは同一

の符号を付し、その説明を省略又は簡潔にすることもある。

【0010】

[第1実施形態]

本発明の第1実施形態によるメモリ制御装置及びメモリ制御方法について図面を用いて

説明する。

本実施形態によるメモリ制御装置は、例えば撮像装置に組み込まれているが、これに限

定されるものではない。図1は、本実施形態によるメモリ制御装置を含む撮像装置100

の構成を示すブロック図である。撮像部101は、不図示の光学レンズ、絞り等を通して

した光学像を電気信号に変換することによって、画像(画像データ、画像信号)を生成する。

本実施形態では、撮像部101は、1フレームが水平1920画素×垂直1080画素

、60フレーム枚秒(fps)の動画データを出力する。評価値取得部102は、撮像部

101によって取得された画像について、領域毎のヒストグラムや積算値を求める。評価

値取得部102によって取得された評価値は、撮像装置(カメラ)100における露出制

御やホワイトバランス制御等に用いられる。信号処理部103は、撮像部101によって

取得された画像に対して、ノイズ除去処理、ガンマ補正処理、補間処理、マトリクス変換

処理等の各種画像処理を施す。変倍処理部104は、信号処理部103によって処理が施

された画像(画像データ)の解像度(画素数)を、表示用の解像度や記録用の解像度に変

換する処理、即ち、変倍処理を行う。圧縮処理部105は、画像データを記録用のデータ

に圧縮する処理、即ち、圧縮処理を行う。表示部(表示手段、モニタ)106としては、

例えば液晶パネル等が用いられる。表示制御部107は、表示用の画像データを表示部1

06に表示するための制御を行う。記録媒体108は、圧縮された画像データ等を格納す

るためのものであり、例えばメモリカード等である。記録媒体制御部109は、記録媒体

108へのデータの書き込みや読み出しの制御を行う。

【0011】

メモリ制御部110、即ち、本実施形態によるメモリ制御装置は、撮像部101、評価

値取得部102、信号処理部103、変倍処理部104、圧縮処理部105、表示制御部

107、又は、記録媒体制御部109との間でデータを入出力する。メモリ制御部110

は、これらのデータのメモリ111への書き込みや読み出しの制御を行う。メモリ111

は、撮像部101によって取得された画像や、表示用の画像等を一時的に格納する記憶手

段であり、例えば、DRAM(Dynamic Random Access Memory)等である。前述のよう

に、評価値取得部102は、1フレームを複数の領域に分け、領域毎に評価値を取得す

る。また、信号処理部103、変倍処理部104は、水平、垂直方向にそれぞれ複数の画

素に対してフィルタ処理を行うため、垂直方向の複数ラインの画像を記憶するため

のメモリを持つ。メモリの容量を少なくするため、信号処理部103は、1画面の水平

1ラインを複数の領域に分割し、更に、垂直方向にも複数の領域に分割して処理を行

う。このように、評価値取得部102、或いは、信号処理部103はそれぞれ、1フレーム

を複数の領域(ブロック)に分割し、ブロックを単位としてメモリ111にアクセスす

ることになる。そのため、本実施形態では、1フレームを複数のブロックに

10

20

30

40

50

分割し、ブロックを単位としてメモリ111に対するデータの書き込み、読み出しを制御する。更に、本実施形態では、処理による遅延を少なくするため、ブロックを単位として、データの書き込みが完了したブロックのデータを読み出す、追いかけ制御を行う。

#### 【0012】

図2は、本実施形態によるメモリ制御装置の構成を示すブロック図である。書き込み制御部(アクセス手段)201は、メモリ111への書き込みアクセスに関する制御を行うものである。書き込み制御部201は、複数の分割ブロックへの書き込み処理を所定の順序で行う。書き込み制御部201は、画像データ等の書き込みデータW DATAを信号処理部103や変倍処理部104等から受け取ると、書き込みアクセスのリクエストを行うための書き込みリクエスト信号WREQを、メモリアクセス制御部202に対して出力する。書き込み制御部201は、分割ブロック毎の書き込み処理に対応し得るものであり、書き込み処理用の分割ブロックのサイズや、書き込み処理用の分割ブロックに対応するメモリアドレスの管理を行い得る。なお、分割ブロックについては、後に詳述することとする。書き込み制御部201は、所定のブロックの分の書き込み処理がメモリ111に対して完了する毎に、各種のイベントW\*ENDをメモリアクセス制御部202に出力する。なお、これらのイベントW\*ENDについては、後に詳述することとする。メモリIF(Memory Interface)204は、書き込みリクエスト信号WREQに対する受付信号WACKを書き込み制御部201に出力する。書き込み制御部201は、書き込みアドレスWADRSや書き込みデータW DATAをメモリIF204に出力する。書き込み制御部201は、書き込み処理が完了した際、具体的には、例えば1フレーム分の書き込み処理が完了した際に、書き込み処理完了信号WFINをHighレベルにする。なお、ここでは、1フレーム分の書き込み処理が完了した際に書き込み処理完了信号WFINをHighレベルにする場合を例に説明するが、これに限定されるものではない。例えば、複数フレーム分の書き込み処理が完了した際に、書き込み処理完了信号WFINをHighレベルにするようにしてもよい。

#### 【0013】

読み出し制御部(アクセス手段)203は、読み出しアクセスに関する制御を行うものである。読み出し制御部203は、複数の分割ブロックからの読み出し処理を所定の順序で行う。読み出し制御部203内に設けられた不図示の画像バッファ(バッファメモリ)に空き容量が存在しており、かつ、読み出し処理が完了していない場合には、読み出し制御部203は、以下のようないくつかの処理を行う。即ち、読み出し制御部203は、読み出しアクセスのリクエストを行うための読み出しリクエスト信号RREQを、メモリアクセス制御部202に対して出力する。読み出し制御部203は、分割ブロック毎の読み出し処理に対応し得るものであり、読み出し処理用の分割ブロックのサイズや、読み出し処理用の分割ブロックに対応するメモリアドレスの管理を行い得る。読み出し制御部203は、所定のブロックの読み出し処理がメモリ111に対して完了する毎に、メモリアクセス制御部202に対して各種のイベントR\*ENDを出力する。なお、これらのイベントR\*ENDについては、後に詳述することとする。メモリIF204は、読み出しリクエスト信号RREQに対する受付信号RACKを読み出し制御部203に出力する。読み出し制御部203は、読み出しアドレスRADRSをメモリIF204に出力する。メモリIF204は、読み出しデータRDATAを読み出し制御部203に出力する。読み出し制御部203は、読み出した画像データ等の読み出しデータRDAT Aを、信号処理部103や変倍処理部104等に出力する。読み出し制御部203は、読み出し処理が完了した際、具体的には、例えば1フレーム分の読み出し処理が完了した際に、読み出し処理完了信号RFINをHighレベルにする。なお、ここでは、1フレーム分の読み出し処理が完了した際に読み出し処理完了信号RFINをHighレベルにする場合を例に説明するが、これに限定されるものではない。例えば、複数フレーム分の読み出し処理が完了した際に、読み出し処理完了信号RFINをHighレベルにするようにしてもよい。

#### 【0014】

メモリアクセス制御部(メモリアクセス制御手段)202は、分割ブロックへのデータ

10

20

30

40

50

の書き込みが完了し次第、当該分割ブロックからのデータ読み出しを行う制御である追いかけ制御を行う。上述したように、書き込み制御部 201 からメモリアクセス制御部 202 へは、書き込みリクエスト信号 WREQ と、イベント（走査イベント） W\*END と、書き込み処理完了信号 WFIN とが入力されるようになっている。また、読み出し制御部 203 からメモリアクセス制御部 202 へは、読み出しリクエスト信号 RRREQ と、イベント（走査イベント） R\*END と、読み出し処理完了信号 RFIN とが入力されるようになっている。メモリアクセス制御部 202 は、これらの入力に基づいて、追いかけ制御を行う。即ち、データの書き込みが完了していないメモリアドレスからの読み出しが行われないように、メモリアクセス制御部 202 は、読み出しリクエスト信号 MRRREQ を適宜マスクする。また、データの読み出しが可能なメモリアドレスからの読み出しが完了した後に、データの書き込みの処理に移行するように、メモリアクセス制御部 202 は、メモリ IF204 に対して出力する書き込みリクエスト信号 MWREQ を適宜マスクする。メモリアクセス制御部 202 は、これら書き込みリクエスト信号 MWREQ や読み出しリクエスト信号 MRRREQ を適宜マスクすることによって、追いかけ制御を的確に行う。なお、追いかけ制御については、後に詳述することとする。メモリ IF204 は、メモリアクセス制御部 202 からの書き込みリクエスト信号 MWREQ や読み出しリクエスト信号 MRRREQ に従って、メモリ 111 への書き込みアクセスや読み出しみアクセスを行う。

#### 【0015】

図 3 は、書き込みアクセスや読み出しみアクセスにおける走査の順序を概念的に示す図である。図 3 は、画像に対応する仮想的なアドレス空間（アドレス領域）を概念的に示している。図 3 に示すように、1 フレーム分のアドレス領域を複数に分割することによって分割ブロック 301a ~ 301i が画定されている。ここでは、1 フレーム分のアドレス領域を水平方向及び垂直方向にそれぞれ 3 分割し、分割によって画定された矩形の分割ブロック 301a ~ 301i を書き込み処理や読み出し処理の単位として追いかけ制御を行う場合を例に説明する。なお、本明細書においては、個々の分割ブロックについて説明する際には、符号 301a ~ 301i を用い、分割ブロック一般について説明する際には、符号 301 を用いることとする。1 フレーム分の画像の水平方向におけるサイズ（画素数）は X であり、1 フレーム分の画像の垂直方向における画素数は Y である。分割ブロック 301 は、1 フレーム分の画像を水平方向及び垂直方向にそれぞれ 3 分割したものであるため、分割ブロック 301 の水平方向における画素数は X であり、分割ブロック 301 の垂直方向における画素数は Y である。図 3 における左側から右側に向かう方向は X 方向であり、図 3 における上側から下側に向かう方向は Y 方向とする。図 3 における矢印は、書き込みアクセスや読み出しみアクセスにおける走査方向を示している。図 3 における破線は、走査座標のジャンプを示している。

#### 【0016】

上述したように、本実施形態では、分割ブロック 301 を書き込み処理や読み出し処理における単位として追いかけ制御が行われる。具体的には、例えば、図 3 の左上に位置する分割ブロック 301a に対してアクセスが行われる。分割ブロック 301a に対してのアクセスが完了した後には、分割ブロック 301a の右側に位置する分割ブロック 301b に対してのアクセスが行われる。分割ブロック 301b に対してのアクセスが完了した後には、分割ブロック 301b の右側に位置する分割ブロック 301c に対してのアクセスが行われる。このように、第 1 番目のブロック行に位置する分割ブロック 301a ~ 301c に対してのアクセスが左側から右側へ順次行われる。第 1 番目のブロック行に位置する分割ブロック 301a ~ 301c に対してのアクセスが完了した後には、第 2 番目のブロック行に位置する分割ブロック 301d ~ 301f に対してのアクセスが左側から右側へ順次行われる。第 2 番目のブロック行に位置する分割ブロック 301d ~ 301f に対してのアクセスが完了した後には、第 3 番目のブロック行に位置する分割ブロック 301g ~ 301i に対してのアクセスが左側から右側へ順次行われる。こうして、全ての分割ブロック 301a ~ 301i に対してのアクセスが順次行われる。

#### 【0017】

10

20

30

40

50

書き込みアクセスや読み出しアクセスにおける走査をより具体的に以下に説明する。まず、分割ブロック 301a の第 1 番目の行に対する走査が行われる。分割ブロック 301a の第 1 番目の行の先頭の座標は (1, 1) であり、分割ブロック 301a の第 1 番目の行の末尾の座標は (X, 1) である。分割ブロック 301a の第 1 番目の行に対する走査においては、走査座標が (1, 1) から (X, 1) まで順次変化する。分割ブロック 301a の第 1 番目の行に対する走査が完了した後には、分割ブロック 301a の第 2 番目の行に対する走査が行われる。分割ブロック 301a の第 2 番目の行の先頭の座標は、(1, 2) である。従って、分割ブロック 301a の第 1 番目の行に対する走査から分割ブロック 301a の第 2 番目の行に対する走査に移行する際には、走査座標が (X, 1) から (1, 2) にジャンプする。この後、同様にして、走査座標を順次ジャンプさせつつ、分割ブロック 301 内に位置する各々の行に対する走査が順次行われる。

#### 【0018】

分割ブロック 301a に対してのアクセスが完了した後には、上述したように、当該分割ブロック 301a の右側に位置する分割ブロック 301b に対してのアクセスが行われる。分割ブロック 301a の最終行である第 Y 番目の行の末尾の座標は、(X, Y) である。一方、分割ブロック 301b の第 1 番目の行の先頭の座標は、(X + 1, 1) である。従って、分割ブロック 301a に対してのアクセスから分割ブロック 301b に対してのアクセスに移行する際には、走査座標が (X, Y) から (X + 1, 1) にジャンプする。この後、同様にして、分割ブロック 301b 内に位置する各々の行に対する走査が順次行われる。

#### 【0019】

分割ブロック 301b に対してのアクセスが完了した後には、上述したように、当該分割ブロック 301b の右側に位置する分割ブロック 301c に対してのアクセスが行われる。分割ブロック 301b の最終行である第 Y 番目の行の末尾の座標は、(2X, Y) である。一方、分割ブロック 301c の第 1 番目の行の先頭の座標は、(2X + 1, 1) である。従って、分割ブロック 301b に対してのアクセスから分割ブロック 301c に対してのアクセスに移行する際には、走査座標は、(2X, Y) から (2X + 1, 1) にジャンプする。この後、同様にして、分割ブロック 301c 内に位置する各々の行に対する走査が順次行われる。

#### 【0020】

第 1 段目のブロック行に位置する分割ブロック 301a ~ 301c に対しての走査が完了した後には、上述したように、第 2 段目のブロック行に位置する分割ブロック 301d ~ 301f に対しての走査が順次行われる。分割ブロック 301c の最終行である第 Y 番目の行の末尾の座標は、(3X, Y) である。一方、分割ブロック 301d の第 1 番目の行の先頭の座標は、(1, Y + 1) である。従って、分割ブロック 301c に対する走査から分割ブロック 301d に対する走査に移行する際には、走査座標は (3X, Y) から (1, Y + 1) にジャンプする。第 2 段目のブロック行に位置する分割ブロック 301d ~ 301f に対してのアクセスが完了した後には、上述したように、第 3 段目のブロック行に位置する分割ブロック 301g ~ 301i に対してのアクセスが順次行われる。分割ブロック 301f の最終行である第 Y 番目の行の末尾の座標は、(3X, 2Y) である。一方、分割ブロック 301g の第 1 番目の行の先頭の座標は、(1, 2Y + 1) である。従って、分割ブロック 301f に対する走査から分割ブロック 301g に対する走査に移行する際には、走査座標が (3X, 2Y) から (1, 2Y + 1) にジャンプする。こうして、分割ブロック 301i の最終行である第 Y 番目の行の末尾の座標 (3X, 3Y) までの走査が行われる。こうして、1 フレーム分の画像についての走査が完了する。

#### 【0021】

なお、ここでは、上記のような順番で各々の分割ブロック 301a ~ 301i に対してのアクセスを行う場合を例に説明したが、これに限定されるものではない。例えば、分割ブロック 301a に対してのアクセスが完了した後に、分割ブロック 301d に対してのアクセスを行い、この後、分割ブロック 301g に対してのアクセスを行うようにしても

10

20

30

40

50

よい。そして、分割ブロック 301b、分割ブロック 301e、分割ブロック 301h に対してのアクセスを順次行い、この後、分割ブロック 301c、分割ブロック 301f、分割ブロック 301i に対してのアクセスを順次行うようにしてもよい。

#### 【0022】

次に、イベント W\*END、R\*END について、図 4 を用いて説明する。図 4 は、各イベントを示す図である。図 4 (a) は、最小アクセス単位と、最小アクセス単位アクセス完了イベントとを示している。最小アクセス単位 401 のサイズは、例えば、1 ワードのサイズ、又は、1 バースト長のサイズに対応している。最小アクセス単位アクセス完了イベント WEND は、アクセスアドレスが各々の最小アクセス単位 401 の最終アドレスに達した際にそれぞれ発行される。なお、本明細書においては、最小アクセス単位アクセス完了イベントについての一般的な説明の際には符号 WEND を用いることとする。一方、具体的な書き込み処理における最小アクセス単位アクセス完了イベントについての説明の際には、符号 WWEND (図 5 参照) を用いる。また、具体的な読み出し処理における最小アクセス単位アクセス完了イベントについての説明の際には、符号 RWEND (図 5 参照) を用いることとする。10

#### 【0023】

図 4 (b) は、行と、行アクセス完了イベントとを示す図である。1 つの行 411 には、複数の最小アクセス単位 401 が含まれている。行アクセス完了イベント LEND は、アクセスアドレスが各々の行 411 の最終アドレスに達した際にそれぞれ発行される。なお、本明細書においては、行アクセス完了イベントについての一般的な説明の際には符号 LEND を用いる。一方、具体的な書き込み処理における行アクセス完了イベントの説明の際には符号 WLEND (図 5 参照) を用い、具体的な読み出し処理における行アクセス完了イベントの説明の際には符号 RLEND (図 5 参照) を用いることとする。20

#### 【0024】

図 4 (c) は、分割ブロックと、分割ブロックアクセス完了イベントとを示す図である。1 つの分割ブロック 421 には、複数の行 411 が含まれている。分割ブロックアクセス完了イベント BEND は、アクセスアドレスが各々の分割ブロック 421 の最終アドレスに達した際にそれぞれ発行される。なお、本明細書においては、分割ブロックアクセス完了イベントについての一般的な説明の際には符号 BEND を用いることとする。一方、具体的な書き込み処理における分割ブロックアクセス完了イベントの説明の際には符号 WBEND (図 5 参照) を用い、具体的な読み出し処理における分割ブロックアクセス完了イベントの説明の際には符号 RBEND (図 5 参照) を用いることとする。30

#### 【0025】

図 4 (d) は、ブロック行と、ブロック行アクセス完了イベントとを示す図である。1 つのブロック行 431 には、複数の分割ブロック 421 が含まれている。ブロック行アクセス完了イベント BLND は、アクセスアドレスがブロック行 431 の最終アドレスに達した際にそれぞれ発行される。なお、本明細書においては、ブロック行アクセス完了イベントについての一般的な説明の際には符号 BLND を用いることとする。一方、具体的な書き込み処理におけるブロック行アクセス完了イベントの説明の際には符号 WBLEND (図 5 参照) を用い、具体的な読み出し処理におけるブロック行アクセス完了イベントの説明の際には符号 RBLEND (図 5 参照) を用いることとする。40

#### 【0026】

図 4 (e) は、フレームと、フレームアクセス完了イベントとを示す図である。1 つのフレーム 441 には、複数のブロック行 431 が含まれている。フレームアクセス完了イベント VEND は、アクセスアドレスがフレーム 441 の最終アドレスに達した際に発行される。なお、本明細書においては、フレームアクセス完了イベントについての一般的な説明の際には、符号 VEND を用いることとする。一方、具体的な書き込み処理におけるフレームアクセス完了イベントの説明の際には符号 WVEND を用い、具体的な読み出し処理におけるフレームアクセス完了イベントの説明の際には符号 RVEND を用いることとする。50

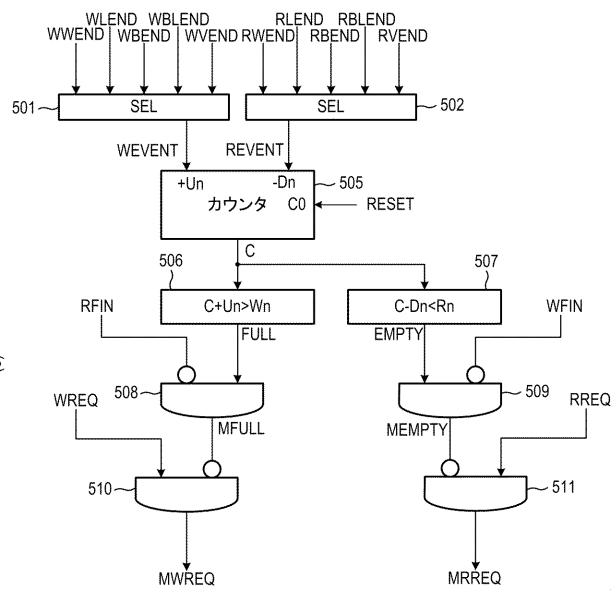

**【 0 0 2 7 】**

図5は、メモリアクセス制御部202の構成を示す図である。セレクタ501には、書き込み制御部201から出力されるイベントWWEND、WLEND、WBEND、WBLEND、WVENDが入力される。セレクタ501は、例えばパラメータ設定に基づいて選択を行う。セレクタ501に入力されるこれらのイベントのうちの1つがセレクタ501によって選択され、選択されたイベントが発行される毎にセレクタ501は書き込みイベントWEVENTを出力する。分割ブロック421を単位として追いかけ制御を行う場合には、例えば、分割ブロック421に対しての書き込みアクセスが完了する毎に発せられる分割ブロックアクセス完了イベントWBENDがセレクタ501によって選択される。

10

**【 0 0 2 8 】**

セレクタ502には、読み出し制御部203から出力されるイベントRWEND、RLEND、RBEND、RBLEND、RVENDが入力される。セレクタ502は、例えばパラメータ設定に基づいて選択を行う。セレクタ502に入力されるこれらのイベントのうちの1つがセレクタ502によって選択され、選択されたイベントが発行される毎にセレクタ502は読み出しイベントREVENTを出力する。分割ブロック421を単位として追いかけ制御を行う場合には、例えば、分割ブロック421に対しての読み出しあクセスが完了する毎に発せられる分割ブロックアクセス完了イベントRBENDがセレクタ502によって選択される。

20

**【 0 0 2 9 】**

アップダウンカウンタ505のカウントアップ端子+Unには、セレクタ501から出力される書き込みイベントWEVENTが入力される。アップダウンカウンタ505のカウントダウン端子-Dnには、セレクタ502から出力される読み出しイベントREVENTが入力される。アップダウンカウンタ505のリセット端子Coには、リセット信号が入力されるようになっている。書き込みイベントWEVENTがアップダウンカウンタ505に入力されると、アップダウンカウンタ505はカウントアップ値Unだけカウントアップする。また、読み出しイベントREVENTがアップダウンカウンタ505に入力されると、アップダウンカウンタ505はカウントダウン値Dnだけカウントダウンする。アップダウンカウンタ505は、カウント値Cを出力する。アップダウンカウンタ505にリセット信号が入力されると、アップダウンカウンタ505はカウント値Cを初期値Coに初期化する。

30

**【 0 0 3 0 】**

比較器(比較手段)506は、カウント値Cとカウントアップ値Unとを加算することにより得られる値(C+Un)が閾値Wnより大きいか否かを判定する。即ち、比較器506は、カウント値Cと閾値Wnとに基づいて比較を行う。ここで、閾値Wnは、メモリ111に備えられた画像バッファの容量に応じた値である。比較の結果、加算値(C+Un)が閾値Wnよりも大きい場合には、メモリ111に備えられた画像バッファがFULLの状態であると判定し、メモリ111に対するこれ以上の書き込みアクセスを禁止する。

40

**【 0 0 3 1 】**

マスク論理(マスク機能、マスク論理回路、マスク手段)508は、読み出し処理の完了を示す読み出し処理完了信号RFINによって比較器506から出力される信号FULLをマスクするものであり、信号MFULLを出力する。マスク論理508は、読み出し処理が完了した場合、即ち、読み出し処理完了信号RFINがHighレベルの際には、比較器506から出力される信号FULLをマスク(無効化)する。マスク論理510は、書き込み制御部201から出力される書き込みリクエスト信号WREQをマスク論理508から出力される信号MFULLに応じてマスクするものであり、書き込みリクエスト信号MWREQを出力する。マスク論理510は、メモリ111に備えられた画像バッファがFULLの状態である場合には、書き込み制御部201から出力される書き込みリクエスト信号WREQをマスクする。マスク論理510は、書き込みリクエスト信号MWREQをマスクする。

50

E Qをメモリ I F 2 0 4に出力する。このように、マスク論理 5 0 8 , 5 1 0は、比較器 5 0 6による比較の結果に基づいて書き込み制御部 2 0 1によるメモリ 1 1 1へ書き込み処理のリクエスト(要求)をマスクする。

#### 【0032】

比較器 5 0 7は、カウント値 C からカウントダウン値 - D n を減算することによって得られる値 ( C - D n ) が閾値 R n より小さいか否かを判定する。即ち、比較器 5 0 7は、カウント値 C と閾値 R n とに基づいて比較を行う。ここで、閾値 R n は、メモリ 1 1 1に備えられた画像バッファの容量に応じた値である。比較の結果、減算値 ( C - D n ) が閾値 R n より小さい場合には、メモリ 1 1 1に備えられた画像バッファが E M P T Y であると判定し、メモリ 1 1 1に対するこれ以上の読み出しアクセスを禁止する。

10

#### 【0033】

マスク論理 5 0 9は、書き込み処理の完了を示す書き込み処理完了信号 W F I N によって、比較器 5 0 7から出力される信号 E M P T Y をマスクするものであり、信号 M E M P T Y を出力する。マスク論理 5 0 9は、書き込み処理完了信号 W F I N が H i g h レベルの際には、比較器 5 0 7から出力される信号 E M P T Y を無効化する。マスク論理 5 1 1は、読み出し制御部 2 0 3から出力される読み出しリクエスト信号 R R E Q をマスク論理 5 0 9から出力される信号 M E M P T Y によってマスクするものであり、読み出しリクエスト信号 M R R E Q を出力する。マスク論理 5 1 1は、メモリ 1 1 1に備えられた画像バッファが E M P T Y の状態である場合には、読み出し制御部 2 0 3から出力される読み出しリクエスト信号 R R E Q をマスクする。マスク論理 5 1 1は、読み出しリクエスト信号 M R R E Q をメモリ I F 2 0 4に出力する。このように、マスク論理 5 0 9 , 5 1 1は、比較器 5 0 7による比較の結果に基づいて読み出し制御部 2 0 3によるメモリ 1 1 1へ読み出し処理のリクエストをマスクする。

20

#### 【0034】

このように、メモリアクセス制御部 2 0 2は、書き込み制御部 2 0 1から発せられるイベント W \* E N D 、又は、読み出し制御部 2 0 3から発せられるイベント R \* E N D に基づいてカウント値 C を増減させる。また、メモリアクセス制御部 2 0 2は、書き込み制御部 2 0 1から発せられるイベント W \* E N D と読み出し制御部 2 0 3から発せられるイベント R \* E N D のそれぞれに応じた増減値でカウント値 C を増減させる。そして、メモリアクセス制御部 2 0 2は、書き込み制御部 2 0 1によるメモリ 1 1 1へのアクセス(書き込み)と読み出し制御部 2 0 3によるメモリ 1 1 1へのアクセス(読み出し)とのうちのいずれかを、カウント値 C に基づいて選択的に許可する。

30

#### 【0035】

次に、各パラメータについて説明する。ここでは、分割ブロック 4 2 1(図 4(c)参照)へのアクセスが完了する毎に発せられる分割ブロックアクセス完了イベント B E N D (W B E N D 、 R B E N D )を用いて、分割ブロックを単位として追いかけ制御を行う場合を例に説明する。

#### 【0036】

メモリアクセス制御部 2 0 2において用いられるパラメータには、初期値 C 0 と、カウントアップ値 U n と、カウントダウン値 D n と、F U L L の閾値 W n と、E M P T Y の閾値 R n とがある。各々のパラメータの値は、例えば以下のような式(1)~(5)によって決定される。

$$U_n = R \times N \quad \dots \quad (1)$$

$$D_n = W \times N \quad \dots \quad (2)$$

$$W_n = R_n + B_u f \quad \dots \quad (3)$$

$$R_n = (W_Y N - R_Y N) \times U_n \times W \times N \quad (\text{ただし、 } R_n < 0 \text{ の場合は } R_n = 0) \quad \dots \\ \dots \quad (4)$$

$$B_u f = (D_n - 1) + U_n \quad \dots \quad (5)$$

ここで、W X N は、書き込み処理用のブロック分割における水平方向の分割数であり、W Y N は、書き込み処理用のブロック分割における垂直方向の分割数である。また、R X

40

50

Nは、読み出し処理用のブロック分割における水平方向の分割数であり、R Y Nは、読み出し処理用のブロック分割における垂直方向の分割数である。

#### 【0037】

初期値C 0は、分割ブロックが互いにオーバラップするように設定される場合には、0以外に設定される。また、書き込み処理用のブロック分割の態様と読み出し処理用のブロック分割の態様とが互いに異なる場合にも、0以外に設定される場合がある。これらの場合を除き、初期値C 0は例えば0に設定される。このように、初期値C 0は、フレームの分割の態様に基づいて設定される。

#### 【0038】

上記のように、増減値U n, D nは、フレームの分割数に基づいて設定される。なお、ここでは、上述したような式に基づいてパラメータの値を設定したが、これに限定されるものではない。

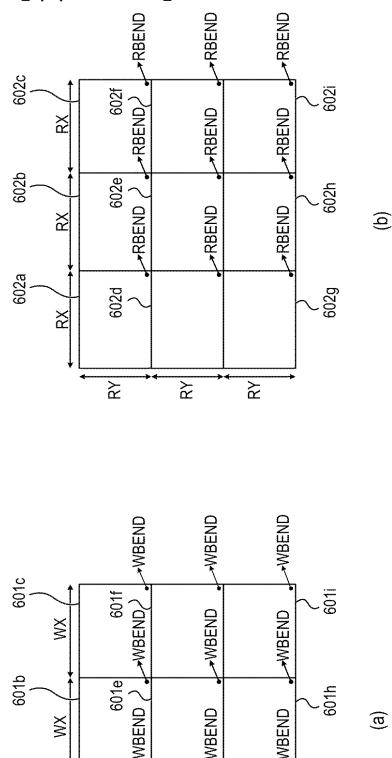

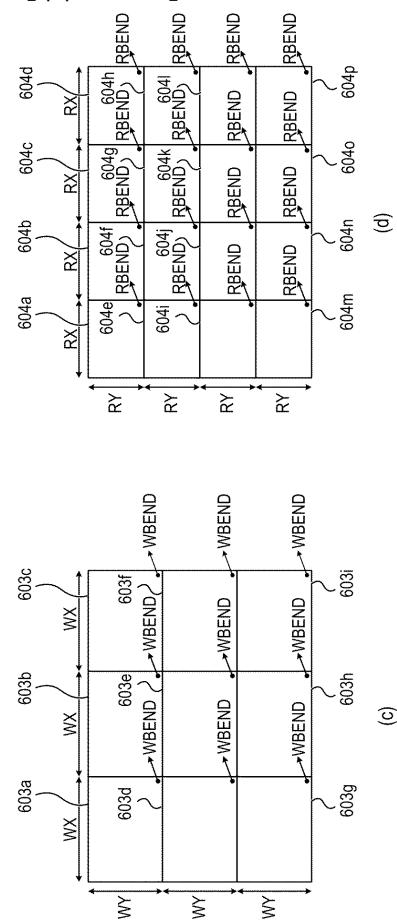

#### 【0039】

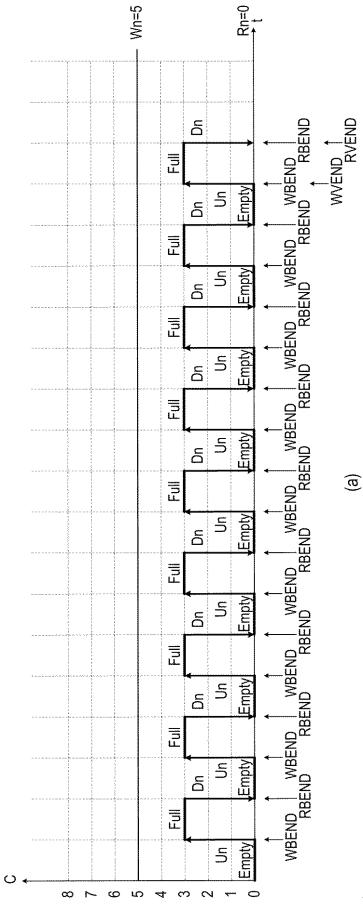

図6は、ブロック分割の例を概念的に示す図である。図6は、1フレーム分の画像に対応する仮想的なアドレス空間を概念的に示している。図6(a)及び図6(b)は、書き込み処理用のブロック分割の態様と読み出し処理用のブロック分割の態様とが互いに等しい例を示している。例えば、図1において、画像の書き込みを行う処理部と読み出しを行う処理部の分割数、ブロックサイズが同じ場合に該当する。図6(a)は、書き込み処理用のブロック分割を示しており、図6(b)は、読み出し処理用のブロック分割を示している。書き込み処理用のブロック分割と読み出し処理用のブロック分割のいずれにおいても、水平方向における分割数W X N, R X Nは3となっており、垂直方向における分割数W Y N, R Y Nは3となっている。書き込み処理用の各々の分割ブロック601a~601iの水平方向におけるサイズ(画素数)W Xと、読み出し処理用の各々の分割ブロック602a~602iの水平方向におけるサイズR Xとは、互いに等しくなっている。また、書き込み処理用の各々の分割ブロック601a~601iの垂直方向におけるサイズW Yと、読み出し処理用の各々の分割ブロック602a~602iの垂直方向におけるサイズR Yとは、互いに等しくなっている。なお、本明細書においては、個々の分割ブロックについて説明する際には、符号601a~601i、602a~602iを用い、分割ブロック一般について説明する際には、符号601、602を用いることとする。図6(a)及び図6(b)に示す例においては、各々のパラメータの値は例えば以下のように設定される。即ち、C 0 = 0、U n = 3、D n = 3、W n = 5、R n = 0、B u f = 5と設定される。

#### 【0040】

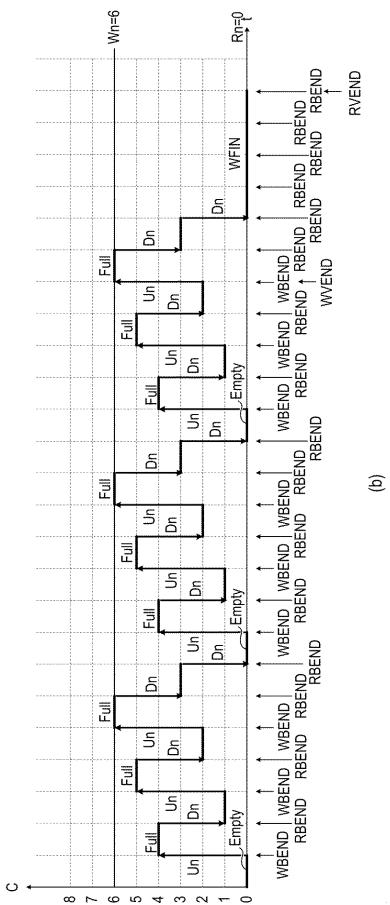

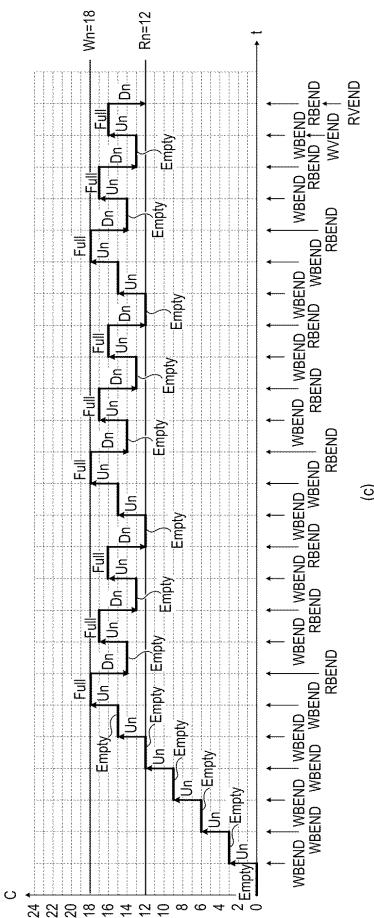

図7(a)は、メモリアクセス制御部202の内部の状態を示すタイムチャートである。図7(a)は、図6(a)及び図6(b)のようにブロック分割した場合に対応している。図7における縦軸はアップダウンカウンタ505から出力されるカウント値Cを示している。図7における横軸は時間軸である。図7における“F u l l”は、比較器506から出力される信号F U L LがH i g hレベルであることを示しており、図7における“E m p t y”は、比較器507から出力される信号E M P T YがH i g hレベルであることを示している。図7におけるW F I Nは、書き込み制御部201から出力される書き込み処理完了信号がH i g hレベルであることを示している。図7において矢印を伴って示されたW B E N D, R B E N D, W V E N D, R V E N Dは、これらのイベントが書き込み制御部201又は読み出し制御部203からメモリアクセス制御部202に出力されるタイミングを示している。

#### 【0041】

まず、初期状態について説明する。初期状態においては、アップダウンカウンタ505におけるカウント値Cは、初期値C 0 = 0に設定されている。C - D n = - 3であり、R n = 0であるため、比較器507における条件式C - D n < R nを満たし、比較器507から出力される信号E M P T YはH i g hレベルである。上述したように、書き込み制御部201から出力される書き込み処理完了信号W F I NがH i g hレベルになるのは、例

10

20

30

40

50

えば 1 フレーム分の書き込み処理が完了した際である。従って、1 フレーム分の書き込み処理が完了するまでは、書き込み処理完了信号 W F I N は L o w レベルのままである。従って、比較器 5 0 7 から出力される信号 E M P T Y が H i g h レベルの場合、マスク論理 5 0 9 から出力される信号 M E M P T Y は H i g h レベルであり、読み出しリクエスト信号 R R E Q がマスク論理 5 1 1 によってマスクされる。この状態においては、読み出し制御部 2 0 3 からメモリアクセス制御部 2 0 2 に読み出しリクエスト信号 R R E Q が出力された場合であっても、メモリアクセス制御部 2 0 2 から出力される読み出しリクエスト信号 M R R E Q は L o w レベルに維持される。即ち、この状態においては、読み出しリクエスト信号 R R E Q が無効化される。このように、信号 E M P T Y が H i g h レベルである場合には、読み出しリクエスト信号 R R E Q は無効化される。また、C + U n = 3 であり、W n = 5 であるため、比較器 5 0 6 における条件式 C + U n > W n を満たさず、比較器 5 0 6 から出力される信号 F U L L は L o w レベルである。マスク論理 5 0 8 から出力される信号 M F U L L は L o w レベルであり、書き込みリクエスト信号 W R E Q はマスク論理 5 1 0 によってマスクされない。この状態においては、書き込み制御部 2 0 1 からメモリアクセス制御部 2 0 2 に出力される書き込みリクエスト信号 W R E Q に応じて、メモリアクセス制御部 2 0 2 からメモリ I F 2 0 4 に書き込みリクエスト信号 M W R E Q が出力される。このように、信号 F U L L が L o w レベルである場合には、書き込みリクエスト信号 W R E Q は有効とされる。書き込みリクエスト信号 W R E Q に応じて、メモリアクセス制御部 2 0 2 からメモリ I F 2 0 4 に書き込みリクエスト信号 M W R E Q が出力されるため、書き込み処理用の分割ブロック 6 0 1 に対応するメモリアドレスへのデータの書き込みが行われる。具体的には、この段階では、書き込み処理用の第 1 番目の分割ブロック 6 0 1 a に対応するメモリアドレスへのデータの書き込みが行われる。

10

#### 【 0 0 4 2 】

上述したように、図 6 ( a ) 及び図 6 ( b ) に示す例においては、書き込み処理用の分割ブロックの分割様態と読み出し処理用の分割ブロックの分割様態とが互いに等しくなっている。このため、書き込み処理用の第 1 番目の分割ブロック 6 0 1 a に対応するメモリアドレスへのデータの書き込みが完了した段階で、読み出し処理用の第 1 番目の分割ブロック 6 0 2 a に対応する全てのメモリアドレスへのデータの書き込みが完了している。従って、書き込み処理用の第 1 番目の分割ブロック 6 0 1 a に対応するメモリアドレスへの書き込みが完了した後には、読み出し処理用の第 1 番目の分割ブロック 6 0 2 a に対応するメモリアドレスからの読み出しを行っても、現在のフレームの画像が書き込まれていないアドレスからの読み出しを行うことがない。従って、書き込み処理用の第 1 番目の分割ブロック 6 0 1 a に対応するメモリアドレスへのデータの書き込みが完了した後には、以下に示すように、読み出し処理用の第 1 番目の分割ブロック 6 0 2 a に対応するメモリアドレスからのデータの読み出しが行われる。

20

#### 【 0 0 4 3 】

即ち、書き込み処理用の第 1 番目の分割ブロック 6 0 1 a に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント W B E N D が出力される。これにより、アップダウンカウンタ 5 0 5 は、U n = 3 だけカウントアップし、カウント値 C = 3 となる。C + U n = 6 であり、W n = 5 であるため、比較器 5 0 6 における条件式 C + U n > W n を満たし、比較器 5 0 6 から出力される信号 F U L L は H i g h レベルである。上述したように、読み出し処理完了信号 R F I N が H i g h レベルとなるのは、例えば 1 フレーム分の読み出し処理が完了した際である。従って、1 フレーム分の読み出し処理が完了するまでは、読み出し処理完了信号 R F I N は L o w レベルのままである。従って、比較器 5 0 6 から出力される信号 F U L L が H i g h レベルの場合、マスク論理 5 0 8 から出力される信号 M F U L L は H i g h レベルであり、書き込みリクエスト信号 W R E Q はマスク論理 5 1 0 によってマスクされる。この状態においては、書き込み制御部 2 0 1 からメモリアクセス制御部 2 0 2 に書き込みリクエスト信号 W R E Q が出力された場合であっても、メモリアクセス制御部 2 0 2 から出力される書き込みリクエスト信号 M W R E Q は L o w レベルに維持される。即ち、この状態においては、書き込み

30

リクエスト信号W R E Qが無効化される。このように、信号F U L LがH i g hレベルである場合には、書き込みリクエスト信号W R E Qは無効化される。また、C - D n = 0であり、R n = 0であるため、比較器5 0 7における条件式C - D n < Rを満たさず、比較器5 0 7から出力される信号E M P T YはL o wレベルである。マスク論理5 0 9から出力される信号M E M P T YはL o wレベルであり、読み出しリクエスト信号R R E Qはマスク論理5 1 1によってマスクされない。この状態においては、読み出し制御部2 0 3からメモリアクセス制御部2 0 2に出力される読み出しリクエスト信号R R E Qに応じて、メモリアクセス制御部2 0 2からメモリI F 2 0 4に読み出しリクエスト信号M R R E Qが出力される。このように、信号E M P T YがL o wレベルである場合には、読み出しリクエスト信号R R E Qは有効とされる。読み出しリクエスト信号R R E Qに応じて、メモリアクセス制御部2 0 2からメモリI F 2 0 4に読み出しリクエスト信号M R R E Qが出力されるため、読み出し用の分割プロック6 0 2に対応するメモリアドレスからのデータの読み出しが行われる。具体的には、読み出し処理用の第1番目の分割プロック6 0 2 aに対応するメモリアドレスからのデータの読み出しが行われる。10

#### 【0 0 4 4】

読み出し処理用の第1番目の分割プロック6 0 2 aに対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第2番目の分割プロック6 0 2 bに対応するメモリアドレスには読み出しの対象となるデータが書き込まれていない。従って、読み出し処理用の第1番目の分割プロック6 0 2 aに対応するメモリアドレスからのデータの読み出しが完了した後には、以下に示すように、書き込み処理用の第2番目の分割プロック6 0 1 bに対応するメモリアドレスへのデータの書き込みが行われる。即ち、読み出し処理用の第1番目の分割プロック6 0 2 aに対応するメモリアドレスからのデータの読み出しが完了すると、分割プロックアクセス完了イベントR B E N Dが発行される。これにより、アップダウンカウンタ5 0 5は、D n = 3だけカウントダウンし、カウント値C = 0となる。C - D n = - 3であり、R n = 0であるため、比較器5 0 7における条件式C - D n < Rを満たし、比較器5 0 7から出力される信号E M P T YはH i g hレベルである。信号E M P T YがH i g hレベルであるため、読み出しリクエスト信号R R E Qは無効化される。また、C + U n = 3であり、W n = 5であるため、比較器5 0 6における条件式C + U n > W nを満たさず、比較器5 0 6から出力される信号F U L LはL o wレベルである。信号F U L LがL o wレベルであるため、書き込みリクエスト信号W R E Qは有効とされる。従って、書き込み処理用の第2番目の分割プロック6 0 1 bに対応するメモリアドレスへのデータの書き込みが行われる。20

#### 【0 0 4 5】

上述したように、図6(a)及び図6(b)に示す例においては、書き込み処理用の分割プロックの分割態様と読み出し処理用の分割プロックの分割態様とが互いに等しくなっている。従って、書き込み処理用の第2番目の分割プロック6 0 1 bに対応するメモリアドレスへの書き込みが完了した後には、読み出し処理用の第2番目の分割プロック6 0 2 bに対応するメモリアドレスからの読み出しを行っても、現在のフレームの画像が書き込まれていないアドレスからの読み出しを行うことはない。従って、書き込み処理用の第2番目の分割プロック6 0 1 bに対応するメモリアドレスへのデータの書き込みが完了した後には、読み出し処理用の第2番目の分割プロック6 0 2 bに対応するメモリアドレスからのデータの読み出しが行われる。30

#### 【0 0 4 6】

この後も、上記と同様にして、追いかけ制御が順次行われる。アップダウンカウンタ5 0 5から出力されるカウント値Cは、図7(a)のように変化する。書き込み処理用の第9番目の分割プロック6 0 1 iに対応するメモリアドレスへのデータの書き込みが完了すると、1フレーム分の書き込み処理が完了したことを示すイベントW V E N Dが発出される。また、1フレーム分の書き込み処理が完了したことを示す書き込み処理完了信号W F I NがH i g hレベルとなる。この後、読み出し処理用の第9番目の分割プロック6 0 2 iに対応するメモリアドレスからのデータの読み出しが完了すると、1フレーム分の読み40

50

出し処理が完了したことを示すイベント R V E N D が出力される。また、1 フレーム分の読み出し処理が完了したことを示す読み出し処理完了信号 R F I N が H i g h レベルとなる。このように、図 6 ( a ) 及び図 6 ( b ) の例においては、書き込み処理用の分割ブロック 6 0 1 に対応するメモリアドレスへのデータの書き込みと読み出し処理用の分割ブロック 6 0 2 に対応するメモリアドレスからのデータの読み出しが交互に順次行われる。このように、本実施形態によれば、追いかけ制御を的確に行うことができる。

#### 【 0 0 4 7 】

図 6 ( c ) 及び図 6 ( d ) は、書き込み処理用のブロック分割の様子と読み出し処理用のブロック分割の様子とが互いに異なる例を示している。例えば、図 1 において、画像の書き込みを行う処理部と読み出しを行う処理部の分割数、ブロックサイズが異なる場合に該当する。図 6 ( c ) は、書き込み処理用のブロック分割を示しており、図 6 ( d ) は、読み出し処理用のブロック分割を示している。書き込み処理用のブロック分割においては、水平方向においても垂直方向においても分割数 W X N , W Y N は 3 となっている。一方、読み出し処理用のブロック分割においては、水平方向においても垂直方向においても分割数 R X N , R Y N は 4 となっている。書き込み処理用の各々の分割ブロック 6 0 3 a ~ 6 0 3 i の水平方向におけるサイズ W X は、読み出し処理用の各々の分割ブロック 6 0 4 a ~ 6 0 4 p の水平方向におけるサイズ R X より大きくなっている。また、書き込み処理用の各々の分割ブロック 6 0 3 a ~ 6 0 3 i の垂直方向におけるサイズ W Y は、読み出し処理用の各々の分割ブロック 6 0 4 a ~ 6 0 4 p の垂直方向におけるサイズ R Y より大きくなっている。なお、本明細書においては、個々の分割ブロックについて説明する際には、符号 6 0 3 a ~ 6 0 3 i 、 6 0 4 a ~ 6 0 4 p を用い、分割ブロック一般について説明する際には、符号 6 0 3 、 6 0 4 を用いることとする。図 6 ( c ) 及び図 6 ( d ) に示す例においては、各々のパラメータの値は例えば以下のように設定される。即ち、 C 0 = 0 、 U n = 4 、 D n = 3 、 W n = 6 、 R n = 0 、 B u f = 6 と設定される。図 7 ( b ) は、メモリアクセス制御部 2 0 2 の内部の状態を示すタイムチャートである。図 7 ( b ) は、図 6 ( c ) 及び図 6 ( d ) のようにブロック分割した場合に対応している。

#### 【 0 0 4 8 】

まず、初期状態について説明する。初期状態においては、アップダウンカウンタ 5 0 5 のカウント値は、初期値 C 0 = 0 に設定されている。C - D n = - 3 であり、R n = 0 であるため、比較器 5 0 7 における条件式 C - D n < R n を満たし、比較器 5 0 7 から出力される信号 E M P T Y は H i g h レベルである。信号 E M P T Y が H i g h レベルであるため、読み出しリクエスト信号 R R E Q は無効化される。また、C + U n = 4 であり、W n = 6 であるため、比較器 5 0 6 における条件式 C + U n > W n を満たさず、比較器 5 0 6 から出力される信号 F U L L は L o w レベルである。信号 F U L L が L o w レベルであるため、書き込みリクエスト信号 W R E Q は有効とされる。従って、書き込み処理用の第 1 番目の分割ブロック 6 0 3 a に対応するメモリアドレスへのデータの書き込みが行われる。

#### 【 0 0 4 9 】

上述したように、図 6 ( c ) 及び図 6 ( d ) に示す例においては、読み出し処理用の各々の分割ブロック 6 0 4 のサイズは水平方向においても垂直方向においても、書き込み処理用の各々の分割ブロック 6 0 3 のサイズより小さくなっている。従って、書き込み処理用の第 1 番目の分割ブロック 6 0 3 a に対応するメモリアドレスへの書き込みが完了した後には、読み出し処理用の第 1 番目の分割ブロック 6 0 4 a に対応するメモリアドレスからの読み出しを行っても、現在のフレームの画像が書き込まれていないアドレスからの読み出しを行うことがない。従って、書き込み処理用の第 1 番目の分割ブロック 6 0 3 a に対応するメモリアドレスへのデータの書き込みが完了した後には、以下に示すように、読み出し処理用の第 1 番目の分割ブロック 6 0 4 a に対応するメモリアドレスからのデータの読み出しが行われる。即ち、書き込み処理用の第 1 番目の分割ブロック 6 0 3 a に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント W B E N D が出力される。これにより、アップダウンカウンタ 5 0 5 は、U n = 4 だ

10

20

30

40

50

けカウントアップし、カウント値  $C = 4$  となる。  $C + U_n = 8$  であり、  $W_n = 6$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たし、比較器 506 から出力される信号 FULL は High レベルである。信号 FULL が High レベルであるため、書き込みリクエスト信号 WREQ は無効化される。また、  $C - D_n = 1$  であり、  $R_n = 0$  であるため、比較器 507 における条件式  $C - D_n < R_n$  を満たさず、比較器 507 から出力される信号 EMPTY は Low レベルである。信号 EMPTY が Low レベルであるため、読み出しリクエスト信号 RRREQ は有効とされる。従って、読み出し処理用の第 1 番目の分割ブロック 604a に対応するメモリアドレスからのデータの読み出しが行われる。

#### 【0050】

読み出し処理用の第 1 番目の分割ブロック 604a に対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第 2 番目の分割ブロック 604b に対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。従って、読み出し処理用の第 1 番目の分割ブロック 604a に対応するメモリアドレスからのデータの読み出しが完了した後には、以下に示すように、書き込み処理用の第 2 番目の分割ブロック 603b に対応するメモリアドレスへのデータの書き込みが行われる。即ち、読み出し処理用の第 1 番目の分割ブロック 604a に対応するメモリアドレスからのデータの読み出しが完了すると、分割ブロックアクセス完了イベント REND が出力される。これにより、アップダウンカウンタ 505 は、  $D_n = 3$  だけカウントダウンし、カウント値  $C = 1$  となる。  $C - D_n = -2$  であり、  $R_n = 0$  であるため、比較器 507 における条件式  $C - D_n < R$  を満たし、比較器 507 から出力される信号 EMPTY は High レベルである。信号 EMPTY が High レベルであるため、読み出しリクエスト信号 RRREQ は無効化される。また、  $C + U_n = 5$  であり、  $W_n = 6$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たさず、比較器 506 から出力される信号 FULL は Low レベルである。信号 FULL が Low レベルであるため、書き込みリクエスト信号 WREQ は有効とされる。従って、書き込み処理用の第 2 番目の分割ブロック 603b に対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0051】

上述したように、図 6(c) 及び図 6(d) に示す例においては、読み出し処理用の各々の分割ブロック 604 のサイズは水平方向においても垂直方向においても、書き込み処理用の各々の分割ブロック 603 のサイズより小さくなっている。従って、書き込み処理用の第 2 番目の分割ブロック 603b に対応するメモリアドレスへの書き込みが完了した後には、読み出し処理用の第 2 番目の分割ブロック 604b に対応するメモリアドレスからの読み出しを行っても、現在のフレームの画像が書き込まれていないアドレスからの読み出しを行うことがない。従って、書き込み処理用の第 2 番目の分割ブロック 603b に対応するメモリアドレスへのデータの書き込みが完了した後には、以下に示すように、読み出し処理用の第 2 番目の分割ブロック 604b に対応するメモリアドレスからのデータの読み出しが行われる。即ち、書き込み処理用の第 2 番目の分割ブロック 603b に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント WEND が出力される。これにより、アップダウンカウンタ 505 は、  $U_n = 4$  だけカウントアップし、カウント値  $C = 5$  となる。  $C + U_n = 9$  であり、  $W_n = 6$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たし、比較器 506 から出力される信号 FULL は High レベルである。信号 FULL が High レベルであるため、書き込みリクエスト信号 WREQ は無効化される。また、  $C - D_n = 2$  であり、  $R_n = 0$  であるため、比較器 507 における条件式  $C - D_n < R$  を満たさず、比較器 507 から出力される信号 EMPTY は Low レベルである。信号 EMPTY が Low レベルであるため、読み出しリクエスト信号 RRREQ は有効とされる。従って、読み出し処理用の第 2 番目の分割ブロック 604b に対応するメモリアドレスからのデータの読み出しが行われる。

#### 【0052】

読み出し処理用の第 2 番目の分割ブロック 604b に対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第 3 番目の分割ブロック 604c

10

20

30

40

50

に対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。従って、読み出し処理用の第2番目の分割ブロック604bに対応するメモリアドレスからのデータの読み出しが完了した後には、以下に示すように、書き込み処理用の第3番目の分割ブロック603cに対応するメモリアドレスへのデータの書き込みが行われる。即ち、読み出し処理用の第2番目の分割ブロック604bに対応するメモリアドレスからのデータの読み出しが完了すると、分割ブロックアクセス完了イベントR B E N Dが出力される。これにより、アップダウンカウンタ505は、 $D_n = 3$ だけカウントダウンし、カウント値 $C = 2$ となる。 $C - D_n = -1$ であり、 $R_n = 0$ であるため、比較器507における条件式 $C - D_n < R$ を満たし、比較器507から出力される信号E M P T YはH i g hレベルである。信号E M P T YがH i g hレベルであるため、読み出しリクエスト信号R R E Qは無効化される。また、 $C + U_n = 6$ であり、 $W_n = 6$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たさず、比較器506から出力される信号F U L LはL o wレベルである。信号F U L LがL o wレベルであるため、書き込みリクエスト信号W R E Q是有効とされる。従って、書き込み処理用の第3番目の分割ブロック603cに対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0053】

上述したように、図6(c)及び図6(d)に示す例においては、読み出し処理用の各々の分割ブロック604のサイズは水平方向においても垂直方向においても、書き込み処理用の各々の分割ブロック603のサイズより小さくなっている。従って、書き込み処理用の第3番目の分割ブロック603cに対応するメモリアドレスへの書き込みが完了した後には、読み出し処理用の第3番目の分割ブロック604cに対応するメモリアドレスからの読み出しを行っても、現在のフレームの画像が書き込まれていないアドレスからの読み出しを行うことがない。従って、書き込み処理用の第3番目の分割ブロック603cに対応するメモリアドレスへのデータの書き込みが完了した後には、以下に示すように、読み出し処理用の第3番目の分割ブロック604cに対応するメモリアドレスからのデータの読み出しが行われる。即ち、書き込み処理用の第3番目の分割ブロック603cに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントW B E N Dが出力される。これにより、アップダウンカウンタ505は、 $U_n = 4$ だけカウントアップし、カウント値 $C = 6$ となる。 $C - D_n = 3$ であり、 $R_n = 0$ であるため、比較器507における条件式 $C - D_n < R$ を満たさず、比較器507から出力される信号E M P T YはL o wレベルである。信号E M P T YがL o wレベルであるため、読み出しリクエスト信号R R E Qは有効とされる。また、 $C + U_n = 10$ であり、 $W_n = 6$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たし、比較器506から出力される信号F U L LはH i g hレベルである。信号F U L LがH i g hレベルであるため、書き込みリクエスト信号W R E Qは無効化される。従って、読み出し処理用の第3番目の分割ブロック604cに対応するメモリアドレスからのデータの読み出しが行われる。

#### 【0054】

読み出し処理用の第3番目の分割ブロック604cに対応するメモリアドレスからのデータの読み出しが完了した段階で、読み出し処理用の第4番目の分割ブロック604dに対応するメモリアドレスには、現在のフレームの読み出しの対象となるデータが書き込まれている。従って、読み出し処理用の第3番目の分割ブロック604cに対応するメモリアドレスからの読み出しが完了した後には、以下に示すように、読み出し処理用の第4番目の分割ブロック604dに対応するメモリアドレスからの読み出しが行われる。即ち、読み出し処理用の第3番目の分割ブロック604cに対応するメモリアドレスからのデータの読み出しが完了すると、分割ブロックアクセス完了イベントR B E N Dが出力される。これにより、アップダウンカウンタ505は、 $D_n = 3$ だけカウントダウンし、カウント値 $C = 3$ となる。 $C - D_n = 0$ であり、 $R_n = 0$ であるため、比較器507における条件式 $C - D_n < R$ を満たさず、比較器507から出力される信号E M P T YはL o wレベルである。信号E M P T YがL o wレベルであるため、読み出しリクエスト信号R R E Qは有効とされる。また、 $C + U_n = 7$ であり、 $W_n = 6$ であるため、比較器506における

る条件式  $C + U_n > W_n$  を満たし、比較器 506 から出力される信号 FULL は High レベルである。信号 FULL が High レベルであるため、書き込みリクエスト信号 WREQ は無効化される。従って、読み出し処理用の第 4 番目の分割ブロック 604d に対応するメモリアドレスからのデータの読み出しが行われる。

#### 【0055】

読み出し処理用の第 4 番目の分割ブロック 604d に対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第 5 番目の分割ブロック 604e に対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。従って、読み出し処理用の第 4 番目の分割ブロック 604d に対応するメモリアドレスからのデータの読み出しが完了した後には、以下に示すように、書き込み処理用の第 4 番目の分割ブロック 603d に対応するメモリアドレスへのデータの書き込みが行われる。即ち、読み出し処理用の第 4 番目の分割ブロック 604d に対応するメモリアドレスからのデータの読み出しが完了すると、分割ブロックアクセス完了イベント RBEND が出力される。これにより、アップダウンカウンタ 505 は、 $D_n = 3$  だけカウントダウンし、カウント値  $C = 0$  となる。 $C - D_n = -3$  であり、 $R_n = 0$  であるため、比較器 507 における条件式  $C - D_n < R$  を満たし、比較器 507 から出力される信号 EMPTY は High レベルである。信号 EMPTY が High レベルであるため、読み込みリクエスト信号 RRREQ は無効化される。また、 $C + U_n = 4$  であり、 $W_n = 6$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たさず、比較器 506 から出力される信号 FULL は Low レベルである。信号 FULL が Low レベルであるため、書き込みリクエスト信号 WREQ は有効とされる。従って、書き込み処理用の第 4 番目の分割ブロック 603d に対応するメモリアドレスへのデータの書き込みが行われる。

10

20

#### 【0056】

この後も、上記と同様にして、追いかけ制御が順次行われる。アップダウンカウンタ 505 から出力されるカウント値 C は、図 7 (b) のように変化する。書き込み処理用の第 9 番目の分割ブロック 601i に対応するメモリアドレスへのデータの書き込みが完了すると、1 フレーム分の書き込み処理が完了したことを示すイベント WVEND が出力される。また、1 フレーム分の書き込み処理が完了したことを示す書き込み処理完了信号 WFIN が High レベルとなる。書き込み処理用の第 9 番目の分割ブロック 603i に対応するメモリアドレスへの書き込みが完了した段階では、読み出し処理用の第 11 番目～第 16 番目までの分割ブロック 604k～604p に対応するメモリアドレスからの読み出しが完了していない。書き込み処理用の第 9 番目の分割ブロック 603i に対応するメモリアドレスへの書き込みが完了した後には、読み出し処理用の第 11 番目～第 16 番目の分割ブロック 604k～604p に対応するメモリアドレスからの読み出しが順次行われる。読み出し処理用の第 16 番目の分割ブロック 604p に対応するメモリアドレスからのデータの読み出しが完了すると、1 フレーム分の読み出し処理が完了したことを示すイベント RVEND が出力される。このように、本実施形態によれば、図 6 (c) 及び図 6 (d) のようにブロック分割した場合であっても、追いかけ制御を的確に行うことができる。

30

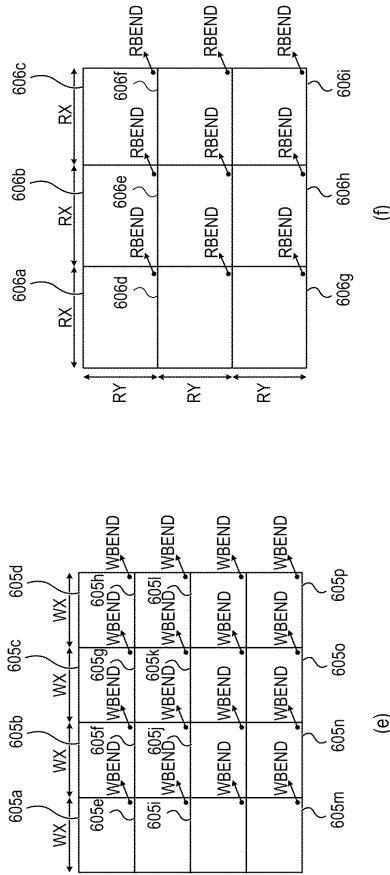

#### 【0057】

図 6 (e) 及び図 6 (f) は、書き込み処理におけるブロック分割の態様と読み出し処理におけるブロック分割の態様とが互いに異なっている例を示している。例えば、図 1において、画像の書き込みを行う処理部と読み出しを行う処理部の分割数、ブロックサイズが異なる場合に該当する。図 6 (e) は、書き込み処理用のブロック分割を示しており、図 6 (f) は、読み出し処理用のブロック分割を示している。書き込み処理用のブロック分割においては、水平方向においても垂直方向においても分割数  $WXN, WYN$  は 4 となっている。一方、読み出し処理用のブロック分割においては、水平方向においても垂直方向においても分割数  $RXN, RYN$  は 3 となっている。書き込み処理用の各々の分割ブロック 605a～605p の水平方向におけるサイズ  $WX$  は、読み出し処理用の各々の分割ブロック 606a～606i の水平方向におけるサイズ  $RX$  より小さくなっている。また

40

50

、書き込み処理用の各々の分割ブロック 605a～605p の垂直方向におけるサイズ W Y は、読み出し処理用の各々の分割ブロック 606a～606i の垂直方向におけるサイズ R Y より小さくなっている。なお、本明細書においては、個々の分割ブロックについて説明する際には、符号 605a～605p、606a～606i を用い、分割ブロック一般について説明する際には、符号 605、606 を用いることとする。図 6(e) 及び図 6(f) に示す例においては、各々のパラメータの値は例えば以下のように設定される。即ち、C0 = 0、Un = 3、Dn = 4、Wn = 18、Rn = 12、Buf = 6 と設定される。図 7(c) は、メモリアクセス制御部 202 の内部の状態を示すタイムチャートである。図 7(c) は、図 6(e) 及び図 6(f) のようにブロック分割した場合に対応している。

10

#### 【0058】

まず、初期状態について説明する。初期状態においては、アップダウンカウンタ 505 のカウント値は、初期値 C0 = 0 に設定されている。C - Dn = -4 であり、Rn = 12 であるため、比較器 507 における条件式 C - Dn < Rn を満たし、比較器 507 から出力される信号 EMPTY は High レベルである。信号 EMPTY が High レベルであるため、読み出しリクエスト信号 RRREQ は無効化される。また、C + Un = 3 であり、Wn = 18 であるため、比較器 506 における条件式 C + Un > Wn を満たさず、比較器 506 から出力される信号 FULL は Low レベルである。信号 FULL が Low レベルであるため、書き込みリクエスト信号 WREQ は有効とされる。従って、書き込み処理用の第 1 番目の分割ブロック 605a に対応するメモリアドレスへのデータの書き込みが行われる。

20

#### 【0059】

上述したように、図 6(e) 及び図 6(f) に示す例においては、読み出し処理用の各々の分割ブロック 606 のサイズは水平方向においても垂直方向においても、書き込み処理用の各々の分割ブロック 605 のサイズより大きくなっている。書き込み処理用の第 1 番目の分割ブロック 605a に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第 1 番目の分割ブロック 606a に対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、書き込み処理用の第 1 番目の分割ブロック 605a に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第 1 番目の分割ブロック 606a に対応するメモリアドレスからのデータの読み出しが行われない。書き込み処理用の第 1 番目の分割ブロック 605a に対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第 2 番目の分割ブロック 605b に対応するメモリアドレスへのデータの書き込みが行われる。即ち、書き込み処理用の第 1 番目の分割ブロック 605a に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント WEND が出力される。これにより、アップダウンカウンタ 505 は、Un = 3 だけカウントアップし、カウント値 C = 3 となる。C - Dn = -1 であり、Rn = 12 であるため、比較器 507 における条件式 C - Dn < Rn を満たし、比較器 507 から出力される信号 EMPTY は High レベルである。信号 EMPTY が High レベルであるため、読み出しリクエスト信号 RRREQ は無効化される。また、C + Un = 6 であり、Wn = 18 であるため、比較器 506 における条件式 C + Un > Wn を満たさず、比較器 506 から出力される信号 FULL は Low レベルである。信号 FULL が Low レベルであるため、書き込みリクエスト信号 WREQ は有効とされる。従って、書き込み処理用の第 2 番目の分割ブロック 605b に対応するメモリアドレスへのデータの書き込みが行われる。

30

#### 【0060】

上述したように、図 6(e) 及び図 6(f) に示す例においては、読み出し処理用の各々の分割ブロック 606 のサイズは水平方向においても垂直方向においても、書き込み処理用の各々の分割ブロック 605 のサイズより大きくなっている。書き込み処理用の第 2 番目の分割ブロック 605b に対応するメモリアドレスへのデータの書き込みが完了した

40

50

段階では、読み出し処理用の第1番目の分割ブロック606aに対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、書き込み処理用の第2番目の分割ブロック605bに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第1番目の分割ブロック606aに対応するメモリアドレスからのデータの読み出しが行われない。書き込み処理用の第2番目の分割ブロック605bに対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第3番目の分割ブロック605cに対応するメモリアドレスへのデータの書き込みが行われる。即ち、書き込み処理用の第2番目の分割ブロック605bに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントWENDが出力される。これにより、アップダウンカウンタ505は、 $U_n = 3$ だけカウントアップし、カウント値 $C = 6$ となる。 $C - D_n = 2$ であり、 $R_n = 12$ であるため、比較器507における条件式 $C - D_n < R$ を満たし、比較器507から出力される信号EMPTYはHighレベルである。信号EMPTYがHighレベルであるため、読み出しリクエスト信号RREQは無効化される。また、 $C + U_n = 9$ であり、 $W_n = 18$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たさず、比較器506から出力される信号FULLはLowレベルである。信号FULLがLowレベルであるため、書き込みリクエスト信号WREQ是有効とされる。従って、書き込み処理用の第3番目の分割ブロック605cに対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0061】

書き込み処理用の第3番目の分割ブロック605cに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第1番目の分割ブロック606aに対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、書き込み処理用の第3番目の分割ブロック605cに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第1番目の分割ブロック606aに対応するメモリアドレスからのデータの読み出しが行われない。書き込み処理用の第3番目の分割ブロック605cに対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第4番目の分割ブロック605dに対応するメモリアドレスへのデータの書き込みが行われる。即ち、書き込み処理用の第3番目の分割ブロック605cに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントWENDが出力される。これにより、アップダウンカウンタ505は、 $U_n = 3$ だけカウントアップし、カウント値 $C = 9$ となる。 $C - D_n = 5$ であり、 $R_n = 12$ であるため、比較器507における条件式 $C - D_n < R$ を満たし、比較器507から出力される信号EMPTYはHighレベルである。信号EMPTYがHighレベルであるため、読み出しリクエスト信号RREQは無効化される。また、 $C + U_n = 12$ であり、 $W_n = 18$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たさず、比較器506から出力される信号FULLはLowレベルである。信号FULLがLowレベルであるため、書き込みリクエスト信号WREQ是有効とされる。従って、書き込み処理用の第4番目の分割ブロック605dに対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0062】

書き込み処理用の第4番目の分割ブロック605dに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第1番目の分割ブロック606aに対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、書き込み処理用の第4番目の分割ブロック605dに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第1番目の分割ブロック606aに対応するメモリアドレスからのデータの読み出しが行われない。書き込み処理用の第4番目の分割ブロック605dに対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第5番目の分割ブロック605eに対応するメモリアドレスへのデータの書き込みが行われる。即ち、書き込み処理用の第4番目の分

割ブロック 605d に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント W B E N D が出力される。これにより、アップダウンカウンタ 505 は、 $U_n = 3$  だけカウントアップし、カウント値  $C = 12$  となる。 $C - D_n = 8$  であり、 $R_n = 12$  であるため、比較器 507 における条件式  $C - D_n < R$  を満たし、比較器 507 から出力される信号 E M P T Y は H i g h レベルである。信号 E M P T Y が H i g h レベルであるため、読み出しリクエスト信号 R R E Q は無効化される。また、 $C + U_n = 15$  であり、 $W_n = 18$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たさず、比較器 506 から出力される信号 F U L L は L o w レベルである。信号 F U L L が L o w レベルであるため、書き込みリクエスト信号 W R E Q は有効とされる。従って、書き込み処理用の第 5 番目の分割ブロック 605e に対応するメモリアドレスへのデータの書き込みが行われる。

#### 【 0 0 6 3 】

書き込み処理用の第 5 番目の分割ブロック 605e に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第 1 番目の分割ブロック 606a に対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、書き込み処理用の第 5 番目の分割ブロック 605e に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第 1 番目の分割ブロック 606a に対応するメモリアドレスからのデータの読み出しが行われない。書き込み処理用の第 5 番目の分割ブロック 605e に対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第 6 番目の分割ブロック 605f に対応するメモリアドレスへのデータの書き込みが行われる。即ち、書き込み処理用の第 5 番目の分割ブロック 605e に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント W B E N D が出力される。これにより、アップダウンカウンタ 505 は、 $U_n = 3$  だけカウントアップし、カウント値  $C = 15$  となる。 $C - D_n = 11$  であり、 $R_n = 12$  であるため、比較器 507 における条件式  $C - D_n < R$  を満たし、比較器 507 から出力される信号 E M P T Y は H i g h レベルである。信号 E M P T Y が H i g h レベルであるため、読み出しリクエスト信号 R R E Q は無効化される。また、 $C + U_n = 18$  であり、 $W_n = 18$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たさず、比較器 506 から出力される信号 F U L L は L o w レベルである。信号 F U L L が L o w レベルであるため、書き込みリクエスト信号 W R E Q は有効とされる。従って、書き込み処理用の第 6 番目の分割ブロック 605f に対応するメモリアドレスへのデータの書き込みが行われる。

#### 【 0 0 6 4 】

書き込み処理用の第 6 番目の分割ブロック 605f に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第 1 番目の分割ブロック 606a に対応する全てのメモリアドレスへのデータの書き込みが完了している。このため、書き込み処理用の第 6 番目の分割ブロック 605f に対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、読み出し処理用の第 1 番目の分割ブロック 606a に対応するメモリアドレスからのデータの読み出しが行われる。即ち、書き込み処理用の第 6 番目の分割ブロック 605f に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント W B E N D が出力される。これにより、アップダウンカウンタ 505 は、 $U_n = 3$  だけカウントアップし、カウント値  $C = 18$  となる。 $C - D_n = 14$  であり、 $R_n = 12$  であるため、比較器 507 における条件式  $C - D_n < R$  を満たさず、比較器 507 から出力される信号 E M P T Y は L o w レベルである。信号 E M P T Y が L o w レベルであるため、読み出しリクエスト信号 R R E Q は有効とされる。また、 $C + U_n = 21$  であり、 $W_n = 18$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たし、比較器 506 から出力される信号 F U L L は H i g h レベルである。信号 F U L L が H i g h レベルであるため、書き込みリクエスト信号 W R E Q は無効化される。従って、読み出し処理用の第 1 番目の分割ブロック 606a に対応するメモリアドレスからのデータの読み出しが行われる。

10

20

30

40

50

## 【0065】

読み出し処理用の第1番目の分割ブロック606aに対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第2番目の分割ブロック606bに対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。従って、読み出し処理用の第1番目の分割ブロック606aに対応するメモリアドレスからのデータの読み出しが完了した後には、以下に示すように、書き込み処理用の第7番目の分割ブロック605gに対応するメモリアドレスへのデータの書き込みが行われる。即ち、読み出し処理用の第1番目の分割ブロック606aに対応するメモリアドレスからのデータの読み出しが完了すると、分割ブロックアクセス完了イベントR B E N Dが出力される。これにより、アップダウンカウンタ505は、 $D_n = 4$ だけカウントダウンし、カウント値 $C = 14$ となる。 $C - D_n = 10$ であり、 $R_n = 12$ であるため、比較器507における条件式 $C - D_n < R$ を満たし、比較器507から出力される信号E M P T YはH i g hレベルである。信号E M P T YがH i g hレベルであるため、読み出しリクエスト信号R R E Qは無効化される。また、 $C + U_n = 17$ であり、 $W_n = 18$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たさず、比較器506から出力される信号F U L LはL o wレベルである。信号F U L LがL o wレベルであるため、書き込みリクエスト信号W R E Qは有効とされる。従って、書き込み処理用の第7番目の分割ブロック605gに対応するメモリアドレスへのデータの書き込みが行われる。

## 【0066】

書き込み処理用の第7番目の分割ブロック605gに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第2番目の分割ブロック606bに対応する全てのメモリアドレスへのデータの書き込みが完了している。このため、書き込み処理用の第7番目の分割ブロック605gに対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、読み出し処理用の第2番目の分割ブロック606bに対応するメモリアドレスからのデータの読み出しが行われる。即ち、書き込み処理用の第7番目の分割ブロック605gに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントW B E N Dが出力される。これにより、アップダウンカウンタ505は、 $U_n = 3$ だけカウントアップし、カウント値 $C = 17$ となる。 $C - D_n = 13$ であり、 $R_n = 12$ であるため、比較器507における条件式 $C - D_n < R$ を満たさず、比較器507から出力される信号E M P T YはL o wレベルである。信号E M P T YがL o wレベルであるため、読み出しリクエスト信号R R E Qは有効とされる。また、 $C + U_n = 20$ であり、 $W_n = 18$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たし、比較器506から出力される信号F U L LはH i g hレベルである。信号F U L LがH i g hレベルであるため、書き込みリクエスト信号W R E Qは無効化される。従って、読み出し処理用の第2番目の分割ブロック606bに対応するメモリアドレスからのデータの読み出しが行われる。

## 【0067】

読み出し処理用の第2番目の分割ブロック606bに対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第3番目の分割ブロック606cに対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。従って、読み出し処理用の第2番目の分割ブロック606bに対応するメモリアドレスからのデータの読み出しが完了した後には、以下に示すように、書き込み処理用の第8番目の分割ブロック605hに対応するメモリアドレスへのデータの書き込みが行われる。即ち、読み出し処理用の第2番目の分割ブロック606bに対応するメモリアドレスからのデータの読み出しが完了すると、分割ブロックアクセス完了イベントR B E N Dが出力される。これにより、アップダウンカウンタ505は、 $D_n = 4$ だけカウントダウンし、カウント値 $C = 13$ となる。 $C - D_n = 9$ であり、 $R_n = 12$ であるため、比較器507における条件式 $C - D_n < R$ を満たし、比較器507から出力される信号E M P T YはH i g hレベルである。信号E M P T YがH i g hレベルであるため、読み出しリクエスト信号R R E Qは無効化される。また、 $C + U_n = 16$ であり、 $W_n = 18$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たさず、比較器506から出力される信号F U L LはL o wレベルである。信号F U L LがL o wレベルであるため、書き込みリクエスト信号W R E Qは有効とされる。

506における条件式  $C + U_n > W_n$  を満たさず、比較器506から出力される信号FULLはLowレベルである。信号FULLがLowレベルであるため、書き込みリクエスト信号WREQ是有効とされる。従って、書き込み処理用の第8番目の分割ブロック605hに対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0068】

書き込み処理用の第8番目の分割ブロック605hに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第3番目の分割ブロック606cに対応する全てのメモリアドレスへのデータの書き込みが完了している。このため、書き込み処理用の第8番目の分割ブロック605hに対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、読み出し処理用の第3番目の分割ブロック606cに対応するメモリアドレスからのデータの読み出しが行われる。即ち、書き込み処理用の第8番目の分割ブロック605hに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントWBENDが出力される。これにより、アップダウンカウンタ505は、 $U_n = 3$ だけカウントアップし、カウント値 $C = 16$ となる。 $C - D_n = 12$ であり、 $R_n = 12$ であるため、比較器507における条件式 $C - D_n < R$ を満たさず、比較器507から出力される信号EMPTYはLowレベルである。信号EMPTYがLowレベルであるため、読み出しリクエスト信号RREQ是有効とされる。また、 $C + U_n = 19$ であり、 $W_n = 18$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たし、比較器506から出力される信号FULLはHighレベルである。信号FULLがHighレベルであるため、書き込みリクエスト信号WREQは無効化される。従って、読み出し処理用の第3番目の分割ブロック606cに対応するメモリアドレスからのデータの読み出しが行われる。

#### 【0069】

読み出し処理用の第3番目の分割ブロック606cに対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第4番目の分割ブロック606dに対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。従って、読み出し処理用の第3番目の分割ブロック606cに対応するメモリアドレスからのデータの読み出しが完了した後には、以下に示すように、書き込み処理用の第9番目の分割ブロック605iに対応するメモリアドレスへのデータの書き込みが行われる。即ち、読み出し処理用の第3番目の分割ブロック606cに対応するメモリアドレスからのデータの読み出しが完了すると、分割ブロックアクセス完了イベントRBENDが出力される。これにより、アップダウンカウンタ505は、 $D_n = 4$ だけカウントダウンし、カウント値 $C = 12$ となる。 $C - D_n = 8$ であり、 $R_n = 12$ であるため、比較器507における条件式 $C - D_n < R$ を満たし、比較器507から出力される信号EMPTYはHighレベルである。信号EMPTYがHighレベルであるため、読み出しリクエスト信号RREQは無効化される。また、 $C + U_n = 15$ であり、 $W_n = 18$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たさず、比較器506から出力される信号FULLはLowレベルである。信号FULLがLowレベルであるため、書き込みリクエスト信号WREQ是有効とされる。従って、書き込み処理用の第9番目の分割ブロック605iに対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0070】

この後も、上記と同様にして、追いかけ制御が順次行われる。アップダウンカウンタ505から出力されるカウント値Cは、図7(c)のように変化する。書き込み処理用の第16番目の分割ブロック605pに対応するメモリアドレスへのデータの書き込みが完了すると、1フレーム分の書き込み処理が完了したことを示すイベントWVENDが出力される。また、1フレーム分の書き込み処理が完了したことを示す書き込み処理完了信号WFINがHighレベルとなる。読み出し処理用の第9番目の分割ブロック606iに対応するメモリアドレスからのデータの読み出しが完了すると、1フレーム分の読み出し処理が完了したことを示すイベントRVENDが出力される。また、1フレーム分の読み出し処理が完了したことを示す読み出し処理完了信号RFINがHighレベルとなる。こ

10

20

30

40

50

のように、本実施形態によれば、図6(e)及び図6(f)のようにブロック分割した場合であっても、追いかけ制御を的確に行うことができる。

#### 【0071】

図8は、ブロック分割の例を概念的に示す図である。図8(a)及び図8(b)は、水平方向においてオーバラップするように読み出し処理用の分割ブロックが設定されている例を示している。図8(a)は、書き込み処理用のブロック分割を示しており、図8(b)は、読み出し処理用のブロック分割を示している。書き込み処理用のブロック分割と読み出し処理用のブロック分割のいずれにおいても、水平方向における分割数 $W \times N$ ,  $R \times N$ は3となっており、垂直方向における分割数 $W \times N$ ,  $R \times N$ は3となっている。読み出し処理用の各々の分割ブロック $802a \sim 802i$ の水平方向におけるサイズ $R \times X$ は、書き込み処理用の各々の分割ブロック $801a \sim 801i$ の水平方向におけるサイズ $W \times X$ より大きくなっている。読み出し処理用の分割ブロック $802a$ 、 $802d$ 、 $802g$ の右側の部分と、読み出し処理用の分割ブロック $802b$ 、 $802e$ 、 $802h$ の左側の部分とが、それぞれ互いにオーバラップしている。読み出し処理用の分割ブロック $802b$ 、 $802e$ 、 $802h$ の右側の部分と、読み出し処理用の分割ブロック $802c$ 、 $802f$ 、 $802i$ の左側の部分とが、それぞれ互いにオーバラップしている。読み出し処理用の各々の分割ブロック $802a \sim 802i$ の垂直方向におけるサイズ $R \times Y$ と、書き込み処理用の各々の分割ブロック $801a \sim 801i$ の垂直方向におけるサイズ $R \times Y$ とは、互いに等しくなっている。なお、本明細書においては、個々の分割ブロックについて説明する際には、符号 $801a \sim 801i$ 、 $802a \sim 802i$ を用い、分割ブロック一般について説明する際には、符号 $801$ 、 $802$ を用いることとする。図8(a)及び図8(b)に示す例においては、各々のパラメータの値は例えば以下のように設定される。即ち、 $C_0 = -3$ 、 $U_n = 3$ 、 $D_n = 3$ 、 $W_n = 5$ 、 $R_n = 0$ 、 $B_{uf} = 5$ と設定される。なお、 $C_0$ を-3に設定しているのは、読み出し処理用の分割ブロック $802$ の水平方向におけるサイズが書き込み処理用の分割ブロック $801$ の水平方向におけるサイズより大きく、読み出し処理を遅らせる必要があるためである。図8(a)及び図8(b)に示す例においては、1回分の書き込み処理の分だけ読み出し処理を遅らせればよい。1回分の書き込み処理に対応するカウントアップ値は $U_n = R \times N = 3$ である。従って、ここでは、 $C_0 = -3$ としている。図9は、メモリアクセス制御部202の内部の状態を示すタイムチャートである。図9は、図8(a)及び図8(b)のようにブロック分割した場合に対応している。

#### 【0072】

まず、初期状態について説明する。初期状態においては、アップダウンカウンタ505のカウント値は、初期値 $C_0 = -3$ に設定されている。 $C - D_n = -6$ であり、 $R_n = 0$ であるため、比較器507における条件式 $C - D_n < R_n$ を満たし、比較器507から出力される信号EMP TYはHighレベルである。信号EMP TYがHighレベルであるため、読み出しリクエスト信号RREQは無効化される。また、 $C + U_n = 0$ であり、 $W_n = 5$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たさず、比較器506から出力される信号FUL LはLowレベルである。信号FUL LがLowレベルであるため、書き込みリクエスト信号WREQは有効とされる。従って、書き込み処理用の第1番目の分割ブロック $801a$ に対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0073】

上述したように、図8(a)及び図8(b)に示す例においては、読み出し処理用の各々の分割ブロック $802$ のサイズは、水平方向において、書き込み処理用の各々の分割ブロック $801$ のサイズより大きくなっている。書き込み処理用の第1番目の分割ブロック $801a$ に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第1番目の分割ブロック $802a$ に対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、書き込み処理用の第1番目の分割ブロック $801a$ に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み

出し処理用の第1番目の分割ブロック802aに対応するメモリアドレスからのデータの読み出しは行われない。書き込み処理用の第1番目の分割ブロック801aに対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第2番目の分割ブロック801bに対応するメモリアドレスへのデータの書き込みが行われる。即ち、書き込み処理用の第1番目の分割ブロック801aに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントW B E N Dが出力される。これにより、アップダウンカウンタ505は、 $U_n = 3$ だけカウントアップし、カウント値 $C = 0$ となる。 $C - D_n = -3$ であり、 $R_n = 0$ であるため、比較器507における条件式 $C - D_n < R$ を満たし、比較器507から出力される信号E M P T YはH i g hレベルである。信号E M P T YがH i g hレベルであるため、読み出しリクエスト信号R R E Qは無効化される。また、 $C + U_n = 3$ であり、 $W_n = 5$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たさず、比較器506から出力される信号F U L LはL o wレベルである。信号F U L LがL o wレベルであるため、書き込みリクエスト信号W R E Qは有効とされる。従って、書き込み処理用の第2番目の分割ブロック801bに対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0074】

書き込み処理用の第2番目の分割ブロック801bに対応するメモリアドレスへのデータの書き込みが完了した段階で、読み出し処理用の第1番目の分割ブロック802aに対応する全てのメモリアドレスへのデータの書き込みが完了している。従って、書き込み処理用の第2番目の分割ブロック801bに対応するメモリアドレスへのデータの書き込みが完了した後には、以下に示すように、読み出し処理用の第1番目の分割ブロック802aに対応するメモリアドレスからのデータの読み出しが行われる。即ち、書き込み処理用の第2番目の分割ブロック801bに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントW B E N Dが出力される。これにより、アップダウンカウンタ505は、 $U_n = 3$ だけカウントアップし、カウント値 $C = 3$ となる。 $C - D_n = 0$ であり、 $R_n = 0$ であるため、比較器507における条件式 $C - D_n < R$ を満たさず、比較器507から出力される信号E M P T YはL o wレベルである。信号E M P T YがL o wレベルであるため、読み出しリクエスト信号R R E Qは有効とされる。また、 $C + U_n = 6$ であり、 $W_n = 5$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たし、比較器506から出力される信号F U L LはH i g hレベルである。信号F U L LがH i g hレベルであるため、書き込みリクエスト信号W R E Qは無効化される。従って、読み出し処理用の第1番目の分割ブロック802aに対応するメモリアドレスからのデータの読み出しが行われる。

#### 【0075】

読み出し処理用の第1番目の分割ブロック802aに対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第2番目の分割ブロック802bに対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、読み出し処理用の第1番目の分割ブロック802aに対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第2番目の分割ブロック802bに対応するメモリアドレスからのデータの読み出しへは行われない。読み出し処理用の第1番目の分割ブロック802aに対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第3番目の分割ブロック801cに対応するメモリアドレスへのデータの書き込みが行われる。即ち、読み出し処理用の第1番目の分割ブロック802aに対応するメモリアドレスからのデータの読み出しが完了すると、分割ブロックアクセス完了イベントR B E N Dが出力される。これにより、アップダウンカウンタ505は、 $D_n = 3$ だけカウントダウンし、カウント値 $C = 0$ となる。 $C - D_n = -3$ であり、 $R_n = 0$ であるため、比較器507における条件式 $C - D_n < R$ を満たし、比較器507から出力される信号E M P T YはH i g hレベルである。信号E M P T YがH i g hレベルであるため、読み出しリクエスト信号R R E Qは無効化される。また、 $C + U_n = 3$ であり、 $W_n = 5$ であるため、比較器506における条件式 $C + U_n > W_n$

10

20

30

40

50

$n$ を満たさず、比較器 506 から出力される信号 FULL は Low レベルである。信号 FULL が Low レベルであるため、書き込みリクエスト信号 WREQ は有効とされる。従って、書き込み処理用の第 3 番目の分割ブロック 801c に対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0076】

この後も、上記と同様にして、追いかけ制御が順次行われる。アップダウンカウンタ 505 から出力されるカウント値 C は、図 9 のように変化する。書き込み処理用の第 9 番目の分割ブロック 801i に対応するメモリアドレスへのデータの書き込みが完了すると、1 フレーム分の書き込み処理が完了したことを示すイベント WEND が出力される。また、1 フレーム分の書き込み処理が完了したことを示す書き込み処理完了信号 WFIN が High レベルとなる。この後、読み出し処理用の第 9 番目の分割ブロック 802i に対応するメモリアドレスからのデータの読み出しが完了すると、1 フレーム分の読み出し処理が完了したことを示すイベント REND が出力される。また、1 フレーム分の読み出し処理が完了したことを示す読み出し処理完了信号 RFIN が High レベルとなる。このように、図 8(a) 及び図 8(b) のようにブロック分割した場合であっても、追いかけ制御を的確に行うことができる。

#### 【0077】

図 8(c) 及び図 8(d) は、垂直方向においてオーバラップするように読み出し処理用の分割ブロックが設定されている例を示している。図 8(c) は、書き込み処理用のブロック分割を示しており、図 8(d) は、読み出し処理用のブロック分割を示している。書き込み処理用のブロック分割と読み出し処理用のブロック分割のいずれにおいても、水平方向における分割数  $WXN$ ,  $RXN$  は 3 となっており、垂直方向における分割数  $WYN$ ,  $RYN$  は 3 となっている。読み出し処理用の各々の分割ブロック 804a ~ 804i の水平方向におけるサイズ  $RX$  と、書き込み処理用の各々の分割ブロック 803a ~ 803i の水平方向におけるサイズとは互いに等しくなっている。読み出し処理用の各々の分割ブロック 804a ~ 804i の垂直方向におけるサイズ  $RY$  は、書き込み処理用の各々の分割ブロック 802a ~ 802i の垂直方向におけるサイズ  $RY$  より大きくなっている。読み出し処理用の分割ブロック 804a ~ 804c の下側の部分と、読み出し処理用の分割ブロック 804d ~ 804f の上側の部分とが、それぞれ互いにオーバラップしている。また、読み出し処理用の分割ブロック 804d ~ 804f の下側の部分と、読み出し処理用の分割ブロック 804g ~ 804i の上側の部分とが、それぞれ互いにオーバラップしている。なお、本明細書においては、個々の分割ブロックについて説明する際には、符号 803a ~ 803i, 804a ~ 804i を用い、分割ブロック一般について説明する際には、符号 803, 804 を用いることとする。図 8(c) 及び図 8(d) に示す例においては、各々のパラメータの値は例えば以下のように設定される。即ち、 $C0 = -9$ ,  $Un = 3$ ,  $Dn = 3$ ,  $Wn = 5$ ,  $Rn = 0$ ,  $Buf = 5$  と設定される。なお、 $C0$  を -9 に設定しているのは、読み出し処理用の分割ブロック 804 の垂直方向におけるサイズが書き込み処理用の分割ブロック 803 の水平方向におけるサイズより大きく、読み出し処理を遅らせる必要があるためである。図 8(c) 及び図 8(d) に示す例においては、3 回分の書き込み処理の分だけ読み出し処理を遅らせればよい。3 回分の書き込み処理に対応するカウントアップ値は  $Un \times 3 = RXN \times 3 = 9$  である。従って、ここでは、 $C0 = -9$  としている。図 10 は、メモリアクセス制御部 202 の内部の状態を示すタイムチャートである。図 10 は、図 8(c) 及び図 8(d) のようにブロック分割した場合に対応している。

#### 【0078】

まず、初期状態について説明する。初期状態においては、アップダウンカウンタ 505 のカウント値 C は、初期値  $C0 = -9$  に設定されている。 $C - Dn = -12$  であり、 $Rn = 0$  であるため、比較器 507 における条件式  $C - Dn < Rn$  を満たし、比較器 507 から出力される信号 EMPTY は High レベルである。信号 EMPTY が High レベルであるため、読み出しリクエスト信号 RREQ は無効化される。また、 $C + Un = -6$  で

10

20

30

40

50

あり、 $W_n = 5$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たさず、比較器 506 から出力される信号 FULL は Low レベルである。信号 FULL が Low レベルであるため、書き込みリクエスト信号 WREQ は有効とされる。従って、書き込み処理用の第 1 番目の分割ブロック 803a に対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0079】

上述したように、図 8 (c) 及び図 8 (d) に示す例においては、読み出し処理用の各々の分割ブロック 804 のサイズは、垂直方向において、書き込み処理用の各々の分割ブロック 803 のサイズより大きくなっている。書き込み処理用の第 1 番目の分割ブロック 803a に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第 1 番目の分割ブロック 804a に対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、書き込み処理用の第 1 番目の分割ブロック 803a に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第 1 番目の分割ブロック 804a に対応するメモリアドレスからのデータの読み出しが行われない。書き込み処理用の第 1 番目の分割ブロック 803a に対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第 2 番目の分割ブロック 803b に対応するメモリアドレスへのデータの書き込みが行われる。即ち、書き込み処理用の第 1 番目の分割ブロック 803a に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント WEND が 10 出力される。これにより、アップダウンカウンタ 505 は、 $U_n = 3$  だけカウントアップし、カウント値  $C = -6$  となる。 $C - D_n = -9$  であり、 $R_n = 0$  であるため、比較器 507 における条件式  $C - D_n < R$  を満たし、比較器 507 から出力される信号 EMPTY は High レベルである。信号 EMPTY が High レベルであるため、読み出しリクエスト信号 RREQ は無効化される。また、 $C + U_n = -3$  であり、 $W_n = 5$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たさず、比較器 506 から出力される信号 FULL は Low レベルである。信号 FULL が Low レベルであるため、書き込みリクエスト信号 WREQ は有効とされる。従って、書き込み処理用の第 2 番目の分割ブロック 803b に対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0080】

書き込み処理用の第 2 番目の分割ブロック 803b に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第 1 番目の分割ブロック 804a に対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、書き込み処理用の第 2 番目の分割ブロック 803a に対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第 1 番目の分割ブロック 804a に対応するメモリアドレスからのデータの読み出しが行われない。書き込み処理用の第 2 番目の分割ブロック 803b に対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第 3 番目の分割ブロック 803c に対応するメモリアドレスへのデータの書き込みが行われる。即ち、書き込み処理用の第 2 番目の分割ブロック 803b に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント WEND が 20 出力される。これにより、アップダウンカウンタ 505 は、 $U_n = 3$  だけカウントアップし、カウント値  $C = -3$  となる。 $C - D_n = -6$  であり、 $R_n = 0$  であるため、比較器 507 における条件式  $C - D_n < R$  を満たし、比較器 507 から出力される信号 EMPTY は High レベルである。信号 EMPTY が High レベルであるため、読み出しリクエスト信号 RREQ は無効化される。また、 $C + U_n = 0$  であり、 $W_n = 5$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たさず、比較器 506 から出力される信号 FULL は Low レベルである。信号 FULL が Low レベルであるため、書き込みリクエスト信号 WREQ は有効とされる。従って、書き込み処理用の第 3 番目の分割ブロック 803c に対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0081】

書き込み処理用の第3番目の分割ブロック803cに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第1番目の分割ブロック804aに対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、書き込み処理用の第3番目の分割ブロック803aに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第1番目の分割ブロック804aに対応するメモリアドレスからのデータの読み出しが行われない。書き込み処理用の第3番目の分割ブロック803cに対応するメモリアドレスへのデータの書き込みが完了した後には、以下のように、書き込み処理用の第4番目の分割ブロック803dに対応するメモリアドレスへのデータの書き込みが行われる。即ち、書き込み処理用の第3番目の分割ブロック803cに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントWENDが出力される。これにより、アップダウンカウンタ505は、 $U_n = 3$ だけカウントアップし、カウント値 $C = 0$ となる。 $C - D_n = -3$ であり、 $R_n = 0$ であるため、比較器507における条件式 $C - D_n < R$ を満たし、比較器507から出力される信号EMPTYはHighレベルである。信号EMPTYがHighレベルであるため、読み出しリクエスト信号RRREQは無効化される。また、 $C + U_n = 3$ であり、 $W_n = 5$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たさず、比較器506から出力される信号FULLはLowレベルである。信号FULLがLowレベルであるため、書き込みリクエスト信号WREQは有効とされる。従って、書き込み処理用の第4番目の分割ブロック803dに対応するメモリアドレスへのデータの書き込みが行われる。

10

20

#### 【0082】

書き込み処理用の第4番目の分割ブロック803dに対応するメモリアドレスへのデータの書き込みが完了した段階では、読み出し処理用の第1番目の分割ブロック804aに対応する全てのメモリアドレスへのデータの書き込みが完了している。このため、書き込み処理用の第4番目の分割ブロック803dに対応するメモリアドレスへの書き込みが完了した後には、以下に示すように、読み出し処理用の第1番目の分割ブロック804aに対応するメモリアドレスからの読み出しが行われる。即ち、書き込み処理用の第4番目の分割ブロック803dに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントWENDが出力される。これにより、アップダウンカウンタ505は、 $U_n = 3$ だけカウントアップし、カウント値 $C = 3$ となる。 $C - D_n = 0$ であり、 $R_n = 0$ であるため、比較器507における条件式 $C - D_n < R$ を満たさず、比較器507から出力される信号EMPTYはLowレベルである。信号EMPTYがLowレベルであるため、読み出しリクエスト信号RRREQは有効とされる。また、 $C + U_n = 6$ であり、 $W_n = 5$ であるため、比較器506における条件式 $C + U_n > W_n$ を満たし、比較器506から出力される信号FULLはHighレベルである。信号FULLがHighレベルであるため、書き込みリクエスト信号WREQは無効化される。従って、読み出し処理用の第1番目の分割ブロック804aに対応するメモリアドレスからのデータの読み出しが行われる。

30

#### 【0083】

読み出し処理用の第1番目の分割ブロック804aに対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第2番目の分割ブロック804bに対応する全てのメモリアドレスへのデータの書き込みが完了しているわけではない。このため、読み出し処理用の第1番目の分割ブロック804aに対応するメモリアドレスからのデータの読み出しが完了した段階では、読み出し処理用の第2番目の分割ブロック804bに対応するメモリアドレスからのデータの読み出しが行われない。読み出し処理用の第1番目の分割ブロック804aに対応するメモリアドレスからのデータの読み出しが完了した後には、以下のように、書き込み処理用の第5番目の分割ブロック803eに対応するメモリアドレスへのデータの書き込みが行われる。即ち、読み出し処理用の第1番目の分割ブロック804aに対応するメモリアドレスからのデータの読み出しが完了すると、分割ブロックアクセス完了イベントRBENDが出力される。これにより、アップダ

40

50

ウンカウンタ 505 は、 $D_n = 3$  だけカウントダウンし、カウント値  $C = 0$  となる。 $C - D_n = -3$  であり、 $R_n = 0$  であるため、比較器 507 における条件式  $C - D_n < R$  を満たし、比較器 507 から出力される信号 E M P T Y は H i g h レベルである。信号 E M P T Y が H i g h レベルであるため、読み出しリクエスト信号 R R E Q は無効化される。また、 $C + U_n = 3$  であり、 $W_n = 5$  であるため、比較器 506 における条件式  $C + U_n > W_n$  を満たさず、比較器 506 から出力される信号 F U L L は L o w レベルである。信号 F U L L が L o w レベルであるため、書き込みリクエスト信号 W R E Q は有効とされる。従って、書き込み処理用の第 5 番目の分割ブロック 803e に対応するメモリアドレスへのデータの書き込みが行われる。

## 【0084】

10

この後も、上記と同様にして、追いかけ制御が順次行われる。アップダウンカウンタ 505 から出力されるカウント値  $C$  は、図 10 のように変化する。書き込み処理用の第 9 番目の分割ブロック 803i に対応するメモリアドレスへのデータの書き込みが完了すると、1 フレーム分の書き込み処理が完了したことを示すイベント W V E N D が出力される。また、1 フレーム分の書き込み処理が完了したことを示す書き込み処理完了信号 W F I N が H i g h レベルとなる。この後、読み出し処理用の第 9 番目の分割ブロック 804i に対応するメモリアドレスからのデータの読み出しが完了すると、1 フレーム分の読み出し処理が完了したことを示すイベント R V E N D が出力される。また、1 フレーム分の読み出し処理が完了したことを示す読み出し処理完了信号 R F I N が H i g h レベルとなる。このように、図 8(c) 及び図 8(d) のようにブロック分割した場合であっても、追いかけ制御を的確に行うことができる。

## 【0085】

20

なお、ここでは、追いかけ制御のパラメータ  $C_0$ 、 $U_n$ 、 $D_n$ 、 $W_n$ 、 $R_n$ 、 $B u f$  を上記のような値に設定する場合を例に説明したが、これに限定されるものではない。

## 【0086】

このように、本実施形態によれば、所定のブロックでの書き込みが完了する毎に第 1 のイベントが発せられ、所定のブロックでの読み出しが完了する毎に第 2 のイベントが発せられる。そして、これら第 1 のイベントや第 2 のイベントに基づいてアップダウンカウンタがカウントアップやカウントダウンを行い、アップダウンカウンタのカウント値に基づいて読み出し処理又は書き込み処理を選択的に行う。従って、本実施形態によれば、読み出し処理や書き込み処理を的確に行い得る画像処理装置を提供することができる。

30

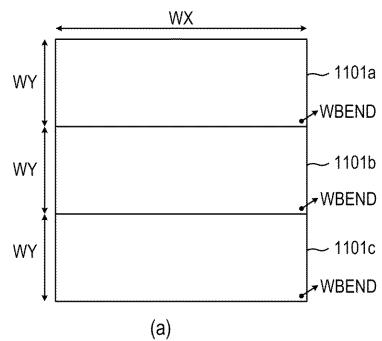

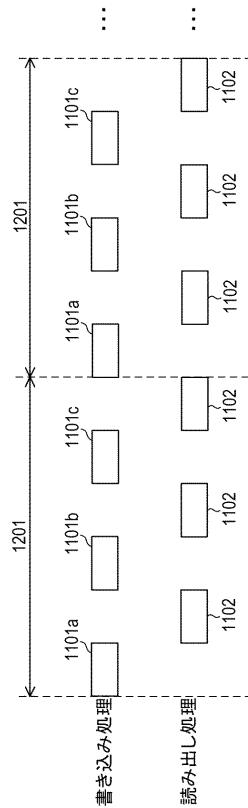

## 【0087】

## [ 第 2 実施形態 ]

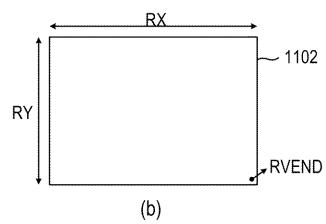

第 2 実施形態によるメモリ制御装置及びメモリ制御方法について図面を用いて説明する。本実施形態によるメモリ制御装置の構成は、第 1 実施形態によるメモリ制御装置の構成と同様であるため、説明を省略する。図 11 は、ブロック分割とフレームの例を概念的に示す図である。図 11 は、1 フレームの画像に対応する仮想的なアドレス空間を概念的に示している。図 11(a) は、書き込み処理用のブロック分割の様子の例を示している。図 11(a) に示すように、書き込み処理用のブロック分割においては、垂直方向における分割数  $W Y N$  は 3 となっている。一方、水平方向においては分割されていない。即ち、水平方向における分割数  $W X N$  は 1 となっている。ここでは、信号処理部 103 や変倍処理部 104 等によって分割ブロック 1101a ~ 1101c の単位で順次処理される画像が、分割ブロック 1101a ~ 1101c の単位でメモリ 111 に順次書き込まれる場合を例に説明する。なお、本明細書においては、書き込み処理用の個々の分割ブロックについて説明する際には、符号 1101a ~ 1101c を用い、書き込み処理用の分割ブロック一般について説明する際には、符号 1101 を用いることとする。図 11(a) に示すように、各々の分割ブロック 1101a ~ 1101c に対応するメモリアドレスへのデータの書き込みが完了する毎に、分割ブロックアクセス完了イベント W B E N D が出力される。

40

## 【0088】

50

図11(b)は、読み出し処理されるフレームの例を示している。ここでは、図11(b)に示すように、読み出し処理においてはブロック分割が行われず、1つのフレーム1102を単位として読み出し処理が行われる。即ち、1フレーム分のデータの読み出しが1回の読み出し処理において行われる。なお、1フレーム分のデータ量は比較的小さく設定されている。メモリ111から読み出されたデータに対して評価値取得部102によって評価が行われる。評価値取得部102によって取得される評価値としては、例えば、ヒストグラムや積算値等が挙げられる。図11(b)に示すように、1フレーム分のデータの読み出しが完了する毎に、1フレーム分のデータの読み出しが完了したことを示すイベントR V E N Dが出力される。

#### 【0089】

なお、ここでは、分割ブロック1101a～1101cに対応するメモリアドレスと、フレーム1102に対応するメモリアドレスとが互いに異なっている場合を例に説明するが、これに限定されるものではない。

#### 【0090】

メモリアクセス制御部202においては、分割ブロックアクセス完了イベントW B E N Dがセレクタ501によって選択される。また、メモリアクセス制御部202においては、フレーム1102a～1102cの読み出しが完了したことを示すイベントR V E N Dがセレクタ502によって選択される。本実施形態では、各々のパラメータの値は例えば以下のように設定される。即ち、C0=0、Un=1、Dn=1、Wn=1、Rn=0と設定される。

#### 【0091】

図12は、本実施形態によるメモリ制御装置によって行われる書き込み処理及び読み出し処理を示すタイムチャートである。

#### 【0092】

まず、初期状態について説明する。初期状態においては、アップダウンカウンタ505のカウント値は、初期値C0=0に設定されている。C-Dn=-1であり、Rn=0であるため、比較器507における条件式C-Dn < Rnを満たし、比較器507から出力される信号E M P T YはH i g hレベルである。信号E M P T YがH i g hレベルであるため、読み出しリクエスト信号R R E Qは無効化される。また、C+Un=1であり、Wn=1であるため、比較器506における条件式C+Un > Wnを満たさず、比較器506から出力される信号F U L LはL o wレベルである。信号F U L LがL o wレベルであるため、書き込みリクエスト信号W R E Qは有効とされる。従って、書き込み処理用の第1番目の分割ブロック1101aに対応するメモリアドレスへのデータの書き込みが行われる。

#### 【0093】

書き込み処理用の第1番目の分割ブロック1101aに対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベントW B E N Dが出力される。これにより、アップダウンカウンタ505は、Un=1だけカウントアップし、カウント値C=1となる。C+Un=2であり、Wn=1であるため、比較器506における条件式C+Un > Wnを満たし、比較器506から出力される信号F U L LはH i g hレベルである。信号F U L LがH i g hレベルであるため、書き込みリクエスト信号W R E Qは無効化される。また、C-Dn=0であり、Rn=0であるため、比較器507における条件式C-Dn < Rnを満たさず、比較器507から出力される信号E M P T YはL o wレベルである。信号E M P T YがL o wレベルであるため、読み出しリクエスト信号R R E Qは有効とされる。従って、フレーム1102に対応するメモリアドレスからのデータの第1回目の読み出しが行われる。

#### 【0094】

フレーム1102に対応するメモリアドレスからのデータの第1回目の読み出しが完了すると、当該フレーム1102に対応するメモリアドレスからのデータの読み出しが完了したことを示すイベントR V E N Dが出力される。これにより、アップダウンカウンタ5

10

20

30

40

50

0 5 は、  $D_n = 1$  だけカウントダウンし、カウント値  $C = 0$  となる。  $C - D_n = -1$  であり、  $R_n = 0$  であるため、比較器 5 0 7 における条件式  $C - D_n < R$  を満たし、比較器 5 0 7 から出力される信号 E M P T Y は H i g h レベルである。信号 E M P T Y が H i g h レベルであるため、読み出しリクエスト信号 R R E Q は無効化される。また、  $C + U_n = 1$  であり、  $W_n = 1$  であるため、比較器 5 0 6 における条件式  $C + U_n > W_n$  を満たさず、比較器 5 0 6 から出力される信号 F U L L は L o w レベルである。信号 F U L L が L o w レベルであるため、書き込みリクエスト信号 W R E Q は有効とされる。従って、書き込み処理用の第 2 番目の分割ブロック 1 1 0 1 b に対応するメモリアドレスへのデータの書き込みが行われる。

## 【 0 0 9 5 】

書き込み処理用の第 2 番目の分割ブロック 1 1 0 1 b に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント W B E N D が出力される。これにより、アップダウンカウンタ 5 0 5 は、  $U_n = 1$  だけカウントアップし、カウント値  $C = 1$  となる。  $C + U_n = 2$  であり、  $W_n = 1$  であるため、比較器 5 0 6 における条件式  $C + U_n > W_n$  を満たし、比較器 5 0 6 から出力される信号 F U L L は H i g h レベルである。信号 F U L L が H i g h レベルであるため、書き込みリクエスト信号 W R E Q は無効化される。また、  $C - D_n = 0$  であり、  $R_n = 0$  であるため、比較器 5 0 7 における条件式  $C - D_n < R_n$  を満たさず、比較器 5 0 7 から出力される信号 E M P T Y は L o w レベルである。信号 E M P T Y が L o w レベルであるため、読み出しリクエスト信号 R R E Q は有効とされる。従って、フレーム 1 1 0 2 に対応するメモリアドレスからのデータの第 2 回目の読み出しが行われる。

## 【 0 0 9 6 】

フレーム 1 1 0 2 に対応するメモリアドレスからのデータの第 2 回目の読み出しが完了すると、当該フレーム 1 1 0 2 に対応するメモリアドレスからのデータの読み出しが完了したこと示すイベント R V E N D が出力される。これにより、アップダウンカウンタ 5 0 5 は、  $D_n = 1$  だけカウントダウンし、カウント値  $C = 0$  となる。  $C - D_n = -1$  であり、  $R_n = 0$  であるため、比較器 5 0 7 における条件式  $C - D_n < R$  を満たし、比較器 5 0 7 から出力される信号 E M P T Y は H i g h レベルである。信号 E M P T Y が H i g h レベルであるため、読み出しリクエスト信号 R R E Q は無効化される。また、  $C + U_n = 1$  であり、  $W_n = 1$  であるため、比較器 5 0 6 における条件式  $C + U_n > W_n$  を満たさず、比較器 5 0 6 から出力される信号 F U L L は L o w レベルである。信号 F U L L が L o w レベルであるため、書き込みリクエスト信号 W R E Q は有効とされる。従って、書き込み処理用の第 3 番目の分割ブロック 1 1 0 1 c に対応するメモリアドレスへのデータの書き込みが行われる。

## 【 0 0 9 7 】

書き込み処理用の第 3 番目の分割ブロック 1 1 0 1 c に対応するメモリアドレスへのデータの書き込みが完了すると、分割ブロックアクセス完了イベント W B E N D が出力される。これにより、アップダウンカウンタ 5 0 5 は、  $U_n = 1$  だけカウントアップし、カウント値  $C = 1$  となる。  $C + U_n = 2$  であり、  $W_n = 1$  であるため、比較器 5 0 6 における条件式  $C + U_n > W_n$  を満たし、比較器 5 0 6 から出力される信号 F U L L は H i g h レベルである。信号 F U L L が H i g h レベルであるため、書き込みリクエスト信号 W R E Q は無効化される。また、  $C - D_n = 0$  であり、  $R_n = 0$  であるため、比較器 5 0 7 における条件式  $C - D_n < R_n$  を満たさず、比較器 5 0 7 から出力される信号 E M P T Y は L o w レベルである。信号 E M P T Y が L o w レベルであるため、読み出しリクエスト信号 R R E Q は有効とされる。従って、フレーム 1 1 0 2 に対応するメモリアドレスからのデータの第 3 回目の読み出しが行われる。

## 【 0 0 9 8 】

このように、1つの周期 1 2 0 1 内において、3回の書き込み処理と3回の読み出し処理とが行われる。1つの周期 1 2 0 1 に含まれる3回の書き込み処理によって、1フレーム分の画像がメモリ 1 1 1 に書き込まれる。一方、1つの周期 1 2 0 1 に含まれる3回の

10

20

30

40

50

読み出し処理によって、同じ画像データが3回読み出される。こうして読み出された各々の画像データを順次用いて、互いに異なる3種類の評価値が評価値取得部102によって順次取得される。即ち、第1回目の読み出し処理によって読み出された画像データからは、第1の評価値が評価値取得部102によって取得される。第2回目の読み出し処理によって読み出された画像データからは、第1の評価値とは異なる第2の評価値が評価値取得部102によって取得される。第3回目の読み出し処理によって読み出された画像データからは、第1の評価値と第2の評価値のいずれとも異なる第3の評価値が評価値取得部102によって取得される。

この後も、上記と同様の処理が繰り返し行われる。

#### 【0099】

10

このように、書き込みにおける単位と読み出しにおける単位とが互いに異なっていてもよく、また、書き込みにおけるアクセスアドレスと読み出しにおけるアクセスアドレスとが互いに異なっていてもよい。本実施形態においても、読み出し処理や書き込み処理を的確に行い得る画像処理装置を提供することができる。

#### 【0100】

##### 〔変形実施形態〕

以上、本発明の好ましい実施形態について説明したが、本発明はこれらの実施形態に限定されず、その要旨の範囲内で種々の変形及び変更が可能である。

#### 【0101】

20

例えば、第1実施形態では、分割ブロックアクセス完了イベントB E N Dに基づいて、アップダウンカウンタ505のカウント値をカウントアップ又はカウントダウンしたが、これに限定されるものではない。例えば、最小アクセス単位アクセス完了イベントW E N Dに基づいて、アップダウンカウンタ505のカウント値をカウントアップ又はカウントダウンさせてもよい。即ち、最小アクセス単位401が、書き込みアクセスや読み出しアクセスを行う際の単位であるブロックであってもよい。この場合、書き込み処理用の最小アクセス単位401のサイズと読み出し処理用の最小アクセス単位401のサイズとが互いに異なっていてもよい。また、最小アクセス単位401にオーバラップが生じていてもよい。C0, Un, Dn, Wn, Rn等の各パラメータを適宜設定することにより、的確なアクセス制御が可能である。また、行アクセス完了イベントL E N Dブロックに基づいて、アップダウンカウンタ505のカウント値をカウントアップ又はカウントダウンさせてもよい。即ち、行411が、書き込みアクセスや読み出しアクセスを行う際の単位であるブロックであってもよい。この場合、書き込み処理用の行411のサイズと読み出し処理用の行411のサイズとが互いに異なっていてもよい。また、行411にオーバラップが生じていてもよい。C0, Un, Dn, Wn, Rn等の各パラメータを適宜設定することにより、的確なアクセス制御が可能である。また、ブロック行アクセス完了イベントB L E N Dに基づいて、アップダウンカウンタ505のカウント値をカウントアップ又はカウントダウンさせてもよい。即ち、ブロック行431が、書き込みアクセスや読み出しアクセスを行う際の単位であるブロックであってもよい。この場合、書き込み処理用のブロック行431のサイズと読み出し処理用のブロック行431のサイズとが互いに異なっていてもよい。また、ブロック行431にオーバラップが生じていてもよい。C0, Un, Dn, Wn, Rn等の各パラメータを適宜設定することにより、的確なアクセス制御が可能である。また、フレームアクセス完了イベントV E N Dに基づいて、アップダウンカウンタ505のカウント値をカウントアップ又はカウントダウンさせてもよい。即ち、フレーム441が、書き込みアクセスや読み出しアクセスを行う際の単位であるブロックであってもよい。

30

#### 【0102】

40

また、第2実施形態では、書き込み用のブロック分割における分割数を3とし、1つの周期1201内において、分割ブロック1101の書き込み処理と、フレーム1102の読み出し処理とを交互に3回ずつ行う場合を例に説明した。しかし、これに限定されるものではない。例えば、書き込み用のブロック分割における分割数を5とし、1つの周期1

50

201内において、分割ブロックの書き込み処理と、フレームの読み出し処理とを交互に5回ずつ行うようにしてもよい。

#### 【0103】

また、第2実施形態では、分割ブロックアクセス完了イベントB E N Dやフレームアクセス完了イベントV E N Dに基づいてアップダウンカウンタ505がカウントアップやカウントダウンを行う場合を例に説明したが、これに限定されるものではない。例えば、最小アクセス単位アクセス完了イベントW E N D、行アクセス完了イベントL E N D、又は、ブロック行アクセス完了イベントB L E N Dに基づいて、アップダウンカウンタ505がカウントアップやカウントダウンを適宜行ってもよい。

#### 【0104】

また、第2実施形態では、ある画像についての書き込み処理を1つの周期1201内において分割して行い、ある画像についての読み出し処理を1つの周期1201内において複数回行う場合を例に説明したが、これに限定されるものではない。例えば、ある画像についての書き込み処理を1つの周期1201内において複数回行い、ある画像についての読み出し処理を1つの周期1201内において分割して行うようにしてもよい。

#### 【0105】

また、第2実施形態では、書き込み処理と読み出し処理とを交互に行う場合を例に説明したが、これに限定されるものではない。例えば、第1の画像についての書き込み処理と、第1の画像とは異なる第2の画像についての書き込み処理とを行う際に適用することも可能である。この場合には、読み出し制御部203の代わりに書き込み制御部201が設けられ、複数の書き込み制御部201から発せられる書き込みリクエスト信号M R E Qのうちのいずれかがメモリアクセス制御部202によって有効とされる。第1の画像の分割ブロックについての書き込み処理と、第2の画像の分割ブロックについての書き込み処理とが、1つの周期1201内において交互に繰り返し行われる。また、第1の画像についての読み出し処理と、第1の画像とは異なる第2の画像についての読み出し処理とを行う際に適用することも可能である。この場合には、書き込み制御部201の代わりに読み出し制御部203が設けられ、複数の読み出し制御部203から発せられる読み出しリクエスト信号R R E Qのうちのいずれかがメモリアクセス制御部202によって有効とされる。これにより、第1の画像の分割ブロックについての読み出し処理と、第2の画像の分割ブロックについての読み出し処理とが、1つの周期1201内において交互に繰り返し行われる。

#### 【0106】

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路（例えば、A S I C）によっても実現可能である。

#### 【符号の説明】

#### 【0107】

101...撮像部

102...評価値取得部

103...信号処理部

104...変倍処理部

105...圧縮処理部

106...表示部

107...表示制御部

108...記録媒体

109...記録媒体制御部

110...メモリ制御部

111...メモリ

10

20

30

40

【図4-2】

【図5】

【図6-1】

【図6-2】

【図 6 - 3】

【図7-2】

【図7-1】

【図 7 - 3】

【図 1 1】

【図 1 2】

---

フロントページの続き

審査官 中村 康司

(56)参考文献 特開2008-117135(JP,A)

特開2003-323333(JP,A)

特開平06-278319(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00