(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4902558号

(P4902558)

(45) 発行日 平成24年3月21日(2012.3.21)

(24) 登録日 平成24年1月13日(2012.1.13)

(51) Int.Cl.

F 1

H01L 23/12 (2006.01)

H01L 23/12 501P

H01L 23/52 (2006.01)

H01L 23/12 501T

H01L 21/3205 (2006.01)

H01L 21/88 T

請求項の数 6 (全 18 頁)

(21) 出願番号 特願2008-12240 (P2008-12240)

(22) 出願日 平成20年1月23日 (2008.1.23)

(65) 公開番号 特開2008-211189 (P2008-211189A)

(43) 公開日 平成20年9月11日 (2008.9.11)

審査請求日 平成23年1月19日 (2011.1.19)

(31) 優先権主張番号 特願2007-20657 (P2007-20657)

(32) 優先日 平成19年1月31日 (2007.1.31)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100105924

弁理士 森下 賢樹

(74) 代理人 100123102

弁理士 宗田 悟志

(72) 発明者 岡山 芳央

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 柳瀬 康行

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

審査官 山本 雄一

最終頁に続く

(54) 【発明の名称】半導体モジュールの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表面に半導体素子と、この半導体素子と電気的に接続された電極と、所定の第1のパターン部とが設けられた基板を用意する第1の工程と、

第1の主面およびその反対側の第2の主面を有し、前記第1の主面から突出して設けられた突起部と前記第2の主面に設けられた所定パターンの溝部と当該溝部内に設けられた凸部とを備える金属板を用意する第2の工程と、

前記第1のパターン部とこれに対応する前記凸部とが所定の位置関係になるように金属板の位置を調整することで前記突起部と前記電極との位置合わせを行い、前記金属板の前記第1の主面側と前記基板とを絶縁層を介して圧着し、前記突起部が前記絶縁層を貫通した状態で前記突起部と前記電極とを電気的に接続する第3の工程と、

前記金属板の前記第2の主面側に所定パターンの配線層を形成する第4の工程と、

を備えることを特徴とする半導体モジュールの製造方法。

## 【請求項 2】

前記第4の工程は、前記金属板の前記第2の主面側をエッチバックして前記溝部の底部を前記第1の主面まで貫通させることにより前記金属板を所定パターンの配線層に加工していることを特徴とする請求項1に記載の半導体モジュールの製造方法。

## 【請求項 3】

前記第4の工程は、前記配線層の側面と、前記配線層の前記絶縁層と反対側の主面との間の領域が面取り形状となるように、前記金属板を加工していることを特徴とする請求項

2 に記載の半導体モジュールの製造方法。

【請求項 4】

前記第2の工程は、平板状の金属板の一方の面に前記突起部を形成する第1のステップと、前記突起部の所定の第2のパターン部を基準として前記平板状の金属板の他方の面に前記溝部および前記凸部を形成する第2のステップと、を備えていることを特徴とする請求項1に記載の半導体モジュールの製造方法。

【請求項 5】

前記半導体素子は前記基板に複数形成され、

前記溝部は複数の前記半導体素子間を区画するように設けられたスクライブ領域にさらに形成されていることを特徴とする請求項1に記載の半導体モジュールの製造方法。

10

【請求項 6】

前記第3の工程は、前記金属板の前記第1の主面側と前記基板とを加熱しながら圧着し、

前記第1のステップは、前記金属板の線膨張係数と前記基板の線膨張係数との差と、前記第3の工程における加熱温度と、前記第3の工程における加熱にともなう膨張によって移動しない前記金属板の基準点からの距離とに応じて、前記電極に対向する位置から前記金属板の膨張方向とは反対側にずらした位置に、前記突起部を形成していることを特徴とする請求項4に記載の半導体モジュールの製造方法。

【発明の詳細な説明】

【技術分野】

20

【0001】

本発明は、半導体モジュールの製造方法、半導体モジュール、携帯機器に関する。

【背景技術】

【0002】

近年、電子機器の小型化・高機能化に伴い、電子機器に使用される半導体素子（半導体モジュール）のさらなる小型化が求められている。半導体素子の小型化に伴い、配線基板に実装するための電極間の狭ピッチ化が不可欠となっている。半導体素子の表面実装方法として、半導体素子の電極にはんだバンプを形成し、はんだバンプと配線基板のパッド電極とをはんだ付けするフリップチップ実装方法が知られている。フリップチップ実装方法では、はんだバンプ自体の大きさや、はんだ付け時のブリッジ発生などが制約となり、電極の狭ピッチ化に限界があった。このような限界を克服するための方法として、金属板をハーフエッチすることによって形成した突起構造を電極またはビアとし、金属板にエポキシ樹脂などの絶縁層を介して半導体素子を装着し、突起構造に半導体素子の電極を接続する方法が知られている（特許文献1および特許文献2参照）。

30

【特許文献1】特開平9-289264号公報

【特許文献2】特開2000-68641号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

ところで、突起構造を絶縁層に埋め込むようにして金属板、絶縁層、及び半導体素子を積層して一体化する際には、突起構造と半導体素子の電極との位置合わせ（アライメント）を行う必要がある。従来の製造技術においては、金属板側にドリルによってアライメント用貫通孔を設け、金属板の貫通孔とこれを通して認識される半導体素子上のアライメントマークとにより金属板の突起構造と半導体素子の電極との位置合わせを行っている。さらに、リソグラフィ技術とエッチング技術により金属板を所定の配線パターンに加工する際にも、こうしたアライメント用貫通孔を用いて位置合わせを行っている。しかしながら、ドリル加工の微細化限界およびその加工精度の低さためにアライメント精度の向上が難しく、製造マージン（位置合わせマージン）の低減による半導体素子（半導体モジュール）の微細化に対応してその低コスト化を図ることが困難であった。また、ドリル加工自体も処理工程の増加となり半導体素子（半導体モジュール）の製造コスト増の一因となって

40

50

いた。

#### 【0004】

本発明はこうした課題に鑑みてなされたものであり、その目的は、金属板の突起構造と半導体素子の電極とを対向させた状態で接続する際の位置合わせ精度を向上させるとともに、半導体モジュールの製造コストの低減を図る技術の提供にある。

#### 【課題を解決するための手段】

#### 【0005】

上記課題を解決するために、本発明のある態様は半導体モジュールの製造方法である。この半導体モジュールの製造方法は、表面に半導体素子と、この半導体素子と電気的に接続された電極と、所定の第1のパターン部とが設けられた基板を用意する第1の工程と、第1の主面およびその反対側の第2の主面を有し、第1の主面から突出して設けられた突起部と第2の主面に設けられた所定パターンの溝部とを備える金属板を用意する第2の工程と、第1のパターン部とこれに対応する溝部が所定の位置関係になるように金属板の位置を調整することで突起部と電極との位置合わせを行い、金属板の第1の主面側と基板とを絶縁層を介して圧着し、突起部が絶縁層を貫通した状態で突起部と電極とを電気的に接続する第3の工程と、金属板の第2の主面側に所定パターンの配線層を形成する第4の工程と、を備えることを特徴とする。

#### 【0006】

上記構成において、第4の工程は、金属板の第2の主面側をエッチバックして溝部の底部を第1の主面まで貫通させることにより金属板を所定パターンの配線層に加工していくてもよい。

#### 【0007】

上記構成において、第4の工程は、配線層の側面と、配線層の絶縁層と反対側の主面との間の領域が面取り形状となるように、金属板を加工していくてもよい。

#### 【0008】

上記構成において、第2の工程は、平板状の金属板の一方の面に突起部を形成する第1のステップと、突起部の所定の第2のパターン部を基準として平板状の金属板の他方の面に溝部を形成する第2のステップと、を備えていてもよい。

#### 【0009】

上記構成において、半導体素子は基板に複数形成され、溝部は複数の半導体素子間を区画するように設けられたスクライブ領域にさらに形成されていてもよい。

#### 【0010】

上記構成において、第3の工程は、金属板の第1の主面側と基板とを加熱しながら圧着し、第1のステップは、金属板の線膨張係数と基板の線膨張係数との差と、第3の工程における加熱温度と、第3の工程における加熱にともなう膨張によって移動しない金属板の基準点からの距離とに応じて、電極に対向する位置から金属板の膨張方向とは反対側にずらした位置に、突起部を形成していくてもよい。

#### 【0011】

また、本発明の別の態様は半導体モジュールである。この半導体モジュールは、突起部が設けられた配線層と、表面に半導体素子と、この半導体素子と電気的に接続されるとともに突起部に対応するように配置された電極とが設けられた基板と、配線層と基板との間に設けられた絶縁層と、を備え、突起部が絶縁層を貫通した状態で突起部と電極とが電気的に接続され、配線層の側面と、配線層の絶縁層と反対側の主面との間の領域が面取り形状であることを特徴とする。

#### 【0012】

さらに、本発明の別の態様は携帯機器である。この携帯機器は、上述の態様の半導体モジュールを搭載したことを特徴とする。

#### 【発明の効果】

#### 【0013】

本発明によれば、金属板の突起構造と半導体素子の電極とを対向させた状態で接続する

10

20

30

40

50

際の位置合わせ精度を向上させるとともに、半導体モジュールの製造コストの低減を図る技術が提供される。

【発明を実施するための最良の形態】

【0014】

以下、本発明を具現化した実施形態について図面に基づいて説明する。なお、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0015】

(実施形態1)

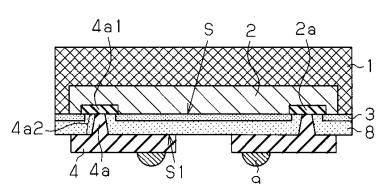

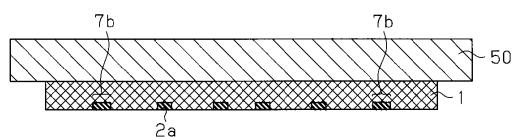

図1は本実施形態に係る半導体モジュールの概略断面図である。図1に基づいて本実施形態の半導体モジュールについて説明する。

10

【0016】

本実施形態の半導体モジュールにおける半導体基板1は、P型シリコン基板などが採用され、その表面S(下面側)に周知の技術により所定の電気回路などの半導体素子2が形成され、実装面となる表面S(特に半導体素子2の外周縁部)に半導体素子2と電気的に接続された電極2aが形成されている。この電極2aの所定の領域(中央部分)が露出するように半導体基板1の表面上の領域には保護膜3が形成されている。半導体基板1の表面Sでは、電極2aのピッチをより広くするために電極2aおよび保護膜3の上に絶縁層8が形成され、この絶縁層8を貫通して電極2aの露出面に接続する突起部4aとこの突起部4aが一体的に設けられた再配線パターン4が形成されている。突起部4aは再配線パターン4の第1の主面S1に設けられ、この第1の主面S1と反対側(下面側)の所定の領域には半導体モジュール外部との信号授受を行うための外部接続電極(はんだボール)9が設けられている。

20

【0017】

具体的には、絶縁層8は、半導体基板1の表面Sに形成され、その厚さは、たとえば、約35μmである。絶縁層8としては、加圧したときに塑性流動を引き起こす材料が好ましい。加圧したときに塑性流動を引き起こす材料としては、エポキシ系熱硬化型樹脂が挙げられる。絶縁層8に採用されるエポキシ系熱硬化型樹脂は、たとえば、温度160℃、圧力8MPaの条件下で、粘度が1kPa・sの特性を有する材料であればよい。また、温度160℃の条件下で、この材料は15MPaで加圧した場合に、加圧しない場合と比較して、樹脂の粘度が約1/8に低下する。

30

【0018】

再配線パターン4は絶縁層8の上に形成されている。再配線パターン4には第1の主面S1から突出してこの絶縁層8を貫通する突起部4aが一体的に設けられている。再配線パターン4および突起部4aには、たとえば、圧延された銅からなる圧延金属が採用される。銅からなる圧延金属は、めっき処理等によって形成された銅からなる金属膜と比較すると、機械的強度の点において強く、再配線のための材料として優れている。再配線パターン4の厚さは、たとえば、約20μmであり、突起部4aの高さ(厚さ)は、たとえば、約35μmである。突起部4aは、円錐の頂点部がその底面部と平行に取り除かれた形状(以下、「円錐台」と称する)に設けられ、半導体基板1の電極2aとの接触面と平行な先端部4a1と、先端部4a1に近づくにつれて径(寸法)が細くなるように形成された側面部4a2とを備えている。突起部4aの先端(先端部4a1)の径および基面の径は、それぞれ約35μmおよび約50μmである。また、突起部4aは電極2aに対応する位置に設けられている。突起部4aの先端(先端部4a1)は半導体基板1の電極2aと直に接するように形成され、電極2aと再配線パターン4とを電気的に接続している。

40

【0019】

なお、半導体基板1は本発明の「基板」、半導体素子2は本発明の「半導体素子」、電極2aは本発明の「電極」、突起部4aは本発明の「突起部」、溝部4bは本発明の「溝部」、絶縁層8は本発明の「絶縁層」、及び再配線パターン4は本発明の「配線層」の一例である。

50

## 【0020】

## (製造方法)

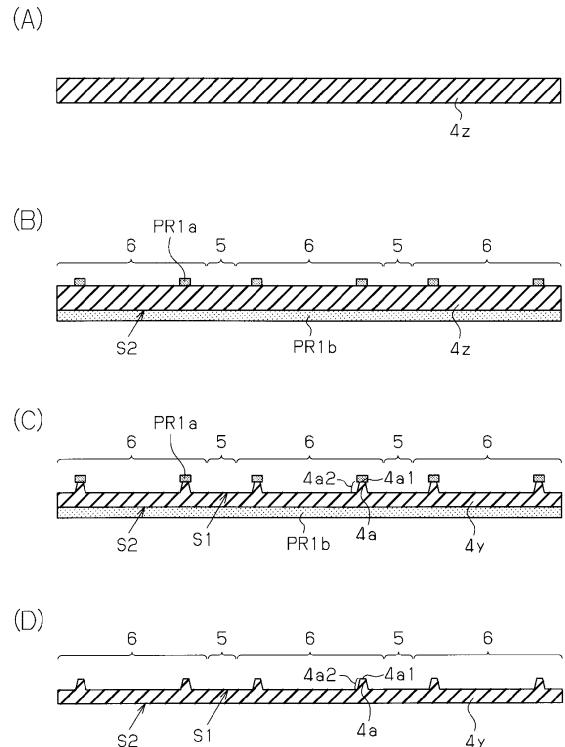

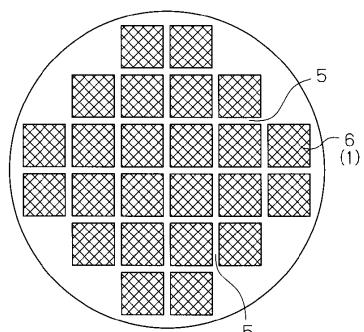

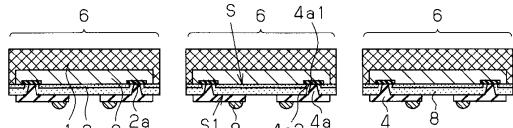

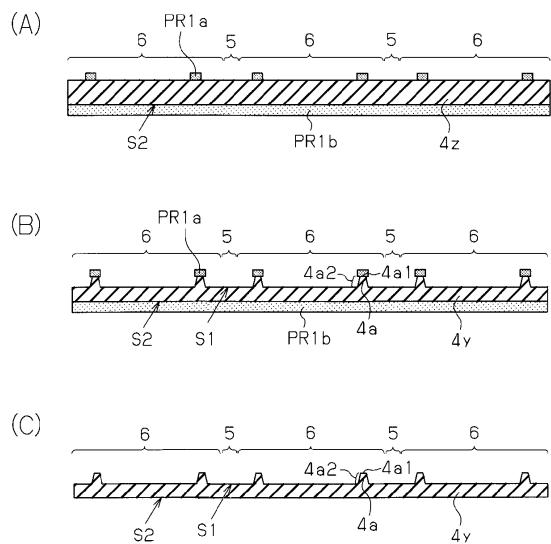

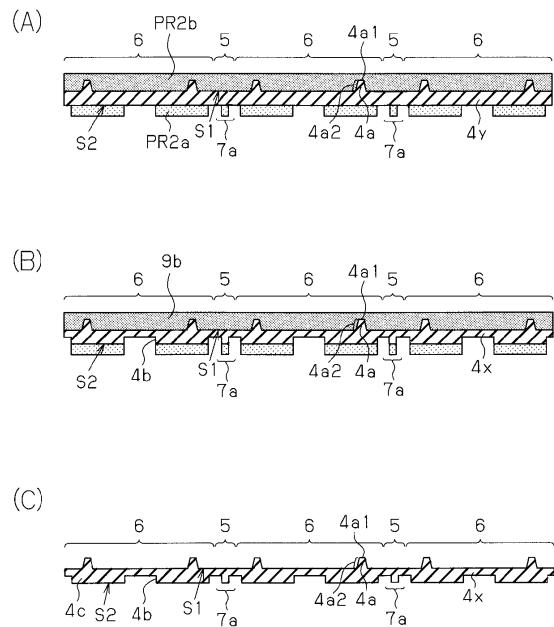

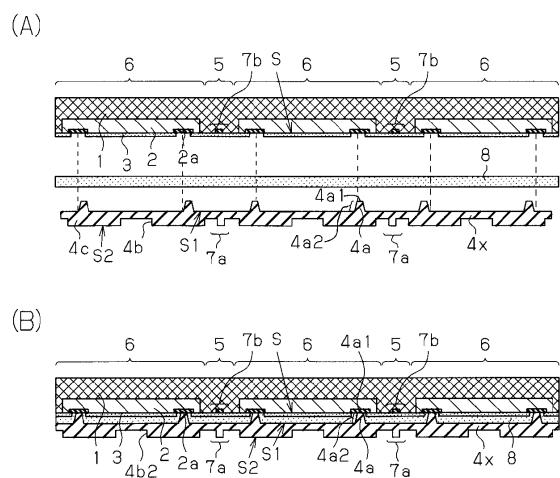

図2および図3は突起部と溝部とを有する銅板の形成方法を説明するための概略断面図である。図4は複数のスクライブラインにより区画された半導体基板がマトリクス状に配置された半導体ウエハを示す平面図(上面図)である。図5および図6は図1に示した本実施形態に係る半導体モジュールの製造プロセスを説明するための概略断面図である。次に、図1～図6を参照して本実施形態に係る半導体モジュールの製造プロセスについて説明する。

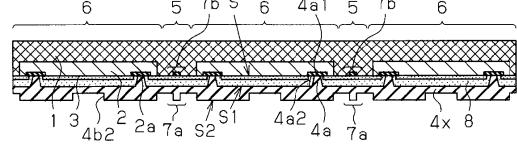

## 【0021】

まず、図2(A)に示すように、少なくとも突起部4aの高さと再配線パターン4の厚さとの和よりも大きい厚さを有する平板状の銅板4zを用意する。10 銅板4zとしては圧延された銅からなる圧延金属が採用され、銅板4zの厚さは約100μmである。なお、平板状の銅板4zは本発明の「平板状の金属板」の一例である。

## 【0022】

図2(B)に示すように、リソグラフィ技術を用いて各半導体モジュール形成領域6内における突起部形成領域にレジストマスクPR1aを形成する。ここで、突起部形成領域の配列は複数のスクライブライン5によって複数の半導体モジュール形成領域6に区画された半導体ウエハにおける半導体基板1の各電極2aの位置に対応している。また、この際、レジストマスクPR1aには、半導体モジュール形成領域6の外側(たとえば、スクライブライン5)の所定の領域(所定の位置)に位置合わせ(アライメント)用パターン部(図7参照)を合わせて形成しておく。このパターン部には、たとえば、十字形、四角形、あるいは円などの位置合せマークが採用され、そのサイズ(全長)は、たとえば、約5μm～約500μmの範囲である。そして、レジストマスクPR1aを設けた面の反対側(第2の主面S2)にレジスト保護膜PR1bを形成して銅板4zを保護しておく。なお、スクライブライン5は本発明の「スクライブ領域」の一例である。20

## 【0023】

図2(C)に示すように、レジストマスクPR1aをマスクとして塩化第二鉄溶液などの薬液を用いたウェットエッチング処理を行い、銅板4zの表面に分離溝を形成することにより、銅板4yの第1の主面S1から突出する所定の円錐台パターンの突起部4aを形成する。この際、突起部4aはその先端部4a1に近づくにつれて径(寸法)が細くなるテーパ状の側面部4a2を有するように形成される。また、突起部4aの高さは約35μmとし、突起部4aの先端(先端部4a1)の径および基面の径はそれぞれ約35μmおよび約50μmとしている。なお、上記処理においては、銅板4yの第2の主面S2側はレジスト保護膜PR1bにより保護されている。30

## 【0024】

図2(D)に示すように、レジストマスクPR1aおよびレジスト保護膜PR1bを除去する。これにより、銅板4yの第1の主面S1に対して突起部(先端部4a1およびこの先端部4a1に近づくにつれて径が細くなるように形成された側面部4a2を有する突起部)4aが一体的に形成される。また、半導体モジュール形成領域6の外側(たとえば、スクライブライン5)の所定の領域(所定の位置)には位置合わせ用パターン部(図7参照)が形成される。なお、レジストマスクPR1aに代えて銀(Ag)などの金属マスクを採用してもよい。この場合には、銅板4zとのエッチング選択比が十分確保されるため、突起部4aや位置合わせ用パターン部のパターニングのさらなる微細化を図ることが可能となる。40

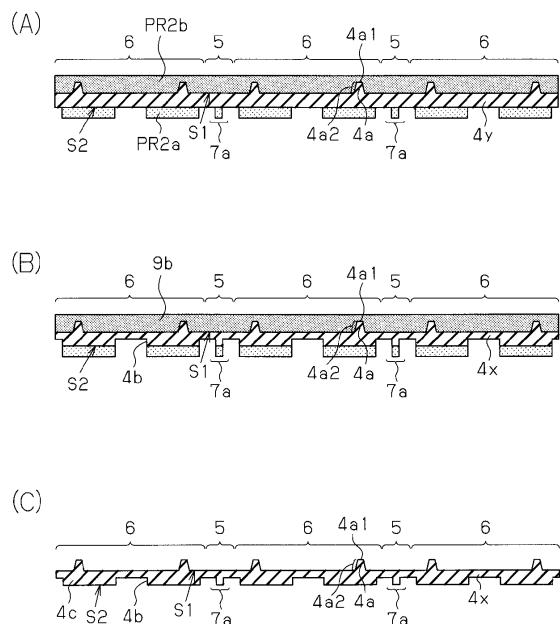

## 【0025】

次に、図3(A)に示すように、銅板4yの第1の主面S1側に設けた位置合わせ用パターン部を目印にして位置合わせを行い、リソグラフィ技術を用いて銅板4yの第2の主面S2側の溝部形成領域にレジストマスクPR2aを形成する。この際、レジストマスクPR2aには、半導体モジュール形成領域6の外側(たとえば、スクライブライン5)の所定の領域(所定の位置)に位置合わせ用パターン部7aを合わせて形成しておく。この50

位置合わせ用パターン部 7 a には、たとえば、十字形、四角形、あるいは円などの位置合わせマークが採用され、そのサイズ(全長)は、たとえば、約 5  $\mu\text{m}$  ~ 約 500  $\mu\text{m}$  の範囲である。そして、レジストマスク P R 2 a を設けた面の反対側(第1の主面 S 1)にレジスト保護膜 P R 2 b を形成して銅板 4 y を保護しておく。なお、レジストマスク P R 2 a の形成時の位置合わせ方法については後述する。

【0026】

図3(B)に示すように、レジストマスク P R 2 a をマスクとして塩化第二鉄溶液などの薬液を用いたウェットエッチング処理を行い、銅板 4 x に第2の主面 S 2 から掘り下げて設けられた溝部 4 b を形成する。ここでは、溝部 4 b の深さは約 20  $\mu\text{m}$  としている。これにより、溝部 4 b は位置合わせ用パターン部 7 a と所定のライン/スペースパターンとを有する再配線パターン 4 に対応したスペースパターンに形成される。 10

【0027】

図3(C)に示すように、レジストマスク P R 2 a およびレジスト保護膜 P R 2 b を除去する。これにより、銅板 4 x の第1の主面 S 1 から突出して設けられた突起部 4 a と第2の主面 S 2 から掘り下げて設けられた溝部 4 b と備える銅板 4 x が形成される。

【0028】

このように製造した銅板 4 x を別途用意しておき、以下に説明する本実施形態での半導体モジュールの製造プロセスに採用する。

【0029】

まず、図5(A)に示すように、表面 S に半導体素子 2 、電極 2 a 、及び保護膜 3 を有する半導体基板 1 がマトリクス状に形成された半導体ウエハを用意する。なお、半導体ウエハは、図4に示すように、複数のスクライブライン 5 によって複数の半導体モジュール形成領域 6 (半導体基板 1) に格子状に区画されている。この半導体モジュール形成領域 6 は先に述べた半導体モジュールが形成される領域である。 20

【0030】

具体的には、図5(A)に示したように、P型シリコン基板などの半導体ウエハ内のそれぞれの半導体基板 1 に対して、その表面 S (下面側) に周知の技術により所定の電気回路などの半導体素子 2 およびその周辺部に半導体素子 2 と電気的に接続された電極 2 a を形成する。そして、半導体基板 1 の表面 S に銅板 4 x の位置合わせ用パターン部 7 a に対応する領域(たとえば、スクライブライン 5)の所定の位置に位置合わせ用パターン部 7 b を形成する。この位置合わせ用パターン部 7 b には、たとえば、十字形、四角形、あるいは円などの位置合わせマークの中で、銅板 4 x の位置合わせ用パターン部 7 a と一対となるものが採用される。また、電極 2 a や位置合わせ用パターン部 7 b の材料にはアルミニウムなどの金属が採用される。そして、この電極 2 a の所定の領域(中央部分)を除いた半導体基板 1 の表面 S 上の領域に、半導体基板 1 を保護するための絶縁性の保護膜 3 を形成する。保護膜 3 としてはシリコン酸化膜(SiO<sub>2</sub>)やシリコン窒化膜(SiN)などが採用される。なお、位置合わせ用パターン部 7 b は本発明の「第1のパターン部」の一例である。 30

【0031】

そして、銅板 4 x の第2の主面 S 2 側に設けた位置合わせ用パターン部 7 a と半導体基板 1 の表面 S に設けた位置合わせ用パターン部 7 b が所定の位置関係(たとえば、両者が重なった状態)になるように銅板 4 x の位置を調整することにより、突起部 4 a と半導体基板 1 の電極 2 a との位置合わせ(重ね合わせ)を行い、半導体基板 1 (表面 S 側)と、突起部 4 a が形成された銅板 4 x (第1の主面 S 1 側)との間に絶縁層 8 を挟持する。絶縁層 8 の厚さは、突起部 4 a の高さと同程度の約 35  $\mu\text{m}$  である。なお、銅板 4 x と半導体基板 1 との位置合わせ方法については後述する。 40

【0032】

図5(B)に示すように、上記のように挟持した上で、プレス装置を用いて加圧成形することにより、半導体基板 1 、絶縁層 8 、及び銅板 4 x を一体化して積層する。プレス加工時の圧力および温度は、それぞれ約 5 MPa および 200 °C である。プレス加工により 50

、絶縁層8の粘度が低下し、絶縁層8は塑性流動を起こす。これにより、突起部4aが絶縁層8を貫通し、突起部4aと電極2aとが電気的に接続される。また、突起部4aが先端部4a1に近づくにつれて径が細くなるように形成された側面部4a2を有することにより、突起部4aが絶縁層8にスムースに貫通する。この結果、突起部4aと電極2aとの界面から絶縁層8が効果的に押し出されて絶縁層8の一部が界面に残存しにくくなる。

#### 【0033】

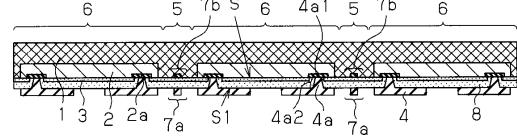

そして、エッティング技術を用いて銅板4xの第2の主面S2側を全面エッチバックすることにより、図5(C)に示すように、銅板4xを一様に薄膜化するとともに、溝部4bの底部を第1の主面S1まで貫通させる。これにより、溝部4bのスペースパターンが反映され、自己整合的に位置合わせ用パターン部7aと所定のライン/スペースパターンを有する再配線パターン4が形成される。再配線パターン4の厚さは、溝部4bの深さが反映され、約20μmである。また、再配線パターン4は、銅板4xの第2の主表面S2側を全面エッチバックすることにより形成されるため、その角部、すなわち再配線パターン4の側面と、絶縁層8と反対側の主面との間の領域がR形状などの面取り形状となっている。そのため、後述する外部接続電極(はんだボール)9を再配線パターン4に形成する前に、再配線パターン4を保護するための保護層としてたとえばフォトソルダーレジスト(図示せず)を積層する場合に、再配線パターン4間にフォトソルダーレジストが入り込みやすくなる。その結果、半導体素子2の小型化にともなって配線ピッチが微細化しても、再配線パターン4とフォトソルダーレジストとの間にボイド(空洞)が生じ難くなり、フォトソルダーレジストの剥離などを抑えることができる。

#### 【0034】

次に、図6(A)に示すように、はんだ印刷法を用いて突起部4aを介して電極2aと接続されている部分の再配線パターン4に対して半導体モジュール外部との信号授受を行うための外部接続端子として機能する外部接続電極(はんだボール)9を形成する。具体的には、樹脂とはんだ材をペースト状にした「はんだペースト」を、スクリーンマスクにより所望の箇所に印刷し、はんだ溶融温度に加熱することで外部接続電極(はんだボール)9を形成する。あるいは、別の方法として再配線パターン4側にあらかじめフラックスを塗布しておき、はんだボールを再配線パターン4にマウントしてもよい。

#### 【0035】

図6(B)に示すように、複数の半導体モジュール形成領域6を区画するスクライブライン5に沿って、半導体ウエハをダイシングすることにより半導体基板1を個別化する。この後、薬液による洗浄処理を行うことで、ダイシング時に発生する残渣などを除去する。

#### 【0036】

これらの工程により、先の図1に示した本実施形態の半導体モジュールが製造される。

#### 【0037】

以下に、本実施形態における突起部を有する金属板(銅板)に関する位置合わせ方法について説明する。

#### 【0038】

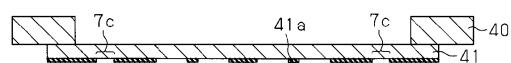

まず、図7は第1の主面に突起部を有する銅板の第2の主面に対して溝部を形成する際の位置合わせ方法を説明するための概略断面図である。

#### 【0039】

図7(A)に示すように、アライメント機能を有する露光装置においてマスクホルダ40に固定された溝部形成用マスク(所定のライン/スペースパターン41aと位置合わせ用パターン部7cが設けられたマスク)41を用いて銅板4yの第2の主面S2に溝部を形成する際、まず、溝部形成用マスク41(位置合わせ用パターン部7c)の位置合わせ用パターン部7cの像を投影し、溝部形成用マスク41(位置合わせ用パターン部7c)の下面側に設けたCCDカメラ等の撮像手段42によって撮影する。そしてこの撮影データをコンピュータに取り込んで位置合わせ用パターン部7cの画像を記憶する。

#### 【0040】

10

20

30

40

50

図7(B)に示すように、基板ホルダ43に固定された銅板4yを所定の位置に介挿する。この銅板4yには先の図2(A)~(D)で示した工程を経て第1の主面S1に突起部4aおよび位置合わせ用パターン部7dが形成され、さらに第2の主面S2にレジスト膜PR2が成膜されている。また、銅板4yはその第2の主面S2上のレジスト膜PR2を溝部形成用マスク41に対向させるように基板ホルダ43に固定されている。なお、位置合わせ用パターン部7dは本発明の「第2のパターン部」の一例である。

【0041】

そして、先と同一のCCDカメラ等の撮像手段42を用いて銅板4yの位置合わせ用パターン部7dを撮影する。

【0042】

引き続き、先の記憶した溝部形成用マスク41の位置合わせ用パターン部7cの画像を基準にして銅板4yの位置合わせ用パターン部7dの画像を重ね合わせ、両者が所定の位置関係になるように基板ホルダ43の位置を移動・調整する。このようにして銅板4yと溝部形成用マスク41と位置合わせが行われる。

【0043】

図7(C)に示すように、溝部形成用マスク41と銅板4yとを位置合わせした状態で、基板ホルダ43を溝部形成用マスク41側に移動させ、レジスト膜PR2を溝部形成用マスク41に近接または接触させて露光を行う。こうした露光の後、所定の熱処理および現像工程を経て図3(A)に示したレジストマスクPR2aが形成される。

【0044】

以上のように、露光装置のアライメント機能を採用して位置合わせを行うことができるので、容易に高精度の位置合わせが実現できる。

【0045】

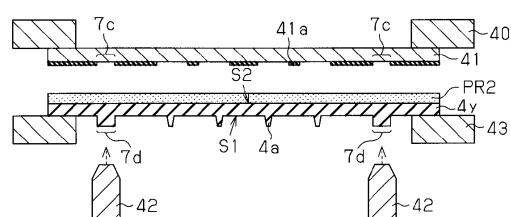

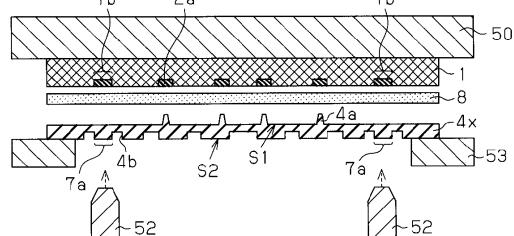

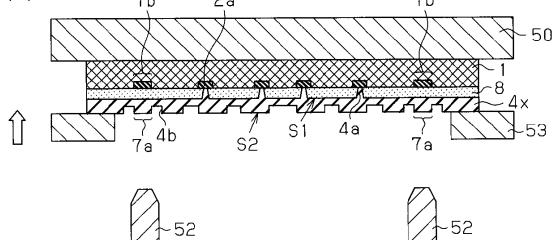

次に、図8は銅板の突起部と半導体基板の電極との位置合わせ方法を説明するための概略断面図である。

【0046】

図8(A)に示すように、アライメント機能を有する圧着装置(貼り合わせ装置)において固定ホルダ50に固定された半導体ウエハ(電極2aと位置合わせ用パターン部7b)を有する半導体基板1)の位置合わせ用パターン部7bの像を投影し、半導体ウエハ(半導体基板1)の下面側に設けたCCDカメラ等の撮像手段52によって撮影する。そしてこの撮影データをコンピュータに取り込んで位置合わせ用パターン部7bの画像を記憶する。

【0047】

図8(B)に示すように、基板ホルダ53に固定された銅板4xを所定の位置に介挿するとともに、半導体ウエハ(半導体基板1)と銅板4xとの間に絶縁層8を介在させて配置する。この銅板4xには第1の主面S1に突起部4aおよび位置合わせ用パターン部(図7参照)が形成され、さらに第2の主面S2に所定パターンの溝部4bおよび位置合わせ用パターン部7aが形成されている。そして、銅板4xはその第1の主面S1の突起部4aを半導体ウエハ(半導体基板1)に対向させた状態で基板ホルダ53に固定されている。

【0048】

そして、先と同一のCCDカメラ等の撮像手段52を用いて銅板4xの位置合わせ用パターン部7aを撮影する。

【0049】

引き続き、先の記憶した半導体ウエハ(半導体基板1)の位置合わせ用パターン部7bの画像を基準にして銅板4xの位置合わせ用パターン部7aの画像を重ね合わせ、両者が所定の位置関係になるように基板ホルダ53の位置を移動・調整する。このようにして銅板4xと半導体ウエハ(半導体基板1)と位置合わせが行われる。

【0050】

図8(C)に示すように、銅板4xと半導体ウエハ(半導体基板1)とを位置合わせし

10

20

30

40

50

た状態で、基板ホルダ 5 3 を半導体ウエハ（半導体基板 1 ）側に移動させ、銅板 4 x を半導体ウエハ（半導体基板 1 ）に絶縁層 8 を介して圧着する。この際、突起部 4 a が絶縁層 8 を貫通することにより突起部 4 a と半導体基板 1 の電極 2 a とが電気的に接続される。なお、位置合わせを行った後、別の装置にて圧着処理を行ってもよい。

#### 【 0 0 5 1 】

このようにして先の図 5 ( A ) および図 5 ( B ) で示した工程が処理され、圧着装置（貼り合わせ装置）のアライメント機能を採用して位置合わせを行うことができるので、容易に高精度の位置合わせが実現できる。

#### 【 0 0 5 2 】

本実施形態の半導体モジュールの製造方法によれば、以下の効果を得ることができる。

10

#### 【 0 0 5 3 】

( 1 ) 第 1 の主面 S 1 に突起部 4 a を有する銅板 4 x においてその反対側の第 2 の主面 S 2 に溝部 4 b を設け、こうした銅板 4 x を半導体基板 1 に圧着する際、溝部 4 b を位置合わせのための目印として利用することで、従来のドリル加工による位置合わせ用パターン部（アライメント用貫通孔）の形成工程が不要となり、半導体モジュールを低成本で製造することができる。また、位置合わせのための目印を再配線パターン 4 のスペースパターンに対応する溝部 4 b としたことで、再配線パターン 4 に対応する加工精度を利用して位置合わせを行うことができるため、従来のドリル加工による位置合わせ用パターン部（アライメント用貫通孔）を用いた位置合わせに比べて位置合わせを高精度に行うことができる。この結果、銅板 4 x の突起部 4 a と半導体基板 1 の電極 2 a との圧着の際に、突起部 4 a と電極 2 a とが高精度に位置合わせされた半導体モジュールを低成本で製造することができる。

20

#### 【 0 0 5 4 】

( 2 ) 第 1 の主面 S 1 に突起部 4 a を有する銅板 4 x においてその反対側の第 2 の主面 S 2 に再配線パターン 4 のスペースパターンに対応する溝部 4 b を設け、こうした銅板 4 x を半導体基板 1 に圧着した後、この溝部 4 b の底部を貫通させて銅板 4 x を再配線パターン 4 に加工するようにしたことで、圧着後における再配線パターン 4 の形成にリソグラフィ工程が不要となり、半導体モジュールを低成本で製造することができる。

#### 【 0 0 5 5 】

( 3 ) 第 1 の主面 S 1 に突起部 4 a を有する銅板 4 x においてその反対側の第 2 の主面 S 2 に溝部 4 b を設けたことで、少なくとも溝部 4 b 部分で銅板 4 x が薄膜化されて銅板 4 x の反りを低減することができるので、銅板 4 x と半導体基板 1 との圧着時の位置合わせ精度をさらに向上させることができる。

30

#### 【 0 0 5 6 】

( 4 ) 平板状の銅板 4 z の一方の面に突起部 4 a を形成した後、従来のドリル加工による位置合わせ用パターン部（アライメント用貫通孔）を採用せず、突起部 4 a の位置合わせ用パターン部 7 d を基準にして平板状の銅板 4 z の他方の面に溝部 4 b を形成したことで、溝部 4 b とその反対の面にある突起部 4 a との位置関係が高精度に制御される。このため、溝部 4 b を位置合わせのための目印として利用した際、突起部 4 a と半導体基板 1 の電極 2 a との位置合わせをより高精度に行うことができる。

40

#### 【 0 0 5 7 】

( 5 ) スクライブライン 5 は一般に半導体ウエハ（半導体基板 1 ）の表面に縦横に形成された複数の半導体素子 2 を個々の半導体素子 2 に区画するように囲む格子状の領域であり、半導体ウエハ（半導体基板 1 ）をダイシングして個別化する際に除去される領域である。このため、スクライブライン 5 には、溝部 4 b ( 位置合わせ用パターン部 7 a ) を半導体素子 2 の電極 2 a などの、再配線パターン 4 のレイアウトを考慮せずに設けることができ、さらに別の半導体素子を新たに製造する場合にも共通化して利用することが可能となる。したがって、銅板 4 x の溝部 4 b ( 位置合わせ用パターン部 7 a ) を複数の半導体素子 2 間を区画するスクライブライン 5 にさらに形成したことで、銅板 4 x と半導体基板 1 との圧着の際に突起部 4 a と電極 2 a との位置合わせ精度が向上した半導体モジュール

50

をさらに低成本で製造することができる。

【0058】

(6) 半導体モジュールが個別化される前の半導体ウエハの状態で一括して突起部4aおよび溝部4bを有する銅板4xを圧着して再配線パターン4を形成したので、半導体モジュールごとに個別に銅板4xを圧着して再配線パターン4などを形成する場合に比べて、半導体モジュールの製造コストを低減することができる。

【0059】

(7) 本製造方法によれば、銅板4xの突起部4aと半導体基板1の電極2aとの位置合わせを高精度に行うことができるので、それらの位置合わせマージンを低減することができ、たとえば、半導体基板1の電極2aのサイズ(寸法)を微細化することが可能となる。このため、半導体モジュールを小型化することができる。

10

【0060】

(8) 再配線パターン4は、その側面と、絶縁層8と反対側の主面との間の領域が面取り形状となっているため、再配線パターン4を保護するための保護層を積層する場合に、再配線パターン4間に保護層が入り込みやすくなる。そのため、半導体素子2の小型化にともなって配線ピッチが微細化しても、再配線パターン4と保護層との間にボイド(空洞)が生じ難くなり、保護層の剥離などを抑えることができ、その結果、半導体モジュールの実装信頼性が向上する。

【0061】

(実施形態2)

20

上述の実施形態1では、銅板4zにおける半導体基板1の各電極2aに対応した位置に突起部4aを形成したが、本実施形態では銅板4xと半導体基板1のそれぞれの線膨張係数の差異と、銅板4xと半導体基板1の圧着時の加熱温度と、加熱にともなう膨張によって移動しない銅板4xの基準点からの距離とを考慮した位置に突起部4aを形成した点が実施形態1と異なる。以下、本実施形態について説明する。なお、実施形態1と同様の構成、方法については、同一の符号を付し、その説明は省略する。

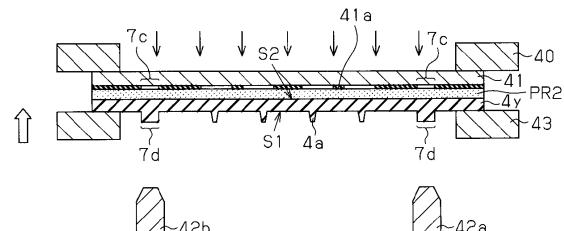

【0062】

図9および図10は本実施形態に係る突起部と溝部とを有する銅板の形成方法を説明するための概略断面図である。図11は本実施形態に係る半導体モジュールの製造プロセスを説明するための概略断面図である。

30

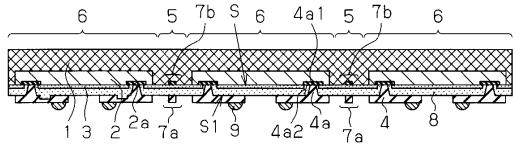

【0063】

図9(A)に示すように、リソグラフィ技術を用いて、用意した銅板4zの所定の突起部形成領域にレジストマスクPR1aを形成する。所定の突起部形成領域は、後述する突起部4aと溝部4bと備える銅板4xの線膨張係数と半導体基板1の線膨張係数との差と、銅板4xと半導体基板1との圧着時の加熱温度と、加熱にともなう膨張によって移動しない銅板4xの基準点からの距離とに応じて、電極2aに対向する位置から銅板4xの膨張方向とは反対側にずらした位置となっている。ここで、銅板4xおよびシリコンからなる半導体基板1の線膨張係数は、それぞれ約17 ppm/および約3 ppm/である。また、加熱にともなう膨張によって移動しない基準点は、通常、銅板4xの中心点である。

40

【0064】

本実施形態では、図4に示すように、複数のスクライブライン5により区画された半導体基板1がマトリクス状に配置された半導体ウエハに銅板4xを圧着している。そこで、スクライブライン5の幅を、銅板4xの線膨張係数と半導体基板1の線膨張係数との差と、圧着時の加熱温度とに応じた距離だけ狭くしている。すなわち、本実施形態では、半導体基板1に対応する銅板4xの区画単位で銅板4xの突起部4aを半導体ウエハの中心方向内側にずらしている。また、半導体ウエハの中心点に対応する銅板4xの点を、加熱にともなう膨張によって移動しない基準点とし、また各スクライブライン5の幅を狭くしている。そのため、基準点から離れた銅板4xの区画ほど中心方向への移動距離が大きくなり、すなわち突起部4aは区画単位で基準点からの距離に応じた距離だけずれることとな

50

る。具体的には、たとえば半導体基板1の大きさが一辺10mmであった場合、各スクライブライン5の幅を10μm狭くしている。なお、図9では、中央の半導体モジュール形成領域6にある銅板4zの区画を半導体ウェハの中央の半導体基板1に対応する区画としている。

【0065】

図9(B)に示すように、レジストマスクPR1aをマスクとしてウェットエッチング処理を行い、突起部4aを形成する。

【0066】

図9(C)に示すように、レジストマスクPR1aおよびレジスト保護膜PR1bを除去する。これにより、銅板4yの第1の主面S1に対して突起部4aが一体的に形成される。

10

【0067】

次に、図10(A)に示すように、リソグラフィ技術を用いて銅板4yの第2の主面S2側の溝部形成領域にレジストマスクPR2aを形成する。

【0068】

図10(B)に示すように、レジストマスクPR2aをマスクとしてウェットエッチング処理を行い、溝部4bを形成する。ここで、溝部4bは、突起部4aの形成領域に対応するように、銅板4xの線膨張係数と半導体基板1の線膨張係数との差と、加熱温度と、加熱により移動しない基準点からの距離に応じた距離だけ銅板4xの膨張方向とは反対側にずらした位置に形成する。本実施形態では、一辺10mmの半導体基板1に対して各スクライブライン5の幅を10μm狭くして、各半導体基板1に対応する銅板4yの区画単位で溝部4bを半導体ウェハの中心方向内側にずらしている。

20

【0069】

図10(C)に示すように、レジストマスクPR2aおよびレジスト保護膜PR2bを除去する。これにより、突起部4aと溝部4bと備える銅板4xが形成される。

【0070】

このように製造した銅板4xを別途用意しておき、以下に説明する本実施形態での半導体モジュールの製造プロセスに採用する。

【0071】

まず、図11(A)に示すように、表面Sに半導体素子2、電極2a、及び保護膜3を有する半導体基板1がマトリクス状に形成された半導体ウェハを用意する。そして、半導体基板1(表面S側)と、突起部4aが形成された銅板4x(第1の主面S1側)との間に絶縁層8を挟持する。その際、実施形態1と同様に、銅板4xの第2の主面S2側に設けた位置合わせ用パターン部7aと半導体基板1の表面Sに設けた位置合わせ用パターン部7bが所定の位置関係になるように銅板4xの位置を調整することにより、銅板4xと半導体基板1との位置合わせを行うようにしてもよい。

30

【0072】

図11(B)に示すように、プレス装置を用いて加圧成形することにより、半導体基板1、絶縁層8、及び銅板4xを一体化して積層する。これにより、突起部4aが絶縁層8を貫通し、突起部4aと電極2aとが電気的に接続される。ここで、プレス装置での加圧成形時の温度上昇によって、銅板4xおよび半導体基板1が熱膨張する。前述の通り、突起部4aは銅板4xおよび半導体基板1の線膨張係数の差と、加熱温度と、加熱により移動しない基準点からの距離に応じた距離だけずらした位置に形成されているため、プレス装置での加圧成形時の熱膨張により、突起部4aは電極2aに対向する位置に移動する。そのため、突起部4aと電極2aとをより高精度に位置合わせすることができ、その結果、突起部4aと電極2aとの間の接続信頼性がさらに向上する。また、溝部4bについても、突起部4aと同様の距離だけずらした位置に形成されているため、熱膨張により溝部4bは再配線パターン4に対応する位置に移動する。

40

【0073】

続く再配線パターン4の形成、外部接続電極(はんだボール)9の形成、半導体基板1

50

の個別化は、実施形態 1 と同様であり、その説明は省略する。

【 0 0 7 4 】

本実施形態の半導体モジュールの製造方法によれば、実施形態 1 の上記 ( 1 ) ~ ( 8 ) の効果に加え、以下のような効果を得ることができるようになる。

【 0 0 7 5 】

( 9 ) 銅板 4 × の線膨張係数と半導体基板 1 の線膨張係数との差と、圧着時の加熱温度と、加熱により移動しない基準点からの距離に応じた距離だけ、電極 2 a に対向する位置から銅板 4 × の膨張方向とは反対側にずらした位置に突起部 4 a を形成している。そのため、銅板 4 × の突起部 4 a と半導体基板 1 の電極 2 a との圧着の際に、突起部 4 a と電極 2 a とがより高精度に位置合わせされた半導体モジュールを製造することができ、半導体モジュールの接続信頼性をさらに向上させることができる。 10

【 0 0 7 6 】

( 実施形態 3 )

次に、本発明の各実施形態に係る半導体モジュールを備えた携帯機器について説明する。なお、携帯機器として携帯電話に搭載する例を示すが、たとえば、個人用携帯情報端末 ( P D A ) 、デジタルビデオカメラ ( D V C ) 、及びデジタルスチルカメラ ( D S C ) といった電子機器であってもよい。

【 0 0 7 7 】

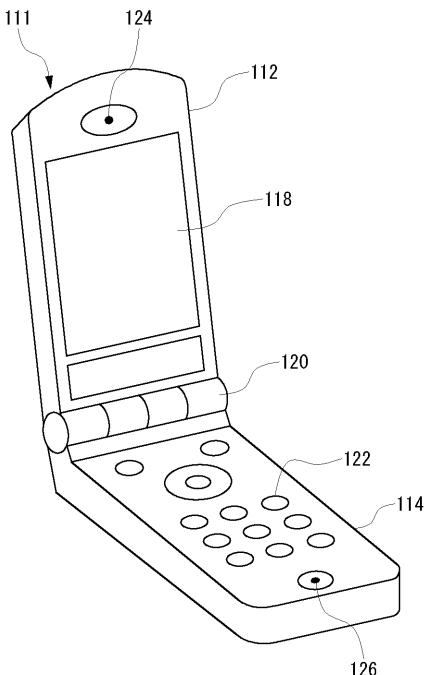

図 1 2 は本発明の実施形態に係る半導体モジュールを備えた携帯電話の構成を示す図である。携帯電話 1 1 1 は、第 1 の筐体 1 1 2 と第 2 の筐体 1 1 4 が可動部 1 2 0 によって連結される構造になっている。第 1 の筐体 1 1 2 と第 2 の筐体 1 1 4 は可動部 1 2 0 を軸として回動可能である。第 1 の筐体 1 1 2 には文字や画像等の情報を表示する表示部 1 1 8 やスピーカ部 1 2 4 が設けられている。第 2 の筐体 1 1 4 には操作用ボタンなどの操作部 1 2 2 やマイク部 1 2 6 が設けられている。なお、本発明の各実施形態に係る半導体モジュールはこうした携帯電話 1 1 1 の内部に搭載されている。 20

【 0 0 7 8 】

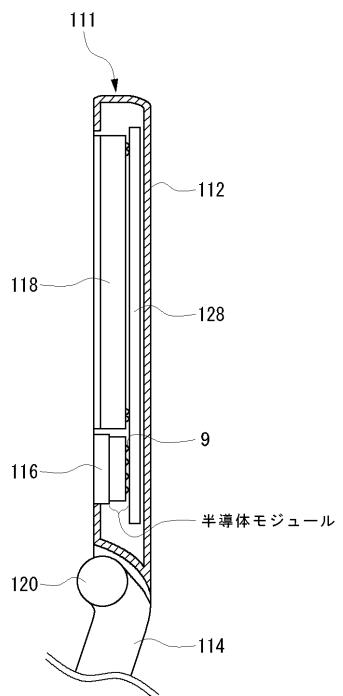

図 1 3 は図 1 2 に示した携帯電話の部分断面図 ( 第 1 の筐体 1 1 2 の断面図 ) である。本発明の各実施形態に係る半導体モジュールは、外部接続電極 ( はんだボール ) 9 を介してプリント基板 1 2 8 に搭載され、こうしたプリント基板 1 2 8 を介して表示部 1 1 8 などと電気的に接続されている。また、半導体モジュールの裏面側 ( 外部接続電極 ( はんだボール ) 9 とは反対側の面 ) には金属基板などの放熱基板 1 1 6 が設けられ、たとえば、半導体モジュールから発生する熱を第 1 の筐体 1 1 2 内部に籠もらすことなく、効率的に第 1 の筐体 1 1 2 の外部に放熱することができるようになっている。 30

【 0 0 7 9 】

本発明の実施形態に係る半導体モジュールを備えた携帯機器によれば、以下の効果を得ることができる。

【 0 0 8 0 】

( 1 0 ) 突起部 4 a と電極 2 a との間の位置合わせ精度が向上し、半導体モジュールの接続信頼性が向上するので、こうした半導体モジュールを搭載した携帯機器の信頼性が向上する。 40

【 0 0 8 1 】

( 1 1 ) 半導体モジュールの製造コストが低減されるので、こうした半導体モジュールを搭載した携帯機器の製造コストを抑制することができる。

【 0 0 8 2 】

本発明は、上記した各実施形態に限定されるものではなく、当業者の知識に基づいて各種の設計変更等の変形を加えることも可能であり、そのような変形が加えられた実施形態も本発明の範囲に含まれうるものである。

【 0 0 8 3 】

上記実施形態では、スクリュープライイン 5 内に位置合わせ用パターン部 7 b およびこれに対応する位置合わせ用パターン部 7 a を設けた例を示したが、本発明はこれに限らず、た 50

とえば、半導体モジュール形成領域 6 内に設けるようにしてもよい。この場合には上記(5)以外の効果を享受することができる。

【0084】

上記実施形態では、銅板 4 x の突起部 4 a を円錐台で、その先端部 4 a 1 に近づくにつれて径が細くなるように形成した例を示したが、本発明はこれに限らず、たとえば、所定の径(寸法)を有する円柱状の突起部であってもよい。また、突起部 4 a として丸型のものを採用したが、四角形などの多角形であってもよい。この場合にも同様の効果を享受することができる。

【0085】

上記実施形態では、半導体基板 1(半導体素子 2)の電極 2 a のピッチをより広くするために、突起部 4 a を絶縁層 8 に埋め込むようにして銅板 4 x、絶縁層 8、及び半導体素子 2 を積層させて再配線パターン 4 を形成し、その裏面側に外部接続電極(はんだボール)9 を設けた例を示したが、本発明はこれに限らず、たとえば、突起部と溝部とを有する銅板を用いて配線層を繰り返し形成して多層化するようにしてもよい。これによれば、配線層と突起部(ピアコンタクトに相当)との位置合わせ精度が向上した多層配線とすることができる。

【図面の簡単な説明】

【0086】

【図1】実施形態1に係る半導体モジュールの概略断面図である。

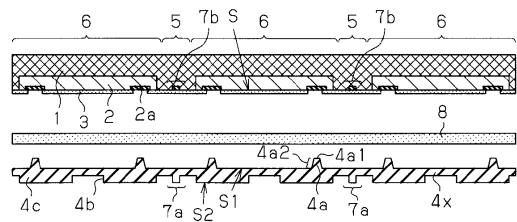

【図2】図2(A)～(D)は突起部と溝部とを有する銅板の形成方法を説明するための概略断面図である。

【図3】図3(A)～(C)は突起部と溝部とを有する銅板の形成方法を説明するための概略断面図である。

【図4】複数のスクライブライインにより区画された半導体基板がマトリクス状に配置された半導体ウエハを示す平面図である。

【図5】図5(A)～(C)は半導体モジュールの製造プロセスを説明するための概略断面図である。

【図6】図6(A), (B)は半導体モジュールの製造プロセスを説明するための概略断面図である。

【図7】図7(A)～(C)は位置合わせ方法を説明するための概略断面図である。

【図8】図8(A)～(C)は位置合わせ方法を説明するための概略断面図である。

【図9】図9(A)～(C)は実施形態2に係る突起部と溝部とを有する銅板の形成方法を説明するための概略断面図である。

【図10】図10(A)～(C)は突起部と溝部とを有する銅板の形成方法を説明するための概略断面図である。

【図11】図11(A), (B)は半導体モジュールの製造プロセスを説明するための概略断面図である。

【図12】実施形態3に係る携帯電話の構成を示す図である。

【図13】携帯電話の部分断面図である。

【符号の説明】

【0087】

1 半導体基板、 2 半導体素子、 2 a 電極、 3 保護膜、 4 再配線パターン、 4 a 突起部、 4 a 1 突起部の先端部、 4 a 2 突起部の側面部、 4 b 溝部、 5 スクライブライイン、 6 半導体モジュール形成領域、 7 a, 7 b 位置合わせ用パターン部、 8 絶縁層、 9 外部接続電極(はんだボール)。

【図1】

【図2】

【図3】

【図4】

【図5】

(A)

(B)

(C)

【図6】

(A)

(B)

【図7】

(A)

(B)

(C)

【図8】

(A)

(B)

(C)

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(56)参考文献 特開2006-310530(JP, A)

国際公開第98/043289(WO, A1)

特開2001-223287(JP, A)

特開2001-053195(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12 - 23/15

H05K 3/46

H01L 21/3205

H01L 23/52