(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4188321号

(P4188321)

(45) 発行日 平成20年11月26日(2008.11.26)

(24) 登録日 平成20年9月19日(2008.9.19)

(51) Int.Cl.

HO2H 9/02 (2006.01)

F 1

HO2H 9/02

E

請求項の数 4 (全 9 頁)

(21) 出願番号 特願2004-551482 (P2004-551482)

(86) (22) 出願日 平成15年9月29日 (2003.9.29)

(65) 公表番号 特表2006-506038 (P2006-506038A)

(43) 公表日 平成18年2月16日 (2006.2.16)

(86) 國際出願番号 PCT/US2003/030722

(87) 國際公開番号 WO2004/045037

(87) 國際公開日 平成16年5月27日 (2004.5.27)

審査請求日 平成18年7月13日 (2006.7.13)

(31) 優先権主張番号 10/287,831

(32) 優先日 平成14年11月5日 (2002.11.5)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 300057230

セミコンダクター・コンポーネンツ・イン

ダストリーズ・リミテッド・ライアビリテ

ィ・カンパニー

アメリカ合衆国 アリゾナ州 85008

フェニックス イースト・マクドウェル

・ロード5005

(74) 代理人 100091915

弁理士 本城 雅則

(74) 代理人 100099106

弁理士 本城 吉子

(72) 発明者 ボール, アラン

アメリカ合衆国 アリゾナ州 85296

ギルバート イースト・ホースシュー・

アベニュー530

最終頁に続く

(54) 【発明の名称】集積突入電流リミッタ回路および方法

## (57) 【特許請求の範囲】

## 【請求項1】

突入電流リミッタ回路において、

制御信号に応答して動作し、供給電圧を受け取るために入力ノードに結合された第1ソース、および、前記突入電流リミッタ回路の出力ノードに結合されたドレインを有する第1トランジスタであって、前記出力ノードは、前記供給電圧を同時に供給する電源に差込むために構成されており、前記ドレインは、保護信号として前記出力ノードへ前記供給電圧の負荷電流をルートするため結合される、第1トランジスタと、

前記制御信号に応答して動作し、前記第1ソースに比例縮小し、かつ、センス電流として前記出力ノードに前記負荷電流の一部をルートするために前記入力ノードに結合された第2ソースを有する第2トランジスタであって、前記第2トランジスタは、前記第1トランジスタのゲートと共に通するゲートを有する、前記第2トランジスタと、

前記センス電流を受取り、それに応じて前記第1トランジスタを通して流れる電流の最大値を動作可能に制限する制御信号を形成するために構成される検出回路であって、前記最大値はゼロより大きい、検出回路と、

から構成されることを特徴とする突入電流リミッタ回路。

## 【請求項2】

前記検出回路を形成するための第1表面、および、前記第1トランジスタの前記ドレインを形成するための第2表面を有する半導体基板をさらに含み、

前記第1トランジスタの前記ドレインおよび前記第2トランジスタのドレインは、前記

半導体基板の共通領域内に形成され、

前記第1および第2トランジスタは、前記制御信号を受信するために前記検出回路の出力に結合された共通ゲートを有する、

ことを特徴とする請求項1記載の突入電流リミッタ回路。

【請求項3】

第1および第2ノードを結合するための突入電流リミッタにおいて、

第1および第2表面を有する半導体基板と、

制御信号を受信するための制御電極、前記第1表面上に形成され、かつ前記第1ノードに結合された第1および第2ソース、および、前記突入電流リミッタの出力ノードに動作可能に結合されたドレインを有するミラー・トランジスタであって、前記出力ノードは、供給電圧を同時に供給する電源に差込むために構成されており、前記ドレインは、前記第2ノードへ電流をルートするために前記第2表面上に形成され、センス信号は、前記第2ソースを経由して流れる電流の一部により生成される、ミラー・トランジスタと、

前記半導体基板の前記第1表面上に形成された検出回路であって、前記検出回路は、前記センス信号を受信するために構成され、それに応答して、前記ミラー・トランジスタの前記制御電極に結合され、かつ、前記ミラー・トランジスタを経由して流れる電流の最大値を前記ミラー・トランジスタを不能にしないで動作可能に制限する前記制御信号を生成する、検出回路と、

から構成されることを特徴とする突入電流リミッタ。

【請求項4】

前記第2ソースと前記第1ノードとの間に結合されたレジスタをさらに含み、

前記第2ソースが前記検出回路の入力に結合される、

ことを特徴とする請求項3記載の突入電流リミッタ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に半導体デバイスに関し、より詳しくは、電源バス上の電流サージを制限するための高電流半導体デバイスに関する。

【背景技術】

【0002】

電気通信、ネットワーク、およびコンピュータのアプリケーションは、システム全体を停止することなく、システムへ回路カードを挿入し取り出す能力、いわゆる「ホット・スワップ」と称される能力をしばしば要求する。分散型電源システムで構成されたネットワーク機器では、回路カードは、電源レールまたはバス上のノイズを減少するために、しばしば大きなフィルタ・コンデンサを含む。ホット・スワップの間、コンデンサは、もし制限されなければ、ピーク振幅の何百倍ものアンペアに達する可能性のある突入電流スパイクを生成することがあり、それによって、回路カードまたはそのコネクタが破損するおそれがある。さらに、そのような大きな突入電流は、システムにプラグインされる他の回路カードを破損し、あるいは、データ損失や他のシステム誤動作の原因となる電力障害を引き起こす場合がある。かかる有害な影響を防止するために、ホット・スワップ可能な回路カードは、典型的には突入電流制限回路で形成され、それが供給電流をルートすることによりパワーMOSFETスイッチを制御する。

【0003】

既存の突入電流リミッタでは、突入電流を指定されたレベルに制限する方法において、パワーMOSFETスイッチの制御のために多くのコンポーネントを必要とすることから、コストが高いという欠点があった。ほとんどの突入電流リミッタは、パワーMOSFETスイッチと並列に結合された低値のセンス・レジスタを使用して供給電流のピーク値を制限する。しかしながら、スイッチおよびセンス・レジスタを通る大きな電流の流れによって、信頼性に悪影響を及ぼす可能性がある大きな電力損失が生じる。

【0004】

10

20

30

40

50

従って、製造コストを削減するためにコンポーネント数を減少させる一方で、電力損失を低減することによって高い信頼性を達成できるよう突入電流リミッタに対する要求がある。

【発明の開示】

【0005】

図面中、参照番号が同一である要素は同様の機能を有する。

【0006】

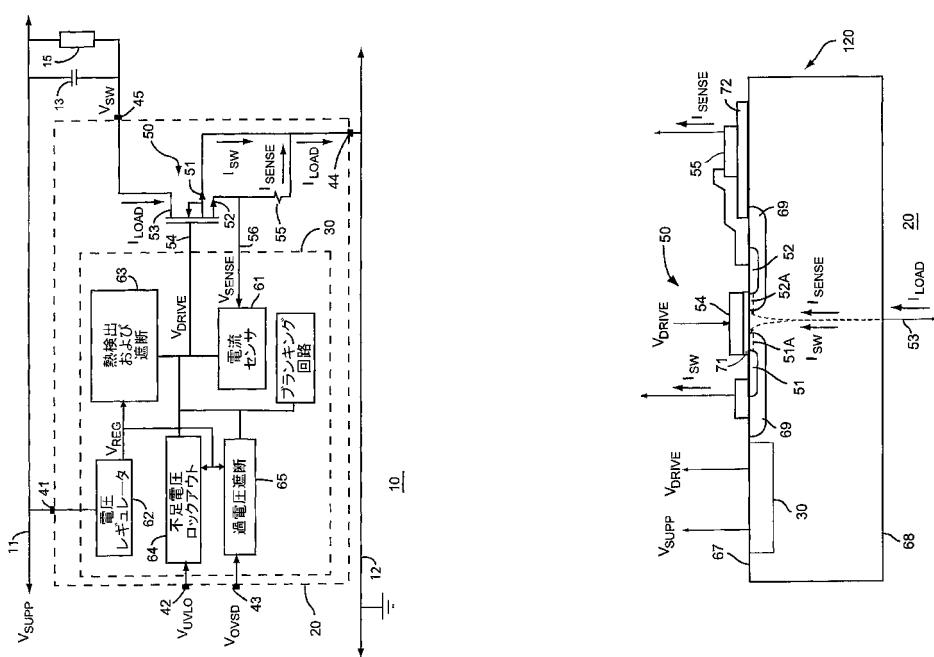

図1は、電源電圧  $V_{SUPP} = 48.0$  ボルトで動作する分散型電源バス11と接地ノード12との間に電力が加えられる間に、電子システムに差込みおよび/または引抜きをするためのホット・スワップ可能な回路カード10の単純化された概要図である。電源バス11および接地ノード12は、電子システムの他のコンポーネント(図示せず)へ同時に電力を供給していくてもよい。

10

【0007】

大きなフィルタ・コンデンサ13は、電源バス11上のノイズ・スパイクを平坦化して安定したバイアスを提供する。回路カード10の機能を実行する回路は、負荷15として示され、突入電流リミッタ回路20を経由して電源バス11から負荷電流  $I_{LOAD}$  を引き出す。ある実施例において、負荷15は、コンデンサ13および負荷15を経由して、ピーク値として負荷電流  $I_{LOAD} = 10.0$  アンペアを流す電圧レギュレータを含む。 $I_{LOAD}$  の典型的な平均値は約4アンペアである。ある実施例において、コンデンサ13は、約1000マイクロファラードの値を有する。回路カードがホット・スワップされるとき、電流  $I_{LOAD}$  はコンデンサ13内に流れ  $V_{SUPP}$  の値に充電する。突入電流リミッタ回路20は、さもなければ100アンペア以上に達するであろう  $I_{LOAD}$  のピーク値を、約10アンペアの値に制限する。

20

【0008】

突入電流リミッタ20は検出回路30を含み、それによってミラー・パワー・トランジスタ50が制御され、負荷電流  $I_{LOAD}$  がコンデンサ13および負荷15ヘルートされる。ある実施例において、突入電流リミッタ20は、5個の外部リード41-45を有する集積回路として半導体基板上に形成される。

【0009】

ミラー・トランジスタ50は、パワー・ソース51、センシング・ソース52、共通ドレイン53、および共通ゲート54を有する縦型パワーMOSFETトランジスタとして形成される。パワー・ソース51およびセンシング・ソース52は、 $I_{LOAD}$  の比例成分  $I_{SW}$  および  $I_{SENSE}$  をそれぞれ導くために、ミラーされ、あるいは比例する。ある実施例において、トランジスタ50は、約1ボルトのゲート対ソース導通スレショルドを有する。ある実施例において、パワー・ソース51およびセンシング・ソース52の有効な大きさは、1000:1の比率で比例するので、電流のピーク値は、 $I_{LOAD} = 10.0$  アンペアのとき、およそ  $I_{SW} = 9.990$  アンペアおよび  $I_{SENSE} = 10.0$  ミリアンペアである。

30

【0010】

集積センス・レジスタ55は、センシング・ソース52と直列に結合され、ノード56で電流  $I_{SENSE}$  を検出することによってセンス電圧  $V_{SENSE}$  を生成する。ある実施例において、レジスタ55は、約10オームの抵抗を有するので、 $I_{SENSE} = 10.0$  ミリアンペアのとき、 $V_{SENSE}$  は約100ミリボルトの値および約1ミリワットの対応する電力消費を有する。

40

【0011】

検出回路30は、電流センサ61、電圧レギュレータ62、熱遮断回路63、不足電圧ロックアウト(UVLO)回路64、過電圧遮断(OVSD)回路65およびブランкиング回路66を含む。

【0012】

電圧レギュレータ62は、接地リード41と給電リード44との間に結合された標準分

50

路レギュレータとして形成され、検出回路30にバイアスをかけるための内部供給電圧 $V_{REG}$ を提供する。

【0013】

電流センサ61は、エラー増幅器によって $I_{LOAD}$ を間接的に検出し、フィードバック信号として $V_{SENSE}$ を受信し、かつ、ゲート54への代表駆動制御信号 $V_{DRIVE}$ を生成する。実際には、電流センサ61は、 $I_{SENSE}$ としてセンシング・ソース52を通って $I_{LOAD}$ の計測部分を経由することによって動作し、負荷電流 $I_{LOAD}$ の大きさを予め決められた最大値、例えば10アンペア、に制限するために $V_{DRIVE}$ を調整する。

【0014】

突入電流リミッタ20の動作は以下のように進行する。回路カード10のホット・スワップ挿入中に、コンデンサ13は実質的に放電され、出力電圧 $V_{SW}$ がドレイン53上でほぼ $V_{SUPP}$ のレベルに生成される。コンデンサ13は、突入電流リミッタ20に低インピーダンス負荷を示し、突入電流リミッタ20は、これに応答して $I_{LOAD}$ の予め決められた最大値、例えば10アンペア、を供給してコンデンサ13を充電する。実際には、コンデンサ13が $V_{SUPP}$ に充電されるまでトランジスタ50は定電流源として動作し、その時点では $V_{DRIVE}$ は $V_{REG}$ のレベルまで引き上げられ、ミラー・トランジスタ50は完全に導通状態である。電流制限機能のために、供給電圧 $V_{SUPP}$ の過度の負荷が回避され、したがって出力電圧 $V_{SW}$ は保護信号と称される。

【0015】

トランジスタ50で突入電流を指定された最大値に制限することによって、突入電流リミッタは、システムの誤動作を引き起こすおそれのある電源バス11上の過負荷状態を防止する。 $I_{LOAD}$ は、直接に検出されるのではなく、低値のセンス電流 $I_{SENSE}$ によってサンプリングされるので、センス・レジスタ55を通して小量の電力のみが消費され、それによって、高性能を提供する。さらに、レジスタ55は、突入電流リミッタ20の他のコンポーネントと同じダイに容易に集積されるので、外部コンポーネントの数が減少し、それによって回路カード10の全費用が低減する。

【0016】

UVLO回路64は、スレショルド比較器を含み、それが供給電圧 $V_{SUPP}$ の大きさを検出し、 $V_{SUPP}$ が予め決められたレベルを上回るまでトランジスタ50をオフ状態に維持する。予め決められたロックアウト・レベルは、リード42に結合された内部分圧器を用いてセットされ、分割電圧 $V_{UVLO}$ を提供するが、これは1つ以上の外部レジスタで調整することができる。ゲート54に結合された出力は、オープン・ドレイン配列によって形成され、不足電圧状態が検出された場合に、ゲート54をほぼ大地電位まで引き下げる。不足電圧状態が検出されるとすぐに、 $V_{SUPP}$ が第2の予め決められたシャットダウン・レベルを上回るまでヒステリシス回路類がトランジスタ50をオフ状態に維持し、それによって、急速なサイクリングおよび/または発振(oscillation)を防止する。ある実施例において、 $V_{SUPP}$ が48ボルトで動作するところでは、予め決められたロックアウト・レベルは約32ボルトの値にセットされる。

【0017】

OVSD回路64はUVLO回路63と同様の方法で動作するが、ただし、スレショルド比較器が $V_{SUPP}$ の大きさを検出し、 $V_{SUPP}$ が、1つ以上の外部レジスタで調整でき、分割された電圧 $V_{OVSD}$ をリード43で提供する内部分圧器によってセットされた第1の予め決められたシャットダウン・レベル以上に上昇した場合には、検出回路30およびトランジスタ50を不能にする点において異なる。ゲート54に結合された出力は、オープン・ドレイン配列によって形成され、過電圧状態が検出された場合に、ゲート54をほぼ大地電位まで引き下げる。一旦、過電圧状態が検出されると、 $V_{SUPP}$ が第2の予め決められたシャットダウン・レベルを下回るまでヒステリシス回路類がトランジスタ50をオフ状態に維持し、それによって、急速なサイクリングおよび/または発振を防止する。ある実施例において、 $V_{SUPP}$ が48ボルトで動作するところでは、 $V_{OVSD}$

10

20

30

40

50

D の第 1 の予め決められたシャットダウン・レベルは約 95 ボルトの値にセットされ、第 2 の予め決められたシャットダウン・レベルは約 90 ボルトの値にセットされる。

【 0018 】

熱遮断回路 63 は、検出回路 30 およびミラー・トランジスタ 50 と同じ半導体基板上に形成された温度センサを含む。温度検出回路類は、好ましくは、電源 51 に隣接して配置されるか、あるいはトランジスタ 50 のレイアウト内に埋め込まれる、すなわち、突入電流リミッタ 20 の最も熱い部分の温度を検出するために、熱が最も生成される場所付近である。温度が上位のスレショルド温度まで上昇したとき、オープン・ドレイン出力はゲート 54 をほぼ大地電位まで引き下げる。過熱状態が検出されるとすぐに、温度ヒステリシス回路類は、温度が下位のスレショルド温度以下に下がるまでミラー・トランジスタ 50 の切断状態を確保する。ある実施例において、上位のスレショルド温度は摂氏約 180 度である。また、下位のスレショルド温度は摂氏約 170 度である。

【 0019 】

プランキング回路 66 は、ホット・スワップ・カード挿入後の遅延時間中、突入電流リミッタ 20 およびトランジスタ 50 をオフ状態に維持する時定数をセットするためのレジスタ・コンデンサ・ネットワークを含む。このスタートアップ遅延は、回路カード 10 が突入電流リミッタ 20 を通って電力を受け取る前に、内部ノードを安定させておくことにより、スタートアップ誤動作を回避する。出力は、オープン・ドレイン配置を有し、スタートアップ遅延中にゲート 54 を大地電位にスイッチする。ある実施例において、遅延時間は約 2 マイクロ秒である。

【 0020 】

図 2 は、トランジスタ 50、レジスタ 55、および検出回路 30 を含む集積回路として半導体基板 120 上に形成された、突入電流リミッタ 20 の単純化した断面図である。

【 0021 】

トランジスタ 50 は、小さなダイ・エリアを達成するために、縦型装置として実装される。従って、ソース 51, 52 は基板 120 の上部表面 67 上の p 型ウェル領域内で n 型にドープされた領域として形成される。共通ゲート 54 は、下側に横たわるパワー・チャネル 51A およびセンス・チャネル 51B の導通を制御するためにゲート酸化層 71 上に形成されるが、これらのチャネルは、大地電位で動作し、かつ、図 2 の図外で相互に結合されたウェル領域 69 内に、上部表面 67 に沿って存在する。ソース 51, 52 は、図では同様のサイズを有するように示されるが、ソース 52 は、典型的には、ソース 51 よりはるかに小さい有効サイズで作られることに注意されたい。ドレイン 53 は、基板 120 の第 2 表面 68 上に形成され、その結果、電流  $I_{SW}$  および  $I_{SENSE}$  は、図示のように、表面 67 からチャネル 51A, 52A をそれぞれ通り、基板 120 を通って、表面 68 でドレイン 53 へ流れる。縦型構造のトランジスタ 50 は、低いオン抵抗および小さなダイサイズを提供し、その結果、高機能性と低製作コストを実現できる。

【 0022 】

レジスタ 55 は、表面 67 上に形成される。ある実施例において、レジスタ 55 は、図示のように、誘電層 72 上にポリシリコン層を堆積し、パターン化することにより形成される。

【 0023 】

検出回路 30 のコンポーネントもまた表面 67 上に形成されるが、レジスタ 55 の下側にあってもなくてもよい。トランジスタは、1 つ以上のウェル領域内に形成されるが、ウェル領域 69 とは別個のものでもよい。熱遮断回路 63 内の温度センサは、高精度で基板 120 の温度を検出するために、トランジスタ 50 にきわめて近接して形成される。

【 0024 】

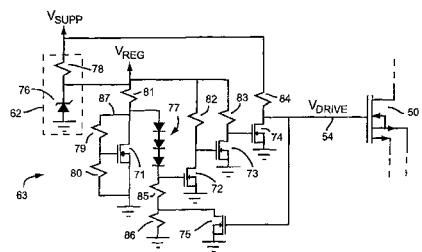

図 3 は、電圧レギュレータ 62 および熱遮断回路 63 をさらに詳細に示す概要図であり、トランジスタ 71 - 75、ツエナダイオード 76、ダイオード列 77、およびレジスタ 79 - 86 を含む。

【 0025 】

10

20

30

40

50

電圧レギュレータ 62 は、ツエナダイオード 76 の両端で内部調整電圧  $V_{REG}$  = 約 12.0 ボルトを生成する分路レギュレータとして動作する。ツエナダイオード 76 は、電圧の正の温度係数を有する。

【0026】

トランジスタ 71 およびレジスタ 79, 80 は、電圧の負の温度係数を有するノード 87 で電圧  $V_{87}$  を設定する分路レギュレータとして動作する。ある実施例において、基板 120 温度が摂氏 25 度であるとき、 $V_{87} = 2.7$  ボルトである。ダイオード列 77 の両端で降下した電圧は、温度とともに低下し、その結果、トランジスタ 72 のゲート電圧は温度とともに上昇する。

【0027】

トランジスタ 72 - 74 は、3 段階の増幅器として機能するためにレジスタ 82 - 84 と結合し、温度が上限のスレショルド・レベルに達したときに、ゲート 54 をほぼ大地電位に切り換えて、トランジスタ 50 を切斷する。ある実施例において、熱遮断温度は約摂氏約 180 度にセットされる。トランジスタ 75 およびレジスタ 85, 86 は、約摂氏 10 度の温度ヒステリシスを提供して熱発振を防止する。

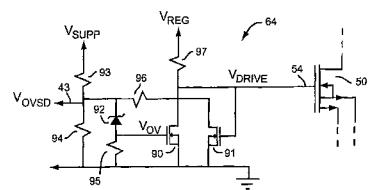

【0028】

図 4 は、過電圧遮断回路 64 をさらに詳細に示す概要図である。レジスタ 93, 94 は、供給電圧  $V_{SUPP}$  を分割してリード 43 で分割電圧  $V_{OVSD}$  を提供する分圧器として動作する。ツエナダイオード 92 は、 $V_{OVSD}$  をレベル・シフトしてトランジスタ 90 のゲートで過電圧検出信号  $V_{OV}$  を提供する。 $V_{SUPP}$  が予め決められた電圧を超過したとき、 $V_{OV}$  はトランジスタ 90 の導通スレショルドを越えるが、それによってトランジスタ 90 がオンになり、ゲート 54 を大地電位に切り換え、トランジスタ 50 がオフになり、突入電流リミッタ 20 を不能にする。トランジスタ 50 が一度切斷されると、トランジスタ 91 は、レジスタ 94 をレジスタ 96 と並列に切り換えて電圧ヒステリシスを提供し、 $V_{SUPP}$  ノイズによりゲート 50 上で生じる発振および / または不正トリガを防止する。ある実施例において、 $V_{SUPP}$  が約 95 ボルトの予め決められたレベルに達したときに、約 5 ボルトのヒステリシスを伴ってトランジスタ 50 が切斷される。リード 43 は、ユーザのために、外部レジスタを加えるための外部接続を提供し、予め決定した過電圧レベルを調整することに注意されたい。

【0029】

不足電圧ロックアウト回路 64 は、内部ロジックが形成されるという点を除いて、過電圧遮断回路 65 と同様の構造を有しており、かつ、同様の方法で動作し、その結果、 $V_{SUPP}$  が予め決められた不足電圧レベル未満であるとき、ゲート 54 が大地電位にスイッチされる。ある実施例において、予め決められた不足電圧レベルは、約 32 ボルトに設定される。

【0030】

以上を要約すると、本発明は、高い信頼性を有し、かつ低価格の突入電流リミッタ集積回路を提供する。検出回路は、センス電流に応答して制御信号を生成する。パワー・トランジスタは、制御信号に応答して動作し、供給電圧を受け取るソース、および、供給電圧の負荷電流を保護信号として出力ノードヘルートするドレインを有する。センス・トランジスタは制御信号に応答して動作し、第 1 ソースに比例し、かつ、負荷電流の一部をセンス電流として出力ノードヘルートするための入力ノードに結合されたソースを有する。

【0031】

パワー・トランジスタおよびセンス・トランジスタは、検出回路と共に半導体基板の上部表面上に形成されたそれぞれのソースおよび共通の制御電極と共に、半導体基板上に形成される。ドレインは、パワー・トランジスタおよびセンス・トランジスタの共通のドレインとして形成され、半導体基板の下部表面上に形成され、その結果、負荷電流が、基板を通って縦方向、すなわち上部表面から下部表面へ流れる。縦型の配列は、10 アンペア以上の電流をスイッチングする一方で、小さなダイ・エリアおよび低製作コストを提供する。検出回路は、過電圧および不足電圧センスおよび遮断と同様に、温度センサと遮断回

10

20

30

40

50

路を含む。その結果、本発明は高い信頼性を提供する。

【図面の簡単な説明】

【0032】

【図1】ホット・スワップ・カードを含む電子システムの概要図である。

【図2】突入電流リミッタ回路の断面図である。

【図3】分路レギュレータおよび熱検出および遮断回路を含む、突入電流リミッタの詳細を示す概要図である。

【図4】突入電流リミッタ回路の過電圧遮断回路の概要図である。

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 ブリッグス, デイビッド

アメリカ合衆国 アリゾナ州 85307 グレンデール ウエスト・フレア・ドライブ1090

0

(72)発明者 ニー, スザンナ

アメリカ合衆国 アリゾナ州 85296 ギルバート イースト・セージブラッシュ・ストリー

ト1455

(72)発明者 ロブ, スティーブン

アメリカ合衆国 アリゾナ州 85268 ファウンテン・ヒルズ ノース・サンリッジ・ドライ

ブ13530

審査官 廣瀬 文雄

(56)参考文献 特開平05-227651(JP, A)

特開平04-100276(JP, A)

特開平03-069159(JP, A)

特開昭63-318781(JP, A)

特開2000-125463(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02H 9/00-9/08