(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6352635号

(P6352635)

(45) 発行日 平成30年7月4日(2018.7.4)

(24) 登録日 平成30年6月15日(2018.6.15)

|                         |                |

|-------------------------|----------------|

| (51) Int.Cl.            | F 1            |

| HO 1 L 29/47 (2006.01)  | HO 1 L 29/48 F |

| HO 1 L 29/872 (2006.01) | HO 1 L 29/48 P |

| HO 1 L 21/329 (2006.01) | HO 1 L 29/91 A |

| HO 1 L 29/868 (2006.01) | HO 1 L 29/91 C |

| HO 1 L 29/861 (2006.01) | HO 1 L 29/91 L |

請求項の数 10 (全 12 頁) 最終頁に続く

(21) 出願番号 特願2013-552664 (P2013-552664)

(86) (22) 出願日 平成24年2月3日(2012.2.3)

(65) 公表番号 特表2014-508407 (P2014-508407A)

(43) 公表日 平成26年4月3日(2014.4.3)

(86) 國際出願番号 PCT/US2012/023724

(87) 國際公開番号 WO2012/106572

(87) 國際公開日 平成24年8月9日(2012.8.9)

審査請求日 平成27年2月2日(2015.2.2)

(31) 優先権主張番号 13/021,078

(32) 優先日 平成23年2月4日(2011.2.4)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 508121463

ヴィシェイ ジェネラル セミコンダクタ

ー、エルエルシー

VISHAY GENERAL SEMI

CONDUCTOR, LLC

アメリカ合衆国・ニューヨーク・1178

8・ホーポージ・モーター・パークウェイ

・150

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100110364

弁理士 実広 信哉

(74) 代理人 100133400

弁理士 阿部 達彦

最終頁に続く

(54) 【発明の名称】複数のフローティングゲートを有するトレンチMOSバリアショットキー(TMBS)

## (57) 【特許請求の範囲】

## 【請求項1】

第1の導電型を有する半導体基板と、

前記第1の導電型を有する基板上に形成され、前記基板より更に低濃度にドープされているエピタキシャル層と、

前記エピタキシャル層に形成される複数のフローティングゲートであって、前記エピタキシャル層に形成される複数のトレンチのそれぞれに配置される複数のフローティングゲートと、

前記エピタキシャル層及び前記トレンチ上に配置される連続した金属層と、

前記金属層と前記エピタキシャル層との間の界面で形成されるショットキー接觸と、

前記金属層上に形成される連続した第1電極、及び前記基板の裏側に形成される第2電極と、

前記トレンチのそれぞれに配置される複数の誘電体層と、

を含み、

前記複数のフローティングゲートが、隣接する誘電体層の間にそれぞれ挿入される複数の導電層を含み、

前記複数の誘電体層が、0.2 μmと2 μmとの間の厚さを有する、半導体整流器。

## 【請求項2】

前記トレンチの底部及び側壁をライニングする絶縁層をさらに含む、請求項1に記載の半導体整流器。

**【請求項 3】**

前記複数の導電層は、複数の A 1 層である、請求項 1 に記載の半導体整流器。

**【請求項 4】**

前記複数の導電層は、複数のドープされたポリシリコン層である、請求項 1 に記載の半導体整流器。

**【請求項 5】**

前記金属層がニッケルであり、前記エピタキシャル層はシリコンを含み、シリサイド層が前記ニッケルとエピタキシャル層との間の界面に形成される、請求項 1 に記載の半導体整流器。

**【請求項 6】**

第 1 の導電型の半導体ボディーを提供する段階と、

前記半導体ボディーの表面に複数のトレンチをエッチングし、メサが隣接するトレンチの間に残存するようにし、前記トレンチのそれぞれが側壁及び底部を有する、段階と、

前記トレンチのそれぞれに複数のフローティングゲートを形成する段階であって、

前記トレンチのそれぞれにおいて誘電材料及び導電材料の複数の交互層を形成する段階を含む、段階と、

前記メサの表面及び前記トレンチ上に連続した金属層を形成し、それとともにショットキー接触が形成される、段階と、

を含み、

前記複数の交互層のそれぞれを形成する段階が、前記誘電材料または導電材料を堆積及びエッチバックする段階を含み、

前記複数の誘電材料の層が、 $0.2 \mu m$  と  $2 \mu m$  との間の厚さを有する、整流器を作成する方法。

**【請求項 7】**

前記半導体ボディーは、第 1 の導電型を有する半導体基板と、前記第 1 の導電型を有する基板上に形成され、前記基板より更に低濃度にドープされているエピタキシャル層と、を含む、請求項 6 に記載の方法。

**【請求項 8】**

前記導電材料は A 1 である、請求項 6 に記載の方法。

**【請求項 9】**

前記導電材料はドープされたポリシリコンである、請求項 6 に記載の方法。

**【請求項 10】**

前記金属層はニッケルであり、エピタキシャル層はシリコンを含み、前記ニッケルとエピタキシャル層との間の界面にシリサイド層が形成される、請求項 6 に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は一般的に、半導体デバイスに関し、より具体的にはトレンチMOSデバイスのためのゲート構造に関する。

**【背景技術】****【0002】**

通常、ショットキーダイオードは、典型的に単結晶シリコンで作られた高濃度にドープされた半導体基板を含む。第 2 層がその基板を覆う。ドリフト領域と呼ばれるその第 2 層は、基板と同じ導電型のキャリアを有する材料でより少なく高濃度にドープされる。金属層または金属シリサイド層は、低濃度にドープされたドリフト領域とともにショットキー接触を形成し、ダイオードアノードを形成する。

**【0003】**

ショットキーダイオードなどのユニポーラ部品を形成する場合、2 つの対立する制約が生じる。特に、その部品は、高いブレークダウン電圧を有する一方、最も低い可能なオン状態抵抗 (the lowest possible on-state resist) を有する。

10

20

30

40

50

ance) (Ron) を示さなくてはならない。オン状態抵抗を最小化することは、より少なくドープされた層の厚さを最小化すること及びこの層のドーピングを最大化することを課す。反対に、高い逆ブレークダウン電圧を得るために、等電位面が強力に湾曲される領域の生成を回避すると同時に、より少なくドープされた層のドーピングは最小化されるべきであり、その厚さは最大化されるべきである。

#### 【0004】

これらの対立する制約を調整するために様々な解決策が提供されてきたが、それはトレンチMOSキャパシタンスショットキーダイオード構造の開発につながり、それはトレンチMOSバリアショットキー(TMBS)ダイオードと呼ばれる。このような構造の一例では、例えば高濃度にドープされたN型ポリシリコン領域などの導電性領域が、下部の基板よりもより少なく高濃度のN型でドープされた厚いドリフト領域の上部部分に形成される。絶縁層は、その厚い層から導電性領域を絶縁する。アノード層が全体の構造を覆い、絶縁された導電性領域の上部面と接触し、低濃度でドープされたドリフト領域とともにショットキー接觸を形成する。

#### 【0005】

逆バイアスされる場合、絶縁された導電性領域は、ドリフト領域内に側方枯渇(a lateral depletion)をもたらし、それはこの層における等電位面の分配を修正する。このことは、ドリフト領域のドーピングの増大を可能にし、故に逆ブレークダウン電圧に悪影響を及ぼすことなく、オン状態抵抗を低減する。

#### 【0006】

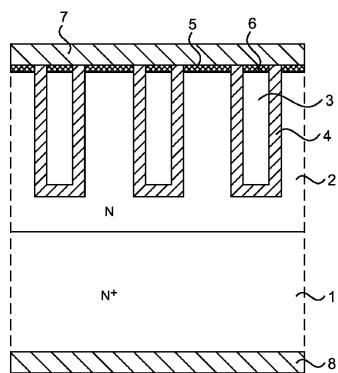

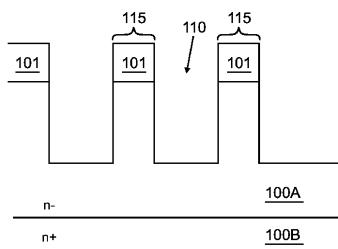

図1は、従来型TMBSショットキーダイオードまたは整流器の簡略化された部分図である。ダイオードは、その上に低濃度でドープされたN型エピタキシャル層2が形成される高濃度でドープされたN型シリコンウェハ1から形成される。このエピタキシャル層には開口が形成され、それは例えば、トレンチ形状であり得る。導電性領域3がその開口に形成され、それは例えば、ドープされたポリシリコンで作られる。絶縁層4は、各導電性領域とその対応する開口(例えばトレンチ)の壁との間に挿入される。絶縁層4は、例えば熱酸化によって形成され得、開口は、共形堆積(conformal deposition)によってポリシリコンで充填され得、その後平坦化ステップが続き得る。この後、ポリシリコン充填領域の上部の単結晶シリコン6の上部にシリサイド5を形成することができる、例えばニッケルなどの金属が堆積される。一旦シリサイドが形成されると、シリコンと反応しなかった金属は選択的エッチングによって除去される。この後、アノード金属堆積7が上部面側に形成され、カソード金属堆積8が下部面側に形成される。

#### 【0007】

平坦構造の代わりにトレンチ構造を使用することは、(略2ミクロン幅のトレンチに対して)追加で略20Vの阻止能力を作り出す。この増加は、エピタキシャル層の表面からトレンチの底部までのピーク電場の再配置及びシリコンにおける電場の再分配に起因する。この追加の阻止能力の重要性は、より高い阻止電圧に対しては低下する。例えば、20Vは80Vデバイスに対しては阻止電圧の25%の増加を示すが、180Vデバイスに対しては11%の増加を示すのみである。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0008】

本発明によると、第1の導電型を有する半導体基板を備える半導体整流器が提供される。エピタキシャル層はその基板上に形成される。エピタキシャル層は第1の導電型を有し、その基板よりも更に低濃度にドープされている。複数のフローティングゲートがそのエピタキシャル層に形成され、金属層がそのエピタキシャル層上に配置され、それらの間にショットキー接觸を形成する。第1電極が金属層の上に形成され、第2電極が基板の裏側に形成される。

#### 【0009】

本発明の別側面によると、それを含む整流器を製作する方法が提供される。その方法は

10

20

30

40

50

、第1の導電型の半導体ボディーを提供する段階と、複数のトレンチをその半導体ボディーの表面にエッティングして、メサが隣接するトレンチの間に残るようとする段階と、を含む。それぞれのトレンチは、側壁及び底部を有する。複数のフローティングゲートが、各トレンチに形成される。金属層がそのメサの表面上に形成され、それとともにショットキー接觸が形成される。

**【図面の簡単な説明】**

**【0010】**

【図1】従来型T M B Sショットキーダイオードまたは整流器の簡略化された部分図である。

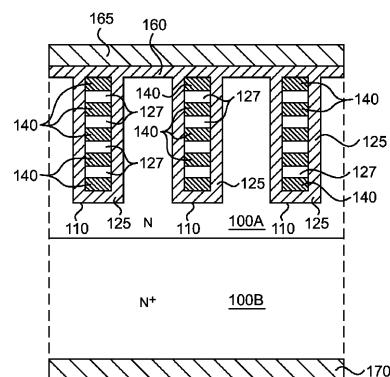

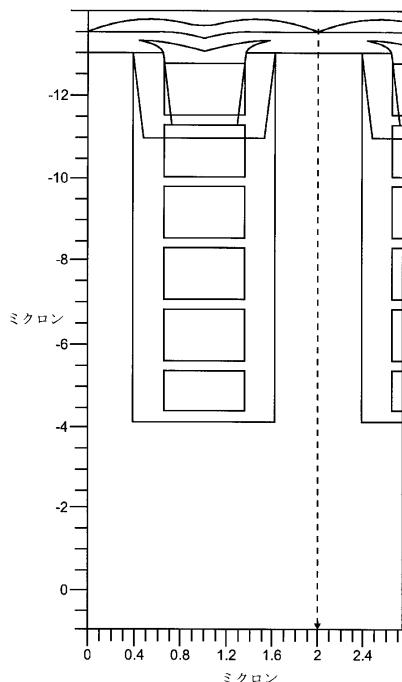

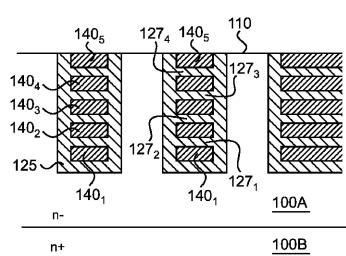

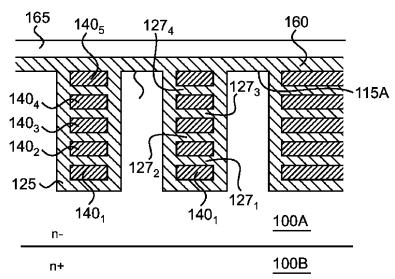

【図2】M F G T M B Sダイオードのアクティブ領域の断面図を示す。

10

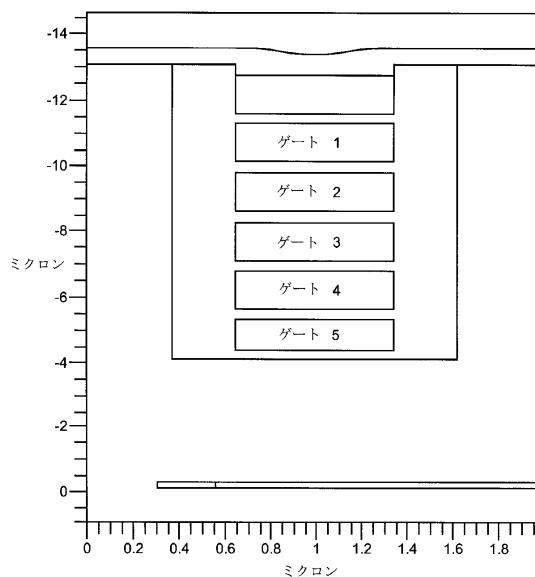

【図3a】5つのフローティングゲートを有するT M B Sダイオードを通る断面図を示す。

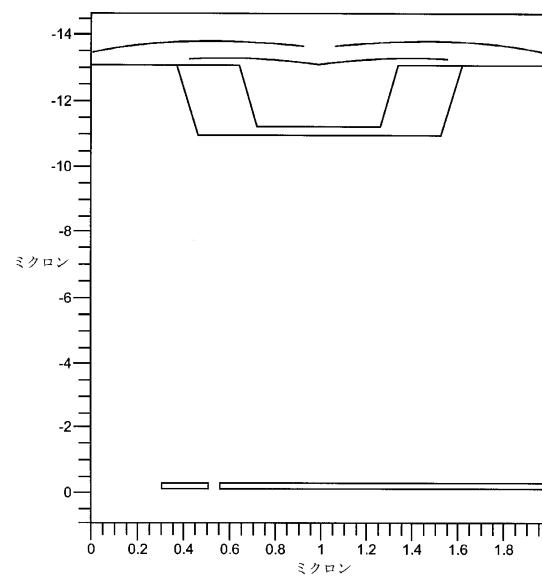

【図3b】単一のゲートのみを有するT M B Sダイオードを通る断面図を示す。

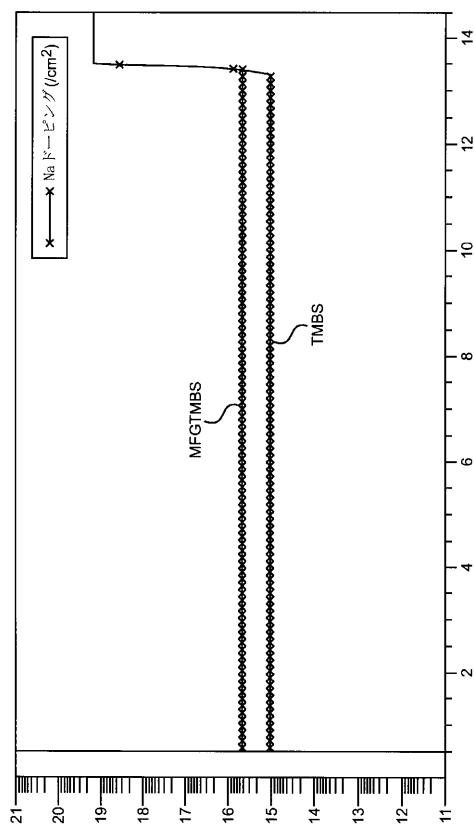

【図3c】図3a及び図3bに示された両方のダイオードに対する広がり抵抗プロファイル(s p r e a d i n g r e s i s t a n c e p r o f i l e、S P R)を示す。

【図4a】5つのフローティングゲートを有するM F G T M B Sダイオード及び単一のゲートのみを有するT M B Sダイオードを通る断面図のオーバーレイを示す。

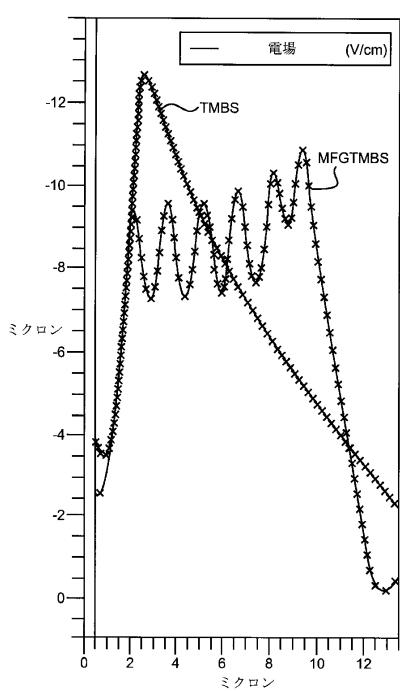

【図4b】200Vで逆バイアスされた場合の、図4aの両方のダイオードにおける電場分配を示す。

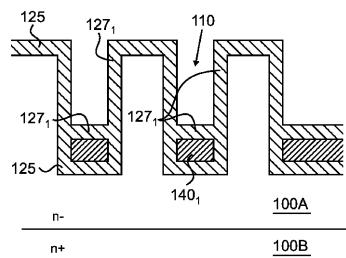

【図5】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

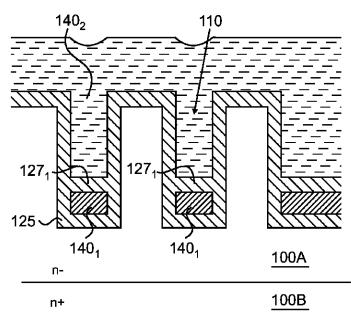

20

【図6】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

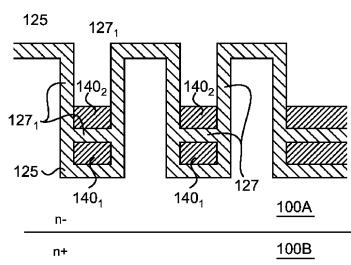

【図7】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

【図8】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

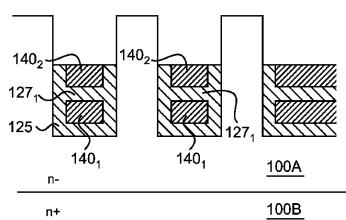

【図9】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

【図10】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

【図11】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

【図12】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

【図13】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

【図14】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

【図15】図2のデバイスを製作するのに採用され得るプロセスステップの一例を示す。

30

**【発明を実施するための形態】**

**【0011】**

以下で詳細に説明するように、トレンチM O Sバリアショットキー(T M B S)ダイオードのゲート構造は、デバイスのエピタキシャル層におけるピーク電場をさらに再配置するために修正される。このように、阻止電圧の追加的な増加が、トレンチ設計の使用によって達成され得る。特に、単一のゲート設計を使用する代わりに、複数のフローティングゲートを使用するT M B Sダイオードが提供される。このようなデバイスは、本明細書では時折、マルティプルフローティングゲートT M B S(M F G T M B S)と呼ばれる。各フローティングゲートの角での電荷結合及び場の込み合いを通じて、複数の電場がデバイスのエピタキシャル層において生成される。このことは、より高濃度でドープされたエピタキシャル層が使用され得るため、スーパージャンクションのような電場を生じさせ、より高い阻止電圧能力を有するデバイスをもたらす。

40

**【0012】**

図2は、M F G T M B Sダイオードのアクティブ領域の断面図を示す。アクティブ領域は、第1の導電型のドーパントにより高濃度でドープされた(例えばn+型の)半導体基板100Bを備える。第1のエピタキシャル層100Aは、基板100B上に形成され、第1の導電型のドーパントでより低濃度でドープされる(例えばn-型である)。1つまたは複数のトレンチ110が第1のエピタキシャル層100Aに形成される。トレンチ110は、絶縁層125で覆われている(l i n e d w i t h)。トレンチ110は、それぞれ導電材料及び絶縁材料である交互層140及び127で充填される。導電層140

50

はフローティングゲート 140 として働き、例えば金属（例えばアルミニウム）またはドープされたポリシリコンなどの導電材料から形成され得る。絶縁層 127 は、例えば SiO<sub>2</sub> などの任意の適切な絶縁材料から形成され得る。絶縁層 125 及び 127 は、同一のまたは異なる絶縁材料から形成され得る。図 2 に示された例は 5 つのフローティングゲート 140 を採用しているが、より一般的には、任意の数のフローティングゲートが採用され得る。

#### 【0013】

金属層 160 は、導電材料 140 及び第 1 のエピタキシャル層 100A の露出された面上に形成される。ショットキー接触は、金属層 160 と第 1 のエピタキシャル層 100A との間の界面に形成される。アノード金属 165 が金属層 160 上に形成される。カソード電極 170 が、半導体基板 100B の裏側に位置される。

10

#### 【0014】

複数のフローティングゲートを有する T M B S の性能の特徴を示すシミュレーションが実施された。例えば、図 3 a 及び 3 b はそれぞれ、（図 2 のような）5 つのフローティングゲートを有する T M B S ダイオードを通る断面図、及び単一のゲートのみを有する T M B S ダイオードを通る断面図を示す。図 3 c は、図 3 a 及び図 3 b に示された両方のダイオードに対する広がり抵抗プロファイル（S P R）を示す。

#### 【0015】

図 4 a は、5 つのフローティングゲートを有する M F G T M B S ダイオード及び単一のゲートのみを有する T M B S ダイオードを通る断面図のオーバーレイを示す。図 4 b は、200V で逆バイアスされた場合の、図 4 a の両方のダイオードにおける電場分配を示す。示されるように、単一ゲート T M B S ダイオードは、単一の電場のピークを有する。しかしながら、M F G T M B S ダイオードは、各フローティングゲートの角での電荷結合及び場の込み合いを通じて、電場を再分配することができ、電場において複数のピークを生成する。前述のように、このように、より高濃度でドープされたエピタキシャル層が使用され得るため、スーパージャンクションのような電場が生成され、より高い阻止電圧能力を有するデバイスをもたらす。例えば、単一ゲート T M B S ダイオードが略  $1 \times 10^{15} / cm^3$  のエピタキシャル層におけるドーパント濃度を有し得る一方、5 つのフローティングゲートを有する同一の電圧定格の M F G T M B S ダイオードの幾つかの実施形態は、略  $5 \times 10^{15} / cm^3$  のエピタキシャル層におけるドーパント濃度を有することができる。

20

#### 【0016】

電場を再配置することによって、より高濃度にドープされたエピタキシャル層はまた、デバイスの順電圧の改善をもたらす。同一の逆阻止電圧は、T M B S および M F G T M B S デバイスの両方で達成され得る一方、M F G T M B S ダイオードの場合は、チップサイズが 70% 以上低減されたデバイスが達成され得る。

30

#### 【0017】

シミュレーションはまた、メサ幅が略 1.5 ミクロンを超えるときに M F G T M B S ダイオードにおける漏れ電流密度が単一ゲート T M B S ダイオードに対するものよりも大きいことを示した。しかしながら、略 2 ミクロン未満のメサ幅を有する M F G T M B S ダイオードの実際の全体の漏れ電流は、単一ゲート T M B S ダイオードの実際の全体の漏れ電流より大きくない。例えば、1.5 ミクロンのメサ幅を有する M F G T M B S ダイオードの J R は、200V 単一ゲート T M B S ダイオードに対する  $1.5 \times 10^{-11} A / \mu m^2$  の値より高い  $2.2 \times 10^{-11} A / \mu m^2$  であるが、そのシリコンの使用は、単一ゲート T M B S ダイオードのたったの 40% である。例えば、0.6V の目標順電圧では、M F G T M B S ダイオードの全体の漏れ電流は  $(2.2 \times 10^{-11}) \times (0.4) = 8.8 \times 10^{-12} A / \mu m^2$  となり、それは 200V 単一ゲート T M B S ダイオードに対する  $(1.5 \times 10^{-11}) \times (1.0) A / \mu m^2$  の値より低い。

40

#### 【0018】

単一ゲート T M B S ダイオードでは、漏れ電流は、ゲートの深さを調整することによっ

50

て制御され得る。ショットキー漏れへの主な寄与はバリアの低下であるとみられているため、MFGTMBSDイオードの漏れ電流は、第1のフローティングゲートの深さを増加することによって低減され得、それは表面電場を低減する手助けをする。最終的に、高濃度の多数キャリアにより順コンダクタンスで操作するときにより少ない少数キャリアが存在するため、MFGTMBSDイオードのスイッチング性能は、200Vの単一ゲートTMBSDより良好であることが予期される。結果として、スイッチング速度はより速いべきである。実際に、200VのMFGTMBSDイオードのスイッチング性能は、100Vの単一ゲートのスイッチング性能と類似しているべきである。

#### 【0019】

追加のシミュレーションは、MFGTMBSDイオードにおけるメサの幅が、単一ゲートTMBSDにおいて生じるトレードオフと類似である、デバイスの逆および順性能の間のトレードオフを作り出すために変化され得ることを証明した。 10

#### 【0020】

図2のMFGTMBSDイオードを形成するのに採用され得る方法の一例が、図5～15に関連して説明される。

#### 【0021】

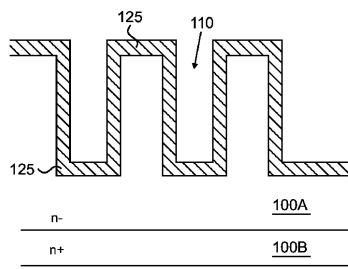

図5は、第1の導電型のドーパントを有する（例えばn-型の）第1の層100Aと、第1の導電型のドーパントでより高濃度にドーピングされている（例えばn+型の）ベース基板100Bと、を含む半導体基板100の断面図である。酸化物層101が化学蒸着（CVD）によって、例えば略2000-10,000オングストロームの厚さまで、第1の基板100A上に形成される。次に、フォトレジスト（図示せず）が酸化物層101上に覆われ、複数のトレンチ110を規定する。トレンチ110は、メサ115によって互いに間隔を隔てて配置される。 20

#### 【0022】

図6を参照すると、酸化物層101の除去の後、高温酸化プロセスが実施され、ゲート酸化物層125を形成する。ゲート酸化物層125は、幾つかの例では略150オングストロームと3000オングストロームとの間の厚さを有し、トレンチの側壁110Aおよび底部110B、並びにメサ115の表面上に形成される（図7参照）。酸化プロセスの代わりに、ゲート酸化物層125がCVD酸化物層によって形成され得る。

#### 【0023】

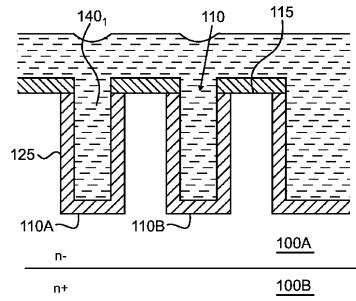

次に、図7に示されるように、第1の導電層140<sub>1</sub>がCVDによってゲート酸化物125上に形成され、トレンチ110を充填する。第1の導電層140<sub>1</sub>は、金属、ドープされたポリシリコン、またはドープされたアモルファスシリコンなどの任意の適切な材料であり得る。1つの特定の実施形態では、第1の導電層140はA1である。幾つかの実施形態では、第1の導電層140<sub>1</sub>は、略0.1から5ミクロンの厚さを有し得る。 30

#### 【0024】

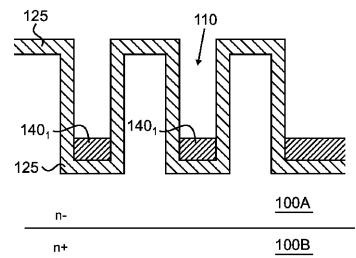

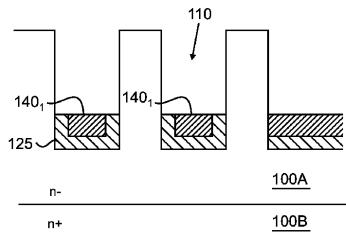

ここで図8を参照すると、異方性エッティングが実施され、トレンチ110内から過剰な第1の導電層140<sub>1</sub>を除去する。同様に、図9では、ゲート酸化物層125は、その上部面が第1の導電層140<sub>1</sub>の上部面と概して共平面になるようにエッティングされる。このエッティングプロセスの後、図10では、第1の誘電体層127<sub>1</sub>が第1の導電層140<sub>1</sub>上でトレンチ110内に形成される。誘電体層127<sub>1</sub>は、例えばSiO<sub>2</sub>などの任意の適切な材料から形成され得る。第1の誘電体層127<sub>1</sub>は次いで、異方的にエッティングされ、第1の導電層140<sub>1</sub>上でその厚さを低減する。幾つかの実施形態では、第1の誘電体層127<sub>1</sub>は、0.2と2ミクロンの間の厚さに低減され得る。 40

#### 【0025】

第1の導電層140<sub>1</sub>は、図2に示される第1のフローティングゲートとして機能する。図7～9に示されるプロセスは、後に形成される追加のフローティングゲートのそれぞれに対して繰り返される。例えば、図11では、第2の導電層140<sub>2</sub>が、第1の誘電体層127<sub>1</sub>上で形成され、図12でエッチバックされる。次に、図13に示される（かつ、図9に類似する）ように、第1の誘電体層127<sub>1</sub>は、その上部面が第2の導電層14 50

$0_2$  の上部面と概して共平面となるようにエッティングされる。図 14 は、5 つの導電層  $140_1 - 140_5$  が形成された後の結果を示す。

#### 【0026】

次に、図 15 では、フローティングゲートの形成後、スパッタリングまたは他の適切なプロセスが実施され、メサ  $115$  上にショットキー接触領域  $115A$  を形成するように導電層  $160$  を堆積する。導電層  $160$  は、下部の第 1 の層  $100A$  とともにショットキーダイオードを形成することができる任意の材料から形成され得る。例えば、導電層  $160$  は、金属シリサイド層であり得る。

#### 【0027】

その方法には、導電体を堆積およびエッティングしてダイオードアノード電極  $165$  を形成する段階が続き、それは導電層  $160$  と同一の空間に延在し得る。同様に、カソード電極  $170$  は、基板  $100B$  の裏側に形成される。

#### 【0028】

上記の例および開示は、例示を目的とするものであり、包括的なものではない。これらの例および説明は、当業者に多くの変形物および代替物を示唆するであろう。すべてのこれらの代替物および変形物は、添付の請求項の範囲内に含まれることが意図される。当該技術分野に精通している者は、本明細書に記載された特定の実施形態の他の相当実施形態を認識することができ、相当実施形態はまた、これに添付された請求項によって包含されることが意図される。

#### 【符号の説明】

#### 【0029】

$100A$  第 1 のエピタキシャル層

$100B$  半導体基板

$101$  酸化物層

$110$  トレンチ

$115$  メサ

$125$  絶縁層

$127$  絶縁層、誘電体層

$140$  導電層

$160$  金属層（導電層）

$165$  アノード金属（ダイオードアノード電極）

$170$  カソード電極

10

20

30

【図1】

FIG. 1

【図2】

FIG. 2

【図3 a】

【図3 b】

【図 3 c】

【図 4 a】

【図 4 b】

【図 5】

FIG. 5

【図 6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

【図13】

FIG. 13

【図14】

FIG. 14

【図 15】

FIG. 15

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/06 (2006.01) H 01 L 29/06 301D

H 01 L 29/06 301V

(72)発明者 ルン - チン・カオ

台湾・台北市・シティー・ウェン・シャン・ディストリクト・ム・シン・ロード・セクション・

3・レーン・232・アレー・6・ナンバー・18・4エフ

審査官 杉山 芳弘

(56)参考文献 特開2002-083963 (JP, A)

特開2005-354056 (JP, A)

特開2004-140086 (JP, A)

国際公開第2010/096261 (WO, A1)

特表2002-538602 (JP, A)

特開2006-237066 (JP, A)

特開2010-129973 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 872

H 01 L 29 / 868

H 01 L 29 / 78

H 01 L 21 / 336

H 01 L 29 / 06