등록특허 10-2150183

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2020년08월31일

(11) 등록번호 10-2150183

(24) 등록일자 2020년08월25일

- (51) 국제특허분류(Int. Cl.)

*H03M 13/00* (2017.01) *H03M 13/11* (2006.01)

- (52) CPC특허분류

*H03M 13/6393* (2013.01)

*H03M 13/005* (2013.01)

- (21) 출원번호 10-2018-7032352

- (22) 출원일자(국제) 2017년05월12일

심사청구일자 2019년11월20일

- (85) 번역문제출일자 2018년11월07일

- (65) 공개번호 10-2019-0006957

- (43) 공개일자 2019년01월21일

- (86) 국제출원번호 PCT/US2017/032413

- (87) 국제공개번호 WO 2017/197267

국제공개일자 2017년11월16일

- (30) 우선권주장

62/335,163 2016년05월12일 미국(US)

15/593,035 2017년05월11일 미국(US)

- (56) 선행기술조사문현

KR1020150118992 A

US20100107033 A1

- (73) 특허권자

퀄컴 인코포레이티드

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

- (72) 발명자

리차드슨 토마스 조셉

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

- (74) 대리인

특허법인코리아나

전체 청구항 수 : 총 24 항

심사관 : 조춘근

## (54) 발명의 명칭 강화된 평처링 및 저-밀도 패리티-체크 (LDPC) 코드 구조

## (57) 요약

본 개시의 특정 양태들은 일반적으로 강화된 평처링 및 저-밀도 패리티-체크 (LDPC) 코드 구조를 위한 기술들에 관한 것이다. 송신 디바이스에 의한 무선 통신을 위한 방법이 제공된다. 이 방법은 일반적으로, 코드 워드를 생성하기 위해 LDPC 코드에 기초하여 정보 비트들의 세트를 인코딩하는 단계로서, 상기 LDPC 코드는 제 1 수의 변수 노드들 및 제 2 수의 체크 노드들을 갖는 베이스 매트릭스에 의해 정의되는, 상기 정보 비트들의 세트를 인코딩하는 단계; 평처링된 코드 워드를 생성하기 위해 상기 변수 노드들 중 적어도 2 개의 변수 노드에 대응하는 비트들을 평처링하도록 설계된 평처링 패턴에 따라 상기 코드 워드를 평처링하는 단계; 적어도 2 개의 평처링된 변수 노드들에 대해 적어도 하나의 추가적인 패리티 비트를 추가하는 단계; 및, 평처링된 상기 코드 워드를 송신하는 단계를 포함한다.

대 표 도 - 도13

(52) CPC특허분류

**H03M 13/1174** (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

복수의 무선 통신 디바이스들을 포함하는 무선 통신 네트워크 내에서 변화하는 통신 레이트들로 무선 라디오 채널을 가로질러 무선 통신하기 위한 무선 통신 디바이스 구현 방법으로서,

무선 통신 디바이스의 인코더를 통해, 코드 워드를 생성하기 위해 저-밀도 패리티-체크 (LDPC) 코드에 기초하여 정보 비트들의 셋트를 인코딩하는 단계로서, 상기 LDPC 코드는 제 1 수의 변수 노드들 및 제 2 수의 체크 노드들을 갖는 베이스 그래프에 의해 정의되는, 상기 정보 비트들의 셋트를 인코딩하는 단계;

평처링 패턴에 따라 상기 무선 통신 디바이스의 평처링 모듈을 통해, 평처링된 코드 워드를 생성하기 위해 상기 베이스 그래프에서의 상기 제 1 수의 변수 노드들 중 적어도 2 개의 변수 노드들을 평처링하는 단계로서, 상기 베이스 그래프는 적어도 2 개의 평처링된 변수 노드들에 대한 적어도 하나의 추가적인 변수 노드를 포함하고, 각각의 추가적인 변수 노드는 하나의 체크 노드에 접속되며, 상기 체크 노드는 평처링된 변수 노드들의 쌍에 커플링되는, 상기 평처링하는 단계; 및

상기 무선 라디오 채널을 가로질러 상기 무선 통신 디바이스의 안테나를 통해 평처링된 상기 코드 워드와 연관된 송신 심볼들을 포함하는 라디오 주파수 신호를 송신하는 단계를 포함하는, 무선 통신하기 위한 무선 통신 디바이스 구현 방법.

#### 청구항 2

제 1 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은 상기 베이스 그래프에서 다른 변수 노드들보다 상기 체크 노드들에 대해 더 높은 접속성을 갖는, 무선 통신하기 위한 무선 통신 디바이스 구현 방법.

#### 청구항 3

제 1 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은  $M$  개의 변수 노드들을 포함하며, 상기 적어도 하나의 추가적인 변수 노드는  $M-1$  개의 변수 노드들을 포함하는, 무선 통신하기 위한 무선 통신 디바이스 구현 방법.

#### 청구항 4

제 1 항에 있어서,

상기 제 1 수의 변수 노드들은 27 또는 28 개의 변수 노드들인, 무선 통신하기 위한 무선 통신 디바이스 구현 방법.

#### 청구항 5

제 1 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은, 레퍼런스 LDPC 코드에서 변수 노드 보다 상대적으로 더 낮은 상기 체크 노드들에 대한 접속성을 갖는, 무선 통신하기 위한 무선 통신 디바이스 구현 방법.

#### 청구항 6

제 1 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들 및 상기 적어도 하나의 추가적인 변수 노드를 갖는 상기 베이스 그래프에 의해 정의된 상기 LDPC 코드의 Z 카페들을 취합으로써 적어도 하나의 리프팅된 LDPC 코드를 생성하는 단계를 더 포함하는, 무선 통신하기 위한 무선 통신 디바이스 구현 방법.

**청구항 7**

복수의 무선 통신 디바이스들을 포함하는 무선 통신 네트워크 내에서 변화하는 통신 레이트들로 무선 라디오 채널을 가로질러 무선 통신하기 위한 장치로서,

코드 워드를 생성하기 위해 저-밀도 패리티-체크 (LDPC) 코드에 기초하여 정보 비트들의 세트를 인코딩하는 수단으로서, 상기 LDPC 코드는 제 1 수의 변수 노드들 및 제 2 수의 체크 노드들을 갖는 베이스 그래프에 의해 정의되는, 상기 정보 비트들의 세트를 인코딩하는 수단;

평처링된 코드 워드를 생성하기 위해 상기 베이스 그래프에서의 상기 제 1 수의 변수 노드들 중 적어도 2 개의 변수 노드들을 평처링하는 수단으로서, 상기 베이스 그래프는 적어도 2 개의 평처링된 변수 노드들에 대한 적어도 하나의 추가적인 변수 노드를 포함하고, 각각의 추가적인 변수 노드는 하나의 체크 노드에 접속되며, 상기 체크 노드는 평처링된 변수 노드들의 쌍에 커플링되는, 상기 평처링하는 수단; 및

평처링된 상기 코드 워드와 연관된 송신 심볼들을 포함하는 라디오 주파수 신호를 송신하는 수단을 포함하는, 무선 통신하기 위한 장치.

**청구항 8**

제 7 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은 상기 베이스 그래프에서 다른 변수 노드들보다 상기 체크 노드들에 대해 더 높은 접속성을 갖는, 무선 통신하기 위한 장치.

**청구항 9**

제 7 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은  $M$  개의 변수 노드들을 포함하며, 상기 적어도 하나의 추가적인 변수 노드는  $M-1$  개의 변수 노드들을 포함하는, 무선 통신하기 위한 장치.

**청구항 10**

제 7 항에 있어서,

상기 제 1 수의 변수 노드들은 27 또는 28 개의 변수 노드들인, 무선 통신하기 위한 장치.

**청구항 11**

제 7 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은, 레퍼런스 LDPC 코드에서 변수 노드 보다 상대적으로 더 낮은 상기 체크 노드들에 대한 접속성을 갖는, 무선 통신하기 위한 장치.

**청구항 12**

제 7 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들 및 상기 적어도 하나의 추가적인 변수 노드를 갖는 상기 베이스 그래프에 의해 정의된 상기 LDPC 코드의 Z 카피들을 취함으로써 적어도 하나의 리프팅된 LDPC 코드를 생성하는 수단을 더 포함하는, 무선 통신하기 위한 장치.

**청구항 13**

복수의 무선 통신 디바이스들을 포함하는 무선 통신 네트워크 내에서 변화하는 통신 레이트들로 무선 라디오 채널을 가로질러 무선 통신하기 위한 장치로서,

상기 장치는,

메모리와 커플링된 적어도 하나의 프로세서; 및

송신기를 포함하고,

상기 적어도 하나의 프로세서는,

코드 워드를 생성하기 위해 저-밀도 패리티-체크 (LDPC) 코드에 기초하여 정보 비트들의 셋트를 인코딩하는 것으로서, 상기 LDPC 코드는 제 1 수의 변수 노드들 및 제 2 수의 체크 노드들을 갖는 베이스 그래프에 의해 정의되는, 상기 정보 비트들의 셋트를 인코딩하는 것을 행하고; 그리고

평처링된 코드 워드를 생성하기 위해 상기 베이스 그래프에서의 상기 제 1 수의 변수 노드들 중 적어도 2 개의 변수 노드들을 평처링하는 것으로서, 상기 베이스 그래프는 적어도 2 개의 평처링된 변수 노드들에 대한 적어도 하나의 추가적인 변수 노드를 포함하고, 각각의 추가적인 변수 노드는 하나의 체크 노드에 접속되며, 상기 체크 노드는 평처링된 변수 노드들의 쌍에 커플링되는, 상기 평처링하는 것을 행하도록 구성되고,

상기 송신기는, 상기 무선 라디오 채널을 가로질러 상기 장치의 안테나를 통해 평처링된 상기 코드 워드와 연관된 송신 심볼들을 포함하는 라디오 주파수 신호를 송신하도록 구성되는, 무선 통신하기 위한 장치.

#### 청구항 14

제 13 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은 상기 베이스 그래프에서 다른 변수 노드들보다 상기 체크 노드들에 대해 더 높은 접속성을 갖는, 무선 통신하기 위한 장치.

#### 청구항 15

제 13 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은  $M$  개의 변수 노드들을 포함하며, 상기 적어도 하나의 추가적인 변수 노드는  $M-1$  개의 변수 노드들을 포함하는, 무선 통신하기 위한 장치.

#### 청구항 16

제 13 항에 있어서,

상기 제 1 수의 변수 노드들은 27 또는 28 개의 변수 노드들인, 무선 통신하기 위한 장치.

#### 청구항 17

제 13 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은, 레퍼런스 LDPC 코드에서 변수 노드 보다 상대적으로 더 낮은 상기 체크 노드들에 대한 접속성을 갖는, 무선 통신하기 위한 장치.

#### 청구항 18

제 13 항에 있어서,

상기 적어도 하나의 프로세서는, 상기 적어도 2 개의 평처링된 변수 노드들 및 상기 적어도 하나의 추가적인 변수 노드를 갖는 상기 베이스 그래프에 의해 정의된 상기 LDPC 코드의 Z 카페들을 취함으로써 적어도 하나의 리프팅된 LDPC 코드를 생성하도록 더 구성되는, 무선 통신하기 위한 장치.

#### 청구항 19

복수의 무선 통신 디바이스들을 포함하는 무선 통신 네트워크 내에서 변화하는 통신 레이트들로 무선 라디오 채널을 가로질러 무선 통신하기 위한 컴퓨터 실행가능 코드를 저장한 비일시적 컴퓨터 판독가능 저장 매체로서,

상기 코드는,

무선 통신 디바이스의 인코더를 통해, 코드 워드를 생성하기 위해 저-밀도 패리티-체크 (LDPC) 코드에 기초하여 정보 비트들의 셋트를 인코딩하기 위한 코드로서, 상기 LDPC 코드는 제 1 수의 변수 노드들 및 제 2 수의 체크 노드들을 갖는 베이스 그래프에 의해 정의되는, 상기 정보 비트들의 셋트를 인코딩하기 위한 코드;

평처링 패턴에 따라 상기 무선 통신 디바이스의 평처링 모듈을 통해, 평처링된 코드 워드를 생성하기 위해 상기 베이스 그래프에서의 상기 제 1 수의 변수 노드들 중 적어도 2 개의 변수 노드들을 평처링하기 위한 코드로서,

상기 베이스 그래프는 적어도 2 개의 평처링된 변수 노드들에 대한 적어도 하나의 추가적인 변수 노드를 포함하고, 각각의 추가적인 변수 노드는 하나의 체크 노드에 접속되며, 상기 체크 노드는 평처링된 변수 노드들의 쌍에 커플링되는, 상기 평처링하기 위한 코드; 및

상기 무선 라디오 채널을 가로질러 상기 무선 통신 디바이스의 안테나를 통해 평처링된 상기 코드 워드와 연관된 송신 심볼들을 포함하는 라디오 주파수 신호를 송신하기 위한 코드를 포함하는, 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 20

제 19 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은 상기 베이스 그래프에서 다른 변수 노드들보다 상기 체크 노드들에 대해 더 높은 접속성을 갖는, 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 21

제 19 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은 M 개의 변수 노드들을 포함하며, 상기 적어도 하나의 추가적인 변수 노드는 M-1 개의 변수 노드들을 포함하는, 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 22

제 19 항에 있어서,

상기 제 1 수의 변수 노드들은 27 또는 28 개의 변수 노드들인, 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 23

제 19 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들은, 레퍼런스 LDPC 코드에서 변수 노드 보다 상대적으로 더 낮은 상기 체크 노드들에 대한 접속성을 갖는, 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 24

제 19 항에 있어서,

상기 적어도 2 개의 평처링된 변수 노드들 및 상기 적어도 하나의 추가적인 변수 노드를 갖는 상기 베이스 그래프에 의해 정의된 상기 LDPC 코드의 Z 카페들을 취함으로써 적어도 하나의 리프팅된 LDPC 코드를 생성하기 위한 코드를 더 포함하는, 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 25

삭제

#### 청구항 26

삭제

#### 청구항 27

삭제

#### 청구항 28

삭제

### 발명의 설명

### 기술 분야

## [0001] 관련 출원들에 대한 상호-참조 및 우선권 주장

이 출원은, 2016년 5월 12일 출원된 미국 가 특허 출원 제 62/335,163 호의 이익 및 그것에 대한 우선권을 주장하는, 2017년 5월 11일 출원된 미국 출원 제 15/593,035 호에 대해 우선권을 주장하고, 이들은 모든 적용가능한 목적들을 위해 그것들의 전체가 참조에 의해 본원에 통합된다.

## [0003] 기술 분야

이하에서 논의되는 기술의 소정 양태들은 일반적으로, 무선 통신 및 이진 데이터에서 예러들을 검출 및/또는 정정하는 것에 관한 것이고, 보다 상세하게는, 강화된 평처링 및 저-밀도 패리티-체크 (LDPC) 코드 구조를 위한 방법들 및 장치에 관한 것이다. 소정 양태들은 평처링된 LDPC 코드들의 향상된 성능을 가능하게 할 수 있다.

## 배경 기술

무선 통신 시스템들은 음성, 비디오, 데이터, 메시징, 브로드캐스트들 등과 같은 다양한 타입들의 통신 콘텐츠를 제공하기 위해 널리 전개된다. 이들 시스템들은 이용가능한 시스템 리소스들 (예컨대, 대역폭 및 송신 전력) 을 공유함으로써 다중 사용자들과의 통신을 지원 가능한 다중-액세스 기술들을 채용할 수도 있다. 이러한 다중-액세스 시스템들의 예들은, 코드 분할 다중 액세스 (CDMA) 시스템들, 시간 분할 다중 액세스 (TDMA) 시스템들, 시간 분할 동기 CDMA (TD-SCDMA) 시스템들, 주파수 분할 다중 액세스 (FDMA) 시스템들, 단일-캐리어 FDMA (SC-FDMA) 시스템들, 제 3 세대 파트너십 프로젝트 (3GPP) 통 텁 에볼루션 (LTE) 시스템들, LTE 어드밴스드 (LTE-A) 시스템들, 및 직교 주파수 분할 다중 액세스 (OFDMA) 시스템들을 포함한다.

다중 액세스 기술들은 차치체, 국가, 지역, 및 심지어 전세계 레벨에서 상이한 무선 디바이스들이 통신하는 것을 가능하게 하는 공통 프로토콜을 제공하기 위해 다양한 전기통신 표준들에서 채택되었다. 떠오르는 전기통신 표준의 일예는 뉴 라디오 (new radio; NR), 예를 들어, 5G 라디오 액세스이다. NR은 3GPP에 의해 발표된 LTE 모바일 표준에 대한 강화들의 셋트이다. 그것은, 다운링크 (DL) 상에서 그리고 업링크 (UL) 상에서 사이클릭 프리픽스 (cyclic prefix; CP) 를 갖는 OFDMA를 이용하여, 스펙트럼 효율을 향상시키고, 비용을 낮추며, 서비스를 향상시키고, 새로운 스펙트럼의 사용을 실시하고, 다른 개방 표준들과 더 잘 통합함으로써 모바일 광대역 인터넷 액세스를 더 잘 지원하고, 또한, 빔포밍, 다중-입력 다중-출력 (MIMO) 안테나 기술, 및 캐리어 어그리게이션 (carrier aggregation) 을 지원하도록 설계된다.

일반적으로, 무선 다중-액세스 통신 시스템은 다중 무선 노드들에 대한 통신을 동시에 지원할 수 있다. 각각의 노드는 순방향 및 역방향 링크를 상의 송신들을 통해 하나 이상의 기지국들과 통신한다. 순방향 링크 (또는 다운링크) 는 기지국들로부터 노드들로의 통신 링크를 지칭하고, 역방향 링크 (또는 업링크) 는 노드들로부터 기지국들로의 통신 링크를 지칭한다. 통신 링크들은 단일-입력 단일-출력, 다중-입력 단일-출력, 또는 다중-입력 다중-출력 (MIMO) 시스템을 통해 확립될 수도 있다.

무선 다중-액세스 통신 시스템은, 사용자 장비 (user equipment; UE) 들로서도 알려진, 다수의 통신 디바이스들에 대한 통신을 동시에 각각 지원하는 다수의 BS 들을 포함할 수도 있다. LTE 또는 LTE-A 네트워크에서, 하나 이상의 BS 들의 셋트는 e 노드 B (eNB) 를 정의할 수도 있다. 다른 예들에서 (예컨대, 차세대, NR, 또는 5G 네트워크에서), 무선 다중 액세스 통신 시스템은 다수의 중앙 유닛 (CU) 들 (예컨대, 중앙 노드 (CN) 들, 액세스 노드 제어기 (ANC) 들 등) 과 통신하는 다수의 분산된 유닛 (distributed unit; DU) 들 (예컨대, 에지 유닛 (EU) 들, 에지 노드 (EN) 들, 라디오 헤드 (RH) 들, 스마트 라디오 헤드 (SRH) 들, 송신 수신 포인트 (transmission reception point; TRP) 들 등) 을 포함할 수도 있고, 여기서, CU 와 통신하는 하나 이상의 DU 들의 셋트는 액세스 노드 (예컨대, BS, NR BS, 5G BS, NB, eNB, NR NB, 5G NB, 액세스 포인트 (AP), 네트워크 노드, gNB, TRP 등) 를 정의할 수도 있다. BS, AN, 또는 DU 는 (예컨대, BS로부터의 또는 UE로의 송신물을 위해) 다운링크 채널을 상에서 그리고 (예컨대, UE로부터 BS, AN, 또는 DU로의 송신물을 위해) 업링크 채널들 상에서 UE 또는 UE 들의 셋트와 통신할 수도 있다.

이진 값들 (예를 들어, 1들 및 0들) 이 비디오, 오디오, 통계 정보 등과 같은 다양한 타입들의 정보를 표현 및 통신하는데 이용된다. 유감스럽게도, 이진 데이터의 저장, 송신, 및/또는 프로세싱 동안, 예러들이 의도치 않게 도입될 수도 있다; 예를 들어, "1" 이 "0" 으로 변경되거나 또는 그 반대일 수도 있다.

일반적으로, 데이터 송신의 경우에, 수신기는 잡음 또는 애곡의 존재에서 각각의 수신된 비트를 관측하고 단지 비트의 값의 표시만이 획득된다. 이들 상황들 하에서, 관측된 값들은 "소프트" 비트들의 소스로서 인터프리

팅된다. 소프트 비트는 비트의 값 (예를 들어, 1 또는 0)의 선호된 추정치를 그 추정치의 신뢰성의 일부 표시와 함께 표시한다. 여러들의 수는 상대적으로 낮을 수도 있지만, 심지어 작은 수의 여러들 또는 레벨의 왜곡으로 데이터가 사용할 수 없게 될 수 있거나, 또는 송신 여러들의 경우에는, 데이터의 재송신을 필요하게 만들 수도 있다. 여러들에 대해 체크하고, 그리고 일부 경우들에는, 여러들을 정정하기 위한 메커니즘을 제공하기 위하여, 이진 데이터는 신중히 설계된 리던던시를 도입하도록 코딩될 수 있다. 데이터의 유닛의 코딩은 코드워드로 통칭되는 것을 생성한다. 그 리던던시로 인해, 코드워드는 코드워드가 생성된 데이터의 입력 유닛보다 더 많은 비트들을 종종 포함할 것이다.

[0011] 리던던트 비트들은 코드워드를 생성하기 위해 인코더에 의해 송신된 비트스트림에 부가된다. 송신된 코드워드들로부터 발생하는 신호들이 수신 또는 프로세싱될 때, 신호에서 관측되는 바와 같은 코드워드에 포함된 리던던트 정보는 원래의 데이터 유닛을 복구하기 위하여 수신된 데이터에서의 여러들을 식별 및/또는 정정하거나 또는 그 수신된 신호로부터 왜곡을 제거하는데 이용될 수 있다. 이러한 여러 체크 및/또는 정정은 디코딩 프로세스의 일부로서 구현될 수 있다. 여러들의 부재에서, 또는 정정가능한 여러들 또는 왜곡의 경우에, 디코딩이 프로세싱되는 소스 데이터로부터, 인코딩되었던 원래의 데이터 유닛을 복구하는데 이용될 수 있다. 복구불가능한 여러들의 경우에, 디코딩 프로세스는 원래의 데이터가 완전히 복구될 수 없다는 일부 표시를 생성할 수도 있다. 디코딩 실패의 이러한 표시들은 데이터의 재송신을 개시하는데 이용될 수 있다. 데이터 통신을 위한 광섬유 라인들의 사용 및 데이터가 데이터 저장 디바이스들 (예를 들어, 디스크 드라이브들, 테이프들 등)로부터 판독되고 그 데이터 저장 디바이스들에 저장될 수 있는 레이트가 증가함에 따라, 데이터 저장 및 송신 용량의 효율적인 사용 뿐만 아니라 고속으로 데이터를 인코딩 및 디코딩하는 능력의 필요성이 증가하고 있다.

### 발명의 내용

[0012] 이하에서는 논의되는 기술의 기본적인 이해를 제공하기 위해 본 개시의 일부 양태들을 요약한다. 이 요약은 본 개시의 모든 고려되는 피처들 (features)의 확장적인 개관이 아니고, 본 개시의 모든 양태들의 중요한 또는 결정적 엘리먼트들을 식별하려는 의도도 아니고, 본 개시의 임의의 또는 모든 양태들의 범위를 나타내려는 의도도 아니다. 그것의 유일한 목적은 나중에 제시되는 보다 상세한 설명에 대한 서두로서 본 개시의 하나 이상의 양태들의 일부 개념들을 요약 형태로 제시하기 위한 것이다. 이 논의를 고려한 후에, 그리고 특히 "상세한 설명"이라는 제목의 섹션을 읽은 후에, 본 개시의 피처들이 무선 네트워크에서의 스테이션들과 액세스 포인트들 간의 개선된 통신을 포함하는 이점들을 제공하는 방법을 이해할 것이다.

[0013] 인코딩 효율 및 높은 데이터 레이트들이 중요하지만, 인코딩 및/또는 디코딩 시스템이 넓은 범위의 디바이스들 (예컨대, 소비자 디바이스들)에서의 사용을 위해 실용적이기 위해서는, 인코더들 및/또는 디코더들이 합리적인 비용으로 구현될 수 있다는 것 또한 중요하다.

[0014] 모바일 광대역 액세스에 대한 수요가 계속 증가함에 따라, NR 기술에서의 추가적인 향상들에 대한 필요성이 존재한다. 바람직하게는, 이들 향상들은 이들 기술들을 채용하는 다른 다중-액세스 기술들 및 전기통신 표준들에 적용가능하여야만 한다. 향상들을 위한 하나의 영역은 NR에 적용가능한 인코딩/디코딩의 영역이다. 예를 들어, NR을 위한 고성능 LDPC 코드들을 위한 기법들이 바람직하다.

[0015] 본 개시의 소정 양태들은 일반적으로, 저-밀도 패리티-체크 (low-density parity-check; LDPC) 코드들의 강화된 (enhanced) 평처링 (puncturing)을 위한 방법들 및 장치에 관한 것이다. 통신 시스템들은 종종 수개의 상이한 레이트들에서 동작할 필요가 있다. LDPC 코드들은 상이한 레이트들에서의 코딩 및 디코딩을 제공하는 간단한 구현을 위한 하나의 옵션이다. 예를 들어, 하위-레이트 LDPC 코드들을 평처링함으로써 상위-레이트 LDPC 코드들이 생성될 수 있다.

[0016] 본 개시의 특정 양태들은 일반적으로 송신 디바이스에 의해 수행될 수도 있는 무선 통신을 위한 방법을 제공한다. 이 방법은 일반적으로, 코드 워드를 생성하기 위해 LDPC 코드에 기초하여 정보 비트들의 세트를 인코딩하는 단계로서, 상기 LDPC 코드는 제 1 수의 변수 노드들 (variable nodes) 및 제 2 수의 체크 노드들 (check nodes)을 갖는 베이스 매트릭스 (base matrix)에 의해 정의되는, 상기 정보 비트들의 세트를 인코딩하는 단계; 평처링된 코드 워드 (code word)를 생성하기 위해 변수 노드들 중 적어도 2 개의 변수 노드에 대응하는 비트들을 평처링하도록 설계된 평처링 패턴에 따라 코드 워드를 평처링하는 단계; 적어도 2 개의 평처링된 변수 노드들에 대해 적어도 하나의 추가적인 패리티 비트 (parity bit)를 추가하는 단계; 및, 평처링된 코드 워드를 송신하는 단계를 포함한다.

[0017]

본 개시의 특정 양태들은 송신 디바이스와 같은 무선 통신을 위한 장치를 제공한다. 이 장치는 일반적으로, 코드 워드를 생성하기 위해 LDPC 코드에 기초하여 정보 비트들의 셋트를 인코딩하는 수단으로서, 상기 LDPC 코드는 제 1 수의 변수 노드들 및 제 2 수의 체크 노드들을 갖는 베이스 매트릭스에 의해 정의되는, 상기 정보 비트들의 셋트를 인코딩하는 수단; 평처링된 코드 워드를 생성하기 위해 변수 노드들 중 적어도 2 개의 변수 노드에 대응하는 비트들을 평처링하도록 설계된 평처링 패턴에 따라 코드 워드를 평처링하는 수단; 적어도 2 개의 평처링된 변수 노드들에 대해 적어도 하나의 추가적인 패리티 비트를 추가하는 수단; 및, 평처링된 코드 워드를 송신하는 수단을 포함한다.

[0018]

본 개시의 특정 양태들은 송신 디바이스와 같은 무선 통신을 위한 장치를 제공한다. 이 장치는 일반적으로, 메모리와 커플링된 적어도 하나의 프로세서를 포함하고, 이 적어도 하나의 프로세서는, 코드 워드를 생성하기 위해 LDPC 코드에 기초하여 정보 비트들의 셋트를 인코딩하는 것으로서, 상기 LDPC 코드는 제 1 수의 변수 노드들 및 제 2 수의 체크 노드들을 갖는 베이스 매트릭스에 의해 정의되는, 상기 정보 비트들의 셋트를 인코딩하는 것을 행하고; 평처링된 코드 워드를 생성하기 위해 변수 노드들 중 적어도 2 개의 변수 노드에 대응하는 비트들을 평처링하도록 설계된 평처링 패턴에 따라 코드 워드를 평처링하며; 그리고, 적어도 2 개의 평처링된 변수 노드들에 대해 적어도 하나의 추가적인 패리티 비트를 추가하도록 구성된다. 이 장치는, 평처링된 코드 워드를 송신하도록 구성된 송신기를 포함한다.

[0019]

본 개시의 특정 양태들은 컴퓨터 실행가능 코드를 그 위에 저장한 컴퓨터 판독가능 매체를 제공한다. 이 컴퓨터 실행가능 코드는 일반적으로, 코드 워드를 생성하기 위해 LDPC 코드에 기초하여 정보 비트들의 셋트를 인코딩하기 위한 코드로서, 상기 LDPC 코드는 제 1 수의 변수 노드들 및 제 2 수의 체크 노드들을 갖는 베이스 매트릭스에 의해 정의되는, 상기 정보 비트들의 셋트를 인코딩하기 위한 코드; 평처링된 코드 워드를 생성하기 위해 변수 노드들 중 적어도 2 개의 변수 노드에 대응하는 비트들을 평처링하도록 설계된 평처링 패턴에 따라 코드 워드를 평처링하기 위한 코드; 적어도 2 개의 평처링된 변수 노드들에 대해 적어도 하나의 추가적인 패리티 비트를 추가하기 위한 코드; 및, 평처링된 코드 워드를 송신하기 위한 코드를 포함한다.

[0020]

본 개시의 다른 양태들, 피쳐들, 및 실시형태들은 첨부하는 도면들과 함께 본 개시의 특정, 예시적인 양태들의 다음의 설명을 리뷰 시, 당업자들에게 명백해질 것이다. 본 개시의 피쳐들은 이하의 소정의 양태들 및 도면들에 대하여 논의될 수도 있지만, 본 개시의 모든 양태들은 본 명세서에서 논의된 유리한 피쳐들 중 하나 이상을 포함할 수 있다. 다시 말해서, 하나 이상의 양태들은 소정의 유리한 피쳐들을 갖는 것으로서 논의될 수도 있지만, 이러한 피쳐들 중 하나 이상은 또한 본 명세서에서 논의된 본 개시의 다양한 양태들에 따라 이용될 수도 있다. 유사한 방식으로, 예시적인 양태들은 이하에 디바이스, 시스템, 또는 방법 실시형태로서 논의될 수도 있지만, 이러한 예시적인 실시형태들은 다양한 디바이스들, 시스템들, 및 방법들로 구현될 수 있는 것으로 이해되어야 한다.

### 도면의 간단한 설명

[0021]

본 개시의 상기 열거된 피쳐들이 상세히 이해될 수 있도록 하기 위해, 상기 간단히 요약된, 보다 특정한 설명은, 일부가 첨부된 도면들에 예시되는, 양태들을 참조하여 이루어질 수도 있다. 그러나, 첨부된 도면들은 단지 본 개시의 소정의 통상적인 양태들을 예시하며, 따라서 그 범위의 제한으로 간주되지 않으며, 설명을 위해 다른 등가의 효과적인 양태들을 인정할 수도 있다.

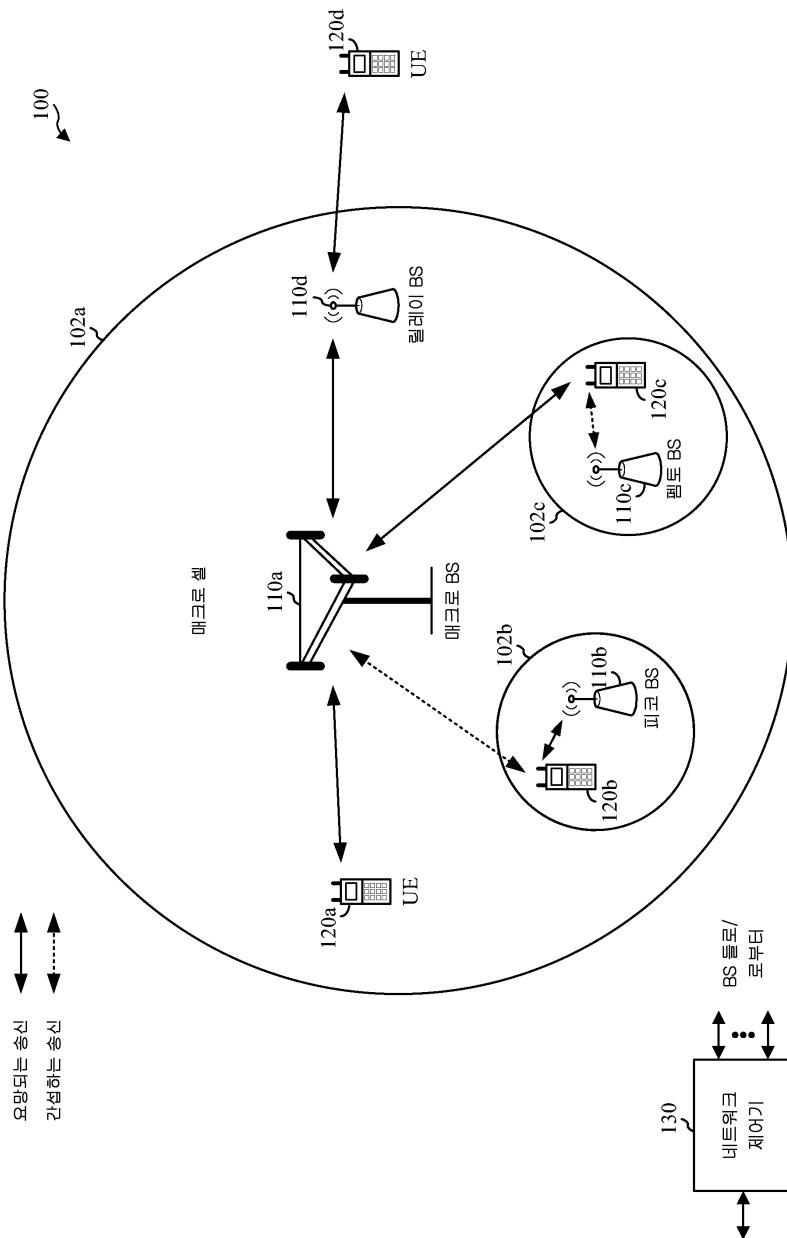

도 1 은, 본 개시의 특정 양태들에 따른, 일 예시적인 무선 통신 네트워크를 나타내는 블록도이다.

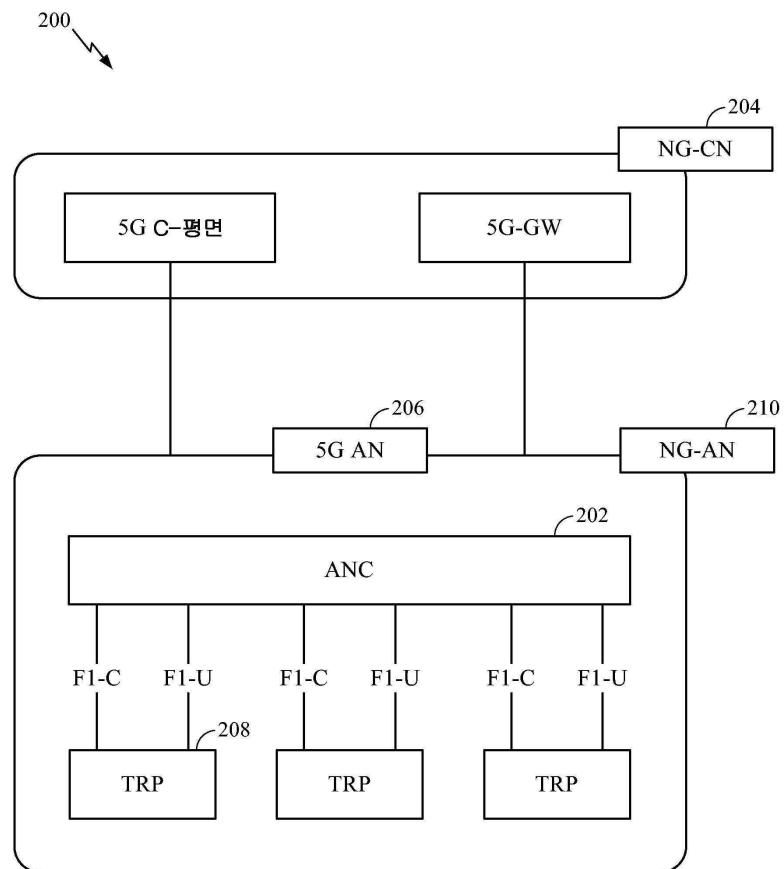

도 2 는, 본 개시의 특정 양태들에 따른, 분산형 라디오 액세스 네트워크 (RAN) 의 일 예시적인 논리적 아키텍처를 나타내는 블록도이다.

도 3 은, 본 개시의 특정 양태들에 따른, 분산형 RAN 의 일 예시적인 물리적 아키텍처를 나타내는 도이다.

도 4 는, 본 개시의 특정 양태들에 따른, 일 예시적인 기지국 (base station; BS) 및 사용자 장비 (UE) 의 설계를 나타내는 블록도이다.

도 5 는, 본 개시의 특정 양태들에 따른, 통신 프로토콜 스택을 구현하기 위한 예들을 나타내는 도이다.

도 6 은, 본 개시의 특정 양태들에 따른, 다운링크 (DL)-중심 서브프레임의 일 예를 나타낸다.

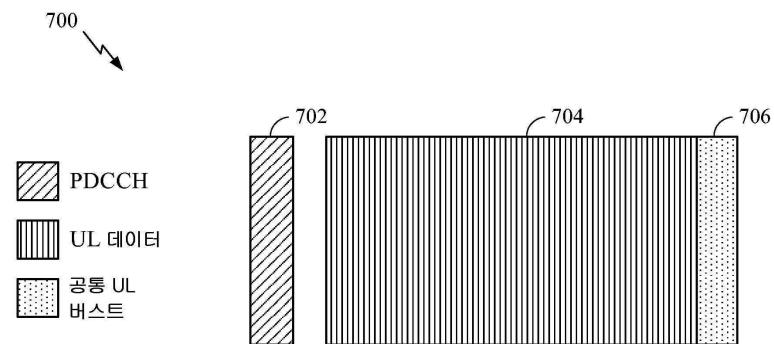

도 7 은, 본 개시의 특정 양태들에 따른, 업링크 (UL)-중심 서브프레임의 일 예를 나타낸다.

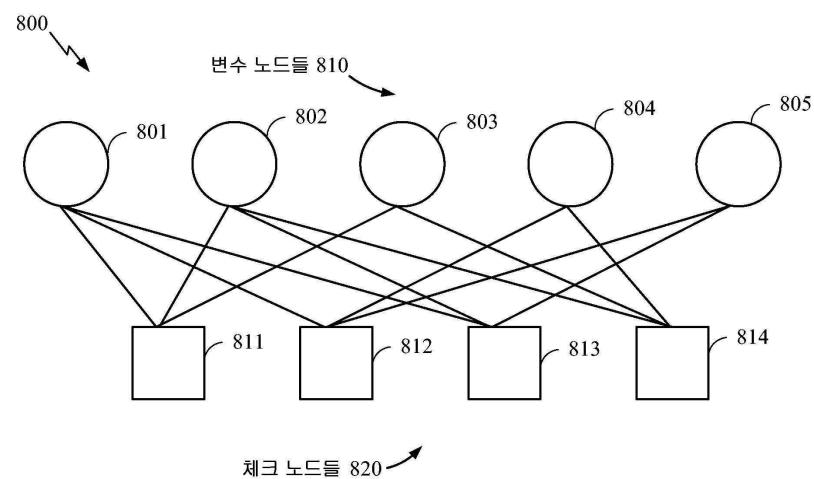

도 8 은, 본 개시의 특정 양태들에 따른, 일 예시적인 저-밀도 패리티-체크 (LDPC) 코드의 그래픽적 표현이다.

도 8a 는, 본 개시의 특정 양태들에 따른, 도 8 의 예시적인 LDPC 코드의 매트릭스 표현이다.

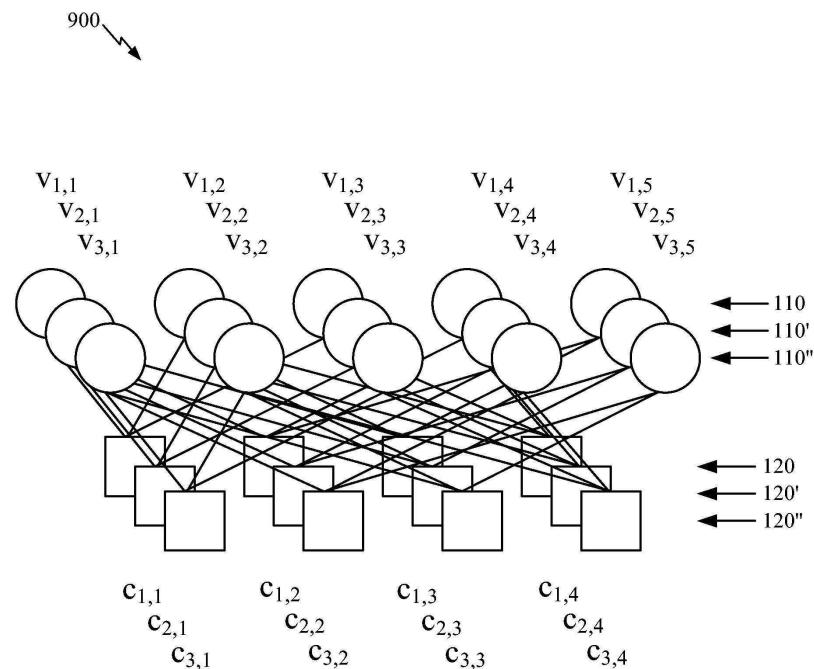

도 9 는, 본 개시의 특정 양태들에 따른, 도 8 의 LDPC 코드의 리프팅들의 그래픽적 표현이다.

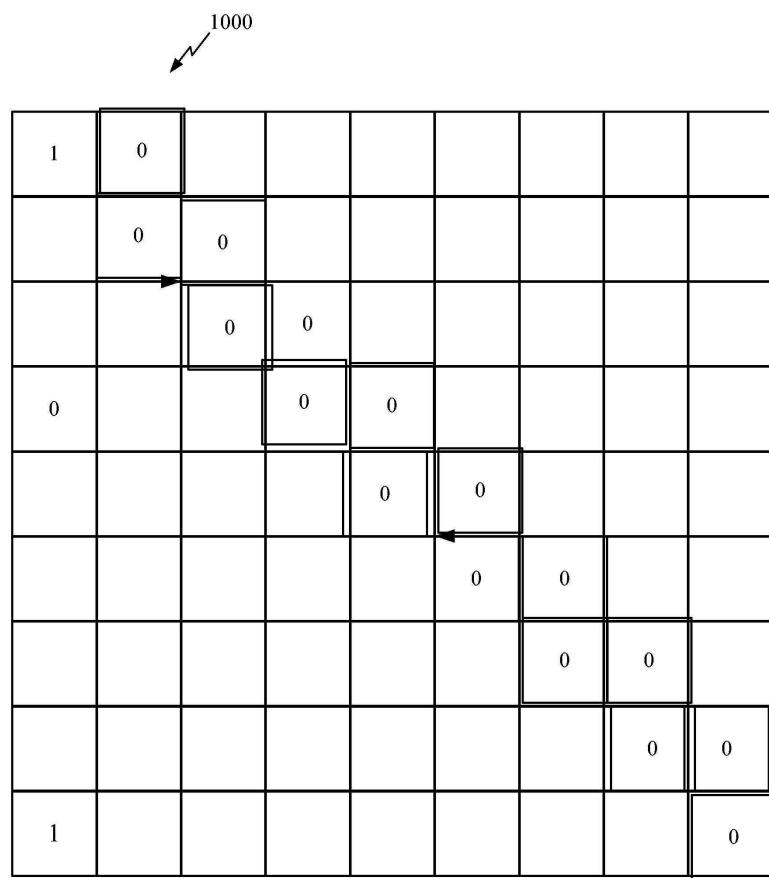

도 10 은 준-순환적 802.11 LDPC 코드를 위한 매트릭스의 정수 표현이다.

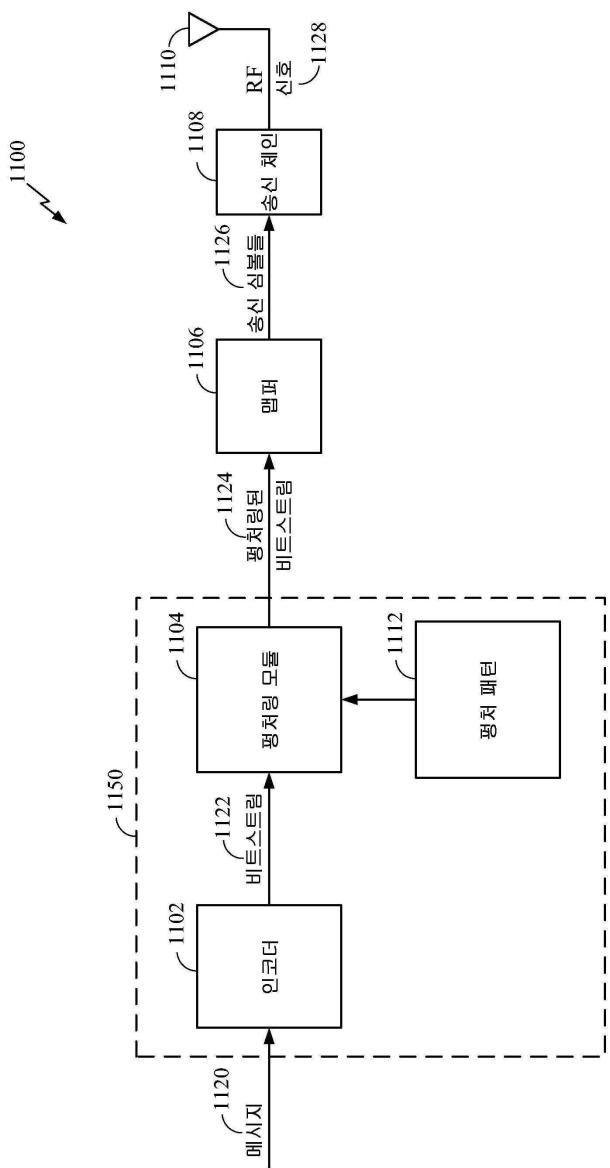

도 11 은, 본 개시의 특정 양태들에 따른, 일 예시적인 인코더를 나타내는 단순화된 블록도이다.

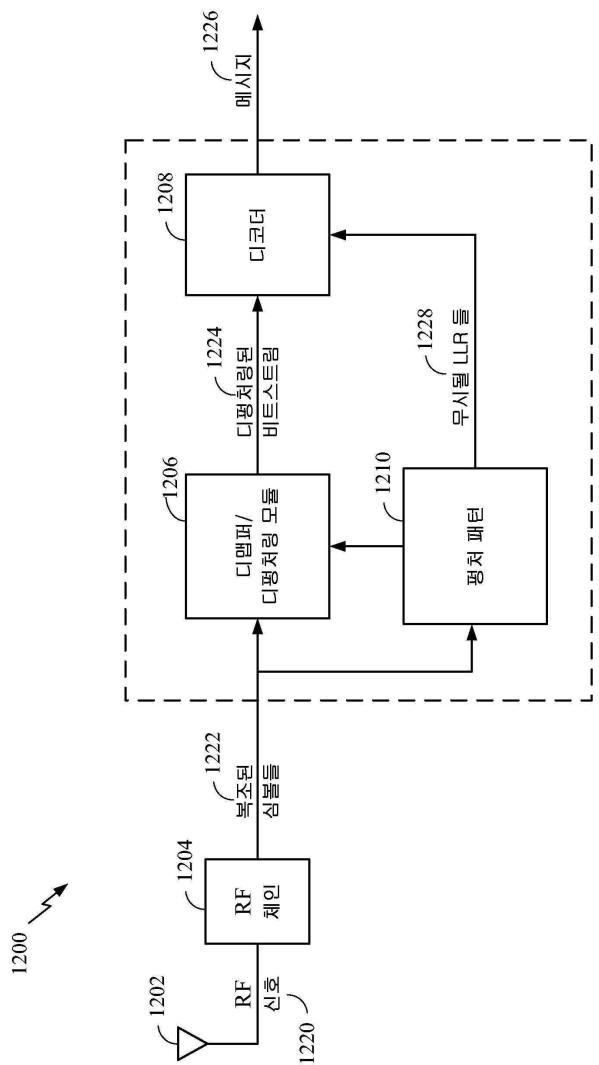

도 12 는, 본 개시의 특정 양태들에 따른, 일 예시적인 디코더를 나타내는 단순화된 블록도이다.

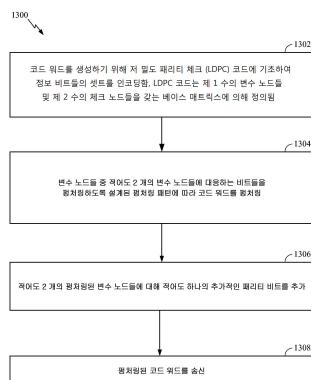

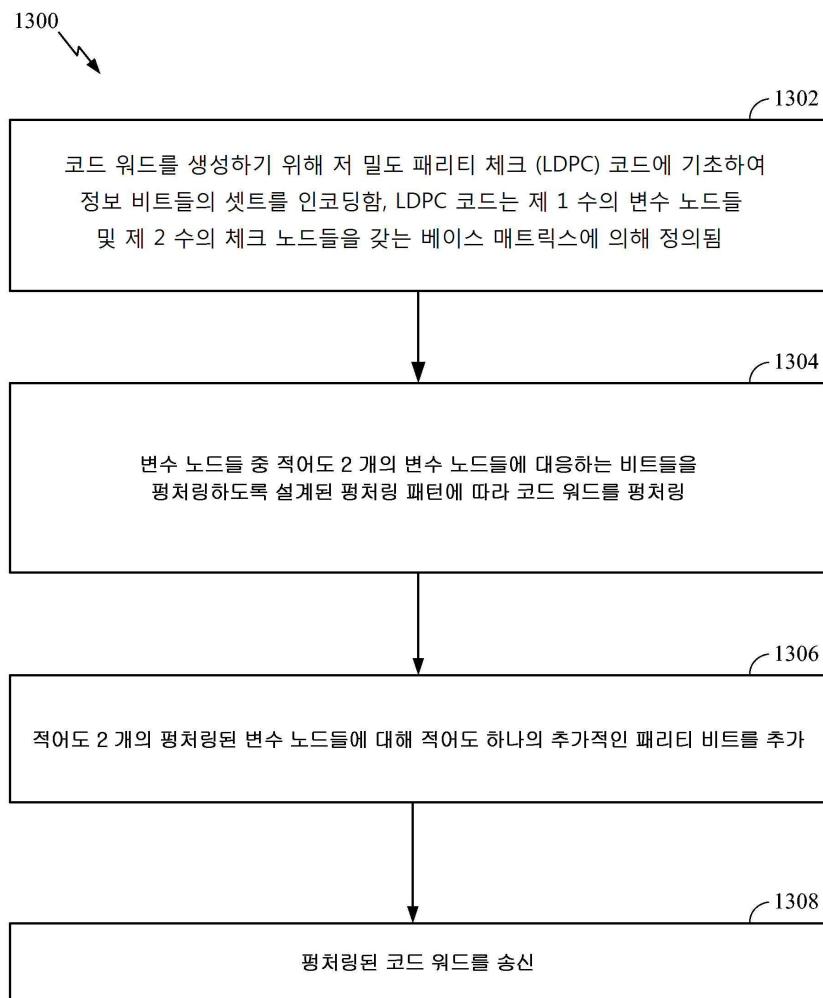

도 13 은, 본 개시의 특정 양태들에 따른, 송신 디바이스에 의한 무선 통신을 위해 강화된 평처링 및 LDPC 코드 구조에 기초하여 정보를 인코딩하기 위한 예시적인 동작들을 나타내는 흐름도이다.

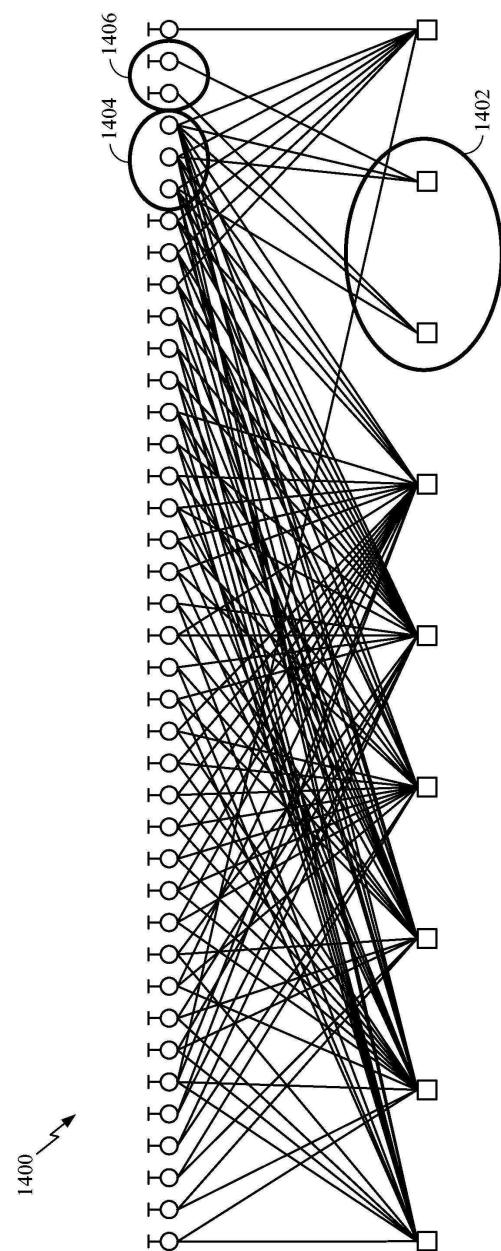

도 14 는, 본 개시의 특정 양태들에 따른, 다수의 평처링된 비교적 낮은-차수 변수 노드들 및 추가적인 패리티를 갖는 일 예시적인 LDPC 코드의 그래픽적 표현이다.

이해를 용이하게 하기 위해, 도면들에 공통인 동일한 엘리먼트들을 지정하기 위해, 가능한 경우 동일한 참조 번호들이 이용되었다. 하나의 실시형태에서 개시된 엘리먼트들은 특정 열거 없이 다른 실시형태들에 유익하게 활용될 수도 있는 것으로 간주된다.

### 발명을 실시하기 위한 구체적인 내용

[0022]

본 개시의 양태들은 뉴 라디오 (NR) 액세스 기술 (예컨대, 5G 라디오 액세스) 을 위한 인코딩 (및/또는 디코딩) 을 위한 장치, 방법들, 프로세싱 시스템들, 및 컴퓨터 프로그램 제품들을 제공한다. NR 은 새로운 에어 인터페이스 또는 정해진 전송 계층에 따라 동작하도록 구성된 라디오들을 지칭할 수도 있다. NR 은, 넓은 대역폭 (예컨대, 80MHz 및 그 너머) 을 목표로 하는 강화된 모바일 브로드밴드 (eMBB) 서비스, 높은 캐리어 주파수 (예컨대, 60GHz) 를 목표로 하는 밀리미터 파 (mmW) 서비스, 비-후방 호환성 MTC 기법들을 목표로 하는 매시브 머신 타입 통신 (massive machine type communications; mMTC) 서비스, 및/또는 초-신뢰가능 저-레이턴시 통신 (ultra-reliable low-latency communications; URLLC) 서비스를 목표로 하는 미션 크리티컬 (mission critical; MiCr) 서비스에 대한 지원을 포함할 수도 있다. 이들 서비스들은 레이턴시 및 신뢰성 요건들을 포함할 수도 있다. NR 은 저-밀도 패리티-체크 (LDPC) 코딩 및/또는 폴라 코드들 (polar codes) 을 이용할 수도 있다.

[0023]

본 개시의 양태들은, 예를 들어, 강화된 성능을 갖는 LDPC 코드들에 대해, 강화된 평처링 및 저-밀도 패리티-체크 (LDPC) 코드 구조를 위한 기법들을 제공한다. 양태들에서, 예를 들어, 단일의 고-차수 변수 노드보다는 다수의 비교적 저-차수 변수 노드들은 평처링될 수 있다. 변수 노드들의 차수 (degree) 는 베이스 그래프 (base graph) 에서 변수 대 체크 노드들 사이의 접속들의 수를 가리킬 수도 있다. 큰 베이스 그래프 (또한 베이스 코드 또는 베이스 PCM 으로서 지칭됨) 에서, 변수 노드들은 더 작은 베이스 그래프의 변수 노드들에 비해 더 높은 차수의 접속성을 지원할 수 있다. 추가적으로, 코드 레이트를 효율적으로 부스트 (boost) 하기 위해, 엑스트라 패리티 비트들 (extra parity bits) 이 LDPC 코드 구조에 추가될 수 있고, 각 패리티 비트는 2 개의 평처링된 노드들의 패리티에 의해 수행된 1-차 변수 노드에 대응한다.

[0024]

본 개시의 다양한 양태들은 첨부하는 도면들을 참조하여 이하에 보다 완전히 설명된다. 본 개시는, 그러나, 많은 상이한 형태들로 구현될 수도 있고 본 개시 전반에 걸쳐 제시된 임의의 특정 구조 또는 기능에 제한되는 것으로 해석되어서는 안된다. 오히려, 이들 양태들은 본 개시가 철저하고 완전하고, 당업자들에게 본 개시의 범위를 완전히 전하도록 하기 위해 제공된다. 본 명세서의 교시들에 기초하여, 당업자는, 본 개시의 임의의 다른 양태에 독립적으로 구현되든 또는 그 임의의 다른 양태와 결합되든 간에, 본 개시의 범위가 본 명세서에서 개시된 본 개시의 임의의 양태를 커버하도록 의도된다는 것을 인식해야 한다. 예를 들어, 본 명세서에 기재된 임의의 수의 양태들을 이용하여 장치가 구현될 수도 있거나 또는 방법이 실시될 수도 있다. 추가로, 본 개시의 범위는 본 명세서에 기재된 본 개시의 다양한 양태들에 더하여 또는 그 이외의 다른 구조, 기능성, 또는 구조와 기능성을 이용하여 실시되는 그러한 장치 또는 방법을 커버하도록 의도된다. 본 명세서에서 개시된 본 개시의 임의의 양태는 청구항의 하나 이상의 엘리먼트들에 의해 구현될 수도 있는 것으로 이해되어야 한다. 단어 "예시적인" 은 본 명세서에서 "일 예, 경우, 또는 예시로서 기능하는 것" 을 의미하는데 사용된다. 본 명세서에서 "예시적인" 으로서 설명된 임의의 양태가 다른 양태들에 비해 유리하거나 또는 선호되는 것으로서 반드시 해석되는 것은 아니다.

[0025]

특정한 양태들이 본 명세서에서 설명되지만, 이들 양태들의 많은 변화들 및 치환들이 본 개시의 범위에 포함된

다. 선호된 양태들의 일부 이익들 및 이점들이 언급되지만, 본 개시의 범위는 특정한 이익들, 사용들, 또는 목적들에 제한되도록 의도되지 않는다. 오히려, 본 개시의 양태들은, 일부가 도면들에 그리고 선호된 양태들의 다음의 설명에 일 예로 예시되는, 상이한 무선 기술들, 시스템 구성들, 네트워크들, 및 송신 프로토콜들에 광범위하게 적용가능한 것으로 의도된다. 상세한 설명 및 도면들은 제한이 아니라 본 개시를 단지 예시할 뿐이며, 본 개시의 범위는 첨부된 청구항들 및 그 등가물들에 의해 정의된다.

[0026] 본 명세서에서 설명된 기법들은 코드 분할 다중 액세스 (CDMA) 네트워크들, 시간 분할 다중 액세스 (TDMA) 네트워크들, 주파수 분할 다중 액세스 (FDMA) 네트워크들, 직교 FDMA (OFDMA) 네트워크들, 단일-캐리어 FDMA (SC-FDMA) 네트워크들 등과 같은 다양한 무선 통신 네트워크들에 대해 이용될 수도 있다. 용어들 "네트워크들" 및 "시스템들"은 종종 상호교환가능하게 사용된다. CDMA 네트워크는 범용 지상 라디오 액세스 (UTRA), CDMA2000 등과 같은 무선 기술을 구현할 수도 있다. UTRA는 광대역-CDMA (W-CDMA) 및 로우 칩 레이트 (Low Chip Rate; LCR) 를 포함한다. CDMA2000은 IS-2000, IS-95, 및 IS-856 표준들을 커버한다. TDMA 네트워크는 GSM (Global System for Mobile Communications) 과 같은 무선 기술을 구현할 수도 있다. OFDMA 네트워크는 진화된 UTRA (E-UTRA), IEEE 802.11, IEEE 802.16, IEEE 802.20, Flash-OFDM® 등과 같은 무선 기술을 구현할 수도 있다. UTRA, E-UTRA, 및 GSM은 범용 모바일 전기통신 시스템 (UMTS) 의 일부이다.

3GPP LTE 및 LTE-어드밴스드 (LTE-A)는 E-UTRA를 이용하는 UMTS의 텔리스들이다. UTRA, E-UTRA, UMTS, LTE, LTE-A 및 GSM은 "제 3 세대 파트너십 프로젝트" (3GPP) 라 명명된 기관으로부터의 문서들에 기술되어 있다. CDMA2000은 "제 3 세대 파트너십 프로젝트 2" (3GPP2) 라 명명된 기관으로부터의 문서들에 기술되어 있다. 이들 통신 네트워크들은, 본 개시에서 설명된 기법들이 적용될 수도 있는 네트워크들의 예들로서 단지 열거될 뿐이다; 그러나, 이 개시는 상기 설명된 통신 네트워크에 제한되지 않는다. 명확성을 위해, 양태들은 본 명세서에서 보통 3G 및/또는 4G 무선 기술들과 연관된 전문용어를 사용하여 설명될 수도 있지만, 본 개시의 양태들은 5G 및 그 이후를 포함하는 뉴 라디오 (NR) 기술들과 같은 다른 세대-기반 통신 시스템들에서 적용될 수도 있다는 것에 유의한다.

#### 무선 통신 시스템 컨텍스트

[0027] [0028] 도 1은 본 개시의 양태들이 수행될 수도 있는 일 예시적인 무선 통신 네트워크 (100)를 나타낸다. 예를 들어, UE (120) 또는 BS (110)와 같은 송신 디바이스는 코드 워드를 생성하기 위해 저-밀도 패리티-체크 (LDPC) 코드에 기초하여 정보 비트들의 셋트를 인코딩할 수 있다. 송신 디바이스는 평처링 패턴에 따라 LDPC의 평처링을 수행할 수도 있다. 평처링 패턴은 변수 노드들 중 적어도 2개에 대응하는 비트들을 평처링하도록 설계될 수 있다. 평처링된 변수 노드들은 베이스 매트릭스에서 최고 차수의 변수 노드들일 수 있지만, 다른 LDPC 코드들에서의 변수 노드들에 비해 상대적으로 낮은 차수의 변수 노드들일 수 있다. 고차 변수 노드들은 체크 노드들에 대해 많은 접속들을 갖는다. (예컨대, 많은 체크 노드들을 갖는) 큰 베이스 그래프들은 (예컨대, 적은 체크 노드들을 갖는) 작은 베이스 그래프들에 비해 더 큰 차수의 변수 노드들을 지원 /포함할 수도 있다. 엑스트라 패리티 비트들은 평처링된 변수 노드들의 각 쌍에 대해 LDPC 코드 구조에 추가될 수 있다.

[0029] 도 1에서 예시된 바와 같이, 무선 통신 네트워크 (100)는 다수의 BS 들 (110) 및 다른 네트워크 엔티티들을 포함할 수도 있다. BS는 UE들과 통신하는 스테이션일 수도 있다. 각 BS (110)는 특정 지리적 영역에 대해 통신 커버리지를 제공할 수도 있다. 3GPP에서, 용어 "셀 (cell)"은, 그 용어가 사용되는 맴맥에 따라, 이 커버리지 영역을 서빙 (serving) 하는 노드 B 및/또는 노드 B 서브시스템의 커버리지 영역을 지칭할 수 있다. NR 시스템들에서, 용어 "셀" 및 gNB, 노드 B, 5G NB, AP, NR BS, NR TRP 등은 상호교환가능할 수도 있다. 일부 예들에서, 셀은 반드시 정적일 필요는 없고, 셀의 지리적 영역은 이동 BS의 위치에 따라 이동할 수도 있다. 일부 예들에서, BS들은, 임의의 적합한 전송 네트워크를 이용하여 직접적인 물리적 접속, 가상 네트워크 등과 같은 다양한 타입들의 백홀 (backhaul) 인터페이스들을 통해 무선 통신 네트워크 (100)에서 서로 및/또는 하나 이상의 다른 BS들 또는 네트워크 노드들 (미도시)에 상호접속될 수도 있다.

[0030] 일반적으로, 임의의 수의 무선 네트워크들이 주어진 지리적 영역에서 전개될 수도 있다. 각 무선 네트워크는 특정 라디오 액세스 기술 (radio access technology; RAT)을 지원할 수도 있고, 하나 이상의 주파수들에서 동작할 수도 있다. RAT는 또한 라디오 기술, 에어 인터페이스 (air interface) 등으로서 지칭될 수도 있다. 주파수는 또한 캐리어, 주파수 채널 등으로서 지칭될 수도 있다. 각각의 주파수는 상이한 RAT들의 무선 네트워크들 사이의 간섭을 회피하기 위해 주어진 지리적 영역에서 단일 RAT를 지원할 수도 있다. 일부 경우들에서, NR 또는 5G RAT 네트워크들이 전개될 수도 있다.

[0031]

BS 는 매크로 셀, 피코 셀, 펨토 셀, 및/또는 다른 태입들의 셀에 대해 통신 커버리지를 제공할 수도 있다. 매크로 셀은 비교적 큰 지리적 영역 (예컨대, 반경 수 킬로미터) 을 커버할 수도 있고, 서비스 가입을 갖는 UE 들에 의한 제한되지 않은 액세스를 허용할 수도 있다. 피코 셀은 비교적 작은 지리적 영역 (예컨대, 가정) 을 커버할 수도 있고, 펨토 셀과의 연관을 갖는 UE 들 (예컨대, 폐쇄 가입자 그룹 (CSG) 에서의 UE 들, 가정에서의 사용자들을 위한 UE 들 등) 에 의한 제한된 액세스를 허용할 수도 있다. 매크로 셀을 위한 BS 는 매크로 BS 로서 지칭될 수도 있다. 피코 셀을 위한 BS 는 피코 BS 로서 지칭될 수도 있다. 펨토 셀을 위한 BS 는 펨토 BS 또는 홈 BS 로서 지칭될 수도 있다. 도 1 에서 나타낸 예에서, BS (110a), BS (110b), 및 BS (110c) 는 각각 매크로 셀 (102a), 매크로 셀 (102b), 및 매크로 셀 (102c) 을 위한 매크로 BS 들일 수도 있다. BS 는 하나 또는 다수 (예컨대, 3) 의 셀들을 지원할 수도 있다.

[0032]

무선 통신 네트워크 (100) 는 릴레이 스테이션들을 또한 포함할 수도 있다. 릴레이 스테이션은 업스트림 스테이션 (예컨대, BS (110) 또는 UE (120)) 로부터 데이터 및/또는 다른 정보의 송신물을 수신하고 다운스트림 스테이션 (예컨대, UE (120) 또는 BS (110)) 으로 데이터 및/또는 다른 정보의 송신물을 전송하는 스테이션이다. 릴레이 스테이션은 또한, 다른 UE 들에 대해 송신물들을 중계하는 UE 일 수도 있다. 도 1 에서 나타낸 예에서, 릴레이 스테이션 (110r) 은 BS (110a) 및 UE (120r) 사이의 통신을 용이하게 하기 위해 BS (110a) 및 UE (120r) 와 통신할 수도 있다. 릴레이 스테이션은 또한 릴레이, 릴레이 eNB 등으로서 지칭될 수도 있다.

[0033]

무선 통신 네트워크 (100) 는 상이한 태입들의 BS 들, 예를 들어, 매크로 BS, 피코 BS, 펨토 BS, 릴레이들 등을 포함하는 이종 네트워크일 수도 있다. 이들 상이한 태입들의 BS 들은 무선 통신 네트워크 (100) 에서 상이한 송신 전력 레벨들, 상이한 커버리지 영역들, 및 간섭에 대한 상이한 영향을 가질 수도 있다. 예를 들어, 매크로 BS 는 높은 송신 전력 레벨 (예컨대, 20 와트) 을 가질 수도 있는 반면에, 피코 BS, 펨토 BS, 및 릴레이들은 보다 낮은 송신 전력 레벨 (예컨대, 1 와트) 을 가질 수도 있다.

[0034]

무선 통신 네트워크 (100) 는 동기적 또는 비동기적 동작을 지원할 수도 있다. 동기적 동작을 위해, BS 들은 유사한 프레임 타이밍을 가질 수도 있고, 상이한 BS 들로부터의 송신물들은 시간에서 대략적으로 정렬될 수도 있다. 비동기적 동작을 위해, BS 들은 상이한 프레임 타이밍을 가질 수도 있고, 상이한 BS 들로부터의 송신물들은 시간에서 정렬되지 않을 수도 있다. 본원에서 설명되는 기법들은 동기적 및 비동기적 양자의 동작을 위해 이용될 수도 있다.

[0035]

네트워크 제어기 (130) 는 BS 들의 셋트에 커플링될 수도 있고, 이들 BS 들에 대해 조정 및 제어를 제공할 수도 있다. 네트워크 제어기 (130) 는 백홀을 통해 BS 들 (110) 과 통신할 수도 있다. BS 들 (110) 은 또한, 예컨대 무선 또는 유선 백홀을 통해 직접적으로 또는 간접적으로, 서로 통신할 수도 있다.

[0036]

UE 들 (120) (예컨대, UE (120x), UE (120y) 등) 은 무선 통신 네트워크 (100) 전체에 걸쳐 분산될 수도 있고, 각 UE 는 정지형 또는 이동형일 수도 있다. UE 는 또한, 모바일 스테이션, 단말기, 액세스 단말, 가입자 유닛, 스테이션, 고객 백내 장치 (CPE), 셀룰러 폰, 스마트 폰, 퍼스널 디지털 어시스턴트 (PDA), 무선 모뎀, 무선 통신 디바이스, 핸드헬드 디바이스, 램프 컴퓨터, 코드리스 폰, 무선 로컬 루프 (WLL) 스테이션, 태블릿, 카메라, 게이밍 디바이스, 노트북, 스마트북, 울트라북, 의료 기기 또는 의료 장비, 생체측정 센서/디바이스, 스마트 위치, 스마트 의류, 스마트 안경, 스마트 손목 밴드, 스마트 장신구 (예컨대, 스마트 링, 스마트 팔찌 등) 와 같은 웨어러블 디바이스, 엔터테인먼트 디바이스 (예컨대, 뮤직 디바이스, 비디오 디바이스, 위성 라디오 등), 차량 컴퓨년트 또는 센서, 스마트 미터/센서, 산업용 제조 장비, 글로벌 포지셔닝 시스템 디바이스, 또는 무선 또는 유선 매체를 통해 통신하도록 구성되는 임의의 다른 적합한 디바이스로서 지칭될 수도 있다. 일부 UE 들은 진화형 또는 머신-타입 통신 (machine-type communication; MTC) 디바이스들 또는 진화형 MTC (eMTC) 디바이스들로 고려될 수도 있다. MTC 및 eMTC UE 들은, 예를 들어, BS, 다른 디바이스 (예컨대, 원격 디바이스), 또는 몇몇 다른 엔티티와 통신할 수도 있는 로봇들, 드론들, 원격 디바이스들, 센서들, 미터들, 모니터들, 위치 태그들 등을 포함한다. 무선 노드는, 예를 들어, 유선 또는 무선 통신 링크를 통해 네트워크 (예컨대, 인터넷과 같은 광역 네트워크 또는 셀룰러 네트워크) 에 대한 또는 그 네트워크에의 접속성을 제공할 수도 있다. 일부 UE 들은 사물 인터넷 (Internet-of-Things; IoT) 디바이스들로 고려될 수도 있다.

[0037]

도 1 에서, 이중 화살표들을 갖는 실선은, 다운링크 및/또는 업링크 상에서 UE 를 서빙하도록 지정된 BS 인 서빙 BS 및 UE 사이의 원하는 송신들을 나타낸다. 이중 화살표들을 갖는 미세 점선은 UE 및 BS 사이에서의 간섭하는 송신물들을 나타낸다.

- [0038] 특정 무선 네트워크들 (예컨대, LTE) 은 다운링크 상에서 직교 주파수 분할 멀티플렉싱 (OFDM) 을 그리고 업링크 상에서 단일-캐리어 주파수 분할 멀티플렉싱 (SC-FDM) 을 이용한다. OFDM 및 SC-FDM 은, 시스템 대역폭을, 톤들, 빈들 등으로도 보통 지정되는 다수 (K) 의 직교 서브캐리어들로 파티셔닝한다. 각 서브캐리어는 데이터로 변조될 수도 있다. 일반적으로, 변조 심볼들은 OFDM 에 있어서 주파수 도메인에서 그리고 SC-FDM 에 있어서 시간 도메인에서 전송된다. 인접하는 서브캐리어들 사이의 간격은 고정될 수도 있고, 서브캐리어들의 총 수 (K) 는 시스템 대역폭에 의존적일 수도 있다. 예를 들어, 서브캐리어들의 간격은 15kHz 일 수도 있고, 최소 리소스 할당 ("리소스 블록 (resource block)" (RB) 으로 불림) 은 12 서브캐리어들 (즉, 180kHz) 일 수도 있다. 결과적으로, 공칭 고속 푸리에 변환 (FFT) 사이즈는 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz, 또는 20 MHz 의 시스템 대역폭에 대해 각각 128, 256, 512, 1024 또는 2048 과 동일할 수도 있다. 시스템 대역폭은 또한 서브밴드들로 파티셔닝될 수도 있다. 예를 들어, 서브밴드는 1.08MHz (즉, 6 RB 들) 를 커버할 수도 있고, 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz, 또는 20 MHz 의 시스템 대역폭에 대해 각각 1, 2, 4, 8 또는 16 서브밴드들이 존재할 수도 있다.

- [0039] 본원에 기술된 예들의 양태들은 LTE 기술들과 연관될 수도 있지만, 본 개시의 양태들은 NR 과 같은 다른 무선 통신 시스템들과 함께 적용가능할 수도 있다.

- [0040] NR 은 업링크 및 다운링크 상에서 CP 를 갖는 OFDM 을 이용할 수도 있고, TDD 를 이용하여 하프-듀플렉스 동작에 대한 지원을 포함할 수도 있다. 100MHz 의 단일 컴포넌트 캐리어 대역폭이 지원될 수도 있다. NR RB 들은 0.1 ms 지속기간에 걸쳐 75kHz 의 서브캐리어 대역폭으로 12 개의 서브캐리어들에 걸칠 수도 있다. 각각의 라디오 프레임은 10ms 의 길이로 50 개의 서브프레임들로 이루어질 수도 있다. 결과적으로, 각 서브프레임은 0.2ms 의 길이를 가질 수도 있다. 각 서브프레임은 데이터 송신을 위한 링크 방향 (즉, 다운링크 또는 업링크) 을 나타낼 수도 있고, 각 서브프레임에 대한 링크 방향은 동적으로 전환될 수도 있다. 각 서브프레임은 DL/UL 데이터 및 DL/UL 제어 데이터를 포함할 수도 있다. NR 을 위한 UL 및 DL 서브프레임들은 도 6 및 도 7 과 관련하여 보다 자세히 이하에서 기술될 수도 있다. 범포밍이 지원될 수도 있고, 범 방향은 동적으로 구성될 수도 있다. 프리코딩을 이용한 MIMO 송신물들이 또한 지원될 수도 있다. DL 에서의 MIMO 구성은 UE 당 2 개까지의 스트리밍들 및 8 개 까지의 스트리밍들로 다중-계층 DL 송신물들로 8 개까지의 송신 안테나들을 지원할 수도 있다. UE 당 2 개까지의 스트리밍들로 다중-계층 송신물들이 지원될 수도 있다. 다중셀들의 어그리게이션은 8 개까지의 서빙 셀들로 지원될 수도 있다. 대안적으로, NR 은 OFDM 기반 이외의 상이한 에어 인터페이스를 지원할 수도 있다.

- [0041] 일부 예들에서, 에어 인터페이스에 대한 액세스가 스케줄링될 수도 있다. 스케줄링 엔티티 (scheduling entity) (예컨대, BS (110) 또는 UE (120)) 는 그것의 서비스 영역 또는 셀 내의 일부 또는 모든 디바이스들 및 장비 사이에 통신을 위한 리소스들을 할당한다. 본 개시 내에서, 이하에서 추가적으로 논의되는 바와 같이, 스케줄링 엔티티는 하나 이상의 종속 엔티티들에 대한 리소스들의 스케줄링, 할당, 재설정, 및 릴리스를 담당할 수도 있다. 즉, 스케줄링된 통신에 대해, 종속 엔티티들은 스케줄링 엔티티에 의해 할당된 리소스들을 이용한다. BS 들은 스케줄링 엔티티로서 기능할 수도 있는 유일한 엔티티들이 아니다. 즉, 일부 예들에서, UE 는, 하나 이상의 종속 엔티티들 (예컨대, 하나 이상의 다른 UE 들) 에 대해 리소스들을 할당하는 스케줄링 엔티티로서 기능할 수도 있다. 이 예에서, UE 는 스케줄링 엔티티로서 기능하고 있고, 다른 UE 들은 무선 통신을 위해 그 UE 에 의해 스케줄링된 리소스들을 이용한다. UE 는 피어-투-피어 (peer-to-peer; P2P) 네트워크에서, 및/또는 메쉬 네트워크 (mesh network) 에서 스케줄링 엔티티로서 기능할 수도 있다. 메쉬 네트워크 예에서, UE 들은 선택적으로, 스케줄링 엔티티와 통신하는 것에 추가하여 서로 직접 통신할 수도 있다.

- [0042] 따라서, 시간-주파수 리소스들에 대한 스케줄링된 액세스를 가지고 셀룰러 구성, P2P 구성, 및 메쉬 구성을 갖는 무선 통신 네트워크에서, 스케줄링 엔티티 및 하나 이상의 종속 엔티티들은 스케줄링된 리소스들을 이용하여 통신할 수도 있다.

- [0043] NR 라디오 액세스 네트워크 (RAN) 는 하나 이상의 중앙 유닛들 (CU) 및 분산된 유닛 (DU) 들을 포함할 수도 있다. NR BS (예컨대, gNB, 5G NB, NB, 5G NB, TRP, AP) 는 하나 이상의 다수의 BS 들에 대응할 수도 있다. NR 셀들은 액세스 셀들 (access cells; ACells) 또는 데이터 유일 셀들 (data only cells; DCells) 로서 구성될 수 있다. DCells 은 캐리어 어그리게이션 또는 이중 접속성을 위해 사용되지만 초기 액세스, 셀 선택/재선택, 또는 핸드오버를 위해서는 사용되지 않는 셀들일 수도 있다.

- [0044] 도 2 는 도 1 에서 예시된 무선 통신 시스템 (100) 에서 구현될 수도 있는 분산형 RAN (200) 의 일 예시적인 논리적 아키텍처 (logical architecture) 를 나타낸다. 5G 액세스 노드 (AN) (206) 는 액세스 노드 제어기

(ANC) (202) 를 포함할 수도 있다. ANC (202) 는 분산형 RAN (200) 의 CU 일 수도 있다. 차세대 코어 네트워크 (NG-CN) (204) 에 대한 백홀 인터페이스는 ANC (202) 에서 종단될 수도 있다. 이웃하는 차세대 액세스 노드 (NG-AN) 들에 대한 백홀 인터페이스는 ANC (202) 에서 종단될 수도 있다. ANC (202) 는 하나 이상의 TRP 들 (208) 을 포함할 수도 있다.

[0045] TRP 들 (208) 은 DU 들을 포함한다. TRP 들 (208) 은 하나의 ANC (ANC (202)) 또는 하나보다 많은 ANC (미 도시) 에 접속될 수도 있다. 예를 들어, RAN 공유, RaaS (radio as a service), 및 서비스 특정적 AND 전개들을 위해, TRP 는 하나보다 많은 ANC (202) 에 접속될 수도 있다. TRP (208) 는 하나 이상의 안테나 포트들을 포함할 수도 있다. TRP 들 (208) 은 UE (예컨대, UE (120)) 에 트래픽을 개별적으로 (예컨대, 동적 선택) 또는 함께 (예컨대, 연합 송신) 서빙하도록 구성될 수도 있다.

[0046] 분산형 RAN (200) 의 예시적인 논리적 아키텍처는 프론트홀 (fronthaul) 정의를 나타내기 위해 사용될 수도 있다. 논리적 아키텍처는 상이한 전개 타입들에 걸쳐 프론트홀링 솔루션들을 지원할 수도 있다. 예를 들어, 논리적 아키텍처는 송신 네트워크 능력들 (예컨대, 대역폭, 레이턴시, 및/또는 지터) 에 기초할 수도 있다. 논리적 아키텍처는 LTE 와 피처들 및/또는 컴포넌트들을 공유할 수도 있다. NG-AN (210) 은 NR 로 이중 접속성을 지원할 수도 있다. NG-AN (210) 은 LTE 및 NR 에 대해 공통의 프론트홀을 공유할 수도 있다. 논리적 아키텍처는 TRP 들 (208) 간의 및 사이의 협동 (cooperation) 을 가능하게 한다. 예를 들어, 협동은 TRP (208) 내에서 및/또는 ANC (202) 를 통해 TRP 들 (208) 에 걸쳐서 사전-구성될 수도 있다. TRP 간 인터페이스가 존재하지 않을 수도 있다.

[0047] 분산형 RAN (200) 을 위한 논리적 아키텍처는 분할된 논리적 기능들의 동적 구성을 포함할 수도 있다. 도 5 를 참조하여 보다 자세히 설명되는 바와 같이, 라디오 리소스 제어 (RRC) 계층, 패킷 데이터 수렴 프로토콜 (PDCP) 계층, 라디오 링크 제어 (RLC) 계층, 매체 액세스 제어 (MAC) 계층, 및 물리 (PHY) 계층들이 DU (예컨대, TRP (208)) 또는 CU (예컨대, ANC (202)) 에서 배치될 수도 있다.

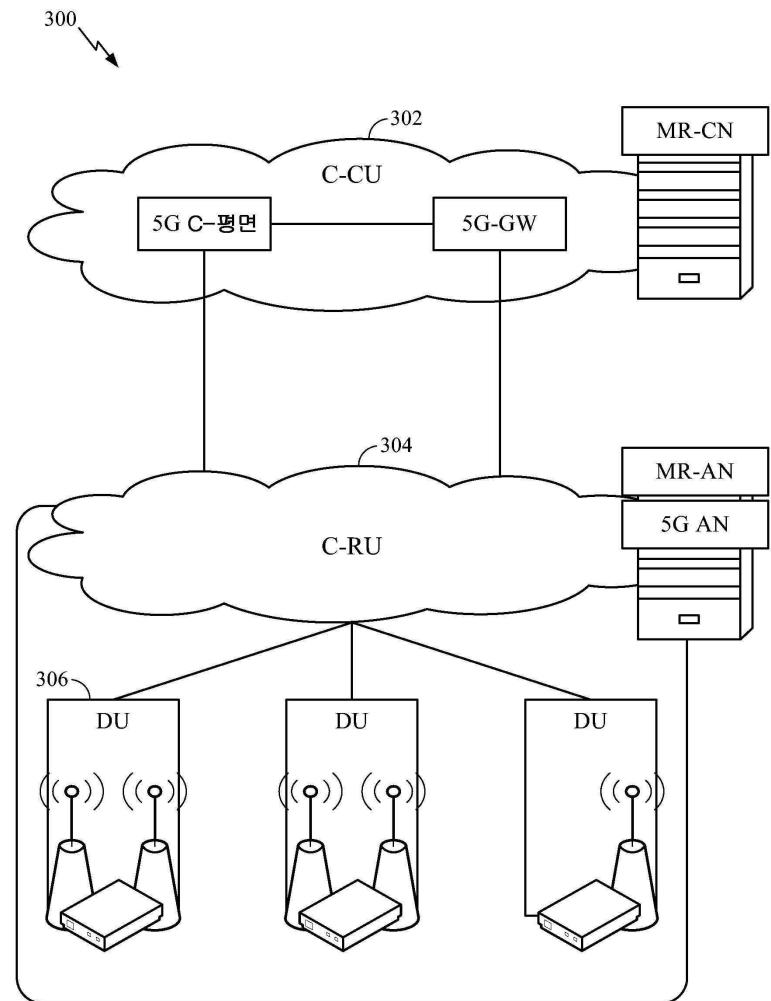

[0048] 도 3 은, 본 개시의 양태들에 따른, 분산형 RAN (300) 의 일 예시적인 물리적 아키텍처를 나타낸다. 도 3 에 도시된 바와 같이, 분산형 RAN (300) 은 중앙집중형 코어 네트워크 유닛 (C-CU) (302), 중앙집중형 RAN 유닛 (C-RU) (304), 및 DU (306) 를 포함한다.

[0049] C-CU (302) 는 코어 네트워크 기능들을 호스팅할 수도 있다. C-CU (302) 는 중앙집중적으로 배치될 수도 있다. C-CU (302) 기능성은 퍼크 용량을 핸들링하기 위한 노력으로 (예컨대, 어드밴스드 무선 서비스 (AWS) 로) 오프로딩될 수도 있다. C-RU (304) 는 하나 이상의 ANC 기능들을 호스팅할 수도 있다. 선택적으로, C-RU (304) 는 코어 네트워크 기능들을 로컬로 호스팅할 수도 있다. C-RU (304) 는 분산된 배치를 가질 수도 있다. C-RU (304) 는 네트워크 에지 부근에 위치될 수도 있다. DU (306) 는 하나 이상의 TRP 들 (에지 노드 (EN), 에지 유닛 (EU), 라디오 헤드 (RH), 스마트 라디오 헤드 (SRH) 등) 을 호스팅할 수도 있다. DU (306) 는 라디오 주파수 (RF) 기능성을 갖는 네트워크의 에지들에 위치할 수도 있다.

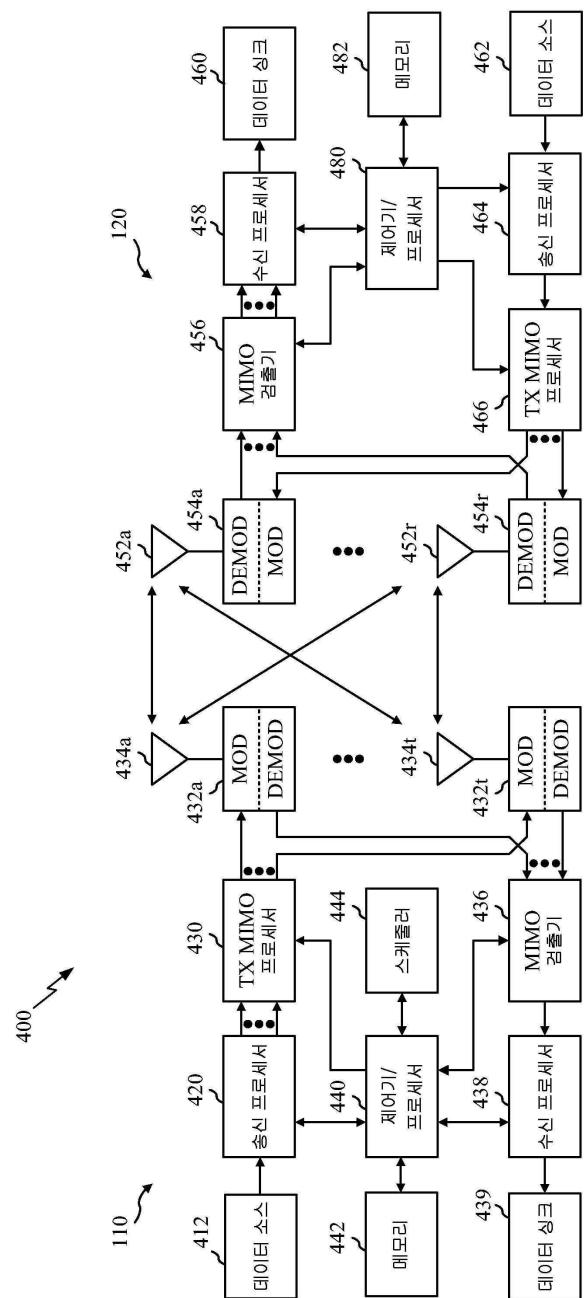

[0050] 도 4 는 고 성능의, 유연하고, 콤팩트한 LDPC 코딩을 위해 본 개시의 양태들을 실시하기 위해 사용될 수도 있는 도 1 에서 예시된 BS (110) 및 UE (120) 의 예시적인 컴포넌트들을 나타낸다. 도 4 에 나타낸 BS (110) 및 UE (120) 의 컴포넌트들 중 하나 이상은 본 개시의 양태들을 실시하기 위해 사용될 수도 있다. 예를 들어, UE (120) 의 안테나(들) (452a-452r), 복조기(들)/변조기(들) (454a-454r), TX MIMO 프로세서 (466), 수신 프로세서 (458), 송신 프로세서 (464), 및/또는 제어기/프로세서 (480) 및/또는 BS (110) 의 안테나(들) (434a-434t), 복조기(들)/변조기(들) (432a-432t), TX MIMO 프로세서 (430), 송신 프로세서 (420), 수신 프로세서 (438), 및/또는 제어기/프로세서 (440) 는 도 3 을 참조하여 예시되고 본원에 기술된 동작들 (1300) 을 수행하기 위해 사용될 수도 있다.

[0051] 제한된 연관 시나리오에 대해, BS (110) 는 도 1 에서의 매크로 BS (110c) 일 수도 있고, UE (120) 는 UE (120y) 일 수도 있다. BS (110) 는 또한 일부 다른 타입의 BS 일 수도 있다. BS (110) 는 안테나들 (434a 내지 434t) 을 구비할 수도 있고, UE (120) 는 안테나들 (452a 내지 452r) 을 구비할 수도 있다.

[0052] BS (110) 에서, 송신 프로세서 (420) 는 데이터 소스 (412) 로부터 데이터를 그리고 제어기/프로세서 (440) 로부터 제어 정보를 수신할 수도 있다. 제어 정보는 물리적 브로드캐스트 채널 (PBCH), 물리적 제어 포맷 표시자 채널 (PCFICH), 물리적 하이브리드 ARQ 표시자 채널 (PHICH), 물리적 다운링크 제어 채널 (PDCCH), 또는 다른 제어 채널 또는 신호에 대한 것일 수도 있다. 데이터는 물리적 다운링크 공유 채널 (PDSCH), 또는 다른 데이터 채널 또는 신호에 대한 것일 수도 있다. 송신 프로세서 (420) 는 데이터 심볼들 및 제어 심볼들

을 각각 획득하기 위해 데이터 및 제어 정보를 프로세싱 (인코딩 및 심볼 맵핑) 할 수도 있다. 예를 들어, 송신 프로세서 (420)는 이하에서 더 자세히 논의되는 LDPC 코드 설계들을 이용하여 정보 비트들을 인코딩할 수도 있다. 송신 프로세서 (420)는 또한, 예를 들어, 프라이머리 동기화 신호 (PSS), 세컨더리 동기화 신호 (SSS), 및 셀-특정적 레퍼런스 신호 (CRS)에 대해 레퍼런스 (reference) 심볼들을 생성할 수도 있다. 송신 (TX) 다중-입력 다중-출력 (MIMO) 프로세서 (430)는, 적용 가능한 경우, 데이터 심볼들, 제어 심볼들, 및/또는 레퍼런스 심볼들에 대한 공간적 프로세싱 (예컨대, 프리코딩)을 수행할 수도 있고, 출력 심볼 스트림들을 변조기 (MOD)들 (432a 내지 432t)에 제공할 수도 있다. 각각의 변조기 (432)는 출력 샘플 스트림을 획득하기 위해 (예컨대, OFDM 등에 대해) 각기의 출력 심볼 스트림을 프로세싱할 수도 있다. 각각의 변조기 (432)는 다운링크 신호를 획득하기 위해 출력 샘플 스트림을 추가로 프로세싱 (예컨대, 아날로그로의 변환, 증폭, 필터링, 및 상향변환) 할 수도 있다. 변조기들 (432a 내지 432t)로부터의 다운링크 신호들은 각각 안테나들 (434a 내지 434t)을 통해 송신될 수도 있다.

[0053] UE (120)에서, 안테나들 (452a 내지 452r)은 BS (110)로부터 다운링크 신호들을 수신할 수도 있고, 수신된 신호들을 복조기 (DEMOD)들 (454a 내지 454r)에 각각 제공할 수도 있다. 각각의 복조기 (454)는 각각의 수신된 신호를 컨디셔닝 (예컨대, 필터링, 증폭, 하향변환, 및 디지털화)하여 입력 샘플들을 획득할 수도 있다. 각각의 복조기 (454)는 (예컨대, OFDM 등에 대해) 입력 샘플들을 추가로 프로세싱하여 수신된 심볼들을 획득할 수도 있다. MIMO 검출기 (456)는 모든 복조기들 (454a 내지 454r)로부터 수신된 심볼들을 획득하고, 적용 가능한 경우, 그 수신된 심볼들에 대해 MIMO 검출을 수행하여, 검출된 심볼들을 제공할 수도 있다.

수신 프로세서 (458)는 검출된 심볼들을 프로세싱 (예컨대, 복조, 디인터리빙, 및 디코딩)하고, 데이터 싱크 (460)에 UE (120)에 대해 디코딩된 데이터를 제공하며, 디코딩된 제어 정보를 제어기/프로세서 (480)에 제공할 수도 있다.

[0054] 업링크 상에서, UE (120)에서, 송신 프로세서 (464)는 데이터 소스 (462)로부터의 (예컨대, 물리적 업링크 공유된 채널 (PUSCH) 또는 다른 데이터 채널 또는 신호에 대한) 데이터 및 제어기/프로세서 (480)로부터의 (예컨대, 물리적 업링크 제어 채널 (PUCCH) 또는 다른 제어 채널 또는 신호에 대한) 제어 정보를 수신 및 프로세싱 할 수도 있다. 송신 프로세서 (464)는 또한 레퍼런스 신호에 대해 레퍼런스 심볼들을 생성할 수도 있다.

송신 프로세서 (464)로부터의 심볼들은, 적용 가능한 경우, TX MIMO 프로세서 (466)에 의해 프리코딩되고, (예컨대, SC-FDM 등에 대해) 복조기들 (454a 내지 454r)에 의해 추가로 프로세싱되며, BS (110)에 송신될 수도 있다. BS (110)에서, UE (120)로부터의 업링크 신호들은 안테나들 (434)에 의해 수신되고, 변조기들 (432)에 의해 프로세싱되며, 적용 가능한 경우, MIMO 검출기 (436)에 의해 검출되며, 수신 프로세서 (438)에 의해 추가로 프로세싱되어, UE (120)에 의해 전송된 디코딩된 데이터 및 제어 정보를 획득할 수도 있다. 수신 프로세서 (438)는 디코딩된 데이터를 데이터 싱크 (439)에 그리고 디코딩된 제어 정보를 제어기/프로세서 (440)에 제공할 수도 있다.

[0055] 메모리 (442)는 BS (110)를 위해 데이터 및 프로그램 코드들을 저장할 수도 있고, 메모리 (482)는 UE (120)를 위해 데이터 및 프로그램 코드들을 저장할 수도 있다. 스케줄러 (444)는 다운링크 및/또는 업링크 상에서의 데이터 송신을 위해 UE들을 스케줄링할 수도 있다.

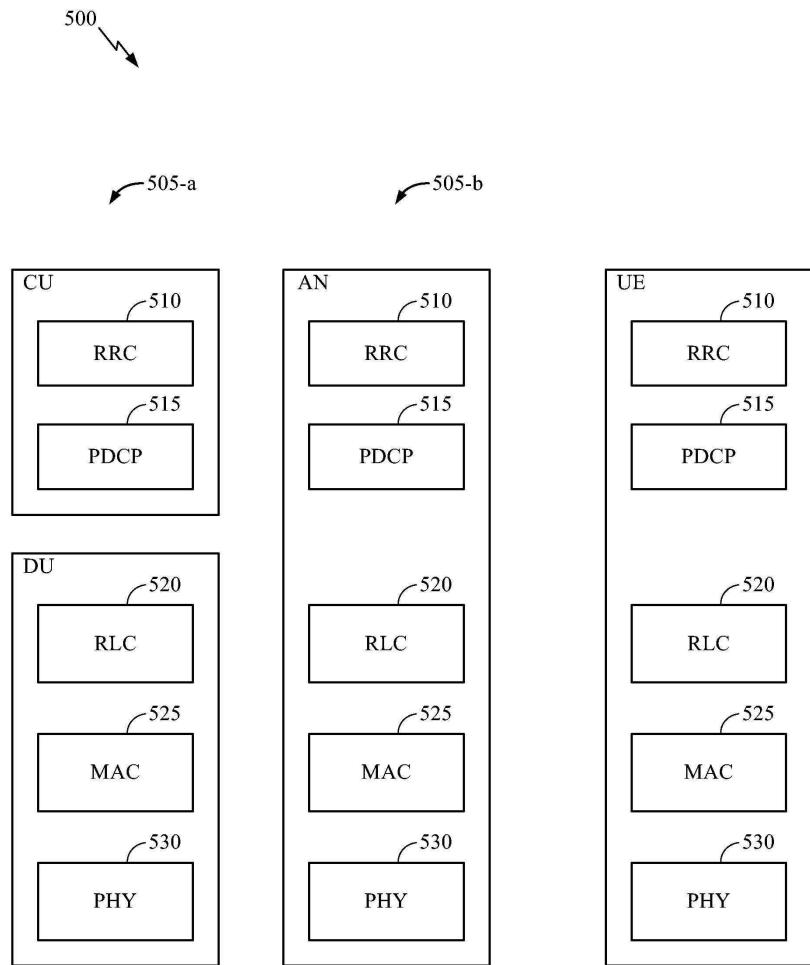

[0056] 도 5는, 본 개시의 양태들에 따른, 통신 프로토콜 스택을 구현하기 위한 예들을 보여주는 도 (500)를 예시한다. 예시된 통신 프로토콜 스택들은 5G 시스템 (예컨대, 업링크-기반 이동성을 지원하는 시스템)에서 동작하는 디바이스들에 의해 구현될 수도 있다. 도 (500)는 RRC 계층 (510), PDCP 계층 (515), RLC 계층 (520), MAC 계층 (525), 및 PHY 계층 (530)을 포함하는 통신 프로토콜 스택을 나타낸다. 일 예에서, 프로토콜 스택의 계층들은 소프트웨어의 개별적 모듈들, 프로세서 또는 ASIC의 부분들, 통신 링크에 의해 접속된 비-병치된 디바이스들의 부분들, 또는 이들의 다양한 조합들로서 구현될 수도 있다. 병치된 및 비-병치된 구현들은, 예를 들어, 네트워크 액세스 디바이스 (예컨대, AN 들, CU 들, 및/또는 DU 들) 또는 UE에 대해 프로토콜 스택에서 사용될 수도 있다.

[0057] 제 1 옵션 (505-a)은 프로토콜 스택의 분할 구현을 나타내고, 여기서, 프로토콜 스택의 구현은 중앙집중형 네트워크 액세스 디바이스 (예컨대, ANC (202))와 분산형 네트워크 액세스 디바이스 (예컨대, DU (208)) 사이에 분할된다. 제 1 옵션 (505-a)에서, RRC 계층 (510) 및 PDCP 계층 (515)은 CU에 의해 구현될 수도 있고, 그리고, RLC 계층 (520), MAC 계층 (525), 및 PHY 계층 (530)은 DU에 의해 구현될 수도 있다. 다양한 예들에서, CU 및 DU는 병치될 수도 있고, 또는 비-병치될 수도 있다. 제 1 옵션 (505-a)은 매크로 셀, 마이크로 셀, 또는 피코 셀 배치에서 유용할 수도 있다.

- [0058] 제 2 옵션 (505-b) 은 프로토콜 스택의 단일화된 구현을 나타내고, 여기서, 프로토콜 스택은 단일의 네트워크 액세스 디바이스 (예컨대, 액세스 노드 (AN), NR BS, NR NB, 네트워크 노드 (NN), TRP, gNB 등) 에서 구현된다. 제 2 옵션에서, RRC 계층 (510), PDCP 계층 (515), RLC 계층 (520), MAC 계층 (525), 및 PHY 계층 (530) 은 각각 AN 에 의해 구현될 수도 있다. 제 2 옵션 (505-b) 은 펨토 셀 배치에서 유용할 수도 있다.

- [0059] 네트워크 액세스 디바이스가 프로토콜 스택의 일부 또는 전부를 구현하는지 여부에 관계 없이, UE 는 전체 프로토콜 스택 (예컨대, RRC 계층 (510), PDCP 계층 (515), RLC 계층 (520), MAC 계층 (525), 및 PHY 계층 (530)) 을 구현할 수도 있다.

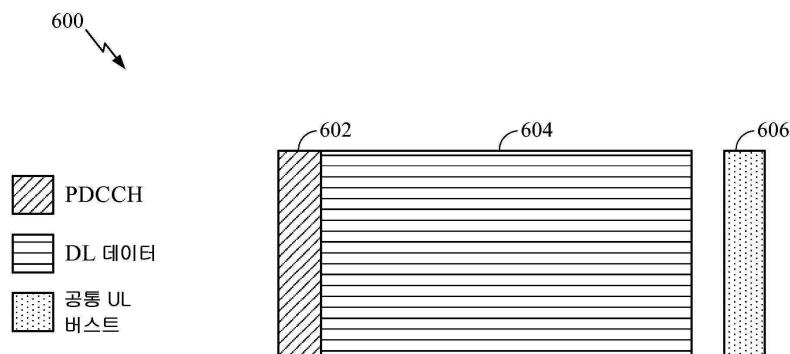

- [0060] 도 6 은 DL-중심 서브프레임 (600) 의 일 예를 나타내는 도이다. DL-중심 서브프레임 (600) 은 제어 부분 (602) 을 포함할 수도 있다. 제어 부분 (602) 은 DL-중심 서브프레임 (600) 의 초기 또는 시작 부분에 존재할 수도 있다. 제어 부분 (602) 은 DL-중심 서브프레임 (600) 의 다양한 부분들에 대응하는 다양한 스케줄링 정보 및/또는 제어 정보를 포함할 수도 있다. 일부 구성들에서, 제어 부분 (602) 은, 도 6 에서 도시된 바와 같이, 물리적 DL 제어 채널 (PDCCH) 일 수도 있다. DL-중심 서브프레임 (600) 은 또한 DL 데이터 부분 (604) 을 포함할 수도 있다. DL 데이터 부분 (604) 은 DL-중심 서브프레임 (600) 의 페이로드로서 지칭될 수도 있다. DL 데이터 부분 (604) 은 DL 데이터를 스케줄링 엔티티 (예컨대, UE 또는 BS) 로부터 종속 엔티티 (예컨대, UE) 로 통신하기 위해 이용되는 통신 리소스들을 포함할 수도 있다. 일부 구성들에서, DL 데이터 부분 (604) 은 물리적 DL 공유된 채널 (PDSCH) 일 수도 있다.

- [0061] DL-중심 서브프레임 (600) 은 또한 공통의 UL 부분 (606) 을 포함할 수도 있다. 공통 UL 부분 (606) 은 UL 버스트, 공통 UL 버스트, 및/또는 다양한 다른 적합한 용어들로서 지칭될 수도 있다. 공통 UL 부분 (606) 은 DL-중심 서브프레임 (600) 의 다양한 다른 부분들에 대응하는 피드백 정보를 포함할 수도 있다. 예를 들어, 공통 UL 부분 (606) 은 제어 부분 (602) 에 대응하는 피드백 정보를 포함할 수도 있다. 피드백 정보의 비-제한적 예들은 확인응답 (ACK) 신호, 부정적 확인응답 (NACK) 신호, HARQ 표시자, 및/또는 다양한 다른 적합한 타입들의 정보를 포함할 수도 있다. 공통 UL 부분 (606) 은, 추가적으로 또는 대안적으로, 랜덤 액세스 채널 (RACH) 프로시저들, 스케줄링 요청 (SR) 들, 및 다양한 다른 적합한 타입들의 정보에 관한 정보와 같은 정보를 포함할 수도 있다. 도 6 에서 예시된 바와 같이, DL 데이터 부분 (604) 은 공통 UL 부분 (606) 의 시작부로부터 시간에서 분리될 수도 있다. 이 시간 분리는 캡, 보호 기간, 보호 간격, 및/또는 다양한 다른 적합한 용어들로서 지칭될 수도 있다. 이러한 분리는 DL 통신 (예컨대, 종속 엔티티 (예컨대, UE) 에 의한 수신 동작) 으로부터 UL 통신 (예컨대, 종속 엔티티 (예컨대, UE) 에 의한 송신) 으로의 전환을 위한 시간을 제공한다. 전술한 것은 DL-중심 서브프레임의 단지 하나의 예일 뿐이고, 유사한 특징들을 갖는 대안적인 구조들이 본원에 기술된 양태들로부터 필수적으로 벗어나는 일 없이 존재할 수도 있다.

- [0062] 도 7 은 UL-중심 서브프레임 (700) 의 일 예를 나타내는 도이다. UL-중심 서브프레임 (700) 은 제어 부분 (702) 을 포함할 수도 있다. 제어 부분 (702) 은 UL-중심 서브프레임 (700) 의 초기 또는 시작 부분에 존재할 수도 있다. 도 7 에서의 제어 부분 (702) 은 도 6 을 참조하여 상기 설명된 제어 부분 (602) 과 유사할 수도 있다. UL-중심 서브프레임 (700) 은 또한 UL 데이터 부분 (704) 을 포함할 수도 있다. UL 데이터 부분 (704) 은 UL-중심 서브프레임 (700) 의 페이로드로서 지칭될 수도 있다. UL 데이터 부분 (704) 은 종속 엔티티 (예컨대, UE) 로부터 스케줄링 엔티티 (예컨대, UE 또는 BS) 로 UL 데이터를 통신하기 위해 이용되는 통신 리소스들을 지칭할 수도 있다. 일부 구성들에서, 제어 부분 (702) 은 PDCCH 일 수도 있다.

- [0063] 도 7 에서 예시된 바와 같이, 제어 부분 (702) 의 종단부는 UL 데이터 부분 (704) 의 시작부로부터 시간에서 분리될 수도 있다. 이 시간 분리는 캡, 보호 기간, 보호 간격, 및/또는 다양한 다른 적합한 용어들로서 지칭될 수도 있다. 이러한 분리는 DL 통신 (예컨대, 스케줄링 엔티티에 의한 수신 동작) 으로부터 UL 통신 (예컨대, 스케줄링 엔티티에 의한 송신) 으로의 전환을 위한 시간을 제공한다. UL-중심 서브프레임 (700) 은 또한 공통 UL 부분 (706) 을 포함할 수도 있다. 도 7 에서의 공통 UL 부분 (706) 은 도 6 을 참조하여 상기 설명된 공통 UL 부분 (606) 과 유사할 수도 있다. 공통 UL 부분 (706) 은, 추가적으로 또는 대안적으로, 채널 품질 표시자 (CQI), 사운딩 레퍼런스 신호 (SRS) 들, 및 다양한 다른 적합한 타입들의 정보에 관한 정보를 포함할 수도 있다. 전술한 것은 UL-중심 서브프레임의 단지 하나의 예일 뿐이고, 유사한 특징들을 갖는 대안적인 구조들이 본원에 기술된 양태들로부터 필수적으로 벗어나는 일 없이 존재할 수도 있다.

- [0064] 일부 상황들에서, 2 개 이상이 종속적 엔티티들 (예컨대, UE 들) 이 사이드링크 신호들을 이용하여 서로 통신할 수도 있다. 이러한 사이드링크 통신의 실세계 애플리케이션은 공공 안전, 근접 서비스, UE-대-네트워크 중

계, 차량-대-차량 (V2V) 통신, 사물 인터넷 (IoE) 통신, IoT 통신, 미션 크리티컬 메쉬, 및/또는 다양한 다른 적합한 애플리케이션들을 포함할 수도 있다. 일반적으로, 사이드링크 신호는, 스케줄링 엔티티가 스케줄링 및/또는 제어 목적들을 위해 이용될 수도 있음에도 불구하고, 스케줄링 엔티티 (예컨대, UE 또는 BS)를 통해 통신물을 중계함이 없이 하나의 종속 엔티티 (예컨대, UE1)로부터 다른 종속 엔티티 (예컨대, UE2)로 통신된 신호를 지정할 수도 있다. 일부 예들에서, 사이드링크 신호들은 (통상적으로 비허가 스펙트럼을 이용하는 무선 로컬 영역 네트워크들 (WLAN)과 달리) 허가된 스펙트럼을 이용하여 통신될 수도 있다.

[0065] UE는 전용 리소스들의 셋트를 이용하여 파일럿들을 송신하는 것과 연관된 구성 (예컨대, 라디오 리소스 제어 (RRC) 전용 스테이트 등) 또는 공통의 리소스들의 셋트를 이용하여 파일럿들을 송신하는 것과 연관된 구성 (예컨대, RRC 공통 스테이트)을 포함하는, 다양한 라디오 리소스 구성들에서 동작할 수도 있다. RRC 전용 스테이트에서 동작할 때, UE는 파일럿 신호를 네트워크에 송신하기 위해 전용 리소스들의 셋트를 선택할 수도 있다. RC 공통 스테이트에서 동작할 때, UE는 파일럿 신호를 네트워크에 송신하기 위해 리소스들의 공통 셋트를 선택할 수도 있다. 어느 경우에도, UE에 의해 송신된 파일럿 신호는 AN, 또는 DU, 또는 그것의 부분들과 같은 하나 이상의 네트워크 액세스 디바이스들에 의해 수신될 수도 있다. 각각의 수신 네트워크 액세스 디바이스는, 공통 리소스들의 셋트 상에서 송신된 파일럿 신호들을 수신 및 측정하고, 또한, 그 네트워크 액세스 디바이스가 UE에 대한 네트워크 액세스 디바이스들의 모니터링 셋트의 멤버인 UE들에 할당된 전용 리소스들의 셋트들 상에서 송신된 파일럿 신호들을 측정하도록 구성될 수도 있다. 수신 네트워크 액세스 디바이스들, 또는 수신 네트워크 액세스 디바이스(들)가 파일럿 신호들의 측정치들을 송신하는 CU 중 하나 이상은, UE들에 대한 서빙 셀들을 식별하기 위해서, 또는, UE들 중 하나 이상에 대한 서빙 셀의 변경을 개시하기 위해서 그 측정치들을 이용할 수도 있다.

#### 예시적인 에러 정정 코딩 퍼처들

[0067] 많은 통신 시스템들은 에러-정정 코드들을 이용한다. 구체적으로, 에러 정정 코드들은 데이터 스트림에 리던던시를 도입함으로써 이들 시스템들에서의 정보 전송의 고유한 신뢰불가능성 (unreliability)을 보상한다. 저 밀도 패리티 체크 (LDPC) 코드들은 반복 코딩 시스템을 이용하는 특정한 타입의 에러 정정 코드들이다. Gallager 코드들은 "정규 (regular)" LDPC 코드들의 조기 예이다. 정규 LDPC 코드들은 그 패리티 체크 매트릭스 ( $H$ )의 엘리먼트들 대부분이 '0'인 선형 블록 코드이다.

[0068] LDPC 코드들은, 이분 그래프 (bipartite graph)들 (종종 "Tanner 그래프들"로도 지칭됨)에 의해 표현될 수 있다. 이분 그래프들에서, 변수 노드들의 셋트는 코드워드의 비트들 (예를 들어, 정보 비트들 또는 시스템 비트들)에 대응하고, 체크 노드들의 셋트는 코드를 정의하는 패리티-체크 제약들의 셋트에 대응한다. 따라서, 그 그래프의 노드들은, 2개의 특유의 셋트들로 그리고 에지들이 2개의 상이한 타입들, 즉 변수 및 체크의 노드들을 접속하는 상태로 분리된다. 정규 그래프 또는 코드는 모든 변수 노드들이 동일한 차수를 가지고 모든 제약 노드들이 동일한 차수를 갖는 것이다. 이 경우에, 그 코드는 정규 코드이다. 다른 한편, 비정규 (irregular) 코드는 상이한 차수들의 제약 노드들 및/또는 변수 노드들을 갖는다. 예를 들어, 일부 변수 노드들은 차수 4의 것일 수도 있고, 다른 것들은 차수 3의 것일 수도 있고, 또 다른 것들은 차수 2의 것일 수도 있다.

[0069] "리프팅 (lifting)"은 LDPC 코드들로 하여금, 큰 LDPC 코드들과 통상적으로 연관된 복잡도를 또한 감소시키면서, 병렬적 인코딩 및/또는 디코딩 구현들을 이용하여 구현되는 것을 가능하게 한다. 보다 구체적으로, 리프팅은 보다 작은 베이스 코드의 다수의 카페들로부터 비교적 큰 LDPC 코드를 생성하기 위한 기법이다. 예를 들어, 리프팅된 LDPC 코드는 베이스 그래프의 다수 ( $Z$ )의 병렬적 카페들을 생성하고 그 다음에 베이스 그래프의 각 카페의 에지 클러스터들의 치환들을 통해 그 병렬적 카페들을 상호접속하는 것에 의해 생성될 수도 있다. 따라서, 더 큰 그래프가 "카페 및 치환" 동작에 의해 획득될 수 있고, 여기서, 다수의 카페들은 동일 타입의 버텍스들이 가까운 근접부에 있고 하지만 전체 그래프는 다수의 접속해제된 서브그래프들로 이루어져도록 중첩된다.

[0070] 리프팅된 그래프는, 프로토그래프로서 또한 지정될 수도 있는 이분 베이스 그래프 ( $G$ )를, 리프팅 사이즈, 또는 리프팅 사이즈 값으로서 지정될 수도 있는, 다수 회,  $Z$  카페함으로서 생성된다. 변수 노드 및 체크 노드는 그들이 그래프에서 "에지" (즉, 변수 노드 및 체크 노드를 접속하는 라인)에 의해 접속되면 "이웃들"로 간주된다. 추가로, 이분 베이스 그래프 ( $G$ )의 각각의 에지 ( $e$ )에 대해,  $G$ 의  $N$  카페들을 상호연결하기 위해 에지 ( $e$ )의  $Z$  카페들에 치환이 적용된다. 치환은 일반적으로, 리프팅 값으로서 지정될 수도 있는, 에지와 연관된 정수 값  $k$ 이다. 변수 노드 시퀀스와의 1-대-1 연관성을 갖는 비트 시퀀스는, 각각

의 체크 노드에 대해, 모든 이웃하는 변수 노드들과 연관된 비트들이 0 모듈로 2 가 되는 (즉, 그들이 짹수 개의 1들을 포함함) 경우 및 그런 경우에만, 유효 코드워드이다. 결과의 LDPC 코드는 이용된 치환들 (리프팅 값들) 이 순환적인 경우 준-순환적 (quasi-cyclic; QC) 일 수도 있다.

[0071] 도 8-8a 는 본 개시의 소정의 양태들에 따른, 일 예시적인 LDPC 코드의 그래픽적 및 매트릭스 표현들을 각각 도시한다. 예를 들어, 도 8 은 LDPC 코드를 표현하는 이분 그래프 (800) 를 도시한다. 이분 그래프 (800) 는 4 개의 체크 노드들 (820) (정사각형들로 표현됨) 에 접속된 5 개의 변수 노드들 (810) (원들로 표현됨) 의 셋트를 포함한다. 이분 그래프 (800) 에서의 에지들은 변수 노드들 (810) 을 체크 노드들 (820) 에 접속한다 (변수 노드들 (810) 을 체크 노드들 (820) 에 접속하는 라인들로 표현됨). 따라서, 이분 그래프 (800) 는,  $|E|=12$  에지들에 의해 접속된,  $|V|=5$  변수 노드들 및  $|C|=4$  체크 노드들로 이루어진다.

[0072] 이분 그래프 (800) 는 도 8a 에서 도시된 바와 같이 단순화된 인접 매트릭스에 의해 표현될 수도 있다. 매트릭스 표현 (800A) 은 패리티 체크 매트릭스 (parity check matrix; PCM) ( $H$ ) 및 코드워드 벡터 ( $x$ ) 를 포함하고, 여기서,  $x_1$  내지  $x_5$  는 코드워드 ( $x$ ) 의 비트들을 표현한다.  $H$  는 수신된 신호가 정상적으로 디코딩되었는지를 결정하기 위해 이용된다.  $H$  는  $j$  개의 체크 노드들에 대응하는  $C$  개의 행 (row) 들 및  $i$  개의 변수 노드들 (즉, 복조된 심볼) 에 대응하는  $V$  개의 열 (column) 들을 갖고, 여기서 행들은 식 (equation) 들을 표현하고 열들은 코드워드의 비트들을 표현한다. 도 8a 에서,  $H$  는 각각 이분 그래프 (800) 로부터의 4 개의 체크 노드들 및 5 개의 변수 노드들에 대응하는 4 개의 행들 및 5 개의 열들을 갖는다.  $j$ -번째 체크 노드가 에지에 의해  $i$ -번째 변수 노드에 접속되는 경우 (즉, 2 개의 노드들이 이웃들),  $H$  의  $i$ -번째 열에 그리고  $j$ -번째 행에는 1 이 존재한다. 즉,  $i$ -번째 행 및  $j$ -번째 열의 교차점은 에지가 대응하는 버텍스들을 조인하는 경우 "1" 그리고 어떤 에지도 없는 경우 "0" 을 포함한다. 코드워드 벡터 ( $x$ ) 는  $Hx=0$  인 경우 및 그런 경우에만 (예를 들어, 각각의 제약 노드에 대해, (변수 노드들과의 그들의 연관성을 통해) 그 제약에 이웃하는 비트들이 0 모듈로 2 로 합산되면 (즉, 그들이 짹수 개의 1 들을 포함하면)), 유효 코드워드를 표현한다. 따라서, 코드워드가 정확히 수신되는 경우,  $Hx=0 \pmod{2}$  이다. 코딩된 수신된 신호와  $H$  의 곱이 '0' 일 때, 이것은 어떤 에러도 발생하지 않았다는 것을 의미한다.

[0073] 복조된 심볼들 또는 변수 노드들의 수는 LDPC 코드 길이이다. 행 (열) 에서의 0 이 아닌 엘리먼트들의 수는 행 (열) 가중치  $dc(dv)$  로서 정의된다. 노드의 차수는 그 노드에 접속된 에지들의 수를 지칭한다. 예를 들어, 도 8 에서 도시된 바와 같이, 변수 노드 (801) 는 체크 노드들 (811, 812, 및 813) 에 에지들이 접속된 3 차의 접속성을 갖는다. 변수 노드 (802) 는 체크 노드들 (811, 813, 및 814) 에 에지들이 접속된 3 차의 접속성을 갖는다. 변수 노드 (803) 는 체크 노드들 (811 및 814) 에 에지들이 접속된 2 차의 접속성을 갖는다. 변수 노드 (804) 는 체크 노드들 (812 및 814) 에 에지들이 접속된 2 차의 접속성을 갖는다. 변수 노드 (805) 는 체크 노드들 (812 및 813) 에 에지들이 접속된 2 차의 접속성을 갖는다. 이 퍼처는, 변수 노드 (810) 에 따르는 에지들의 수가 대응하는 열에서의 1들의 수와 동일하고 변수 노드 차수 ( $d(v)$ ) 라 불리는 도 8a 에 도시된 H 매트릭스에서 예시된다. 유사하게, 체크 노드 (820) 와 접속된 에지들의 수는 대응하는 행에서의 1들의 수와 동일하고 체크 노드 차수  $d(c)$  라 불린다. 예를 들어, 도 8a 에서 도시된 바와 같이, 매트릭스  $H$  에서의 제 1 열은 변수 노드 (801) 에 대응하고, 열 (1, 1, 1, 0) 에서의 대응하는 엔트리들은 체크 노드들 (811, 812, 및 813) 에 대한 에지 접속들을 나타내는 한편, 0 은 체크 노드 (814) 에 대한 에지가 존재하지 않음을 나타낸다.  $H$  의 제 2, 제 3, 제 4, 및 제 5 열들에서의 엔트리들은 체크 노드들에 대한 변수 노드들 (802, 803, 804, 및 805) 의 에지 접속들을 각각 나타낸다.

[0074] 도 9 는 도 8 의 이분 그래프의 3 개의 카페들의 리프팅을 예시하는 이분 그래프 (900) 이다. 3 개의 카페들은 카페들 간에 유사 에지들을 치환함으로써 상호접속될 수도 있다. 치환들이 순환적 치환들에 한정되면, 결과의 그래프는 리프팅  $Z=3$  인 준-순환 LDPC 에 대응한다. 3 개의 카페들이 만들어진 원래의 그래프는 본 명세서에 베이스 그래프로 지칭된다. 베이스 그래프로부터 상이한 사이즈들의 그래프들을 도출하기 위해, 베이스 그래프에 "카페 및 치환" 연산이 적용될 수 있다.

[0075] 리프팅된 그래프의 대응하는 PCM 은  $Z \times Z$  매트릭스로 베이스 PCM 에서의 각각의 엔트리를 대체함으로써 베이스 그래프의 PCM 으로부터 구성될 수 있다. "0" 엔트리들 (베이스 에지들을 갖지 않는 것들) 은 0 매트릭스로 대체되고, (베이스 에지를 나타내는) 1 엔트리들은  $Z \times Z$  치환 매트릭스로 대체된다. 순환적 리프팅들의 경우에, 치환들은 순환적 치환들이다.

[0076] 순환적으로 리프팅된 LDPC 코드는 또한 이진 다항식 모듈로  $x^2 + 1$  의 링에 걸쳐 코드로서 인터프리팅될 수 있

다. 이 인터프리팅에서, 이진 다항식,  $(x) = b_0 + b_1x + b_2x^2 + \dots + b_{z-1}x^{z-1}$  은 베이스 그래프에서 각각의 변수 노드에 연관될 수도 있다. 이진 벡터  $(b_0, b_1, b_2, \dots, b_{z-1})$  는 리프팅된 그래프에서 변수 노드들에 대응하는  $Z$ , 즉, 단일 베이스 변수 노드의  $Z$  카피들에 연관된 비트들에 대응한다. 이진 벡터의 (그래프에서 예지들에 연관된 리프팅 값으로서 지정된)  $k$  에 의한 순환적 치환은 대응하는 이진 다항식을  $x^k$  에 의해 곱함으로써 달성되고, 여기서, 곱셈이 모듈로  $x^z + 1$ 에 취해진다. 베이스 그래프에서의 차수  $d$  패리티 체크는 이웃하는 이진 다항식들  $B_1(x), \dots, B_d(x)$ 에 대한 선형 제약으로서 인터프리팅될 수 있고,  $x^{k_1}B_1(x) + x^{k_2}B_2(x) + \dots + x^{k_d}B_d(x) = 0^{x^{k_1}}B_1(x) + x^{k_2}B_2(x) + \dots + x^{k_d}B_d(x) = 0$  으로서 쓰여지고, 값들  $k_1, \dots, k_d$ 는 대응하는 예지들에 연관된 순환적 리프팅 값들이다.

[0077] 이 결과적인 식은 베이스 그래프에서 단일의 연관된 패리티 체크에 대응하는 순환적으로 리프팅된 Tanner 그래프에서의  $Z$  패리티 체크들과 동등하다. 따라서, 리프팅된 그래프에 대한 패리티 체크 매트릭스는, 1 엔트리들은 품  $x^k$ 의 단항식들로 대체되고 0 엔트리들은 0으로서 리프팅되지만, 이제 0은 0이진 다항식 모듈로  $x^z + 1$ 로서 인터프리팅되는, 베이스 그래프에 대한 매트릭스를 이용하여 표현될 수 있다. 이러한 매트릭스는  $x^k$  대신에 값  $k$ 를 제공함으로써 쓰여질 수도 있다. 이 경우에, 0 다항식은 그것을  $x^0$ 로부터 구별하기 위해 때로는 "-1"로서 그리고 때로는 다른 문자로서 표현된다.

[0078] 통상적으로, 패리티 체크 매트릭스의 정사각형 서브매트릭스는 코드의 패리티 비트들을 나타낸다. 상보적 열들은 인코딩 시에 인코딩될 정보 비트들과 동일하게 설정되는 정보 비트들에 대응한다. 인코딩은 패리티 체크 방정식들을 만족하기 위해 전술된 정사각형 서브매트릭스에서 변수들에 대해 품으로써 달성될 수도 있다. 매트릭스  $H$ 는 2개의 파트를  $M$  및  $N$ 으로 파티셔닝될 수도 있고, 여기서,  $M$ 은 정사각형 부분이다. 따라서, 인코딩은  $M_c = s = Nd$ 를 푸는 것으로 감소되고, 여기서,  $c$  및  $d$ 는  $x$ 를 포함한다. 준-순환적 코드들, 또는 순환적으로 리프팅된 코드들의 경우에, 상기 대수학은 이진 다항식 모듈로  $x^z + 1$ 의 링에 결친 것으로서 인터프리팅될 수 있다. 준-순환적인 802.11 LDPC 코드들의 경우에, 서브매트릭스  $M$ 을 인코딩하는 것은 도 10에서 도시된 것과 같은 정수 표현을 갖는다.

[0079] 수신된 LDPC 코드워드는 원래의 코드워드의 복원된 버전을 생성하기 위해 디코딩될 수 있다. 여러들의 부재에서, 또는 정정가능한 여러들의 경우에, 디코딩은 인코딩되었던 원래의 데이터 유닛을 복구하는데 이용될 수 있다. 리던던트 비트들은 비트 여러들을 검출 및 정정하기 위해 디코더들에 의해 이용될 수도 있다. LDPC 디코더(들)는 일반적으로, 반복적으로 로컬 계산들을 수행하고 그리고 그 결과들을, 예지들을 따라, 이분 그래프 (800) 내에서 메시지들을 교환하고 이를 메시지들을 인입 메시지들에 기초하여 그 노드들에서 계산들을 수행하는 것에 의해 업데이트함으로써 전달하는 것에 의해 동작한다. 이들 단계들은 통상적으로 수 회 반복될 수도 있다. 예를 들어, 그래프 (800)에서의 각각의 변수 노드 (810)에는 초기에, 통신 채널로부터의 관측들에 의해 결정된 바와 같은 연관된 비트의 값의 추정치를 표시하는 "소프트 비트" (예를 들어, 코드워드의 수신된 비트를 표현함) 가 제공될 수도 있다. 이들 소프트 비트들을 이용하면 LDPC 디코더들은 반복적으로 그들, 또는 그 일부 부분을 메모리로부터 편독하고 업데이트된 메시지, 또는 그 일부 부분을 다시 메모리에 기록함으로써 메시지들을 업데이트할 수도 있다. 업데이트 동작들은 통상적으로 대응하는 LDPC 코드의 패리티 체크 제약들에 기초한다. 리프팅된 LDPC 코드들에 대한 구현들에서, 유사 예지들에 대한 메시지들은 종종 병렬로 프로세싱된다.

[0080] 고속 애플리케이션들을 위해 설계된 LDPC 코드들은 종종 인코딩 및 디코딩 동작들에서 높은 병렬성을 지원하기 위해 큰 리프팅 팩터들 및 상대적으로 작은 베이스 그래프들을 가진 준-순환 구성을 이용한다. 더 높은 코드 레이트들 (예를 들어, 메시지 길이 대 코드워드 길이의 비율)을 가진 LDPC 코드들은 상대적으로 더 적은 패리티 체크들을 가지는 경향이 있다. 베이스 패리티 체크들의 수가 변수 노드의 차수 (예를 들어, 변수 노드에 접속된 예지들의 수) 보다 더 작다면, 베이스 그래프에서, 그 변수 노드는 2개 이상의 예지들에 의해 베이스 패리티 체크들 중 적어도 하나에 접속된다 (예를 들어, 변수 노드는 "더블 예지"를 가질 수도 있다). 베이스 패리티 체크들의 수가 변수 노드의 차수 (예를 들어, 변수 노드에 접속된 예지들의 수) 보다 더 작다면, 베이스 그래프에서, 그 변수 노드는 2개 이상의 예지들에 의해 베이스 패리티 체크들 중 적어도 하나에 접속된다. 2개 이상의 예지들에 의해 접속된 베이스 변수 노드 및 베이스 체크 노드를 갖는 것은 일반

적으로 병렬 하드웨어 구현 목적들을 위해 바람직하지 않다. 예를 들어, 이러한 더블 에지들은 동일한 메모리 로케이션들에의 다중 동시 판독 및 기록 동작들을 초래할 수도 있고, 이는 결국 데이터 코히어런시 문제들을 생성할 수도 있다. 베이스 LDPC 코드에서의 더블 에지는 단일 병렬 패리티 체크 업데이트 동안 두번 동일한 소프트 비트 값 메모리 로케이션의 병렬 판독을 트리거할 수도 있다. 따라서, 추가적인 회로부는 통상적으로, 양자의 업데이트들을 적절히 통합하도록, 메모리에 다시 기록되는 소프트 비트 값들을 결합할 필요가 있다. LDPC 코드에서의 더블 에지들을 제거하는 것은 이 가외의 복잡성을 회피하는 것을 돋는다.

[0081] 순환 리프팅에 기초한 LDPC 코드 설계들은 다항식 모듈로의 링에 걸친 코드들이 이진 다항식 모듈로  $(x^Z - 1)$  일 수도 있는 것으로서 인터프리팅될 수 있고, 여기서  $Z$ 는 리프팅 사이즈 (예를 들어, 준-순환 코드에서의 사이클의 사이즈)이다. 따라서, 이러한 코드들을 인코딩하는 것은 종종 이 링에서 대수적 연산으로서 인터프리팅 될 수 있다.

[0082] 표준 비정규 LDPC 코드 양상블들 (차수 분포들)의 정의에서, Tanner 그래프 표현에서의 모든 에지들은 통계적으로 상호교환 가능할 수도 있다. 다시 말해서, 단일 통계적 동등 클래스의 에지들이 존재한다. 멀티-에지 LDPC 코드들에 대해, 다수의 동등 클래스들의 에지들이 가능할 수도 있다. 표준 비정규 LDPC 양상블 정의에서, 그래프에서의 노드들 (변수 및 제약 양자 모두)은 그들의 차수, 즉 그들이 접속되는 에지들의 수에 의해 특정되지만, 멀티-에지 타입 설정에서, 에지 차수는 벡터이다; 그것은 독립적으로 각각의 에지 동등 클래스 (타입)로부터 노드에 접속된 에지들의 수를 특정한다. 멀티-에지 타입 양상블은 유한 수의 에지 타입들로 구성된다. 제약 노드의 차수 타입은 (비-음의) 정수들의 벡터이다; 이 벡터의  $i$ -번째 엔트리는 이러한 노드에 접속된  $i$ -번째 타입의 소켓들의 수를 래코딩한다. 이 벡터는 에지 차수로 지칭될 수도 있다. 변수 노드의 차수 타입은 2 개의 파트들을 가지지만 그것은 (비-음의) 정수들의 벡터로서 보여질 수 있다. 제 1 파트는 수신된 분포에 관한 것이고 수신된 차수라 불릴 것이고 제 2 파트는 에지 차수를 특정한다. 에지 차수는 제약 노드들에 대해 동일한 역할을 한다. 에지들은 그들이 동일한 타입의 소켓들을 한 쌍으로 할 때 타입화 (typing) 된다. 소켓들이 유사 타입의 소켓들과 한 쌍을 이루어야 하는 제약은, 멀티-에지 타입 개념을 특성화한다. 멀티-에지 타입 디스크립션에서, 상이한 노드 타입들은 상이한 수신된 분포들을 가질 수 있다 (예를 들어, 연관된 비트들은 상이한 채널들을 거칠 수도 있다).

[0083] 평처링은 더 짧은 코드워드를 생성하기 위해 코드워드로부터 비트들을 제거함으로써 수행된다. 따라서, 평처링된 변수 노드들은 실제로 송신되지 않은 코드워드 비트들에 대응한다. LDPC 코드에서 변수 노드를 평처링하는 것은 체크 노드를 또한 효과적으로 제거하면서, (예를 들어, 비트의 제거로 인해) 단축된 코드를 생성한다. 구체적으로, 평처링될 변수 노드가 (예컨대, 행 결합에 의해) 1 의 차수를 갖는, 평처링될 비트들을 포함하는, LDPC 코드의 매트릭스 표현에 대해, 변수 노드를 평처링하는 것은 코드로부터 연관된 비트를 제거하고 그래프로부터 그 단일 이웃하는 체크 노드를 효과적으로 제거한다. 그 결과, 그래프에서의 체크 노드들의 수는 1 쪽 감소된다. 평처링은 평처링 패턴에 따라 수행될 수 있다. 평처링 패턴은 평처링될 비트들을 특정한다.

[0084] 도 11 은 본 개시의 소정의 양태들에 따른, 인코더를 예시하는 단순화된 블록도이다. 도 11 은 무선 송신을 위해 인코딩된 메시지를 포함하는 신호를 제공하도록 구성될 수도 있는 라디오 주파수 (RF) 모뎀 (1150)의 부분을 예시하는 단순화된 블록도 (1100)이다. 하나의 예에서, BS (110) (또는 역방향 경로 상의 UE (120))에서의 콘볼루션 인코더 (1102)는 송신을 위한 메시지 (1120)를 수신한다. 메시지 (1120)는 수신 디바이스로 향한 데이터 및/또는 인코딩된 보이스 또는 다른 콘텐츠를 포함할 수도 있다. 인코더 (1102)는 BS (110) 또는 다른 네트워크 엔티티에 의해 정의된 구성에 기초하여 통상 선택된, 적합한 변조 및 코딩 스Kim (MCS)을 이용하여 메시지를 인코딩한다. 인코더 (1102)에 의해 생성된 인코딩된 비트스트림 (1122)은 그 후 별도의 디바이스 또는 컴포넌트일 수도 있거나, 또는 인코더 (1102) 와 통합될 수도 있는, 평처링 모듈 (1104)에 의해 선택적으로 평처링될 수도 있다. 평처링 모듈 (1104)은 비트스트림이 송신 이전에 평처링 되어야 하거나, 또는 평처링 없이 송신되어야 한다고 결정할 수도 있다. 비트스트림 (1122)을 평처링하기 위한 판정은 통상적으로 네트워크 컨디션들, 네트워크 구성, RAN 정의된 선호도들, 및/또는 다른 이유들에 기초하여 행해진다. 비트스트림 (1122)은 평처링 패턴 (1112)에 따라 평처링되고 메시지 (1120)를 인코딩하는데 이용될 수도 있다. 평처링 모듈 (1104)은 안테나 (1110)를 통한 송신을 위해 RF 신호 (1128)를 생성하기 위해 Tx 체인 (1108)에 의해 변조, 증폭 및 다르게는 프로세싱되는 Tx 심볼들 (1126)의 시퀀스를 생성하는 맵퍼 (1106)에 출력 (1124) 을 제공한다.

[0085] 평처링 모듈 (1104)의 출력 (1124) 은, 모뎀 부분 (1150) 이 비트스트림 (1122) 을 평처링하도록 구성되는지

여부에 따라, 평처링되지 않은 비트스트림 (1122) 또는 비트스트림 (1122) 의 평처링된 버전일 수도 있다. 하나의 예에서, 패리티 및/또는 다른 에러 정정 비트들은 RF 채널의 제한된 대역폭 내에서 메시지 (1120) 를 송신하기 위하여 인코더 (1102) 의 출력 (1124) 에서 평처링될 수도 있다. 다른 예에서, 비트스트림은 메시지 (1120) 를 송신하는데 필요한 전력을 감소시키거나, 간섭을 회피하거나, 또는 다른 네트워크 관련 이유들로 평처링될 수도 있다. 이를 평처링된 코드워드 비트들은 송신되지 않는다.

[0086] LDPC 코드워드들을 디코딩하는데 이용되는 디코더들 및 디코딩 알고리즘들은 에지들을 따라 그래프 내에서 메시지들을 교환하고 이를 메시지들을 인입 메시지들에 기초하여 노드들에서 계산들을 수행하는 것에 의해 업데이트 함으로써 동작한다. 그래프에서의 각각의 변수 노드에는 처음에, 예를 들어, 통신 채널로부터의 관측들에 의해 결정된 바와 같은 연관된 비트의 값의 추정치를 표시하는, 수신된 값이라 불리는, 소프트 비트가 제공된다. 이상적으로, 별도의 비트들에 대한 추정치들은 통계적으로 독립적이다. 이 이상은 실제로 위반될 수도 있다. 수신된 워드는 수신된 값들의 콜렉션으로 구성된다.

[0087] 도 12 는 본 개시의 소정의 양태들에 따른, 디코더를 예시하는 단순화된 블록도이다. 도 12 는 평처링된 인코딩된 메시지를 포함하는 무선으로 송신된 신호를 수신 및 디코딩하도록 구성될 수도 있는 RF 모뎀 (1250) 의 일부를 예시하는 단순화된 개략도 (1200) 이다. 평처링된 코드워드 비트들은 소거된 것으로서 취급될 수도 있다. 예를 들어, 평처링된 노드들의 LLR들은 초기화에서 "0" 으로 설정될 수도 있다. 다양한 예들에서, 신호를 수신하는 모뎀 (1250) 은 UE 예, BS 예, 또는 설명된 기능들을 수행하기 위한 임의의 다른 적합한 장치 또는 수단에 상주할 수도 있다. 안테나 (1202) 는 액세스 단말기에 RF 신호 (1220) 를 제공한다.

RF 채인 (1204) 은 RF 신호 (1220) 를 프로세싱 및 복조하고 인코딩된 메시지를 나타내는 비트스트림 (1224) 을 생성하는 디맵퍼 (1206) 에 심볼들 (1222) 의 시퀀스를 제공할 수도 있다.

[0088] 디맵퍼 (1206) 는 디평처링된 비트스트림 (1224) 을 제공할 수도 있다. 하나의 예에서, 디맵퍼 (1206) 는 평처링된 비트들이 송신기에 의해 삭제되었던 비트스트림에서의 로케이션들에 널 값들을 삽입하도록 구성될 수 있는 디평처링 모듈을 포함할 수도 있다. 디평처링 모듈은 송신기에서 평처링된 비트스트림을 생성하는데 이용되는 평처 패턴 (1210) 이 알려질 때 이용될 수 있다. 평처 패턴 (1210) 은 콘볼루션 디코더 (1208) 에 의해 비트스트림 (1224) 의 디코딩 동안 무시될 수도 있는 LLR들 (1228) 을 식별하는데 이용될 수 있다. LLR들은 비트스트림 (1224) 에서의 디평처링된 비트 로케이션들의 세트와 연관될 수도 있다. 이에 따라, 디코더 (1208) 는 식별된 LLR들 (1228) 을 무시함으로써 감소된 프로세싱 오버헤드를 가진 디코딩된 메시지 (1226) 를 생성할 수도 있다. LDPC 디코더는 패리티 체크 또는 변수 노드 동작들을 병렬로 수행하기 위해 복수의 프로세싱 엘리먼트들을 포함할 수도 있다. 예를 들어, 리프팅 사이즈 Z 인 코드워드를 프로세싱할 때, LDPC 디코더는 리프팅된 그래프의 모든 Z 에지들에 대해 동시에 패리티 체크 동작들을 수행하기 위해 다수 (Z) 의 프로세싱 엘리먼트들을 활용할 수도 있다.

[0089] 디코더 (1208) 의 프로세싱 효율은 평처링된 비트스트림 (1222) 에서 송신된 메시지에서의 평처링된 비트들에 대응하는 LLR들 (1228) 을 무시하도록 디코더 (1208) 를 구성함으로써 개선될 수도 있다. 평처링된 비트스트림 (1222) 은 인코딩된 메시지로부터 제거될 소정의 비트들을 정의하는 평처링 스킴에 따라 평처링되었을 수도 있다. 하나의 예에서, 소정의 패리티 또는 다른 에러-정정 비트들이 제거될 수도 있다. 평처링 패턴은 각각의 메시지에서 평처링될 비트들의 로케이션을 식별하는 평처링 매트릭스 또는 테이블로 표현될 수도 있다. 평처링 스킴은 통신 채널 상의 데이터 레이트들에의 및/또는 네트워크에 의해 설정된 송신 전력 제한들에의 준수를 유지하면서 메시지 (1226) 를 디코딩하는데 이용되는 프로세싱 오버헤드를 감소시키도록 선택될 수도 있다. 결과의 평처링된 비트스트림은 통상적으로 높은 레이트의 에러-정정 코드의 에러-정정 특성들을 보이지만, 리던던시가 더 적다. 이에 따라, 평처링은 채널 컨디션들이 상대적으로 높은 신호 대 잡음비를 생성할 때 수신기에서의 디코더 (1208) 에서 프로세싱 오버헤드를 감소시키도록 효과적으로 채용될 수도 있다.

[0090] 콘볼루션 디코더 (1208) 는 콘볼루션 코드를 이용하여 인코딩된 비트스트림으로부터 m-비트 정보 스트링들을 디코딩하는데 이용될 수도 있다. 디코더 (1208) 는 Viterbi 디코더, 대수 디코더, 또는 다른 적합한 디코더를 포함할 수도 있다. 하나의 예에서, Viterbi 디코더는 수신된 비트스트림 (1224) 에 대응하는 시그널링 상태들 중 가장 가능성있는 시퀀스 (Viterbi 경로) 를 발견하도록 잘 알려진 Viterbi 알고리즘을 채용한다. 비트스트림 (1224) 은 비트스트림 (1224) 에 대해 계산된 LLR들의 통계 분석에 기초하여 디코딩될 수도 있다. 하나의 예에서, Viterbi 디코더는 비트스트림 (1224) 으로부터 LLR들을 생성하기 위해 우도비 테스트를 이용하여 시그널링 상태들의 시퀀스를 정의하는 정확한 Viterbi 경로를 비교 및 선택할 수도 있다. 우도비들은 어느 경로가 비트스트림 (1224) 을 생성한 심볼들의 시퀀스를 고려할 가능성이 더 큰지를 결정하기 위해 각각의 후보 Viterbi 경로에 대한 우도비의 로그 (즉, LLR) 를 비교하는 우도비 테스트를 이용하여 복수의 후보

Viterbi 경로들의 피트 (fit) 를 통계적으로 비교하는데 이용될 수 있다.

[0091] 수신기에서, 평처링되지 않은 비트스트림들을 디코딩하기 위해 이용되는 동일한 디코더는 통상적으로, 얼마나 많은 비트들이 평처링되었는지에 상관없이, 평처링된 비트스트림들을 디코딩하기 위해 이용될 수 있다. 종래의 수신기들에서, LLR 정보는 통상적으로, 평처링된 상태들 또는 포지션들에 대한 LLR들 (디평처링된 LLR들) 을 0들로 채움으로써 디코딩이 시도되기 전에 디-평처링된다. 디코더는 어떤 정보도 효과적으로 반송하지 않는 디-평처링된 LLR들을 무시할 수도 있다.

[0092] 예시적인 강화된 평처링 및 LDPC 코드 구조 피쳐들

[0093] 무선 송신을 위해 의도된 저-밀도 패리티-체크 (LDPC) 코드들에 대한 바람직한 특성들 중 하나는 가우시안 잡음 채널들 및 페이딩 채널들 양자에 대한 높은 성능이다. 변수 노드들의 최대 차수 (예컨대, 그래프에서의 체크 노드들에 대한 그래프에서의 변수 노드들의 접속성의 차수 또는 접속들의 수) 는 (예컨대, 레퍼런스 LDPC 코드에 비해) 매우 크지 않은 것이 또한 바람직하다.

[0094] 특정 시스템들 (예컨대, 802.11n, 802.11ad, WiMAX, ATSC 등) 은 멀티-에지 타입 LDPC 코드 구조를 이용할 수도 있다. 멀티-에지 타입 LDPC 코드들은 표준 비정규 LDPC 코드들에 비해 이점들을 가질 수도 있다. 예를 들어, 멀티-에지 타입 LDPC 코드 구조는 표준 비정규 LDPC 코드들보다 많이 더 많은 차수들의 자유도를 제공할 수도 있고, 이는 훌륭한 성능, 낮은 인코딩/디코딩 복잡도, 및/또는 다른 바람직한 특성들로 코드들을 설계하기 위해 이용될 수 있다.

[0095] 멀티-에지 타입 구조들은 고-차수 평처링된 변수 노드들을 설계 내로 도입하여 용량에 대한 갑이 경계진 노드 차수들로 감소될 수 있도록 한다. 비록 평처링된 노드들이 매칭 조건으로서 알려진 설계 목표를 달성하기 위해 도움이 되지만, 평처링된 노드들은 반복적 디코더로 하여금 디코딩 프로세스의 시작부에서 느리게 할 수 있다. 예를 들어, 평처링된 노드들은, 밖으로의 에지들을 따라 소거 정보를 전송해 내보내서, 연결된 체크 노드들로 하여금 처음 몇 번의 반복들에서 적은 정보를 밖으로 전송하게 하거나 정보를 밖으로 전송하지 않게 한다. 리프팅된 LDPC 코드들의 맥락에서, 비교적 작은 베이스 코드를 리프팅 (예컨대, 카피) 함으로써 구성된 코드에 대해, 베이스 코드는 적은 더블 에지들을 가지거나 더블 에지들을 가지지 않는 것 (예컨대, 2 개의 에지들에 의해 체크 노드에 접속된 변수 노드) 이 종종 바람직하다. 높은 차수 변수 노드들은 많은 체크 노드들에 접속되기 때문에, 높은 차수 변수 노드들은, 예를 들어, 체크 노드들의 수가 비교적 작을 때 보다 높은 레이트들에서, 더블 에지들의 생성을 초래할 수도 있다.

[0096] LDPC 코드들에 대한 또 다른 바람직한 특성은 하이브리드 자동 반복 요청 (hybrid automatic repeat request; HARQ) 확장들에 대한 지원이다. HARQ 확장들은 1-차 변수 노드의 추가로 추가적인 패리티 비트들을 추가하는 것 및 기존의 패리티 체크들을 분할하는 것을 수반할 수 있다. 분할의 양 절반들이 평처링된 변수 노드에 접속되는 경우에, 이는 원하는 성능을 달성하기 위해 바람직할 수도 있는데, 그 경우에, 사전-분할된 체크 노드는 평처링된 변수 노드들에 접속되는 적어도 2 개의 에지들을 가질 수도 있다. 예를 들어, LDPC 코드는 베이스 코드에서 더블 에지들의 존재에서 단일의 고-차 평처링된 변수 노드로 설계한다. 따라서, 큰 차수의 하나의 평처링된 변수 노드보다는 보다 작은 차수의 다수의 평처링된 변수 노드들을 가지는 것이 바람직할 수도 있다. 달리 말하면, 더블 에지들을 회피하는 것과 보다 높은 코드 레이트들을 달성하는 것 사이에 트레이드 오프 (tradeoff) 가 존재할 수도 있다.

[0097] 따라서, 적은 더블 에지들을 가지지만 넓은 범위의 코드 레이트들에 걸쳐 고 성능을 여전히 달성 가능한 LDPC 코드들의 평처링을 위한 기법들이 바람직하다.

[0098] 베이스 그래프에서 최고 차수의, 하지만, 다른 타입들의 LDPC 코드들에 비해 상대적으로 낮은 차수의 변수 노드들의, 다수의 변수들 노드들의 강화된 평처링을 위한 기법들이 본원에서 제공되고, LDPC 코드 구조들은 멀티-에지 타입 LDPC 코드 구조에 추가된 추가적인 패리티 비트들을 가지며, 이는 가우시안 및 페이딩 채널들에 대해 원하는 코드 레이트 및 성능을 달성하는데 도움이 될 수도 있다.

[0099] 도 13 은 본 개시의 특정 양태들에 따른, 무선 통신을 위한 예시적인 동작들 (1300) 을 나타낸다. 동작들 (1300) 은 예를 들어 송신 디바이스 (예컨대, UE (120) 또는 BS (110)) 에 의해 수행될 수도 있다. 동작들 (1300) 은, 1302 에서, 코드 워드를 생성하기 위해 LDPC 코드 (예컨대, 멀티-에지 타입 LDPC 코드) 에 기초하여 정보 비트들의 셋트를 인코딩함으로써 시작할 수도 있다. LDPC 코드는 제 1 수의 변수 노드들 (베이스 매트릭스에서의 열들) 및 제 2 수의 체크 노드들 (베이스 매트릭스에서의 행들) 을 갖는 베이스 매트릭스에 의해 정의된다. 변수 노드들은 레퍼런스 LDPC 코드 (예컨대, 단일의 고-차수 평처링된 노드를 갖는 LDPC 코드) 에

서의 변수 노드들에 비해 체크 노드들에 대한 낮은 차수의 접속성을 가질 수도 있고, 베이스 매트릭스는 평처링된 변수 노드들에 대해 적어도 하나의 추가적인 패리티 비트를 갖는다 (예컨대, 평처링된 변수 노드들의 각 쌍에 대해 하나의 엑스트라 변수 노드 또는  $M-1$  엑스트라 변수 노드들). 1304에서, 송신 디바이스는 평처링된 코드 워드를 생성하기 위해 변수 노드들 중 적어도 2 개의 변수 노드들 (예컨대, 베이스 매트릭스의 2 개의 가장 높은 차수의 변수 노드들)에 대응하는 비트들 (예컨대,  $M$  변수 노드들)을 평처링하도록 설계된 평처링 패턴에 따라 코드 워드를 평처링한다. 1306에서, 송신 디바이스는 적어도 2 개의 평처링된 변수 노드들의 적어도 하나의 쌍에 대해 베이스 그래프에 적어도 추가적인 패리티 비트를 추가한다.

[0100] 1308에서, 송신 디바이스는 평처링된 코드 워드를 송신한다. 특정 양태들에 따르면, 적어도 하나의 엑스트라 변수 노드가 2 개의 평처링된 변수 노드들의 패리티에 의해 형성된다. 적어도 하나의 엑스트라 변수 노드들은 1 의 체크 노드들에 대한 접속성의 차수를 가질 수도 있다.

[0101] 특정 양태들에 따르면, 단일의 고-차수 노드를 평처링하는 대신에 평처링된 다수의 보다 낮은 차수의 노드들을 갖는 LDPC 코드가 설계될 수 있다. 예를 들어, 특정 차수의 2 개의 노드들이 그 차수의 2 배의 하나의 평처링된 노드 대신에 평처링될 수도 있다. 평처링된 변수 노드들은, LDPC 코드 구조에서 최고 차수의 변수 노드들일 수도 있지만, 여전히, 단일의 고-차수 평처링된 변수 노드를 갖는 다른 (예컨대, 종래의) LDPC 코드들에 비해 상대적으로 저-차수 변수 노드들일 수도 있다. 보다 낮은 차수의 노드들인 2 개의 평처링된 노드들의 존재는 그들 노드들에 대한 보다 느린 디코딩 수렴에 기여할 수도 있고, 이는, 특히 체크 노드들의 수가 비교적 작은 경우에, 높은 레이트 코드들에 대해 양호한 성능을 달성하기에 보다 어렵게 만들 수도 있다. 일부 경우들에서, 평처링된 노드들은 베이스 그래프에서 최고 차수 노드들 (즉, 베이스 그래프에서 체크 노드들에 대한 가장 많은 접속된 에지들을 갖는 변수들 노드들) 일 수도 있다; 하지만, 평처링된 노드들은 레퍼런스 LDPC 코드에서 최고의 가능한 평처링된 노드들의 차수 또는 접속성의 차수에 비해 낮은 차수의 접속성을 가질 수도 있다.

[0102] 특정 양태들에 따르면, 추가적인 비-평처링된 비트(들)가 LDPC 코드 구조에 추가될 수도 있다. 추가적인 비-평처링된 비트들은 2 개의 평처링된 노드들의 패리티를 취함으로써 형성될 수도 있다 (예컨대, 그 패리티 비트들은 1 차의 변수 노드들일 수도 있다). LDPC 코드 구조에 엑스트라 비-평처링된 비트들을 추가하는 것은 순 평처링 레이트를 감소시키는 효과를 가질 수도 있다. 2 개의 평처링된 노드들의 전체 구조 및 하나의 추가적인 송신된 패리티 비트는 코드로부터 오직 1 차의 자유도로 유효하게 평처링한다. 평처링된 노드들은 그들의 혜택들이 여전히 존재하도록 남지만, 패리티 비트는 보다 신속한 수렴을 허용하고, 이에 의해, 디코딩 프로세스에서 평처링된 비트들의 값들의 결정을 용이하게 할 수도 있다. 이러한 구조는, 상기 논의된 다른 바람직한 피처들에 대한 지원을 제공하면서 가우시안 및 페이딩 채널들 양자에 대한 전체 설계의 성능을 향상시키는데 도움이 될 수도 있다.

[0103] 특정 양태들에 따르면, 베이스 그래프가 적당한 (예컨대, 비교적 낮은) 차수 (예컨대, 차수 3 내지 차수 7)의 다소 작은 수의 평처링된 변수 노드들을 갖는 LDPC 코드 구조들이 사용될 수도 있다. LDPC 코드 구조는 또한, 2 개의 이러한 평처링된 노드들로부터 각각 형성된 추가적인 패리티 비트(들)를 포함할 수도 있다.

[0104] 하나의 예시적인 구현에서, 길이 27 또는 28 의 베이스 그래프를 갖는 LDPC 코드 구조가 사용될 수도 있다. 베이스 그래프에서, 2 개의 저 차수 변수 노드들이 평처링될 수도 있고, 2 개의 평처링된 노드들의 패리티에 의해 형성된 하나의 추가적인 패리티 비트가 LDPC 코드 구조에 추가될 수도 있다. 이 LDPC 코드 구조는 예를 들어 1/4 내지 8/9 의 코드 레이트들에 대해 유용할 수도 있다.

[0105] 특정 양태들에 따르면, 큰 베이스 그래프를 갖는 LDPC 코드 구조들은 큰 수의 평처링된 저 차수 노드들 및 추가된 보다 큰 수의 연관된 패리티 비트들을 수반할 수도 있다. 예를 들어,  $m$  개의 평처링된 변수 노드들에 대해,  $m-1$  개의 1 차 패리티 비트들이 추가될 수도 있다. 비록 다른 경우들에서는 상이한 수의 패리티 비트들이 추가될 수도 있지만, 예를 들어, 일부 경우들에서,  $m-1$  보다 적은 패리티 비트들이 사용될 수도 있다. 도 14에서 예시된 또 다른 예시적인 구현에서, 길이 36 의 베이스 그래프를 갖는 LDPC 코드 구조 (1400) 가 사용될 수도 있다. 비교적 낮은 차수를 갖는, LDPC 코드 구조 (1400)에서의 3 개의 최고 차수 변수 노드들 (1304) 이 평처링되고, 2 개의 추가적인 패리티 비트들 (1306) 이 LDPC 코드 구조 (1400)에 추가되고, 각각은 평처링된 노드들 중 2 개의 평처링된 노드들의 패리티에 의해 형성되며, 체크 노드들 (1402) 중 하나에 접속된다.

[0106] 비교적 낮은 차수의 평처링된 노드들의 차수는 추가적인 패리티 비트들을 형성하기 위해 사용되는 에지들을 포함하지 않음에 주목할 수도 있다. HARQ 확장들에서, 평처링된 노드들의 차수들은 추가의 패리티 비트들의 추가로 인해 실질적으로 증가할 수도 있다. 멀티-에지 탑입 설계들의 이점들 중 하나는 그것들이 제어된 방

식으로 차수 1 변수 노드들의 도입을 허용한다는 점이다. 모든 차수 1 변수 노드들을 평처링하는 것, 및 그 것들의 연관된 체크 노드를 역시 제거함으로써 코드 그래프에서 그들 변수 노드들을 스트립핑하는 것에 의해, "코어 (core)" 그래프가 획득될 수도 있다. 평처링된 변수 노드들의 "차수 (degree)"는 코어 그래프에서의 노드들의 차수일 수도 있다.

[0107] 적어도 2 개의 평처링된, 비교적 낮은 차수의 변수 노드들을 갖는 LDPC 코드 구조를 생성하고, 평처링된 변수 노드들의 쌍들에 대해 추가적인 패리티 비트들을 추가하기 위한 본원에 기술된 기법들 및 장치는 보다 양호한 인코더/디코더 동작들을 제공할 수도 있고, 따라서, 프로세서 및/또는 프로세싱 시스템들의 강화된 성능을 제공할 수도 있다. 예를 들어, 보다 낮은 평처링된 노드들의 사용은 반복적 디코딩을 늦출 수 있는 그래프에서의 더블 에지의 존재를 회피하는데 도움이 된다. 평처링된 변수 노드들에 대한 베이스 그래프에 추가적인 패리티 비트들을 추가함으로써, 평처링된 변수 노드들의 존재의 경우에도, 양호한 성능이 여전히 획득될 수 있고, 그래프에서 더블 에지들의 생성을 여전히 회피하면서도 보다 높은 코드 레이트들이 달성될 수 있다. 따라서, 제안된 LDPC 코드 구조들을 이용하는 인코딩/디코딩은 개선된 프로세싱 시간들로 이끈다.

[0108] 본 명세서에서 개시된 방법들은 설명된 방법을 달성하기 위한 하나 이상의 단계들 또는 액션들을 포함한다. 방법 단계들 및/또는 액션들은 청구항들의 범위로부터 벗어남 없이 서로 상호교환될 수도 있다. 다시 말해서, 단계들 또는 액션들의 특정 순서가 특정되지 않는 한, 특정 단계들 및/또는 액션들의 순서 및/또는 이용은 청구항들의 범위로부터 벗어남 없이 변형될 수도 있다.

[0109] 본 명세서에서 사용한 바와 같이, 용어 "결정하는 것"은 광범위한 액션들을 포괄한다. 예를 들어, "결정하는 것"은 계산하는 것, 컴퓨팅하는 것, 프로세싱하는 것, 도출하는 것, 조사하는 것, 룩업하는 것 (예를 들어, 테이블, 데이터베이스 또는 다른 데이터 구조에서 룩업하는 것), 확인하는 것 등을 포함할 수도 있다. 또한, "결정하는 것"은 수신하는 것 (예를 들어, 정보를 수신하는 것), 액세스하는 것 (예를 들어, 메모리 내의 데이터에 액세스하는 것) 등을 포함할 수도 있다. 또한, "결정하는 것"은 해결하는 것, 선택하는 것, 선정하는 것, 확립하는 것 등을 포함할 수도 있다.

[0110] 일부 경우들에서, 프레임을 실제로 송신하는 것보다는, 디바이스는 송신을 위해 프레임을 출력하기 위한 인터페이스를 가질 수도 있다. 예를 들어, 프로세서는 버스 인터페이스를 통해, 송신을 위한 RF 프론트 엔드로 프레임을 출력할 수도 있다. 유사하게, 프레임을 실제로 수신하는 것보다는, 디바이스는 다른 디바이스로부터 수신된 프레임을 획득하기 위한 인터페이스를 가질 수도 있다. 예를 들어, 프로세서는 버스 인터페이스를 통해, 송신을 위한 RF 프론트 엔드로부터 프레임을 획득 (또는 수신) 할 수도 있다.

[0111] 상기 설명된 방법들의 다양한 동작들은 대응하는 기능들을 수행하는 것이 가능한 임의의 적합한 수단에 의해 수행될 수도 있다. 수단은 회로, 주문형 집적 회로 (ASIC), 또는 프로세서를 포함하지만 이들에 제한되지는 않는 다양한 하드웨어 및/또는 소프트웨어 컴포넌트(들) 및/또는 모듈(들)을 포함할 수도 있다. 일반적으로, 도면들에 예시된 동작들이 존재하는 경우, 그 동작들은 유사한 넘버링을 가진 대응하는 상대 수단-플러스-기능 컴포넌트들을 가질 수도 있다.

[0112] 본 개시와 관련하여 설명된 다양한 예시적인 논리 블록들, 모듈들 및 회로들은 범용 프로세서, 디지털 신호 프로세서 (DSP), 주문형 집적 회로 (ASIC), 필드 프로그래밍가능 게이트 어레이 (FPGA) 또는 다른 프로그래밍가능 로직 디바이스 (PLD), 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들, 또는 본 명세서에서 설명된 기능들을 수행하도록 설계된 그 임의의 조합으로 구현 또는 수행될 수도 있다. 범용 프로세서는 마이크로프로세서일 수도 있지만, 대안으로, 프로세서는 임의의 상업적으로 입수가능한 프로세서, 제어기, 마이크로제어기, 또는 상태 머신일 수도 있다. 프로세서는 또한, 컴퓨팅 디바이스들의 조합, 예를 들어, DSP 와 마이크로프로세서의 조합, 복수의 마이크로프로세서들, DSP 코어와 결합된 하나 이상의 마이크로프로세서들, 또는 임의의 다른 이러한 구성으로서 구현될 수도 있다.

[0113] 하드웨어로 구현되면, 일 예의 하드웨어 구성은 무선 노드에서 프로세싱 시스템을 포함할 수도 있다. 프로세싱 시스템은 버스 아키텍처로 구현될 수도 있다. 버스는 프로세싱 시스템의 특정 애플리케이션 및 전체 설계 제약들에 의존하여 임의의 수의 상호접속 버스들 및 브릿지들을 포함할 수도 있다. 버스는 프로세서, 머신 관리 가능 매체들, 및 버스 인터페이스를 포함하는 다양한 회로들을 함께 링크할 수도 있다. 버스 인터페이스는 다른 것들 중에서도, 버스를 통해 프로세싱 시스템에 네트워크 어댑터를 접속시키는데 이용될 수도 있다. 네트워크 어댑터는 PHY 계층의 신호 프로세싱 기능들을 구현하는데 이용될 수도 있다. 무선 노드 (도 1 참조)의 경우에, 사용자 인터페이스 (예를 들어, 키패드, 디스플레이, 마우스, 조이스틱 등)는 또한 버스에 접속될 수도 있다. 버스는 또한, 당업계에 잘 알려져 있고, 따라서 더 이상 설명되지 않을 타이밍 소

스들, 주변기기들, 전압 레귤레이터들, 전력 관리 회로들 등과 같은 다양한 다른 회로들을 링크할 수도 있다.

프로세서는 하나 이상의 범용 및/또는 특수-목적 프로세서들로 구현될 수도 있다. 예들은 마이크로프로세서들, 마이크로제어기들, DSP 프로세서들, 및 소프트웨어를 실행할 수 있는 다른 회로부를 포함한다. 당업자들은 전체 시스템에 부과된 전체 설계 제약들 및 특정한 애플리케이션에 의존하여 프로세싱 시스템에 대해 설명된 기능성을 구현하는 최선의 방법을 인정할 것이다.

[0114]

소프트웨어로 구현되면, 기능들은 컴퓨터 판독가능 매체 상에 하나 이상의 명령들 또는 코드로서 저장되거나 또는 이를 통해 송신될 수도 있다. 소프트웨어는 소프트웨어, 펌웨어, 미들웨어, 마이크로코드, 하드웨어 기술 언어, 또는 다른 것으로 지칭되든 간에, 명령들, 데이터, 또는 그 임의의 조합을 의미하는 것으로 광범위하게 해석되어야 한다. 컴퓨터 판독가능 매체들은 일 장소로부터 다른 장소로의 컴퓨터 프로그램의 전송을 용이하게 하는 임의의 매체를 포함하는 통신 매체들과 컴퓨터 저장 매체들 양자 모두를 포함한다. 프로세서는 머신 판독가능 저장 매체들 상에 저장된 소프트웨어 모듈들의 실행을 포함하여, 일반적인 프로세싱 및 버스를 관리하는 것을 담당할 수도 있다. 컴퓨터 판독가능 저장 매체는 프로세서에 커플링될 수도 있어 프로세서는 저장 매체로부터 정보를 판독하고 그 저장 매체에 정보를 기록할 수 있다. 대안으로, 저장 매체는 프로세서와 일체형일 수도 있다. 예시적으로, 머신 판독가능 매체들은, 전부가 버스 인터페이스를 통하여 프로세서에 의해 액세스될 수도 있는, 무선 노드와는 별개인 명령들을 저장하고 있는 컴퓨터 판독가능 저장 매체, 송신 라인, 및/또는 데이터에 의해 변조된 캐리어파를 포함할 수도 있다. 대안적으로, 또는 추가로, 머신 판독가능 매체들, 또는 그 임의의 부분은 프로세서에 통합될 수도 있고, 이를 테면, 그 경우는 캐시 및/또는 일반 레지스터 파일들과 함께 있을 수도 있다. 머신 판독가능 저장 매체들의 예들은 일 예로, RAM (랜덤 액세스 메모리), 플래시 메모리, ROM (판독 전용 메모리), PROM (프로그래밍가능 판독 전용 메모리), EPROM (소거가능한 프로그래밍가능 판독 전용 메모리), EEPROM (전기적으로 소거가능한 프로그래밍가능 판독 전용 메모리), 레지스터들, 자기 디스크들, 광학 디스크들, 하드 드라이브들, 또는 임의의 다른 적합한 저장 매체, 또는 그 임의의 조합을 포함할 수도 있다. 머신 판독가능 매체들은 컴퓨터 프로그램 제품에 수록될 수도 있다.

[0115]

소프트웨어 모듈은 단일 명령, 또는 다수의 명령들을 포함할 수도 있고, 여러 상이한 코드 세그먼트들에 걸쳐, 상이한 프로그램들 간에, 그리고 다중 저장 매체들을 가로질러 분포될 수도 있다. 컴퓨터 판독가능 매체들은 다수의 소프트웨어 모듈들을 포함할 수도 있다. 소프트웨어 모듈들은, 프로세서와 같은 장치에 의해 실행될 때, 프로세싱 시스템으로 하여금, 다양한 기능들을 수행하게 하는 명령들을 포함한다. 소프트웨어 모듈들은 송신 모듈 및 수신 모듈을 포함할 수도 있다. 각각의 소프트웨어 모듈은 단일 저장 디바이스에 상주하거나 또는 다중 저장 디바이스들에 걸쳐서 분포될 수도 있다. 일 예로, 소프트웨어 모듈은 트리거링 이벤트가 발생할 때 하드 드라이브로부터 RAM 으로 로딩될 수도 있다. 소프트웨어 모듈의 실행 동안, 프로세서는 액세스 속도를 증가시키기 위해 명령들의 일부를 캐시로 로딩할 수도 있다. 하나 이상의 캐시 라인들은 그 후 프로세서에 의한 실행을 위해 일반 레지스터 파일로 로딩될 수도 있다. 아래에 소프트웨어 모듈의 기능성을 참조할 때, 이러한 기능성은 그 소프트웨어 모듈로부터 명령들을 실행할 때 프로세서에 의해 구현되는 것으로 이해될 것이다.

[0116]

또한, 임의의 접속이 적절히 컴퓨터 판독가능 매체라 불린다. 예를 들어, 소프트웨어가 동축 케이블, 광섬유 케이블, 트위스티드 폐어, 디지털 가입자 회선 (DSL), 또는 적외선 (IR), 무선, 및 마이크로파와 같은 무선 기술들을 이용하여 웹사이트, 서버, 또는 다른 원격 소스로부터 송신되면, 매체의 정의에는, 동축 케이블, 광섬유 케이블, 트위스티드 폐어, DSL, 또는 적외선, 무선, 및 마이크로파와 같은 무선 기술들이 포함된다. 디스크 (disk) 및 디스크 (disc) 는 본 명세서에서 사용한 바와 같이, 콤팩트 디스크 (CD), 레이저 디스크, 광 디스크, 디지털 다기능 디스크 (DVD), 플로피 디스크, 및 블루-레이® 디스크를 포함하고, 여기서 디스크 (disk) 들은 보통 데이터를 자기적으로 재생하는 한편, 디스크 (disc) 들은 레이저들로 데이터를 광학적으로 재생한다.

따라서, 일부 양태들에서, 컴퓨터 판독가능 매체들은 비일시적 컴퓨터 판독가능 매체들 (예를 들어, 유형의 매체들) 을 포함할 수도 있다. 추가로, 다른 양태들에 대해, 컴퓨터 판독가능 매체들은 일시적 컴퓨터 판독 가능 매체들 (예를 들어, 신호) 을 포함할 수도 있다. 상기의 조합들이 또한 컴퓨터 판독가능 매체들의 범위 내에 포함되어야 한다.

[0117]

따라서, 소정의 양태들은 본 명세서에서 제시된 동작들을 수행하기 위한 컴퓨터 프로그램 제품을 포함할 수도 있다. 예를 들어, 이러한 컴퓨터 프로그램 제품은 명령들을 저장 (및/또는 인코딩) 하고 있는 컴퓨터 판독 가능 매체를 포함할 수도 있고, 그 명령들은 본 명세서에서 설명된 동작들을 수행하도록 하나 이상의 프로세서들에 의해 실행가능하다.

[0118]

게다가, 본 명세서에서 설명된 방법들 및 기법들을 수행하기 위한 모듈들 및/또는 다른 적절한 수단은 적용가능

한 대로 무선 노드 및/또는 기지국에 의해 다운로드 및/또는 다르게는 획득될 수 있다는 것이 인식되어야 한다.

예를 들어, 이러한 디바이스는 본 명세서에서 설명된 방법들을 수행하기 위한 수단의 전송을 용이하게 하기 위해 서버에 커플링될 수 있다. 대안적으로, 본 명세서에서 설명된 다양한 방법들은 무선 노드 및/또는 기지국이 저장 수단을 디바이스에 커플링 또는 제공 시에 다양한 방법들을 획득할 수 있도록 저장 수단 (예를 들어, RAM, ROM, 물리적 저장 매체, 이를 테면 콤팩트 디스크 (CD) 또는 플로피 디스크 등)을 통해 제공될 수 있다. 더욱이, 본 명세서에서 설명된 방법들 및 기법들을 디바이스에 제공하기 위한 임의의 다른 적합한 기법이 활용될 수 있다.

[0119]

청구항들은 상기 예시된 정확한 구성 및 컴포넌트들에 제한되지 않는 것으로 이해되어야 한다. 청구항들의 범위로부터 벗어남 없이 상기 설명된 방법들 및 장치의 배열, 동작 및 상세들에 있어서 다양한 변형들, 변경들 및 변화들이 행해질 수도 있다.

## 도면

### 도면1

## 도면2

## 도면3

도면4

## 도면5

## 도면6

도면7

도면8

도면8a

$$H = \begin{bmatrix} 1 & 1 & 1 & 0 & 0 \\ 1 & 0 & 0 & 1 & 1 \\ 1 & 1 & 0 & 0 & 1 \\ 0 & 1 & 1 & 1 & 0 \end{bmatrix} \quad x = \begin{bmatrix} x_1 \\ x_2 \\ x_3 \\ x_4 \\ x_5 \end{bmatrix}$$

## 도면9

## 도면10

도면 11

도면12

## 도면13

도면14