(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7066347号**

**(P7066347)**

(45)発行日 令和4年5月13日(2022.5.13)

(24)登録日 令和4年5月2日(2022.5.2)

(51)国際特許分類

|         |                 |         |        |       |

|---------|-----------------|---------|--------|-------|

| H 0 4 N | 5/374(2011.01)  | H 0 4 N | 5/374  |       |

| H 0 1 L | 27/146(2006.01) | H 0 1 L | 27/146 | A     |

| H 0 4 N | 5/369(2011.01)  | H 0 4 N | 5/369  | 6 0 0 |

| H 0 4 N | 5/376(2011.01)  | H 0 4 N | 5/376  |       |

F I

請求項の数 24 (全50頁)

(21)出願番号 特願2017-143686(P2017-143686)

(22)出願日 平成29年7月25日(2017.7.25)

(65)公開番号 特開2019-29694(P2019-29694A)

(43)公開日 平成31年2月21日(2019.2.21)

審査請求日 令和2年7月22日(2020.7.22)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100126240

弁理士 阿部 琢磨

100124442

弁理士 黒岩 創吾

小黒 康裕

(72)発明者 東京都大田区下丸子3丁目30番2号キ

ヤノン株式会社内

識名 紀之

東京都大田区下丸子3丁目30番2号キ

ヤノン株式会社内

審査官 大室 秀明

最終頁に続く

(54)【発明の名称】 撮像装置、撮像システム、移動体

**(57)【特許請求の範囲】****【請求項1】**

各々が、入射光の光量に対応する信号を出力する、複数行および複数列に渡って配された複数の有効画素と、

前記複数行に渡って配され、属する行の位置を示すアドレス信号を成すための画素信号を出力する複数の参照画素と、

前記複数行のそれぞれに対応して設けられ、各々が対応する前記有効画素と前記参照画素とを制御する制御信号を出力する複数の制御信号出力部を有する垂直走査回路とを有し、

前記複数の参照画素のうちの一部の参照画素に、第1の電圧を供給する第1電圧供給線が接続され、前記一部の参照画素は、前記第1の電圧に対応する信号を前記画素信号として出力し、

前記複数の参照画素のうちの他の一部の参照画素に、第2の電圧を供給する第2電圧供給線が接続され、前記他の一部の参照画素は、前記第2の電圧に対応する信号を前記画素信号として出力することを特徴とする撮像装置。

**【請求項2】**

前記第1の電圧に対応する信号と、前記第2の電圧に対応する信号とによって、前記アドレス信号が成されることを特徴とする請求項1に記載の撮像装置。

**【請求項3】**

前記複数の参照画素の各々は、増幅トランジスタと、前記増幅トランジスタのゲートに接続されたリセットトランジスタと、一方のノードおよび前記増幅トランジスタに接続され

た他方のノードとを有する転送トランジスタとを有し、

前記一部の参照画素の各々の前記転送トランジスタの前記一方のノードに前記第1電圧供給線が接続され、

前記他的一部の参照画素の各々の前記転送トランジスタの前記一方のノードに前記第2電圧供給線が接続されていることを特徴とする請求項1または2に記載の撮像装置。

**【請求項4】**

フレームごとに前記アドレス信号の信号値が変化することを特徴とする請求項1～3のいずれか1項に記載の撮像装置。

**【請求項5】**

前記複数の参照画素は半導体基板に形成され、

10

前記複数の参照画素の各々は、第1導電型の第1半導体領域と、前記第1導電型の浮遊拡散領域と、前記第1半導体領域と前記浮遊拡散領域との間に位置するとともに前記半導体基板の正面の上に設けられた転送ゲートとを有し、

前記複数の参照画素において、前記第1半導体領域の一部の領域が、コンタクトから電位が供給され、

前記第1半導体領域と前記正面との間であって、平面視における前記一部の領域と前記転送ゲートとの間の領域に形成された第2導電型の第2半導体領域がさらに設けられていることを特徴とする請求項1～4のいずれか1項に記載の撮像装置。

**【請求項6】**

各々が、入射光の光量に対応する信号を出力する、複数行および複数列に渡って配された複数の有効画素と、

20

前記複数行に渡って配され、属する行の位置を示すアドレス信号を成すための画素信号を出力する複数の参照画素と、

前記複数行のそれぞれに対応して設けられ、各々が対応する前記有効画素と前記参照画素とを制御する制御信号を出力する複数の制御信号出力部を有する垂直走査回路とを有し、フレームごとに前記アドレス信号の信号値が変化することを特徴とする撮像装置。

**【請求項7】**

各々が、入射光の光量に対応する信号を出力する、複数行および複数列に渡って配された複数の有効画素と、

前記複数行に渡って配され、属する行の位置を示すアドレス信号を成すための画素信号を出力する複数の参照画素と、

30

前記複数行のそれぞれに対応して設けられ、各々が対応する前記有効画素と前記参照画素とを制御する制御信号を出力する複数の制御信号出力部を有する垂直走査回路とを有し、前記複数の参照画素は半導体基板に形成され、

前記複数の参照画素の各々は、第1導電型の第1半導体領域と、前記第1導電型の浮遊拡散領域と、前記第1半導体領域と前記浮遊拡散領域との間に位置するとともに前記半導体基板の正面の上に設けられた転送ゲートとを有し、

前記複数の参照画素において、前記第1半導体領域の一部の領域が、コンタクトから電位が供給され、

前記第1半導体領域と前記正面との間であって、平面視における前記一部の領域と前記転送ゲートとの間の領域に形成された第2導電型の第2半導体領域がさらに設けられていることを特徴とする撮像装置。

40

**【請求項8】**

前記複数の参照画素のうち、1行に配された複数の参照画素において、

前記1行に配された複数の参照画素が含まれる複数の組のうちの一部の組に含まれる複数の参照画素の画素信号によって成されるアドレス信号が、前記複数の組で繰り返されるとによって、前記属する行の位置を示すアドレス信号が成されることを特徴とする請求項1～7のいずれか1項に記載の撮像装置。

**【請求項9】**

各々が、入射光の光量に対応する信号を出力する、複数行および複数列に渡って配された

50

複数の有効画素と、

前記複数行に渡って配され、属する行の位置を示すアドレス信号を成すための画素信号を出力する複数の参照画素と、

前記複数行のそれぞれに対応して設けられ、各々が対応する前記有効画素と前記参照画素とを制御する制御信号を出力する複数の制御信号出力部を有する垂直走査回路とを有し、前記複数の参照画素のうち、1行に配された複数の参照画素において、

前記1行に配された複数の参照画素が含まれる複数の組のうちの一部の組に含まれる複数の参照画素の画素信号によって成されるアドレス信号が、前記複数の組で繰り返されるとによって、前記属する行の位置を示すアドレス信号が成されることを特徴とする撮像装置。

**【請求項 10】**

前記複数の参照画素のうちの一部の参照画素に、第1の電圧を供給する第1電圧供給線が接続され、前記一部の参照画素は、前記第1の電圧に対応する信号を前記画素信号として出力し

前記複数の参照画素のうちの他の一部の参照画素に、第2の電圧を供給する第2電圧供給線が接続され、前記他の一部の参照画素は、前記第2の電圧に対応する信号を前記画素信号として出力することを特徴とする請求項9に記載の撮像装置。

**【請求項 11】**

前記第1の電圧に対応する信号と、前記第2の電圧に対応する信号とによって、前記アドレス信号が成されることを特徴とする請求項10に記載の撮像装置。

**【請求項 12】**

前記複数の参照画素の各々は、増幅トランジスタと、前記増幅トランジスタのゲートに接続されたリセットトランジスタと、一方のノードおよび前記増幅トランジスタに接続された他方のノードとを有する転送トランジスタとを有し、

前記一部の参照画素の各々の前記転送トランジスタの前記一方のノードに前記第1電圧供給線が接続され、

前記他の一部の参照画素の各々の前記転送トランジスタの前記一方のノードに前記第2電圧供給線が接続されていることを特徴とする請求項10または11に記載の撮像装置。

**【請求項 13】**

前記複数行のうちの1行と、前記複数の制御信号出力部の1つとを各々が有する複数の組によって、前記複数の制御信号出力部のそれぞれが、前記複数行のそれぞれに対応して配されていることを特徴とする請求項1～12のいずれか1項に記載の撮像装置。

**【請求項 14】**

前記複数行のうちの一部の複数行と、前記複数の制御信号出力部の1つとを各々が有する複数の組によって、前記複数の制御信号出力部のそれぞれが、前記複数行のそれぞれに対応して配されていることを特徴とする請求項1～12のいずれか1項に記載の撮像装置。

**【請求項 15】**

前記垂直走査回路が、デコーダであることを特徴とする請求項1～14のいずれか1項に記載の撮像装置。

**【請求項 16】**

前記デコーダは、走査する行を指示する情報を含む走査指示信号が入力されるとともに、前記走査指示信号に基づくデコーダ信号を前記複数の制御信号出力部に出力するアドレスデコーダ回路をさらに有し、

前記アドレス信号が、前記デコーダ信号の値に対応する値を有することを特徴とする請求項15に記載の撮像装置。

**【請求項 17】**

前記垂直走査回路が、シフトレジスタであることを特徴とする請求項1～14のいずれか1項に記載の撮像装置。

**【請求項 18】**

前記複数行のうちの一の行に含まれる複数の有効画素と複数の参照画素は、対応する前記制御信号出力部と共に共通の制御線によって接続されていることを特徴とする請求項1～17

10

20

30

40

50

のいずれか 1 項に記載の撮像装置。

**【請求項 19】**

前記複数の制御信号出力部の各々は、バッファ回路であることを特徴とする請求項 1 ~ 18 のいずれか 1 項に記載の撮像装置。

**【請求項 20】**

前記複数の参照画素が出力する前記画素信号と期待値とを比較し、前記複数の参照画素が出力する前記画素信号が前記期待値と異なる場合に、異常を通知する信号を生成する検出部を有することを特徴とする請求項 1 ~ 19 のいずれか 1 項に記載の撮像装置。

**【請求項 21】**

請求項 1 ~ 20 のいずれか 1 項に記載の撮像装置と、

10

前記撮像装置が出力する信号を用いて画像を生成する信号処理部とを有することを特徴とする撮像システム。

**【請求項 22】**

請求項 1 ~ 19 のいずれか 1 項に記載の撮像装置と、

前記複数の参照画素が出力する前記画素信号と期待値とを比較し、前記複数の参照画素が出力する前記画素信号が前記期待値と異なる場合に、異常を通知する信号を生成する検出部とを有することを特徴とする撮像システム。

**【請求項 23】**

移動体であって、

請求項 1 ~ 20 のいずれか 1 項に記載の撮像装置と、

20

前記撮像装置の前記有効画素から出力された前記画素信号に対して処理を行う処理装置と、前記処理の結果に基づいて前記移動体を制御する制御手段とを有することを特徴とする移動体。

**【請求項 24】**

移動体であって、

請求項 1 ~ 19 のいずれか 1 項に記載の撮像装置と、

前記複数の参照画素が出力する前記画素信号と期待値とを比較し、前記複数の参照画素が出力する前記画素信号が前記期待値と異なる場合に、異常を通知する信号を生成する検出部とを有することを特徴とする移動体。

**【発明の詳細な説明】**

30

**【技術分野】**

**【0001】**

本発明は、撮像装置、撮像システム、移動体に関する。

**【背景技術】**

**【0002】**

特許文献 1 には、有効画素領域と非有効画素領域を含む撮像装置の故障検出について記載されている。

**【0003】**

有効画素領域には、フォトダイオードを有する画素が配置され、各フォトダイオードに外部から光を入射させて光電変換により電気信号を生成する。非有効画素領域は、リファレンス領域と故障検出用パターン領域から形成されている。リファレンス領域には、遮光膜で覆われた画素が配置されており、リファレンス信号を生成する。故障検出用パターン領域には、フォトダイオード具備画素とフォトダイオード不備画素を特定の配列パターンで配置した故障検出用画素が配置されている。当該配列パターンに応じた信号をフレームごとに確認することによって、撮像装置の故障の有無を判定している。

40

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【文献】** 特開 2009 - 118427 号公報

**【発明の概要】**

50

**【発明が解決しようとする課題】**

**【0005】**

特許文献1には、フォトダイオード具備画素とフォトダイオード不備画素を特定の配列パターンで配置した参照画素を複数行に渡って配した構成について開示していない。よって、複数行に渡って参照画素が配された場合における、撮像装置の故障有無の判定の高速化に寄与する、参照画素からの信号を好適に読み出す回路について検討がなされていない。

**【課題を解決するための手段】**

**【0006】**

本発明は上記の課題を鑑みて為されたものであり、一の態様は、各々が、入射光の光量に対応する信号を出力する、複数行および複数列に渡って配された複数の有効画素と、前記複数行に渡って配され、属する行の位置を示すアドレス信号を成すための画素信号を出力する複数の参照画素と、前記複数行のそれぞれに対応して設けられ、各々が対応する前記有効画素と前記参照画素とを制御する制御信号を出力する複数の制御信号出力部を有する垂直走査回路とを有し、前記複数の参照画素のうちの一部の参照画素に、第1の電圧を供給する第1電圧供給線が接続され、前記一部の参照画素は、前記第1の電圧に対応する信号を前記画素信号として出力し、前記複数の参照画素のうちの他の一部の参照画素に、第2の電圧を供給する第2電圧供給線が接続され、前記他の一部の参照画素は、前記第2の電圧に対応する信号を前記画素信号として出力することを特徴とする撮像装置である。

10

**【発明の効果】**

**【0007】**

本発明により、複数行に渡って参照画素が配された場合における、撮像装置の故障の有無の判定の高速化に寄与する、参照画素からの信号を好適に読み出す回路を実現することができる。

20

**【図面の簡単な説明】**

**【0008】**

**【図1】**撮像装置の構成を示す図

**【図2】**撮像装置の駆動を示す図

**【図3】**画素の等価回路を示す図

**【図4】**画素の動作を示す図

**【図5】**アドレス信号を示す図

30

**【図6】**アドレス信号と期待値との比較のフローチャートを示す図

**【図7】**アドレス信号を示す図

**【図8】**アドレス信号を示す図

**【図9】**アドレス信号と期待値との比較のフローチャートを示す図

**【図10】**各フレームにおけるアドレス信号を示す図

**【図11】**各フレームにおけるアドレス信号を示す図

**【図12】**撮像装置の構成を示す図

**【図13】**撮像装置の駆動を示す図

**【図14】**画素の等価回路を示す図

**【図15】**画素の動作を示す図

40

**【図16】**アドレス信号を示す図

**【図17】**アドレス信号と期待値との比較のフローチャートを示す図

**【図18】**アドレス信号を示す図

**【図19】**アドレス信号と期待値との比較のフローチャートを示す図

**【図20】**撮像装置の構成を示す図

**【図21】**撮像装置の動作を示す図

**【図22】**撮像装置の全体図

**【図23】**画像取得用画素と故障検出用画素の等価回路図

**【図24】**画素の動作を示した図

**【図25】**画素の上面図

50

- 【図 2 6】光電変換部、転送トランジスタの上面図

- 【図 2 7】光電変換部、転送トランジスタの断面図

- 【図 2 8】光電変換部、転送トランジスタの上面図

- 【図 2 9】光電変換部、転送トランジスタの断面図

- 【図 3 0】光電変換部、転送トランジスタの製造工程を示した図

- 【図 3 1】光電変換部、転送トランジスタと、他のトランジスタが形成される活性領域の上面図

- 【図 3 2】光電変換部、転送トランジスタと、他のトランジスタが形成される活性領域の上面図

- 【図 3 3】撮像システムの全体図

- 【図 3 4】移動体の全体図

- 【図 3 5】移動体の制御フローを示す図

- 【発明を実施するための形態】

- 【0 0 0 9】

本発明に係る 1 つの実施形態は撮像装置である。撮像装置は行列を構成するように配された複数の画素を備える。複数の画素は、受光画素と参照画素とを含む。受光画素には外部からの光が入射する。受光画素は入射した光に応じた画素信号を出力する。参照画素は、アドレス信号を構成するための画素信号を出力する。

#### 【0 0 1 0】

アドレス信号は、行または列の位置に関する情報を含む。少なくとも 2 つの行、あるいは 2 つの列に対して、異なる信号値のアドレス信号が割り当てられる。1 つのアドレス信号は、1 つの参照画素からの画素信号、あるいは、複数の参照画素からの画素信号によって構成される。

#### 【0 0 1 1】

1 つのアドレス信号が 1 つの参照画素からの画素信号によって構成される実施例では、各行に少なくとも 1 つの参照画素が配される。異なる行の参照画素は、互いに異なるレベルの複数の画素信号を出力する。レベルは、画素信号の電流値や電圧値を意味する。参照画素の画素信号のレベルが、アドレス信号の信号値を表す。例えば、各行に 1 つの参照画素が配され、奇数行の参照画素がハイレベルの画素信号を出力し、偶数行の参照画素がローレベルの画素信号を出力する。これにより、撮像装置が偶数行の信号を読み出しているのか、奇数行の信号を読み出しているのかを判断することができる。あるいは、行ごとの参照画素が、属する行に固有のレベルの画素信号を出力する。撮像装置が 4 0 0 0 行の画素を含む場合、参照画素は 4 0 0 0 段階のレベルの画素信号を出力する。これにより、撮像装置がどの行の信号を読み出しているのかを判断することができる。

#### 【0 0 1 2】

別の例では、1 つの行に複数の参照画素が配される。この例では、1 つのアドレス信号が複数の参照画素からの画素信号によって構成される。例えば、参照画素のそれぞれが、ハイレベルの画素信号またはローレベルの画素信号を出力する。N 個の参照画素が配される場合、ハイレベルの画素信号とローレベルの画素信号との組み合わせにより、N ビットのデジタル信号として、アドレス信号が構成される。ハイレベルの画素信号が、各ビットの「1」に対応し、ローレベルの画素信号が、各ビットの「0」に対応する。この場合、デジタル信号の 0 と 1 との配列パターンが、アドレス信号の信号値を表す。1 2 個の参照画素を配することにより、4 0 9 6 行のそれぞれに固有の信号値を持つアドレス信号を生成することができる。なお、全ての行に対して固有のアドレス信号を生成しなくてもよい。4 0 9 6 行の画素に対して、各行に含まれる参照画素が 1 2 個より少なくてよい。この場合、同じ信号値のアドレス信号が複数の行に割り当てられる。

#### 【0 0 1 3】

なお、上述のそれぞれの例において、各参照画素が、異なるレベルの少なくとも 2 つの画素信号を出力してもよい。あるいは、各参照画素が、1 つのレベルの画素信号のみを出力するように構成されてもよい。また、以上の説明では、各行が参照画素を含む撮像装置を

10

20

30

40

50

例に挙げたが、各列が参照画素を含む撮像装置については、明細書中の「行」を「列」に読み替えればよい。

#### 【0014】

本発明に係る1つの実施形態は撮像システムである。撮像システムは、撮像装置から出力された画素信号を処理して、画像信号を取得する信号処理部を備える。信号処理部は、さらに、撮像装置から出力されるアドレス信号を受けとり、撮像装置から画素信号が正常に出力されているかを判断する。アドレス信号は、前述の撮像装置の実施形態で説明したものと同じである。

#### 【0015】

1つの実施例では、信号処理部は、複数の行の画素信号が所定の順番で出力されているかを判断する。複数の行の画素信号の読み出しに伴って、順次出力される複数のアドレス信号が、予期した通りに変化するかを判断する。例えば、奇数行と偶数行に異なる信号値のアドレス信号が割り当てられている場合、当該異なる信号値のアドレス信号が交互に出力されているかを判定する。これにより、複数の行の画素信号が所定の順番で出力されているかを判断することができる。

10

#### 【0016】

あるいは、信号処理部は、指定した行の画素信号が適切に出力されているかを判断する。画素信号と共に出力されたアドレス信号の信号値が、指定した行に割り当てられた信号値に一致するかを判断する。これにより、所定の行の画素信号が正常に出力されているかを判断することができる。

20

#### 【0017】

本実施形態において、アドレス信号が予期した信号値を出力している間は、撮像装置が正常に動作している、あるいは、正常に信号を出力していると判断される。アドレス信号の信号値が予期された信号値と異なる場合には、信号処理部は、撮像装置が正常に動作していない、あるいは、撮像装置が故障したと判断する。

#### 【0018】

本実施形態では、撮像装置の外部の信号処理部が、撮像装置が正常に画素信号を出力しているか否かを判断している。これに対して、撮像装置の実施形態において、撮像装置の内部の回路が、正常に信号が出力されているか否かの判断を行ってもよい。

30

#### 【0019】

上述の撮像装置や撮像システムは、カメラ、監視装置、ロボット等に用いられる。あるいは、上述の撮像装置や撮像システムは移動体に用いられる。特に、車、飛行機、船舶などの人を輸送するための移動体においては、装備された装置が高い信頼性を有することが望ましい。上述の実施形態の撮像装置や撮像システムによれば、撮像装置から正常に画素信号が出力されているかを判断することができる。そのため、撮像装置が故障した場合に、撮像動作を停止したり、故障が生じたことを警告したりすることができる。

#### 【0020】

いくつかの実施例においては、撮像装置あるいは撮像システムが、参照画素の異常を検出する手段を備える。換言すると、参照画素から出力されたアドレス信号の信号値が予期された信号値と一致しなかった場合に、当該不一致が、参照画素の異常や故障に起因するものか、実際に意図していない受光画素から信号を読み出していることを示すのかを、判断する。このような手段により、撮像装置または撮像システム、あるいは、それらを用いた移動体の信頼性を更に向上させることができる。

40

#### 【0021】

以下では、本発明の実施例について図面を用いて詳細に説明する。本発明は以下に説明される実施例のみに限定されない。本発明の趣旨を超えない範囲で以下に説明される実施例の一部の構成が変更された変形例も、本発明の実施例である。また、以下のいずれかの実施例の一部の構成を、他の実施例に追加した例、あるいは他の実施例の一部の構成と置換した例も本発明の実施例である。

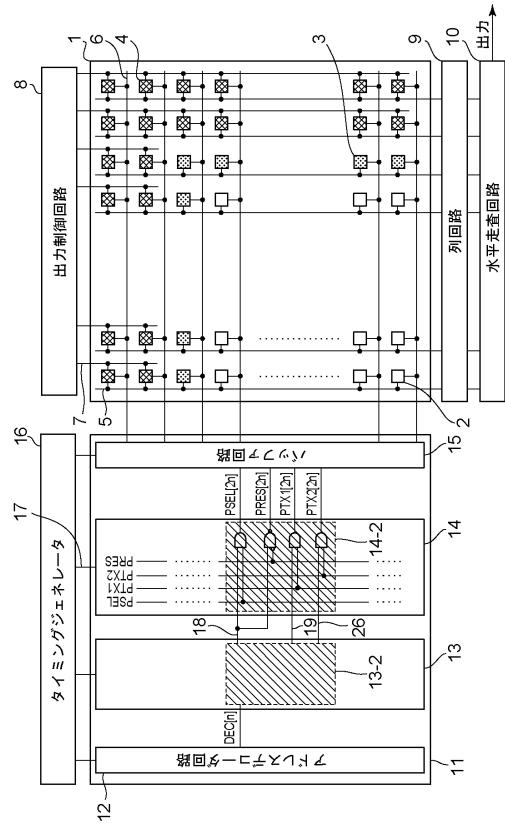

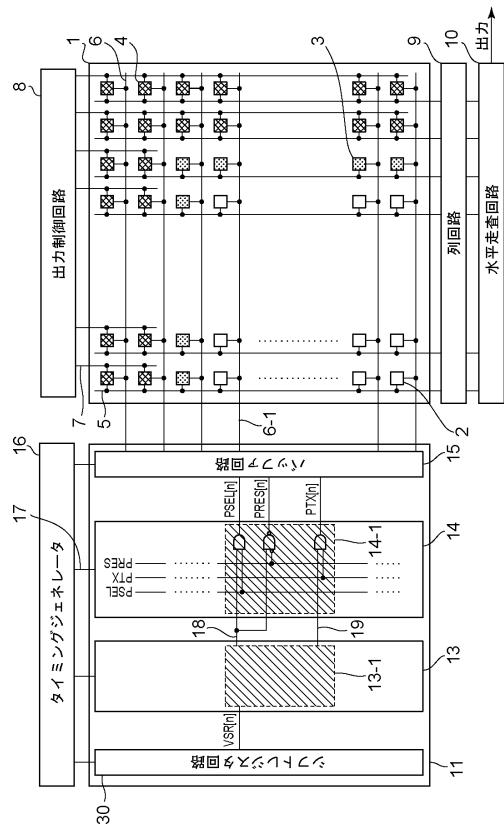

#### 【0022】

50

(実施例 1 )

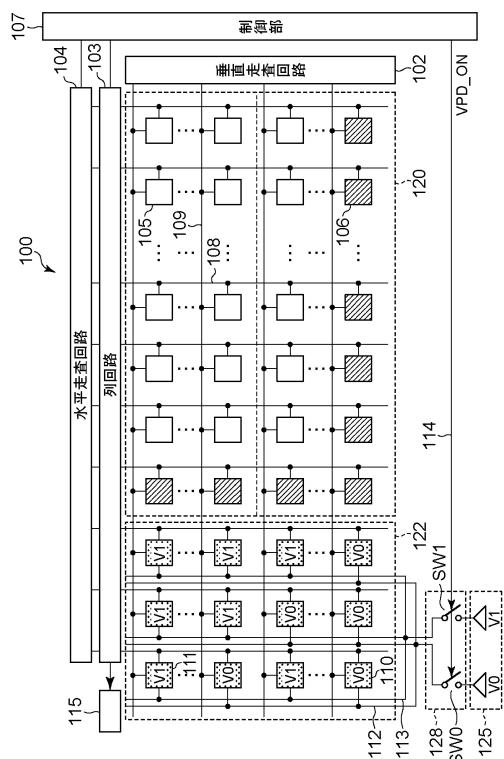

実施例 1 について説明する。図 1 は、実施例 1 に係る撮像装置の構成を模式的に示している。撮像装置は、複数行および複数列に渡って配置された複数の画素 2、3、4 を備える。複数の画素は、受光画素 2、オプティカルブラック画素（以下、O B 画素）3、参照画素 4 を含む。撮像装置は、さらに、垂直走査回路 11、列回路 9、水平走査回路 10、出力制御回路 8、垂直出力線 5、駆動制御線 6 - 1、出力制御線 7 を備える。撮像装置はさらにタイミングジェネレータ 16 を備える。

【 0 0 2 3 】

1つの行に含まれる複数の画素 2、3、4 は、共通の駆動制御線 6 - 1 に接続される。垂直走査回路 11 は、駆動制御線 6 - 1 を介して、複数の画素 2、3、4 に駆動信号を供給する。駆動信号に基づいて、1つの行に含まれる複数の画素 2、3、4 から画素信号が出力線 5 に並行して出力される。1つの列に含まれる複数の画素 2、3、4 が、共通の出力線 5 に接続される。出力線 5 に出力された画素信号は、列回路 9 に入力される。出力線 5 のそれぞれに対して、1つの列回路 9 が配される。列回路 9 は、画素信号の増幅、画素信号に対するアナログデジタル変換、画素信号の保持、画素信号のノイズの除去などの動作を行う。水平走査回路 10 によって、列回路 9 から画素信号を順次読み出す。

10

【 0 0 2 4 】

受光画素 2 は、外部からの光を受けるように構成される。受光画素 2 は、入射光に応じた画素信号を出力する。O B 画素 3 は、不図示の遮光膜に覆われている。遮光膜は、受光画素 2 を露出するように配置される。O B 画素 3 は、入射光がない状態に対応したレベル、つまり、ダークレベルの画素信号を出力する。O B 画素 3 の出力する画素信号は、画素ごとに異なるノイズ成分を含みうる。そのため、O B 画素 3 の出力する画素信号が、位置に応じて異なる可能性がある。しかし、ノイズ成分の量は、例えば製造ばらつきや熱雑音に起因するため、ランダムである。したがって、O B 画素 3 からの画素信号は、行や列の位置を特定するための情報ではない。

20

【 0 0 2 5 】

参照画素 4 は、アドレス信号を構成するための画素信号を出力する。本実施例には、上述の説明したアドレス信号のいずれかが用いられる。本実施例では、出力制御回路 8 が、参照画素 4 の出力する画素信号のレベルを制御する。具体的には、出力制御回路 8 が、所定の電圧を出力制御線 7 に供給する。参照画素 4 は、出力制御線 7 の電圧に応じたレベルの画素信号を出力する。参照画素 4 は、不図示の遮光膜に覆われていてもよい。あるいは、参照画素 4 はフォトダイオードを持たないので、参照画素 4 は露出していてもよい。

30

【 0 0 2 6 】

撮像装置は、さらにタイミングジェネレータ 16 を有する。

【 0 0 2 7 】

垂直走査回路 11 について説明する。

【 0 0 2 8 】

垂直走査回路 11 は、論理部 13 と、制御信号生成部 14 を有する。論理部 13 は、画素 2、3、4 が配された行に対応して各々が設けられた、複数の論理セル 13 - n を有する。また、制御信号生成部 14 は、画素 2、3、4 が配された行に対応して各々が設けられた、複数の信号生成セル 14 - n を有する。複数の信号生成セル 14 - n のそれぞれは、有効画素 2、O B 画素 3、参照画素 4 を制御する制御信号を出力する制御信号出力部である。本実施例では、1行の画素行に対し、1つの制御信号出力部（信号生成セル 14 - n ）が対応して設けられている。

40

【 0 0 2 9 】

アドレスデコーダ回路 12 には、タイミングジェネレータ 16 から n 行目の行アドレスを指定する情報を含む信号である走査指示信号が供給される。アドレスデコーダ回路 12 は、n 行目の論理生成部 13 - 1 にデコーダ信号 D E C [ n ] を供給する。

【 0 0 3 0 】

n 行目の論理生成部 13 - 1 は、デコーダ信号 D E C [ n ] を受けて、行選択信号 18 を

50

$n$  行目の信号生成セル 14-1 に行選択パルスとして供給する。また、 $n$  行目の論理生成部 13-1 は、シャッタ動作信号 19 を  $n$  行目の信号生成セル 14-1 にシャッタ動作パルスとして供給する。

#### 【0031】

タイミングジェネレータ 16 は、画素駆動信号 17 を制御信号生成部 14 に供給する。画素駆動信号には、PSEL、PTX、PRES が含まれる。

#### 【0032】

$n$  行目の信号生成セル 14-1 は、 $n$  行目の論理生成部 13-1 から供給される行選択信号 18 と PSEL で論理処理を行い PSEL [n] を生成し、行選択信号 18 と PRES で論理処理を行い PRES [n] を生成する。また、 $n$  行目の論理生成部 13-1 から供給されるシャッタ動作信号 19 と PTX で論理処理を行い PTX [n] を生成する。10

#### 【0033】

$n$  行目の信号生成セル 14-1 で生成された、制御パルス PSEL [n]、PRES [n]、PTX [n] は、バッファ回路 15 を介して、撮像領域 1 の  $n$  行目の画素駆動信号線 6-1 に供給される。

#### 【0034】

垂直走査回路 11 より出力される制御パルスは、受光画素 2、OB 画素 3、及び、参照画素 4 に供給される。受光画素 2 は、フォトダイオード（以下 PD）を含み、外部からの入射光を光電変換することで電気信号に変換し、入射光量に応じた画素信号を出力する。OB 画素 3 は、受光画素 2 の上部を遮光膜で覆ったものであり、画素信号の基準となるダークレベルを出力する。参照画素 4 は、撮像領域 1 内の行を識別するためのアドレス信号を出力する。参照画素 4 には、出力制御線 7 を介して出力制御回路 8 より固定電圧が供給されており、PD を含まず出力制御回路 8 より供給される固定電圧に応じた信号を出力する。20

#### 【0035】

1 つの行の受光画素 2、OB 画素 3、参照画素 4 には、共通の画素駆動信号線 6 が接続されている。また、1 つの列の受光画素 2、OB 画素 3、参照画素 4 には、共通の垂直出力線 5 が接続されている。各列の垂直出力線 5 に出力された受光画素 2、OB 画素 3、参照画素 4 の画素信号は、画素が配列された列に対応する列回路 9 に入力される。

#### 【0036】

列回路 9 は、画素信号の増幅、画素信号の保持、画素信号のアナログデジタル変換などの動作を行う。30

#### 【0037】

水平走査回路 10 は、列回路 9 の出力信号を順次走査し、撮像装置の外部に出力させる。

#### 【0038】

ここで、アドレスデコーダ回路 12 から出力されるデコーダ信号単位を 1 段とし、撮像領域 1 の選択行を 1 行とする。本実施例は、デコーダ信号 1 段に対して、撮像領域 1 が 1 行選択される構成である。

#### 【0039】

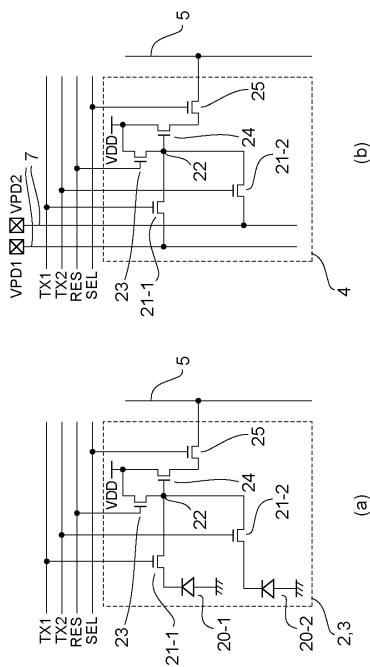

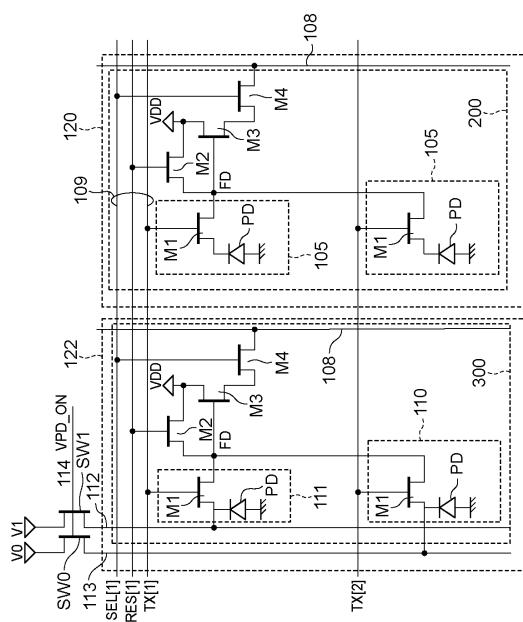

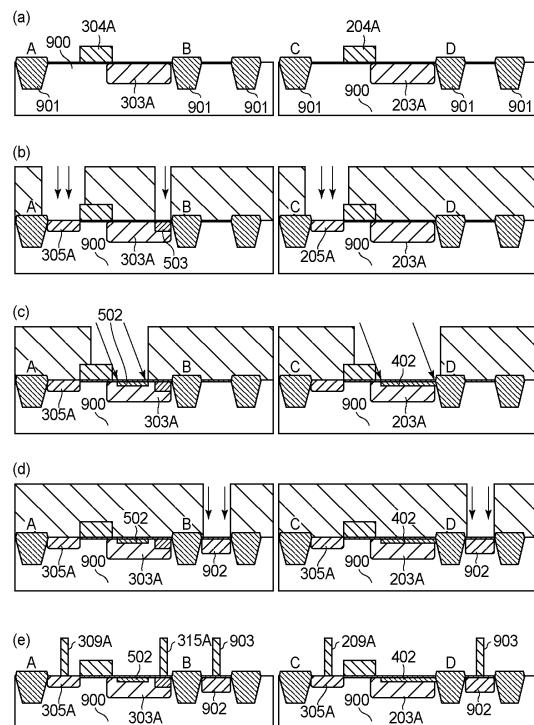

図 3 は、本実施例における受光画素 2、OB 画素 3、および参照画素 4 の構成を示す。

#### 【0040】

図 3 (a) は、受光画素 2 および OB 画素 3 の等価回路図である。図 3 (b) および (c) は、参照画素 4 の等価回路図である。40

#### 【0041】

図 3 (a) に示すように、受光画素 2 および OB 画素 3 は同じ回路構成である。入射した光を光電変換する PD 20 を含む。OB 画素 3 の PD 20 は遮光されており、光を入射しない状態のノイズ信号が蓄積される。

#### 【0042】

一方、図 3 (b) および (c) に示すように、参照画素 4 には PD 20 を含まず、代わりに参照画素 4 は出力制御線 7 に接続される。出力制御線 7 を介して参照画素 4 に供給される電圧値は、VPD1 と VPD2 がある。VPD1 と VPD2 はそれぞれ異なる電圧値で50

あり、出力制御回路 8 は、参照画素 4 に供給する電圧として、V P D 1 と V P D 2 のいずれかを選択することができる。よって、参照画素 4 は V P D 1 に対応したレベルの画素信号と V P D 2 に対応したレベルの画素信号を 1 つの画素毎に選択して出力することができる。

#### 【 0 0 4 3 】

受光画素 2 および O B 画素 3 は、P D 2 0 で発生した電荷を蓄積するフローティングディフュージョン（以下 F D ）2 2、及び、P D 2 0 で発生した電荷を F D 2 2 に転送する転送トランジスタ 2 1 を備える。

#### 【 0 0 4 4 】

参照画素 4 も転送トランジスタ 2 1 を備えている。転送トランジスタ 2 1 は、一方のノードは、電圧値 V P D 1 もしくは電圧阿多い V P D 2 を供給する供給線に接続され、他方のノードは、増幅トランジスタ 2 4 のゲートに接続されている。転送トランジスタ 2 1 は、出力制御線 7 より供給される電圧値 V P D 1 もしくは電圧値 V P D 2 に応じた画素信号を F D 2 2 に転送する。参照画素 4 の F D 2 2 には、出力制御線 7 より供給される電圧値 V P D 1 もしくは電圧値 V P D 2 に応じた画素信号が蓄積される。

10

#### 【 0 0 4 5 】

受光画素 2、O B 画素 3、参照画素 4 のそれぞれは、F D 2 2 を電源電圧 V D D にリセットするリセットトランジスタ 2 3、F D 2 2 の電圧に対応する信号を出力する増幅トランジスタ 2 4 を有する。さらに各画素は、増幅トランジスタ 2 4 の出力を垂直出力線 5 に接続する行選択トランジスタ 2 5 を有する。

20

#### 【 0 0 4 6 】

バッファ回路 1 5 から画素駆動信号線 6 に供給される制御信号のうち、画素信号をリセットする信号 R E S はリセットトランジスタ 2 3 のゲートに出力される。また、信号 T X は、P D 2 0 に蓄積された信号、もしくは出力制御線 7 より供給される電圧値に応じた画素信号を F D 2 2 に転送する転送トランジスタ 2 1 のゲートに出力される。また、信号 S E L は、読み出す行として選択される画素行に属する各画素の行選択トランジスタ 2 5 のゲートに出力される。

#### 【 0 0 4 7 】

以上の構成により、受光画素 2 は入射光量に応じて発生する画素信号、O B 画素 3 は遮光によって発生するダークレベル信号、参照画素 4 で出力制御回路 8 により選択された電圧値 V P D 1 もしくは V P D 2 に対応したレベルの画素信号をそれぞれ出力する。

30

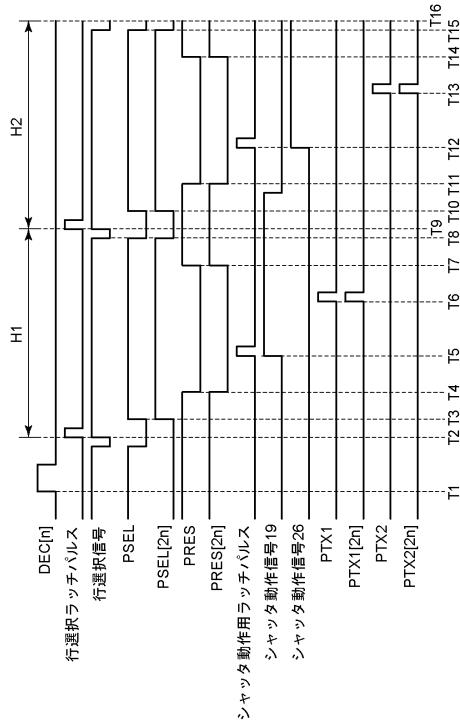

#### 【 0 0 4 8 】

次に、デコーダ信号が出力されてから、受光画素 2、O B 画素 3、参照画素 4 に制御信号が供給されるまでの駆動の詳細を説明する。

#### 【 0 0 4 9 】

図 2 は、n 段目のデコーダ信号が出力された時のタイミングチャートである。

#### 【 0 0 5 0 】

時刻 T 1 で、アドレスデコーダ回路 1 2 は、n 行目を選択するためのデコーダ信号 D E C [ n ] パルスが出力する。

40

#### 【 0 0 5 1 】

時刻 T 2 になる前に、行選択信号 1 8 と信号 P S E L がロー・レベルとなる。

#### 【 0 0 5 2 】

時刻 T 2 に、タイミングジェネレータ 1 6 は、行選択ラッチパルスを n 行目の論理生成部 1 3 - 1 に供給する。これにより、行選択信号 1 8 がハイ・レベルとなる。

#### 【 0 0 5 3 】

時刻 T 3 に、タイミングジェネレータ 1 6 は、n 行目の信号生成セル 1 4 - 1 に供給される信号 P S E L をハイ・レベルにする。行選択信号 1 8 と信号 P S E L の論理積をとることで、n 行目の信号 P S E L [ n ] がハイ・レベルとなる。

#### 【 0 0 5 4 】

時刻 T 4 で、画素リセットパルス P R E S がハイ・レベルからロー・レベルになり、行選択信

50

号 18 と P R E S の論理をとることで、n 行目の画素リセットパルス P R E S [ n ] がローレベルになる。

**【 0 0 5 5 】**

時刻 T 5 に、タイミングジェネレータ 16 は、シャッタ動作用ラッチパルスを n 行目の論理生成部 13 - 1 に供給し、シャッタ動作信号 19 はハイレベルになる。

**【 0 0 5 6 】**

時刻 T 6 に、画素転送パルス P T X がハイレベルとなり、シャッタ動作信号 19 と P T X の論理をとることで、n 行目の画素転送パルス P T X [ n ] がハイレベルとなる。

**【 0 0 5 7 】**

時刻 T 7 に、P R E S がハイレベルとなり、同時に P R E S [ n ] もハイレベルとなる。

10

**【 0 0 5 8 】**

時刻 T 8 に、P S E L がローレベルとなり、同時に P S E L [ n ] もローレベルとなる。

**【 0 0 5 9 】**

時刻 T 9 に、タイミングジェネレータ 16 は、行選択ラッチパルスを論理生成部 13 に供給し、n + 1 行目の画素駆動信号が生成される。

**【 0 0 6 0 】**

時刻 T 2 から T 9 までの期間 H 1 が、n 行目の画素駆動信号生成期間となる。

**【 0 0 6 1 】**

図 4 は、本実施例における、受光画素 2 、O B 画素 3 、および参照画素 4 の動作タイミングを示す。

20

**【 0 0 6 2 】**

信号 P S E L ( n ) は行選択トランジスタ 25 のゲートに入力される信号である。信号 P R E S ( n ) はリセットトランジスタ 23 のゲートに入力される信号である。信号 P T X ( n ) は転送トランジスタ 21 のゲートに入力される信号である。なお、トランジスタのゲートに入力される信号がハイレベルの場合、当該トランジスタはオンする。一方、ゲートに入力される信号がローレベル場合、当該トランジスタはオフする。また、図 4 は、受光画素 2 の F D の電圧と、参照画素 4 の F D の電圧をそれぞれ示している。

**【 0 0 6 3 】**

時刻 T 1 0 0 より前の期間では、行選択トランジスタ 25 はオフとなっている。つまり、時刻 T 1 0 0 より前の期間では、図 4 に示した駆動を行う画素行は、信号を出力する画素行には選択されていない。一方、リセットトランジスタ 23 はオンとなっている。よって、電源電圧 V D D と増幅トランジスタ 24 のゲートが接続されている。よって、F D 2 2 の電圧が電源電圧 V D D に対応する電圧にリセットされている。よって、図 4 に示した画素行に属する受光画素 2 、O B 画素 3 、参照画素 4 のそれぞれの F D の電圧は電源電圧 V D D である。厳密に言えば、この時の F D 2 2 の電圧は、電源電圧 V D D から、リセットトランジスタ 23 の閾値電圧 V t h を引いた電圧であるが、電源電圧 V D D として扱って差し支えない。よって、この時の F D 2 2 の電圧を電源電圧 V D D として扱う。

30

**【 0 0 6 4 】**

時刻 T 1 0 2 よりも前の期間では、転送トランジスタ 21 はオフとなっている。よって、P D 2 0 と増幅トランジスタ 24 のゲートとは電気的に切り離されている。これにより、P D 2 0 はフローティング状態となるから、受光画素 2 には入射光量に応じて光電変換された電荷が蓄積される。また、O B 画素 3 には光が入射しないダークレベルの電荷が蓄積される。参照画素 4 には出力制御回路 8 により選択した電圧値である V P D 1 もしくは V P D 2 に対応したレベルの信号が蓄積される。

40

**【 0 0 6 5 】**

時刻 T 1 0 0 に、図 4 に示した動作を行う画素行が信号を出力する画素行として選択される。つまり、信号 P S E L ( n ) がハイレベルとなって、行選択トランジスタ 25 がオンする。これにより、増幅トランジスタ 24 と垂直出力線 5 が接続される。

**【 0 0 6 6 】**

時刻 T 1 0 1 に、R E S 信号がローレベルとなり、リセットトランジスタ 23 がオフする

50

。これにより、電源電圧 V D D と増幅トランジスタ 2 4 のゲートとが電気的に切り離される。受光画素 2 、 O B 画素 3 、および参照画素 4 のそれぞれの F D 2 2 のリセットノイズに対応したノイズ信号が増幅トランジスタ 2 4 により、垂直出力線 5 に出力される。

#### 【 0 0 6 7 】

時刻 T 1 0 2 に、転送トランジスタ 2 1 がオンする。これにより、 P D 2 0 と増幅トランジスタ 2 4 のゲートが電気的に接続される。よって、受光画素 2 および O B 画素 3 において、 P D 2 0 に蓄積された電荷が F D 2 2 に転送される。したがって、 F D 2 2 の電圧は、電源電圧 V D D に対応した電圧から信号電圧 V s i g に変化する。受光画素 2 の増幅トランジスタ 2 4 は、信号電圧 V s i g に応じた信号レベルの画素信号を、垂直出力線 5 に出力する。

10

#### 【 0 0 6 8 】

一方、参照画素 4 は、出力制御回路 8 により選択された電圧値 V P D 1 もしくは電圧値 V P D 2 が、 F D 2 2 に転送される。これにより、 F D 2 2 の電圧は、電圧値 V P D 1 が F D 2 2 に供給されている場合は、電源電圧 V D D に対応した電圧から電圧 V P D 1 に変化する。一方、電圧値 V P D 2 が F D 2 2 に供給されている場合は、 F D 2 2 の電圧は、電源電圧 V D D に対応した電圧から電圧 V P D 2 に変化する。参照画素 4 の増幅トランジスタ 2 4 は、電圧値 V P D 1 または電圧値 V P D 2 に応じた信号レベルの画素信号を垂直出力線 5 に出力する。

#### 【 0 0 6 9 】

時刻 T 1 0 3 に、リセットトランジスタ 2 3 がオンする。これにより、 F D 2 2 が電源電圧 V D D によってリセットされる。その後、行選択トランジスタ 2 5 がオフする。これによって、1行に含まれる受光画素 2 、 O B 画素 3 、参照画素 4 からの画素信号の読み出し動作が終了する。

20

#### 【 0 0 7 0 】

同じ行に属する受光画素 2 、 O B 画素 3 、参照画素 4 は、共通の画素信号駆動線 6 が接続されている。したがって、同じ行に属する、受光画素 2 、 O B 画素 3 、及び、参照画素 4 の画素信号は、それぞれ対応する垂直出力線 5 に、並行して読み出される。なお、参照画素 4 の画素信号は、撮像領域 1 の各行を識別するためのアドレス信号となる。

#### 【 0 0 7 1 】

次に、複数の参照画素 4 が出力する画素信号によって成されるアドレス信号の詳細を説明する。

30

#### 【 0 0 7 2 】

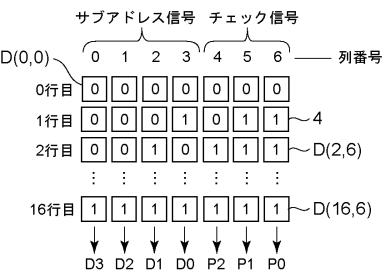

##### ( アドレス信号の例 1 )

参照画素 4 の出力する画素信号が構成するアドレス信号を詳細に説明する。本実施例のアドレス信号には、デジタル信号が用いられる。すなわち、参照画素 4 の画素信号は、デジタル信号の各ビットの信号値に相当する。図 5 が示す通り、電圧 V a に対応したレベルの画素信号が「 0 」を表し、電圧 V b に対応したレベルの画素信号が「 1 」を表す。画素信号を互いに区別するため、画素信号に符号 D ( m 、 n ) を付している。 m は行番号を表し、 n は列番号を表す。

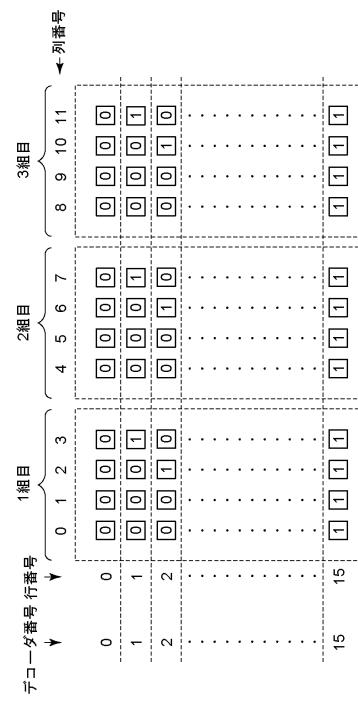

#### 【 0 0 7 3 】

図 5 は、本実施例のアドレス信号の信号値を模式的に示している。図 5 には、 1 6 行 × 1 2 列の参照画素 4 の画素信号が例示されている。しかし、参照画素 4 の数はこれに限定されるものではない。

40

#### 【 0 0 7 4 】

本実施例では、1つの行に、12個の参照画素 4 が含まれている。つまり、本実施例では、アドレス信号は、12ビットのデジタル信号として表される。1つの行の参照画素 4 からの画素信号が成すアドレス信号は、同じ信号値を持つ3組のサブ信号を含む。例えば1行目の列番号 0 ~ 3 の参照画素 4 は、信号値「 0 0 0 1 」を持つサブ信号を出力する。1行目の列番号 4 ~ 7 の参照画素 4 は、同じ信号値「 0 0 0 1 」を持つサブ信号を出力する。そして、1行目の列番号 8 ~ 11 の参照画素 4 は、同じ信号値「 0 0 0 1 」を持つサブ

50

信号を出力する。

**【 0 0 7 5 】**

また、アドレス信号は行ごとに異なる信号値を持つ。例えば、1行目のアドレス信号のサブ信号は、信号値「0 0 0 1」を持つ。2行目のアドレス信号のサブ信号は、信号値「0 0 1 0」を持つ。「0 0 0 1」と「0 0 1 0」とは異なる信号値である。

**【 0 0 7 6 】**

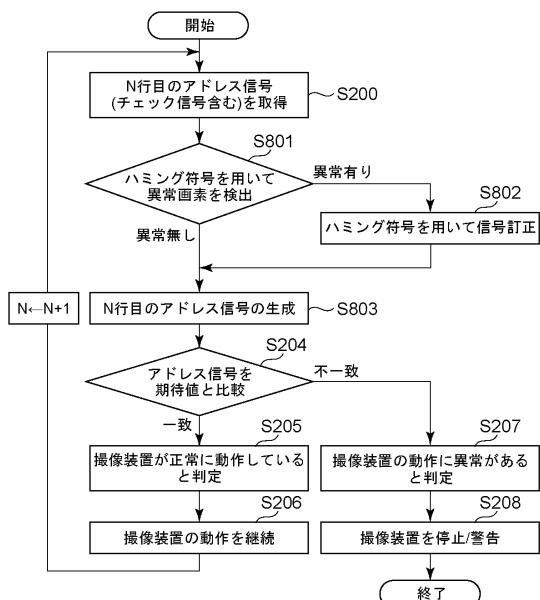

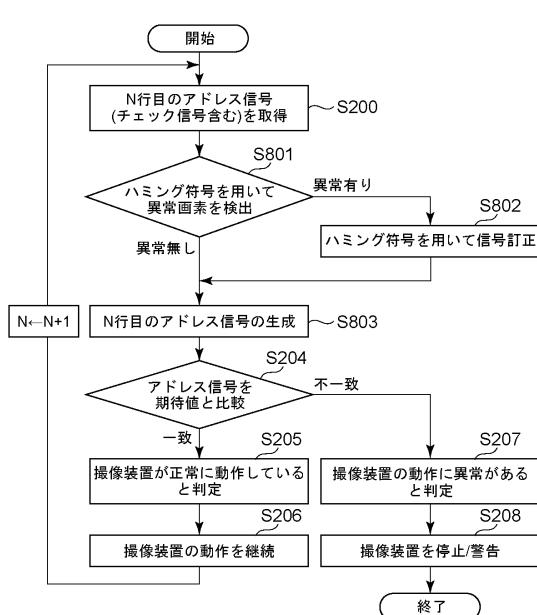

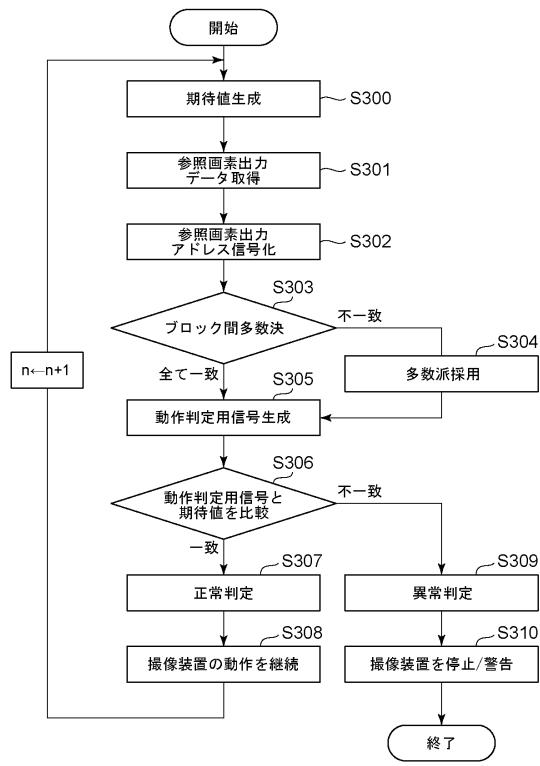

続いて、アドレス信号に基づいて、撮像装置が正常に画素信号を出力しているか否かを判断する方法を説明する。図6は、撮像装置の動作を判断するためのフローチャートである。この判断処理は、例えば、撮像装置の外部の信号処理部によって行われる。あるいは、撮像装置の内部の信号処理回路によって行われる。

10

**【 0 0 7 7 】**

ステップS200で、N行目のアドレス信号を取得する。前述の通り、アドレス信号は3組のサブ信号を含んでいる。

**【 0 0 7 8 】**

ステップS201で、3組のサブ信号の信号値が互いに一致しているかを判定する。3組のサブ信号の信号値が全て一致した場合、参照画素4に異常はないと判断する。この場合、次のステップS203に進む。もし、3組のサブ信号のいずれか1つの信号値が、他の信号値と異なる場合には、参照画素4の一部に異常があると判断する。この場合ステップS202に進む。

20

**【 0 0 7 9 】**

ステップS202では、多数派のサブ信号の信号値を、当該行を表すアドレス信号として採用する。換言すると、ステップS202では、3つのサブ信号を用いた多数決を行う。例えば、3つのサブ信号の信号値が、それぞれ、「0 0 0 1」、「0 0 0 1」、「0 1 0 1」である場合、N行目を示すアドレス信号の信号値として、「0 0 0 1」を採用する。

**【 0 0 8 0 】**

ステップS203では、前のステップで得られた信号値を持つアドレス信号を、N行目を示すアドレス信号として生成する。3組のサブ信号の信号値が全て一致している場合は、その一致した信号値を持つアドレス信号が生成される。いずれか1つのサブ信号の信号値が他の信号値と異なる場合は、ステップS202の多数決によって選ばれた信号値を持つアドレス信号が生成される。

30

**【 0 0 8 1 】**

ステップS204では、生成されたアドレス信号を、N行目のアドレス信号の期待値と比較する。アドレス信号の信号値が期待値に一致した場合は、ステップS205で撮像装置が正常に動作していると判定する。そして、N+1行目の読み出し動作に移行する。

**【 0 0 8 2 】**

ステップS204においてアドレス信号の信号値が期待値に一致しない場合は、ステップS207で撮像装置の動作に異常があると判定する。つまり、撮像装置に故障が生じたと判断する。この場合は、ステップS208で、撮像装置の動作を停止する、あるいは、撮像装置が故障したことを示す警告を行う。

40

**【 0 0 8 3 】**

以上に説明した通り、本実施例では、参照画素4の出力する画素信号が、属する行の位置を示すアドレス信号を構成する。このような構成により、指定された行から正常に画素信号が出力されたか否かを判断することができる。結果として、撮像装置の故障を正確に検知することができる。

**【 0 0 8 4 】**

また、本実施例では、1つのアドレス信号が、互いに同じ信号値を持つ3つのサブ信号を含む。このような構成により、一部の参照画素4に異常が生じても、撮像装置の故障の有無を正確に判断することができる。つまり、1つの行に含まれる複数の参照画素4が、全体として、参照画素の異常を検出する検出手段として機能している。

**【 0 0 8 5 】**

50

(実施例 1 の効果 )

本実施例では、1段のアドレスデコーダが選択された場合に、複数の画素行のうち、1つの画素行が選択される。選択された1行に含まれる複数の参照画素4の画素信号は、他の行の複数の参照画素4の画素信号とは異なる値であって、選択された1行に固有のアドレス信号を形成する。このアドレス信号を用いることで、撮像装置の外部の信号処理部が、当該アドレス信号を出力した画素行を識別することができる。そして信号処理部が、選択された行が正常に画素信号を出力しているか否かを判定することができる。本実施例の撮像装置は、アドレスデコーダ信号に応じた制御信号を出力する信号生成セル14-nごとに動作判定を行うことを可能としている。

【 0 0 8 6 】

特許文献1に記載の撮像装置では、1フレームごとに撮像装置の異常の有無を判定していたため、撮像装置の異常の有無の検出に1フレームの期間を要していた。また、複数行に渡って配された参照画素を用いた場合における、撮像装置の故障の有無の判定の高速化に寄与する、参照画素からの信号を好適に読み出す回路について検討がなされていなかった。本実施例では、参照画素4が配された行に対応して、信号生成セル14-nが設けられている。よって、参照画素4が配された複数行のうち、一部の行のみを選択して画素信号を読み出すことができる。これにより、参照画素4が配された全ての画素行から画素信号を読み出す場合に比べて、画素信号を垂直出力線5に読み出す期間を短縮することができる。これにより、その後の列回路9の信号処理期間の回数および複数の列回路9から信号を読み出す水平走査期間の回数もまた低減される。撮像装置の外部の信号処理部は、参照画素3が配された全ての行からの画素信号の読み出しを待たずに、一部の行のみの参照信号3の画素信号を用いて、撮像装置の故障の有無を判定することができる。これにより、本実施例では、複数行に渡って配された参照画素を用いた場合における、撮像装置の故障の有無の判定の高速化に寄与する、参照画素からの信号の好適な読み出しを実現することができる。

【 0 0 8 7 】

また、撮像装置に異常があると判定された時点で、撮像装置の動作を停止させることができる。したがって、撮像装置に故障が生じている状態のまでの撮像動作の継続を防ぐことができる。撮像装置の形態として、例えば、工場の生産ラインに流れる物体を検出する工業用カメラや、自動車の運転支援のために前方を撮影する車載カメラ等がある。たとえば、工業用カメラでは撮像装置の故障の高速な検出によって、生産ラインをより早急に停止させることができる。また、車載カメラでは、撮像装置の故障の高速な検出によって、運転者に故障を素早く通知することができる。よって、撮像装置の故障の有無の判断の高速化は、この撮像装置を利用する装置あるいは人に及ぼす影響を小さくすることができる効果がある。

【 0 0 8 8 】

(アドレス信号の例 2 )

アドレス信号について、別の例を説明する。以下の例では、上述した例に対し、アドレス信号の構成が異なる。

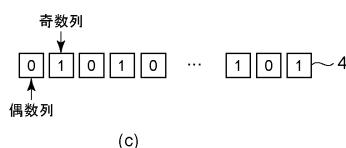

【 0 0 8 9 】

図7は、本実施例のアドレス信号の信号値を模式的に示している。図7(a)に示された撮像装置では、各行が1つの参照画素4を含む。参照画素4は、属する行が偶数行であるか奇数行であるかを示す画素信号を出力する。例えば、偶数行の参照画素4は、「0」を示すレベルの画素信号を出力する。奇数行の参照画素4は、「1」を示すレベルの画素信号を出力する。その他の構成は、実施例1と同じであるため、説明を省略する。

【 0 0 9 0 】

このような構成により、撮像装置から正しい順序で信号が出力されているかを判定することができる。例えば、全ての行から順番に画素信号を出力する動作を行う場合、出力されるアドレス信号の信号値は、「0」と「1」とで交互に変化する。このアドレス信号の変化を検出することで、撮像装置が正しく画素信号を出力していることを判断できる。

10

20

30

40

50

**【 0 0 9 1 】**

図7( b )は、別の実施例を示している。図7( b )に示された撮像装置では、参照画素4が、属する行に固有のレベルの画素信号を出力する。そして、参照画素4の出力する画素信号のレベルが、アドレス信号の信号値を表す。つまり、本実施例のアドレス信号はアナログ信号である。具体的に、0行目の参照画素4は、電圧V0に対応するレベルの画素信号を出力する。同様に、n行目の参照画素4は、電圧Vnに対応するレベルの画素信号を出力する。電圧V0から電圧Vnのそれぞれは、他の電圧と異なる値である。

**【 0 0 9 2 】**

このような構成により、指定した行の画素信号が適切に出力されているかを判断することができる。例えば、2行目の受光画素2およびOB画素3から画素信号を読み出す時に、参照画素4から出力された画素信号の信号値が、2行目に割り当てられた信号値、この例では電圧V2に一致するかを判断する。両者が一致していない場合には、2行目の受光画素2およびOB画素3から画素信号が読み出されていない可能性があるため、撮像装置が故障したと判断することができる。

10

**【 0 0 9 3 】**

図7( c )は、さらに別の実施例を示している。図7( c )に示された撮像装置では、1つの列に1つの参照画素4が配されている。参照画素4は、属する列が偶数列であるか奇数列であるかを示す画素信号を出力する。他の構成は図7( a )で説明した内容と同じである。また、各列の参照画素4が、図7( b )のように、互いに異なるレベルの画素信号を出力するように構成されてもよい。

20

**【 0 0 9 4 】**

以上に説明した通り、本実施例では、参照画素4の出力する画素信号が、属する行または列の位置を示すアドレス信号を構成する。このような構成により、指定された行または列から正常に画素信号が出力されたか否かを判断することができる。結果として、撮像装置の故障を正確に検知することができる。

**【 0 0 9 5 】**

さらに、本実施例では、1つの行が1つの参照画素4のみを含むか、あるいは、1つの列が1つの参照画素4のみを含む。したがって、参照画素4の数を低減することができるため、撮像装置を小型化することができる。

**【 0 0 9 6 】**

30

なお、本実施例は、参照画素4の異常を検出する検出手段を備えていない。そのため、図6のフローチャートのステップS201とステップS202を行わない。参照画素4から出力された画素信号をそのままアドレス信号として用いる。本実施例の変形例として、実施例1のように、参照画素4の異常を検出する検出手段を追加してもよい。

**【 0 0 9 7 】****( アドレス信号の例 3 )**

アドレス信号の別の一例について説明する。本例は、アドレス信号の例1に対し、アドレス信号の構成が異なる。以下では主として、アドレス信号の例1と異なる部分を説明する。

**【 0 0 9 8 】**

本例では、同じ行に含まれる受光画素2、OB画素3、および、参照画素4が、共通の駆動制御線6-1に接続されている。そのため、受光画素2やOB画素3から画素信号が読み出されるのと並行して、参照画素4から画素信号が読み出される。参照画素4から画素信号は、その属する行を示すアドレス信号を構成する。そのため、このような構成により、指定された行から正常に画素信号が出力されたか否かを判断することができる。なお、同じ行に含まれる受光画素2、OB画素3、および、参照画素4は、それぞれ、電気的に分離された個別の駆動制御線に接続されてもよい。同じ行の受光画素2、OB画素3、および、参照画素4が、共通の駆動制御線6-1に接続されることとは、これらの画素信号を並行して読み出す構成の1つの例である。

40

**【 0 0 9 9 】**

参照画素4の出力する画素信号が構成するアドレス信号を詳細に説明する。本例のアドレ

50

ス信号には、デジタル信号が用いられる。すなわち、参照画素 4 の画素信号は、デジタル信号の各ビットの信号値に相当する。図 4 が示す通り、電圧 V a に対応したレベルの画素信号が「0」を表し、電圧 V b に対応したレベルの画素信号が「1」を表す。画素信号を互いに区別するため、画素信号に符号 D ( m, n ) を付している。m は行番号を表し、n は列番号を表す。

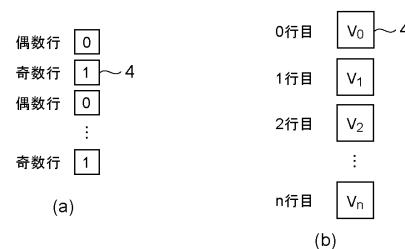

#### 【 0 1 0 0 】

図 8 は、本実施例のアドレス信号の信号値を模式的に示している。図 8 には、16 行 × 7 列の参照画素 4 の画素信号が例示されている。しかし、参照画素 4 の数はこれに限定されるものではない。

#### 【 0 1 0 1 】

1 つの行に、7 個の参照画素 4 が含まれている。つまり、本実施例では、アドレス信号は、7 ビットのデジタル信号として表される。1 つの行の参照画素 4 からの画素信号が成すアドレス信号は、属する行の位置を示すサブアドレス信号と、チェック信号とを含む。各行の列番号 0 ~ 3 の参照画素 4 の出力する画素信号が、サブアドレス信号を構成する。各行の列番号 4 ~ 6 の参照画素 4 の出力する画素信号が、チェック信号を構成する。チェック信号は、アドレス信号の誤りを訂正するための情報を含む。本実施例のチェック信号は、サブアドレス信号に対してハミング符号化演算を行うことで設定される。つまり、本実施例のアドレス信号には、ハミング符号が用いられている。なお、この他の例として、チェック信号がパリティビットとして生成されてもよい。

#### 【 0 1 0 2 】

ハミング符号化演算について説明する。本実施例では、サブアドレス信号は 4 ビットのデジタル信号である。サブアドレス信号を構成する 4 ビットを D 0 ~ D 3 で表す。チェック信号は 3 ビットのデジタル信号である。チェック信号を構成する 3 ビットを P 0 ~ P 2 で表す。下記の式(1) ~ 式(3)の演算を行うことで、チェック信号の各ビットの信号値が得られる。

$$P_2 = D_3 + D_2 + D_1 \quad (1)$$

$$P_1 = D_3 + D_1 + D_0 \quad (2)$$

$$P_0 = D_2 + D_1 + D_0 \quad (3)$$

各式において、「+」は排他的論理和 (EXOR) の論理演算を行うことを意味する。2 つの論理値が異なる場合は、演算結果は「1」である。2 つの論理値が等しい場合は、演算結果は「0」である。

#### 【 0 1 0 3 】

0 行目のサブアドレス信号は、信号値「0 0 0 0」を持つ。そのため、0 行目のチェック信号は、信号値「0 0 0」を持つ。1 行目のサブアドレス信号は、信号値「0 0 0 1」を持つ。そのため、1 行目のチェック信号は、信号値「0 1 1」を持つ。2 行目のサブアドレス信号は、信号値「0 0 1 0」を持つ。そのため、2 行目のチェック信号は、信号値「1 1 1」を持つ。他の行についても、同様にして、チェック信号の信号値が設定される。本実施例では、アドレス信号が行ごとに異なる信号値を持つ。

#### 【 0 1 0 4 】

続いて、アドレス信号に基づいて、撮像装置が正常に画素信号を出力しているか否かを判断する方法を説明する。図 9 は、撮像装置の動作を判断するためのフローチャートである。図 6 と同じ動作を行うステップには、図 6 と同じ符号を付してある。この判断処理は、例えば、撮像装置の外部の信号処理部によって行われる。あるいは、撮像装置の内部の信号処理回路によって行われる。

#### 【 0 1 0 5 】

ステップ S 2 0 0 で、N 行目のアドレス信号を取得する。前述の通り、アドレス信号はサブアドレス信号とチェック信号とを含んでいる。

#### 【 0 1 0 6 】

ステップ S 8 0 1 で、ハミング符号化されたアドレス信号を用いて参照画素 4 に異常が生じているかを判定する。具体的には、アドレス信号に対して復号処理を行う。これにより

10

20

30

40

50

、アドレス信号のどのビットに異常が生じているかを判定することができる。復号処理について、公知のハミング符号の復号技術が用いられる。

#### 【0107】

ステップS801で、参照画素4の異常が検知された場合は、ステップS802においてアドレス信号の信号値を訂正する。具体的には、異常であると判断された参照画素4に対応するビットの信号値を反転する。その後、ステップS803に進む。ステップS801で、参照画素4の異常が検知されなかった場合は、そのまま、ステップS803に進む。

#### 【0108】

ステップS803では、前のステップで得られた信号値を持つアドレス信号を、N行目を示すアドレス信号として生成する。参照画素4に異常がない場合は、サブアドレス信号の信号値を持つアドレス信号が生成される。参照画素4に異常がある場合は、ステップS802で訂正されたサブアドレス信号の信号値を持つアドレス信号が生成される。

10

#### 【0109】

以降の動作は、アドレス信号の例1と同じである。ステップS204では、生成されたアドレス信号を、N行目のアドレス信号の期待値と比較する。アドレス信号の信号値が期待値に一致した場合は、ステップS205で撮像装置が正常に動作していると判定する。そして、N+1行目の読み出し動作に移行する。

#### 【0110】

ステップS204においてアドレス信号の信号値が期待値に一致しない場合は、ステップS207で撮像装置の動作に異常があると判定する。つまり、撮像装置に故障が生じたと判断する。この場合は、ステップS208で、撮像装置の動作を停止する、あるいは、撮像装置が故障したことを示す警告を行う。

20

#### 【0111】

以上に説明した通り、本例では、参照画素4の出力する画素信号が、属する行の位置を示すアドレス信号を構成する。このような構成により、指定された行から正常に画素信号が出力されたか否かを判断することができる。結果として、撮像装置の故障を正確に検知することができる。

#### 【0112】

また、本例では、アドレス信号がハミング符号化演算に基づいて演算されたチェック信号を含む。このような構成により、一部の参照画素4に異常が生じっていても、撮像装置の故障の有無を正確に判断することができる。つまり、チェック信号を構成する画素信号を出力する参照画素4が、参照画素の異常を検出する検出手段として機能している。

30

#### 【0113】

以上の説明では、各行のアドレス信号を例に挙げたが、各列のアドレス信号を用いて撮像装置の動作の判定を行ってもよい。この場合、明細書中の「行」を「列」に読み替えればよい。

#### 【0114】

##### (アドレス信号の例4)

アドレス信号の例4について説明する。本例では、1つの参照画素が互いに異なるレベルの複数の画素信号を出力する点において、アドレス信号の例1と異なる。また、参照画素4の異常を検出する方法が、アドレス信号の例1と異なる。以下では主として、アドレス信号の例1と異なる部分を説明する。

40

#### 【0115】

なお、実施例1の参照画素4は、出力制御回路304の制御に基づいて、電圧V<sub>a</sub>に対応するレベルの画素信号と、電圧V<sub>b</sub>に対応するレベルの画素信号とを、選択的に出力するように構成されている。しかし、実施例1においては、必ずしも、1つの参照画素4が、レベルの異なる2つの画素信号を出力しなくてもよい。これに対して、本実施例の参照画素4は、出力制御回路304の制御に基づいて、電圧V<sub>a</sub>に対応するレベルの画素信号と、電圧V<sub>b</sub>に対応するレベルの画素信号との両方を出力する。参照画素4の出力する画素信号のレベルが予期した通りに変化するかを判定することにより、参照画素4の異常の有

50

無を判定することができる。

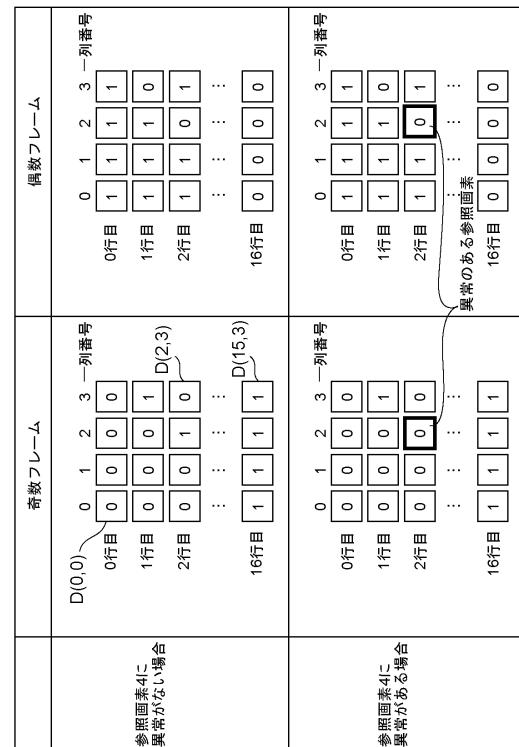

**【0116】**

図10は、本例のアドレス信号の信号値を模式的に示している。図10には、16行×4列の参照画素4の画素信号が例示されている。しかし、参照画素4の数はこれに限定されるものではない。1つの行に、4個の参照画素4が含まれている。つまり、本実施例では、アドレス信号は、4ビットのデジタル信号として表される。

**【0117】**

図10は、各行のアドレス信号が、撮像装置の動作状態に応じて、異なる信号値を持つ例を示す。具体的には、奇数フレームにおけるアドレス信号と、偶数フレームにおけるアドレス信号とが、互いに反転した信号値を持つ。例えば、2行目のアドレス信号は、奇数フレームにおいては、信号値「0010」を持つ。一方、2行目のアドレス信号は、偶数フレームにおいては、信号値「1101」を持つ。同様に、図10が示す通り、奇数フレームと偶数フレームとにおいて、アドレス信号の各ビットの信号値が反転する。出力制御回路304が、参照画素4に供給する電圧を、フレームごとに電圧V<sub>a</sub>と電圧V<sub>b</sub>との間で切り替えることで、アドレス信号の各ビットの信号値を反転させることができる。

10

**【0118】**

ここで、参照画素4に異常がある場合、当該参照画素4の出力する画素信号のレベルが変化しない。図10は、2行目の列番号2の参照画素4に異常がある例を示している。奇数フレームでは、2行目のアドレス信号は、信号値「0000」を持つ。一方、偶数フレームでは、2行目のアドレス信号は、信号値「1101」を持つ。このように、信号値D(2、2)が反転しないため、2行目の列番号2の参照画素4に異常があることを検知することができる。

20

**【0119】**

アドレス信号の信号値を変化の仕方について、別の例を説明する。図11は、本実施例のアドレス信号の信号値を模式的に示している。図11には、16行×4列の参照画素4の画素信号が例示されている。しかし、参照画素4の数はこれに限定されるものではない。1つの行に、4個の参照画素4が含まれている。つまり、本実施例では、アドレス信号は、4ビットのデジタル信号として表される。

**【0120】**

図11に示された例では、撮像を行っている期間と、それ以外の期間とにおいて、同じ参照画素4から出力される画素信号によって構成されるアドレス信号の信号値が異なる。そして、受光画素2およびOB画素3から画素信号を出力する前、あるいは、1フレームの撮像を行う前に、参照画素4の画素信号を読み出す動作を行う。まず、出力制御回路304が、全ての参照画素4に、信号値「0」に対応する電圧V<sub>a</sub>を供給する。この状態で、参照画素4の画素信号を読み出す。この読み出し動作を、撮像前フレーム1の読み出し動作と呼ぶ。次に、出力制御回路304が、全ての参照画素4に、信号値「1」に対応する電圧V<sub>b</sub>を供給する。この状態で、参照画素4の画素信号を読み出す。この読み出し動作を、撮像前フレーム2の読み出し動作と呼び。参照画素4に異常がなければ、各参照画素4の出力する画素信号は、いずれも、「0」と「1」とを交互に示す。

30

**【0121】**

ここで、参照画素4に異常がある場合、当該参照画素4の出力する画素信号のレベルが変化しない。図11は、2行目の列番号2の参照画素4に異常がある例を示している。上述の撮像前フレーム1の読み出し動作と撮像前フレーム2の読み出し動作とを行うと、図11が示す通り、信号値D(2、2)が反転しないことがわかる。つまり、2行目の列番号2の参照画素4に異常があることを検知することができる。

40

**【0122】**

その後、撮像を行う時には、各行のアドレス信号が属する行に固有の信号値を持つように、出力制御回路304が電圧V<sub>a</sub>および電圧V<sub>b</sub>のいずれかを選択して参照画素4に供給する。

**【0123】**

50

このように、本実施例の撮像装置によれば、図10や図11に示した方法により、参照画素4の異常を検知することができる。そこで、異常のある参照画素4の画素信号を含むアドレス信号に対しては、図6および図9に示されたアドレス信号と期待値との比較(ステップS204)を行わないなどの処理を行うことができる。これにより、誤って撮像装置が故障していると判断する可能性を低減することができる。すなわち、本実施例では、出力制御回路304が、参照画素の異常を検出する検出手段として機能している。

#### 【0124】

##### (実施例2)

実施例2について説明する。実施例1と行選択行およびアドレス信号の構成が異なる。本実施例では、実施例1と異なる部分の詳細を説明し、実施例1と同様の箇所の説明は省略する。

10

#### 【0125】

図12は、本実施例における撮像装置の全体構成を示す。

#### 【0126】

本実施例の撮像装置は、実施例1の撮像装置に対して、垂直走査回路11の構成が異なる。実施例1の撮像装置の垂直走査回路は、1つのアドレスデコーダ信号によって、1行の画素行を制御していた。本実施例の撮像装置の垂直走査回路は、1つのアドレスデコーダ信号によって、2行の画素行が制御される点が異なる。別の見方をすれば、1つの信号生成セル14-nが出力する制御信号によって、2行の画素行が制御される。

20

#### 【0127】

画素の行数は、PDを基準に計算する。つまり、2行の画素行とは、2行のPD20および2行のPD20が蓄積する電荷に基づく信号を出力するための画素回路を指す。本実施例では、後述するように、2つのPD20が1つのFD22を共有している。よって、2行の画素行とは、2つのPD20と、1つの画素回路を含む。

#### 【0128】

アドレスデコーダ回路12からデコーダ信号DEC[n]が出力されると、2n行目の論理生成部13-2は、この信号を受けて、行選択信号18と、シャッタ動作信号19と、シャッタ動作信号19を2n行目の信号生成セル14-2に供給する。

#### 【0129】

シャッタ動作信号19とPTX1の論理処理によりPTX1[2n]が生成され、シャッタ動作信号26とPTX2の論理処理によりPTX2[2n]が生成される。

30

#### 【0130】

また、2n行目の論理生成部13-2は、行選択信号18を2n行目の信号生成セル14-2に供給し、行選択信号18とPSELの論理処理によりPSEL[2n]が生成され、行選択信号18とPRESの論理処理によりPRES[2n]が生成される。

#### 【0131】

生成された制御パルスPSEL[2n]、PRES[2n]、PTX1[2n]及び、PTX2[2n]のそれぞれは、バッファ回路15を介して、2n行目および2n+1行目の画素駆動信号線6に供給される。制御パルスPSEL[2n]、PRES[2n]は、2n行目および2n+1行目に属する画素を共通に制御する制御信号である。制御パルスPTX1[2n]は、2n行目に属する画素の転送トランジスタ21を制御する制御信号である。制御パルスPTX2[2n]は、2n+1行目に属する画素の転送トランジスタ21を制御する制御信号である。このような構成をとることにより、1つのアドレスデコーダ信号に対して、2行の画素行が制御される。

40

#### 【0132】

次に、アドレスデコーダ信号が出力されてから、対応する画素行に制御信号が供給されるまでの駆動タイミングの詳細を説明する。

#### 【0133】

図13は、本実施例における垂直走査回路の動作タイミングチャートである。

#### 【0134】

50

時刻 T<sub>2</sub> から T<sub>9</sub> までの期間 H<sub>1</sub> は、2n 行目の画素駆動信号生成期間を示す。時刻 T<sub>9</sub> から T<sub>16</sub> までの期間 H<sub>2</sub> は、2n + 1 行目の画素駆動信号生成期間を示す。

【0135】

図 13 に記載されている P TX<sub>1</sub> とは、実施例 1 の図 2 に示す P TX と同様の動作をする。

【0136】

また、図 13 に記載されている P TX<sub>1</sub>[n] に関しても、実施例 1 の図 2 に示す P TX[2n] と同様の動作をするため、時刻 T<sub>9</sub> 以前までの説明は省略する。

【0137】

時刻 T<sub>9</sub> に、タイミングジェネレータ 16 が、行選択ラッチパルスを 2n 行目の論理生成部 13 - 2 に供給する。これにより、行選択信号 18 がハイレベルになる。

10

【0138】

時刻 T<sub>10</sub> に、タイミングジェネレータ 16 が、2n 行目の信号生成セル 14 - 2 に供給する画素選択パルス PSEL をハイレベルとする。これにより、行選択信号 18 と PSEL の論理をとることで、2n + 1 行目の信号 PSEL[2n] がハイレベルとなる。信号 PSEL[2n] は、2n 行目に属する画素と、2n + 1 行目に属する画素とを制御する選択パルスである。

【0139】

時刻 T<sub>11</sub> に、タイミングジェネレータ 16 が、信号 PRES をローレベルとする。行選択信号 18 と信号 PRES の論理をとることで、2n + 1 行目の信号 PRES[2n] がローレベルになる。信号 PRES[2n] は、2n 行目に属する画素のリセットトランジスタ 23 および、2n + 1 行目に属する画素のリセットトランジスタ 23 を制御する信号である。

20

【0140】

時刻 T<sub>12</sub> に、タイミングジェネレータ 16 が、シャッタ動作用ラッチパルスを 2n 行目の論理生成部 13 - 2 に供給する。これにより、シャッタ動作信号 19 はハイレベルになる。

【0141】

時刻 T<sub>13</sub> に、タイミングジェネレータ 16 は、画素転送パルス P TX<sub>2</sub> をハイレベルとする。これにより、2n + 1 行目の信号 P TX<sub>2</sub>[2n] がハイレベルとなる。

30

【0142】

時刻 T<sub>14</sub> に、タイミングジェネレータ 16 が PRES をハイレベルとする。これにより、信号 PRES[2n] がハイレベルとなる。

【0143】

時刻 T<sub>15</sub> に、タイミングジェネレータ 16 が PSEL をローレベルにする。これにより、信号 PSEL[2n] がローレベルとなる。

【0144】

時刻 T<sub>16</sub> に、タイミングジェネレータ 16 が、行選択ラッチパルスを論理生成部 13 に供給する。これにより、2n + 2 行目の画素駆動信号が生成される。

【0145】

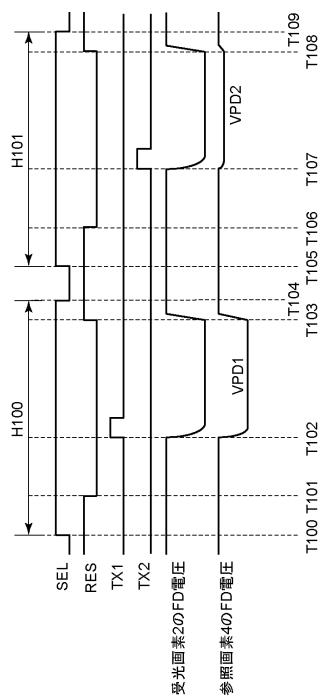

図 14 は、本実施例における、受光画素 2、OB 画素 3、および参照画素 4 の構成を示す。

40

【0146】

図 14(a) は、受光画素 2 および OB 画素 3 の等価回路図である。図 14(b) は参照画素 4 の等価回路図である。

【0147】

図 14(a) に示すように、PD20 - 1 を 2n 行目の PD とした場合、PD20 - 2 は 2n + 1 行目の PD を示す。PD20 - 1 には、2n 行目の転送トランジスタ 21 - 1 が接続する。PD20 - 2 には、2n + 1 行目の転送トランジスタ 21 - 2 が接続する。2n 行目の転送トランジスタ 21 - 1 と 2n + 1 行目の転送トランジスタ 21 - 2 は FD22 に接続される。つまり、2 行の画素が、1 つの FD22 を共有する。また、OB 画素 3 の PD20 - 1、PD20 - 2 は遮光されている。

50

**【 0 1 4 8 】**

一方、図 14 ( b ) に示すように、参照画素 4 に関しても、受光画素 2 、 O B 画素 3 と同じく、 2 行の参照画素 4 で 1 つの F D 2 2 を共有している。実施例 1 と同じく、参照画素 4 は P D 2 0 を含まない。一方で、各行の参照画素 4 は出力制御線 7 に接続される。また、 2 n 行目に電圧値 V P D 1 が供給され、 2 n + 1 行目に電圧値 V P D 2 が供給される。なお、出力制御回路 8 により、参照画素 4 に供給する V P D 1 と V P D 2 は選択することができる。

**【 0 1 4 9 】**

本実施例における、受光画素 2 、 O B 画素 3 、及び、参照画素 4 の動作タイミングを図 1 5 に示す。

10

**【 0 1 5 0 】**

S E L は行選択トランジスタ 2 5 のゲートに入力される信号、 R E S はリセットトランジスタ 2 3 のゲートに入力される信号、 T X 1 は転送トランジスタ 2 1 - 1 のゲートに入力される信号を示している。また、 T X 2 は転送トランジスタ 2 1 - 2 のゲートに入力される信号をそれぞれ示している。

**【 0 1 5 1 】**

ゲートに入力される信号がハイレベルの時はトランジスタがオン、ゲートレベルがローレベルの時はトランジスタがオフする。

**【 0 1 5 2 】**

また、受光画素 2 の F D の電圧、 2 n 行目の参照画素 4 、及び、 2 n + 1 行目の参照画素 4 の F D の電圧を示している。 2 n 行目の参照画素 4 には電圧値 V P D 1 が、 2 n + 1 行目の参照画素 4 には電圧値 V P D 2 がそれぞれ供給されているとする。

20

**【 0 1 5 3 】**

まず、時刻 T 1 0 0 までの期間は、行選択トランジスタ 2 5 はオフとなっており、画素行は選択されていない。リセットトランジスタ 2 3 はオンとなっており、電源電圧 V D D と増幅トランジスタ 2 4 のゲートが接続され、 F D 2 2 の電圧がリセットされている。このとき、受光画素 2 、 O B 画素 3 、及び、参照画素 4 の F D 2 2 の電圧は電源電圧 V D D に対応した電圧となっている。

**【 0 1 5 4 】**

転送トランジスタ 2 1 - 1 および 2 1 - 2 はオフとなっており、 P D 2 0 - 1 および P D 2 0 - 2 と増幅トランジスタ 2 4 のゲートは電気的に切り離されている。

30

**【 0 1 5 5 】**

時刻 T 1 0 0 で、行選択トランジスタ 2 5 がオンとなり、所定の行が選択され、増幅トランジスタ 2 4 と垂直出力線 5 が接続される。期間 H 1 0 0 は 2 n 行目の選択期間を示している。

**【 0 1 5 6 】**

時刻 T 1 0 1 で、リセットトランジスタ 2 3 がオフとなり、電源電圧 V D D と増幅トランジスタ 2 4 のゲートとが電気的に切り離される。受光画素 2 、 O B 画素 3 、及び、参照画素 4 のそれぞれの F D 2 2 のリセットノイズに対応したノイズ信号が増幅トランジスタ 2 4 により、垂直出力線 5 に出力される。

40

**【 0 1 5 7 】**

時刻 T 1 0 2 で、転送トランジスタ 2 1 - 1 がオンする。これにより、 P D 2 0 - 1 と増幅トランジスタ 2 4 のゲートが電気的に接続される。よって、受光画素 2 および O B 画素 3 において、 P D 2 0 - 1 に蓄積された電荷が F D 2 2 に転送される。したがって、 F D 2 2 の電圧は、電源電圧 V D D から信号電圧 V s i g 变化する。受光画素 2 の増幅トランジスタ 2 4 は、信号電圧 V s i g に応じた信号レベルの画素信号を、垂直出力線 5 に出力する。

**【 0 1 5 8 】**

一方、 2 n 行目の参照画素 4 では、出力制御回路 8 により選択された電圧値 V P D 1 が F D 2 2 に転送される。これにより、 F D 2 2 の電圧は、電源電圧 V D D から電圧 V P D 1

50

に変化する。参照画素 4 の増幅トランジスタ 24 は、電圧値 VPD1 に応じた信号レベルの画素信号を垂直出力線 5 に出力する。

【0159】

時刻 T103 に、リセットトランジスタ 23 がオンする。これにより、FD22 が電源電圧 VDD によりリセットされる。

【0160】

時刻 T104 に、行選択トランジスタ 25 がオフする。これにより、2n 行目に含まれる受光画素 2、OB 画素 3、及び、参照画素 4 の読み出し動作が終了する。

【0161】

時刻 T105 に、行選択トランジスタ 25 がオンする。これにより、増幅トランジスタ 24 と垂直出力線 5 が再び電気的に接続される。期間 H101 は 2n + 1 行目の選択期間を示している。10

【0162】

時刻 T106 に、リセットトランジスタ 23 がオフとなり、電源電圧 VDD と増幅トランジスタ 24 のゲートが切り離される。受光画素 2、OB 画素 3、及び、参照画素 4 の FD は、電源電圧 VDD に応じた信号を、増幅トランジスタ 24 を介して垂直出力線 5 に出力する。

【0163】

時刻 T107 に、転送トランジスタ 21 - 2 がオンする。これにより、PD20 - 2 と増幅トランジスタ 24 のゲートが電気的に接続される。よって、受光画素 2 および OB 画素 3 において、PD20 - 2 に蓄積された電荷が FD22 に転送される。したがって、FD 22 の電圧は、電源電圧 VDD から信号電圧 Vsig に変化する。受光画素 2 の増幅トランジスタ 24 は、信号電圧 Vsig に応じた信号レベルの画素信号を、垂直出力線 5 に出力する。20

【0164】

一方、2n + 1 行目の参照画素 4 では、出力制御回路 8 により選択された電圧値 VPD2 が FD22 に転送される。これにより、FD22 の電圧は、電源電圧 VDD から電圧 VPD2 に変化する。参照画素 4 の増幅トランジスタ 24 は、電圧値 VPD2 に応じた信号レベルの画素信号を垂直出力線 5 に出力する。

【0165】

以降の動作は、上述した時刻 T103、T104 と同じである。30

【0166】

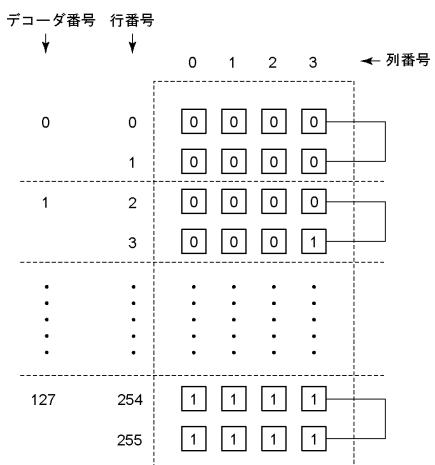

図 16 は、本実施例における、参照画素 4 より構成されたアドレス信号を示す。

【0167】

本実施例では、上述の通り、1つのアドレスデコーダ信号に対して、2行の画素行が制御される。

【0168】

1段のデコーダに対して、選択される2行に含まれる参照画素 4 によりアドレス信号を構成する。1つのアドレスデコーダ信号に対して、2行の画素行が選択されるため、デコーダ番号の値が1つ大きくなるにつれて、行番号は2ずつ大きくなる。40

【0169】

図 16 には、参照画素 4 を行方向に 4 画素、列方向に 256 画素配置している。1段のデコーダに対して、選択される2行に含まれる参照画素 4 によりアドレス信号を構成する場合、アドレス信号は8ビットのデジタル信号として表される。0行目および1行目のアドレス信号は「00000000」、1行目および2行目のアドレス信号は「00000001」を示す。このように、デコーダ信号単位で異なるアドレス信号を与えることにより、デコーダ信号単位での識別が可能となる。

【0170】

図 16 の例では、アドレス信号を8ビットにすることで、128段以上のデコーダを個別に識別することができる。実施例 1 に対して、参照画素 4 の数が同様でも、より多くの行

10

20

30

40

50

数をデコーダ単位で識別することができる。また、撮像領域1の読み出す行数に応じて、1行における参照画素4の配置数を変更することにより、128段以上のデコーダに対応する行数であっても、識別することが可能となる。

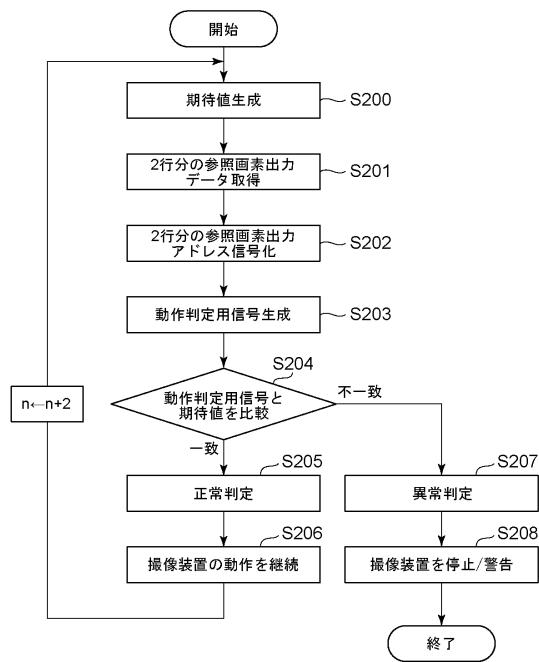

**【0171】**

本実施例における、撮像装置の動作の正常可否を判断する方法について説明する。

**【0172】**

図17は、本実施例のフローチャート図を示す。

**【0173】**

デコーダn段目の動作判定を例に、図17のフローチャートを説明する。

**【0174】**

ステップS200で、アドレス信号の期待値生成を行う。

10

**【0175】**

ステップS201で、n段目のデコーダ信号により選択された撮像装置1の $2^n$ 行目および $2^n + 1$ 行目に含まれる参照画素4の出力データを取得する。この時、参照画素4に電圧値VPD1が供給された場合の出力信号を「1」、電圧値VPD2が供給された場合の出力信号を「0」とする。

**【0176】**

ステップS202で、ステップS201で得られた参照画素4の出力信号をアドレス信号化する。アドレス信号化とは、ステップS201で出力信号が「1」または「0」となった2行分の参照画素4を並べ、1つの信号とすることを指す。

20

**【0177】**

ステップS203で、動作判定用信号が生成される。

**【0178】**

ステップS204で、ステップS203で生成した動作判定用信号とステップS200で生成した期待値を比較する。

**【0179】**

ステップS204の比較結果が一致した場合、ステップS205でデコーダn段目は正常であると判定される。そして、ステップS206で撮像装置の動作は継続し、デコーダn+1段目、つまり $2^n + 2$ 行目と $2^n + 3$ 行目の動作判定に進む。

**【0180】**

30

一方、ステップS204の比較結果が不一致の場合、ステップS207でデコーダn段目は異常判定される。そして、ステップS208で撮像装置の動作は停止する、または撮像装置が故障したことを示す警告を行う。この場合、デコーダn+1段目の動作判定には進まない。

**【0181】**

以上に説明した通り、本実施例では、アドレスデコーダが1段選択された場合に、撮像領域1が2行選択される。デコーダ1段により選択された2行に含まれる参照画素4は、他のデコーダとは異なる固有のアドレス信号を構成する。このアドレス信号を用いることで、デコーダ信号単位ごとに個別に識別し、デコーダ信号により選択された2行が正常に画素信号を出力しているかを判定することができる。結果として、デコーダ信号単位毎に動作判定を行い、異常判定された場合は撮像装置の動作を停止することで、異常判定までの時間を短縮することができる。

40

**【0182】**

(実施例3)

実施例3は、実施例1とアドレス信号の構成が異なる。それ以外は、実施例1と同様なので説明を省略する。

**【0183】**

図18は、本実施例における参照画素4より構成されたアドレス信号の例を示す。

**【0184】**

図18に示す本実施例の参照画素4は、行方向に12画素、列方向に16画素が配置され

50

ている。この場合、1行のアドレス信号は12ビットのデジタル信号として表される。また、1行のアドレス信号には、同じ信号値を出力する4ビットのデジタル信号が3組含まれる。例えば、1行目の0列目から3列目に表示される1組目のアドレス信号が「0001」であった場合、4列目から7列目に表示される2組目のアドレス信号は「0001」、8列目から11列目に表示される3組目のアドレス信号は「0001」と表示される。4ビットで表示されるアドレス信号を単位信号とすると、この場合、1行に「0001」の単位信号が3組並んだ構成となる。なお、各行に配置する単位信号は、3組に限定されない。

#### 【0185】

次に、参照画素4のアドレス信号出力を用いて、撮像装置の画素信号出力の正常可否を判断する方法について説明する。

10

#### 【0186】

図19は、撮像装置の動作の正常可否を判断するまでの流れを示したフロー チャート図である。

#### 【0187】

n行目の動作判定を例に説明する。

#### 【0188】

ステップS300で、アドレス信号の期待値生成を行う。

20

#### 【0189】

ステップS301で、n段目のデコーダ信号により選択された撮像装置1の1行に含まれる参照画素4の出力データを取得する。この時、参照画素4に電圧値VPD1が供給された場合の出力信号を「1」、電圧値VPD2が供給された場合の出力信号を「0」とする。

#### 【0190】

ステップS302で、ステップS301で得られた参照画素4の出力信号をアドレス信号化する。アドレス信号化することにより、3組のアドレス単位信号が生成される。

30

#### 【0191】

ステップS303で、3組の単位信号を比較する。3組の単位信号が一致した場合は、ステップS305で動作判定信号が生成される。動作判定信号とは、上述した単位信号を示す。一方、ステップS303で、参照画素4に不良があった場合などに、3組の単位信号が一致しなかった場合は、ステップS304で3組の単位信号の各ビットについて多数決をとり、各ビットにおいて多数派となった信号が各ビットの信号値となる。この場合、ステップS305で生成される動作判定用信号は、ステップS304の多数決で決まった各ビットの信号値により構成される単位信号となる。

30

#### 【0192】

ステップS306で、ステップS305で生成した動作判定用信号とステップS300で生成した期待値を比較する。ステップS306の比較結果が一致した場合、ステップS307でn行目は正常であると判定され、ステップS308で撮像装置の動作は継続し、n+1行目の動作判定に進む。一方、ステップS306の比較結果が不一致の場合、ステップS309でn行は異常判定される。そして、ステップS310で撮像装置の動作は停止する、または撮像装置が故障したことを示す警告を行う。この場合、n+1行目の動作判定には進まない。

40

#### 【0193】

以上に説明した通り、本実施例では、参照画素4に異常があった場合でも撮像装置の正常可否を判断することができる。この構成においても、実施例1と同様の効果が得られる。

#### 【0194】

##### (実施例4)

実施例4は、実施例1と垂直走査回路11の構成が異なる。それ以外は、実施例1と同様なので説明を省略する。

#### 【0195】

図20は、本実施例の撮像装置の構成を示す。垂直走査回路11に着目すると、タイミン

50

ゲジェネレータ 16 による制御信号により行選択信号を出力する部分は、シフトレジスタ回路 30 となっている。その他の撮像装置の構成は、実施例 1 と同じであるので説明は省略する。

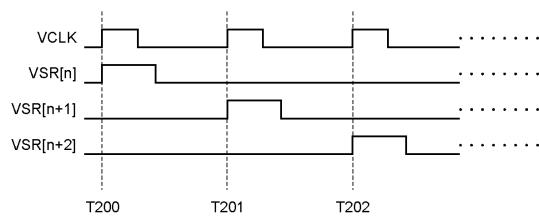

**【0196】**

図 21 は、タイミングジェネレータ 16 により制御信号がシフトレジスタ回路 30 に供給されてから、行選択信号が出力されるまでの駆動タイミングを示す。

**【0197】**

タイミングジェネレータ 16 より制御信号 VCLK がシフトレジスタ回路 30 に供給される。

**【0198】**

時刻 T200 で、VCLK パルスが入力されると、行選択信号 VSR[n] がハイレベルとなり、n 段目の行選択信号がシフトレジスタ回路 30 から出力される。

**【0199】**

時刻 T201 で、VCLK パルスが入力されると、行選択信号 VSR[n+1] がハイレベルとなり、n+1 段目の行選択信号がシフトレジスタ回路 30 から出力される。

**【0200】**

時刻 T202 で、VCLK パルスが入力されると、行選択信号 VSR[n+2] がハイレベルとなり、n+2 段目の行選択信号がシフトレジスタ回路 30 から出力される。つまり、VCLK パルスの入力に応じて、行選択信号が 1 段ずつ出力される。行選択信号 VSR[n] は、実施例 1 のデコーダ信号 DEC[n] に対応している。

**【0201】**

以上に説明した通り、本実施例のように、シフトレジスタ回路 30 により行選択パルスを供給する構成においても、実施例 1 と同様の効果が得られる。

**【0202】**

以上の説明では、各行のアドレス信号を例に挙げたが、各列のアドレス信号を用いて撮像装置の動作の判定を行ってもよい。この場合、明細書中の「行」を「列」に読み替えればよい。

**【0203】**

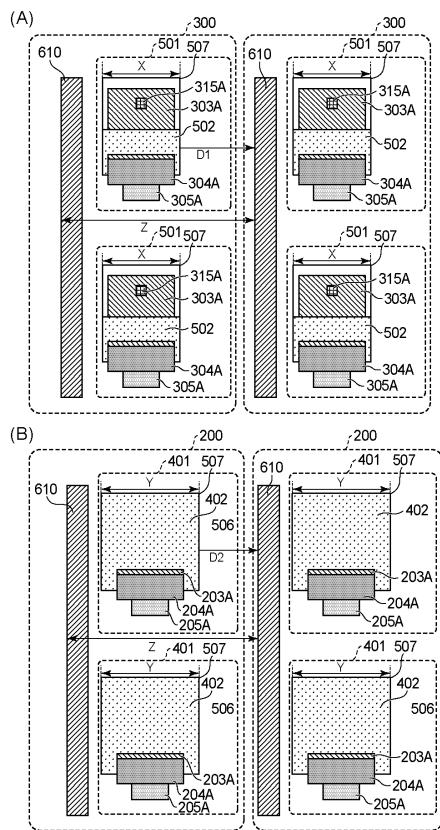

(実施例 5)

図 22 は、本実施形態の撮像装置の概略構成を示すブロック図である。図 23 は、本実施形態による撮像装置における画素の構成例を示す回路図である。図 24 は、本実施形態による撮像装置の駆動方法を示すタイミング図である。

**【0204】**

はじめに、本実施形態による撮像装置の構造について、図 22 及び図 23 を用いて説明する。

**【0205】**

本実施形態による撮像装置 100 は、図 22 に示すように、第 1 領域 120、第 2 領域 122、垂直走査回路 102、列回路 103、水平走査回路 104、出力回路 115、制御部 107、電圧供給部 125、電圧スイッチ 128 を含む。

**【0206】**

本実施形態の垂直走査回路 102 は、上述した実施例 1 ~ 4 のいずれかの垂直走査回路を適用することができる。

**【0207】**

第 1 領域 120 には、第 1 のグループの画素 105 と、第 2 のグループの画素 106 とが、複数の行及び複数の列に渡って配されている。第 1 領域 120 は、画像取得用の画素が配された、画像取得用画素領域である。画素 105 は、光電変換部を備えた画素であり、図 22 には白抜きのブロックで示している。画素 106 は、遮光された光電変換部を備えた画素であり、図 22 には斜線を付したブロックで示している。画素 106 は、黒レベルの基準となる基準信号を出力するための画素であり、典型的には第 1 領域 120 の周縁部に配される。なお、画素 106 は、必ずしも設ける必要はない。

10

20

30

40

50

**【 0 2 0 8 】**

第2領域122には、第3のグループの画素110と、第4のグループの画素111とが、複数の行及び複数の列に渡って配されている。第2領域122は、故障検出用の画素が配された、故障検出用画素領域である。画素110は、固定電圧端子V0の電位に応じた信号を出力する画素であり、図22には「V0」と記載されたブロックで示している。画素111は、固定電圧端子V1の電位に応じた信号を出力する画素であり、図22には「V1」と記載されたブロックで示している。

**【 0 2 0 9 】**

第1領域120と第2領域122とは行方向(図22において横方向)に隣接して配されており、第1領域120と第2領域122とが配された行は同じであるが列は異なっている。

10

**【 0 2 1 0 】**

第1領域120及び第2領域122の各行には、行方向に延在する画素制御線109が配されている。それぞれの行の画素制御線109は、対応する行に属する画素105, 106, 110, 111に共通の信号線をなしている。画素制御線109は、垂直走査回路102に接続されている。

**【 0 2 1 1 】**

第1領域120及び第2領域122の各列には、列方向に延在する垂直出力線108が配されている。第1領域120のそれぞれの列の垂直出力線108は、対応する列に属する画素105, 106に共通の信号線をなしている。第2領域122のそれぞれの列の垂直出力線108は、対応する列に属する画素110, 111に共通の信号線をなしている。垂直出力線108は、列回路103に接続されている。

20

**【 0 2 1 2 】**

垂直走査回路102は、画素制御線109を介して画素105, 106, 110, 111を駆動するための所定の制御信号を供給する。垂直走査回路102には、シフトレジスタやアドレスデコーダなどの論理回路が用い得る。図22には各行の画素制御線109を1本の信号線で示しているが、実際には複数の制御信号線を含む。垂直走査回路102により選択された行の画素105, 106, 110, 111は、それぞれが対応する垂直出力線108に同時に信号を出力するように動作する。

30

**【 0 2 1 3 】**

列回路103は、垂直出力線108に出力された画素信号を増幅し、リセット時の信号と光電変換時の信号とに基づく相關二重サンプリング処理を行う。故障検出用の画素110, 111から出力された画素信号に対しては、リセット時の信号と固定電圧入力時の信号とに基づく相關二重サンプリング処理を、画像取得用の画素105, 106と同様に行う。

**【 0 2 1 4 】**

水平走査回路104は、列回路103において処理された画素信号を列毎に順次、出力回路115に転送するための制御信号を、列回路103に供給する。

**【 0 2 1 5 】**

出力回路115は、バッファアンプ、差動増幅器などから構成され、列回路103から転送される画素信号を撮像装置100の外部の信号処理部(図示せず)に出力する。なお、列回路103や出力回路115にA/D変換部を設け、デジタルの画像信号を外部に出力するようにしてもよい。

40

**【 0 2 1 6 】**

電圧供給部125は、所定の固定電圧端子V0, V1の電位を供給する電源回路である。電圧スイッチ128は、スイッチSW0, SW1を含む。スイッチSW0は、電圧供給部125の固定電圧端子V0と電圧供給線112との間に設けられており、制御部107から制御信号線114を介して供給される制御信号(VPD\_ON)に応じて、電圧供給線112に固定電圧端子V0の電位を供給する。スイッチSW1は、電圧供給部125の固定電圧端子V1と電圧供給線113との間に設けられており、制御部107から制御信号線114を介して供給される制御信号(VPD\_ON)に応じて、電圧供給線113に固

50

定電圧端子 V 1 の電位を供給する。

**【 0 2 1 7 】**

電圧供給線 1 1 2 , 1 1 3 は、第 2 領域 1 2 2 に配された画素 1 1 0 , 1 1 1 に電圧供給部 1 2 5 からの固定電圧端子 V 0 , V 1 の電位を供給するための配線である。第 2 領域 1 2 2 内の複数の画素 1 1 0 , 1 1 1 において、例えば図示するように電圧供給線 1 1 2 , 1 1 3 を共通化することで、省回路化を図ることが可能である。

**【 0 2 1 8 】**

第 2 領域 1 2 2 には、固定電圧端子 V 0 の電位が供給される画素 1 1 0 と、固定電圧端子 V 0 の電位とは異なる固定電圧端子 V 1 の電位が供給される画素 1 1 1 とが、特定のパターンに従って行列状に配置されている。

10

**【 0 2 1 9 】**

第 2 領域 1 2 2 が 3 列で構成される場合を例にして説明すると、例えば、ある行（例えば、図 2 2 において一番下の行）には、各列に画素 1 1 0 , 1 1 0 , 1 1 0 が配されている。また、別の行（例えば、図 2 2 において下から二番目の行）には、各列に画素 1 1 1 , 1 1 0 , 1 1 1 が配されている。すなわち、垂直走査の行によって、画素 1 1 0 , 1 1 1 に印加される固定電圧のパターンが変わっている。

**【 0 2 2 0 】**

同じ行に属する故障検出用の画素 1 1 0 と画像取得用の画素 1 0 5 とは、画素制御線 1 0 9 を共有している。したがって、第 2 領域 1 2 2 における出力のパターンを期待値と照合することにより、垂直走査回路 1 0 2 が正常に動作しているのか、故障して想定と異なる行を走査しているのか、を検知することが可能となる。

20

**【 0 2 2 1 】**

なお、本実施形態では第 2 領域 1 2 2 を 3 列で構成した場合を例示しているが、第 2 領域 1 2 2 を構成する列の数は 3 列に限定されるものではない。

**【 0 2 2 2 】**

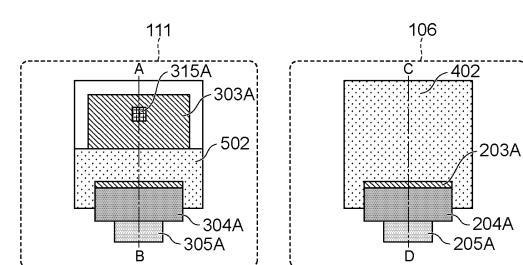

図 2 3 は、第 1 領域 1 2 0 及び第 2 領域 1 2 2 を構成する画素 1 0 5 , 1 0 6 , 1 1 0 , 1 1 1 の構成例を示す回路図である。図 2 3 には、第 1 領域 1 2 0 のうちの 1 列から第 1 行に配された画素 1 0 5 と第 2 行の配された画素 1 0 6 とを、第 2 領域 1 2 2 のうちの 1 列から第 1 行に配された画素 1 1 1 と第 m 行の配された画素 1 1 0 とを抜き出して記載している。

30

**【 0 2 2 3 】**

第 1 領域 1 2 0 に配された画素 1 0 5 の各々は、光電変換部 P D 、転送トランジスタ M 1 を含む。画素セル 2 0 0 は、2 つの画素 1 0 5 を有する。画素セル 2 0 0 は、リセットトランジスタ M 2 、増幅トランジスタ M 3 、選択トランジスタ M 4 を含む。光電変換部 P D は、例えばフォトダイオードである。光電変換部 P D のフォトダイオードは、アノードが基準電圧端子 G N D に接続され、カソードが転送トランジスタ M 1 のソースに接続されている。転送トランジスタ M 1 のドレインは、リセットトランジスタ M 2 のソース及び増幅トランジスタ M 3 のゲートに接続されている。転送トランジスタ M 1 のドレイン、リセットトランジスタ M 2 のソース及び増幅トランジスタ M 5 のゲートの接続ノードは、フローティングディフュージョン F D を構成する。リセットトランジスタ M 2 のドレイン及び増幅トランジスタ M 3 のドレインは、電源電圧端子 V D D に接続されている。増幅トランジスタ M 3 のソースは、選択トランジスタ M 4 のドレインに接続されている。選択トランジスタ M 4 のソースは、垂直出力線 1 0 8 に接続されている。1 行目の画素 1 0 5 と 2 行目の画素 1 0 5 は、1 つの増幅トランジスタ M 3 のゲートの入力ノードであるフローティングディフュージョン F D を共有している。

40

**【 0 2 2 4 】**

第 2 領域 1 2 2 に配された画素 1 1 0 、画素 1 1 1 は、遮光されたフォトダイオード P D 、転送トランジスタ M 1 を含む。画素セル 3 0 0 は、画素 1 1 0 、画素 1 1 1 を有する。さらに画素セル 3 0 0 は、リセットトランジスタ M 2 、増幅トランジスタ M 3 、選択トランジスタ M 4 を含む。画素 1 1 1 の転送トランジスタ M 1 のソースは、電圧供給線 1 1 2

50

に接続されている。以下、画素 111について説明する。転送トランジスタ M1 のドレインは、リセットトランジスタ M2 のソース及び増幅トランジスタ M3 のゲートに接続されている。転送トランジスタ M1 のドレイン、リセットトランジスタ M2 のソース及び増幅トランジスタ M5 のゲートの接続ノードは、フローティングディフィュージョン FD を構成する。リセットトランジスタ M2 のドレイン及び増幅トランジスタ M3 のドレインは、電源電圧端子 VDD に接続されている。増幅トランジスタ M3 のソースは、選択トランジスタ M4 のドレインに接続されている。選択トランジスタ M4 のソースは、垂直出力線 108 に接続されている。1 行目の画素 111 と 2 行目の画素 110 は、1 つの増幅トランジスタ M3 のゲートの入力ノードであるフローティングディフィュージョン FD を共有している。

10

#### 【0225】

第 2 領域 122 に配された画素 110 は、転送トランジスタ M1 のソースが電圧供給線 112 ではなく電圧供給線 113 に接続されている。

#### 【0226】

図 23 の画素構成の場合、各行に配された画素制御線 109 は、信号線 TX, RES, SEL を含む。信号線 TX は、対応する行に属する画素の転送トランジスタ M1 のゲートにそれぞれ接続されている。信号線 RES は、対応する行に属する画素のリセットトランジスタ M2 のゲートにそれぞれ接続されている。信号線 SEL は、対応する行に属する画素の選択トランジスタ M4 のゲートにそれぞれ接続されている。なお、図 23 には、信号線の参照符号に行番号を付記している（例えば、SEL(1), RES(1)）。

20

#### 【0227】

信号線 TX には、垂直走査回路 102 から、転送トランジスタ M1 を制御するための駆動パルスである制御信号 PTX が出力される。信号線 RES には、垂直走査回路 102 から、リセットトランジスタ M2 を制御するための駆動パルスである制御信号 PRES が出力される。信号線 SEL には、垂直走査回路 102 から、選択トランジスタ M4 を制御するための駆動パルスである制御信号 PSEL が出力される。各トランジスタが N 型トランジスタで構成される場合、垂直走査回路 102 からハイレベルの制御信号が供給されると対応するトランジスタがオンとなり、垂直走査回路 102 からローレベルの制御信号が供給されると対応するトランジスタがオフとなる。

30

#### 【0228】

画像取得用の画素 105 が備える光電変換部 PD は、入射光をその光量に応じた量の電荷に変換（光電変換）するとともに、生じた電荷を蓄積する。画素 105 の転送トランジスタ M1 は、オンすることにより光電変換部 PD の電荷をフローティングディフィュージョン FD に転送する。フローティングディフィュージョン FD は、その容量による電荷電圧変換によって、光電変換部 PD から転送された電荷の量に応じた電圧となる。画素 110, 111 の転送トランジスタ M1 は、オンすることにより電圧供給線 112, 113 から供給された電圧をフローティングディフィュージョン FD に印加する。増幅トランジスタ M3 は、ドレインに電源電圧が供給され、ソースに選択トランジスタ M4 を介して図示しない電流源からバイアス電流が供給される構成となっており、ゲートを入力ノードとする増幅部（ソースフォロワ回路）を構成する。これにより増幅トランジスタ M3 は、フローティングディフィュージョン FD の電圧に基づく信号を、選択トランジスタ M4 を介して垂直出力線 108 に出力する。リセットトランジスタ M2 は、オンすることによりフローティングディフィュージョン FD を電源電圧 VDD に応じた電圧にリセットする。

40

#### 【0229】

同一行の画素に対しては、第 1 領域 120 と第 2 領域 122 とに、共通の制御信号 PTX, PRES, PSEL が垂直走査回路 102 から供給される。例えば、第 m 行の画素 105, 106, 110, 111 の転送トランジスタ M1、リセットトランジスタ M2、選択トランジスタ M4 には、制御信号 PTX(m)、PSEL(m)、PRES(m) が、それぞれ供給される。

#### 【0230】

50

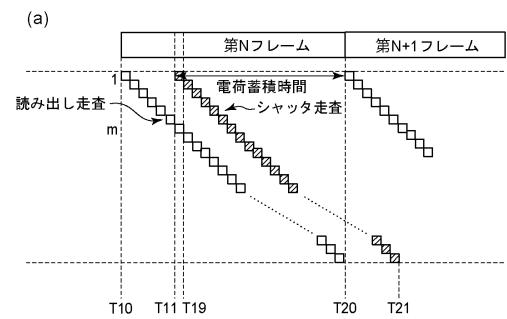

次に、本実施形態による撮像装置の駆動方法について、図24を用いて説明する。図24(a)は、1フレーム期間における読み出し走査とシャッタ走査との関係を示すタイミング図である。図24(b)は、読み出し走査行とシャッタ走査行の走査における画素の動作の詳細を示すタイミング図である。

#### 【0231】

図24(a)には、時刻T10に開始し時刻T20に終了する第Nフレームと、時刻T20から開始する第N+1フレームの動作の概略を示している。各フレームの動作には、画素105, 106, 110, 111からの読み出し動作を行順次で行う読み出し走査と、画素105, 106の光電変換部PDへの電荷蓄積を行順次で開始するシャッタ走査とが含まれる。

10

#### 【0232】

第Nフレームの読み出し走査は、時刻T10に開始され、時刻T20に終了するものとする。時刻T10が1行目の画素からの読み出し動作の開始時刻であり、時刻T20が最終行の画素からの読み出し動作の終了時刻である。

#### 【0233】

第Nフレームのシャッタ走査は、時刻T11に開始され、時刻T21に終了するものとする。時刻T11が1行目の画素におけるシャッタ動作の開始時刻であり、時刻T21が最終行の画素におけるシャッタ動作の終了時刻である。シャッタ動作の開始時刻から次の読み出し動作の開始時刻までの期間が、電荷蓄積時間となる。例えば1行目に着目すると、時刻T11から時刻T20までの期間が電荷蓄積時間となる。シャッタ動作の開始タイミングを制御することで、電荷蓄積時間を制御することが可能となる。

20

#### 【0234】

ここで、1行目の画素のシャッタ動作が開始する時刻T11において、m行目の画素からの読み出し動作が開始するものとする。1行目の画素のシャッタ動作及びm行目の画素106からの読み出し動作は、時刻T19に終了するものとする。

#### 【0235】

図24(b)は、時刻T11から時刻T19における画素の動作の詳細を示したものである。なお、シャッタ動作と読み出し動作とにおける画素の動作は同じである。

#### 【0236】

時刻T11において、読み出し走査行(第m行)の制御信号PSEL(m)がハイレベルとなり、読み出し走査行の画素の選択トランジスタM4がオンになる。この動作により、読み出し走査行の画素から垂直出力線108への信号の読み出しが可能な状態となる。

30

#### 【0237】

次いで、時刻T11から時刻T12の間に、シャッタ走査行(第1行)の制御信号PRE(1)と読み出し走査行の制御信号PRE(m)がハイレベルとなる。この動作により、シャッタ走査行及び読み出し走査行の画素のリセットトランジスタM2がオンになり、フローティングディフュージョンFDがリセットされる。

#### 【0238】

次いで、時刻T12において、読み出し走査行の制御信号PRE(m)がローレベルとなり、読み出し走査行の画素のリセットトランジスタM2がオフになる。この動作により、フローティングディフュージョンFDに存在する電荷が電源電圧端子VDDに排出され、フローティングディフュージョンFDの電圧がソースフォロワ動作によって増幅され、垂直出力線108に読み出される。

40

#### 【0239】

次いで、時刻T13において、制御信号VPD\_ONがハイレベルとなることによって電圧スイッチ128のスイッチSW0, SW1がオンになる。よって、電圧供給部125から電圧供給線112, 113にそれぞれ固定電圧端子V0, V1のそれぞれの電位が供給される。

#### 【0240】

次いで、時刻T13から時刻T14の間に読み出し走査行の制御信号PTX(m)がハイ

50

レベルとなり、読み出し走査行の画素の転送トランジスタM 1がオンになる。この動作により、読み出し走査行の画素105, 106では、光電変換部PDに蓄積されていた電荷がフローティングディフュージョンFDへと転送される。また、読み出し走査行の画素110, 111では、電圧供給部125から供給される固定電圧端子V0, V1の電位がフローティングディフュージョンFDに書き込まれる。

#### 【0241】

次いで、時刻T14において、読み出し走査行の制御信号PTX(m)がローレベルとなり、読み出し走査行の画素の転送トランジスタM 1がオフになる。この動作により、読み出し走査行のフローティングディフュージョンFDの電圧が確定し、確定した電圧がソースフォロワ動作によって増幅され、垂直出力線108に読み出される。

10

#### 【0242】

次いで、時刻T15において、制御信号VPD\_ONがローレベルとなることによって電圧スイッチ128のスイッチSW0, SW1がオフとなり、電圧供給部125から電圧供給線112, 113への固定電圧端子V0, V1の電位の供給が遮断される。

#### 【0243】

次いで、時刻T16において、シャッタ走査行の制御信号PTX(1)がハイレベルとなり、シャッタ走査行の画素の転送トランジスタM 1がオンになる。この際、シャッタ走査行の画素のリセットトランジスタM 2もオンのため、光電変換部PDの電荷が転送トランジスタM 1及びリセットトランジスタM 2を介して電源電圧端子VDDに排出される。

20

#### 【0244】

次いで、時刻T17において、シャッタ走査行の制御信号PTX(1)がローレベルとなり、シャッタ走査行の画素の転送トランジスタM 1がオフになる。また、時刻T18において、シャッタ走査行の制御信号PRES(1)がローレベルとなり、シャッタ走査行の画素のリセットトランジスタM 2がオフになる。この動作により、シャッタ走査行のシャッタ動作が終了する。

#### 【0245】

次いで、時刻T19において、読み出し走査行の制御信号PSEL(m)がローレベルとなり、読み出し走査行の画素の選択トランジスタM 4がオフになる。この動作により、読み出し走査行の画素の選択が解除され、読み出し走査行の読み出し動作が終了する。

30

#### 【0246】

本実施形態では、上述のように、シャッタ走査行の転送トランジスタM 1をオンにしている期間に、電圧スイッチ128のスイッチSW0, SW1をオフ（制御信号VPD\_ONをローレベル）にしている。この理由について以下に説明する。

#### 【0247】

シャッタ動作によって第1領域120の画素105, 106の光電変換部PDの電荷を完全に除去するためには、シャッタ走査行のリセットトランジスタM 2と転送トランジスタM 1とを同時にオンすることが望ましい。特に、光電変換部PDの飽和電荷量がフローティングディフュージョンFDの飽和電荷量を上回る場合は、リセットトランジスタM 2と転送トランジスタM 1とを同時にオンすることが必須である。

40

#### 【0248】

しかしながら、その状態で、故障検出用画素領域である第2領域122の画素110, 111に電圧供給部125からの電圧供給がなされたままであると、固定電圧端子V1, V0と電源電圧端子VDDとが短絡する。典型的には固定電圧端子V1の電位が約1.6V、電源電圧VDDが3.3Vであるため、短絡電流が流れることによって第2領域122の画素110, 111の電位が正しく読めなくなる等の悪影響が発生する。

#### 【0249】

そこで、本実施形態では、電圧供給部125と第2領域122の画素110, 111との間に電圧スイッチ128を設ける構成としている。そして、シャッタ走査行の転送トランジスタM 1をオンにするときには、電圧スイッチ128のスイッチSW0, SW1がオフになるように駆動する。

50

**【 0 2 5 0 】**

これにより、シャッタ走査時に固定電圧端子 V 0 , V 1 と電源電圧端子 V D D とが短絡することを回避し、故障検出の検出精度を高めることが可能となる。すなわち、シャッタ走査時の電圧端子間の短絡を回避することで、撮像と故障検出とをリアルタイムで行いつつ、故障検出の検出精度を高めるという効果が得られる。

**【 0 2 5 1 】**

なお、本実施例では、シャッタ走査行の転送トランジスタ M 1 をオンにするタイミングが読み出し走査行の転送トランジスタ M 1 をオンにするタイミングよりも後とした。本実施例は、必ずしもこの動作に限定されるものではない。すなわち、シャッタ走査行の転送トランジスタ M 1 をオンにするタイミングは、読み出し走査行の転送トランジスタ M 1 をオンにするタイミングよりも前であってもよい。10

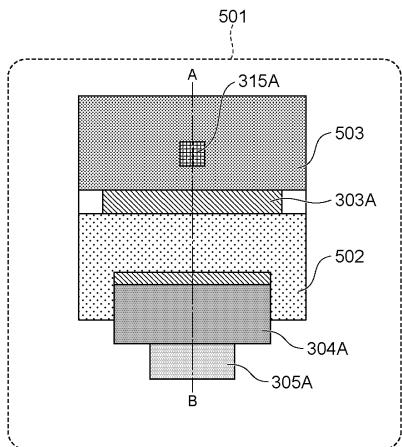

**【 0 2 5 2 】**

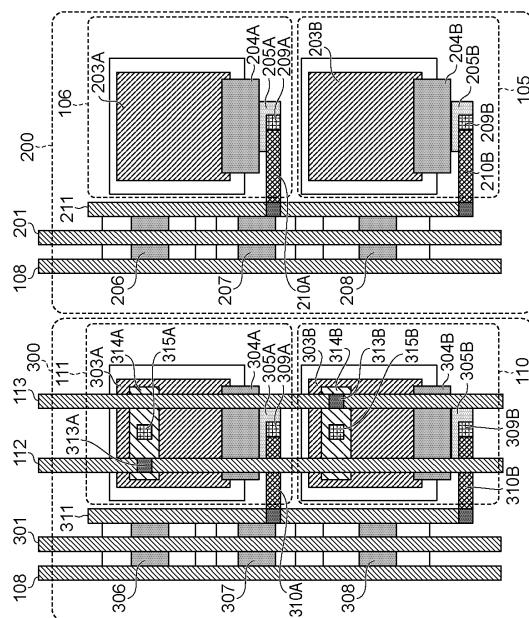

## &lt;画素の上面図&gt;

図 25 は、画素 105、110、111 の上面図である。図 23 で示した部材と同じ機能を有する部材については、図 23 で付した符号と同じ符号が図 25 においても付されている。

**【 0 2 5 3 】**

画素電源配線 201 は、画像取得用の画素に電源電圧 V D D を伝送する配線である。画素セル 200 は、光電変換部 P D の一部である、半導体領域 203A、203B を有する。半導体領域 203A、203B は、光電変換によって生じた電荷を蓄積する電荷蓄積部である。ここでは、半導体領域 203A、203B の導電型は N 型であるとする。また、半導体領域 203A、203B が蓄積する電荷が電子であるとする。20

**【 0 2 5 4 】**

さらに画素セル 200 は、転送トランジスタ M 1 のゲート 204A、204B、フローティングディフュージョン（以下、F D と表す。）の一部である浮遊拡散領域 205A、205B を有する。さらに画素セル 200 は、選択トランジスタ M 4 のゲート 206、増幅トランジスタ M 3 のゲート 207、リセットトランジスタ M 2 のゲート 208 を有する。さらに画素セル 200 は、F D 接続コンタクト（以下、コンタクトを C N T と表す） 209A、209B、F D 接続配線 A 210A、210B、F D 接続配線 211 を含む。以下、リセットトランジスタのゲートをリセットゲート、転送トランジスタのゲートを転送ゲート、増幅トランジスタのゲートを増幅ゲート、選択トランジスタのゲートを選択ゲートと表す。30

**【 0 2 5 5 】**

半導体領域 203A は転送ゲート 204A を介して浮遊拡散領域 205A に接続されている。半導体領域 203A に蓄積された電荷は、転送ゲート 204A を介して浮遊拡散領域 205A へ転送される。浮遊拡散領域 205A は F D 接続 C N T 209A と F D 接続配線 A 210A、F D 接続配線 211 を介して増幅ゲート 207 に接続される。

**【 0 2 5 6 】**

半導体領域 203B は、転送ゲート 204B を介して浮遊拡散領域 205B へ接続されている。半導体領域 203B に蓄積された電荷は、転送ゲート 204B を介して浮遊拡散領域 205B へ転送される。浮遊拡散領域 205B は F D 接続 C N T 209B と F D 接続配線 A 210B、F D 接続配線 211 を介して増幅ゲート 207 へ接続される。40

**【 0 2 5 7 】**

浮遊拡散領域 205A は F D 接続 C N T 209A と F D 接続配線 A 210A と F D 接続配線 211 を介してリセットトランジスタ M 2 に接続される。浮遊拡散領域 205B は F D 接続 C N T 209B と F D 接続配線 A 210B と F D 接続配線 211 を介してリセットトランジスタ M 2 に接続される。

**【 0 2 5 8 】**

画素電源配線 301 は、故障検出用の画素に電源電圧 V D D を伝送する配線である。

**【 0 2 5 9 】**

故障検出用の画素セル300は、遮光された光電変換部PDの一部である半導体領域303A、303Bを有する。画素セル300は、転送ゲート304A、304B、浮遊拡散領域305A、305B、選択ゲート306、増幅ゲート307、リセットゲート308を有する。

#### 【0260】

さらに画素セル300は、FD接続CNT309A、309B、FD接続配線A310A、310B、FD接続配線311、電圧供給線112、113を有する。さらに画素セル300は、故障検出用VIA313A、313B、故障検出用配線C314A、314B、故障検出用CNT315A、315Bを有する。

#### 【0261】

電圧供給線112と電圧供給線113は、画素セル300の光電変換部PDの上部に配されている。換言すれば、平面視において、電圧供給線112と光電変換部PDとが重なっており、電圧供給線113と光電変換部PDとが重なっている。

#### 【0262】

電圧供給線112は故障検出用VIA313Aを介して故障検出用配線C314Aに接続される。更に、故障検出用配線C314Aは故障検出用CNT315Aを介して半導体領域303Aに接続される。

#### 【0263】

半導体領域303Aに電圧供給線112より印加された電位が、転送トランジスタM2を介して浮遊拡散領域305Aへ出力される。

#### 【0264】

電圧供給線113は故障検出用VIA313Bを介して故障検出用配線C314Bに接続される。更に、故障検出用配線C314Bは故障検出用CNT315Bを介して半導体領域303Bに接続される。

#### 【0265】

半導体領域303Bに電圧供給線113より印加された電位が、転送トランジスタM2を介して浮遊拡散領域305Bへ出力される。

#### 【0266】

増幅トランジスタM3は、増幅ゲート307の電位に応じた信号を、選択トランジスタM4を介して垂直出力線108に出力する。

#### 【0267】

浮遊拡散領域305AはFD接続CNT309AとFD接続配線A310AとFD接続配線311を介してリセットトランジスタM2に接続される。浮遊拡散領域305BはFD接続CNT309BとFD接続配線A310BとFD接続配線311を介してリセットトランジスタM2に接続される。

#### 【0268】

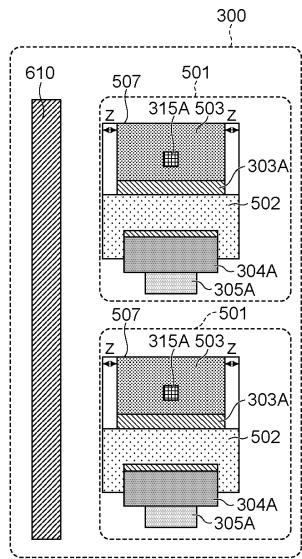

故障検出用の画素セル300の出力は、電圧供給線112もしくは電圧供給線113の電位に応じた信号レベルとなる。

#### 【0269】

<光電変換部の上面図、断面図>

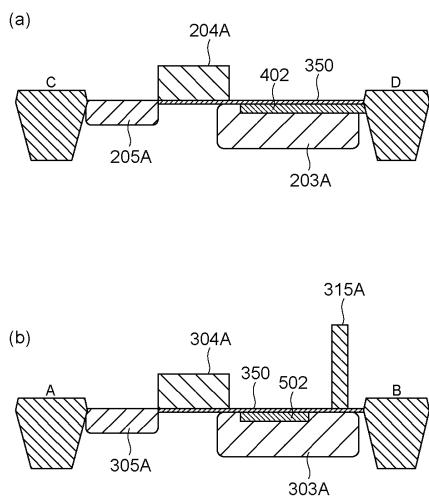

図25で説明した画素の上面について、さらに光電変換部を中心に、図26を用いて説明する。

#### 【0270】

図26は、画像取得用の画素106と、故障検出用の画素111の光電変換部PDと、転送トランジスタM2とを示した上面図である。図25で示した部材と同じ機能を有する部材については、図25で付された符号と同じ符号が図26でも付されている。

#### 【0271】

まず、画像取得用の画素106について説明する。平面視において、電荷を蓄積する半導体領域203Aは、P型の半導体領域402と重なっている。図27を用いて後述するが、半導体領域402は、半導体領域203の表面を保護する表面保護層として機能する。

10

20

30

40

50

以降、半導体領域 402 を表面保護層として表記することができる。

#### 【0272】

次に、故障検出用の画素 111 について説明する。平面視において、半導体領域 303A において故障検出用 CNT315A が接続された部分と、転送ゲート 304A との間に、P 型の半導体領域 502 が設けられている。

#### 【0273】

図 27(a) は、図 26 において、C-D として示した線が通過する位置における画素の断面図である。図 27(b) は、図 26 において、A-B として示した線が通過する位置における画素の断面図である。

#### 【0274】

まず、図 27(a) に示した、画像取得用の画素 106(C-D の線に対応する断面)について説明する。電荷を蓄積する半導体領域 203A は、P 型の半導体領域 402 の下部に形成されている。これにより、半導体領域 402 は、半導体領域 203 の表面を保護する表面保護層として機能する。半導体領域 402 は、半導体基板の正面 350 と、半導体領域 203A との間に形成されている。

10

#### 【0275】

次に図 27(b) に示した、故障検出用の画素 111(A-B の線に対応する断面)について説明する。電荷を蓄積する半導体領域 303A の一部の領域に、故障検出用 CNT315A が接続されている。この故障検出用 CNT315A の下部には、半導体領域 502 は形成されていない。また、半導体領域 303A において故障検出用 CNT315A が接続された部分と、転送ゲート 304A との間には、半導体領域 502 が設けられている。また、半導体領域 502 と半導体領域 303A が平面視において重なる部分については、半導体領域 502 の下部に半導体領域 303A が設けられている。半導体領域 502 は、半導体基板の正面 350 と、半導体領域 303A との間に形成されている。

20

#### 【0276】

##### <半導体領域 502 による効果>

半導体領域 303A の導電型が N 型であるとすると、半導体領域 502 の導電型は P 型である。このため、半導体領域 502 は半導体領域 303A に比べて低い電位となっている。つまり、半導体領域 502 の電位は、転送ゲート 304A のオフ時の電位と、半導体領域 303A の電位との間の電位となっている。半導体領域 502 が形成されていない場合には、転送ゲート 304A には、転送ゲート 304 と半導体領域 303A との間の電位差に対応する電界が印加されている。一方、本実施例では半導体領域 502 を備えることにより、転送ゲート 304 には、転送ゲート 304 と半導体領域 502 との間の電位差に対応する電界に緩和される。これにより、故障検出用の画素 111 の転送トランジスタ M2 の故障を生じにくくさせることができる。つまり、本実施例の画素構成は、画素 111 の故障を生じにくくすることができる。また、本実施例の撮像装置は、製造不良を生じにくくさせることができる。これにより、本実施例の撮像装置は、撮像装置の製造の歩留りを向上させることができる効果も得られる。

30

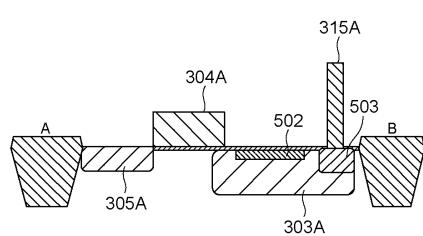

#### 【0277】

##### (実施例 6)

本実施例の撮像装置について、実施例 5 と異なる点を中心に説明する。

40

#### 【0278】

本実施例の撮像装置は、半導体領域 303A の内部に設けられ、半導体領域 303A と同じ導電型であって、半導体領域 303A よりも不純物濃度が高い半導体領域に故障検出用 CNT315A が接続されている。

#### 【0279】

図 28 は、本実施例の故障検出用の画素 501 の光電変換部と転送トランジスタの上面図である。図 25 で示した部材と同じ機能を有する部材には、図 25 で付された符号と同じ符号が図 26 においても付されている。

#### 【0280】

50

平面視において、半導体領域 303A が半導体領域 502 と重ならない部分に、半導体領域 503 が形成されている。半導体領域 503 は、半導体領域 303A と同じ導電型であって、半導体領域 303A よりも不純物濃度が高い領域である。平面視において、半導体領域 503 と、半導体領域 502 との間には間隙が設けられている。

【0281】

図29は、図28に示したA-Bの線の断面図である。

【0282】

半導体領域 503 は、半導体領域 303A の内部に形成されている。半導体領域 503 の底部は、半導体領域 502 よりも深い位置にある。

【0283】

本実施例の撮像装置は、半導体領域 503 を備えることにより、故障検出用 CNT315A と半導体領域 303A との間の電気抵抗を低減することができる。これにより、故障検出における検出精度を向上させることができる。

10

【0284】

図30は、本実施例の撮像装置の製造方法を示している。図30のA、Bは図28のA、Bと対応している。また、図30のC、Dは、図26のC、Dと対応している。図30(e)は、本実施例の撮像装置の構成を示している。P型の半導体領域 900 が、図1に示した第1領域 120、第2領域 122 に渡って形成されている。また、P型の半導体領域 900 よりも高い不純物濃度を有するP型の半導体領域 902 が形成されている。半導体領域 902 には、コンタクト 903 が接続されている。半導体領域 900 には、半導体領域 902 を介してコンタクト 903 から電位が与えられる。

20

【0285】

図30(a)では、素子分離部 901 が形成されている。素子分離部 901 は、STI(Shallow Trench Isolation)法、LOCOS(LOCal Oxidation of Silicon)法などを用いて形成することができる。また、半導体領域 303A は、イオン注入によって形成される。また、転送ゲート 304A は PVD 法によって形成される。

【0286】

図30(b)は、半導体領域 205A、半導体領域 305A、半導体領域 503 を形成する工程を示している。半導体領域 205A、半導体領域 305A、半導体領域 503 が形成される領域以外の領域は、レジストによってマスクされている。このマスクが為された状態において、ヒ素等のN型半導体領域を形成するためのドーパントを、半導体領域 205A、半導体領域 305A、半導体領域 503 となる領域にイオン注入する。これにより、N型の半導体領域 205A、305A、503 が形成される。つまり、半導体領域 503 を形成する工程は、半導体領域 205A、305A を形成する工程と並行して行われる。これにより、半導体領域 503 を形成するための工程を別途設ける必要が無い。よって、半導体露光装置のフォトマスクあるいはレチクルの枚数の削減によるコスト低減と、工程数の削減によるスループット向上の効果が得られる。

30

【0287】

図30(c)は、半導体領域 402、半導体領域 502 を形成する工程を示している。半導体領域 203A の上部にはレジストによるマスクが形成されていない一方、半導体領域 303A の一部の上部には、レジストによるマスクが形成されている。さらに言えば、半導体領域 503 は、レジストによってマスクされている。このレジストによるマスクが為された状態で、ホウ素等のP型半導体領域を形成するためのドーパントを、半導体領域 402、502 が形成される領域にイオン注入する。このイオン注入は、半導体基板の法線に対して、イオン注入の方向が角度を為す、いわゆる斜めイオン注入によって行われる。斜めイオン注入により、半導体基板において転送ゲート 304A の射影部となる部分ができる。これにより、射影部へのイオン注入は抑制される。このようにして、領域イオン注入の角度によって生じる転送ゲート 304A の射影部と、レジストによるマスクとによって規定される領域に、半導体領域 402、502 が形成される。

40

50

**【0288】**

図30(d)は、半導体領域902を形成する工程を示している。半導体領域902となる領域の上部以外の領域にはレジストによるマスクが形成されている。このマスクが為された状態で、ホウ素等のP型半導体領域を形成するためのドーパントを、半導体領域902が形成される領域に注入する。これにより、P型の半導体領域902が形成される。

**【0289】**

その後、層間絶縁膜を半導体基板の上部に形成する。そして、FD接続CNT209A、309A、315A、903が形成される領域をエッチングすることによって開口を形成する。この開口に、タンゲステン等の金属材料を注入することにより、FD接続CNT209A、309A、315A、903が形成される。つまり、故障検出用CNT315Aを形成する工程は、FD接続CNT209A、309A、903を形成する工程と並行して行われる。これにより、故障検出用CNT315Aを形成するための工程を別途設ける必要が無い。よって、半導体露光装置のフォトマスクあるいはレチクルの枚数の削減によるコスト低減と、工程数の削減によるスループット向上の効果が得られる。

10

**【0290】**

このようにして、本実施例の撮像装置の故障検出用の画素110、111と、画像取得用の画素105、106を形成することができる。

**【0291】****(実施例7)**

本実施例の撮像装置について、実施例5と異なる点を中心に説明する。

20

**【0292】**

本実施例の撮像装置は、故障検出用の画素の光電変換部が設けられた活性領域の幅を、画像取得用の画素の光電変換部が設けられた活性領域の幅よりも小さくする。

**【0293】**

図31(A)は、本実施例の故障検出用の画素501の光電変換部PD、転送トランジスタM2と、増幅トランジスタおよび選択トランジスタが設けられた活性領域610を示した上面図である。

**【0294】**

光電変換部PDは、活性領域507に形成されている。図31(A)では、故障検出用の画素501の光電変換部PDの活性領域507の幅を、Xとして図示している。この幅Xとは、図25で示した、垂直出力線108が延在する方向に対して交差する方向における、活性領域507の長さである。

30

**【0295】**

一方、図31(B)は、本実施例の画像取得用の画素401の光電変換部PD、転送トランジスタM2と、増幅トランジスタおよび選択トランジスタが設けられた活性領域610を示した上面図である。

**【0296】**

光電変換部PDは、活性領域507に形成されている。図31(B)では、画像取得用の画素401の光電変換部PDの活性領域507の幅を、Yとして図示している。この幅Yとは、図25で示した垂直出力線108が延在する方向に対して交差する方向における、活性領域507の長さである。

40

**【0297】**

図31(A)では、一の画素セル300の半導体領域303Aから、別の画素セル300のトランジスタが形成された活性領域610までの距離をD1として示している。また、図31(B)では、一の画素セル200の半導体領域203Aから、別の画素セル200のトランジスタが形成された活性領域610までの距離をD2として示している。本実施例では幅Xを、幅Yよりも小さくしている。これにより距離D1を、距離D2よりも大きくすることができる。これにより、一の画素セル200の半導体領域303Aと、別の画素セル200の活性領域610との間に生じる電界を緩和することができる。これにより、活性領域610に形成されるトランジスタあるいは光電変換部PDの故障を生じにくく

50

させることができる。

**【0298】**

(実施例8)

本実施例の撮像装置について、実施例6と異なる点を中心に説明する。

**【0299】**

図32を用いて説明する、図28に示した部材と同じ機能を有する部材には、図28で付した符号と同じ符号が、図32においても付されている。

**【0300】**

図32は故障検出用の画素セル300の上面図である。

**【0301】**

図32において、故障検出用の画素セル300の画素501と隣接して、増幅トランジスタM3、選択トランジスタM4が形成される活性領域610が配置されている。N型の半導体領域503は、N型の半導体領域303Aよりも不純物濃度の高い領域である。光電変換部PDの活性領域507の端部より距離Z分、内側に形成されている。この距離Zとは、図25に示した垂直出力線108が延在する方向に対して交差する方向における、光電変換部PDの活性領域507の端部から、半導体領域503の端部までの距離である。

**【0302】**

本実施例の撮像装置は、距離Zを設けることにより、光電変換部PDと、活性領域610との間で生じる電界を緩和することができる。これにより、活性領域610に形成されるトランジスタあるいは光電変換部PDの故障を生じにくくさせることができる。

**【0303】**

(実施例9)

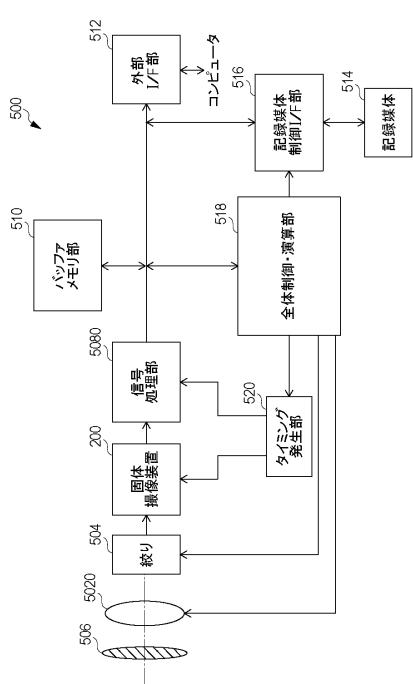

図33は、本実施例による撮像システム500の構成を示すブロック図である。本実施例の撮像システム500は、上述の各実施例で述べた撮像装置のいずれかの構成を適用した撮像装置200を含む。撮像システム500の具体例としては、デジタルスチルカメラ、デジタルカムコーダー、監視カメラ等が挙げられる。図33に、上述の各実施例のいずれかの撮像装置を撮像装置200として適用したデジタルスチルカメラの構成例を示す。

**【0304】**

図33に例示した撮像システム500は、撮像装置200、被写体の光学像を撮像装置200に結像させるレンズ5020、レンズ5020を通過する光量を可変にするための絞り504、レンズ5020の保護のためのバリア506を有する。レンズ5020及び絞り504は、撮像装置200に光を集光する光学系である。

**【0305】**

撮像システム500は、また、撮像装置200から出力される出力信号の処理を行う信号処理部5080を有する。信号処理部5080は、必要に応じて入力信号に対して各種の補正、圧縮を行って出力する信号処理の動作を行う。信号処理部5080は、撮像装置200より出力される出力信号に対してA/D変換処理を実施する機能を備えていてもよい。この場合、撮像装置200の内部には、必ずしもA/D変換回路を有する必要はない。

**【0306】**

撮像システム500は、更に、画像データを一時的に記憶するためのバッファメモリ部510、外部コンピュータ等と通信するための外部インターフェース部(外部I/F部)512を有する。更に撮像システム500は、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体514、記録媒体514に記録又は読み出しを行うための記録媒体制御インターフェース部(記録媒体制御I/F部)516を有する。なお、記録媒体514は、撮像システム500に内蔵されていてもよく、着脱可能であってもよい。

**【0307】**

更に撮像システム500は、各種演算を行うとともにデジタルスチルカメラ全体を制御する全体制御・演算部518、撮像装置200と信号処理部5080に各種タイミング信号を出力するタイミング発生部520を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システム500は、少なくとも撮像装置200と、撮像装置200

10

20

30

40

50

から出力された出力信号を処理する信号処理部 5080 を有すればよい。全体制御・演算部 518 及びタイミング発生部 520 は、撮像装置 200 の制御機能の一部又は全部を実施するように構成してもよい。

#### 【0308】

撮像装置 200 は、画像用信号を信号処理部 5080 に出力する。信号処理部 5080 は、撮像装置 200 から出力される画像用信号に対して所定の信号処理を実施し、画像データを出力する。また、信号処理部 5080 は、画像用信号を用いて、画像を生成する。

#### 【0309】

上述した各実施例の撮像装置による撮像装置を用いて撮像システムを構成することにより、より良質の画像が取得可能な撮像システムを実現することができる。

10

#### 【0310】

##### (実施例 10)

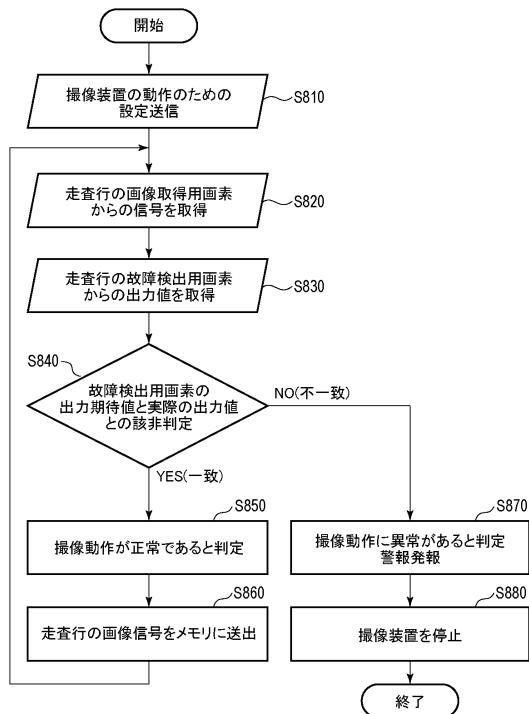

本実施例の撮像システム及び移動体について、図 34 及び図 35 を用いて説明する。

#### 【0311】

図 34 は、本実施例による撮像システム及び移動体の構成例を示す概略図である。図 35 は、本実施例による撮像システムの動作を示すフロー図である。

20

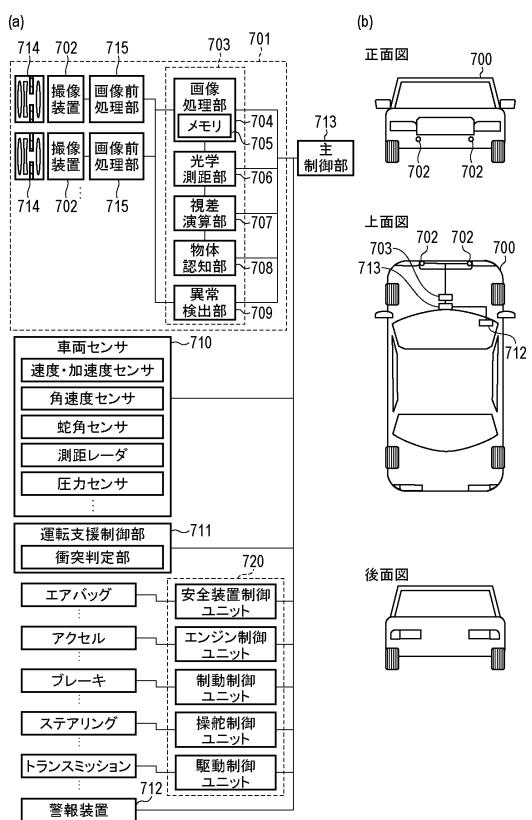

#### 【0312】

本実施例では、車載カメラに関する撮像システムの一例を示す。図 34 は、車両システムと共に搭載される撮像システムの一例を示したものである。撮像システム 701 は、撮像装置 702、画像前処理部 715、集積回路 703、光学系 714 を含む。光学系 714 は、撮像装置 702 に被写体の光学像を結像する。撮像装置 702 は、光学系 714 により結像された被写体の光学像を電気信号に変換する。撮像装置 702 は、上述した各実施例のいずれかの撮像装置である。画像前処理部 715 は、撮像装置 702 から出力された信号に対して所定の信号処理を行う。画像前処理部 715 の機能は、撮像装置 702 内に組み込まれていてもよい。撮像システム 701 には、光学系 714、撮像装置 702 及び画像前処理部 715 が、少なくとも 2 組設けられており、各組の画像前処理部 715 からの出力が集積回路 703 に入力されるようになっている。

#### 【0313】

集積回路 703 は、撮像システム用途向けの集積回路であり、メモリ 705 を含む画像処理部 704、光学測距部 706、視差演算部 707、物体認知部 708、異常検出部 709 を含む。画像処理部 704 は、画像前処理部 715 の出力信号に対して、現像処理や欠陥補正等の画像処理を行う。メモリ 705 は、撮像画像の一次記憶、撮像画素の欠陥位置を格納する。光学測距部 706 は、被写体の合焦や、測距を行う。視差演算部 707 は、複数の撮像装置 702 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う。物体認知部 708 は、車、道、標識、人等の被写体の認知を行う。異常検出部 709 は、撮像装置 702 の異常を検知すると、主制御部 713 に異常を発報する。

30

#### 【0314】

集積回路 703 は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよいし、これらの組合せによって実現されてもよい。また、FPGA (Field Programmable Gate Array) や ASIC (Application Specific Integrated Circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。

40

#### 【0315】

主制御部 713 は、撮像システム 701、車両センサ 710、制御ユニット 720 等の動作を統括・制御する。なお、主制御部 713 を持たず、撮像システム 701、車両センサ 710、制御ユニット 720 が個別に通信インターフェースを有して、それぞれが通信ネットワークを介して制御信号の送受を行う（例えば CAN 規格）方法も取りうる。

#### 【0316】

集積回路 703 は、主制御部 713 からの制御信号を受け或いは自身の制御部によって、撮像装置 702 へ制御信号や設定値を送信する機能を有する。例えば、集積回路 703 は

50

、撮像装置 702 内の電圧スイッチ 13 をパルス駆動させるための設定や、フレーム毎に電圧スイッチ 13 を切り替える設定等を送信する。

#### 【 0 3 1 7 】

撮像システム 701 は、車両センサ 710 に接続されており、車速、ヨーレート、舵角などの自車両走行状態及び自車外環境や他車・障害物の状態を検知することができる。車両センサ 710 は、視差画像から対象物までの距離情報を取得する距離情報取得手段もある。また、撮像システム 701 は、自動操舵、自動巡航、衝突防止機能等の種々の運転支援を行う運転支援制御部 711 に接続されている。特に、衝突判定機能に関しては、撮像システム 701 や車両センサ 710 の検知結果を基に他車・障害物との衝突推定・衝突有無を判定する。これにより、衝突が推定される場合の回避制御、衝突時の安全装置起動を行う。

10

#### 【 0 3 1 8 】

また、撮像システム 701 は、衝突判定部での判定結果に基づいて、ドライバーに警報を発する警報装置 712 にも接続されている。例えば、衝突判定部の判定結果として衝突可能性が高い場合、主制御部 713 は、ブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして、衝突を回避、被害を軽減する車両制御を行う。警報装置 712 は、音等の警報を鳴らす、カーナビゲーションシステムやメーターパネルなどの表示部画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

20

#### 【 0 3 1 9 】

本実施例では、車両の周囲、例えば前方又は後方を撮像システム 701 で撮影する。図 3 4 ( b ) に、車両前方を撮像システム 701 で撮像する場合の撮像システム 701 の配置例を示す。

#### 【 0 3 2 0 】

2つの撮像装置 702 は、車両 700 の前方に配置される。具体的には、車両 700 の進退方位又は外形（例えば車幅）に対する中心線を対称軸に見立て、その対称軸に対して2つの撮像装置 702 が線対称に配置されると、車両 700 と被写対象物との間の距離情報の取得や衝突可能性の判定を行う上で好ましい。また、撮像装置 702 は、運転者が運転席から車両 700 の外の状況を視認する際に運転者の視野を妨げない配置が好ましい。警報装置 712 は、運転者の視野に入りやすい配置が好ましい。

30

#### 【 0 3 2 1 】

次に、撮像システム 701 における撮像装置 702 の故障検出動作について、図 3 5 を用いて説明する。撮像装置 702 の故障検出動作は、図 3 5 に示すステップ S810 ~ S880 に従って実施される。

#### 【 0 3 2 2 】

ステップ S810 は、撮像装置 702 のスタートアップ時の設定を行うステップである。すなわち、撮像システム 701 の外部（例えば主制御部 713）又は撮像システム 701 の内部から、撮像装置 702 の動作のための設定を送信し、撮像装置 702 の撮像動作及び故障検出動作を開始する。撮像装置 702 の動作のための設定には、電圧スイッチ 13 の制御のための設定が含まれる。

40

#### 【 0 3 2 3 】

次いで、ステップ S820において、走査行に属する画像取得用画素領域である第 1 領域 10 の画素 105, 106 からの信号を取得する。また、ステップ S830において、走査行に属する第 2 領域 11 の画素 110, 111 からの出力値を取得する。なお、ステップ S820 とステップ S830 とは逆でもよい。

#### 【 0 3 2 4 】

次いで、ステップ S840において、画素 110, 111 への固定電圧端子 V0, V1 の接続設定に基づく画素 110, 111 の出力期待値と、実際の画素 110, 111 からの出力値との該非判定を行う。

#### 【 0 3 2 5 】

50

ステップ S 840 における該非判定の結果、出力期待値と実際の出力値とが一致している場合は、ステップ S 850 に移行し、第 1 領域 10 における撮像動作が正常に行われていると判定し、処理ステップがステップ S 860 へと移行する。ステップ S 860 では、走査行の画素信号をメモリ 705 に送信して一次保存する。そののち、ステップ S 820 に戻り、故障検出動作を継続する。

#### 【0326】

一方、ステップ S 840 における該非判定の結果、出力期待値と実際の出力値とが一致していない場合は、処理ステップはステップ S 870 に移行する。ステップ S 870 において、第 1 領域 10 における撮像動作に異常があると判定し、主制御部 713、又は警報装置 712 に警報を発報する。警報装置 712 は、表示部に異常が検知されたことを表示させる。その後、ステップ S 880 において撮像装置 702 を停止し、撮像システム 701 の動作を終了する。

10

#### 【0327】

なお、本実施例では、1 行毎にフローチャートをループさせる例を例示したが、複数行毎にフローチャートをループさせてもよいし、1 フレーム毎に故障検出動作を行ってもよい。

#### 【0328】

また、本実施例では、他の車両と衝突しない制御を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。さらに、撮像システム 701 は、自車両等の車両に限らず、例えば、船舶、航空機或いは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

20

#### 【0329】

##### [変形実施例]

本発明は、上記実施例に限らず種々の変形が可能である。

#### 【0330】

例えば、いずれかの実施例の一部の構成を他の実施例に追加した例や、他の実施例の一部の構成と置換した例も、本発明の実施例である。

#### 【0331】

また、これまで説明してきた画素の回路構成は、図 3、図 23 に示したものに限定されるものではなく、適宜変更が可能である。例えば、図 23 の画素 105, 106, 110, 111 は、1 つのマイクロレンズに対し、2 つの光電変換部が配されたデュアルピクセル構造であってもよい。

30

#### 【0332】

上述の実施例は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらの例示によって本発明の技術的範囲が限定的に解釈されなければならない。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な態様で実施することができる。また、これまで述べた各実施例を種々組み合わせて実施することができる。

#### 【符号の説明】

40

#### 【0333】

1 撮像領域

2 有効画素

3 O B 画素

4 参照画素

5 垂直出力線

6 制御線

11 垂直走査回路

13 論理生成回路部

14 画素駆動信号生成回路部

50

15 バッファ回路

16 タイミングジェネレータ

【図面】

【図1】

【図2】

10

20

30

40

50

【図3】

【図4】

【図5】

|        | 列番号 |   |   |     |   |   |     |   |   |   |    |    |

|--------|-----|---|---|-----|---|---|-----|---|---|---|----|----|

|        | 1組目 |   |   | 2組目 |   |   | 3組目 |   |   |   |    |    |

| D(0,0) | 0   | 1 | 2 | 3   | 4 | 5 | 6   | 7 | 8 | 9 | 10 | 11 |

| 0行目    | 0   | 0 | 0 | 0   | 0 | 0 | 0   | 0 | 0 | 0 | 0  | 0  |

| 1行目    | 0   | 0 | 0 | 1   | 0 | 0 | 0   | 1 | 0 | 0 | 0  | 1  |

| 2行目    | 0   | 0 | 1 | 0   | 0 | 0 | 1   | 0 | 0 | 0 | 1  | 0  |

| ⋮      | ⋮   | ⋮ | ⋮ | ⋮   | ⋮ | ⋮ | ⋮   | ⋮ | ⋮ | ⋮ | ⋮  | ⋮  |

| 16行目   | 1   | 1 | 1 | 1   | 1 | 1 | 1   | 1 | 1 | 1 | 1  | 1  |

D(0,0) ~ D(16,11)

【図6】

【図 7】

【図 8】

検査情報の算出式

$P2 = D3 + D2 + D1$

$P1 = D3 + D1 + D0$

$P0 = D2 + D1 + D0$  (「+」はEXOR)

10

20

【図 9】

【図 10】

30

40

50

【図 1 1】

|               | 撮像前フレーム1 |        |        | 撮像前フレーム2 |        |        | 撮像フレーム  |         |         |

|---------------|----------|--------|--------|----------|--------|--------|---------|---------|---------|

|               | 0<br>列   | 1<br>列 | 2<br>列 | 0<br>行   | 1<br>行 | 2<br>行 | 0<br>行目 | 1<br>行目 | 2<br>行目 |

| 参考画素4に異常がない場合 | 0        | 0      | 0      | 0行目      | 1      | 1      | 1       | 0       | 0       |

|               | 0        | 0      | 0      | 1行目      | 1      | 1      | 1       | 0       | 0       |

|               | 0        | 0      | 0      | 2行目      | 1      | 1      | 1       | 0       | 1       |

|               | ⋮        | ⋮      | ⋮      | ⋮        | ⋮      | ⋮      | ⋮       | ⋮       | ⋮       |

|               | 0        | 0      | 0      | 16行目     | 1      | 1      | 1       | 1       | 1       |

| 参考画素4に異常がある場合 | 0        | 0      | 0      | 0行目      | 1      | 1      | 1       | 0       | 0       |

|               | 0        | 0      | 0      | 1行目      | 1      | 1      | 1       | 0       | 1       |

|               | 0        | 0      | 0      | 2行目      | 1      | 1      | 0       | 0       | 0       |

|               | ⋮        | ⋮      | ⋮      | ⋮        | ⋮      | ⋮      | ⋮       | ⋮       | ⋮       |

|               | 0        | 0      | 0      | 16行目     | 1      | 1      | 1       | 1       | 1       |

【図 1 2】

10

20

30

40

【図 1 3】

【図 1 4】

50

【図 15】

【図 16】

10

20

【図 17】

【図 18】

30

40

50

【図19】

【 図 2 0 】

【図21】

【 図 2 2 】

【図 2 3】

【図 2 4】

10

20

【図 2 5】

【図 2 6】

30

40

50

【図27】

【図28】

10

20

【図29】

【図30】

30

40

50

【図 3 1】

【図 3 2】

【図 3 3】

【図 3 4】

10

20

30

40

50

【図 3 5】

10

20

30

40

50

---

フロントページの続き

(56)参考文献      特表2007-535252(JP,A)

特開2006-229799(JP,A)

特開平11-308531(JP,A)

特開2013-109391(JP,A)

特開2009-118427(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H01L21/339

H01L27/14-27/148

H01L27/30

H01L29/762

H04N5/30-5/378