등록특허 10-2698578

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년08월23일

(11) 등록번호 10-2698578

(24) 등록일자 2024년08월21일

(51) 국제특허분류(Int. Cl.)

*G02B 5/18* (2006.01) *G02B 1/10* (2015.01)

*G02B 5/20* (2022.01)

(52) CPC특허분류

*G02B 5/1814* (2013.01)*G02B 1/10* (2013.01)

(21) 출원번호 10-2018-0095147

(22) 출원일자 2018년08월14일

심사청구일자 2021년08월06일

(65) 공개번호 10-2019-0019025

(43) 공개일자 2019년02월26일

(30) 우선권주장

62/546,174 2017년08월16일 미국(US)

15/837,990 2017년12월11일 미국(US)

(56) 선행기술조사문헌

JP2004062200 A\*

JP2011187139 A\*

KR100697614 B1\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

루멘텀 오피레이션즈 엘엘씨

미국 캘리포니아주 95035 밀피타스 엔. 맥카시 블

러바드 400

(72) 발명자

밀러 존 마이클

캐나다 오타와 케이2제이 0피7 61 빌 리템 드라이

브

베그날드 스티븐

캐나다 오타와 케이2제이 0피7 61 빌 리템 드라이

브

(74) 대리인

특허법인아주김장리

전체 청구항 수 : 총 19 항

심사관 : 이성룡

(54) 발명의 명칭 회절 광학 소자를 위한 다층 박막 스택

**(57) 요 약**

광학 소자는 기판을 포함할 수도 있다. 광학 소자는 기판 상에 형성된 특정한 파장 범위에 대한 제1 반사-방지 구조체를 포함할 수도 있다. 광학 소자는 제1 반사-방지 구조체의 일부 상에 배치된 적어도 하나의 층을 포함할 수도 있다. 광학 소자는 적어도 하나의 층 상에 형성된 특정한 파장 범위에 대한 제2 반사-방지 구조체를 포함할 수도 있다. 제1 반사-방지 구조체의 제1 표면과 제2 반사-방지 구조체의 제2 표면 사이의 깊이, 제1 반사-방지 구조체의 제1 굴절률, 제2 반사-방지 구조체의 제2 굴절률 및 적어도 하나의 층의 제3 굴절률은, 특정한 파장에 대한 특정한 위상 지연과 연관된 회절 광학 소자를 형성하도록 선택될 수도 있다.

**대 표 도**

300 →

(52) CPC특허분류

*G02B 5/20* (2022.01)

---

## 명세서

### 청구범위

#### 청구항 1

광학 소자로서,

기판;

상기 기판 상에 형성된 특정한 파장 범위에 대한 제1 반사-방지 구조체로서, 상기 제1 반사-방지 구조체는 제1 재료의 제1 층과 제2 재료의 제2 층으로 형성되는, 상기 제1 반사-방지 구조체;

상기 제1 반사-방지 구조체의 분획 부분(fractional portion) 상에 배치된 적어도 하나의 층으로서, 상기 적어도 하나의 층은 상기 제1 재료의 제3 층으로 형성되는, 상기 적어도 하나의 층; 및

상기 적어도 하나의 층 상의 적어도 일 부분에 형성된 상기 특정한 파장 범위에 대한 제2 반사-방지 구조체를 포함하되,

상기 제2 반사-방지 구조체는 상기 제2 재료의 상기 제1 층, 상기 제2 층, 상기 제3 층, 제4 층과 상기 제1 재료의 제5 층으로 형성되고,

상기 제1 반사-방지 구조체의 제1 표면과 상기 제2 반사-방지 구조체의 제2 표면 사이의 깊이, 상기 제1 반사-방지 구조체의 제1 유효 굴절률, 상기 제2 반사-방지 구조체의 제2 유효 굴절률 및 상기 적어도 하나의 층의 제3 굴절률은, 상기 특정한 파장 범위에 포함된 특정한 파장에 대한 특정한 위상 지연과 연관된 회절 광학 소자(diffractive optical element)를 형성하도록 선택되고,

상기 제2 유효 굴절률은 상기 제3 굴절률과는 상이하며, 그리고

상기 제1 반사-방지 구조체는 서로 상이한 대응하는 굴절률을 가진 2개 이상의 층을 포함하는, 광학 소자.

#### 청구항 2

제1항에 있어서, 상기 제1 반사-방지 구조체는 상기 기판의 제1 측면 상에 형성되고; 그리고

상기 광학 소자는 상기 기판의 제2 측면 상에 형성된 반사-방지 코팅을 더 포함하는, 광학 소자.

#### 청구항 3

제1항에 있어서, 상기 제1 반사-방지 구조체는 상기 제2 반사-방지 구조체를 예칭하기 위한 예칭 정지부인, 광학 소자.

#### 청구항 4

제1항에 있어서, 상기 제1 반사-방지 구조체, 상기 제2 반사-방지 구조체 또는 상기 적어도 하나의 층 중 적어도 하나는 박막 증착을 사용하여 형성되는, 광학 소자.

#### 청구항 5

제1항에 있어서, 상기 제1 반사-방지 구조체는 제1 실리콘층과 제1 이산화규소층을 포함하고;

상기 적어도 하나의 층은 제2 실리콘층을 포함하며;

상기 제2 반사-방지 구조체는 제2 이산화규소층을 포함하고; 그리고

상기 특정한 파장 범위는 840nm 내지 860nm인, 광학 소자.

#### 청구항 6

제1항에 있어서, 상기 제1 반사-방지 구조체, 상기 제2 반사-방지 구조체 및 상기 적어도 하나의 층은 실리콘과

이산화규소의 교변층으로 형성되는, 광학 소자.

#### 청구항 7

제1항에 있어서, 상기 제1 반사-방지 구조체, 상기 제2 반사-방지 구조체 및 상기 적어도 하나의 층은 수소화된 실리콘과 이산화규소의 교변층으로 형성되는, 광학 소자.

#### 청구항 8

삭제

#### 청구항 9

제1항에 있어서, 상기 제1 반사-방지 구조체는 상기 기판의 제1 측면 상에 형성되고; 그리고 상기 광학 소자는,

상기 기판의 제2 측면 상에 형성된 또 다른 특정한 파장 범위에 대한 제3 반사-방지 구조체;

상기 제3 반사-방지 구조체의 분획 부분 상에 배치된 또 다른 적어도 하나의 층; 및

상기 다른 적어도 하나의 층 상에 형성된 상기 다른 특정한 파장 범위에 대한 제4 반사-방지 구조체를 더 포함하는, 광학 소자.

#### 청구항 10

제1항에 있어서, 상기 제1 반사-방지 구조체와 상기 제2 반사-방지 구조체는 2-레벨 요철 프로파일을 형성하는, 광학 소자.

#### 청구항 11

제1항에 있어서, 상기 제1 반사-방지 구조체는 제1 실리콘층과 제1 이산화규소층을 포함하고;

상기 적어도 하나의 층은 제2 실리콘층을 포함하며;

상기 제2 반사-방지 구조체는 제2 이산화규소층을 포함하고; 그리고

상기 특정한 파장 범위는 930nm 내지 950nm인, 광학 소자.

#### 청구항 12

제1항에 있어서, 상기 제1 반사-방지 구조체는 제1 실리콘층과 제1 이산화규소층을 포함하고;

상기 적어도 하나의 층은 제2 실리콘층과 제2 이산화규소층을 포함하며;

상기 제2 반사-방지 구조체는 제3 실리콘층을 포함하고; 그리고

상기 특정한 파장 범위는 1540nm 내지 1560nm인, 광학 소자.

#### 청구항 13

제1항에 있어서, 상기 특정한 파장은 840nm 내지 940nm인, 광학 소자.

#### 청구항 14

제1항에 있어서, 상기 깊이는  $\lambda/4$  내지  $3\lambda/4$ 이되,

$\lambda$ 는 상기 특정한 파장을 나타내는, 광학 소자.

#### 청구항 15

제1항에 있어서, 상기 광학 소자의 유효 굴절률은 2.0 내지 3.0인, 광학 소자.

#### 청구항 16

제1항에 있어서, 상기 특정한 위상 지연은  $\pi$  위상 지연인, 광학 소자.

**청구항 17**

제1항에 있어서, 상기 특정한 위상 지연은 π가 아닌 위상 지연인, 광학 소자.

**청구항 18**

광학 소자로서,

기판;

상기 기판 상에 배치된 제1 유효 굴절률을 가진 제1 층 세트로서, 제1의 2가지 이상의 상이한 굴절률을 가진 제1의 2개 이상의 층으로 형성되고, 상기 제1의 2개 이상의 층은 제1 재료의 제1 층과 제2 재료의 제2 층을 포함하는, 상기 제1 층 세트;

상기 제1 층 세트의 분획 부분 상에 배치된, 특정 굴절률을 가진 적어도 하나의 스페이서 층으로서, 상기 적어도 하나의 스페이서 층은 상기 제1 재료의 제3 층으로 형성되는, 상기 적어도 하나의 스페이서 층; 및

상기 적어도 하나의 스페이서 층 상에 배치된 제2 유효 굴절률을 가진 제2 층 세트로서, 제2의 2가지 이상의 상이한 굴절률을 가진 제2의 2개 이상의 층으로 형성된, 상기 제2 층 세트

를 포함하되;

상기 제2 층 세트는 상기 제2 재료의 제4 층과 상기 제1 재료의 제5 층으로 형성되고,

상기 제1 층 세트는 상기 기판 상에 특정한 파장에서 제1 반사-방지 구조체를 형성하고,

상기 제1 층 세트, 상기 적어도 하나의 스페이서 층, 및 상기 제2 층 세트는 상기 기판 상에 상기 특정한 파장에서 제2 반사-방지 구조체를 형성하고 상기 특정한 파장에 대한 특정 위상 지연을 가진 회절 광학 소자를 상기 기판 상에 형성하며, 그리고

상기 제2 층 세트의 제1 표면과 상기 제1 층 세트의 제2 표면 사이의 깊이는 상기 특정 위상 지연을 형성하는, 광학 소자.

**청구항 19**

제18항에 있어서, 상기 제1 반사-방지 구조체와 상기 제2 반사-방지 구조체는 상기 기판의 제1 측면 상에 형성되고; 그리고

상기 광학 소자는 상기 기판의 제2 측면 상에 형성된 반사-방지 코팅을 더 포함하는, 광학 소자.

**청구항 20**

광학 소자를 제조하는 방법으로서,

웨이퍼 상에 복수의 층을 중착하는 단계로서,

상기 중착하는 단계는 특정한 파장에 대한 제1 반사-방지 구조체의 분획 부분 상에 형성된 적어도 하나의 층 밑에 상기 제1 반사-방지 구조체를, 그리고 상기 특정한 파장에 대한 제2 반사-방지 구조체를 형성하고,

상기 제2 반사-방지 구조체의 유효 굴절률이 상기 적어도 하나의 층의 굴절률과는 상이하고,

상기 제1 반사-방지 구조체는 서로 상이한 대응하는 굴절률을 가진 2개 이상의 층을 포함하고,

상기 2개 이상의 층은 제1 재료의 제1 층과 제2 재료의 제2 층을 포함하고,

상기 적어도 하나의 층은 상기 제1 재료의 제3 층으로 형성되며,

상기 제2 반사-방지 구조체는 상기 적어도 하나의 층 상에 형성되고,

상기 제2 반사-방지 구조체는 상기 제2 재료의 상기 제1 층, 상기 제2 층, 상기 제3 층, 제4 층과 상기 제1 재료의 제5 층으로 형성되는, 상기 중착하는 단계; 및

2-레벨 요철 프로파일을 형성하도록 상기 복수의 층 중 층의 하위세트를 에칭하는 단계로서,

상기 제1 반사-방지 구조체와 상기 제2 반사-방지 구조체 사이에 상기 특정한 파장에 대한 특정한 위상 지연과 연관된 회절 광학 소자를 형성하는, 상기 예칭하는 단계

를 포함하는, 광학 소자를 제조하는 방법.

### 청구항 21

삭제

### 청구항 22

삭제

### 청구항 23

삭제

### 청구항 24

삭제

### 청구항 25

삭제

## 발명의 설명

### 기술 분야

[0001]

본 개시내용은 박막 스택에 관한 것이다. 더 구체적으로, 본 개시내용의 일부 양태는 다중 박막 스택의 예칭된 영역과 예칭되지 않은 영역 사이에 특정한 위상 지연을 제공하고, 그리고 특정한 파장 범위에 대한 반사-방지 코팅을 제공하는 회절 광학 소자(diffractive optical element: DOE)를 위한 다중 박막 스택에 관한 것이다.

### 배경 기술

[0002]

회절 광학 소자(DOE)는 빔을 지향시키기 위해 사용될 수도 있다. 예를 들어, DOE, 예컨대, 회절 렌즈, 스롯 어레이 조명기(spot array illuminator), 스롯 어레이 발생기, 푸리에 어레이 발생기(Fourier array generator) 등은 빔을 분할하고, 빔을 성형하고, 빔의 초점을 맞추는 등을 하도록 사용될 수도 있다. DOE는 멀티캐스트 스 위치, 파장 선택 스위치, 제스처 인식 시스템, 움직임 감지 시스템 등에 통합될 수도 있다.

[0003]

다중 레벨 표면 요철 프로파일은 표면 요철 DOE를 위해 선택될 수도 있다. 예를 들어, 2-레벨(때때로 "바이너리"로 지칭됨) 표면 요철 프로파일은 표면 요철 DOE를 위해 선택될 수도 있다. 다중 레벨 표면 요철 프로파일은 연속적인 표면 요철 프로파일과 유사해지도록 그리고 포토리소그래피 절차 및/또는 예칭 절차의 사용이 DOE를 제작하게 하도록 선택될 수도 있다. 2-레벨 박막 스택은 단일 차수의 바이너리 DOE, 예컨대, 회절 렌즈를 생성하도록 사용될 수도 있다. DOE를 위해 사용되는 일부 재료는 문턱값 초과의 예칭 깊이를 요구할 수도 있어서, DOE를 제작하기 위한 문턱값 예칭 시간을 발생시킨다.

### 발명의 내용

[0004]

일부 가능한 구현예에 따르면, 광학 소자는 기판을 포함할 수도 있다. 광학 소자는 기판 상에 형성된 특정한 파장 범위에 대한 제1 반사-방지 구조체를 포함할 수도 있다. 광학 소자는 제1 반사-방지 구조체의 일부 상에 배치된 적어도 하나의 층을 포함할 수도 있다. 광학 소자는 적어도 하나의 층 상에 형성된 특정한 파장 범위에 대한 제2 반사-방지 구조체를 포함할 수도 있다. 제1 반사-방지 구조체의 제1 표면과 제2 반사-방지 구조체의 제2 표면 사이의 깊이, 제1 반사-방지 구조체의 제1 굴절률, 제2 반사-방지 구조체의 제2 굴절률 및 적어도 하나의 층의 제3 굴절률은, 특정한 파장에 대한 특정한 위상 지연과 연관된 회절 광학 소자를 형성하도록 선택될 수도 있다.

[0005]

일부 가능한 구현예에 따르면, 방법은 웨이퍼 상에 복수의 층을 증착하는 단계를 포함할 수도 있다. 증착 단계는 특정한 파장에 대한 제2 반사-방지 구조체 아래에 특정한 파장에 대한 제1 반사-방지 구조체를 형성할 수도

있다. 방법은 2-레벨 요철 프로파일을 형성하도록 복수의 층 중 층의 하위세트를 에칭할 수도 있다. 에칭 단계는 제1 반사-방지 구조체와 제2 반사-방지 구조체 사이에 특정한 파장에 대한 특정한 위상 지연과 연관된 회절 광학 소자를 형성할 수도 있다.

[0006] 일부 가능한 구현예에 따르면, 방법은 박막 증착 기법을 사용하여 웨이퍼 상에 복수의 박막을 증착하는 단계를 포함할 수도 있다. 복수의 박막을 증착하는 단계는 특정한 파장에 대한 제1 반사-방지 구조체를 증착하는 것과 제1 반사-방지 구조체를 증착한 후 특정한 파장에 대한 제2 반사-방지 구조체를 증착하는 것을 포함할 수도 있다. 방법은 웨이퍼의 복수의 영역을 획정하는 결정된 전이점의 세트에 기초하여 마스크를 패터닝하는 단계를 포함할 수도 있다. 방법은 마스크에 기초하여 2-레벨 요철 프로파일을 형성하도록 복수의 박막 중 박막의 하위세트를 에칭하는 단계를 포함할 수도 있다. 에칭 단계는 제1 반사-방지 구조체와 제2 반사-방지 구조체 사이에 특정한 파장에 대한  $\pi$  위상 지연과 연관된 회절 광학 소자를 형성할 수도 있다. 방법은 마스크를 제거하는 단계를 포함할 수도 있다.

### 도면의 간단한 설명

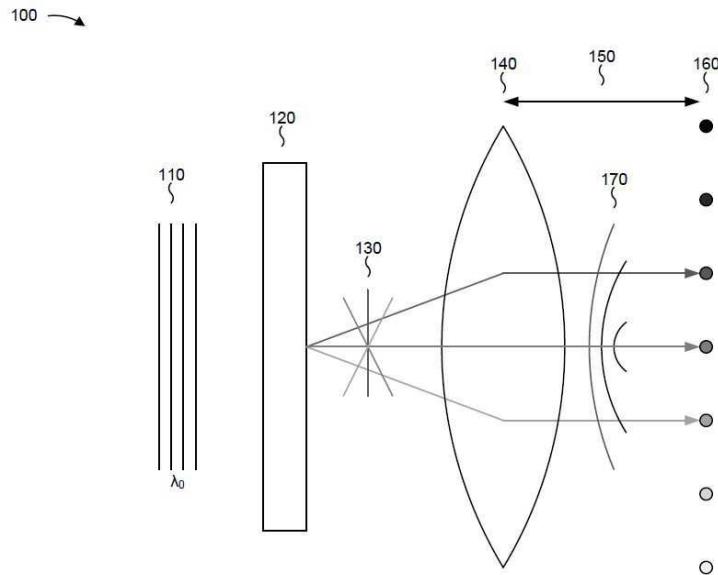

[0007] 도 1은 본 명세서에 설명된 예시적인 구현예의 개요의 도면;

도 2a 및 도 2b는 본 명세서에 설명된 예시적인 구현예에 관한 특성의 도면;

도 3a 및 도 3b는 본 명세서에 설명된 예시적인 구현예에 관한 특성의 도면;

도 4a 내지 도 4c는 본 명세서에 설명된 예시적인 구현예의 도면;

도 5는 본 명세서에 설명된 예시적인 구현예를 구성하기 위한 예시적인 과정의 흐름도;

도 6a 및 도 6b는 도 5에 도시된 예시적인 과정에 관한 예시적인 구현예의 도면;

도 7은 본 명세서에 설명된 예시적인 구현예를 제작하기 위한 예시적인 과정의 흐름도; 및

도 8a 및 도 8b는 도 7에 도시된 예시적인 과정에 관한 예시적인 구현예의 도면.

### 발명을 실시하기 위한 구체적인 내용

[0008] 예시적인 구현예의 다음의 상세한 설명은 첨부된 도면에 관한 것이다. 상이한 도면에서 동일한 참조 부호는 동일하거나 유사한 구성요소를 식별할 수도 있다.

[0009] 회절 광학 소자(DOE)는 포토리소그래피 절차 및/또는 에칭 절차를 사용하여 제작될 수도 있다. 예를 들어, 연속적인 표면 요철 프로파일과 유사해지도록, 다중 레벨 표면 요철 프로파일이 DOE에 대해 선택될 수도 있고 그리고 DOE의 표면은 다중 레벨 표면 요철 프로파일을 형성하도록 에칭 또는 패터닝될 수도 있다. 다중 레벨 표면 요철 프로파일은 DOE를 통과하는 빔에 대한 위상 지연을 생성하도록 사용될 수도 있다. 단일 차수의 바이너리 DOE, 예컨대, 회절 렌즈에 대해, 대략 40%의 회절 효율이 바이너리-레벨의 표면 요철 프로파일을 사용하여 달성될 수도 있다. 그러나, 이 회절 효율은 광통신 시스템, 제스처 인식 시스템, 움직임 검출 시스템 등과 같은 광시스템에서 DOE의 활용을 위해 필요한 문턱값 미만일 수도 있다. 또한, 예를 들어, 제스처 인식 시스템에서 눈 손상을 유발하는 것을 방지하도록 광시스템에 대한 0-차수를 감소시키는 것이 일부 시스템에서 유리할 수도 있다.

[0010] 본 명세서에 설명된 일부 구현예는 2-레벨 DOE에 문턱값 회절 효율을 제공할 수도 있다. 예를 들어, 본 명세서에 설명된 일부 구현예는 DOE의 부분 사이의  $\pi$  위상 지연을 제공하도록 2-레벨(또한 "바이너리"로 지칭됨) DOE에 문턱값 피처 크기(예를 들어, 문턱값 양의 파장)을 제공할 수도 있다. 또한, DOE는 문턱값 미만의 선택된 표면 요철 프로파일을 제조하도록 에칭 깊이와 연관될 수도 있어서, DOE를 제작하기 위한 다른 기법에 비해 DOE에 대한 감소된 종횡비, 감소된 에칭 시간 및/또는 감소된 제조 비용을 발생시킨다. 또한, DOE의 층은 DOE에 반사-방지 기능을 제공할 수도 있고, DOE에 통합된 에칭 정지부를 제공할 수도 있고, DOE에 대한 특정한 작동 파장 범위에 대해 선택된 재료 등을 포함할 수도 있다. 본 명세서에 설명된 일부 구현예는 DOE를 구성 및/또는 제작하기 위한 방법을 제공할 수도 있다. 박막 증착 기법을 사용하는 것에 기초하여, 위상 지연은 더 큰 정확도로 제어될 수도 있고, 이는 광시스템에 대한 0-차수를 감소시킬 수도 있다. 예를 들어, 박막 증착 기법은 1% 미만, 0.5% 미만, 0.2% 미만, 0.1% 미만 등의 허용 오차와 연관될 수도 있다. 유사하게 제어된 허용 오차를 가진 다른 제작 기법이 또한 본 명세서에 설명된 DOE를 구성하도록 사용될 수도 있다.

[0011] 도 1은 본 명세서에 설명된 예시적인 구현예(100)의 개요의 도면이다. 도 1은 스포트 어레이 조명기(때때로 스포

어레이 발생기로 지칭됨)로서 수렴 렌즈 및 표면 요철 DOE 격자를 사용한 스포 어레이 발생의 실시예를 도시한다.

[0012] 도 1에 도시된 바와 같이,  $\lambda_0$ 의 파장을 가진 입사 평면파(110)는 표면 요철 DOE 격자(120)를 향하여 지향된다. 일부 구현예에서, 표면 요철 DOE 격자(120)는 다중 레벨 표면 요철 프로파일을 가진 DOE, 예컨대, 2-레벨 DOE (때때로 바이너리 DOE로 지칭됨)일 수도 있다. 일부 구현예에서, 표면 요철 DOE 격자(120)는 예를 들어, 실리콘(Si)과 이산화규소( $SiO_2$ )의 교번층, 수소화된 실리콘(Si:H)과 이산화규소의 교번층 등을 포함할 수도 있다. 일부 구현예에서, 표면 요철 DOE 격자(120)의 층은 표면 요철 DOE 격자(120)의 예칭된 영역에 그리고 표면 요철 DOE 격자(120)의 예칭되지 않은 영역에 반사-방지 기능을 제공하도록 구성될 수도 있다. 일부 구현예에서, 표면 요철 DOE 격자(120)의 층(예를 들어, 이산화규소층)은 표면 요철 DOE 격자(120)의 제작 동안 예칭 정지 기능을 제공할 수도 있다. 일부 구현예에서, 입사 평면파(110)는 대략 800nm(나노미터) 내지 대략 1100nm, 대략 800nm 내지 대략 1000nm, 대략 830nm 내지 대략 1000nm, 대략 850nm 내지 대략 1000nm, 대략 915nm 내지 대략 1000nm, 대략 940nm 내지 대략 1000nm 등의 범위 내의 파장을 가질 수도 있다. 표면 요철 DOE 격자(120)에 관한 부가적인 상세사항이 본 명세서에 설명된다.

[0013] 또한 도 1에 도시된 바와 같이, 표면 요철 DOE 격자(120)는 입사 평면파(110)를 회절시키고 그리고 과면(130) (예를 들어, 입사 평면파(110)의 회절 차수)을 수렴 렌즈(140)를 향하여 지향시킨다. 수렴 렌즈(140)는 초점면(160)으로부터 초점 거리(150)만큼 이격된다. 일부 구현예에서, 예시적인 구현예(100)는 제스처 인식 시스템을 위해 사용될 수도 있고 그리고 초점면(160)은 제스처 인식을 위한 타겟일 수도 있다. 부가적으로 또는 대안적으로, 초점면(160)은 (예를 들어, 움직임 감지 시스템에 대한) 물체, (예를 들어, 광통신 시스템에 대한) 통신 타겟 등일 수도 있다.

[0014] 또한 도 1에 도시된 바와 같이, 과면(170)을 형성하도록 과면(130)의 방향을 변경하는 수렴 렌즈(140)에 기초하여, 과면(170)이 초점면(160)을 향하여 지향되어 다수의 스포 어레이 패턴이 초점면(160)에 형성되게 한다. 일부 구현예에서, 표면 요철 DOE 격자(120)는 1차원 스포 어레이를 생성하도록 사용될 수도 있다. 일부 구현예에서, 표면 요철 DOE 격자(120)는 2차원 스포 어레이를 생성하도록 사용될 수도 있다. 이 방식으로, 표면 요철 DOE 격자는 입사 평면파(110)로부터 초점면(160)에 스포 어레이를 생성하도록 스포 어레이 조명기로서 사용될 수도 있어서 제스처 인식 시스템, 움직임 감지 시스템, 광통신 시스템 등을 가능하게 한다.

[0015] 위에 나타낸 바와 같이, 도 1은 단지 실시예로서 제공된다. 다른 실시예가 가능하고 그리고 도 1에 관하여 설명된 것과는 상이할 수도 있다.

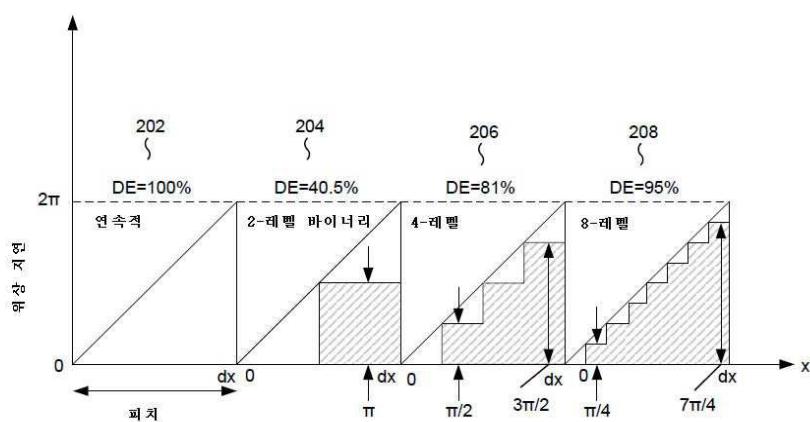

[0016] 도 2a 및 도 2b는 각각, DOE에 관한 특성과 연관된 도면(200 및 250)이다. 도 2a에 도시된 바와 같이 그리고 도면(200)에 의해, 연속적인 요철 프로파일은 포토리소그래피 및/또는 예칭 절차가 DOE를 제작하기 위해 사용되도록 일련의 별개의 레벨로 양자화될 수 있다.

[0017] 도 2a에 그리고 참조 부호(202)로 또한 도시된 바와 같이, 연속적인 요철 프로파일은 (단일 차수의 구성에 대해) 대략 100%의 회절 효율과 연관될 수도 있고 그리고 제1 피치 위치(0)에 비해, 제2 피치 위치( $dx$ )로부터  $\pi$ 의 연속적으로 증가되는 위상 지연을 제공할 수도 있다. 참조 부호(204)로 도시된 바와 같이, 연속적인 요철 프로파일은 2-레벨 요철 프로파일(때때로 바이너리 요철 프로파일로 지칭됨)과 유사할 수도 있다. 2-레벨 바이너리 요철 프로파일은 (단일 차수의 구성에 대해) 대략 40.5%의 회절 효율과 연관될 수도 있고 그리고 피치 위치(0)로부터 피치 위치( $0.5dx$ )로의 DOE의 제1 영역에 비해, 피치 위치( $0.5dx$ )로부터 피치 위치( $dx$ )로의 DOE의 제2 영역에서  $\pi$  위상 지연을 제공할 수도 있다.

[0018] 도 2a에 그리고 참조 부호(206)로 또한 도시된 바와 같이, 연속적인 요철 프로파일은 4-레벨 요철 프로파일과 유사할 수도 있다. 4-레벨 요철 프로파일은 (단일 차수의 구성에 대해) 대략 81%의 회절 효율과 연관될 수도 있고 그리고 0으로부터  $0.25dx$ 로의 제1 영역에 비해, 피치 위치( $0.25dx$ )로부터 피치 위치( $0.5dx$ )로의 DOE의 제2 영역에서  $\pi/2$  위상 지연; DOE의 제1 영역에 비해,  $0.5dx$ 로부터  $0.75dx$ 로의 DOE의 제3 영역에서  $\pi$  위상 지연; 및 DOE의 제1 영역에 비해,  $0.75dx$ 로부터  $dx$ 로의 DOE의 제4 영역에서  $3\pi/2$  위상 지연을 제공할 수도 있다.

[0019] 도 2a에 그리고 참조 부호(208)로 또한 도시된 바와 같이, 연속적인 요철 프로파일은 8-레벨 요철 프로파일과 유사할 수도 있다. 8-레벨 요철 프로파일은 (단일 차수의 구성에 대해) 대략 95%의 회절 효율과 연관될 수도 있고 그리고 DOE의 영역에서  $\pi/4$ 의 증가의 위상 지연(예를 들어, 0으로부터  $0.125dx$ 로의 DOE의 제1 영역에 비해,  $0.125dx$ 로부터  $0.25dx$ 로의 제2 영역에서  $\pi/4$ ;  $0.25dx$ 로부터  $0.375dx$ 로의 제3 영역에서  $\pi/2$ ;  $0.375dx$ 로부터  $0.5dx$ 로의 제4 영역에서  $3\pi/4$ ; 등)을 제공할 수도 있다. 일부 구현예에서, 또 다른 회절 효율을 가진 또 다른

구성이 사용될 수도 있다. 예를 들어, 2 차수, 4 차수, 10 차수, 100 차수, 수천 차수 등을 사용하는 구성이 단일 차수의 구성에 비해 회절 효율을 증가시키도록 사용될 수도 있다. 이 경우에, 예컨대, +/- 100 차수에 대하여, 대략 65% 내지 80%의 회절 효율이 2-레벨 요철 프로파일에 대해 달성될 수도 있다.

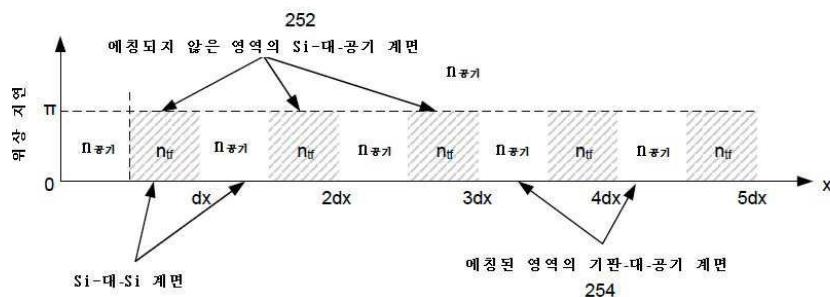

[0020] 도 2b에 그리고 도면(250)으로 도시된 바와 같이, 2-레벨 요철 프로파일은 다수의 예칭되지 않은 영역(252)과 예칭된 영역(254)을 가진 DOE에 대해 사용될 수도 있다. 일부 구현예에서, 예칭되지 않은 영역(252)은 예칭된 영역(254)에 비해  $\pi$  위상 지연과 연관될 수도 있다. 일부 구현예에서, 예칭되지 않은 영역(252)은 실리콘(Si) 대 공기 계면에 대한, 박막 굴절률( $n_{tf}$ )과 연관될 수도 있다. 일부 구현예에서, 예칭된 영역(254)은 위상 지연과 연관되지 않을 수도 있다. 즉, 예칭되지 않은 영역(252)은 예칭된 영역(254)에 비해  $\pi$  위상 지연과 연관된다. 일부 구현예에서, 예칭된 영역(254)은 기판(예를 들어, 실리콘) 대 공기 계면에 대한, 굴절률( $n_{공기}$ )과 연관된다. 일부 구현예에서, 예칭된 영역(254)과 예칭되지 않은 영역(252)의 각각의 군은 집합적으로, 폭( $dx$ )과 연관될 수도 있고 그리고 DOE는 ( $N*dx$ )의 총 폭과 연관될 수도 있고 여기서  $N$ 은 예칭된 영역(254)과 예칭되지 않은 영역(252)의 양을 나타내는 정수값(예를 들어, 1, 2, 3, 4, 5 등)이다.

[0021] 위에 나타낸 바와 같이, 도 2a 및 도 2b는 단지 실시예로서 제공된다. 다른 실시예가 가능하고 그리고 도 2a 및 도 2b에 관하여 설명된 것과는 상이할 수도 있다.

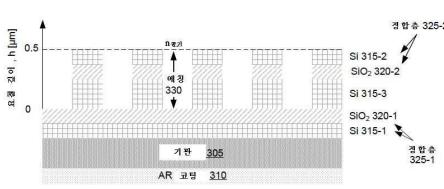

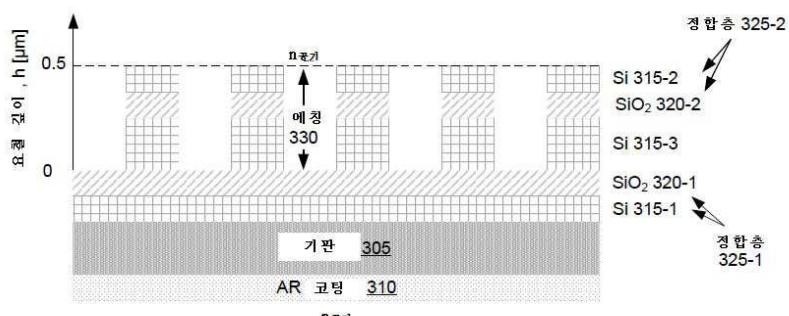

[0022] 도 3a 및 도 3b는 DOE에 관한 특성과 연관된 도면이다. DOE(300)를 도시하는 도 3a는  $\pi$  위상 지연을 제공하도록 구성될 수도 있는 도 2b의 DOE의 2-레벨 요철 프로파일에 대응한다.

[0023] 도 3a에 도시된 바와 같이, DOE(300)는 기판(305)을 포함할 수도 있다. 일부 구현예에서, 기판(305)은 유리 기판, 용융 실리카 기판 등일 수도 있다. 예를 들어, 기판(305)은 대략 200 $\mu\text{m}$ 의 두께를 갖고 그리고 1.45의 굴절률( $n_{sub}$ )을 가진 용융 실리카 기판일 수도 있다. 일부 구현예에서, 반사-방지 코팅(310)이 기판(305)의 표면 상에 배치될 수도 있다. 예를 들어, 도 3a에 도시된 바와 같이, 교변하는 실리콘층과 이산화규소층의 세트가 기판(305)의 상단 표면 상에 배치될 수도 있고 그리고 본 명세서에 설명된 바와 같이 요철 프로파일을 형성하도록 패터닝될 수도 있고 그리고 반사-방지 코팅(310)이 기판(305)의 하단 표면을 덮을 수도 있다.

[0024] 또한 도 3a에 도시된 바와 같이, 실리콘층(315)의 세트와 이산화규소층(320)의 세트는 기판(305)의 상단 표면 상에 배치될 수도 있다. 예를 들어, 실리콘층(315-1)이 기판(305) 상에 배치될 수도 있고 그리고 이산화규소층(320-1)이 실리콘층(315-1) 상에 배치될 수도 있다. 실리콘층(315-1)과 이산화규소층(320-1)은 정합층(325-1)의 쌍을 형성할 수도 있다. 유사하게, 실리콘층(315-2)이 이산화규소층(320-2) 상에 배치될 수도 있고 그리고 정합층(325-2)의 쌍을 형성할 수도 있다. 도시된 바와 같이, 실리콘층(315-3)이 정합층(325-1)과 정합층(325-2) 사이에 배치될 수도 있다.

[0025] 일부 구현예에서, 정합층(325-1)과 정합층(325-2)은 DOE(300)의 투과율을 증가시키도록 반사-방지 코팅을 형성 할 수도 있다. 일부 구현예에서, DOE(300)는 공기 계면에 노출될 수도 있다. 예를 들어, DOE(300)의 제1 표면(예를 들어, 정합층(325-1)의 표면과 정합층(325-2)의 표면)과 DOE(300)의 제2 표면(예를 들어, 반사-방지 코팅(310)의 표면)은 1.0의 굴절률( $n_{공기}$ )을 가진 공기 계면에 노출될 수도 있다. 요철 깊이( $h$ )는 방정식:

$$h = \frac{\lambda_0}{2(n_{tf} - n_{\text{공기}})}$$

[0026] 예 기초하여 계산될 수도 있고,

[0027] 여기서  $\lambda_0$ 은 DOE, 예컨대, DOE(300)에 대한 공칭 조명 파장이다. 요철 깊이를 감소시키기 위해서, 비교적 큰 굴절률을 가진 재료, 예컨대, 실리콘이 선택될 수도 있고, 이는 일부 구현예에서, 대략 0.5 $\mu\text{m}$ (마이크로미터)의 예칭(예를 들어, 예칭(330))의 요철 깊이( $h$ )를 발생시킬 수도 있다. 일부 구현예에서, 요철 깊이는 대략  $\lambda/4$  내지  $\lambda/2$ 일 수도 있고, 여기서  $\lambda$ 는 예를 들어,  $\pi$  위상 지연이 2.0 내지 3.0의 유효 굴절률, 2.2의 유효 굴절률 등으로 달성되는, 대략 940nm의 파장, 840nm 내지 940nm의 파장 등과 같은, 특정한 위상 지연이 달성되는 특정한 파장을 나타낸다. 일부 구현예에서, 충은 DOE(300)의 투과도를 증가시키도록 굴절률 정합될 수도 있다. 예를 들어, 실리콘층(315)과 이산화규소층(320)은 3.1 내지 3.9 및 1.4 내지 1.5의 문턱값 양 각각 내에 있는 3.5와 1.45의 각각의 굴절률에 기초하여 선택될 수도 있다. 이 방식으로, 다른 DOE에 비해 요철 깊이를 감소시키는 것에 기초하여, 본 명세서에 설명된 일부 구현예는 개선된 제작 허용 오차를 가능하게 한다.

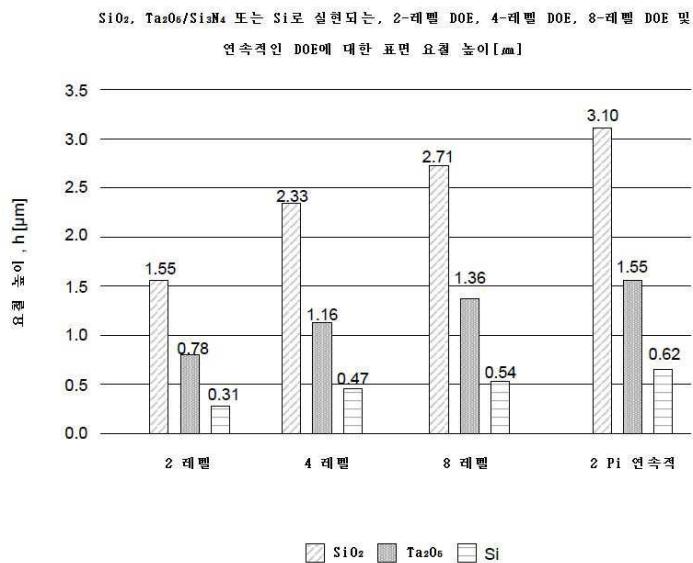

[0028] 도 3b에 그리고 도면(350)으로 도시된 바와 같이, 다른 재료가 대략 2.0의 굴절률을 가질 수도 있는, 탄탈륨 산화물( $Ta_2O_5$ )과 실리콘 질화물( $Si_3N_4$ )과 같은 박막 코팅 재료를 위해 선택될 수도 있다. 또한 도면(350)으로 도

시된 바와 같이, DOE(300)의 층을 위해 실리콘 박막을 사용하는 것에 기초하여, 2-레벨, 4-레벨, 8-레벨 또는 연속적인 요철 프로파일의 각각에 대한 요철 깊이가 다른 재료 선택에 비해 감소된다. 예를 들어, 1550nm의 공칭 조명 파장에서 2-레벨 요철 프로파일의  $\pi$  위상 지연에 대해, 이산화규소는 대략 1.55 $\mu\text{m}$ 의 요철 깊이와 연관될 수도 있고, 탄탈륨 오산화물과 실리콘 질화물은 대략 0.78 $\mu\text{m}$ 의 요철 깊이와 연관될 수도 있고 그리고 실리콘은 대략 0.31 $\mu\text{m}$ 의 요철 깊이와 연관될 수도 있다.

[0029] 위에 나타낸 바와 같이, 도 3a 및 도 3b는 단지 실시예로서 제공된다. 다른 실시예가 가능하고 그리고 도 3a 및 도 3b에 관하여 설명된 것과는 상이할 수도 있다.

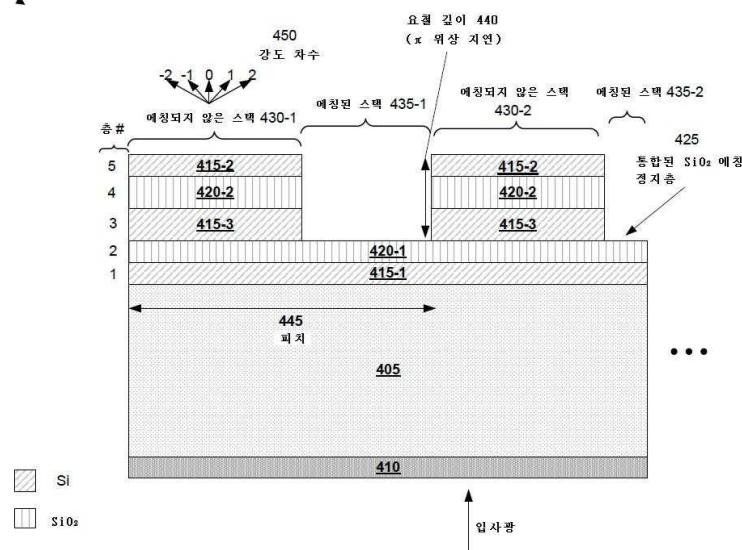

[0030] 도 4a 내지 도 4c는 DOE(400/400'/400'')의 예시적인 구현예의 도면이다. 도 4a에 도시된 바와 같이, DOE(400)는 기판(405), 반사-방지 코팅(410), 실리콘층(415-1 내지 415-3)의 세트 및 이산화규소층(420-1 및 420-2)의 세트를 포함한다.

[0031] 도 4a에 그리고 참조 부호(425)로 또한 도시된 바와 같이, 이산화규소층(420-1)은 예칭이  $\pi$  위상 지연을 형성하게 하기 위한 예칭 정지층일 수도 있다. 예를 들어, 예칭 절차는, 예칭된 스택(435-1 및 435-2)과 예칭되지 않은 스택(430-1 및 430-2) 사이에  $\pi$  위상 지연을 제공하기 위해 예칭되지 않은 스택(430-1 및 430-2)이 예칭되지 않은 채로 있고 그리고 예칭된 스택(435-1 및 435-2)이 문턱값 요철 깊이(440)로 예칭되도록 수행될 수도 있다. 일부 구현예에서, 다수의 툴을 사용하는 다수의 예칭 절차가 DOE(400)를 예칭하도록 수행될 수도 있다. 예를 들어, DOE(400)는 예칭 정지부로서 이산화규소층의 제1 실리콘 예칭, 예칭 정지부로서 실리콘층의 제1 이산화규소 예칭 및 예칭 정지부로서 또 다른 이산화규소층의 제2 실리콘 예칭(예를 들어, 심도 반응성 이온 예칭(deep reactive ion etch: DRIE) 툴을 사용함) 등을 사용하여 제작될 수도 있다.

[0032] 일부 구현예에서, DOE(400)의 층은 반사-방지 구조체의 세트를 형성할 수도 있다. 예를 들어, 층(420-1 및 415-1)이 특정한 파장 범위에 대한 제1 반사-방지 구조체를 형성할 수도 있고 그리고 층(415-2 및 420-2)이 특정한 파장 범위에 대한 제2 반사-방지 구조체를 형성할 수도 있어서, 2-레벨 요철 프로파일을 형성한다. 부가적으로 또는 대안적으로, 층(415-2)은 제2 반사-방지 구조체를 형성할 수도 있다. 제2 반사-방지 구조체는 제1 반사-방지 구조체 상에(예를 들어, 예칭되지 않은 스택(430)에) 형성될 수도 있고 그리고 제1 반사-방지 구조체(예를 들어, 층(420-1))는 제2 반사-방지 구조체를 형성하도록 예칭을 위한 예칭 정지부일 수도 있다. 일부 구현예에서, 적어도 하나의 층, 예컨대, 층(415-3), 층(415-3 및 420-2) 둘 다 같은 제1 반사-방지 구조체와 제2 반사-방지 구조체 사이에 있을 수도 있다. 이 방식으로, 예칭 영역에 대한 변경은 DOE(400)의 투과를 변경하는 일 없이 DOE(400)의 특성을 변경하도록 수행될 수도 있다. 일부 구현예에서, 제1 반사-방지 구조체와 제2 반사-방지 구조체는 층에 의해 분리되지 않을 수도 있다. 일부 구현예에서, 층(415-3)은 또 다른 기능, 예컨대, 특정한 위상 지연(예를 들어,  $\pi$  위상 지연)과 반사-방지 기능 외의 또 다른 기능을 DOE(400)에 제공할 수도 있다. 일부 구현예에서, 집합적으로, DOE(400)의 반사-방지 구조체는 DOE를 형성한다.

[0033] 일부 구현예에서, 각각의 층은 특정한 두께와 연관될 수도 있다. 예를 들어, 층(1)(예를 들어, 실리콘층(415-1))은 대략 209nm의 두께와 연관될 수도 있고; 층(2)(예를 들어, 이산화규소층(420-1))은 162nm의 두께와 연관될 수도 있으며; 층(3)(예를 들어, 실리콘층(415-3))은 존재하는 경우, 238nm의 두께와 연관될 수도 있고; 층(4)(예를 들어, 이산화규소층(420-2))은 존재하는 경우, 254nm의 두께와 연관될 수도 있으며; 그리고 층(5)(예를 들어, 실리콘층(415-2))은 20nm의 두께와 연관될 수도 있다. 일부 구현예에서, DOE(400)는 특정한 피치(445)(때때로 주기로 지칭됨)(dx)와 연관될 수도 있다. 예를 들어, 피치(445)는 대략 1 $\mu\text{m}$  내지 1000 $\mu\text{m}$ 일 수도 있다. 일부 구현예에서, 캡핑층은 제5 층(예를 들어, 또 다른 이산화규소층) 상에 형성될 수도 있고, 이는 기판(405)을 포함하는 웨이퍼의 다이싱 동안 강건성을 개선할 수도 있다.

[0034] 일부 구현예에서, DOE(400)의 층의 두께, 피치(445)의 크기, 반사-방지 구조체 및/또는 반사-방지 구조체의 층의 굴절률 등을 반사-방지 구조체가 반사-방지 기능을 제공하는 특정한 파장에서 특정한 위상 지연(예를 들어,  $\pi$  위상 지연)을 유발하도록 선택될 수도 있다. 예를 들어, 제1 반사-방지 구조체는 1.5의 제1(유효) 굴절률과 연관될 수도 있고, 제2 반사-방지 구조체는 3.5의 제2(유효) 굴절률과 연관될 수도 있으며 그리고 제1 반사-방지 구조체와 제2 반사-방지 구조체 사이의 층(예를 들어, 층(415-3))의 세트는 3.5의 제3(유효) 굴절률과 연관될 수도 있다. 부가적으로 또는 대안적으로, 특정한 파장은 대략 1540nm 내지 1560nm의 파장 범위를 포함할 수도 있다. 참조 부호(450)로 도시된 바와 같이, 입사광이 기판(405)의 제1 측면으로 지향되는 것에 기초하여, 강도 차수(예를 들어, 강도 차수(-2, -1, 0, 1, 2, 등))가 DOE(400)에 의해 제공된다.

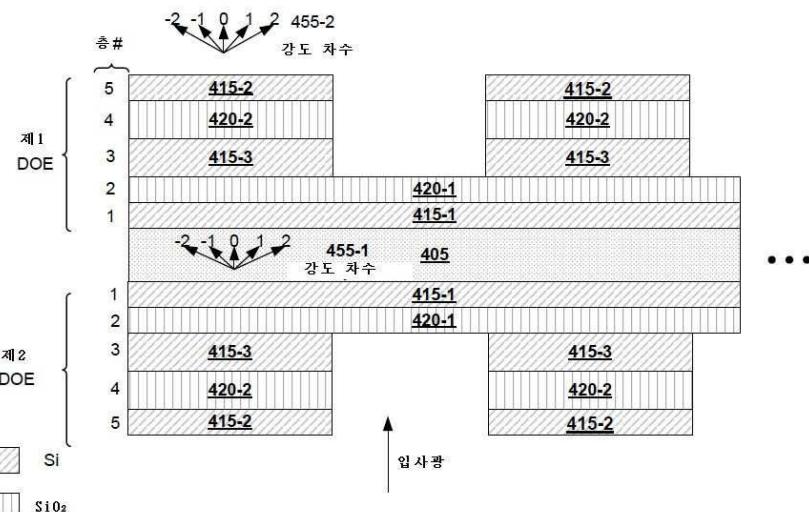

[0035] 도 4b에 도시된 바와 같이, DOE(400')는 기판(405)의 제1 측면 상에 형성된 제1 회절 광학 소자와 기판(405)의 제2 측면 상에 형성된 제2 회절 광학 소자를 포함한다. 각각의 회절 광학 소자는 실리콘층(415-1 내지 415-3)의

세트와 이산화규소층(420-1 및 420-2)의 세트를 포함한다. 참조 부호(455-1 및 455-2)로 도시된 바와 같이, 입사광이 DOE(400')를 향하여 지향되는 것에 기초하여, 제2 회절 광학 소자는 강도 차수의 제1 세트가 기판(405)을 통해 제1 회절 광학 소자로 지향되게 하고, 이는 강도 차수의 제2 세트가 DOE(400')로부터 제공되게 한다. 이 방식으로, 기판(405)은 제1 회절 광학 소자와 제2 회절 광학 소자의 정렬을 유지하여, 또 다른 기법, 예컨대, 자유 공간 광학(free space optics) 또는 접기 놓기 기계를 사용하는 것에 비해 정렬을 유지하는 것의 어려움을 감소시킨다.

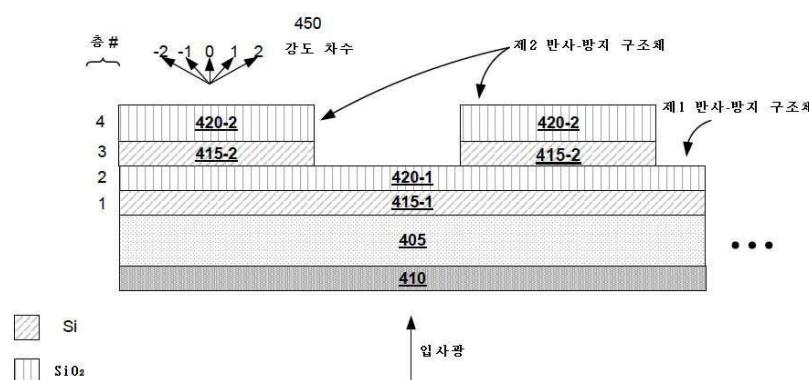

[0036] 도 4c에 도시된 바와 같이, DOE(400'')는 기판(405)의 표면 상에 형성된 제1 반사-방지 구조체와 제1 반사-방지 구조체의 일부의 표면 상에 형성된 제2 반사-방지 구조체를 (예를 들어, 하나 이상의 층이 제1 반사-방지 구조체와 제2 반사-방지 구조체 사이에 형성되는 일 없이) 포함한다. 예를 들어, 제1 반사-방지 구조체와 제2 반사-방지 구조체는 반사-방지 기능을 특정한 파장, 예컨대, 930nm 내지 950nm의 파장 범위에 제공할 수도 있고 그리고 특정한 파장에서 특정한 위상 지연, 예컨대,  $\pi$  위상 지연을 제공할 수도 있다. 일부 구현예에서, DOE(400'')의 층은 특정한 두께와 연관될 수도 있다. 예를 들어, 층(1)은 대략 121nm의 두께와 연관될 수도 있고, 층(2)은 대략 107nm의 두께와 연관될 수 있으며, 층(3)은 대략 130nm의 두께와 연관될 수 있고, 층(4)은 대략 258nm의 두께와 연관될 수도 있는 등이다.

[0037] 본 명세서에 설명된 일부 구현예가 특정한 수의 층, 예컨대, 4층 또는 5층에 관하여 설명되지만, 다른 수의 층, 예컨대, 6층(예를 들어, 6개의 교번하는 실리콘/이산화규소층), 7층, 10층, 20층 등이 가능하다.

[0038] 위에 나타낸 바와 같이, 도 4a 내지 도 4c는 단지 실시예로서 제공된다. 다른 실시예가 가능하고 그리고 도 4a 내지 도 4c에 관하여 설명된 것과는 상이할 수도 있다.

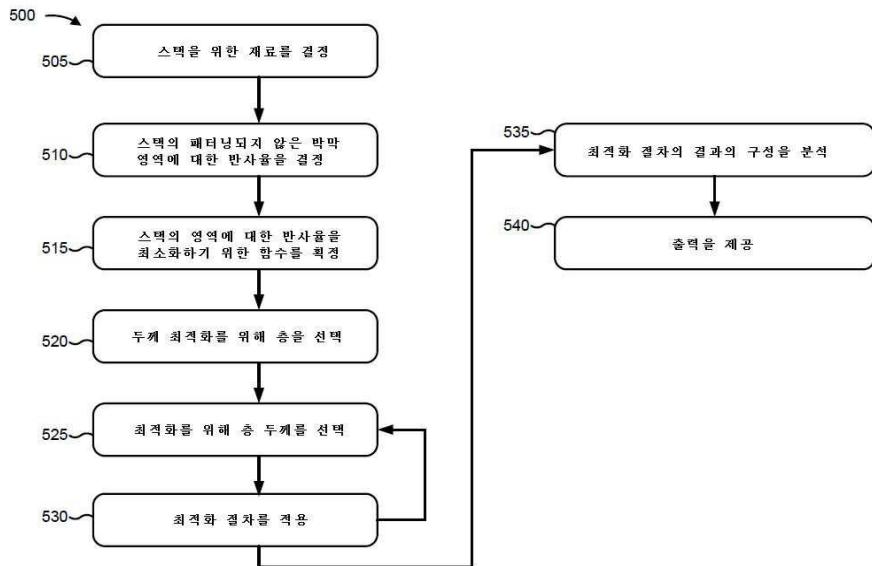

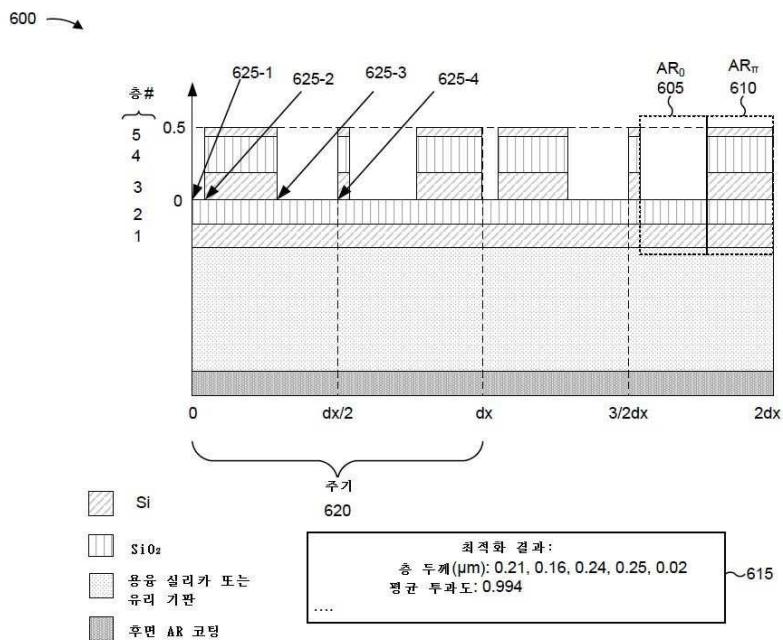

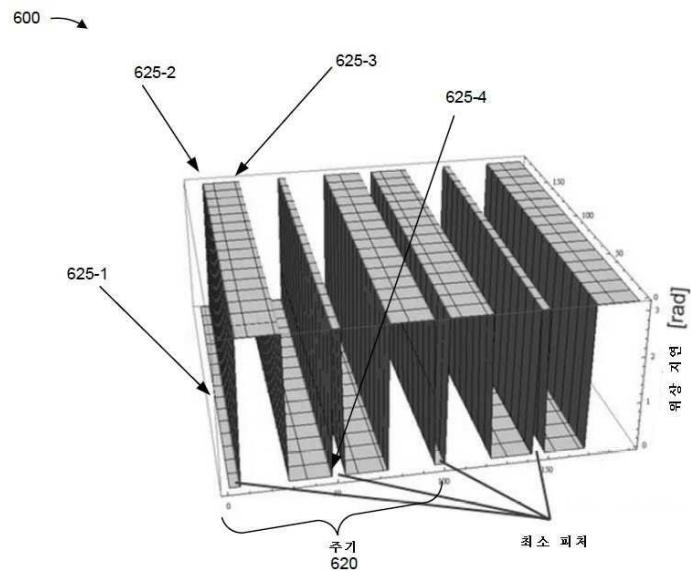

[0039] 도 5는 DOE를 구성하기 위한 예시적인 과정(500)의 흐름도이다. 일부 구현예에서, 도 5의 하나 이상의 과정 블록이 클라이언트 디바이스에 의해 수행될 수도 있다. 일부 구현예에서, 도 5의 하나 이상의 과정 블록은 클라이언트 디바이스, 예컨대, 서버 디바이스로부터 분리되거나 또는 이를 포함하는 또 다른 디바이스 또는 디바이스의 군에 의해 수행될 수도 있다. 도 6a 및 도 6b는 도 5에 도시된 예시적인 과정(500)에 관한 예시적인 구현예(600)의 도면이다.

[0040] 도 5에 도시된 바와 같이, 과정(500)은 스택을 위한 재료를 결정하는 단계(블록(505))를 포함할 수도 있다. 예를 들어, 클라이언트 디바이스는 스택을 위한 재료를 결정할 수도 있다. 일부 구현예에서, 클라이언트 디바이스는 스택을 위한 재료를 식별하는 입력을 수신할 수도 있다. 예를 들어, DOE의 디자인 동안, 디자이너는 디자인 기준의 세트에 기초하여 코팅 재료의 세트를 선택할 수도 있다. 일부 구현예에서, 코팅 재료의 세트는 실리콘, 수소화된 실리콘, 이산화규소, 탄탈륨 오산화물, 실리콘 질화물, 이들의 조합 등을 포함할 수도 있다. 일부 구현예에서, 디자인 기준의 세트는 DOE에 대한 파장 범위, 재료에 대한 굴절률, 재료의 투과율 등을 포함할 수도 있다. 일부 구현예에서, 스택은 다층 스택일 수도 있다. 예를 들어, 도 6a에 도시된 바와 같이, 스택은 용융 실리카 기판, 유리 기판 등 상에 배치된 교번하는 실리콘 박막과 이산화규소 박막의 5층 스택일 수도 있다.

[0041] 또한 도 5에 도시된 바와 같이, 과정(500)은 스택의 패터닝되지 않은 박막 영역에 대한 반사율을 결정하는 단계(블록(510))를 포함할 수도 있다. 예를 들어, 클라이언트 디바이스는 스택의 패터닝되지 않은 박막 영역에 대한 반사율을 결정할 수도 있다. 일부 구현예에서, 클라이언트 디바이스는 제1 영역과 제2 영역에 대한 반사율을 식별하는 입력을 수신할 수도 있다. 예를 들어, 디자이너는 도 6a에 참조 부호(605)로 도시된 바와 같이, 기판 및 교번하는 실리콘 박막 층과 이산화규소 박막 층의 제1 쌍을 포함하는 스택의 제1 영역에 대한 반사율을 결정할 수도 있다. 이 제1 영역은  $AR_0$ 으로 지칭될 수도 있다. 이 경우에, 디자이너는 도 6a에 참조 부호(610)로 도시된 바와 같이, 기판, 교번하는 실리콘 박막 층과 이산화규소 박막 층의 제1 쌍, 실리콘 박막 층 및 교번하는 실리콘 박막 층과 이산화규소 박막 층의 제2 쌍을 포함하는 스택의 제2 영역에 대한 반사율을 결정할 수도 있다. 이 제2 영역은  $AR_{\pi}$ 로 지칭될 수도 있다. 별개의 패터닝되지 않은 스택인  $AR_0$  및  $AR_{\pi}$ 에 기초하여, 반사율, 투과도 및 위상 지연이 박막 이론을 사용하여  $AR_0$  및  $AR_{\pi}$ 에 대해 결정될 수 있어서, 전역 최적화가 회절 이론을 사용하여 행해진 계산의 최적화에 비해 개선된 효율을 가지며 채용되게 한다. 이 방식으로, DOE에 대한 구성의 최적화를 위한 클라이언트 디바이스에 의한 활용 컴퓨팅 자원은 다른 기법에 비해 감소될 수도 있다.

[0042] 또한 도 5에 도시된 바와 같이, 과정(500)은 스택의 영역에 대한 반사율을 최소화하기 위한 함수를 획정하는 단계(블록(515))를 포함할 수도 있다. 예를 들어, 클라이언트 디바이스는 스택의 영역에 대한 반사율을 최소화하기 위한 함수를 획정할 수도 있다. 일부 구현예에서, 함수는 가점 함수, 비용 함수 등일 수도 있다. 예를 들어, 클라이언트 디바이스는 함수의 최적화(예를 들어, 최소화)가  $\pi$ 의 위상 지연이  $AR_0$ 과  $AR_{\pi}$  사이에 유지되는 스택

의 영역에 대해 감소되는 반사율을 발생시키도록 함수를 식별하는 입력을 수신할 수도 있다. 이 방식으로, 클라이언트 디바이스는 적어도 대략 80%, 대략 90%, 대략 95%, 대략 99% 등의 투과도와 같이, 투과도를 특정한 파장 범위에 대한 문턱값 레벨로 개선할 수도 있다.

[0043] 또한 도 5에 도시된 바와 같이, 과정(500)은 두께 최적화를 위해 층을 선택하는 단계(블록(520))를 포함할 수도 있다. 예를 들어, 클라이언트 디바이스는 두께 최적화를 위해 적어도 하나의 층을 선택할 수도 있다. 일부 구현 예에서, 클라이언트 디바이스는 적어도 하나의 층을 식별하는 입력을 수신할 수도 있다. 예를 들어, 디자이너는 도 6a에 도시된 층(3)(예를 들어, 정합층(1 및 2)과 정합층(4 및 5) 사이에 샌드위치된 실리콘층)의 두께를 최적화하도록 선택할 수도 있고 그리고 층(3)에 대한 두께에 관하여 DOE에 대한 반사율의 최적화를 가능하게 하도록 층(1, 2, 4, 5)에 대한 두께를 지정할 수도 있다. 일부 구현 예에서, 층에 대한 두께는 방정식의 세트:

$$\Delta\phi = k \sum_{i=1}^N h_i (n_i - 1)$$

[0044]

$$k = 2\pi/\lambda_0$$

에 기초하여 결정될 수도 있다:

[0045] 여기서  $\Delta\phi$ 는 선택된 위상 지연(예를 들어,  $\pi$ )을 나타내고,  $k$ 는 (예를 들어, 층(3)의) 상수 값을 나타내며,  $h_i$ 는 층( $i$ )의 요철 깊이를 나타내고,  $n_i$ 는 층( $i$ )의 굴절률을 나타내며, 그리고  $\lambda_0$ 은 DOE의 공칭 조명 파장을 나타낸다. 이 방식으로, 클라이언트 디바이스는 DOE의 다른 층의 두께에 기초하여 선택된 위상 지연을 획득하도록 예를 들어, 층(3)의 두께를 계산할 수도 있다.

[0046] 또한 도 5에 도시된 바와 같이, 과정(500)은 최적화를 위해 층 두께를 선택하는 단계(블록(525))를 포함할 수도 있다. 예를 들어, 클라이언트 디바이스는 최적화를 위해 층 두께를 선택할 수도 있다. 일부 구현 예에서, 클라이언트 디바이스는 두께를 임의로 선택할 수도 있다. 예를 들어, 클라이언트 디바이스는 층(3)의 층 두께의 결정을 가능하게 하도록 층(1, 2, 4, 및 5)에 대한 층 두께를 선택하는 임의적 선택 절차를 활용할 수도 있다. 일부 구현 예에서, 클라이언트 디바이스는 두께를 선택하도록 비-임의적 선택 절차, 예컨대, 최적화 절차를 활용할 수도 있다.

[0047] 또한 도 5에 도시된 바와 같이, 과정(500)은 최적화 절차를 적용하는 단계(블록(530))를 포함할 수도 있다. 예를 들어, 클라이언트 디바이스는 최적화 절차를 적용할 수도 있다. 일부 구현 예에서, 클라이언트 디바이스는 DOE의 반사율을 최적화하도록 시뮬레이션된 어닐링을 사용할 수도 있다. 예를 들어, 클라이언트 디바이스는 반사율을 최적화(예를 들어, 최소화)하기 위해 층 두께를 구성하기 위한 비용 함수를 최적화하도록 시뮬레이션된 어닐링 절차 및 최급 강하 알고리즘 절차를 수행할 수도 있다. 일부 구현 예에서, 클라이언트 디바이스는 문턱값 기준이 충족(예를 들어, 투과의 문턱값 레벨이 50% 초과의 투과, 80% 초과의 투과, 90% 초과의 투과, 95% 초과의 투과, 99% 초과의 투과, 99.5% 초과의 투과 등과 같이 계산)될 때까지 최적화 절차를 수행할 수도 있다.

[0048] 또한 도 5에 도시된 바와 같이, 과정(500)은 최적화 절차의 결과의 구성을 분석하는 단계(블록(535))를 포함할 수도 있다. 예를 들어, 클라이언트 디바이스는 표면 요철 프로파일을 결정하도록 DOE에 대한 전이점을 결정할 수도 있다. 도 6a에 그리고 참조 부호(615)로 도시된 바와 같이, 최적화의 결과는 DOE에 대한 최적화된 특성을 식별할 수도 있다. 일부 구현 예에서, 클라이언트 디바이스는 짹수 차수와 0 차수가 억제되는 구성(EOM(even order missing) 구성으로 지칭될 수도 있음)을 분석할 수도 있다. 예를 들어, 도 6a 및 도 6b에 관하여 도시된 바와 같이, 클라이언트 디바이스는  $1 \times 4$  스폿 어레이 발생기에 대한 DOE의 요철 프로파일을 결정하도록 회절 이론 분석을 결정할 수도 있다. 이 경우에, DOE는 주기(620) 동안 요철 프로파일을 포함하며, 전이점(625)의 세트를 갖는다. 예를 들어, 전이점(625-1)은  $0dx$ 에 위치될 수도 있고, (625-2)는  $0.054dx$ 에 위치될 수도 있으며, (625-3)은  $0.277dx$ 에 위치될 수도 있고 그리고 (625-4)는  $0.5dx$ 에 위치될 수도 있으며, 여기서  $dx$ 는 주기(620)의 폭을 나타낸다. 일부 구현 예에서, 클라이언트 디바이스는 DOE를 포함하는 스폿 어레이 조명기에 대한 구성에 기초하여 전이점을 식별하는 정보를 수신할 수도 있다. 일부 구현 예에서, 클라이언트 디바이스는 스폿 어레이 조명기에 대한 구성에 기초하여 전이점을 자동으로 결정할 수도 있다. 또한 도 6a 및 도 6b에 관하여 도시된 바와 같이, 각각의 전이점은 요철 깊이 최소와 요철 깊이 최대 사이의 전이점, 그리고 위상 지연 최소(0)와 위상 지연 최대( $\pi$ ) 사이의 전이점에 대응한다.

[0049] 일부 구현 예에서, 클라이언트 디바이스는 전자기 회절 이론 분석을 수행할 수도 있다. 예를 들어, 클라이언트 디바이스는 빔의 횡-전기(transverse-electric: TE) 편극부와 빔의 횡-자기(transverse-magnetic: TM) 편극부

의 회절 효율을 결정할 수도 있다. TE 편극과 TM 편극에 대한 회절 효율이 제1 문턱값을 충족하는 것(즉, 제1 문턱값보다 크거나 또는 문턱값 이내, 예컨대, 연속적인 요철 프로파일 회절 효율의 10% 이내, 5% 이내, 2% 이내에 있는 등)에 기초하여 그리고 0 차수 회절 효율이 제2 문턱값을 충족하는 것(즉, 제2 문턱값 미만, 예컨대, 10% 미만, 5% 미만, 2% 미만에 있는 등)에 기초하여, 클라이언트 디바이스는 DOE를 위한 구성이 디자인 기준의 세트를 충족한다고 결정할 수도 있다.

[0051] 또한 도 5에 도시된 바와 같이, 과정(500)은 출력을 제공하는 단계(블록(540))를 포함할 수도 있다 예를 들어, 클라이언트 디바이스는 DOE의 제작을 가능하게 하도록 DOE에 대한 구성(예를 들어, 요철 프로파일)을 식별하는 출력을 제공할 수도 있다. 일부 구현예에서, 클라이언트 디바이스는 구성을 식별하는 출력을 저장할 수도 있고, DOE의 제작 등을 트리거링(trigger)하도록 구성을 식별하는 출력을 서버 디바이스에 제공할 수도 있다.

[0052] 도 5가 과정(500)의 예시적인 블록을 도시하지만, 일부 구현예에서, 과정(500)은 추가의 블록, 더 적은 블록, 상이한 블록 또는 도 5에 도시된 것과는 상이하게 배열된 블록을 포함할 수도 있다. 부가적으로 또는 대안적으로, 과정(500)의 블록 중 2개 이상은 동시에 수행될 수도 있다. 위에 나타낸 바와 같이, 도 6a 및 도 6b는 단지 실시예로서 제공된다. 다른 실시예가 가능하고 그리고 도 6a 및 도 6b에 관하여 설명된 것과는 상이할 수도 있다.

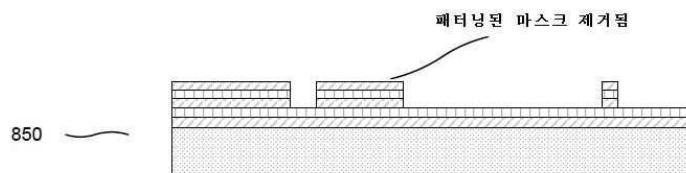

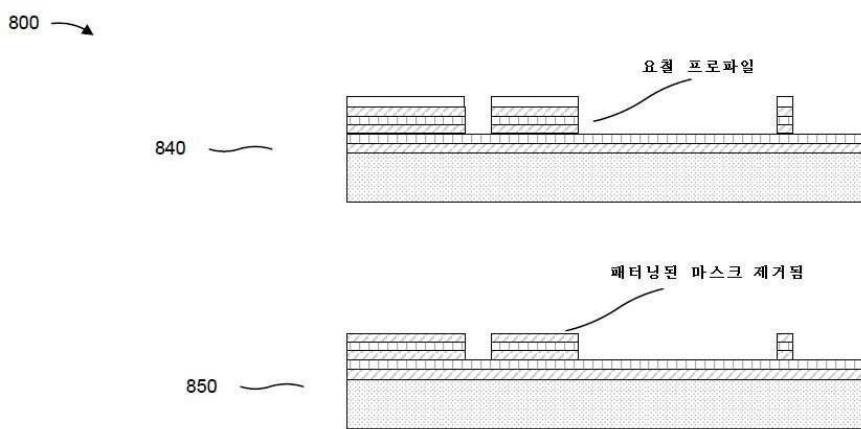

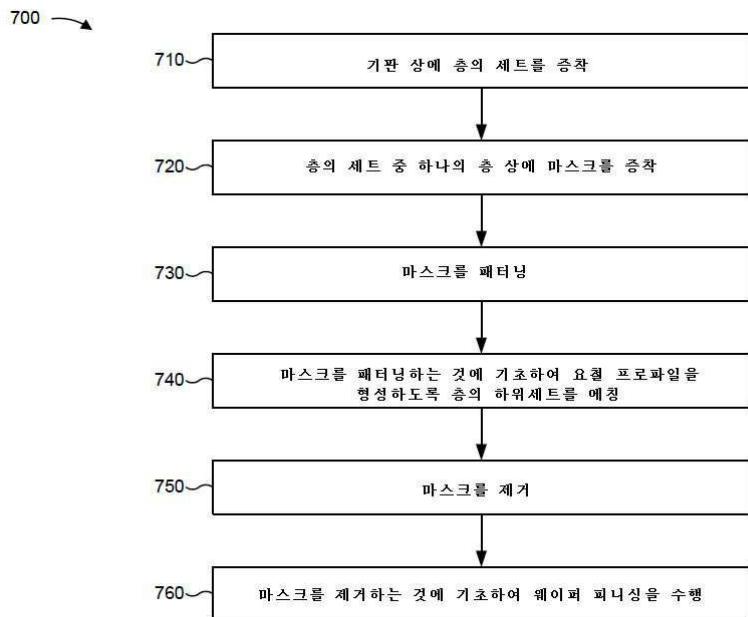

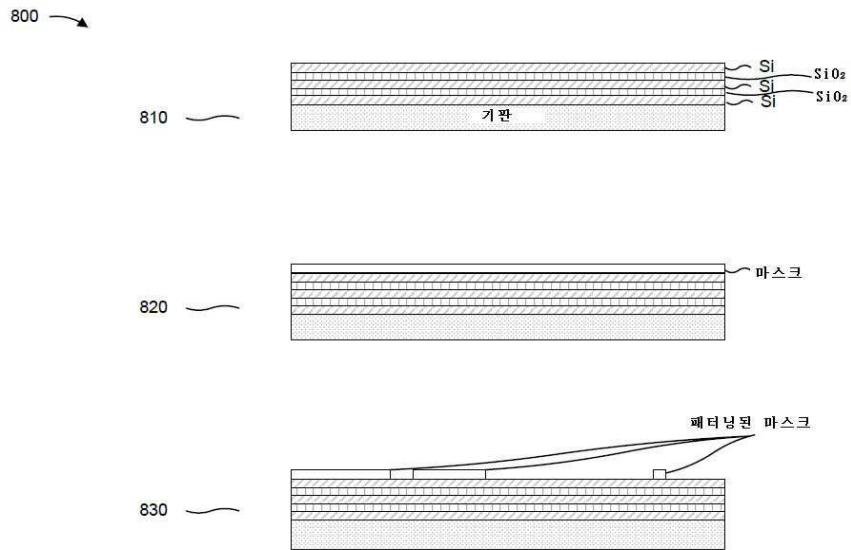

[0053] 도 7은 DOE를 제작하기 위한 예시적인 과정(700)의 흐름도이다. 도 8a 및 도 8b는 도 7에 도시된 예시적인 과정(700)에 관한 예시적인 구현예(800)의 도면이다.

[0054] 도 7에 도시된 바와 같이, 과정(700)은 기판 상에 층의 세트를 증착하는 단계(블록(710))를 포함할 수도 있다. 예를 들어, 도 8a에 관하여 그리고 참조 부호(810)로 도시된 바와 같이, 복수의 박막, 예컨대, 실리콘층과 이산화규소층의 세트는 특정한 파장에 대한 제1 반사-방지 구조체와 특정한 파장에 대한 제2 반사-방지 구조체를 증착하도록, 기판, 예컨대, 유리 기판 또는 용융 실리카 기판 상에 증착될 수도 있다. 일부 구현예에서, 층의 세트는 실리콘층과 이산화규소층의 제1 쌍, 실리콘층 및 기판 상에 증착된, 실리콘층과 이산화규소층의 제2 쌍을 포함할 수도 있다. 일부 구현예에서, 반사-방지 코팅은 기판이 반사-방지 코팅과, 교번하는 실리콘층과 이산화규소층 사이에 배치되도록, 기판의 또 다른 표면 상에 증착될 수도 있다. 일부 구현예에서, 반사-방지 구조체는 기판의 제1 측면과 기판의 제2 측면 상에 증착될 수도 있다. 일부 구현예에서, 재료의 또 다른 세트는 탄탈륨 오산화물계 재료, 실리콘 질화물계 재료 등과 같이, 층의 적어도 하나를 위해 사용될 수도 있다.

[0055] 또한 도 7에 도시된 바와 같이, 과정(700)은 층의 세트 중 하나의 층 상에 마스크를 증착하는 단계(블록(720))를 포함할 수도 있다. 예를 들어, 도 8a에 관하여 그리고 참조 부호(820)로 도시된 바와 같이, 마스크층은 마스크층이 실리콘층을 덮도록, 실리콘층과 이산화규소층의 제2 쌍 중 실리콘층 상에 증착될 수도 있다. 일부 구현예에서, 마스크를 위한 재료는 마스크가 실리콘 에칭 및 이산화규소 에칭에 대한 문턱값 선택적으로 또는 문턱값 저항률과 연관되도록 선택될 수도 있다.

[0056] 또한 도 7에 도시된 바와 같이, 과정(700)은 마스크를 패터닝하는 단계(블록(730))를 포함할 수도 있다. 예를 들어, 도 8a에 관하여 그리고 참조 부호(830)로 도시된 바와 같이, 마스크층은 DOE에 대한 구성에 기초하여 패터닝될 수도 있다. 이 경우에, 마스크층은 마스크가 도 4에 관하여, 에칭되지 않은 스택(430)에 대응하는 DOE의 부분을 덮고 그리고 도 4에 관하여 에칭된 스택(435)에 대응하는 DOE의 부분에서 제거되도록 패터닝될 수도 있다. 이 경우에, 마스크에 대한 패턴은 도 5에 관하여 본 명세서에 설명된 바와 같이, DOE를 구성하는 것에 기초하여 결정될 수도 있다. 예를 들어, 마스크는 DOE에 대한 결정된 전이점에 기초하여 패터닝된다.

[0057] 또한 도 7에 도시된 바와 같이, 과정(700)은 마스크를 패터닝하는 것에 기초하여 요철 프로파일을 형성하도록 층의 하위세트를 에칭하는 단계(블록(740))를 포함할 수도 있다. 예를 들어, 도 8b에 관하여 그리고 참조 부호(840)로 도시된 바와 같이, 패터닝된 마스크에 의해 덮이지 않은 층의 세트의 일부는 실리콘 에칭, 이산화규소 에칭 등을 사용하여 제거될 수도 있다. 이 경우에, 요철 프로파일은 층의 세트 중 하위세트에 형성된다. 일부 구현예에서, 에칭은 층의 전체 세트보다 적게 제거되도록 수행된다. 예를 들어, 도 4에 관하여, 에칭은 층(3 내지 5)의 부분을 제거하도록 수행된다. 이 경우에, (예를 들어, 층(2)의) 이산화규소는 DOE에 대한 에칭 정지 기능을 수행할 수도 있다.

[0058] 또한 도 7에 도시된 바와 같이, 과정(700)은 마스크를 제거하는 단계(블록(750))를 포함할 수도 있다. 예를 들어, 도 8b에 관하여 그리고 참조 부호(850)로 도시된 바와 같이, 마스크가 제거될 수도 있다. 이 경우에, 층의 세트는 층의 하위세트가 제거되는 DOE의 부분과 층의 하위세트가 제거되지 않은 DOE의 부분 사이의 π 위상 지연을 제공하도록 패터닝된 기판 상에 남아 있다.

- [0059] 또한 도 7에 도시된 바와 같이, 과정(700)은 마스크를 제거하는 것에 기초하여 웨이퍼 피니싱(wafer finishing)을 수행하는 단계(블록(760))를 포함할 수도 있다. 예를 들어, DOE는 테스트될 수도 있고, DOE는 다수의 별개의 DOE로 다이싱될 수도 있으며(예를 들어, 다수의 DOE가 패터닝되는 웨이퍼가 다수의 별개의 DOE로 다이싱될 수도 있음), 그리고 DOE는 광디바이스 내의 포함을 위해 포장될 수도 있다. 일부 구현예에서, 웨이퍼는 200mm × 0.725mm 웨이퍼일 수도 있다.

- [0060] 이 방식으로, 제작을 위한 단계의 수는 표면 요철 프로파일을 생성하도록 실리카 웨이퍼를 에칭, 반사-방지 코팅으로 표면 요철 프로파일을 코팅 등을 포함하는 또 다른 기법에 비해 반사-방지 박막 층으로 코팅되는 웨이퍼를 제공함으로써 감소된다. 또한, 단계의 수를 감소시키는 것에 기초하여, 비용, 공급망 어려움 등이 다른 기법에 비해 감소될 수도 있다.

- [0061] 도 7이 과정(700)의 예시적인 블록을 도시하지만, 일부 구현예에서, 과정(700)은 추가의 블록, 더 적은 블록, 상이한 블록 또는 도 7에 도시된 것과는 상이하게 배열된 블록을 포함할 수도 있다. 부가적으로 또는 대안적으로, 과정(700)의 블록 중 2개 이상은 동시에 수행될 수도 있다. 위에 나타낸 바와 같이, 도 8a 및 도 8b는 단지 실시예로서 제공된다. 다른 실시예가 가능하고 그리고 도 8a 및 도 8b에 관하여 설명된 것과는 상이할 수도 있다.

- [0062] 이 방식으로, 2-레벨 요철 프로파일로 에칭되는, 교변하는 실리콘층(예를 들어, 수소화된 실리콘층)과 이산화규소층을 포함하는 박막 스택을 가진 DOE가 디자인 및/또는 제작된다. 또한, DOE의 층은 반사-방지 성질, 통합적인 에칭 정지 성질 등을 제공하도록 디자인될 수도 있다. 또한, 디자인은 0 차수 전력을 제어할 수도 있는, 박막 과정 증착을 사용하여 수행될 수도 있다. 일부 구현예에서, DOE는 비-회절 이론 기반 계산 기법을 사용하여 디자인될 수도 있어서, DOE에 대한 디자인을 결정하는 처리 자원을 감소시킨다. 또한, 박막 증착 기법과 에칭 기법을 사용하는 것에 기초하여, DOE를 제작하기 위한 제작 단계의 수가 감소될 수도 있어서, DOE를 제작하기 위한 다른 기법에 비해 시간과 비용을 감소시킨다.

- [0063] 앞서 말한 개시내용이 예시 및 설명을 제공하지만, 총망라하거나 또는 구현예를 개시된 정확한 형태로 제한하고자 의도되지 않는다. 수정 및 변형이 위의 개시내용에 비추어 가능하거나 또는 구현예의 수행으로부터 획득될 수도 있다.

- [0064] 일부 구현예는 문턱값과 관련되어 본 명세서에 설명된다. 본 명세서에서 사용될 때, 문턱값을 충족하는 것은 값이 문턱값보다 크고, 문턱값보다 많고, 문턱값보다 높고, 문턱값 이상이고, 문턱값 미만이고, 문턱값보다 적고, 문턱값보다 낮고, 문턱값 이하이고, 문턱값과 같은 등임을 지칭할 수도 있다.

- [0065] 본 명세서에 설명된 시스템 및/또는 방법이 하드웨어, 펌웨어 또는 하드웨어와 소프트웨어의 조합의 상이한 형태로 구현될 수도 있다는 것이 분명할 것이다. 이 시스템 및/또는 방법을 구현하도록 사용되는 실제의 특수화된 제어 하드웨어 또는 소프트웨어 코드는 구현예를 제한하지 않는다. 따라서, 시스템 및/또는 방법의 작동 및 거동은 특정한 소프트웨어 코드의 참조 없이 본 명세서에 설명되고-소프트웨어 및 하드웨어는 본 명세서의 설명에 기초한 시스템 및/또는 방법을 구현하도록 디자인될 수 있다는 것이 이해된다.

- [0066] 피처의 특정한 조합이 청구항에 언급되고/되거나 명세서에 개시되지만, 이 조합은 가능한 구현예의 개시내용을 제한하고자 의도되지 않는다. 실제로, 이 피처 중 대다수는 특별히 청구항에 언급되고/되거나 명세서에 개시되지 않은 방식으로 조합될 수도 있다. 이하에 나열된 각각의 종속항이 단 하나의 청구항에 직접적으로 따를 수도 있지만, 가능한 구현예의 개시내용은 청구항 세트 내의 모든 다른 청구항과 조합하여 각각의 종속항을 포함한다.

- [0067] 본 명세서에 사용되는 구성요소, 행위 또는 명령은 달리 이와 같이 분명히 설명되지 않는 한 중요하거나 본질적인 것으로서 해석되어서는 안 된다. 또한, 본 명세서에서 사용될 때, 단수표현은 하나 이상의 항목을 포함하는 것으로 의도되고 그리고 "하나 이상"과 교환 가능하게 사용될 수도 있다. 또한, 본 명세서에서 사용될 때, 용어 "세트"는 하나 이상의 항목(예를 들어, 관련된 항목, 비관련된 항목, 관련된 항목과 비관련된 항목의 조합 등)을 포함하는 것으로 의도되고 그리고 "하나 이상"과 교환 가능하게 사용될 수도 있다. 단 하나의 항목을 의도하는 경우에, 용어 "하나" 또는 유사한 언어가 사용된다. 또한, 본 명세서에서 사용될 때, 용어 "갖는", "구비하는" 등은 개방형 용어인 것으로 의도된다. 또한, 어구 "기초하여"는 달리 명확히 언급되지 않는 한 "적어도 부분적으로 기초하여"를 의미하는 것으로 의도된다.

## 도면

## 도면1

## 도면2a

200 →

## 도면2b

250

### 도면3a

300

## 도면3b

350 ↗

## 도면4a

400 ↗

도면4b

400° ↗

도면4c

400° ↗

## 도면5

## 도면6a

## 도면6b

## 도면7

## 도면8a

## 도면8b