# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2023/0045336 A1 Yu et al.

# Feb. 9, 2023 (43) Pub. Date:

# (54) INTEGRATED DRY PROCESSES FOR PATTERNING RADIATION PHOTORESIST **PATTERNING**

(71) Applicant: Lam Research Corporation, Fremont, CA (US)

(72) Inventors: Jengyi Yu, San Ramon, CA (US); Samantha S.H. Tan, Newark, CA (US); Mohammed Haroon Alvi, San Jose, CA (US); Richard Wise, Los Gatos, CA (US); Yang Pan, Los Altos, CA (US); Richard Alan Gottscho, Menlo Park, CA (US); Adrien LaVoie, Newberg, OR (US); Sivananda Krishnan Kanakasabapathy, Pleasanton, CA (US); Timothy William Weidman, Sunnyvale, CA (US); Qinghuang Lin, Yorktown Heights, NY (US); Jerome S. Hubacek, Fremont, CA (US)

(21) Appl. No.: 17/758,125

PCT Filed: Jul. 2, 2021 (22)

PCT/US2021/040381 (86) PCT No.:

§ 371 (c)(1),

(2) Date: Jun. 28, 2022

#### Related U.S. Application Data

Provisional application No. 62/705,616, filed on Jul. 7, 2020.

#### **Publication Classification**

(51) Int. Cl. (2006.01)H01L 21/67 G03F 7/16 (2006.01)G03F 7/004 (2006.01)G03F 7/38 (2006.01)G03F 7/36 (2006.01)

(52)U.S. Cl.

> H01L 21/67225 (2013.01); G03F 7/167 CPC (2013.01); G03F 7/0042 (2013.01); G03F 7/38 (2013.01); H01L 21/67167 (2013.01); G03F 7/36 (2013.01)

#### (57)ABSTRACT

Methods for making thin-films on semiconductor substrates, may be patterned using EUV, include: depositing the organometallic polymer-like material onto the surface of the semiconductor substrate, exposing the surface to EUV to form a pattern, and developing the pattern for later transfer to underlying layers. The depositing operations may be performed by chemical vapor deposition (CVD), atomic layer deposition (ALD), and ALD with a CVD component, such as a discontinuous, ALD-like process in which metal precursors and counter-reactants are separated in either time or space.

FIG. 1

FIG. 3E

FIG. 5

FIG. 7

FIG. 8

FIG. 9

FIG. 12

FIG. 13B

# INTEGRATED DRY PROCESSES FOR PATTERNING RADIATION PHOTORESIST PATTERNING

#### INCORPORATED BY REFERENCE

[0001] A PCT Request Form is filed concurrently with this specification as part of the present application. Each application that the present application claims benefit of or priority to as identified in the concurrently filed PCT Request Form is incorporated by reference herein in its entirety and for all purposes.

#### BACKGROUND

[0002] The background description provided herein is for the purpose of generally presenting the context of the present technology. Work of the presently named inventors, to the extent it is described in this background section, as well as aspects of the description that may not otherwise qualify as prior art at the time of filing, are neither expressly nor impliedly admitted as prior art against the present technology.

[0003] The fabrication of semiconductor devices, such as integrated circuits, is a multi-step process involving photolithography. In general, the process includes the deposition of material on a wafer and patterning the material through lithographic techniques to form structural features (e.g., transistors and circuitry) of the semiconductor device. The steps of a typical photolithography process known in the art include: preparing the substrate; applying a photoresist, such as by spin coating; exposing the photoresist to light in a desired pattern, causing the exposed areas of the photoresist to become more or less soluble in a developer solution; developing by applying a developer solution to remove either the exposed or the unexposed areas of the photoresist; and subsequent processing to create features on the areas of the substrate from which the photoresist has been removed, such as by etching or material deposition.

[0004] The evolution of semiconductor design has created the need, and has been driven by the ability, to create ever smaller features on semiconductor substrate materials. This progression of technology has been characterized in "Moore's Law" as a doubling of the density of transistors in dense integrated circuits every two years. Indeed, chip design and manufacturing has progressed such that modern microprocessors may contain billions of transistors and other circuit features on a single chip. Individual features on such chips may be on the order of 22 nanometers (nm) or smaller, in some cases less than 10 nm.

[0005] One challenge in manufacturing devices having such small features is the ability to reliably and reproducibly create photolithographic masks having sufficient resolution. Current photolithography processes typically use 193 nm ultraviolet (UV) light to expose a photoresist. The fact that the light has a wavelength significantly greater than the desired size of the features to be produced on the semiconductor substrate creates inherent issues. Achieving feature sizes smaller than the wavelength of the light requires use of complex resolution enhancement techniques, such as multipatterning. Thus, there is significant interest and research effort in developing photolithographic techniques using shorter wavelength light, such as extreme ultraviolet radiation (EUV), having a wavelength of from 10 nm to 15 nm, e.g., 13.5 nm.

[0006] EUV photolithographic processes can present challenges, however, including low power output and loss of light during patterning. Traditional organic chemically amplified resists (CAR) similar to those used in 193 nm UV lithography have potential drawbacks when used in EUV lithography, particularly as they have low absorption coefficients in EUV region and the diffusion of photo-activated chemical species can result in blur or line edge roughness. Furthermore, in order to provide the etch resistance required to pattern underlying device layers, small features patterned in conventional CAR materials can result in high aspect ratios at risk of pattern collapse. Accordingly, there remains a need for improved EUV photoresist materials, having such properties as decreased thickness, greater absorbance, and greater etch resistance.

#### **SUMMARY**

[0007] Disclosed herein are methods and systems of an integrated process for forming a patterned photoresist. In one aspect of the embodiments disclosed herein, an integrated lithography system is provided, the system including: a plurality of reaction chambers within a cluster, the plurality of reaction chambers including: a photoresist (PR) deposition chamber, a post-application bake (PAB) chamber, a post-exposure bake (PEB) chamber, and a development chamber; and a controller that includes one or more processors and one or more memory devices, where the one or more memory devices store computer-executable instructions for controlling the one or more processors to: receive a substrate in the PR deposition chamber, deposit a PR on a surface of the substrate within the PR deposition chamber, receive the substrate having the PR in the PAB chamber, treat the PR within the PAB chamber to modify material properties of the PR, after treating the PR, receive the substrate in the PEB chamber, where portions of the PR have been chemically altered by exposure to radiation to create a patterned PR, treat the patterned PR within the PEB chamber to modify material properties of the patterned PR, and dry developing the patterned PR within the development chamber by removing either an exposed portion or an unexposed portion of the patterned PR by a dry development process including exposure to a chemical compound to form a PR mask.

[0008] In some embodiments, the PR may be a metalcontaining PR. In some embodiments, the PR may be an EUV PR. In some embodiments, the plurality of reaction chambers further includes a substrate clean chamber, and the computer-executable instructions further include instructions for controlling the one or more processors to, prior to the computer-executable instruction to receive the substrate having the PR in the PAB chamber: receive the substrate having the PR in the clean chamber and perform a dry clean process to remove PR from the bevel edge and/or backside of the substrate. In some embodiments, the plurality of reaction chambers further includes an underlayer deposition chamber, and the computer-executable instructions further include instructions for controlling the one or more processors to, prior to the computer-executable instruction to deposit a PR: deposit an underlayer on the surface of the substrate via a dry process, where the underlayer increases the adhesion of the PR to the substrate. In some embodiments, the underlayer deposition chamber may be the PR deposition chamber.

[0009] In some embodiments, the plurality of reaction chambers further includes a pre-treatment chamber, and the computer-executable instructions further include instructions for controlling the one or more processors to, prior to the computer-executable instruction to deposit a metal-containing PR: treat the surface of the substrate via a dry process to cause more exposed hydroxyl groups on the surface of the substrate. In some embodiments, the plurality of reaction chambers are each below atmospheric pressure, and the PR may be under below-atmospheric pressure until after the dry development process. In some embodiments, the ambient environment of the substrate may be controlled to reduce exposure of the photoresist to moisture prior to dry developing the patterned PR.

[0010] In some embodiments, the computer-executable instructions further include computer-executable instructions to deposit the PR via a dry process including mixing a vapor stream of an organometallic precursor with a vapor stream of a counter-reactant. In some embodiments, the processes performed by the plurality of reaction chambers are all dry processes. In some embodiments, the processes performed by the plurality of reaction chambers include wet and dry processes.

[0011] In some embodiments, the cluster includes multiple PR deposition chambers. In some embodiments, the PAB chamber and the PEB chamber are the same chamber. In some embodiments, the computer-executable instructions further include instructions for controlling the one or more processors to perform a dry clean process to remove PR from the bevel edge and/or backside of the substrate within the PAB chamber. In some embodiments, the plurality of reaction chambers further includes a lithography scanner, and the computer-executable instructions further include instructions for controlling the one or more processors to, prior to the computer-executable instruction to receive the substrate in the PEB chamber: receive the substrate in the lithography scanner and expose portions of the PR to radiation to create a patterned PR. In some embodiments, the plurality of substrate processing environments further includes a thermal treatment processing environment, and the one or more memory devices store further computerexecutable instructions for controlling the one or more processors to: before and/or after portions of the metalcontaining PR have been chemically altered by exposure to radiation to create a patterned PR, thermally treat the metalcontaining PR within the thermal treatment processing environment.

[0012] In another aspect of the embodiments disclosed herein, an integrated substrate processing system is provided, the system including: a plurality of substrate processing environments, the plurality of substrate processing environments comprising a metal-containing photoresist (PR) deposition environment and one or more other separate integrated processing environments selected from the group consisting of: an additional metal-containing photoresist (PR) deposition environment; a metal-containing PR development environment, and a thermal treatment processing environment; and a controller that includes one or more processors and one or more memory devices, wherein the one or more memory devices store computer-executable instructions for controlling the one or more processors to: receive a substrate in the metal-containing PR deposition environment; deposit a metal-containing PR on a surface of the substrate within the metal-containing PR deposition environment; and conduct additional PR processing operations in the one or more other separate integrated processing environments.

[0013] In some implementations, the plurality of substrate processing environments further includes a PR dry development processing environment, and the one or more memory devices store further computer-executable instructions for controlling the one or more processors to: after portions of the metal-containing PR have been chemically altered by exposure to radiation to create a patterned PR, dry develop the patterned PR within the development environment by removing either an exposed portion or an unexposed portion of the patterned PR by a dry development process including exposure to a chemical compound to form a PR mask. In some implementations, the plurality of substrate processing environments further includes a scanner environment, and the one or more memory devices store further computer-executable instructions for controlling the one or more processors to: expose portions of the metalcontaining PR to radiation within the scanner environment to chemically alter the exposed portions.

[0014] In some implementations, the plurality of substrate processing environments are different process chambers within a cluster. In some implementations, the plurality of substrate processing environments are different stations within a chamber. In some implementations, the plurality of substrate processing environments includes three metal-containing PR deposition environments. In some implementations, the plurality of substrate processing environments includes two metal-containing PR deposition environments and a metal-containing PR development environment, and the one or more memory devices store further computer-executable instructions for controlling the one or more processors to: after portions of the metal-containing PR have been chemically altered by exposure to radiation to create a patterned PR, develop the patterned PR via a dry process.

[0015] In some implementations, the plurality of substrate processing environments includes a metal-containing PR deposition environments, a thermal treatment processing environment, and a metal-containing PR development environment, and the one or more memory devices store further computer-executable instructions for controlling the one or more processors to: before and/or after portions of the metal-containing PR have been chemically altered by exposure to radiation to create a patterned PR, thermally treat the metal-containing PR within the thermal treatment processing environment and after thermally treating the metalcontaining PR within the thermal treatment processing environment, developing the patterned PR via a dry process. In some implementations, the plurality of substrate processing environments includes a metal-containing PR deposition environments, a first thermal treatment processing environment, a second thermal treatment processing environment, and a metal-containing PR development environment, and the one or more memory devices store further computerexecutable instructions for controlling the one or more processors to: before portions of the metal-containing PR have been chemically altered by exposure to radiation to create a patterned PR, thermally treat the metal-containing PR within the first thermal treatment processing environment, after portions of the metal-containing PR have been chemically altered by exposure to radiation to create a patterned PR, thermally treat the metal-containing PR within the second thermal treatment processing environment, and after thermally treating the metal-containing PR within the second thermal treatment processing environment, developing the patterned PR via a dry process.

[0016] These and other features of the disclosed embodiments will be described in detail below with reference to the associated drawings.

# BRIEF DESCRIPTION OF DRAWINGS

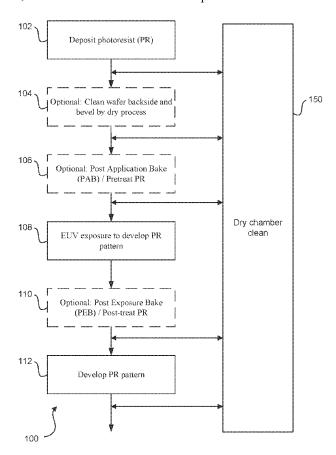

[0017] FIG. 1 presents a process flow diagram for one example embodiment.

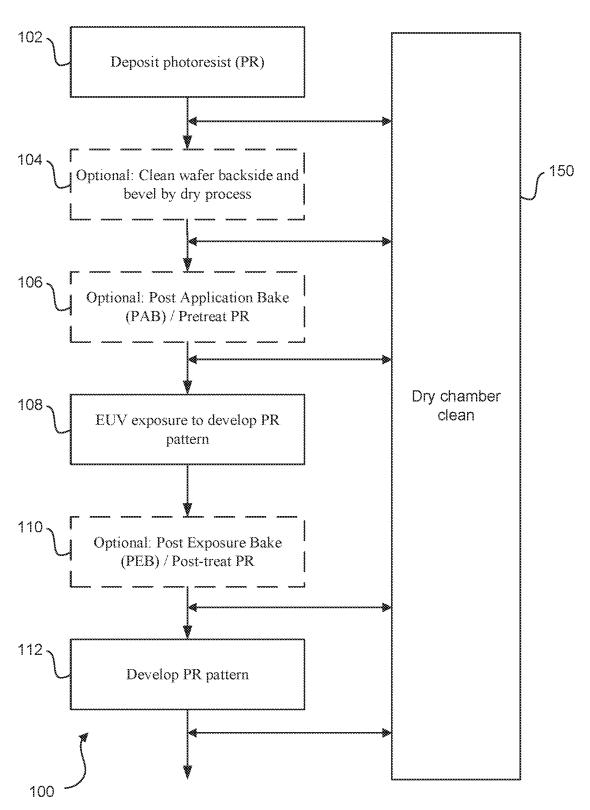

[0018] FIG. 2 presents an exemplary chemical reaction scheme of the present technology.

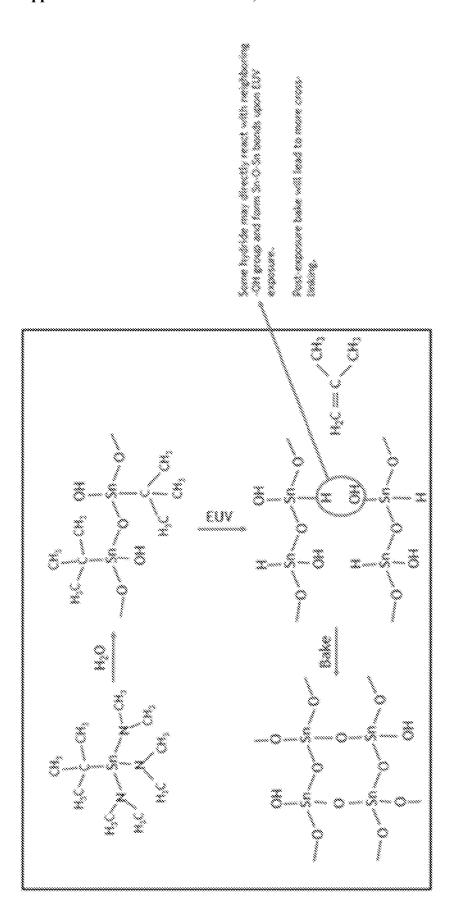

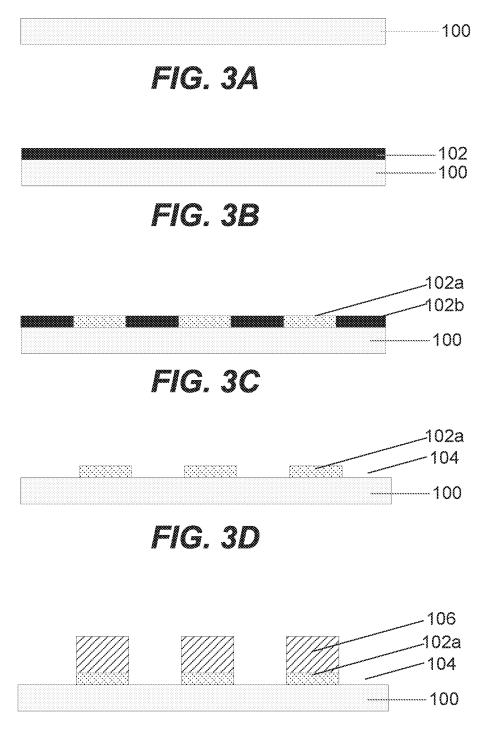

[0019] FIGS. 3A-E illustrate a representative process flow for an example embodiment.

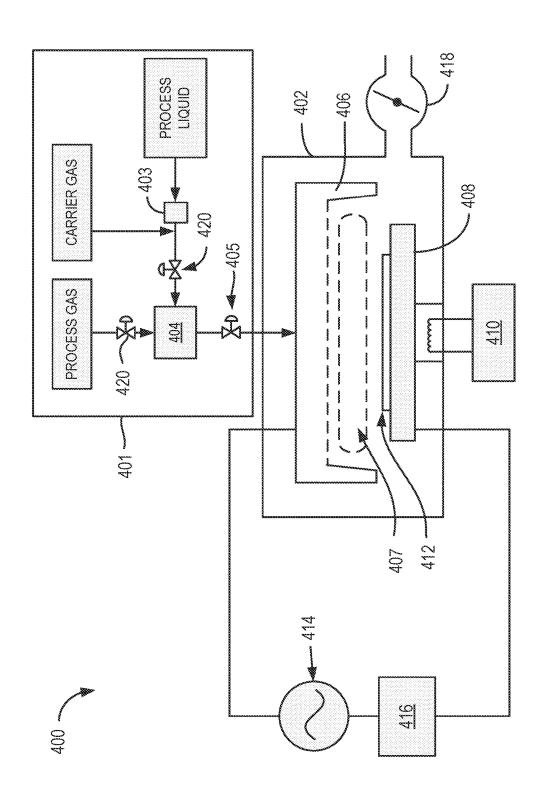

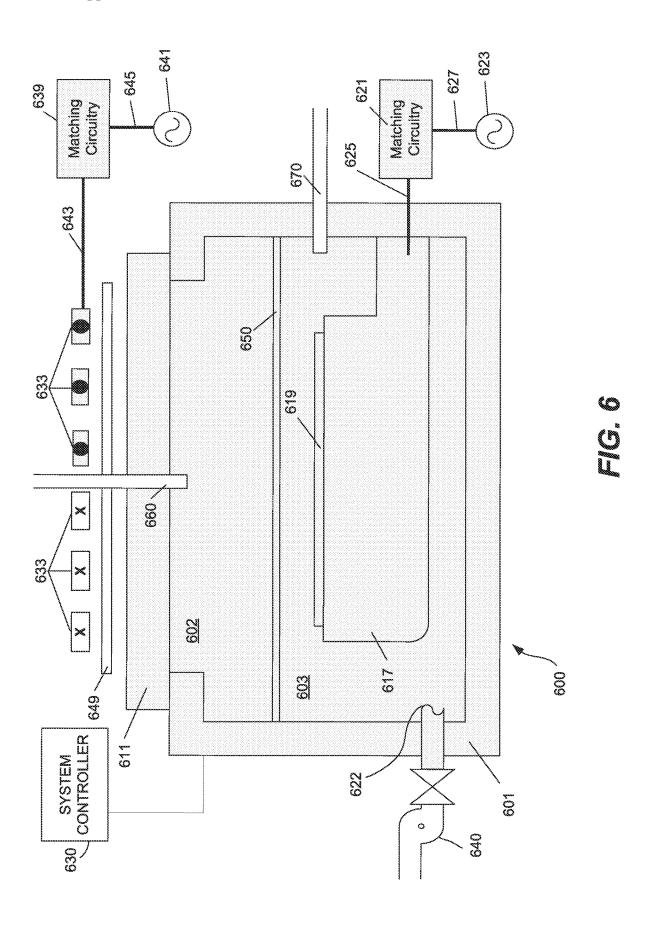

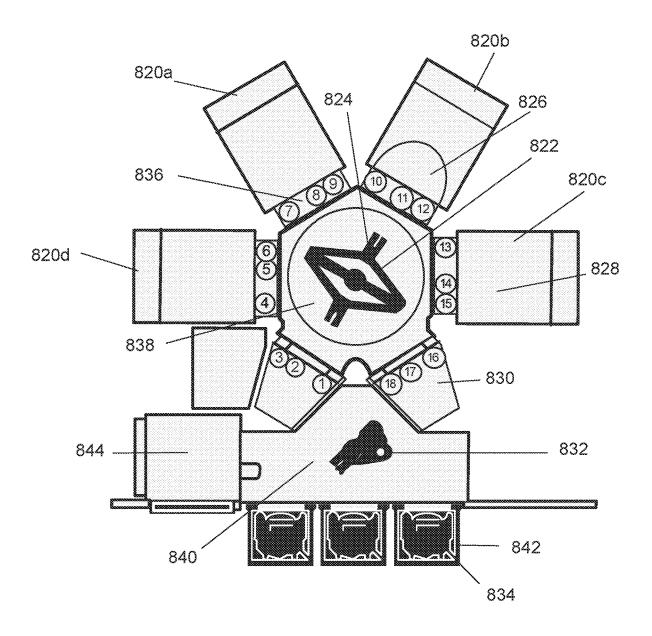

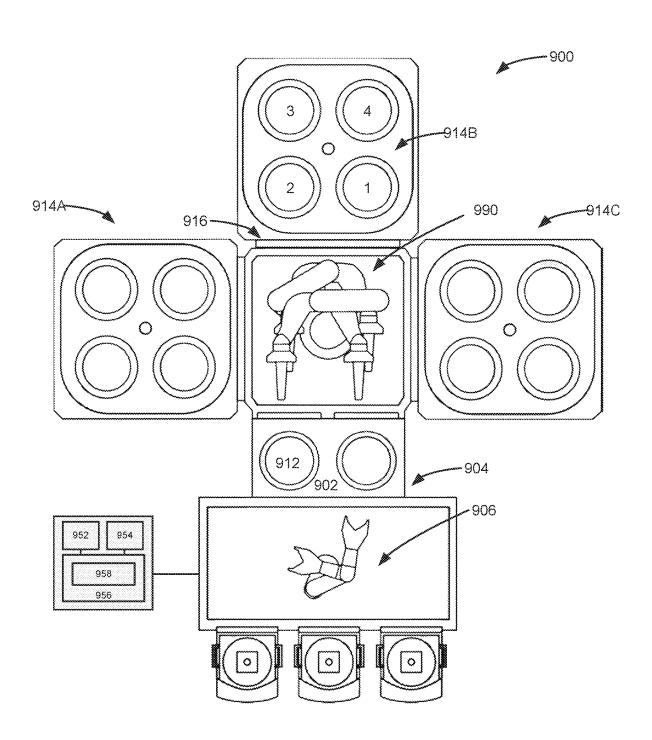

[0020] FIGS. 4-9 are schematic diagrams of examples of process chambers for performing methods in accordance with disclosed embodiments.

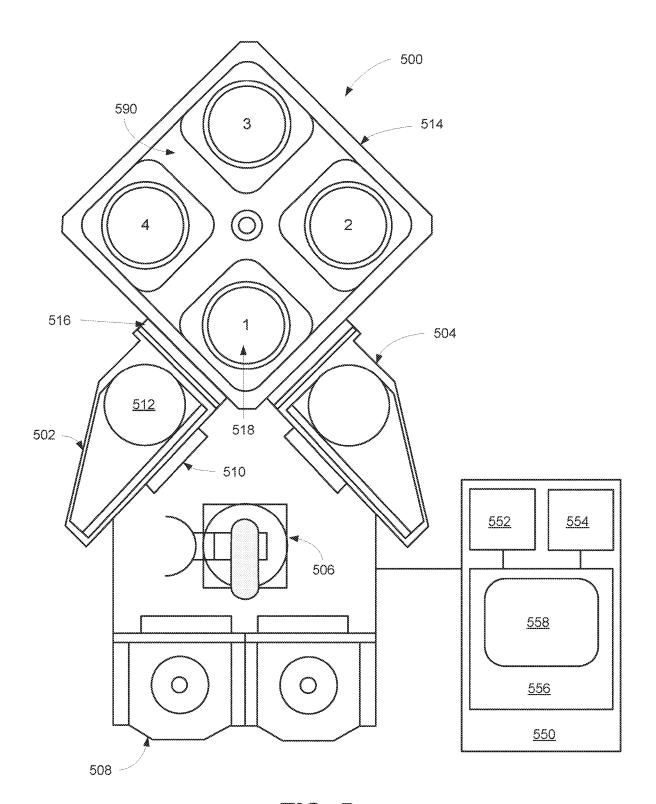

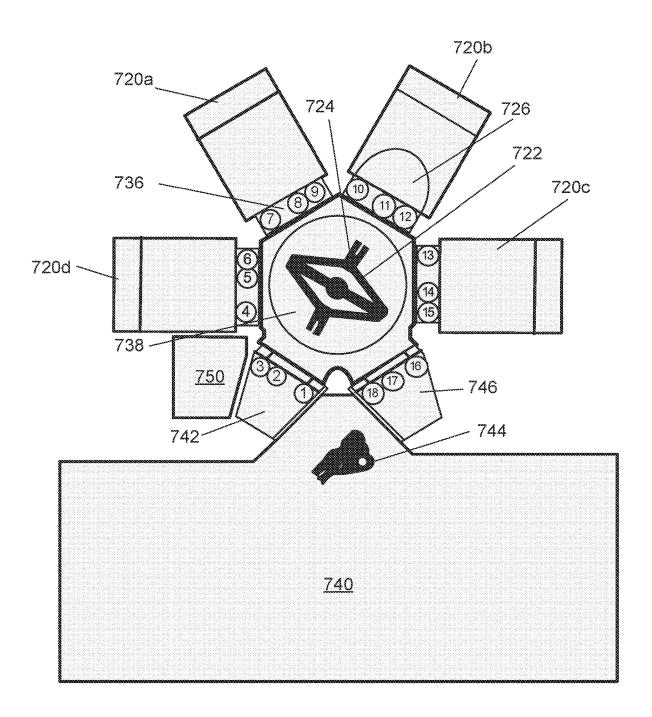

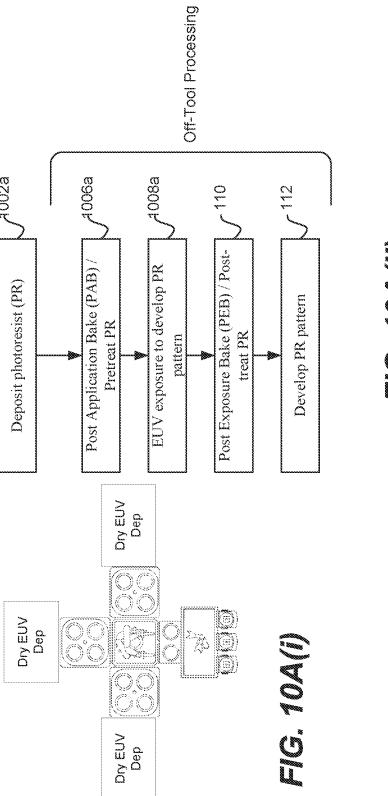

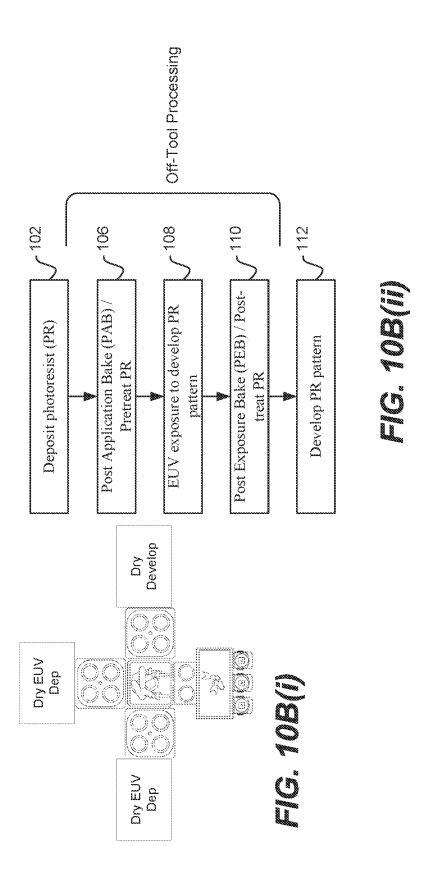

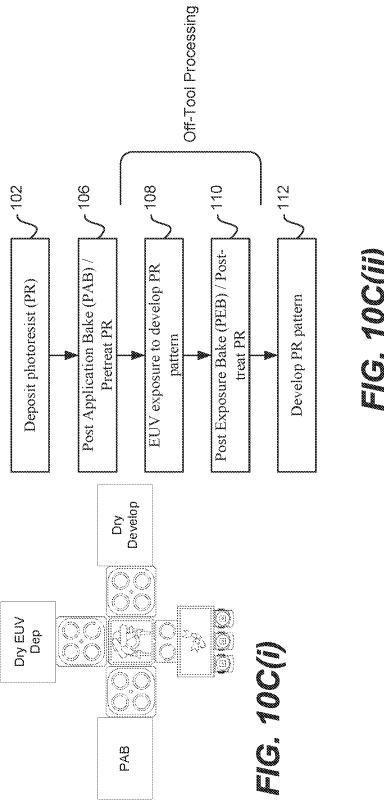

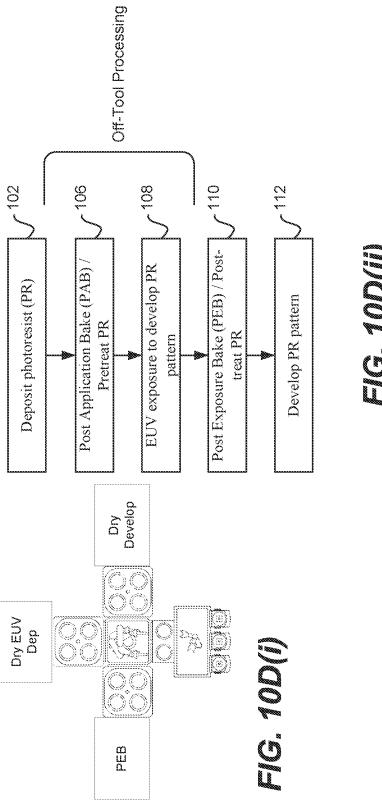

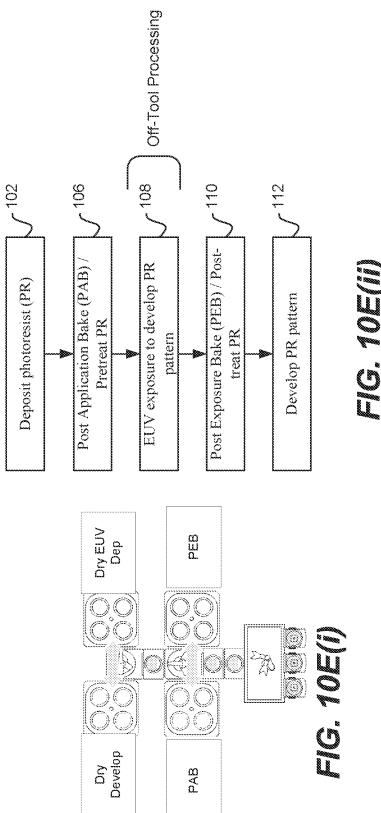

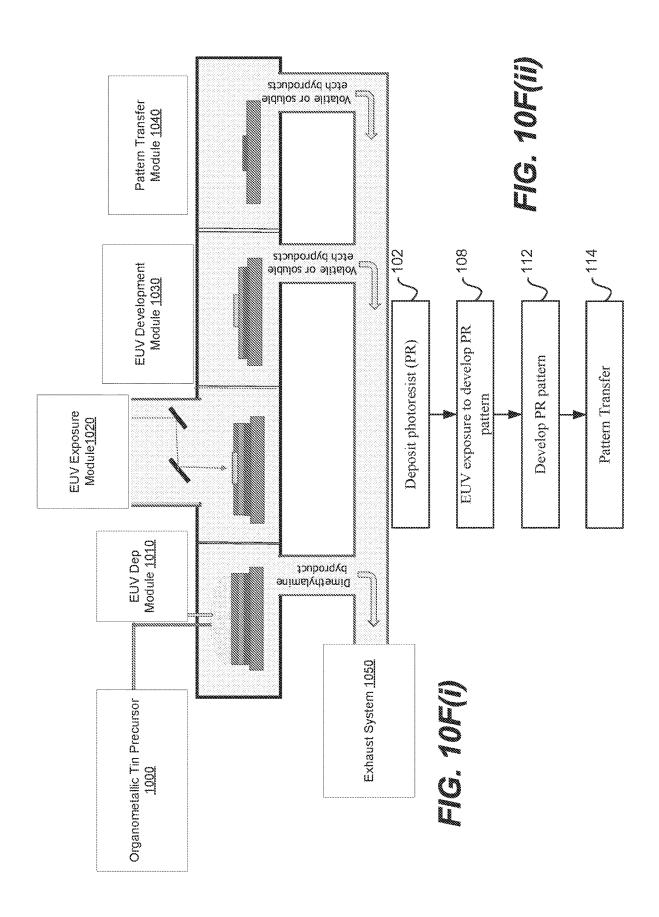

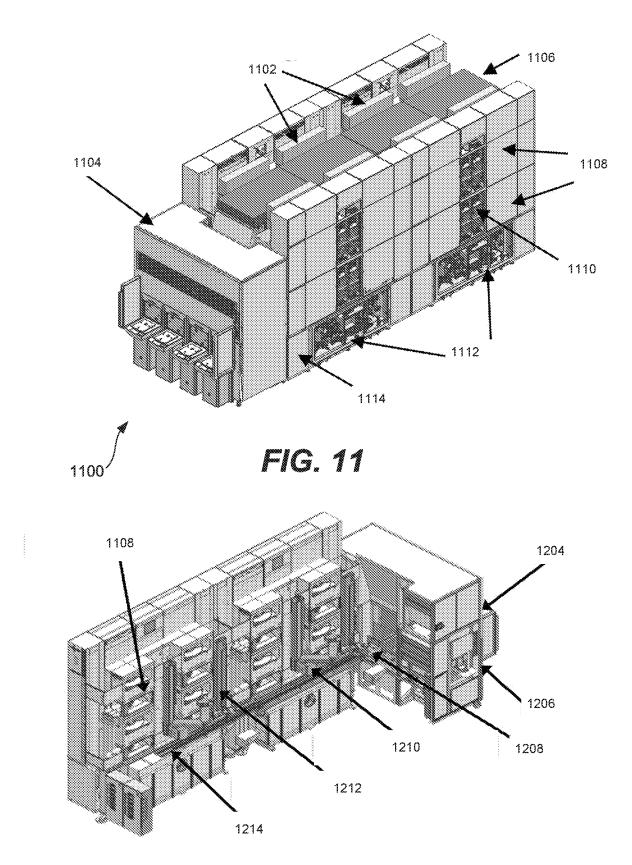

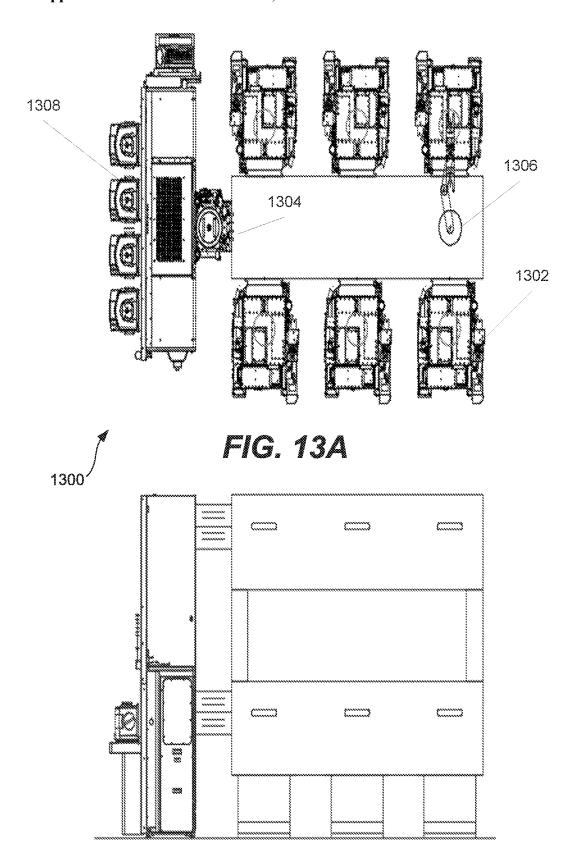

[0021] FIGS. 10A-F present schematic diagrams of various process cluster configurations in accordance with disclosed embodiments.

[0022] FIGS. 11-12 and 13A-B present various example tool architectures that may be used to perform methods in accordance with disclosed embodiments.

#### DETAILED DESCRIPTION

[0023] This disclosure relates generally to the field of semiconductor processing. In particular aspects, the disclosure is directed to methods and apparatus for processing of EUV photoresists (e.g., EUV-sensitive metal and/or metal oxide-containing resist films) in the context of EUV patterning and EUV patterned film development to form a patterning mask.

[0024] Reference is made herein in detail to specific embodiments of the disclosure. Examples of the specific embodiments are illustrated in the accompanying drawings. While the disclosure will be described in conjunction with these specific embodiments, it will be understood that it is not intended to limit the disclosure to such specific embodiments. On the contrary, it is intended to cover alternatives, modifications, and equivalents as may be included within the spirit and scope of the disclosure. In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present disclosure. The present disclosure may be practiced without some or all of these specific details. In other instances, well known process operations have not been described in detail so as to not unnecessarily obscure the present disclosure.

[0025] Patterning of thin films in semiconductor processing is often an important step in the fabrication of semiconductors. Patterning involves lithography. In conventional photolithography, such as 193 nm photolithography, patterns are printed by emitting photons from a photon source onto a mask and printing the pattern onto a photosensitive photoresist, thereby causing a chemical reaction in the photoresist that, after development, removes certain portions of the photoresist to form the pattern.

[0026] Advanced technology nodes (as defined by the International Technology Roadmap for Semiconductors) include nodes 22 nm, 16 nm, and beyond. In the 16 nm node, for example, the width of a typical via or line in a Damascene structure is typically no greater than about 30 nm.

Scaling of features on advanced semiconductor integrated circuits (ICs) and other devices is driving lithography to improve resolution.

[0027] Extreme ultraviolet (EUV) lithography can extend lithography technology by moving to smaller imaging source wavelengths than would be achievable with conventional photolithography methods. EUV light sources at approximately 10-20 nm, or 11-14 nm wavelength, for example 13.5 nm wavelength, can be used for leading-edge lithography tools, also referred to as scanners. The EUV radiation is strongly absorbed in a wide range of solid and fluid materials including quartz and water vapor, and so operates in a vacuum.

[0028] EUV lithography makes use of EUV resists that are patterned to form masks for use in etching underlying layers. EUV resists may be polymer-based chemically amplified resists (CARs) produced by liquid-based spin-on techniques. An alternative to CARs are directly photopatternable metal oxide-containing films, such as those available from Inpria, Corvallis, OR, and described, for example, in US Patent Publications US 2017/0102612, US 2016/021660 and US 2016/0116839, incorporated by reference herein at least for their disclosure of photopatternable metal oxide-containing films. Such films may be produced by spin-on techniques or dry vapor-deposited. The metal oxide-containing film can be patterned directly (i.e., without the use of a separate photoresist) by EUV exposure in a vacuum ambient providing sub-30 nm patterning resolution, for example as described in U.S. Pat. No. 9,996,004, issued Jun. 12, 2018 and titled EUV PHOTOPATTERNING OF VAPOR-DEPOSITED METAL OXIDE-CONTAINING HARDMASKS, and/or in Application PCT/US19/31618, filed May 9, 2019, and titled METH-ODS FOR MAKING EUV PATTERNABLE HARD MASKS, the disclosures of which at least relating to the composition, deposition, and patterning of directly photopatternable metal oxide films to form EUV resist masks is incorporated by reference herein. Generally, the patterning involves exposure of the EUV resist with EUV radiation to form a photo pattern in the resist, followed by development to remove a portion of the resist according to the photo pattern to form the mask.

[0029] It should also be understood that the while present disclosure relates to lithographic patterning techniques and materials exemplified by EUV lithography, it is also applicable to other next generation lithographic techniques. In addition to EUV, which includes the standard 13.5 nm EUV wavelength currently in use and development, the radiation sources most relevant to such lithography are DUV (deep-UV), which generally refers to use of 248 nm or 193 nm excimer laser sources, X-ray, which formally includes EUV at the lower energy range of the X-ray range, as well as e-beam, which can cover a wide energy range. The specific methods may depend on the particular materials and applications used in the semiconductor substrate and ultimate semiconducting device. Thus, the methods described in this application are merely exemplary of the methods and materials that may be used in present technology.

[0030] Directly photopatternable EUV resists may be composed of or contain metals and/or metal oxides mixed within organic components. The metals/metal oxides are highly promising in that they can enhance the EUV photon adsorption and generate secondary electrons and/or show increased etch selectivity to an underlying film stack and device layers. To date, these resists have been developed

using a wet (solvent) approach, which requires the wafer to move to the track, where it is exposed to developing solvent, dried and baked. Wet development does not only limit productivity but can also lead to line collapse due to surface tension effects during the evaporation of solvent between fine features.

[0031] Dry development techniques have been proposed to overcome these issues by eliminating substrate delamination and interface failures. Dry development has its own challenges, including etch selectivity between unexposed and EUV exposed resist material which can lead to a higher dose to size requirement for effective resist exposure when compared to wet development. Suboptimal selectivity can also cause PR corner rounding due to longer exposures under etching gas, which may increase line critical dimension (CD) variation in the following transfer etch step.

[0032] FIG. 1 presents a flow diagram of an example method for performing a dry chamber clean when depositing and developing a photoresist according to some embodiments. The operations of a process 100 may be performed in different orders and/or with different, fewer, or additional operations. One or more operations of the process 100 may be performed using various apparatuses described herein. In some embodiments, the operations of the process 100 may be implemented, at least in part, according to software stored in one or more non-transitory computer readable media.

[0033] At block 102 of the process 100, a layer of photoresist is deposited. This may be either a dry deposition process such as a vapor deposition process or a wet process such as a spin-on deposition process. The photoresist can be an EUV resist or metal-containing EUV rests. FIG. 2 presents an exemplary process by which a polymerized organometallic material may be formed to deposit a metal-containing EUV resist.

[0034] Returning to FIG. 1, in addition to depositing a metal-containing EUV resist thin film on a semiconductor substrate at block 102 of the process 100, metal-containing EUV resist material may be formed on internal surfaces of the process chamber. The internal surfaces may include chamber walls, floors, and ceilings of the process chamber. Other internal surfaces may include a showerhead, nozzles, and substrate support surfaces. The metal-containing EUV resist material may form as a result of dry deposition processes, such as CVD or ALD processes. A thickness of the metal-containing EUV resist material formed on the internal surfaces may increase over time as a result of additional processing (e.g., deposition) operations being performed in the process chamber. The metal-containing EUV resist material is prone to flake off, shed particles, or peel from the internal surfaces of the process chamber to contaminate subsequent semiconductor substrates during processing.

[0035] At block 150 of the process 100, a dry chamber clean operation of the present disclosure may be performed after deposition of the metal-containing EUV resist thin film on the semiconductor substrate at block 102 of the process 100. This allows for deposition and dry cleaning to be performed in the same process chamber. However, it will be understood that the dry chamber clean may be performed in a different process chamber than the deposition operation in embodiments. In fact, the dry chamber clean may be performed subsequent to a bevel and/or backside clean, bake, development, or etch operation.

[0036] The dry-deposited metal-containing EUV photoresist films being removed are generally composed of Sn, O and C, but the same clean approaches can be extended to films of other metal oxide resists and materials. In addition, this approach can also be used for film strip and PR rework. [0037] At block 104 of the process 100, an optional cleaning process is performed to clean a backside and/or bevel edge of the semiconductor substrate. The backside and/or bevel edge clean may non-selectively etch EUV resist film to equally remove film with various levels of oxidation or crosslinking on the substrate backside and bevel edge. During application of the EUV-patternable film, either by wet deposition processing or dry deposition processing, there may be some unintended deposition of resist material on the substrate bevel edge and/or backside. The unintended deposition may lead to undesirable particles later moving to a top surface of the semiconductor substrate and becoming particle defects. Moreover, this bevel edge and backside deposition can cause downstream processing problems, including contamination of the patterning (scanner) and development tools. Conventionally, removal of this bevel edge and backside deposition is done by wet cleaning techniques. For spin-coated photoresist material, this process is called edge bead removal (EBR) and is performed by directing a stream of solvent from above and below the bevel edge while the substrate is spinning. The same process can be applied to soluble organotin oxide-based resists deposited by vapor deposition techniques. The substrate bevel edge and/or backside clean may also be a dry clean process.

[0038] At block 150 of the process 100, a dry chamber clean operation of the present disclosure may be performed after a bevel edge and/or backside clean operation. This allows for bevel and/or backside clean and dry chamber clean to be performed in the same process chamber. However, it will be understood that the dry chamber clean may be performed in a different process chamber than the bevel edge and/or backside clean operation in some embodiments. [0039] At block 106 of the process 100, an optional post-application bake (PAB) is performed after deposition of the EUV-patternable film and prior to EUV exposure. The PAB treatment may involve a combination of thermal treatment, chemical exposure, and moisture to increase the EUV sensitivity of the EUV-patternable film, reducing the EUV dose to develop a pattern in the EUV-patternable film.

[0040] At block 150 of the process 100, a dry chamber clean operation of the present disclosure may be performed after a PAB treatment. This allows for bake and dry chamber clean to be performed in the same process chamber. However, it will be understood that the dry chamber clean may be performed in a different process chamber than the PAB treatment operation in some embodiments.

[0041] At block 108 of the process 100, the metal-containing EUV resist film is exposed to EUV radiation to develop a pattern. Generally speaking, the EUV exposure causes a change in the chemical composition and cross-linking in the metal-containing EUV resist film, creating a contrast in etch selectivity that can be exploited for subsequent development. Following exposure of the metal-containing EUV resist film to EUV light, a photopatterned metal-containing EUV resist is provided. The photopatterned metal-containing EUV resist includes EUV-exposed and unexposed regions.

[0042] At block 110 of the process 100, an optional post-exposure bake (PEB) is performed to further increase

contrast in etch selectivity of the photopatterned metal-containing EUV resist. The photopatterned metal-containing EUV resist can be thermally treated in the presence of various chemical species to facilitate cross-linking of the EUV-exposed regions of the photopatterned metal-containing EUV resist or simply baked on a hot plate in ambient air.

[0043] At block 150 of the process 100, a dry chamber clean operation of the present disclosure may be performed after a PEB treatment. This allows for bake and dry chamber clean to be performed in the same process chamber. However, it will be understood that the dry chamber clean may be performed in a different process chamber than the PEB treatment operation in some embodiments.

[0044] At block 112 of the process 100, the photopatterned metal-containing resist is developed to form a resist mask. In various embodiments, the exposed regions are removed (positive tone) or the unexposed regions are removed (negative tone). In some embodiments, development may include selective deposition on either the exposed or unexposed regions of the photopatterned metal-containing resist, followed by an etching operation. In various embodiments, these processes may be dry processes or wet processes. Examples of processes for development involve an organotin oxide-containing EUV-sensitive photoresist thin film (e.g., 10-30 nm thick, such as 20 nm), subjected to a EUV exposure dose and post-exposure bake, and then developed. The photoresist film may be, for example, deposited based on a gas phase reaction of an organotin precursor such as isopropyl(tris)(dimethylamino)tin and water vapor, or may be a spin-on film comprising tin clusters in an organic matrix. The photopatterned metal-containing resist is developed by exposure to a development chemistry. In some embodiments, the development chemistry includes a halidecontaining chemistry.

[0045] At block 150 of the process 100, a dry chamber clean operation of the present disclosure may be performed after development. This allows for development and dry chamber clean to be performed in the same process chamber. However, it will be understood that the dry chamber clean may be performed in a different process chamber than the development operation in some embodiments. Moreover, it will be understood that the dry chamber clean may be performed in the same or different process chamber than an etch operation in some embodiments. The etch operation may be applied to etch a substrate underlayer of the semi-conductor substrate.

[0046] Each of operations 102-112 is further elucidated below. In various embodiments, methods of the present technology combine all dry steps of film formation by vapor deposition, (EUV) lithographic photopatterning and dry development. In other embodiments, methods of the present technology include a wet deposition and a dry development, or a dry deposition and a wet development. In some processes, a substrate may directly go to a dry development/etch chamber following photopatterning in an EUV scanner. Such processes may avoid material and productivity costs associated with a wet development. Alternatively, a post exposure bake step during which the exposed regions undergo further crosslinking to form a denser SnO-like network may be conducted in the development chamber, or another chamber.

[0047] In some embodiments, a substrate may be provided to various processing environments to perform each of

operations 102-112. For example, there may be a PR deposition environment, one or more thermal treatment environments for PAB and/or

[0048] PEB, a wafer cleaning environment, a scanning environment, and a PR development environment. As will be described below, in some embodiments one or more of these environments may be a station/pedestal within a chamber, a chamber having one or more pedestals, and/or a multi-chamber cluster tool having one or more chambers. In some embodiments, multiple operations may be performed in a single processing environment, e.g., a thermal treatment environment and a wafer cleaning environment may be the same processing environment, where both operations may be performed sequentially without moving the wafer to a different pedestal, chamber, or tool. In some embodiments, multiple processing environments may be within the same chamber or tool, e.g., a thermal treatment environment and a wafer cleaning environment may be at different stations within a quad-station module chamber. In some embodiments, a plurality of processing environments of the same type may be provided in the same tool, for example to enhance or optimize throughput in situations when one processing operation is much slower than another in a multi-operation wafer processing. Other combinations of the above-defined environments should be understood to be within the scope of this disclosure.

[0049] Without limiting the mechanism, function or utility of present technology, dry processes of the present technology may provide various benefits relative to wet development processes among those known in the art. For example, dry vapor deposition techniques described herein can be used to deposit thinner and more defect free films than can be applied using wet spin-coating techniques, and that the exact thickness of the deposited film can be modulated and controlled simply by increasing or decreasing the length of the deposition step or sequence. Accordingly, a dry process may provide more tunability and give further critical dimension (CD) control and scum removal. Dry development can improve performance (e.g., prevent line collapse due to surface tension in wet development) and enhance throughput (e.g., by avoiding wet development track). Other advantages may include eliminating the use of organic solvent developers, reduced sensitivity to adhesion issues, avoiding the need to apply and remove wet resist formulations (e.g., avoiding scumming and pattern distortion), improving line edge roughness, patterning directly over device topography, offering the ability to tune hardmask chemistry to the specific substrate and semiconductor device design, and a lack of other solubility-based limitations.

[0050] In some instances, a combination of wet and dry processing may be suitable or optimal, such as where substantial capital investment has been made in wet processing wafer processing apparatus whose performance can be enhanced by integrated dry processing and associated apparatus for some operations in a multi-operation process.

[0051] Therefore, this disclosure provides processes and apparatus configured for dry development of an EUV-photopatterned metal and/or metal oxide-containing resist as part of a EUV resist mask formation process. Various embodiments include combining all dry operations of film formation by vapor deposition, (EUV) lithographic photopatterning, and dry development. Various other embodiments include dry processing operations described herein advantageously combined with wet processing operations,

for example, spin-on EUV photoresists (wet process), such as available from Inpria Corp., may be combined with dry development or other wet or dry processes as described herein. In various embodiments, the wafer clean may be a wet process as described herein, while other processes are dry processes. In further embodiments, a wet development process may be used in combination with (dry) vapor deposition of a PR film.

### Lithographic Processing

[0052] FIGS. 3A-E illustrate another representative process flow for a metal photoresist hardmask formation process. Generally, a metal-containing film that is sensitive to a patterning agent such as photons, electrons, protons, ions or neutral species, such that the film can be patterned by exposure to one of these species, is deposited on a semiconductor substrate. The metal-containing film is then patterned by exposure to the patterning agent in a vacuum ambient to form the metal mask. This description references primarily metal-containing films, particularly where the metal is Sn, that are patterned by extreme ultraviolet lithography (EUV lithography (EUVL)), particularly EUVL having an EUV source which uses excited Sn droplets. Such films are referred to herein as EUV-sensitive films. However, it should be understood that other implementations are possible, including different metal-containing films and patterning agents/techniques.

[0053] Referring to FIG. 3A, a semiconductor substrate to be patterned 100 is shown. In a typical example, the semiconductor substrate 100 is a silicon wafer including partially-formed integrated circuits.

[0054] FIG. 3B illustrates a metal-containing film 102 that is sensitive to a patterning agent deposited on the semiconductor substrate 100. The metal-containing film may be a metal salt, for example a metal halide, or an organometallic compound sensitive to exposure to a patterning agent such that the metal-containing film gets decomposed to the base metal or is rendered sensitive to a subsequent development process. Suitable patterning agents may be photons, electrons, protons, ions or neutral species, such that the metal-containing film 102 can be patterned by exposure to one of these species by decomposition to the base metal or is rendered sensitive to a subsequent development process. In general, prior to the deposition, the semiconductor substrate 100 is placed in a reactor chamber for metal-containing film deposition under vacuum.

[0055] A blanket of the metal-containing film 102 can be formed by condensation from a suitable precursor (e.g., in a non-plasma CVD reactor, such as an Altus® CVD tool or an Aether® GP CVD tool, available from Lam Research Corporation, Fremont, Calif.). Suitable process conditions for this deposition via condensation include a deposition temperature between about 0 and 250° C., for example about from ambient temperature (e.g., 23° C.) to 150° C., and a reactor pressure of less than 20 Torr, for example maintained between 0.5 and 2 Torr at 60° C. Maintaining the precursor flow rate between about 100 and 1000 sccm allows for control of the deposition rate.

[0056] To prevent degradation due to water vapor, formation and transfer of the Sn-containing films is conducted in a vacuum-ambient. The formed film is then transferred to a EUV patterning tool and patterned via direct exposure, without the use of a photoresist, as illustrated in FIGS. 3C-D.

[0057] It should be noted that a EUVL tool typically operates at a higher vacuum than a deposition tool. If this is the case, it is desirable to increase the vacuum environment of the substrate during the transfer from the deposition to the patterning tool to allow the substrate and deposited metal-containing film to degas prior to entry into the patterning tool. This is so that the optics of the patterning tool are not contaminated by off-gassing from the substrate.

[0058] As shown in FIG. 3C, the patterning results in exposed metal-containing film regions of formed metal mask 102a and unexposed regions 102b of material to be removed by pattern development.

[0059] Referring to FIG. 3D, the pattern can then be developed. Development is further discussed elsewhere herein. In some embodiments, development of the pattern can occur simply by heating the substrate to volatilize the unexposed regions 102b of the metal-containing film, so that only the exposed regions 102a remain as a fully-formed metal mask. It should be noted that this pattern development operation may not require vacuum integration since a thermally and environmentally stable patterned metal mask may have been formed. It may also be desirable to conduct the pattern development outside the patterning tool to avoid contaminating the tool optics with any incompatible byproducts of the metal-containing film decomposition.

[0060] Referring to FIG. 3E, as an optional step, a pattern amplification can be done. For example selective ALD or electroless deposition (ELD) may be performed on the patterned substrate following the operations depicted in FIGS. 3C and/or 3D to build up the thickness of the metal mask with additional selectively deposited metal 106. This may be helpful to reduce optical transmission of the mask or make it more mechanically robust. Such amplification may be accomplished, for example, by adaptation of an electroless deposition process such as that described in U.S. Pat. Nos. 6,911,067, 6,794,288, 6,902,605 and 4,935,312, the disclosures of which in this regard are incorporated by reference herein.

[0061] For example, an initial lnm seed could be amplified to 10 nm in this way. Like the pattern development discussed with reference to FIG. 3D, this operation may not require vacuum integration since a thermally and environmentally stable patterned metal mask would have been formed before amplification.

[0062] One advantage of an all dry or partially dry film formation operation is that dry operations may be one-pass tunable processes. By changing various process conditions (as described below), an operation can be optimized. For example, a dry process for underlayer and PR deposition may be performed in two operations, while wet processes may require cleaning and bake operations before deposition of the PR film. Wet processes, by contrast, may require the use of pre-formulated solution that constrains process parameters, as well as additional passes of thermal treatment, cooling, and spin drying. A dry process may avoid any liquid solution drying steps and reduce PR delamination or line leaning/collapse.

[0063] Another advantage of an all dry or partially dry film formation operation is enhanced control over the processing environment. A wet, spin-on process may use preformulated solutions and be performed at ambient pressure. A dry process may be performed under vacuum with control of, e.g., pressure, humidity, oxygen, and temperature. In embodiments where integrated processes are performed on

the same tool, chamber, or station, vacuum may be maintained between dry processes, which is advantageous to control the environment of the wafer during and between processing operations. Furthermore, integrated processes may allow for reduced queue time as processes are performed within the same tool, chamber, or station.

#### Deposition of Photoresist (PR)

[0064] As discussed above, the present disclosure provides methods for making imaging layers on semiconductor substrates, which may be patterned using EUV or other next generation lithographic techniques. Methods include those where polymerized organometallic materials are produced in a vapor and deposited on a substrate. In other embodiments, a spin-on formulation may be used.

[0065] The present technology provides methods by which EUV-sensitive thin films are deposited on a substrate, such films being operable as resists for subsequent EUV lithography and processing. Such EUV-sensitive films comprise materials which, upon exposure to EUV, undergo changes, such as the loss of bulky pendant substituents bonded to metal atoms in low density M-OH rich materials, allowing their crosslinking to denser M-O-M bonded metal oxide materials. Through EUV patterning, areas of the film are created that have altered physical or chemical properties relative to unexposed areas. These properties may be exploited in subsequent processing, such as to dissolve either unexposed or exposed areas, or to selectively deposit materials on either the exposed or unexposed areas. In some embodiments, the unexposed film has a hydrophobic surface and the exposed film has a hydrophilic surface (it being recognized that the hydrophilic properties of exposed and unexposed areas are relative to one another) under the conditions at which such subsequent processing is performed. For example, the removal of material may be performed by leveraging differences in chemical composition, density and cross-linking of the film. Removal may be by wet processing or dry processing, as further described below.

[0066] The thickness of the EUV-patternable film formed on the surface of the substrate may vary according to the surface characteristics, materials used, and processing conditions. In various embodiments, the film thickness may range from 0.5 nm to 100 nm, and is preferably of sufficient thickness to absorb most of the EUV light under the conditions of EUV patterning. For example, the overall absorption of the resist film may be 30% or less (e.g., 10% or less, or 5% or less) so that the resist material at the bottom of the resist film is sufficiently exposed. In some embodiments, the film thickness is from 10 to 20 nm. Without limiting the mechanism, function or utility of present disclosure, it is believed that, unlike wet, spin-coating processes of the art, the processes of the present disclosure have fewer restrictions on the surface adhesion properties of the substrate, and therefore can be applied to a wide variety of substrates. Moreover, as discussed above, the deposited films may closely conform to surface features, providing advantages in forming masks over substrates, such as substrates having underlying features, without "filling in" or otherwise planarizing such features.

### Substrates

[0067] Substrates useful in the methods of the present technology may include any material construct suitable for

lithographic processing, particularly for the production of integrated circuits and other semiconducting devices. In some embodiments, substrates are silicon wafers. Substrates may be silicon wafers upon which features have been created ("underlying topographical features"), having an irregular surface topography. (As referred to herein, the "surface" is a surface onto which a film of the present technology is to be deposited or that is to be exposed to EUV during processing.) Such underlying topographical features may include regions in which material has been removed (e.g., by etching) or regions in which materials have been added (e.g., by deposition) during processing prior to conducting a method of this technology. Such prior processing may include methods of this technology or other processing methods in an iterative process by which two or more layers of features are formed on the substrate. Without limiting the mechanism, function or utility of present technology, it is believed that, in some embodiments, methods of the present technology offer advantages relative to methods among those known in the art in which photolithographic films are deposited on the surface of substrates using spin casting methods. Such advantages may derive from the conformance of the films of the present technology to underlying features without "filling in" or otherwise planarizing such features, and the ability to deposit films on a wide variety of material surfaces.

[0068] In some embodiments, an incoming wafer can be prepared with a substrate surface of a desired material, with the uppermost material being the layer into which the resist pattern is transferred. While the material selection may vary depending on integration, it is generally desired to select a material which can be etched with high selectivity to (i.e., much faster than) the EUV resist or imaging layer. Suitable substrate materials can include various carbon—based films (e.g., ashable hard mask (AHM), silicon based films (e.g., SiOx, SiOxNy, SiOxCyNz), a-Si:H, poly-Si, or SiN), or any other (generally sacrificial) film applied to facilitate the patterning process.

[0069] In some embodiments, the substrate is a hard mask, which is used in lithographic etching of an underlying semiconductor material. The hard mask may comprise any of a variety of materials, including amorphous carbon (a-C), SnO<sub>x</sub>, SiO<sub>2</sub>, SiO<sub>x</sub>N<sub>y</sub>, SiO<sub>x</sub>C, Si<sub>3</sub>N<sub>4</sub>, TiO<sub>2</sub>, TiN, W, W-doped C, WO<sub>x</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub>. For example, the substrate may preferably comprise SnO<sub>x</sub>, such as SnO<sub>2</sub>. In various embodiments, the layer may be from 1 nm to 100 nm thick, or from 2 nm to 10 nm thick.

[0070] In some embodiments, a substrate comprises an underlayer. An underlayer may be deposited on a hard mask or other layer and is generally underneath an imaging layer as described herein. An underlayer may be used to improve the sensitivity of a PR, increase EUV absorptivity, and/or increase the patterning performance of the PR. In cases where there are device features present on the substrate to be patterned which create significant topography, another important function of the underlayer can be to overcoat and planarize the existing topography so that the subsequent patterning step may be performed on a flat surface with all areas of the pattern in focus. For such applications, the underlayer (or at least one of multiple underlayers) may be applied using spin-coating techniques. When the photoresist material being employed possesses a significant inorganic component, for example it exhibits a predominately metal oxide framework, the underlayer may advantageously be a carbon-based film, applied either by spin-coating or by dry vacuum based deposition processes. The layer may include various ashable hard mask (AHM) films with carbon and hydrogen based compositions and may be doped with additional elements such as tungsten, boron, nitrogen, or fluorine. Methods and apparatus among those useful in such processes are described in U.S. Patent Application 62,909, 4309, filed Oct. 2, 2019, incorporated by reference herein for its disclosure of the methods and apparatus.

#### Film Deposition

[0071] In various embodiments, the EUV-patternable films are made and deposited on the substrate using vapor deposition equipment and processes among those known in the art. In such processes, the polymerized organometallic material is formed in vapor phase or in situ on the surface of the substrate.

[0072] In general, methods comprise mixing a vapor stream of an organometallic precursor with a vapor stream of a counter-reactant so as to form a polymerized organometallic material, and depositing the organometallic material onto the surface of the semiconductor substrate. As will be understood by one of ordinary skill in the art, the mixing and depositing aspects of the process may be concurrent, in a substantially continuous process. Methods and apparatus among those useful in such processes are described in Application PCT/US2019/031618, filed May 9, 2019 and Application PCT/US2019/060742, filed Nov. 11, 2019, incorporated by reference herein for its disclosure of the methods and apparatus, in particular various organometallic precursors. EUV-sensitive thin films may be deposited on the semiconductor substrate, such films being operable as resists for subsequent EUV lithography and processing. Such EUV-sensitive thin films comprise materials which, upon exposure to EUV, undergo changes, such as the loss of bulky pendant substituents bonded to metal atoms in low density M-OH rich materials, allowing their crosslinking to denser M-O-M bonded metal oxide materials. Through EUV patterning, areas of the film are created that have altered physical or chemical properties relative to unexposed areas. These properties may be exploited in subsequent processing, such as to dissolve either unexposed or exposed areas, or to selectively deposit materials on either the exposed or unexposed areas. In some embodiments, the unexposed film has a more hydrophobic surface than the exposed film under the conditions at which such subsequent processing is performed. For example, the removal of material may be performed by leveraging differences in chemical composition, density and cross-linking of the film. Removal may be by wet processing or dry processing, as further described

[0073] The thin films are, in various embodiments, organometallic materials, for example organotin materials comprising tin oxide, or other metal oxide materials/moieties. The organometallic compounds may be made in a vapor phase reaction of an organometallic precursor with a counter reactant. In various embodiments, the organometallic compounds are formed through mixing specific combinations of organometallic precursors having bulky alkyl groups or fluoroalkyl with counter-reactants and polymerizing the mixture in the vapor phase to produce a low-density, EUV-sensitive material that deposits onto the semiconductor substrate.

[0074] In various embodiments, organometallic precursors comprise at least one alkyl group on each metal atom that can survive the vapor-phase reaction, while other ligands or ions coordinated to the metal atom can be replaced by the counter-reactants. Organometallic precursors include those of the formula:

$M_a R_b L_c$  (Formula 1)

wherein: M is a metal with a high EUV absorption cross-section; R is alkyl, such as  $C_nH_{2n+1}$ , preferably wherein n $\geq$ 2; L is a ligand, ion or other moiety which is reactive with the counter-reactant;  $a\geq 1$ ;  $b\geq 1$ ; and  $c\geq 1$ .

[0075] In various embodiments, M has an atomic absorption cross section equal to or greater than  $1 \times 10^7$  cm<sup>2</sup>/mol. M may be, for example, selected from the group consisting of tin, hafnium, tellurium, bismuth, indium, antimony, germanium, and combinations thereof. In some embodiments, M is tin. R may be fluorinated, e.g., having the formula  $C_nF_xH_{(2n+1)}$ . In various embodiments, R has at least one beta-hydrogen or beta-fluorine. For example, R may be selected from the group consisting of ethyl, i-propyl, n-propyl, t-butyl, i-butyl, n-butyl, sec- butyl, n-pentyl, i-pentyl, t-pentyl, sec-pentyl, and mixtures thereof. L may be any moiety readily displaced by a counter-reactant to generate an M-OH moiety, such as a moiety selected from the group consisting of amines (such as dialkylamino, monoalkylamino), alkoxy, carboxylates, halogens, and mixtures thereof.

[0076] Counter-reactants have the ability to replace the reactive moieties, ligands or ions (e.g., L in Formula 1, above) so as to link at least two metal atoms via chemical bonding. Counter-reactants can include water, peroxides (e.g., hydrogen peroxide), di- or polyhydroxy alcohols, fluorinated di- or polyhydroxy alcohols, fluorinated glycols, and other sources of hydroxyl moieties. In various embodiments, a counter-reactant reacts with the organometallic precursor by forming oxygen bridges between neighboring metal atoms.

[0077] Other potential counter-reactants include hydrogen sulfide and hydrogen disulfide, which can crosslink metal atoms via sulfur bridges. In other instances, Te-containing precursors may be used counter-reactants with or instead of water to form Te-Sn-Te-Sn cross-links, for example. Suitable tellurium co-reactants for use with Sn(NMe<sub>2</sub>)x type precursors are RTeH or RTeD (D=deuterium) and R<sub>2</sub>Te precursors, with R=alkyl groups, particularly t-butyl or isopropyl, such as t-butylTeD. For use with M(OR)x type precursors, Bis(trimethylsilyl)Te may be used, for example. [0078] The thin films may include optional materials in addition to an organometallic precursor and counter-reactants to modify the chemical or physical properties of the film, such as to modify the sensitivity of the film to EUV or enhancing etch resistance. Such optional materials may be introduced, such as by doping during vapor phase formation prior to deposition on the semiconductor substrate, after deposition of the thin film, or both. In some embodiments, a gentle remote H<sub>2</sub> plasma may be introduced so as to replace some Sn—L bonds with Sn—H, which can increase reactivity of the resist under EUV.

[0079] In various embodiments, the EUV-patternable films are made and deposited on the semiconductor substrate using vapor deposition equipment and processes among those known in the art. In such processes, the polymerized organometallic material is formed in vapor phase or in situ

on the surface of the semiconductor substrate. Suitable processes include, for example, chemical vapor deposition (CVD), atomic layer deposition (ALD), and ALD with a CVD component, such as a discontinuous, ALD-like process in which metal precursors and counter-reactants are separated in either time or space.

[0080] In general, methods comprise mixing a vapor stream of an organometallic precursor with a vapor stream of a counter-reactant so as to form a polymerized organometallic material, and depositing the organometallic material onto the surface of the semiconductor substrate. In some embodiments, more than one organometallic precursor is included in the vapor stream. In some embodiments, more than one counter-reactant is included in the vapor stream. As will be understood by one of ordinary skill in the art, the mixing and depositing aspects of the process may be concurrent, in a substantially continuous process.

[0081] In an example continuous CVD process, two or more gas streams, in separate inlet paths, of organometallic precursor and source of counter-reactant are introduced to the deposition chamber of a CVD apparatus, where they mix and react in the gas phase, to form agglomerated polymeric materials (e.g., via metal-oxygen-metal bond formation). The streams may be introduced, for example, using separate injection inlets or a dual-plenum showerhead. The apparatus is configured so that the streams of organometallic precursor and counter-reactant are mixed in the chamber, allowing the organometallic precursor and counter-reactant to react to form a polymerized organometallic material. Without limiting the mechanism, function, or utility of present technology, it is believed that the product from such vapor-phase reaction becomes heavier in molecular weight as metal atoms are crosslinked by counter-reactants, and is then condensed or otherwise deposited onto the semiconductor substrate. In various embodiments, the steric hindrance of the bulky alkyl groups prevents the formation of densely packed network and produces smooth, amorphous, lowdensity films.

[0082] The CVD process is generally conducted at

reduced pressures, such as from 10 milliTorr to 10 Torr. In some embodiments, the process is conducted at from 0.5 to 2 Torr. In some embodiments, the temperature of the semiconductor substrate is at or below the temperature of the reactant streams. For example, the substrate temperature may be from 0° C. to 250° C., or from ambient temperature (e.g., 23° C.) to 150° C. In various processes, deposition of the polymerized organometallic material on the substrate occurs at rates inversely proportional to surface temperature. [0083] The thickness of the EUV-patternable film formed on the surface of the semiconductor substrate may vary according to the surface characteristics, materials used, and processing conditions. In various embodiments, the film thickness may range from 0.5 nm to 100 nm, and may be a sufficient thickness to absorb most of the EUV light under the conditions of EUV patterning. The EUV-patternable film may be able to accommodate absorption equal to or greater than 30%, thereby having significantly fewer EUV photons available towards the bottom of the EUV-patternable film. Higher EUV absorption leads to more cross-linking and densification near the top of an EUV-exposed film compared to the bottom of the EUV-exposed film. Though efficient utilization of EUV photons may occur with EUV-patternable films having higher overall absorption, it will be understood that in some instances, the EUV-patternable film may be less than about 30%. For comparison, the maximum overall absorption of most other resist films are less than 30% (e.g., 10% or less, or 5% or less) so that the resist material at the bottom of the resist film is sufficiently exposed. In some embodiments, the film thickness is from 5 nm to 40 nm or from 10 nm to 20 nm. Without limiting the mechanism, function, or utility of present disclosure, it is believed that, unlike wet, spin-coating processes of the art, the processes of the present disclosure have fewer restrictions on the surface adhesion properties of the substrate, and therefore can be applied to a wide variety of substrates. Moreover, as discussed above, the deposited films may closely conform to surface features, providing advantages in forming masks over substrates, such as substrates having underlying features, without "filling in" or otherwise planarizing such features.

[0084] In some embodiments of the techniques discussed herein, another strategy that can further improve the EUV sensitivity in a PR film is to create a film where the film composition is vertically graded, resulting in depth-dependent EUV sensitivity. In a homogenous PR with a high absorption coefficient, the decreasing light intensity throughout the film depth necessitates a higher EUV dose to ensure the bottom is sufficiently exposed. By increasing the density of atoms with high EUV absorptivity at the bottom of the film relative to the top of the film (i.e., by creating a gradient with increasing EUV absorption) it becomes possible to more efficiently utilize available EUV photons while more uniformly distributing absorption (and the effects of secondary electrons) towards the bottom of more highly absorbing films.

[0085] The strategy of engineering a vertical composition gradient in a PR film is particularly applicable to dry deposition methods such as CVD and ALD and can be realized by tuning the flow ratios between different reactants during deposition. The type of composition gradients that can be engineered include: the ratios between different high-absorbing metals, the percentage of metal atoms that have EUV- cleavable bulky groups, the percentages of bulky groups or counter-reactants that contain high-absorbing elements (such as Te, and I), and combinations of the above. Further discussion of vertically graded films is found in Application PCT/US20/70172, filed Jun. 24, 2020, incorporated by reference herein for its disclosure of the methods and apparatus.

#### Backside/Bevel Clean

[0086] During application of an EUV photoresist film to a substrate, either by conventional wet, e.g., spin-on, processing or dry deposition as described herein, there may be some unintended deposition of resist material on the wafer bevel edge and/or backside. This bevel edge and backside deposition can cause downstream processing problems, including contamination of the patterning (scanner) and development tools. Conventionally, removal of this bevel edge and backside deposition is done by wet cleaning techniques.

[0087] The current state-of-the-art for cleaning spin-coated metal-organic photoresists is by wet-clean processing. An edge bead removal (EBR) is performed on a wet track on both the front and the backside of a wafer. A nozzle is positioned over the edge of the wafer on both the frontside and the backside of the wafer, and solvent is dispensed while the wafer is rotating. An organic solvent (for example: PGME, PGMEA, 2-heptanone) dissolves the photoresist on

the edge, cleaning the bevel edge region. If the backside is contaminated, the wafer needs to go to another wet clean station for backside cleaning of the wafer. For spin-coating, the wafer region contacting the chuck typically remains clean and a separate backside clean is not always used. Additional cleans such as dilute hydrofluoric acid (dHF), dilute hydrochloric acid (dHCl), dilute sulfuric acid, or standard clean 1 (SC-1) may be necessary to reduce metals contamination. Before entering the EUV scanner, a backside scrub is commonly performed.

[0088] Solvents used in wet-clean processing inherently have issues of high cost for both acquisition and disposal. Such solvents may become hazardous to the environment and present health concerns. Wet-clean processing may be limited by uniformity of removal of the EUV resist material on the bevel edge regions. Due to surface tension and vapor concerns, the removal is often wavy and does not result in crisp removal of the EUV resist material at the bevel edge regions. Additionally, backsplashes using organic solvents can generate defects on the frontside of the wafer. The wet-clean processing is typically performed in a stand-alone tool/chamber, and so wafers need to be transferred after deposition in between tools/chambers. This can result in contamination of the tools/chambers used in backside and/or bevel edge cleaning.

[0089] Described herein is a cleaning process to clean a backside and/or bevel edge of the semiconductor substrate. The backside and/or bevel edge clean may non-selectively etch EUV resist film to equally remove film with various levels of oxidation or crosslinking on the substrate backside and bevel edge. During application of the EUV-patternable film, either by wet deposition processing or dry deposition processing, there may be some unintended deposition of resist material on the substrate bevel edge and/or backside. The unintended deposition may lead to undesirable particles later moving to a top surface of the semiconductor substrate and becoming particle defects. Moreover, this bevel edge and backside deposition can cause downstream processing problems, including contamination of the patterning (scanner) and development tools. Conventionally, removal of this bevel edge and backside deposition is done by wet cleaning techniques. For spin-coated photoresist material, this process is called edge bead removal (EBR) and is performed by directing a stream of solvent from above and below the bevel edge while the substrate is spinning The same process can be applied to soluble organotin oxide-based resists deposited by vapor deposition techniques.

[0090] The substrate bevel edge and/or backside clean may also be a dry clean process. In some embodiments, the dry clean process involves a vapor and/or plasma having one or more of the following gases: HBr, HCl, HI, BCl<sub>3</sub>, SOCl<sub>2</sub>, Cl<sub>2</sub>, BBr<sub>3</sub>, H<sub>2</sub>, O<sub>2</sub>, PCl<sub>3</sub>, CH<sub>4</sub>, methanol, ammonia, formic acid, NF<sub>3</sub>, HF. In some embodiments, the dry clean process may use the same chemistries as a dry development process described herein. For example, the bevel edge and backside clean may use hydrogen halide development chemistry. For the backside and bevel edge clean process, the vapor and/or the plasma has to be limited to a specific region of the substrate to ensure that only the backside and the bevel are removed, without any film degradation on a frontside of the substrate.

[0091] Process conditions may be optimized for bevel edge and backside clean. In some embodiments, higher temperature, higher pressure, and/or higher reactant flow

may lead to increased etch rate. Suitable process conditions for a dry bevel edge and backside clean may be: reactant flow of 100-10000 sccm (e.g., 500 sccm HCl, HBr, HI, or  $\rm H_2$  and  $\rm Cl_2$  or  $\rm Br_2$ ,  $\rm BCl_3$  or  $\rm H_2$ ), temperature of 20 to 140° C. (e.g., 80° C.), pressure of 20-1000 mTorr (e.g., 100 mTorr), plasma power of 0 to 500 W at high frequency (e.g., 13.56 MHz), and for a time of about 10 to 20 seconds, dependent on the photoresist film and composition and properties. ft should be understood that while these conditions are suitable for some processing reactors, e.g., a Kiyo etch tool available from Lam Research Corporation, Fremont, Calif., a wider range of process conditions may be used according to the capabilities of the processing reactor.

[0092] Further discussion of bevel edge and backside cleaning is found in Application PCT/US20/70187, filed Jun. 25, 2020, and/or in Application PCT/US20/39615, filed Jun. 25, 2020, incorporated by reference herein for all purposes.

#### PR Rework

[0093] The dry-cleaning operation may alternatively be extended to a full photoresist removal or photoresist "rework" in which an applied EUV photoresist is removed and the semiconductor substrate prepared for photoresist reapplication, such as when the original photoresist is damaged or otherwise defective. Photoresist rework should be accomplished without damaging the underlying semiconductor substrate, so an oxygen-based etch should be avoided. Instead, variants of halide-containing chemistries as described herein may be used. It will be understood that the photoresist rework operation may be applied at any stage during the process 100. Thus, the photoresist rework operation may be applied after photoresist deposition, after bevel edge and backside clean, after PAB treatment, after EUV exposure, after PEB treatment, or after development. In some embodiments, the photoresist rework may be performed for non-selective removal of exposed and unexposed regions of the photoresist but selective to an underlayer.

[0094] In some embodiments, the photoresist rework process involves a vapor and/or plasma having one or more of the following gases: HBr, HCl, HI, BCl<sub>3</sub>, Cl<sub>2</sub>, BBr<sub>3</sub>, H<sub>2</sub>, PCl<sub>3</sub>, CH<sub>4</sub>, methanol, ammonia, formic acid, NF<sub>3</sub>, HF. In some embodiments, the photoresist rework process may use the same chemistries as a dry development process described herein. For example, the photoresist rework may use hydrogen halide development chemistry.

[0095] Process conditions may be optimized for the photoresist rework. In some embodiments, higher temperature, higher pressure, and/or higher reactant flow may lead to increased etch rate. Suitable process conditions for a photoresist rework may be: reactant flow of 100-500 sccm (e.g., 500 seem HCl, HBr, HI, BCl<sub>3</sub> or H<sub>2</sub> and Cl<sub>2</sub> or Br<sub>2</sub>), temperature of 20 to 140° C. (e.g., 80° C.), pressure of 20-1000 mTorr (e.g., 300 mTorr), plasma power of 300 to 800 W (e.g., 500 W) at high frequency (e.g., 13.56 MHz), wafer bias of 0 to 200  $Y_b$  (a higher bias may be used with harder underlying substrate materials) and for a time of about 20 seconds to 3 minutes, sufficient to completely remove the EUV photoresist, dependent on the photoresist film and composition and properties. It should be understood that while these conditions are suitable for some processing reactors, e.g., a Kiyo etch tool available from Lam Research

Corporation, Fremont, Calif., a wider range of process conditions may be used according to the capabilities of the processing reactor.

[0096] Further discussion of bevel edge and backside cleaning, or PR rework, is found in Application PCT/US20/39615, filed Jun. 25, 2020, incorporated by reference herein for all purposes.

#### PAB/Softbake

[0097] Photolithography processes typically involve one or more bake steps, to facilitate the chemical reactions required to produce chemical contrast between exposed and unexposed areas of the photoresist. For high volume manufacturing (HVM), such bake steps are typically performed on tracks where the wafers are baked on a hot-plate at a pre-set temperature under ambient-air or in some cases  $N_2$  flow. More careful control of the bake ambient as well as introduction of additional reactive gas component in the ambient during these bake steps can help further reduce the dose requirement and/or improve pattern fidelity.

[0098] According to various aspects of this disclosure, one or more post treatments to metal and/or metal oxide-based photoresists after deposition (e.g., post-application bake (PAB)) and/or exposure (e.g., post-exposure bake (PEB)) are capable of increasing material property differences between exposed and unexposed photoresist and therefore decreasing dose to size (DtS), improving PR profile, and improving line edge and width roughness (LER/LWR) after subsequent dry development. The PAB treatment may involve a combination of thermal treatment, chemical exposure, and moisture to increase the EUV sensitivity of the EUV-patternable film, reducing the EUV dose to develop a pattern in the EUVpatternable film. The PAB treatment temperature may be tuned and optimized for increasing the sensitivity of the EUV-patternable film. For example, the treatment temperature may be between about 90° C. and about 200° C. or between about 150° C. and about 190° C. In some embodiments, the PAB treatment may be conducted with a pressure between atmospheric and vacuum, and a treatment duration of about 1 to 15 minutes, for example about 2 minutes. In some embodiments, the PAB treatment is conducted at a temperature between about 100° C. to 200° C. for about 1 minute to 2 minutes.

[0099] At block 108 of the process 100, the metal-containing EUV resist film is exposed to EUV radiation to develop a pattern. Generally speaking, the EUV exposure causes a change in the chemical composition and cross-linking in the metal-containing EUV resist film, creating a contrast in etch selectivity that can be exploited for subsequent development.

[0100] The metal-containing EUV resist film may then be patterned by exposing a region of the film to EUV light, typically under relatively high vacuum. EUV devices and imaging methods among those useful herein include methods known in the art. In particular, as discussed above, exposed areas of the film are created through EUV patterning that have altered physical or chemical properties relative to unexposed areas. For example, in exposed areas, metalcarbon bond cleavage may occur, as through a beta-hydride elimination, leaving behind reactive and accessible metal hydride functionality that can be converted to hydroxide and cross-linked metal oxide moieties via metal-oxygen bridges during a subsequent post-exposure bake (PEB) step. This process can be used to create chemical contrast for devel-

opment as a negative tone resist. In general, a greater number of beta-H in the alkyl group results in a more sensitive film. This can also be explained as weaker Sn—C bonding with more branching. Following exposure, the metal-containing EUV resist film may be baked, so as to cause additional cross-linking of the metal oxide film. The difference in properties between exposed and unexposed areas may be exploited in subsequent processing, such as to dissolve unexposed areas or to deposit materials on the exposed areas. For example the pattern can be developed using a dry method to form a metal oxide-containing mask. [0101] In particular, in various embodiments, the hydrocarbyl-terminated tin oxide present on the surface is converted to hydrogen-terminated tin oxide in the exposed region(s) of an imaging layer, particularly when the exposure is performed in a vacuum using EUV. However, removing exposed imaging layers from vacuum into air, or the controlled introduction of oxygen, ozone, H<sub>2</sub>O<sub>2</sub>, or water, can result in the oxidation of surface Sn—H into Sn—OH. The difference in properties between exposed and unexposed regions may be exploited in subsequent processing, such as by reacting the irradiated region, the unirradiated region, or both, with one or more reagents to selectively add

[0102] Without limiting the mechanism, function or utility of present technology, EUV exposure, for example, at doses of from 10 mJ/cm² to 100 mJ/cm² results in the cleavage of Sn—C bonds resulting is loss of the alkyl substituent, alleviating steric hindrance and allowing the low-density film to collapse. In addition, reactive metal-H bond generated in the beta-hydride elimination reactions can react with neighboring active groups such as hydroxyls in the film, leading to further cross-linking and densification, and creating chemical contrast between exposed and unexposed region(s).

material to or remove material from the imaging layer.

[0103] Following exposure of the metal-containing EUV resist film to EUV light, a photopatterned metal-containing EUV resist is provided. The photopatterned metal-containing EUV resist includes EUV-exposed and unexposed regions.

[0104] In some embodiments, a post-exposure bake (PEB) is performed to further increase contrast in etch selectivity of the photopatterned metal-containing EUV resist. The photopatterned metal-containing EUV resist can be thermally treated in the presence of various chemical species to facilitate cross-linking of the EUV-exposed regions or simply baked on a hot plate in ambient air, for example between 150° C. and 250° C. for between one and five minutes (e.g., 190° C. for two minutes).

[0105] In various embodiments, a bake strategy involves careful control of the bake ambient, introduction of reactive gases, and/or careful control of the ramping rate of the bake temperature. Examples of useful reactive gases include e.g., air, H<sub>2</sub>O, H<sub>2</sub>O<sub>2</sub> vapor, CO<sub>2</sub>, CO, O<sub>2</sub>, O<sub>3</sub>, CH<sub>4</sub>, CH<sub>3</sub>OH, N<sub>2</sub>, H<sub>2</sub>, NH<sub>3</sub>, N<sub>2</sub>O, NO, alcohol, acetyl acetone, formic acid, Ar, He, or their mixtures. The PEB treatment is designed to (1) drive complete evaporation of organic fragments that are generated during EUV exposure and (2) oxidize any Sn—H, Sn—Sn, or Sn radical species generated by EUV exposure into metal hydroxide, and (3) facilitate cross-linking between neighboring Sn—OH groups to form a more densely crosslinked SnO<sub>2</sub>-like network. The bake temperature is carefully selected to achieve optimal EUV lithographic performance. Too low a PEB temperature would