(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 102 31 385 B4 2007.02.22

(12)

## Patentschrift

(21) Aktenzeichen: 102 31 385.7

(22) Anmelddetag: 08.07.2002

(43) Offenlegungstag: 30.01.2003

(45) Veröffentlichungstag

der Patenterteilung: 22.02.2007

(51) Int Cl.<sup>8</sup>: H01L 23/50 (2006.01)

H01L 25/065 (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

(30) Unionspriorität:

2001/41154 10.07.2001 KR

2002/3030 18.01.2002 KR

(73) Patentinhaber:

Samsung Electronics Co., Ltd., Suwon, Kyonggi,

KR

(74) Vertreter:

Patentanwälte Ruff, Wilhelm, Beier, Dauster &

Partner, 70174 Stuttgart

(72) Erfinder:

Song, Young-Hee, Yongin, Kyungki, KR; Choi,

III-Heung, Suwon, Kyungki, KR; Kim, Jung-Jin,

Cheonan, Chungcheongnam, KR; Sohn,

Hai-Jeong, Suwon, Kyungki, KR; Lee, Chung-Woo,

Suwon, Kyungki, KR

(56) Für die Beurteilung der Patentfähigkeit in Betracht

gezogene Druckschriften:

DE 196 10 302 A1

US 61 75 149 B1

US 61 11 317

US 58 34 844

US 58 34 844

US 57 51 065

US 57 23 822

US 47 23 197

EP 10 94 517 A2

EP 02 21 496 A2

JP 06-2 75 794 A

MASATOSHI YASUNAGA: Chip Scale Package:

"A Lightly Dressed LSI Chip". In: IEEE Transact.

on Components, Packaging, and Manufacturing

Technology-Part A, Vol. 18, No. 3, Sept. 1995,

pp. 451-7;

(54) Bezeichnung: Halbleiterchip mit Bondkontaktstellen und zugehörige Mehrchippackung

(57) Hauptanspruch: Halbleiterchip mit folgenden Merkmalen:

- einem Halbleitersubstrat (11) mit einem Zellenbereich ( $A_{cell1}$ ,  $A_{cell2}$ ) und einem dazu benachbarten, peripheren Schaltkreisbereich ( $A_{peri}$ ),

- einer Kontaktstellen-Verdrahtungsstruktur (12), die auf dem Halbleitersubstrat im Wesentlichen in einem Mittenbereich des Halbleitersubstrats auf einem Teil des peripheren Schaltkreisbereichs ausgebildet ist und sich über einen Teil des Zellenbereichs erstreckt,

- einer Passivierungsschicht (16) auf dem Halbleitersubstrat und der Kontaktstellen-Verdrahtungsstruktur,

- einer ersten dielektrischen Zwischenschicht (13) auf dem Halbleitersubstrat mit der Kontaktstellen-Verdrahtungsstruktur,

- einer zweiten dielektrischen Zwischenschicht (20b) auf der ersten dielektrischen Zwischenschicht,

- einer ersten Öffnung (22), die sich durch die Passivierungsschicht und die erste und zweite dielektrische Zwischenschicht hindurch im Zellenbereich erstreckt, um dort einen Teil der Kontaktstellen-Verdrahtungsstruktur freizulegen,

- einer zweiten Öffnung (24), die sich im Zellenbereich von der ersten Öffnung beabstandet...

## Beschreibung

**[0001]** Die Erfindung bezieht sich auf einen Halbleiterchip mit Bondkontaktstelle und auf eine Mehrchippackung mit einem derartigen Halbleiterchip.

**[0002]** Von der Industrie werden beträchtliche Anstrengungen zur Fertigung kleinerer und dünnerer Halbleiterchips unternommen, um der Anforderung nach hoher Packungsdichte für Mehrfunktions-Halbleiterbauelemente hoher Betriebsgeschwindigkeit zu entsprechen. Um die Chipabmessung zu reduzieren, sollten sowohl die Abmessung von Bondkontaktstellen als auch deren Rasterabstand verringert werden.

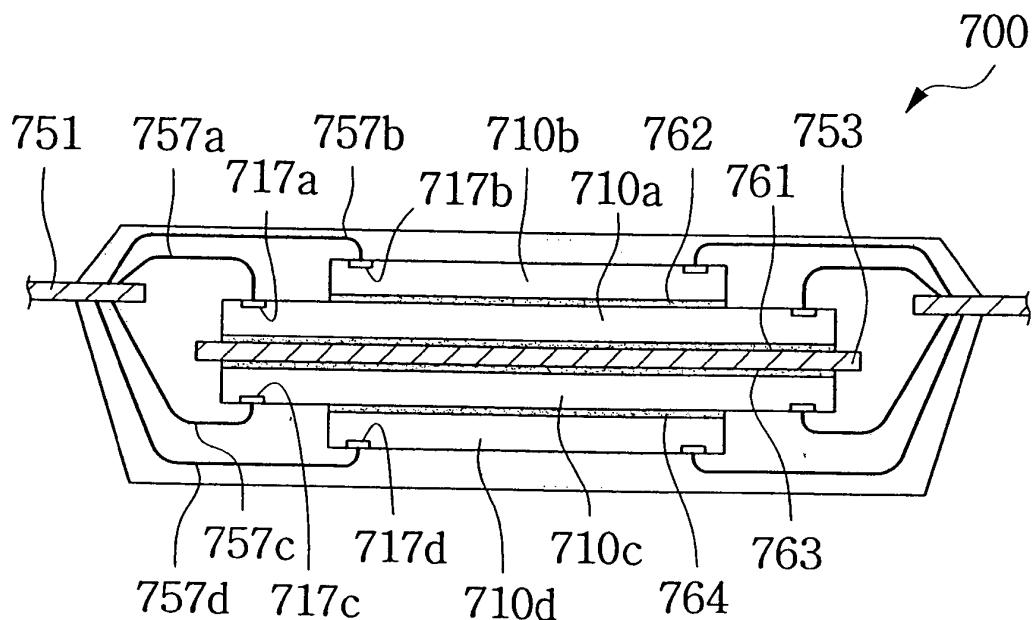

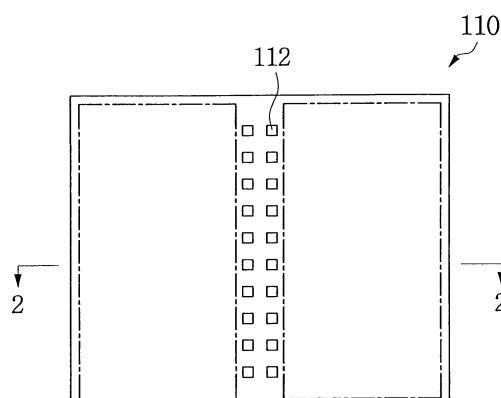

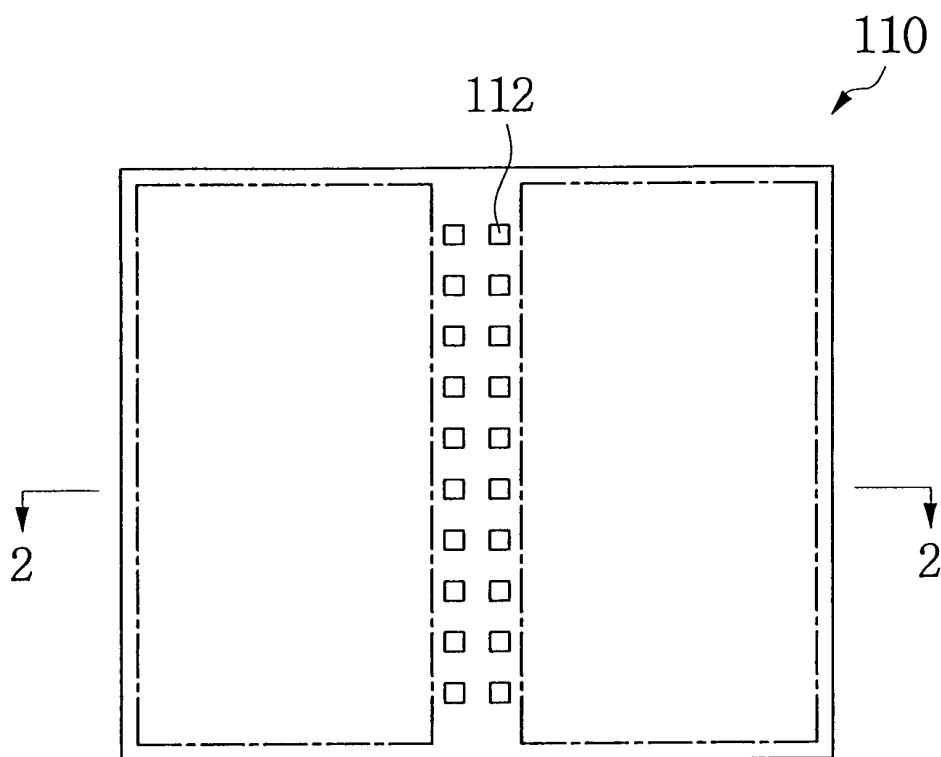

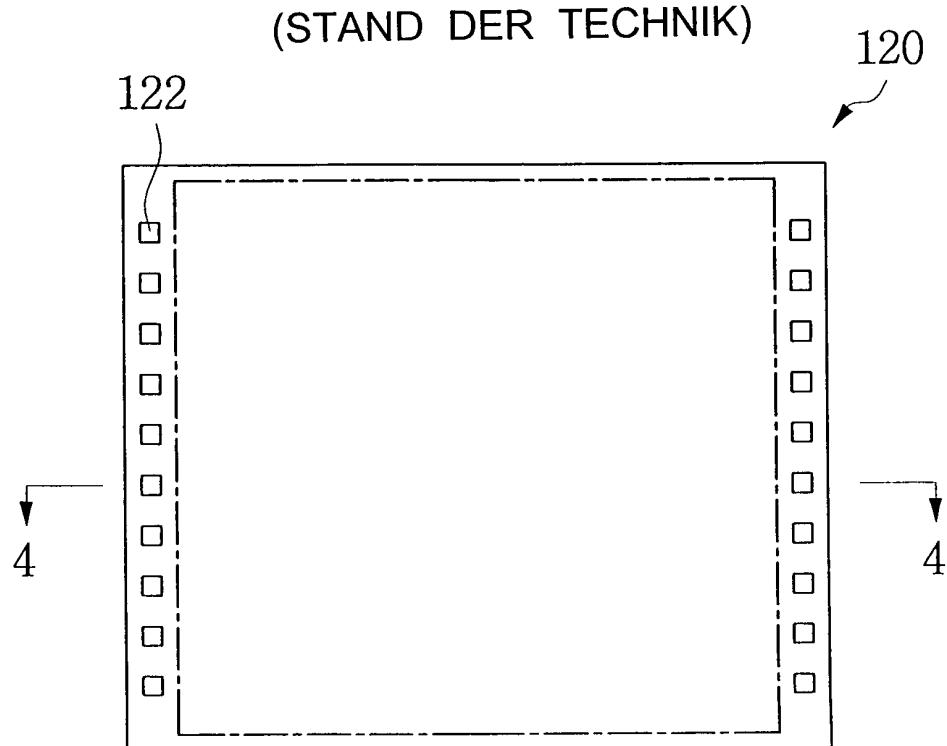

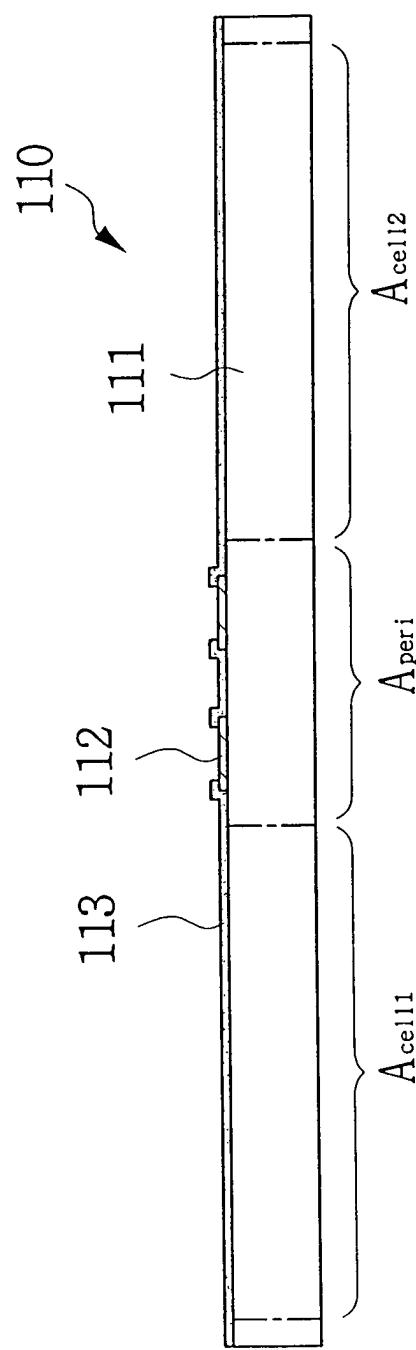

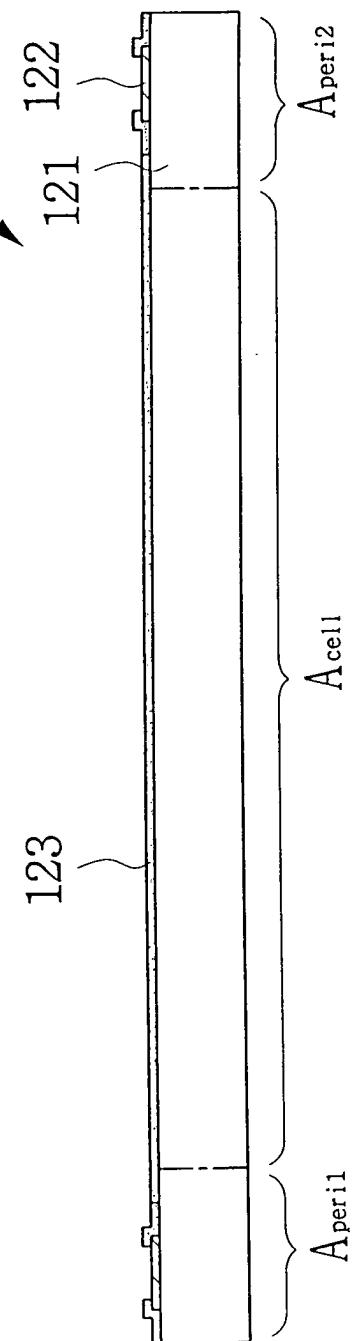

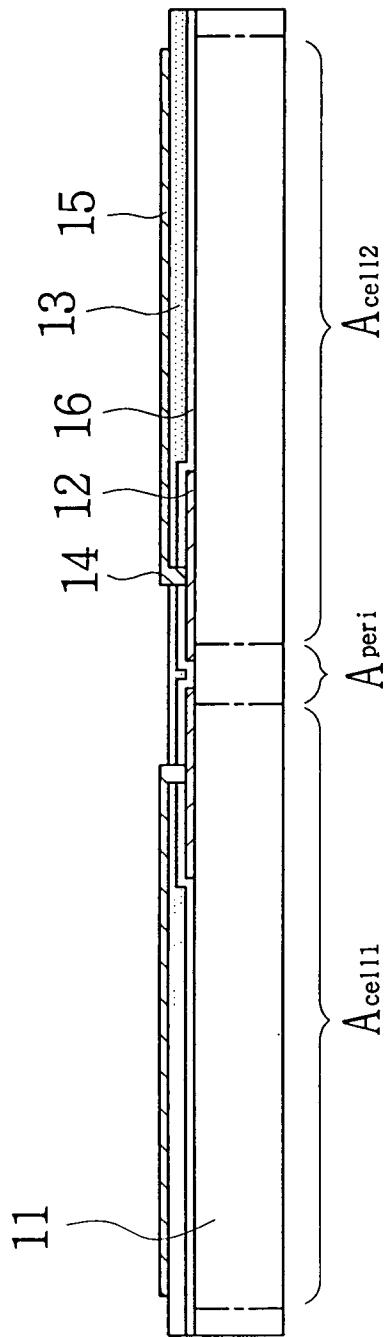

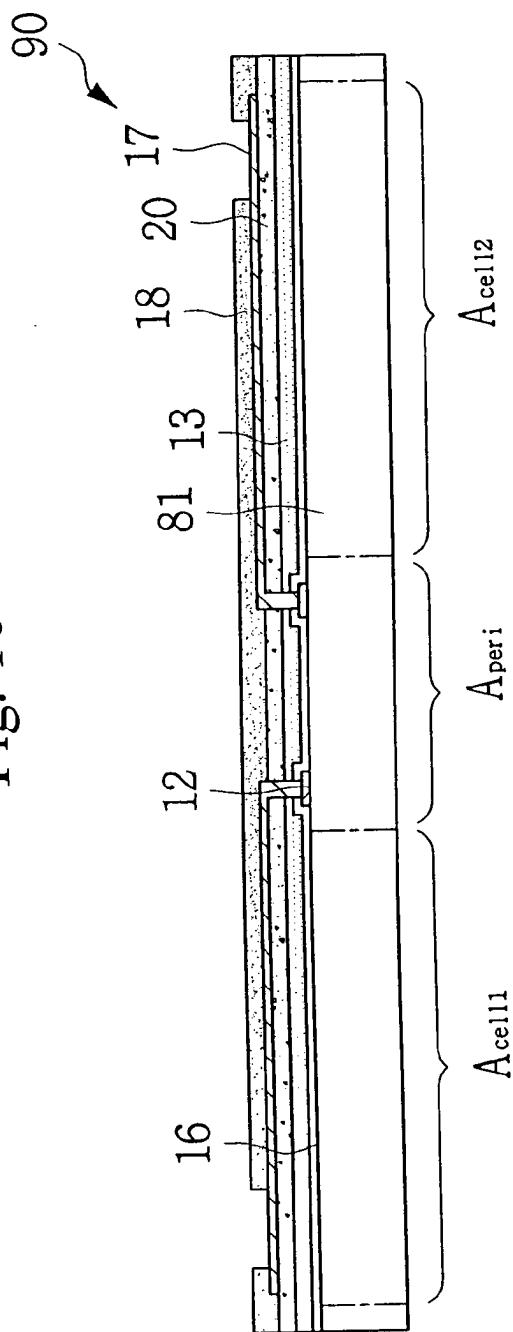

**[0003]** Herkömmliche Halbleiterchips besitzen normalerweise entweder eine Struktur vom Mittenanschlusstyp oder eine Struktur vom peripheren Anschlusstyp. [Fig. 1](#) zeigt in Draufsicht schematisch einen Halbleiterchip vom herkömmlichen Mittenanschlusstyp. [Fig. 2](#) stellt einen Querschnitt längs der Linie 2-2 von [Fig. 1](#) dar. [Fig. 3](#) zeigt in Draufsicht schematisch einen Halbleiterchip vom herkömmlichen peripheren Anschlusstyp. [Fig. 4](#) ist eine Querschnittsansicht entlang der Linie 4-4 von [Fig. 3](#).

**[0004]** Wie aus den [Fig. 1](#) und [Fig. 2](#) ersichtlich, beinhaltet der dortige Halbleiterchip **110** vom Mittenanschlusstyp einen peripheren Schaltkreisbereich  $A_{peri}$  zur Bildung von Bondkontaktstellen **112** sowie Zellenbereiche  $A_{cell1}$  und  $A_{cell2}$ . Der periphere Schaltkreisbereich  $A_{peri}$  ist im Mittenbereich eines Halbleitersubstrats **111** ausgebildet. Die Zellenbereiche  $A_{cell1}$  und  $A_{cell2}$  sind an den Seiten des peripheren Schaltkreisbereichs  $A_{peri}$  ausgebildet.

**[0005]** Wie aus den [Fig. 3](#) und [4](#) ersichtlich, umfasst der dortige Halbleiterchip **120** vom peripheren Anschlusstyp periphere Schaltkreisbereiche  $A_{peri1}$  und  $A_{peri2}$  sowie einen Zellenbereich  $A_{cell}$ . Der Zellenbereich  $A_{cell}$  ist im Mittenbereich eines Halbleitersubstrats **121** ausgebildet. Die peripheren Schaltkreisbereiche  $A_{peri1}$  und  $A_{peri2}$  sind an den Seiten des Zellenbereichs  $A_{cell}$  ausgebildet. Wie aus den [Fig. 2](#) und [4](#) zu ersehen, ist sowohl beim Mittenanschlusstyp als auch beim peripheren Anschlusstyp dieser herkömmlichen Chips eine Passivierungsschicht **113**, **123** über den Zellenbereichen und den peripheren Schaltkreisbereichen ausgebildet.

**[0006]** Bei den herkömmlichen Halbleiterchips **110**, **120** der [Fig. 1](#) bis [4](#) wird eine zusätzliche Chipfläche in peripheren Schaltkreisbereichen zur Bildung von Bondkontaktstellen **112**, **122** benötigt. Dadurch ist für beide herkömmliche Kontaktstellentypen von Chips die Möglichkeit einer Verringerung der Abmessung begrenzt. Außerdem hat es sich als schwierig erwiesen, die Bondkontaktstellenabmessung und das Rastermaß zwischen den Bondkontaktstellen **112**, **122** in diesen herkömmlichen Halbleiterchips **110**,

**120** zu verringern. Denn die Bondkontaktstellen **112**, **122** müssen gemäß Entwurf eine minimale Abmessung und ein minimales Rastermaß zur elektrischen Chipsortierung (EDS) und zur Bildung elektrischer Zwischenverbindungen aufweisen.

**[0007]** Die Möglichkeit einer Verringerung der Abmessung einer Mehrchippackung (MCP) mit mehreren herkömmlichen Halbleiterchips in einem einzigen Packungskörper ist aufgrund von Schwierigkeiten wie dem Übereinanderstapeln von Chips des Mittenanschlusstyps auf Chips desselben oder ähnlicher Typen ebenfalls begrenzt. Denn hier kann sich das Drahtbonden erschweren, da in diesen Fällen lange Drahtschleifen benötigt werden.

**[0008]** Es besteht daher ein Bedarf nach kleineren Halbleiterchips, mit denen problemlos eine MCP gebildet werden kann, ohne dabei auf die obigen Schwierigkeiten zu stoßen.

## Stand der Technik

**[0009]** Es sind bereits verschiedentlich Halbleiterchips mit einer Kontaktstellen-Umordnungsstruktur vorgeschlagen worden, die dazu dient, Kontaktstellen, welche von einer Kontaktstellen-Verdrahtungsstruktur auf einem Halbleitersubstrat des Chips bereitgestellt werden, zu einem anderen Bereich des Chips umzuleiten. So sind z.B. bei einem in der Offenlegungsschrift DE 196 10 302 A1 offenbarten Chip Lothügel-Kontaktstellen über einem Zellengebiet gebildet und durch eine Kontaktstellen-Umordnungsstruktur mit außerhalb des Zellengebietes in einem Mittenbereich des Chips vorgesehenen Kontaktblöcken elektrisch verbunden. Dazu ist auf ein zugehöriges Halbleitersubstrat mit den Kontaktblöcken eine Passivierungsschicht aufgebracht, auf der die Umordnungsstruktur gebildet ist, wobei die elektrische Verbindung mit den Kontaktblöcken über entsprechende Öffnungen in der Passivierungsschicht erfolgt. Über der Umordnungsstruktur sind Isolationschichten gebildet, die an entsprechenden Stellen Öffnungen zur Bildung der Lothügel-Kontaktstellen aufweisen. Im Bereich der Lothügel-Kontaktstellen kann unter der Umordnungsstruktur eine Pufferschicht z.B. aus Polyimidharz vorgesehen sein.

**[0010]** Ähnliche Kontaktstellen-Umleitungsstrukturen zur Bildung von Lothügeln in einem Bereich lateral außerhalb einer auf einem Halbleitersubstrat eines Chips vorgesehenen Kontaktstellen-Verdrahtungsstruktur sind in den Patentschriften US 5,834,84 A und US 6,111,317 A sowie dem Zeitschriftenaufsatz M. Yasunaga et al., Chip Scale Package: „A Lightly Dressed LSI Chip“, IEEE Trans. on Components, Packaging, and Manufacturing Technology – Teil A, Band 18, Nr. 3, September 1995, Seiten 451 bis 457 offenbart.

**[0011]** In der Patentschrift US 4,723,197 ist ein Halbleiterchip mit einer Kontaktstellen-Umordnungsstruktur beschrieben, die dazu dient, eine Kontaktstellen-Verdrahtungsstruktur auf einem Halbleitersubstrat mit über aktiven Bauelementbereichen des Chips gebildeten Bondkontaktstellen elektrisch zu verbinden. Dazu sind über dem Halbleitersubstrat mit der Kontaktstellen-Verdrahtungsstruktur eine Polymidschicht und eine gegen Durchschläge beim späteren Bondvorgang sichernde Schicht z.B. aus Siliziumnitrid aufgebracht, wobei eine oder mehrere Passivierungsschichten vor dem Aufbringen der Polymidschicht vorgesehen sein können. In diesen Schichtstapel wird dann eine Öffnung zur Kontaktstellen-Verdrahtungsstruktur eingebracht, wonach die Kontaktstellen-Umordnungsstruktur gebildet wird. Auf diese wird eine Passivierungsschicht aufgebracht, in die im entsprechenden Bereich eine Öffnung zur Bildung der Bondkontaktstelle eingebracht wird.

**[0012]** In der Patentschrift US 5,723,822 A ist eine integrierte Schaltkreisstruktur beschrieben, bei der eine auf einem Halbleitersubstrat gebildete Kontaktstellen-Verdrahtungsstruktur z.B. zur Kontaktierung einer MOS-Transistorelektrode über eine Zwischenverbindungsschicht mit einer lateral neben der Kontaktstellen-Verdrahtungsstruktur vorgesehenen Bondkontaktstelle elektrisch verbunden ist. Die Zwischenverbindungsschicht befindet sich auf einem Stapel mehrerer Isolationsschichten, die auf das Halbleitersubstrat aufgebracht sind. Eine Passivierungsschicht bedeckt die Zwischenverbindungsschicht und beinhaltet eine Öffnung für die Bondkontaktstelle. Speziell wird dort vorgeschlagen, die Oberseite des Isolationsschichtstapels im Bereich der Bondkontaktstelle mit absichtlichen Unebenheiten zu versehen, z.B. einer zinnen- oder wellenförmigen Struktur, um die Berührkontaktfläche zwischen Bondkontaktstelle und Isolationsschicht zu erhöhen und dadurch die Schichthaftung zu verbessern.

#### Aufgabenstellung

**[0013]** Der Erfindung liegt als technisches Problem die Bereitstellung eines Halbleiterchips und einer diesen verwendenden Mehrchippackung zugrunde, die sich mit vergleichsweise geringer Chipabmessung, geringem Fertigungsaufwand und hoher Produktivität herstellen lassen.

**[0014]** Die Erfindung löst dieses Problem durch die Bereitstellung eines Halbleiterchips mit den Merkmalen des Anspruchs 1 sowie eine Mehrchippackung mit den Merkmalen des Anspruchs 7, 14, oder 15.

**[0015]** Der erfindungsgemäße Halbleiterchip weist eine Kontaktstellen-Umordnungsstruktur auf, die elektrisch mit einer Kontaktstellen-Verdrahtungsstruktur verbunden ist und über wenigstens einem

Teil eines Zellenbereichs eine Bondkontaktstelle beinhaltet. Diese Maßnahme ermöglicht eine deutliche Reduzierung der gesamten Chipabmessung und einer MCP mit einem oder mehreren solchen Chips unter Vermeidung der oben angesprochenen Schwierigkeiten herkömmlicher Chips mit Bondkontaktstellen und diese enthaltenden Mehrchippackungen. Mit der erfindungsgemäßen Maßnahme lassen sich zudem die Herstellungskosten senken und die Produktivität steigern. Erfindungsgemäß ist die Bondkontaktstelle auf einer ersten dielektrischen Zwischenschicht innerhalb einer Öffnung einer auf die erste dielektrische Zwischenschicht aufgebrachten zweiten dielektrischen Zwischenschicht vorgesehen, was hinsichtlich Stabilität gegenüber mechanischer Belastung bei anschließenden Drahtbondvorgängen vorteilhaft ist und einen Pufferungseffekt durch die zweite dielektrische Zwischenschicht vermeidet.

**[0016]** Vorteilhafte Weiterbildungen der Erfindung sind in den Unteransprüchen angegeben.

#### Ausführungsbeispiel

**[0017]** Vorteilhafte, nachfolgend beschriebene Ausführungsformen der Erfindung sowie die zu deren besserem Verständnis oben erläuterten, herkömmlichen und ebenfalls nachfolgend beschriebene, nicht erfindungsgemäße Ausführungsbeispiele sind in den Zeichnungen dargestellt, in denen zeigen:

**[0018]** [Fig. 1](#) eine schematische Draufsicht auf einen herkömmlichen Halbleiterchip vom Mittenanschlusstyp,

**[0019]** [Fig. 2](#) eine Querschnittsansicht längs der Linie 2-2 von [Fig. 1](#),

**[0020]** [Fig. 3](#) eine schematische Draufsicht auf einen herkömmlichen Halbleiterchip vom peripheren Anschlusstyp,

**[0021]** [Fig. 4](#) eine Querschnittsansicht längs der Linie 4-4 von [Fig. 3](#),

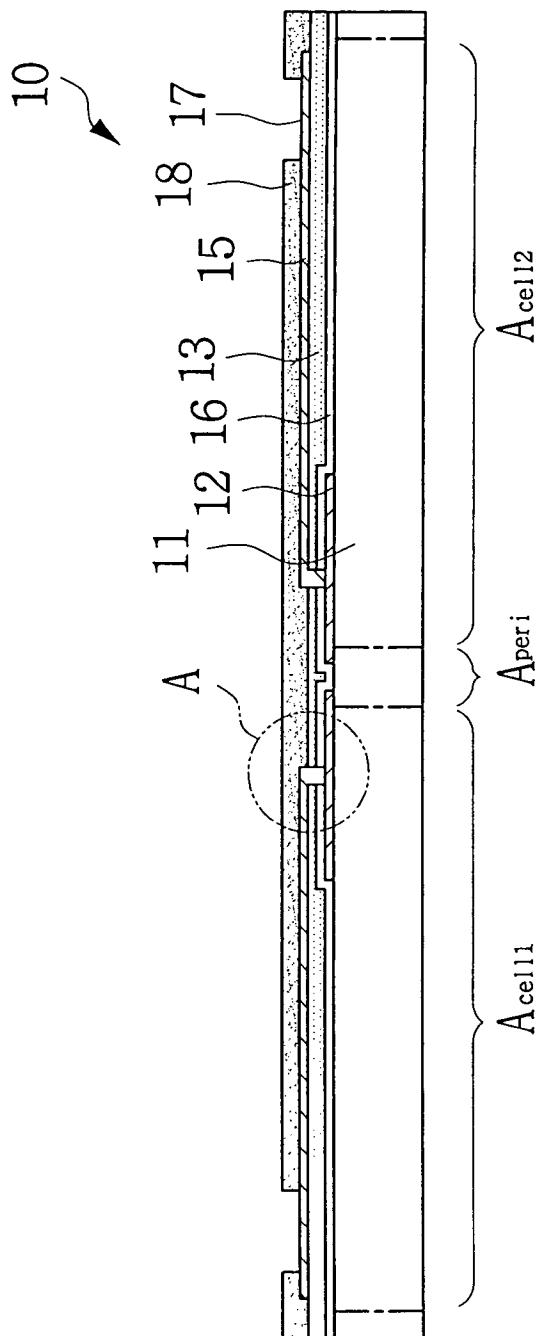

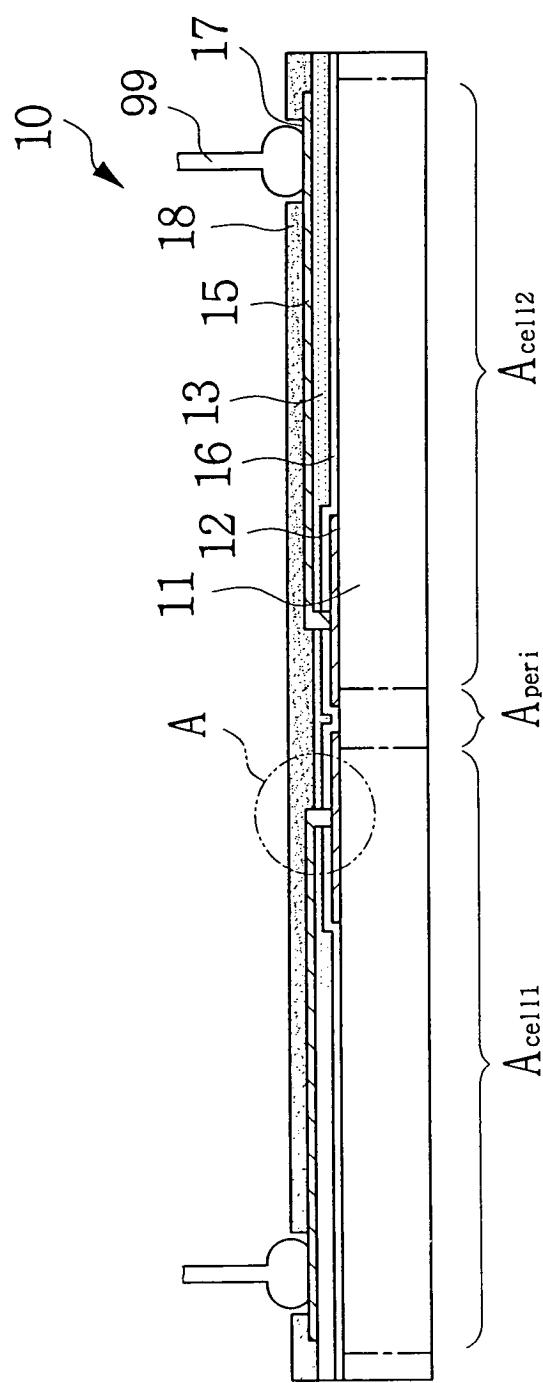

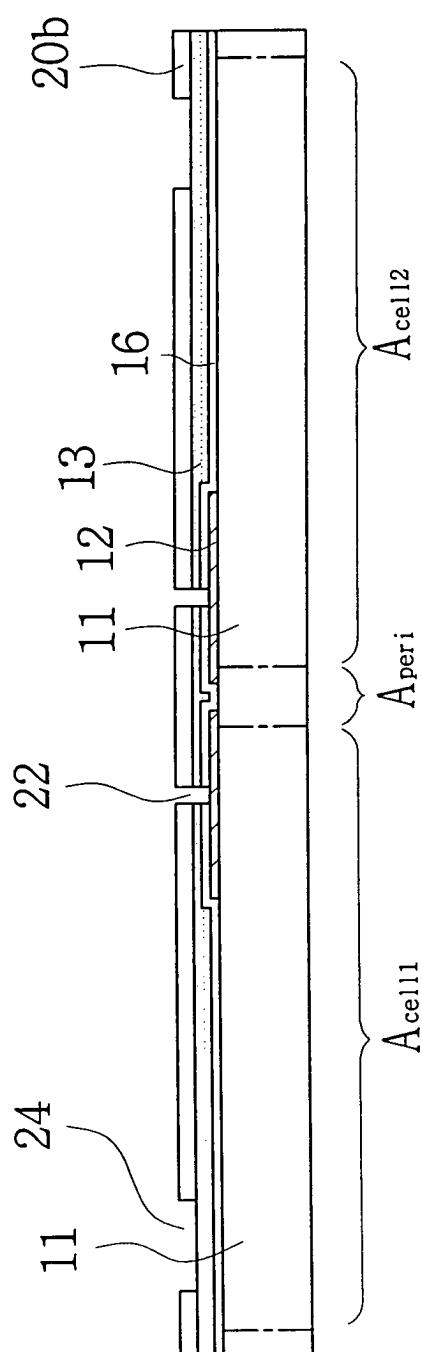

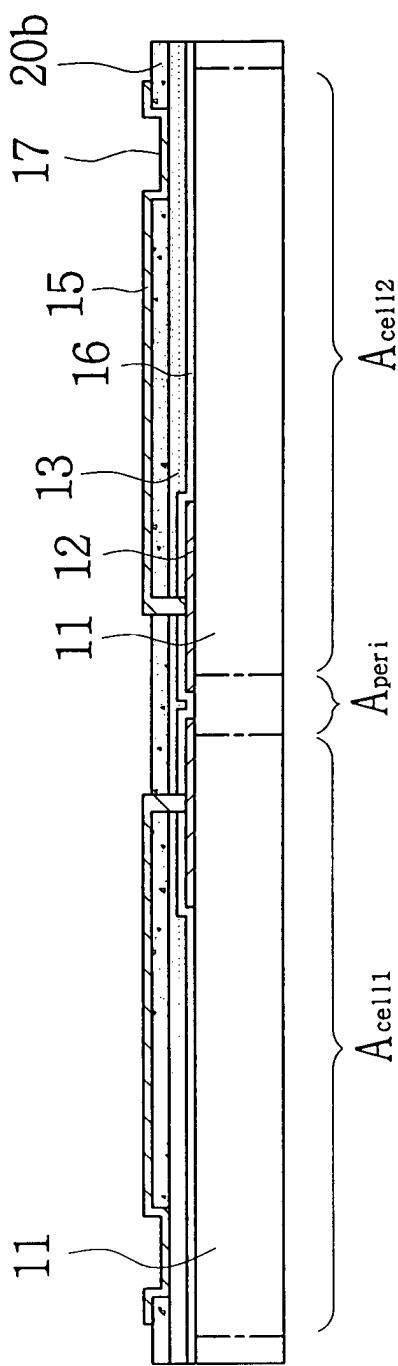

**[0022]** [Fig. 5](#) bis [Fig. 8](#) Querschnittsansichten eines nicht erfindungsgemäßen Halbleiterchips in verschiedenen Stufen eines Verfahrens zur Herstellung des selben,

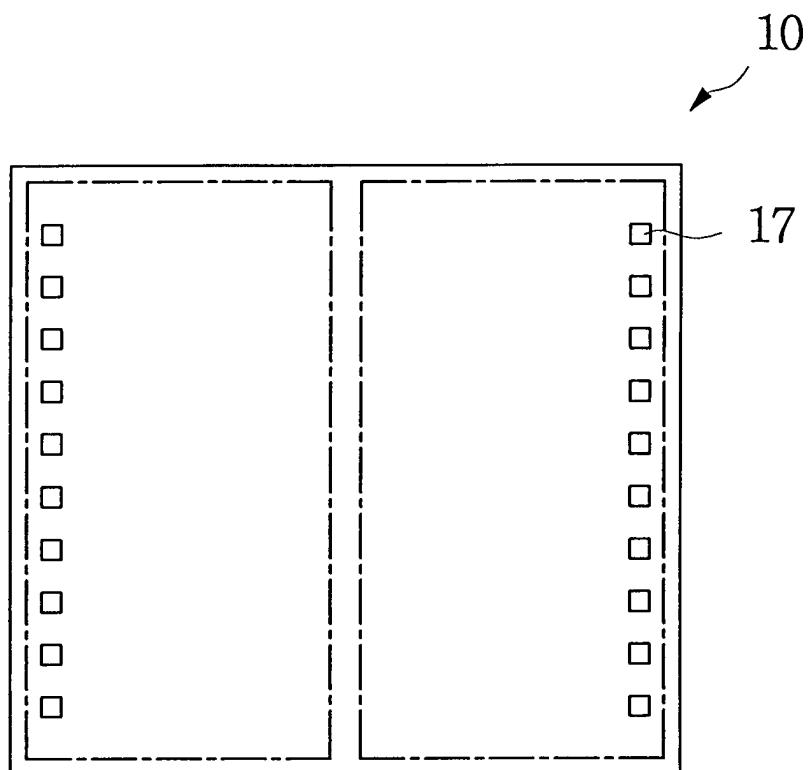

**[0023]** [Fig. 9](#) eine schematische Draufsicht auf den Halbleiterchip von [Fig. 8](#),

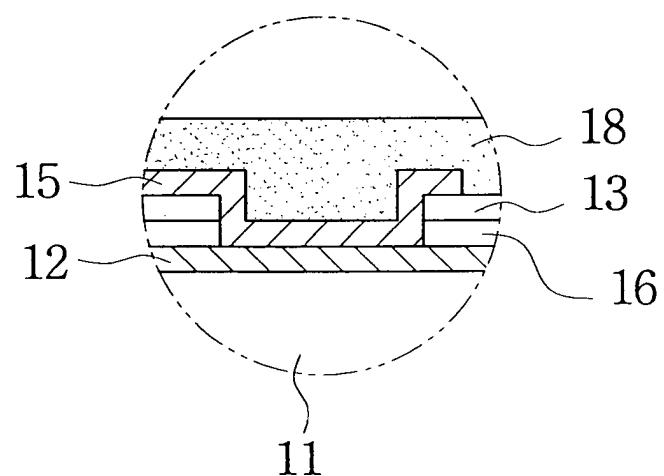

**[0024]** [Fig. 10](#) eine vergrößerte, ausschnittweise Querschnittsansicht eines weiteren nicht erfindungsgemäßen Halbleiterchips mit einer alternativen Konfiguration in einem Bereich A von [Fig. 8](#),

**[0025]** [Fig. 11](#) eine Querschnittsansicht des Halbleiterchips von [Fig. 9](#) nach einem Drahtbondvorgang,

[0026] [Fig. 12](#) eine Querschnittsansicht eines weiteren nicht erfindungsgemäßen Halbleiterchips,

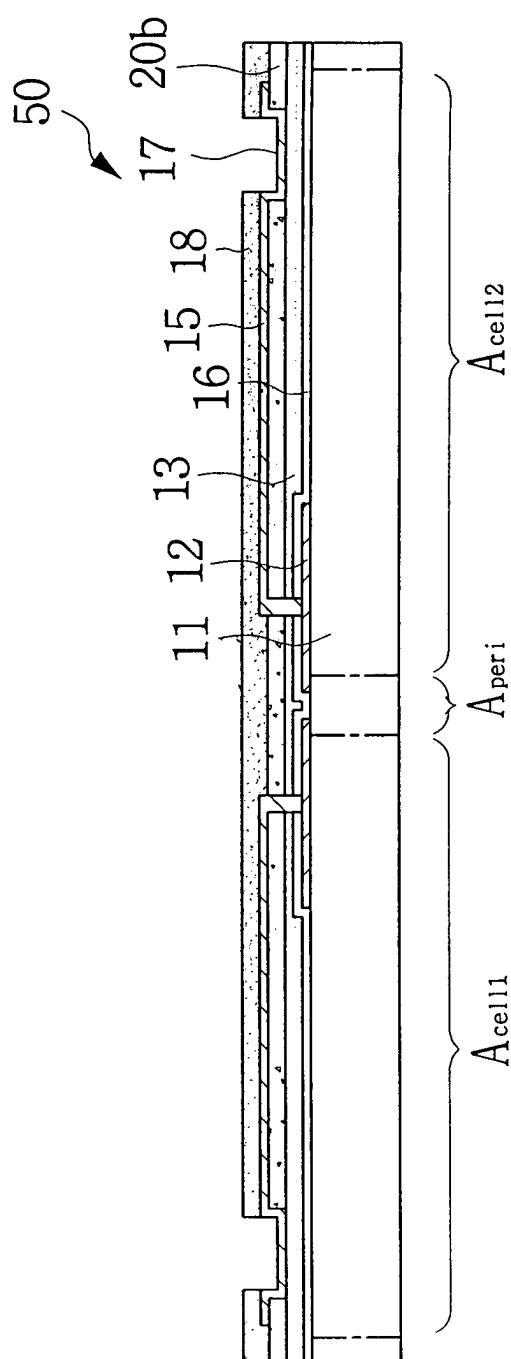

[0027] [Fig. 13](#) bis [Fig. 15](#) Querschnittsansichten eines erfindungsgemäßen Halbleiterchips in aufeinanderfolgenden Stufen eines Verfahrens zur Herstellung desselben,

[0028] [Fig. 16](#) eine Querschnittsansicht eines weiteren nicht erfindungsgemäßen Halbleiterchips,

[0029] [Fig. 17](#) eine Querschnittsansicht einer erfindungsgemäßen MCP,

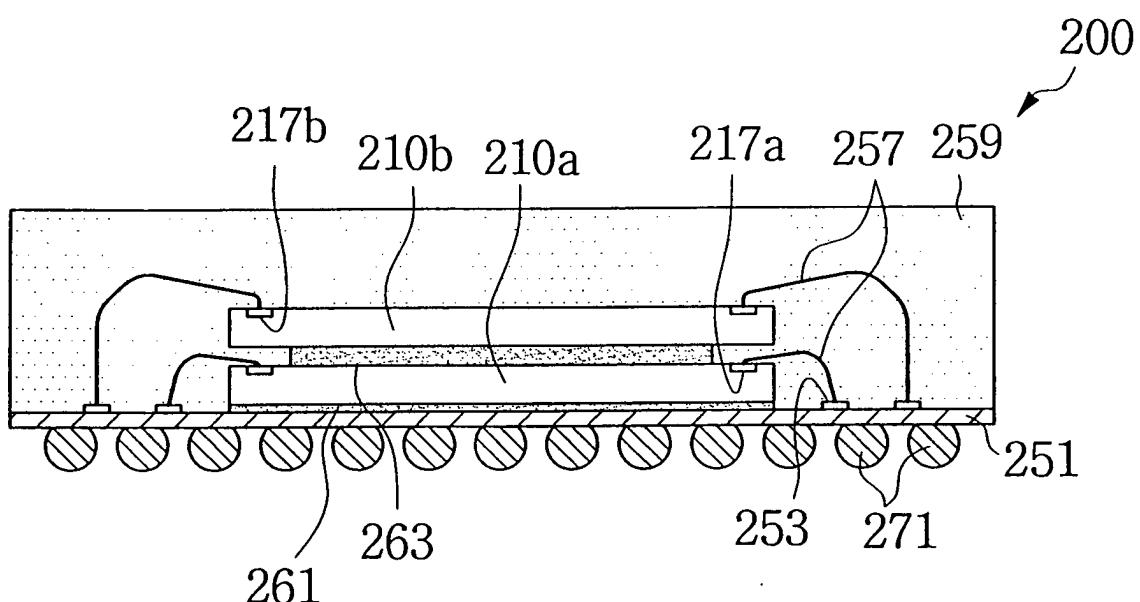

[0030] [Fig. 18](#) eine Querschnittsansicht einer weiteren erfindungsgemäßen MCP,

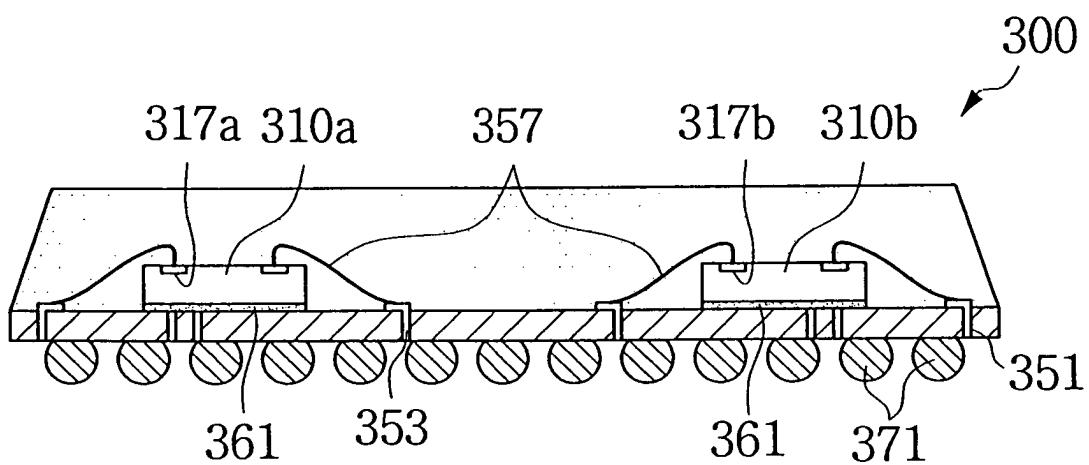

[0031] [Fig. 19](#) eine Querschnittsansicht noch einer weiteren erfindungsgemäßen MCP,

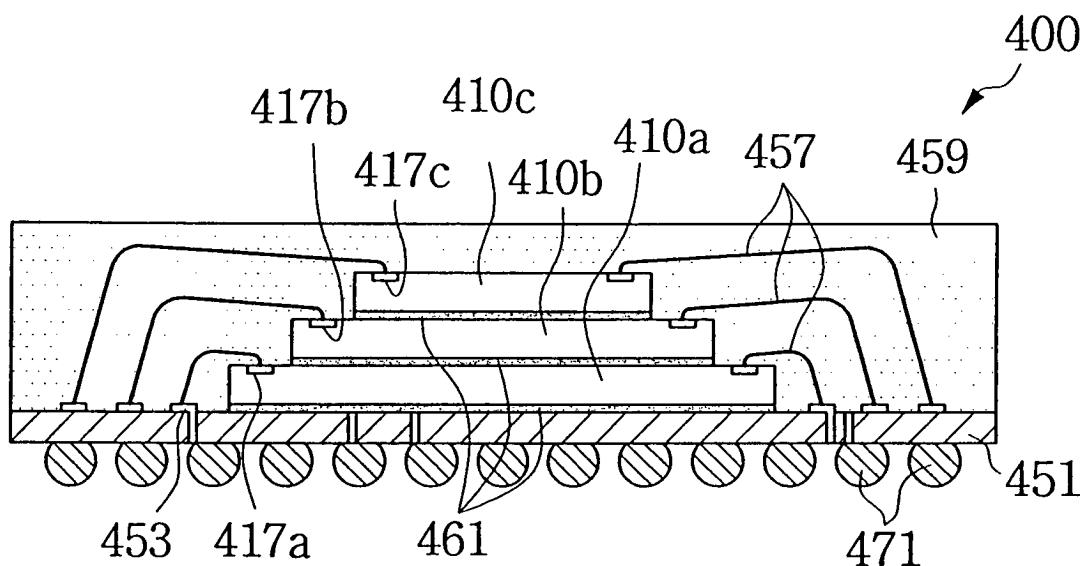

[0032] [Fig. 20](#) eine Querschnittsansicht noch einer weiteren erfindungsgemäßen MCP,

[0033] [Fig. 21](#) eine Querschnittsansicht noch einer weiteren erfindungsgemäßen MCP und

[0034] [Fig. 22](#) eine Querschnittsansicht noch einer weiteren erfindungsgemäßen MCP.

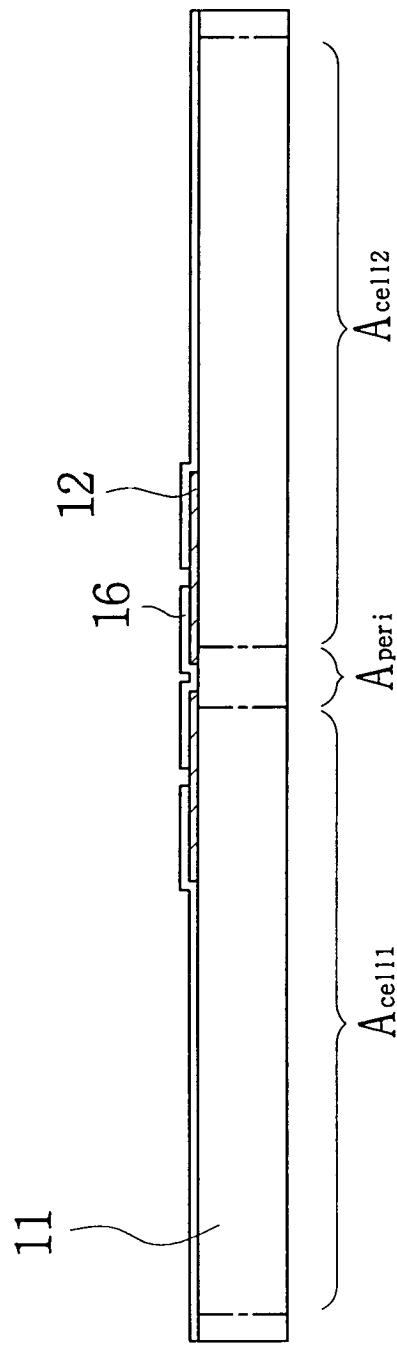

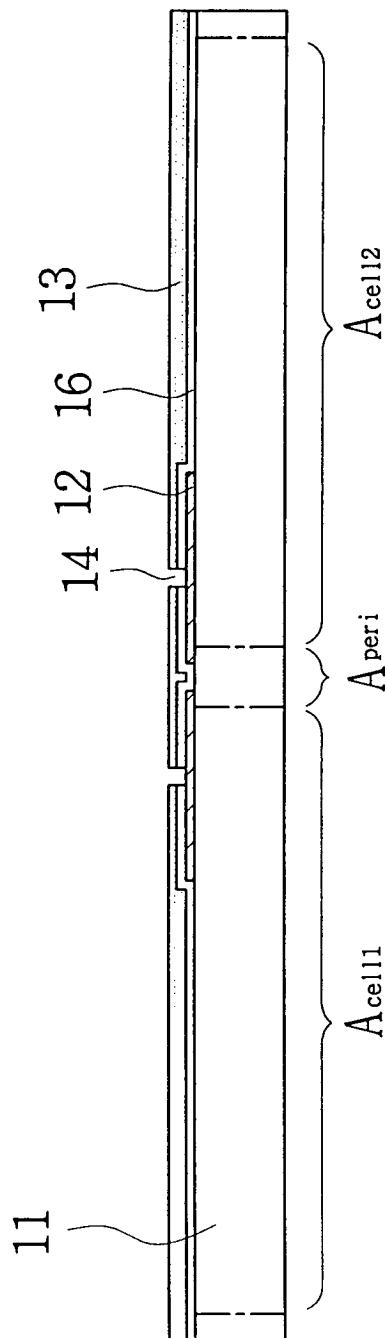

[0035] [Fig. 8](#) veranschaulicht zum leichteren Verständnis von weiter unten erläuterten, erfindungsgemäßen Ausführungsformen im Querschnitt einen nicht erfindungsgemäß aufgebauten Halbleiterchip **10** mit einem Halbleitersubstrat **11**, das darauf gebildete, integrierte Schaltkreise beinhaltet. Insbesondere umfasst das Halbleitersubstrat **11** einen in einem Mittenbereich desselben gebildeten, peripheren Schaltkreisbereich  $A_{peri}$  sowie auf den beiden Seiten des peripheren Schaltkreisbereichs  $A_{peri}$  angeordnete Zellenbereiche  $A_{cell1}$  und  $A_{cell2}$ . In einem vorgegebenen Gebiet des Substrats **11** ist eine Bondkontaktstellen-Verdrahtungsstruktur **12** ausgebildet. Die Bondkontaktstellen-Verdrahtungsstruktur **12** kann aus einem Metall mit ausgezeichneter elektrischer Leitfähigkeit hergestellt sein, z.B. aus Aluminium (Al).

[0036] Die Bondkontaktstellen-Verdrahtungsstruktur **12** ist in einem Mittenbereich des Halbleitersubstrats **11** ausgebildet. Ein Endbereich der Bondkontaktstellen-Verdrahtungsstruktur **12** ist auf dem Teil des peripheren Schaltkreisbereichs  $A_{peri}$  gebildet. Beim herkömmlichen Halbleiterchip, wie oben erläutert, wird ein zusätzliches Chipgebiet in peripheren Schaltkreisbereichen benötigt, um Bondkontaktstellen mit einer minimalen Abmessung und einem minimalen Rastermaß gemäß Entwurf für elektrische Chipsortierung (EDS) und zum Herstellen elektrischer Zwischenverbindungen zu bilden. Beim vorliegenden Beispiel wird hingegen kein größerer, zusätzlicher Flächenbereich zur Bildung von Bondkontakt-

stellen benötigt, sondern es muss nur der kleine Teil für die Bondkontaktstellen-Verdrahtungsstruktur **12** auf dem peripheren Schaltkreisbereich  $A_{peri}$  gebildet werden. Der restliche Teil der Bondkontaktstellen-Verdrahtungsstruktur **12** erstreckt sich bei dieser erfindungsgemäßen Realisierung über einen Teil des Zellenbereichs hinweg. Die Breite des Halbleitersubstrats **11** kann daher um etwa die Breite des Bondkontaktstellengebiets des herkömmlichen Halbleiterchips verringert werden.

[0037] Gemäß der Erfindung kann die gesamte Chipabmessung unter Verwendung der oben angegebenen Prinzipien der Erfindung beträchtlich reduziert werden, wie sie oben bereits angedeutet wurden und nachfolgend weiter im Detail beschrieben werden.

[0038] Wie aus den [Fig. 5](#) bis [Fig. 8](#) des weiteren ersichtlich, wird in dieser nicht erfindungsgemäßen Realisierung auf der Bondkontaktstellen-Verdrahtungsstruktur **12** eine Passivierungsschicht **16** ausgebildet. Auf die Passivierungsschicht **16** wird dann eine dielektrische Zwischenschicht (ILD) **13** aufgebracht. Die ILD **13** besteht aus einem Material, das gute Isolations- und Integrationseigenschaften aufweist, um Bondkontaktstellen **17** vor mechanischen Spannungen durch nachfolgendes Drahtboden, Anschlussfahnen-Bonden oder Kugelboden zu schützen. Beispielsweise kann für die ILD **13** eine durch ein Plasma hoher Dichte (HDP) oxidierte Schicht, eine Benzocyclobuten(BCB)-Schicht, eine Polybenzoxazol(PBO)-Schicht oder eine Polyimid-Schicht verwendet werden. Bevorzugt wird eine HDP-Oxidschicht unter Verwendung von Silan-, Sauerstoff- und Argongasen, beispielsweise eine HDP-SiO<sub>2</sub>-Schicht, verwendet. Die Passivierungsschicht **16** und die ILD **13** weisen darin gebildete Öffnungen **14** auf, um vorgegebene Teile der Bondkontaktstellen-Verdrahtungsstruktur **12** freizulegen.

[0039] Auf der ILD **13** wird entsprechend einem vorgegebenen Layout eine Kontaktstellen-Umordnungsstruktur **15** erzeugt. Wie im Bereich "A" von [Fig. 8](#) gezeigt, werden die Öffnungen **14** mit der Kontaktstellen-Umordnungsstruktur **15** gefüllt. Eine alternative nicht erfindungsgemäße Konfiguration für den Bereich A von [Fig. 8](#) ist in [Fig. 10](#) gezeigt. Die Kontaktstellen-Umordnungsstruktur **15** weist vorzugsweise drei Schichten auf. Diese drei Schichten können beispielsweise eine Titan(Ti)-Schicht mit einer Dicke von etwa 30nm bis 50nm, eine Aluminium(Al)-Schicht mit einer Dicke von etwa 1500nm und eine Titannitrid(TiN)-Schicht mit einer Dicke von etwa 30nm bis 50nm beinhalten. Die Kontaktstellen-Umordnungsstruktur **15** kann aus Kupfer (Cu), Aluminium (Al), Zink (Zn), Eisen (Fe), Platin (Pt), Kobalt (Co), Blei (Pb), Nickel (Ni) oder einer Legierung mehrerer dieser Elemente gebildet sein.

**[0040]** Auf der Kontaktstellen-Umordnungsstruktur **15** wird eine Isolationsschicht **18** aufgebracht. Die Isolationsschicht **18** kann eine HDP-Oxidschicht sein, z.B. eine HDP-SiO<sub>2</sub>-Schicht oder eine HDP-SiN-Schicht. Sie kann außerdem eine Polyimid-Schicht auf der HDP-SiO<sub>2</sub>-Schicht beinhalten, um integrierte Schaltkreise vor Alphateilchen zu schützen. Ein vorgegebener Teil der Kontaktstellen-Umordnungsstruktur **15** wird durch die Isolationsschicht freigelegt, um die Bondkontaktstellen **17** zu definieren. Die Bondkontaktstellen **17** fluchen vorzugsweise mit der Kontaktstellen-Umordnungsstruktur **15** und sind über wenigstens einem Teil der Zellenbereiche A<sub>cell1</sub>, A<sub>cell2</sub> des Substrats **11** angeordnet. Während im Beispiel von [Fig. 9](#) die Bondkontaktstellen **17** in einer einzelnen Reihe entlang gegenüberliegender Kanten des Substrats **11** angeordnet sind, können die Bondkontaktstellen **17** alternativ auch entlang von allen vier Kanten oder in einer Zick-Zack-Form angeordnet sein.

**[0041]** Die Kontaktstellen-Umordnungsstruktur **15** bewirkt eine Neuplatzierung der Bondkontaktstellen **17** von der Bondkontaktstellen-Verdrahtungsstruktur **12** im peripheren Schaltkreisbereich A<sub>peri</sub> in einen Bereich über den Zellenbereichen A<sub>cell1</sub> und A<sub>cell2</sub>. Wie oben angegeben, ist ein Endbereich der Kontaktstellen-Umordnungsstruktur **15** elektrisch mit der freiliegenden Bondkontaktstellen-Verdrahtungsstruktur **12** über die Öffnungen **14** verbunden. Der andere Endbereich erstreckt sich in Richtung der Kante des Substrats **11**. Mit anderen Worten erstreckt sich der Teil der Kontaktstellen-Umordnungsstruktur **15** im wesentlichen vom Mittenbereich des Halbleitersubstrats **11** zum Kantenbereich des Halbleitersubstrats **11**. Die Bondkontaktstellen **17** können daher entlang den Seiten des Halbleitersubstrats **11** gebildet sein. Somit können Halbleiterchips vom peripheren Kontaktstellentyp unter Verwendung von Halbleiterchips vom Mittenanschluss typ hergestellt werden, die dafür bekannt sind, dass sie im Vergleich zu den Chips vom peripheren Anschluss typ verbesserte elektrische Leistungseigenschaften aufweisen. Das Rastermaß zwischen den Bondkontaktstellen kann erhöht werden. Während eines EDS-Tests kann eine Probe problemlos mit den Bondkontaktstellen kontaktiert werden. Diese modifizierten Chips vom peripheren Anschluss typ brauchen daher nicht in einer Packung vom "Lead-on-Chip" (LOC)-Typ gepackt werden, sondern können in einer herkömmlichen Packung implementiert sein.

**[0042]** Wie anhand des Beispiels von [Fig. 11](#) ersichtlich, können mit den Bondkontaktstellen **17** elektrische Verbindungsmittel, wie Bonddrähte **99**, gekoppelt sein. Falls erforderlich, können die Positionen der Bondkontaktstellen **17** in Abhängigkeit vom Entwurf und der Struktur der elektrischen Zwischenverbindungen passend festgelegt werden.

**[0043]** Wie oben erläutert, sind die Bondkontaktstellen **17** bei dieser Realisierung vorzugsweise über wenigstens einem Teil der Zellenbereiche des Substrats **11** ausgebildet. Daher weist der peripheren Schaltkreisbereich A<sub>peri</sub> eine deutlich geringere Breite auf als der herkömmliche peripheren Schaltkreisbereich. Somit kann die Gesamtbreite des Halbleiterchips **10** reduziert werden. Die Breiten der Zellenbereiche A<sub>cell1</sub> und A<sub>cell2</sub> können gleich groß sein wie beim herkömmlichen Zellenbereich. Es versteht sich, dass die Gesamtdicke des Halbleiterchips **10** durch die Bildung der Kontaktstellen-Umordnungsstruktur **15** und der Isolationsschicht **18** über den Zellenbereichen A<sub>cell1</sub> oder A<sub>cell2</sub> anwächst. Der erhöhte Prozentsatz an Gesamtdicke des Chips **10** ist jedoch nicht höher als der verringerte Prozentsatz an Gesamtbreite des Chips **10**, so dass die Gesamtdimension des Chips **10** verringert werden kann.

**[0044]** Nachfolgend wird ein Verfahren zur Herstellung des oben erläuterten, nicht erfindungsgemäßen Halbleiterchips **10** näher erläutert. Wie aus [Fig. 5](#) ersichtlich, umfasst das Halbleitersubstrat **11** Schaltkreise auf dem Chip, die auf den Zellenbereichen A<sub>cell1</sub> und A<sub>cell2</sub> und dem peripheren Schaltkreisbereich A<sub>peri</sub> ausgebildet sind. Wenn der Halbleiterchip **10** ein Speicherbauelement ist, sind die auf den Zellenbereichen A<sub>cell1</sub> und A<sub>cell2</sub> ausgebildeten Schaltkreise Speicherzellen mit MOS-Transistoren und Kondensatoren, während die im peripheren Schaltkreisbereich ausgebildeten Schaltkreise beispielsweise Adressdecodierschaltungen und Dateneingabe-/Datenausgabepuffer für die Speicherzellen enthalten. Die Bondkontaktstellen-Verdrahtungsstruktur **12** wird auf dem Substrat **11** zur selektiven Verbindung mit den integrierten Schaltkreisen gebildet. Dann wird auf der Bondkontaktstellen-Verdrahtungsstruktur **12** die Passivierungsschicht **16** gebildet. Die Bondkontaktstellen-Verdrahtungsstruktur **12** wird unter Verwendung herkömmlicher Techniken, z.B. chemische Gasphasenabscheidung (CVD) oder physikalische Gasphasenabscheidung (PVD) einschließlich Sputtern, in einem vorgegebenen Layout gebildet. Wie oben erläutert, kann die Bondkontaktstellen-Verdrahtungsstruktur **12** sowohl in den Zellenbereichen A<sub>cell1</sub> und A<sub>cell2</sub> als auch im peripheren Schaltkreisbereich A<sub>peri</sub> gebildet werden, alternativ ist jedoch auch in nicht gezeigter Weise eine Bildung derselben nur in den Zellenbereichen A<sub>cell1</sub> und A<sub>cell2</sub> möglich.

**[0045]** Gemäß [Fig. 6](#) wird dann die ILD **13** auf der Passivierungsschicht **16** gebildet. Anschließend werden Öffnungen **14** erzeugt, die sich durch die Passivierungsschicht **16** und die ILD **13** hindurch erstrecken, um vorgegebene Teile der Bondkontaktstellen-Verdrahtungsstruktur **12** freizulegen. Die ILD **13** besteht aus einem Material mit guten Integrations- und Isolationseigenschaften, wie HDP-SiO<sub>2</sub>. Dadurch können die integrierten Schaltkreise unter der ILD **13** vor physikalischen Belastungen während der Bildung

elektrischer Zwischenverbindungen geschützt werden. Die ILD **13** unterstützt außerdem die Planarisierung der darunter liegenden Struktur. Die Öffnungen **14** können entweder über den Zellenbereichen  $A_{cell1}$  und  $A_{cell2}$  oder über dem peripheren Schaltkreisbereich  $A_{peri}$  ausgebildet werden.

**[0046]** Wenngleich das vorstehende Beispiel eine einzelne ILD aufweist, sind in alternativen Realisierungen auch zwei oder mehr ILDs möglich, wie in den [Fig. 12](#) und [Fig. 16](#) gezeigt. Wie aus den [Fig. 12](#) und [Fig. 16](#) ersichtlich, sind in den betreffenden nicht erfindungsgemäßen Ausführungsbeispielen zwischen der ILD **13** und der Kontaktstellen-Umordnungsstruktur **15** zweite ILDs **20a**, **20** vorgesehen. Insbesondere werden, wie in den [Fig. 12](#) und [Fig. 16](#) veranschaulicht, durch das Zwischenfügen der zweiten ILDs **20a**, **20** zwischen die ILD **13** und die Kontaktstellen-Umordnungsstruktur **15** die elektrischen Eigenschaften der Halbleiterchips **30**, **90** verbessert. Beispielsweise kann die Kapazität verringert werden. Die Dicke der zweiten ILD **20a** beträgt zwischen 2 µm bis 50 µm, beispielsweise bestimmt auf der Basis zusätzlicher Kapazitäts- und Intensitätsbetrachtung. Die zweite ILD **20a** kann aus Benzocyclobuten (BCB), Polybenzoxazol (PBO), Polyimid usw. bestehen. Außerdem wird in diesem Fall vorzugsweise der Planarisierungsprozess für die ILDs durchgeführt, um die Planarität der ILDs **13**, **20a** bzw. **20** zu verbessern. Dementsprechend kann wiederum die Planarität der Kontaktstellen-Umordnungsstruktur **15** verbessert werden. Des Weiteren werden Verbindungsauflöse der Bonddrähte oder Anschlussfahnen auf den Bondkontakte **17** vermieden, und die Adhäsion zwischen diesen Anschlusskomponenten wird verbessert. Die Planarisierung wird vorzugsweise durch chemisches und mechanisches Polieren (CMP) ausgeführt.

**[0047]** Die ILDs **13** und **20** des Halbleiterchips **90**, wie in [Fig. 16](#) gezeigt, verteilen mechanische Belastungen während der Bildung der elektrischen Zwischenverbindungen und schützen die Bondkontakte **17** vor den mechanischen Belastungen. Zusätzlich wird die Bondstabilität des Drahtbondens zwischen den Bondkontakte **17** und einem externen Bauelement verbessert, da die Bondkontakte **17** nach zwei Planarisierungsprozessen für die beiden ILDs gebildet werden.

**[0048]** Wie in [Fig. 7](#) gezeigt, wird dann auf der ILD **13** die Kontaktstellen-Umordnungsstruktur **15** erzeugt. Die Kontaktstellen-Umordnungsstruktur **15** füllt die Öffnungen **14** und ist elektrisch mit der Bondkontakte-Verdrahtungsstruktur **12** verbunden. Die Kontaktstellen-Umordnungsstruktur **15** wird beispielsweise durch CVD oder Sputtern in einem gewünschten Layout erhalten.

**[0049]** Gemäß [Fig. 8](#) wird anschließend auf der Kontaktstellen-Umordnungsstruktur **15** eine Isolati-

onsschicht **18** gebildet, die eine Öffnung zur Freilegung vorgegebener Teile der Kontaktstellen-Umordnungsstruktur **15** beinhaltet. Die freigelegten Teile der Struktur **15** sind als die Bondkontakte **17** definiert. Die Isolationsschicht **18** besteht vorzugsweise aus HDP-SiO<sub>2</sub>, um die integrierten Schaltkreise vor mechanischen Belastungen zu schützen. Des Weiteren kann die Isolationsschicht **18** eine Polyimidsschicht auf der HDP-SiO<sub>2</sub>-Schicht aufweisen, um die integrierten Schaltkreise vor Alphateilchen zu schützen. Die ILD **20a** und die Isolationsschicht **18** können alternativ aus Polymid bestehen.

**[0050]** Die [Fig. 13](#) bis [Fig. 15](#) veranschaulichen in Querschnittsansichten ein Verfahren zur Herstellung eines erfindungsgemäßen Halbleiterchips in aufeinanderfolgenden Herstellungsstufen. In diesem Ausführungsbeispiel weist der Halbleiterchip **50**, wie in [Fig. 15](#) gezeigt, eine zweite ILD **20b** auf einer ersten ILD **13** auf. Die Bondkontakte **17** sind in diesem Ausführungsbeispiel jedoch auf der ersten ILD **13** ausgebildet. Um einen Pufferungseffekt aufgrund der mechanischen Belastung der elektrischen Zwischenverbindungen zu vermeiden, werden Teile der zweiten ILD **20b** unter den Bondkontakte **17** entfernt.

**[0051]** Wie aus den [Fig. 13](#) bis [Fig. 15](#) ersichtlich, ist ein Halbleitersubstrat **11** mit einer Bondkontakte-Verdrahtungsstruktur **12** vorgesehen, die auf wenigstens einem Teil des peripheren Schaltkreisbereichs  $A_{peri}$  ausgebildet und damit elektrisch verbunden ist. Auf dem Halbleitersubstrat **11** und der Bondkontakte-Verdrahtungsstruktur **12** ist eine Passivierungsschicht **16** ausgebildet. Die erste ILD **13** wird über dem Halbleitersubstrat **11** mit der Bondkontakte-Verdrahtungsstruktur **12** aufgebracht. Die zweite ILD **20b** wird dann über die erste ILD **13** aufgebracht. Eine erste Öffnung **22** wird durch die erste und zweite ILD **13**, **20b** und die Passivierungsschicht **16** hindurch eingebracht, um einen Teil der Bondkontakte-Verdrahtungsstruktur **12** freizulegen. Eine zweite Öffnung **24** wird durch die zweite ILD **20b** hindurch eingebracht, um einen Teil der ersten ILD **13** freizulegen. Über der zweiten ILD **20b** und innerhalb der ersten Öffnung **22** wird eine Kontaktstellen-Umordnungsstruktur **15** ausgebildet und elektrisch mit der Bondkontakte-Verdrahtungsstruktur **12** verbunden. Die Kontaktstellen-Umordnungsstruktur **15** wird außerdem innerhalb der zweiten Öffnung **24** vorgesehen. Über der Kontaktstellen-Umordnungsstruktur **15** wird eine Isolationsschicht **18** aufgebracht, die eine Öffnung **26** aufweist, welche einen Teil der innerhalb der zweiten Öffnung **24** ausgebildeten Kontaktstellen-Umordnungsstruktur **15** freilegt, um die Bondkontakte **17** über wenigstens einem Teil des Zellenbereichs  $A_{cell}$  zu definieren. Die nicht durch die Isolationsschicht **18** bedeckten Teile der Kontaktstellen-Umordnungsstruktur **15** stellen die Bondkontakte **17** bereit. Dieses Ausführungsbeispiel besitzt

vergleichbare Eigenschaften wie das zuvor beschriebene. Beispielsweise ist die Bondkontaktstellen-Verdrahtungsstruktur **12** im wesentlichen in einem Mittenbereich des Halbleitersubstrats **11** ausgebildet.

**[0052]** Wie nachstehend erläutert, können verschiedene MCPs unter Verwendung erfindungsgemäßer Realisierungen von Halbleiterchips erhalten werden. In einer Realisierung gemäß [Fig. 17](#) weist eine MCP **200** vorzugsweise einen ersten Chip **210a** und einen zweiten Chip **210b** auf, die vertikal auf einem Packungssubstrat **251** übereinander gestapelt sind. Als Packungssubstrat **251** kann eine gedruckte Leiterplatte (PCB) oder ein Folienverdrahtungssubstrat verwendet werden. Diese Substratoberfläche weist vorzugsweise eine Mehrzahl von darauf ausgebildeten Bondspitzen **253** auf. Beim ersten und zweiten Chip **210a, 210b** handelt es sich bevorzugt um denselben Typ von Chips. Beide Chips **210a, 210b** können Strukturen beinhalten, die gemäß den oben erläuterten Prinzipien der Erfindung gebildet sind. Beispielsweise kann eine Bondkontaktstellen-Verdrahtungsstruktur im wesentlichen in einem Mittenbereich eines Halbleitersubstrats ausgebildet sein. Dementsprechend sind Bondkontaktstellen **217a, 217b** des ersten und zweiten Chips **210a, 210b** über Zellenbereichen entlang von Seitenbereichen der Chips **210a, 210b** ausgebildet. Die Chips **210a, 210b** können folglich eine modifizierte Konfiguration aufweisen, beispielsweise kann ein Chip vom Mittenanschlussstyp in einen solchen vom peripheren Anschlussstyp modifiziert werden.

**[0053]** Der erste und der zweite Chip **210a, 210b** sind elektrisch mit dem Packungssubstrat **251** durch elektrische Verbindungsmitte z.B. in Form von Bonddrähten **257** verbunden, die ihrerseits elektrisch mit den Bondspitzen **253** verbunden sind. Jede Bondspitze **253** ist daher mit jeweils einer der Bondkontaktstellen **217a, 217b** verbunden.

**[0054]** Der erste Chip **210a** ist auf dem Packungssubstrat **251** durch ein Klebemittel **261** montiert, und der zweite Chip **210b** ist auf dem ersten Chip **210a** durch ein Klebematerial **263** montiert. Das Klebematerial **263** ist zwischen den ersten und zweiten Chip **201, 210b** zwischengefügt, so dass ausreichend Platz für die Bonddrähte **257** gewährleistet ist, die zum Verbinden des ersten Chips **210a** mit dem Packungssubstrat **251** verwendet werden.

**[0055]** Eine Verkapselung **259** aus einem Material wie z.B. einer Epoxid-Gießverbindung schützt die Oberseite des Packungssubstrats **251** vor äußeren Umgebungseinflüssen, indem sie den ersten und zweiten Chip **210a, 210b** und die Bonddrähte **257** einkapselt. Auf der Unterseite des Packungssubstrats **253** sind Lotkugel **271** ausgebildet, um externe Verbindungsanschlüsse bereitzustellen.

**[0056]** Da die MCP **200** gemäß diesem Ausführungsbeispiel mehrere Halbleiterchips in einem einzelnen Packungskörper beinhaltet, können die Prinzipien der Erfindung, wie oben erläutert, zur Steigerung der Speicherkapazität sowie der Anzahl an Eingabe/Ausgabe-Anschlüssen ohne komplizierte Montageprozesse verwendet werden.

**[0057]** [Fig. 18](#) zeigt als weiteres erfindungsgemäßes Ausführungsbeispiel eine MCP **300** mit einem ersten Chip **310a** und einem zweiten Chip **310b**, die seitlich nebeneinander auf einem Packungssubstrat **351** montiert sind. Der erste und zweite Chip **310a, 310b** weisen hierbei vorzugsweise dieselben oder ähnliche Strukturen, wie sie weiter unten in Verbindung mit [Fig. 20](#) erläutert werden, oder dieselben oder ähnliche Strukturen wie die oben erläuterten Chiprealisierungen auf. Beispielsweise sind der erste und der zweite Chip **310a, 310b** bevorzugt durch Bonddrähte **357** über Bondspitzen **353** elektrisch mit dem Substrat **351** verbunden. Mit Bezugszeichen **359, 361** und **371** sind eine Verkapselung, Klebemittel bzw. Lotkugeln bezeichnet.

**[0058]** [Fig. 19](#) zeigt eine weitere erfindungsgemäßes MCP **400** mit drei Halbleiterchips **410a, 410b, 410c**, die übereinander auf ein Packungssubstrat **451** gestapelt sind. Die Chips **410a, 410b, 410c** weisen bevorzugt dieselben oder ähnliche Strukturen auf, wie sie zuvor gemäß den Prinzipien der Erfindung erläutert wurden. Beispielsweise sind die Halbleiterchips **410a, 410b, 410c** bevorzugt vom peripheren Anschlussstyp mit Umordnungs-Bondkontaktstellen **417a, 417b, 417c**, die über Zellenbereichen entlang von Rand- oder Seitenbereichen derselben ausgebildet sind. Die Halbleiterchips **410a, 410b, 410c** können voneinander verschiedene Breiten aufweisen. Beispielsweise sind die Halbleiterchips **410a, 410b, 410c** vorzugsweise in der Reihenfolge ihrer Abmessung übereinander gestapelt, d.h. beginnend mit dem größten Chip **410a** bis zum kleinsten Chip **410c**. Je nach Anwendungsfall sind jedoch andere Konfigurationen möglich. Beispielsweise können beliebige zwei der drei Chips **410a, 410b, 410c** in alternativen Ausführungsformen dieselbe Abmessung besitzen.

**[0059]** Die Halbleiterchips **410a, 410b, 410c** sind vorzugsweise durch Bonddrähte **457** über Bondspitzen **453** elektrisch mit dem Substrat **451** verbunden. Wie oben erläutert, kann die MCP **400** in diesem Fall verschiedene Chiparten umfassen. Da der Chip vom Mittenanschlussstyp in einen Chip vom peripheren Anschlussstyp modifiziert wird, ist die Möglichkeit geschaffen, mehrere Chips vertikal übereinander zu stapeln, und die Längen der Bonddrähte können vergleichsweise kurz gehalten werden, was ein leichteres Drahtboden erlaubt.

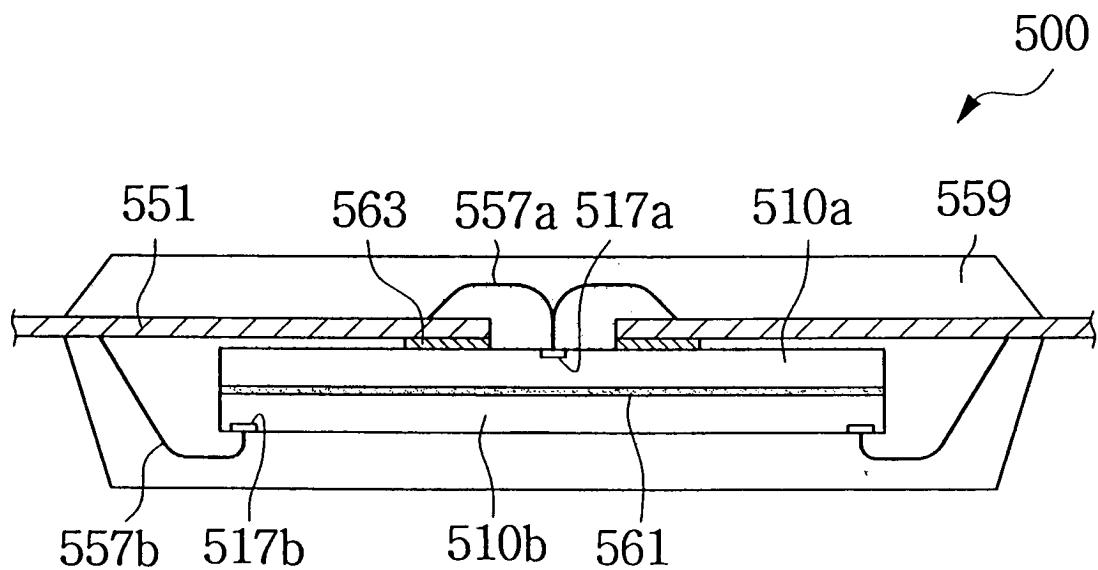

**[0060]** [Fig. 20](#) zeigt eine weitere erfindungsgemäßes MCP **500** in Form einer dualen Chippackung (DDP)

mit einem ersten und zweiten Halbleiterchip **510a**, **510b**. Ein Leiterrahmen **551** wird zur Montage der Chips **510a**, **510b** verwendet. Der zweite Halbleiterchip **510b** ist vorzugsweise gemäß den oben erläuterten Prinzipien der Erfindung gebildet. Beispielsweise kann er ein Chip vom peripheren Anschlussstyp mit einer auf dem peripheren Schaltkreisbereich entlang von Seitenbereichen des Chips **510b** ausgebildeten Umordnungs-Bondkontaktstelle **517b** sein. Im Gegensatz dazu weist der erste Halbleiterchip **510a** bevorzugt eine Bondkontaktstelle **517a** gemäß dem Mittenanschlussstyp auf.

**[0061]** Die MCP **500** weist in diesem Beispiel keine Chipkontaktstelle zum Montieren der Halbleiterchips **510a**, **510b** auf. Stattdessen werden bevorzugt die Anschlussleiter des Leiterrahmens **551** in dieser Packung vom LOC-Typ verwendet. Die Länge der Anschlussleiter des Leiterrahmens **551** ist bevorzugt größer als diejenige der herkömmlichen Anschlussleiter, dies ist jedoch nicht zwingend. Die Oberseite des ersten Halbleiterchips **510a** ist an die Unterseiten gegenüberliegender Anschlussleiter des Leiterrahmens **551** durch Klebestreifen **563** montiert. Die Bondkontaktstelle **517a** des ersten Chips **510a** befindet sich zwischen den gegenüberliegenden Anschlussleitern des Leiterrahmens **551** und ist an die Oberseite der zugehörigen Anschlussleiter des Leiterrahmens **551** mittels Bonddrähten **557a** drahtgebondet. Die Oberseite des zweiten Chips **510b** ist an die Unterseite des ersten Chips **510a** durch ein Klebemittel **561** montiert. Die Umordnungs-Bondkontaktstelle **517b** des zweiten Chips **510b** ist an die Unterseite der zugehörigen Anschlussleiter des Leiterrahmens **551** mittels Bonddrähten **557b** drahtgebondet. Der erste und der zweite Chip **510a**, **510b** und die zugehörigen Bonddrähte **557a**, **557b** sind durch eine Verkapselung **559** ver kapselt.

**[0062]** Insgesamt stellt dadurch die MCP **500** eine DDP dar, die Halbleiterchips beinhaltet, welche vom Mittenanschlussstyp in den peripheren Anschlussstyp oder umgekehrt modifiziert sind. Außerdem können für die MCP **500** größere Halbleiterchips verwendet werden als bei den zuvor beschriebenen Ausführungsformen.

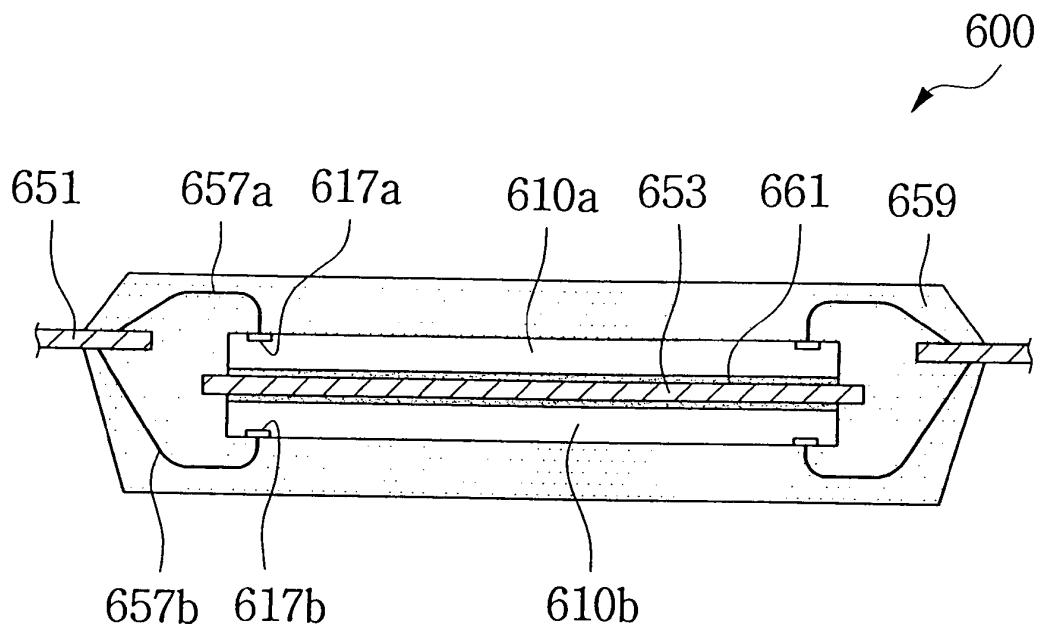

**[0063]** [Fig. 21](#) zeigt eine weitere erfindungsgemäße MCP **600** in Form einer DDP mit einem ersten und einem zweiten Halbleiterchip **610a**, **610b**. Eine Chipkontaktstelle **653** und Anschlussleiter **651** werden zur Montage der Chips **610a**, **610b** benutzt. Der erste und der zweite Chip **610a**, **610b** sind vorzugsweise vom peripheren Anschlussstyp, wobei Bondkontaktstellen **617a**, **617b** entlang von Seitenbereichen der Chips **610a**, **610b** ausgebildet sind. Der erste und der zweite Chip **610a**, **610b** sind an die Oberseite bzw. die Unterseite der Chipkontaktstelle **653** durch ein Klebemittel **661** montiert. Die Bondkontaktstellen **617a** des ersten Chips **610a** sind an die Oberseiten

der Anschlussleiter **651** mittels Bonddrähten **657a** drahtgebondet. Die Bondkontaktestellen **617b** des zweiten Chips **610b** sind an die Unterseiten der Anschlussleiter **651** mittels Bonddrähten **657b** drahtgebondet. Der erste und der zweite Chip **610a**, **610b** und die Bonddrähte **657a**, **657b** sind durch eine Verkapselung **659** ver kapselt.

**[0064]** Die MCP **600** gemäß diesem Ausführungsbeispiel weist Chips auf, die gemäß den oben erläuterten Prinzipien der Erfindung ausgebildet sind. Beispielsweise kann die MCP **600** als Halbleiterchips solche beinhalten, die von einem Mittenanschlussstyp in einen peripheren Anschlussstyp modifiziert sind.

**[0065]** [Fig. 22](#) zeigt eine weitere erfindungsgemäße MCP **700** mit vier Halbleiterchips **710a**, **710b**, **710c**, **710d**. Vorzugsweise ist dabei die Breite eines ersten Chips **710a** deutlich größer als diejenige eines zweiten Chips **710b**. Außerdem ist die Breite eines dritten Chips **710c** vorzugsweise deutlich größer als diejenige eines vierten Chips **710d**. Die Breite des ersten Chips **710a** ist außerdem vorzugsweise ungefähr gleich groß wie diejenige des dritten Chips **710c**. Der Fachmann erkennt jedoch ohne weiteres, dass die Abmessungen des ersten und dritten Chips **710a**, **710c** oder des zweiten und vierten Chips **710b**, **710d** nicht zwingend gleich groß sein müssen, sondern je nach Anwendungsfall unterschiedlich gewählt werden können.

**[0066]** Zur Montage der Chips **710a** bis **710d** wird ein Leiterrahmen **751** mit einer Chipkontaktstelle **753** verwendet. Die nicht aktive Oberfläche des ersten Chips **710a** ist an der Oberseite der Chipkontaktstelle **753** angebracht. Die nicht aktive Oberfläche des zweiten Chips **710b** ist an einem Teil der aktiven Oberfläche des ersten Chips **710a** angebracht und die nicht aktive Oberfläche des dritten Chips **710c** ist an der Unterseite der Chipkontaktstelle **753** angebracht. Die nicht aktive Oberfläche des vierten Chips **710d** ist an einem Teil der aktiven Oberfläche des dritten Chips **710c** angebracht. Der erste und der zweite Chip **710a**, **710b** weisen vorzugsweise nach unten, während der dritte und der vierte Chip **710c**, **710d** vorzugsweise nach unten weisen.

**[0067]** Die Bondkontaktstellen **717a**, **717b** des ersten und zweiten Chips **710a**, **710b** sind an die Oberseite der Anschlussleiter des Leiterrahmens **751** über erste bzw. zweite Bonddrähte **757a**, **757b** drahtgebondet. Die Bondkontaktstellen **717c**, **717d** des dritten und vierten Chips **710c**, **710d** sind an die Unterseite der Anschlussleiter des Leiterrahmens **751** durch dritte bzw. vierte Bonddrähte **757c**, **757d** drahtgebondet. Die Halbleiterchips **710a** bis **710d** und die Bonddrähte **757a** bis **757d** sind durch eine Verkapselung **753** ver kapselt. Die Bezugszeichen **761**, **762**, **763** und **764** bezeichnen ein jeweiliges Klebemittel.

**[0068]** In verschiedenen erfindungsgemäßen Ausführungsformen, wie sie oben erläutert wurden, werden elektrische Verbindungen zwischen den Chips und dem Leiterrahmen oder Packungssubstrat bevorzugt durch Drahtboden bewerkstelligt. Alternativ können jedoch andere Techniken bei der Bildung einer erfindungsgemäßen MCP eingesetzt werden.

**[0069]** Des weiteren versteht sich für den Fachmann, dass andere Typen von Leiterrahmen oder Folien statt der gezeigten Leiterrahmen verwendet werden können. Beispielsweise können Leiterrahmen zum Einsatz kommen, die zweifach gebogene innere Anschlussleiter und J-förmig geführte, äußere Anschlussleiter beinhalten. In diesem Fall liegt der gebogene Teil der inneren Leiterstücke über der aktiven Oberfläche eines von mehreren Chips und ist an diesem durch ein Klebeband oder andere geeignete Klebemittel angebracht.

**[0070]** Wenngleich in den verschiedenen gezeigten, bevorzugten Ausführungsformen der Erfindung MCPs veranschaulicht sind, die zwischen zwei und vier Halbleiterchips in einem einzelnen MCP-Körper aufweisen, können je nach Anwendungsfall eine andere Anzahl von Chips in einer MCP enthalten sein.

**[0071]** Die Chips einer Packung können alle vom selben Typ sein, beispielsweise Speicherchips. In einer anderen Ausführungsform kann einer der Chips ein DRAM-Bauelement und ein anderer Chip ein Flash-Speicherbauelement sein. Alternativ können die Chips von unterschiedlichem Typ sein. Beispielsweise kann einer der Chips ein Speicherchip sein, wie ein Flash-Speicher, ein statischer Speicher mit wahlfreiem Zugriff (SRAM) oder ein dynamischer Speicher mit wahlfreiem Zugriff (DRAM), während ein anderer Chip ein Nichtspeicher-Chip sein kann, z.B. ein Mikroprozessor. Die Erfindung kann folglich dazu verwendet werden, ein System in einer Packung (SIP) zu implementieren und dadurch die Packungsdichte signifikant zu steigern.

## Patentansprüche

### 1. Halbleiterchip mit folgenden Merkmalen:

- einem Halbleitersubstrat (11) mit einem Zellenbereich ( $A_{cell1}, A_{cell2}$ ) und einem dazu benachbarten, peripheren Schaltkreisbereich ( $A_{peri}$ ),

- einer Kontaktstellen-Verdrahtungsstruktur (12), die auf dem Halbleitersubstrat im Wesentlichen in einem Mittenbereich des Halbleitersubstrats auf einem Teil des peripheren Schaltkreisbereichs ausgebildet ist und sich über einen Teil des Zellenbereichs erstreckt,

- einer Passivierungsschicht (16) auf dem Halbleitersubstrat und der Kontaktstellen-Verdrahtungsstruktur,

- einer ersten dielektrischen Zwischenschicht (13) auf dem Halbleitersubstrat mit der Kontaktstellen-Verdrahtungsstruktur,

- einer zweiten dielektrischen Zwischenschicht (20b) auf der ersten dielektrischen Zwischenschicht,

- einer ersten Öffnung (22), die sich durch die Passivierungsschicht und die erste und zweite dielektrische Zwischenschicht hindurch im Zellenbereich erstreckt, um dort einen Teil der Kontaktstellen-Verdrahtungsstruktur freizulegen,

- einer zweiten Öffnung (24), die sich im Zellenbereich von der ersten Öffnung beabstandet durch die zweite dielektrische Zwischenschicht hindurch erstreckt, um einen Teil der ersten dielektrischen Zwischenschicht freizulegen,

- einer Kontaktstellen-Umordnungsstruktur (15), die über der zweiten dielektrischen Zwischenschicht und in der ersten und zweiten Öffnung gebildet ist, wobei sie in der ersten Öffnung elektrisch mit der Kontaktstellen-Verdrahtungsstruktur (12) verbunden ist, und

- einer Isolationsschicht (18) über der Kontaktstellen-Umordnungsstruktur, wobei die Isolationsschicht eine darin eingebrachte Öffnung aufweist, die einen innerhalb der zweiten Öffnung gebildeten Teil der Kontaktstellen-Umordnungsstruktur freilegt, um eine Bondkontaktstelle über wenigstens einem Teil des Zellenbereichs zu bilden.

2. Halbleiterchip nach Anspruch 1, weiter dadurch gekennzeichnet, dass auf dem Zehenbereich des Halbleitersubstrats integrierte Schaltkreise ausgebildet sind.

3. Halbleiterchip nach Anspruch 1 oder 2, weiter dadurch gekennzeichnet, dass die Bondkontaktstelle (17) entlang eines Seitenbereichs des Halbleitersubstrats gebildet ist.

4. Halbleiterchip nach einem der Ansprüche 1 bis 3, weiter dadurch gekennzeichnet, dass die erste dielektrische Zwischenschicht planarisierter ist.

5. Halbleiterchip nach einem der Ansprüche 1 bis 4 weiter dadurch gekennzeichnet, dass die Kontaktstellen-Umordnungsstruktur eine Schichtfolge mit einer Titan(Ti)-Schicht, einer Aluminium(Al)-Schicht und einer Titannitrid(TiN)-Schicht beinhaltet.

6. Halbleiterchip nach einem der Ansprüche 1 bis 5, weiter dadurch gekennzeichnet, dass die Kontaktstellen-Umordnungsstruktur Kupfer (Cu), Aluminium (Al), Zink (Zn), Eisen (Fe), Platin (Pt), Kobalt (Co), Blei (Pb), Nickel (Ni) oder eine Legierung aus diesen Elementen beinhaltet.

7. Halbleiter-Mehrchippackung mit

- einem Packungssubstrat (251) mit einer Oberfläche, auf der eine Mehrzahl von Bondspitzen (253) ausgebildet sind, und

- zwei oder mehr Halbleiterchips (210a, 210b), die auf der Substratoberfläche montiert sind, dadurch gekennzeichnet, dass

- wenigstens einer der beiden Halbleiterchips (210a,

**210b)** ein solcher nach einem der Ansprüche 1 bis 7 ist und – jede Bondspitze (**253**) elektrisch mit einer Bondkontaktstelle dieses Halbleiterchips verbunden ist.

8. Mehrchippackung nach Anspruch 7 weiter dadurch gekennzeichnet, dass die zwei oder mehr Chips (**310a**, **310b**) nebeneinander angeordnet sind.

9. Mehrchippackung nach Anspruch 7, weiter dadurch gekennzeichnet, dass die zwei oder mehr Chips (**210a**, **210b**) vertikal übereinander gestapelt sind.

10. Mehrchippackung nach einem der Ansprüche 7 bis 9, weiter dadurch gekennzeichnet, dass die zwei oder mehr Chips vom gleichen Chiptyp sind.

11. Mehrchippackung nach Anspruch 9 oder 10 weiter dadurch gekennzeichnet, dass die zwei oder mehr Chips (**410a**, **410b**, **410c**) wenigstens einen unteren und einen über diesem angeordneten, oberen Chip beinhalten, wobei die Breite des oberen Chip kleiner als diejenige des unteren Chip ist.

12. Mehrchippackung nach einem der Ansprüche 7 bis 9 und 11, weiter dadurch gekennzeichnet, dass die zwei oder mehr Chips einen Speicherchip und einen Nichtspeicher-Chip beinhalten.

13. Mehrchippackung nach einem der Ansprüche 7 bis 11 weiter dadurch gekennzeichnet, dass die zwei oder mehr Chips einen DRAM-Chip und einen Flash-Speicherchip beinhalten.

14. Halbleiter-Mehrchippackung mit – einem Leiterrahmen (**551**) mit einer Vorderseite und einer Rückseite, – einem ersten Chip (**510a**) mit einer Oberseite und einer Unterseite, wobei die Oberseite des ersten Chip an der Rückseite des Leiterrahmens angeordnet ist und der erste Chip Bondkontaktstellen (**517a**) aufweist, die im wesentlichen entlang eines Mittenbereichs der Oberseite ausgebildet sind, und – einem zweiten Chip (**510b**) mit einer Oberseite und einer Unterseite, wobei die Oberseite des zweiten Chip an der Unterseite des ersten Chip angeordnet ist, dadurch gekennzeichnet, dass – der zweite Chip (**510b**) ein Halbleiterchip nach einem der Ansprüche 1 bis 7 ist und – die Bondkontaktstellen (**517a**) des ersten Chip (**510a**) elektrisch mit dem Leiterrahmen (**551**) und die Bondkontaktstellen (**517b**) des zweiten Chip elektrisch mit dem Leiterrahmen verbunden sind.

15. Halbleiter-Mehrchippackung mit – einem Leiterrahmen mit einer Chipkontaktstelle (**653**) und einem Anschlussleiter (**651**), wobei die Chipkontaktstelle eine Vorderseite und eine Rücksei-

te aufweist, und – einem an der Vorderseite der Chipkontaktstelle angeordneten ersten Chip (**610a**) und einem an der Rückseite der Chipkontaktstelle angeordneten zweiten Chip (**610b**), dadurch gekennzeichnet, dass – wenigstens einer der beiden Chips (**610a**, **610b**) ein Halbleiterchip nach einem der Ansprüche 1 bis 7 ist und – die Bondkontaktstellen (**617a**, **617b**) des ersten und zweiten Chip jeweils elektrisch mit dem Anschlussleiter (**651**) verbunden sind.

16. Mehrchippackung nach Anspruch 15, weiter dadurch gekennzeichnet, dass ein zusätzlicher Chip (**710b**, **710d**) auf wenigstens einem von dem ersten und zweiten Chip angeordnet ist, wobei der zusätzliche Chip periphere Kontaktstellen (**717b**, **717d**) aufweist, die elektrisch mit dem Anschlussleiter (**751**) verbunden sind.

17. Mehrchippackung nach Anspruch 16 weiter dadurch gekennzeichnet, dass die Breite des zusätzlichen Chip kleiner als diejenige des ersten oder des zweiten Chip ist.

Es folgen 12 Blatt Zeichnungen

Anhängende Zeichnungen

FIG. 1

(STAND DER TECHNIK)

FIG. 3

(STAND DER TECHNIK)

FIG. 2

(STAND DER TECHNIK)

FIG. 4

(STAND DER TECHNIK)

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

Fig. 16

Fig. 17

Fig. 18

Fig. 19

Fig. 20

Fig. 21

Fig. 22