(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6469427号

(P6469427)

(45) 発行日 平成31年2月13日(2019.2.13)

(24) 登録日 平成31年1月25日(2019.1.25)

|                       |                   |

|-----------------------|-------------------|

| (51) Int.Cl.          | F 1               |

| G09F 9/00 (2006.01)   | G09F 9/00 3 4 6 D |

| G02F 1/1345 (2006.01) | G02F 1/1345       |

| G09F 9/30 (2006.01)   | G09F 9/30 3 3 8   |

請求項の数 12 (全 23 頁)

(21) 出願番号 特願2014-245419 (P2014-245419)

(22) 出願日 平成26年12月3日 (2014.12.3)

(65) 公開番号 特開2016-109791 (P2016-109791A)

(43) 公開日 平成28年6月20日 (2016.6.20)

審査請求日 平成29年9月22日 (2017.9.22)

(73) 特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 100080001

弁理士 筒井 大和

(74) 代理人 100108279

弁理士 青山 仁

(74) 代理人 100113642

弁理士 菅田 篤志

(74) 代理人 100117008

弁理士 筒井 章子

(74) 代理人 100147430

弁理士 坂次 哲也

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1面を備える基板、を有し、

前記第1面は、複数の画素を備える表示領域と、前記複数の画素に供給される信号が入力される入力部と、前記表示領域と前記入力部とを電気的に接続する引出配線部と、を有し、

前記基板は、第1方向に沿って延びる第1辺、前記第1辺の反対側に位置する第2辺、前記第1方向に直交する第2方向に沿って延びる第3辺、および前記第3辺の反対側に位置する第4辺を備え、

前記引出配線部と前記入力部は、前記基板の前記第1辺と前記表示領域との間に設けられ、

前記引出配線部は、複数の第1配線を有する第1配線層と、前記第1配線層の前記第1面と反対側に形成された複数の第2配線を有する第2配線層と、前記第1配線層と前記第2配線層間に形成された第1絶縁層と、前記第2配線層の前記第1面と反対側に形成された第2絶縁層と、を有し、

前記引出配線部において、

前記第1配線層と前記第2配線層は、前記表示領域側において前記第2方向に沿って延在する第1部分と、前記入力部側において前記第2方向に沿って延在する第3部分と、前記第1部分と前記第3部分を接続し、前記第2方向に対して斜めに延在する第2部分と、を有し、

10

20

前記第3部分において、前記第1絶縁層に開口部が形成され、前記開口部を介して前記第1配線層と前記第2配線層が電気的に接続される、表示装置。

**【請求項2】**

請求項1に記載の表示装置であって、

前記第1絶縁層は、無機材料からなり、前記第2絶縁層は、有機絶縁層からなる、表示装置。

**【請求項3】**

請求項1に記載の表示装置であって、

平面視において、前記複数の第1配線と、前記複数の第2配線とは交互に配置され、かつ互いに重ならない、表示装置。 10

**【請求項4】**

請求項3に記載の表示装置であって、

前記開口部の上には、有機絶縁層からなる前記第2絶縁層が形成される、表示装置。

**【請求項5】**

請求項3に記載の表示装置であって、

平面視において、前記複数の第1配線のそれぞれの線幅は、前記複数の第2配線のそれぞれの線幅よりも広い、表示装置。

**【請求項6】**

請求項1に記載の表示装置であって、

前記表示領域の前記複数の画素のそれぞれは、ゲート電極を有するトランジスタを有し 20

、前記第1配線層は、前記ゲート電極と同層に形成されている、表示装置。

**【請求項7】**

請求項1に記載の表示装置であって、

前記複数の第1配線と前記複数の第2配線とは、互いに異なる種類の金属材料により形成されている、表示装置。 20

**【請求項8】**

請求項1に記載の表示装置であって、

前記引出配線部は、複数の第3配線を有する第3配線層をさらに有し、

前記第2配線層と前記第3配線層間には、前記第2絶縁層が形成されている、表示装置 30

。

**【請求項9】**

請求項8に記載の表示装置であって、

平面視において、前記複数の第3配線は、前記複数の第1配線および前記複数の第2配線のうちの一部と重なっている、表示装置。

**【請求項10】**

請求項8に記載の表示装置であって、

平面視において、前記複数の第3配線は、前記複数の第2配線とは互いに重ならず、かつ、前記複数の第1配線と重なっている、表示装置。

**【請求項11】**

請求項8に記載の表示装置であって、

前記引出配線部は、

前記第2絶縁層に開口部が形成され、前記開口部を介して前記第2配線層と前記第3配線層が電気的に接続される、表示装置。 40

**【請求項12】**

請求項1に記載の表示装置であって、

隣り合う第1配線間に、複数本の第2配線が配置される、表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、表示装置に関し、例えば、表示領域に形成された複数の表示素子に信号を伝送する複数の引出配線を有する表示装置に適用して有効な技術に関する。

【背景技術】

【0002】

表示領域に形成された複数の表示素子に複数の引出配線を介して信号を伝送し、画像を表示させる表示装置がある。

【0003】

例えば、特開2007-164219号公報（特許文献1）には、画素領域に形成された複数のゲート線に接続される複数のゲート接続線を、複数の配線層に形成する技術が記載されている。

10

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007-164219号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

表示装置は、例えば、液晶層、あるいはエレクトロルミネッセンスを利用する発光層、などの表示機能層を有する。また、表示装置は、表示領域に形成されたトランジスタなどの複数の表示素子を有する。表示装置では、複数の表示素子に信号を伝送し、表示素子を駆動することにより、画像を表示する。

20

【0006】

上記複数の表示素子に信号を伝送するためには、多数の信号線が必要になる。信号線の数は、表示画像の高精細化に伴って増大する。また、表示装置に対しては、表示領域の周囲を囲む非表示部分である周辺領域、あるいは額縁領域と呼ばれる部分の面積を低減する技術が要求されている。額縁領域には、信号線に接続され、信号線に信号を供給する引出線が形成されている。つまり、表示装置の性能を向上させるためには、額縁領域において、多数の引出線が効率的にレイアウトされている必要がある。

【0007】

そこで、本願発明者は、絶縁膜を介して積層された複数の配線層に多数の引出線を割り振って設けることにより、引出線の配線密度を向上させる技術に関して検討を行い、以下の課題を見出した。なお、引出線は表示領域の信号線に接続しており、信号線の一部であるとも考えられるため、以下、引出線を信号線とも称する。

30

【0008】

すなわち、複数の信号線を積層する場合、各信号線が互いに干渉し、ノイズの影響を受ける原因になる。また、製造プロセス上の理由などにより、配線幅や配線間距離の最小値を規定する設計ルールが、配線層毎に異なる場合、上層の配線層に形成された配線と、下層の配線層に形成された配線とが、交互に配列されるようにすると、信号線の配線密度を十分に向上させることができない場合があることが判った。

【0009】

40

本発明の目的は、表示装置の額縁領域において、複数の配線を効率的に配列する技術を提供することにある。

【課題を解決するための手段】

【0010】

本発明の一態様である表示装置は、第1面を備える基板と、前記基板の前記第1面に設けられた表示機能層と、前記基板の前記第1面に形成され、前記表示機能層を駆動する回路部と、を有し、

前記第1面は、前記表示機能層を駆動するための複数の表示素子が配列された表示素子部と、前記表示素子部に供給される信号が入力される入力部と、前記表示素子部と前記入力部とを電気的に接続する引出配線部と、を有し、

50

前記引出配線部は、絶縁膜を介して積層された複数の配線層を有し、

前記複数の配線層には、第1の配線幅の複数の第1配線が形成された第1配線層と、前記第1の配線幅よりも狭い第2の配線幅の複数の第2配線が形成された第2配線層と、が含まれ、

前記複数の第2配線の数は、前記複数の第1配線の数よりも多い。

#### 【0011】

また、他の一態様として、前記基板の前記第1面は、第1方向に沿って延びる第1辺、前記第1辺の反対側に位置する第2辺、前記第1方向に直交する第2方向に沿って延びる第3辺、および前記第3辺の反対側に位置する第4辺を備え、

前記基板の前記第1辺と前記表示素子部との間には、前記第1辺側から前記入力部、および前記引出配線部が順に設けられ、

前記第1方向における前記入力部の長さは、前記第1方向における前記表示素子部の長さよりも短くても良い。

#### 【0012】

また、他の一態様として、前記基板の前記第1面は、第1方向に沿って延びる第1辺、前記第1辺の反対側に位置する第2辺、前記第1方向に直交する第2方向に沿って延びる第3辺、および前記第3辺の反対側に位置する第4辺を備え、

前記引出配線部は、

前記表示素子部と前記入力部との間において、前記複数の第1配線および前記複数の第2配線を含む複数の引出配線が前記第2方向に沿って延びる第1部分と、

前記第1部分と前記入力部との間において、前記複数の引出配線が前記第2方向および前記第1方向と交差する第3方向に沿って延びる第2部分と、

前記第2部分と前記入力部との間において、前記複数の引出配線が前記第2方向に沿って延びる第3部分と、

を有し、

平面視において、前記複数の第1配線と、前記複数の第2配線とは互いに重ならなくても良い。

#### 【0013】

また、他の一態様として、前記引出配線部の前記第2部分において、

前記複数の第1配線は、第1離間距離で配列され、

前記複数の第2配線は、前記第1離間距離よりも小さい第2離間距離で配列されていても良い。

#### 【0014】

また、他の一態様として、平面視において、前記複数の第1配線のうち、隣り合う第1配線の間には、前記複数の第2配線がそれぞれ複数本ずつ配列されていても良い。

#### 【0015】

また、他の一態様として、前記表示素子部に配列された前記複数の表示素子のそれぞれは、ゲート電極を有するトランジスタであって、

前記ゲート電極は、前記第1配線層と同層に形成されていても良い。

#### 【0016】

また、他の一態様として、前記複数の第1配線と前記複数の第2配線とは、互いに異なる種類の金属材料により形成されていても良い。

#### 【0017】

また、他の一態様として、前記複数の配線層には、前記第2の配線幅よりも広い第3の配線幅の複数の第3配線が形成された第3配線層がさらに含まれ、

前記複数の第2配線の数は、前記複数の第3配線の数よりも多くても良い。

#### 【0018】

また、他の一態様として、前記第1配線層と前記第2配線層との間には、第1絶縁膜が設けられ、

前記第2配線層と前記第3配線層との間には、前記第1絶縁膜よりも厚い第2絶縁膜が

10

20

30

40

50

設けられ、

平面視において、前記複数の第1配線と前記複数の第2配線とは互いに重ならず、かつ、前記複数の第3配線は、前記複数の第1配線および前記複数の第2配線のうちの一部と重なっていても良い。

**【0019】**

また、他の一態様として、平面視において、前記複数の第1配線と前記複数の第2配線とは互いに重ならず、前記複数の第2配線と前記複数の第3配線とは互いに重ならず、かつ、前記複数の第3配線は、前記複数の第1配線と重なっていても良い。

**【0020】**

また、他の一態様として、前記基板の前記第1面は、第1方向に沿って延びる第1辺、前記第1辺の反対側に位置する第2辺、前記第1方向に直交する第2方向に沿って延びる第3辺、および前記第3辺の反対側に位置する第4辺を備え、

10

前記引出配線部は、

前記表示素子部と前記入力部との間において、前記複数の第1配線、前記複数の第2配線、および前記複数の第3配線を含む複数の引出配線が前記第2方向に沿って延びる第1部分と、

前記第1部分と前記入力部との間において、前記複数の引出配線が前記第2方向および前記第1方向と交差する第3方向に沿って延びる第2部分と、

前記第2部分と前記入力部との間において、前記複数の引出配線が前記第2方向に沿って延びる第3部分と、

20

を有し、

前記第1配線層と前記第2配線層との間には、無機絶縁膜である第1絶縁膜が設けられ

、

前記第2配線層と前記第3配線層との間には、有機絶縁膜である第2絶縁膜が設けられ

、

前記引出配線部の前記第3部分には、前記第2絶縁膜を厚さ方向に貫通するように前記第1方向に沿って延びる開口部が設けらいても良い。

**【0021】**

また、他の一態様である表示装置は、第1面を備える基板と、前記基板の前記第1面に形成された表示機能層と、前記基板の前記第1面に形成され、前記表示機能層を駆動する回路部と、を有し、

30

前記回路部は、前記表示機能層が形成された表示領域と重なる位置に複数の表示素子が配列された表示素子部と、前記表示素子部に前記表示機能層を駆動する信号を伝送する入力部と、前記表示素子部と前記入力部とを電気的に接続する引出配線部と、を有し、

前記引出配線部は、積層された複数の配線層を有し、

前記複数の配線層には、第1離間距離で複数の第1配線が形成された第1配線層と、前記第1離間距離よりも小さい第2離間距離で複数の第2配線が形成された第2配線層と、が含まれ、

前記複数の第2配線の数は、前記複数の第1配線の数よりも多い。

**【図面の簡単な説明】**

40

**【0022】**

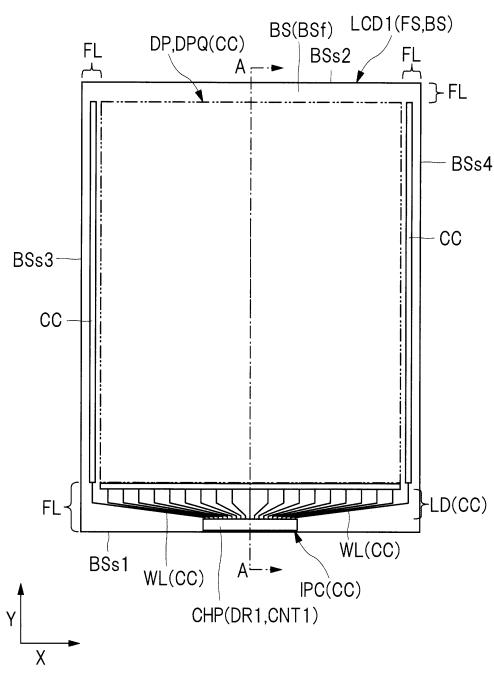

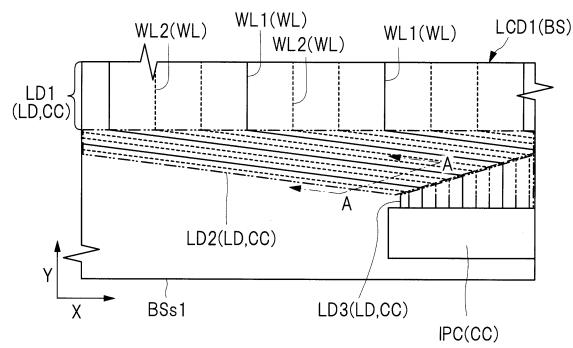

**【図1】**実施の形態の表示装置の一例を示す平面図である。

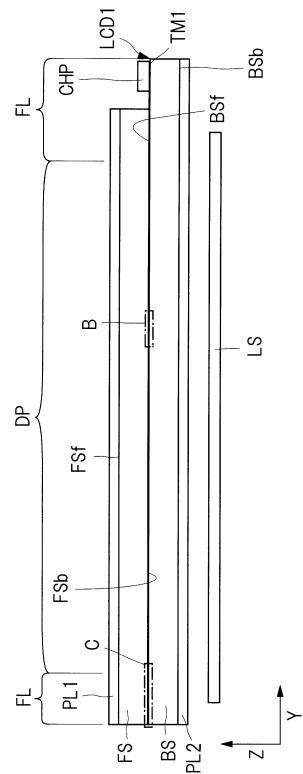

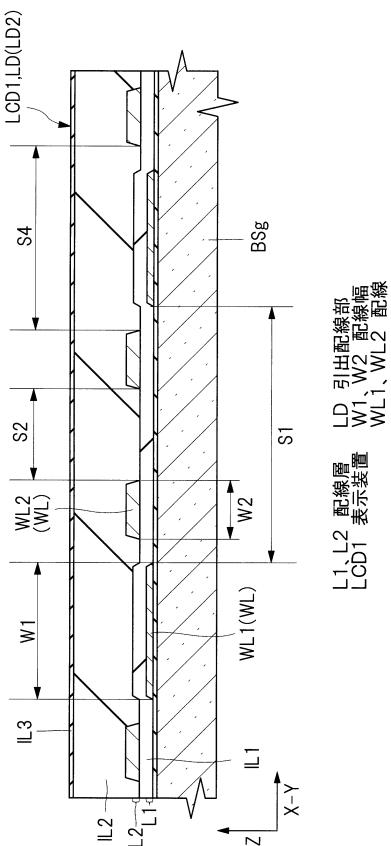

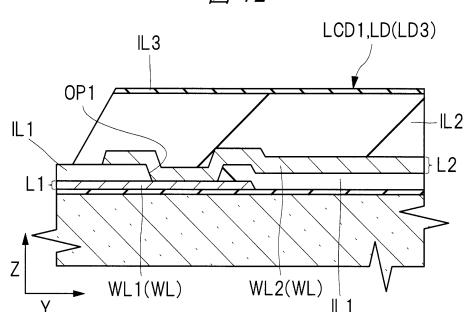

**【図2】**図1のA-A線に沿った断面図である。

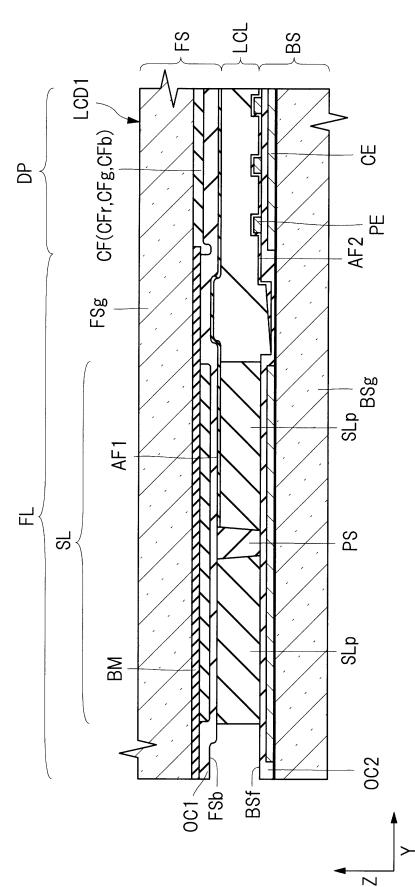

**【図3】**図2のB部の拡大断面図である。

**【図4】**図2のC部の拡大断面図である。

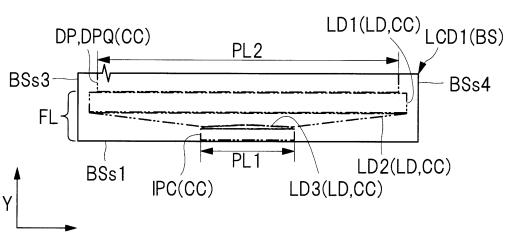

**【図5】**図1に示す引出配線部のレイアウトを模式的に示す拡大平面図である。

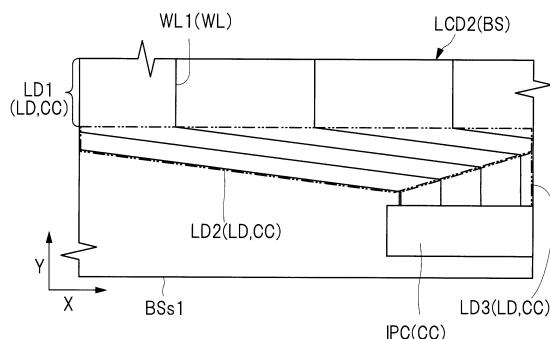

**【図6】**図1に示す引出配線部において、複数の配線を二層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。

**【図7】**図6に対応する検討例であって、複数の配線を単層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。

50

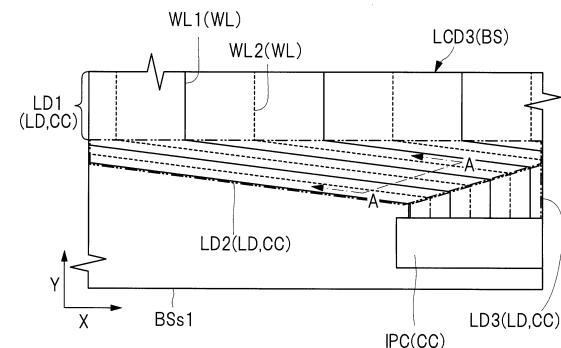

【図8】図6に対応する別の検討例であって、複数の配線を二層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。

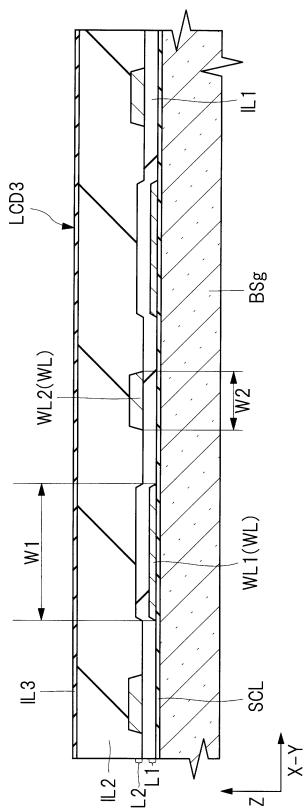

【図9】図8のA-A線に沿った拡大断面図である。

【図10】図6のA-A線に沿った拡大断面図である。

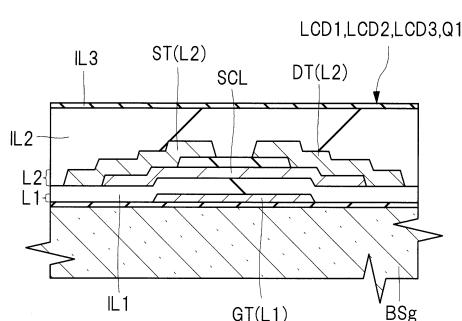

【図11】図1に示す表示素子部に設けられた表示素子の構造例を示す拡大断面図である。

【図12】図6および図10に示す第一層目の配線層の配線と第二層目の配線層の配線とを電気的に接続する構造例を示す拡大断面図である。

【図13】図6に対する変形例であって、複数の配線を三層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。

10

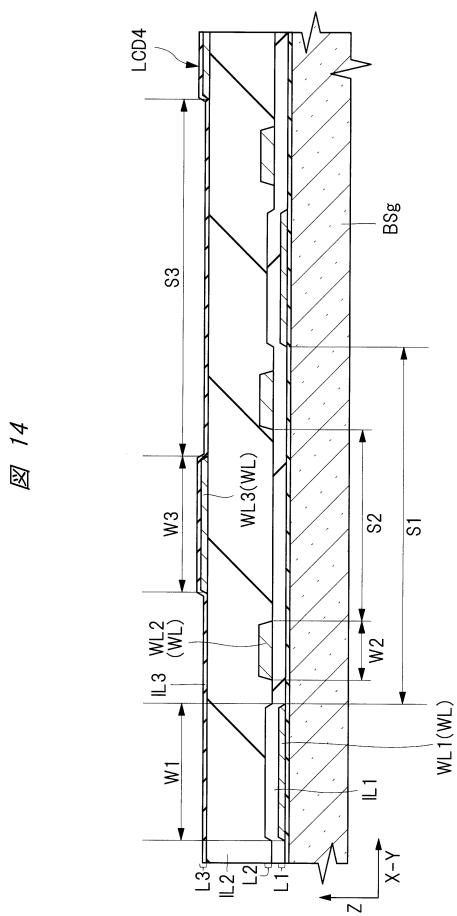

【図14】図13のA-A線に沿った拡大断面図である。

【図15】図13に対する変形例であって、複数の配線のうちの一部が、厚さ方向に重なっている場合のレイアウト例を示す拡大平面図である。

【図16】図15のA-A線に沿った拡大断面図である。

【図17】図13および図15に示す表示装置において、複数の配線層の配線を電気的に接続する部分の構造例を示す拡大断面図である。

#### 【発明を実施するための形態】

##### 【0023】

以下に、本発明の各実施の形態について、図面を参照しつつ説明する。なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一または関連する符号を付して、詳細な説明を適宜省略することがある。

20

##### 【0024】

また、以下の実施の形態で説明する技術は、表示機能層が設けられた表示領域の複数の素子に、表示領域の周囲から信号を供給する機構を備える表示装置に広く適用可能である。上記のような表示装置には、例えば、液晶表示装置、有機EL(Electro-Luminescence)表示装置など、種々の表示装置が例示できる。以下の実施の形態では、表示装置の代表例として、液晶表示装置を取り上げて説明する。

30

##### 【0025】

また、液晶表示装置は、表示機能層である液晶層の液晶分子の配向を変化させるための電界の印加方向により、大きくは以下の2通りに分類される。すなわち、第1の分類として、表示装置の厚さ方向(あるいは面外方向)に電界が印加される、所謂、縦電界モードがある。縦電界モードには、例えばTN(Twisted Nematic)モードや、VA(Vertical Alignment)モードなどがある。また、第2の分類として、表示装置の平面方向(あるいは面内方向)に電界が印加される、所謂、横電界モードがある。横電界モードには、例えばIPS(In-Plane Switching)モードや、IPSモードの一つであるFFS(Fringe Field Switching)モードなどがある。以下で説明する技術は、縦電界モードおよび横電界モードのいずれにも適用できるが、以下で説明する実施の形態では、一例として、横電界モードの表示装置を取り上げて説明する。

40

##### 【0026】

###### <表示装置の基本構成>

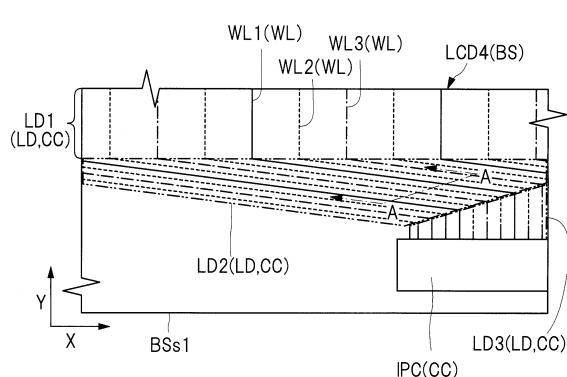

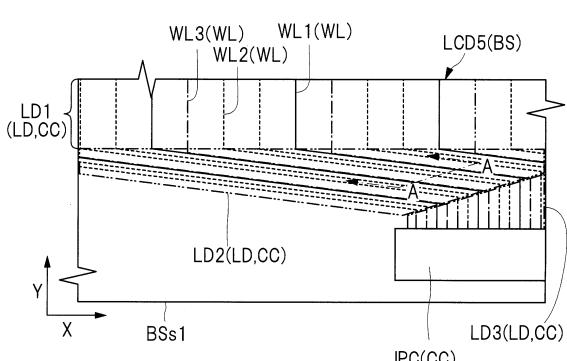

まず、表示装置の基本構成について説明する。図1は、本実施の形態の表示装置の一例を示す平面図、図2は図1のA-A線に沿った断面図である。また、図3は、図2のB部の拡大断面図である。また、図4は、図2のC部の拡大断面図である。

##### 【0027】

なお、図1では、平面視における表示部DPと額縁部(周辺部)FLの境界を見やすくするため、表示部DPの輪郭を二点鎖線で示している。また、図1に示す複数の配線WL

50

は、表示部 D P の周辺領域から表示部 D P と重なる領域まで延びている。しかし、図 1 では見易さのため、表示部 D P と重なる領域では、配線 W L の図示を省略している。また、図 2 は断面図であるが、見易さのためにハッチングは省略した。

#### 【 0 0 2 8 】

図 1 に示すように、本実施の形態の表示装置 L C D 1 は、入力信号に応じて外部から視認可能な画像が形成される表示領域である表示部 D P を有する。また、表示装置 L C D 1 は、平面視において、表示部 D P の周囲に枠状に設けられた非表示領域である額縁部 F L を有する。なお、本表示装置の表示領域は矩形形状を有しているが、表示領域が多角形や円形であってもよい。また、表示領域が表示装置の端部近傍まで延在するものであってもよい。この場合、表示領域の周辺領域は額縁形状とはならないが、この場合であっても額縁部と称する。10

#### 【 0 0 2 9 】

また、表示装置 L C D 1 は、対向配置される一対の基板の間に、表示機能層である液晶層が形成された構造を備える。すなわち、図 2 に示すように、表示装置 L C D 1 は、表示面側の基板 F S 、基板 F S の反対側に位置する基板 B S 、および基板 F S と基板 B S の間に配置される液晶層 L C L ( 図 3 参照 ) を有する。

#### 【 0 0 3 0 】

また、図 1 に示す基板 B S は、平面視において、X 方向に沿って延びる辺 B S s 1 、辺 B S s 1 に対向する辺 B S s 2 、X 方向に対して直交する Y 方向に沿って延びる辺 B S s 3 、および辺 B S s 3 に対向する辺 B S s 4 を有する。図 1 に示す基板 B S が有する辺 B S s 2 、辺 B S s 3 、および辺 B S s 4 のそれぞれから表示部 D P までの距離は、同程度であって、辺 B S s 1 から表示部 D P までの距離よりも短い。以下、本願において、基板 B S の周縁部と記載した場合には、基板 B S の外縁を構成する辺 B S s 1 、辺 B S s 2 、辺 B S s 3 、および辺 B S s 4 のうちのいずれかを意味する。また、単に周縁部と記載した場合には、基板 B S の周縁部を意味する。20

#### 【 0 0 3 1 】

また、図 1 に示す表示部 D P に設けられた液晶層 L C L は、回路部 C C に印加される信号に応じて画素 ( 詳しくはサブピクセル ) 每に駆動される。

#### 【 0 0 3 2 】

回路部 C C は、表示部 D P と重なる位置に複数の表示素子が配列された表示素子部 D P Q に接続される。表示素子部 D P Q に設けられた複数の表示素子は、画素 ( 詳しくはサブピクセル ) 每に行列状に設けられ、スイッチング動作をする。本実施の形態では、複数の表示素子は、基板に形成された T F T ( Thin-Film Transistor ) と呼ばれるトランジスタである。30

#### 【 0 0 3 3 】

また、回路部 C C は、表示部 D P の周囲の額縁部 F L に設けられ、表示素子部 D P Q の複数の表示素子と電気的に接続される複数の配線 W L が含まれる。また、表示機能層を駆動する回路部 C C には、表示素子部 D P Q と電気的に接続され、複数の配線 W L を介して表示素子部 D P Q の複数の表示素子に駆動信号や映像信号を入力する、入力部 I P C が含まれる。図 1 に示す例では、入力部 I P C には、画像表示用の駆動回路 D R 1 や制御回路 C N T 1 が形成された半導体チップ C H P が搭載されている。40

#### 【 0 0 3 4 】

また、図 1 に示す例では、入力部 I P C は、表示装置 L C D 1 の額縁部 F L のうち、基板 B S の辺 B S s 1 と表示部 D Pとの間に設けられている。また、基板 B S の辺 B S s 1 と表示部 D Pとの間には、複数の配線 W L が形成された引出配線部 L D が設けられている。表示素子部 D P Q と入力部 I P C とは、引出配線部 L D を介して電気的に接続されている。引出配線部 L D の詳細な構造については、後述する。

#### 【 0 0 3 5 】

また、表示装置 L C D 1 は、平面視において、額縁部 F L に形成されたシール部を有する。シール部は、表示部 D P の周囲を連続的に囲むように形成され、図 2 に示す基板 F S 50

と基板 B S は、シール部に設けられるシール材より接着固定される。このように、表示部 D P の周囲にシール部を設けることで、表示機能層である液晶層 L C L ( 図 3 参照 ) を封止することができる。

#### 【 0 0 3 6 】

また、図 2 に示すように、表示装置 L C D 1 の基板 B S の背面 B S b 側には、光源 L S から発生した光を偏光する偏光板 P L 2 が設けられている。偏光板 P L 2 は、基板 B S に固定されている。一方、基板 F S の前面 F S f 側には、偏光板 P L 1 が設けられている。偏光板 P L 1 は、基板 F S に固定されている。

#### 【 0 0 3 7 】

なお、図 2 では、表示画像を形成するための基本的な構成部品を例示的に示しているが 10 、変形例としては図 2 に示す構成部品に加えて、他の部品を追加することができる。例えば、偏光板 P L 1 を傷や汚れなどから保護する保護層として、保護フィルムやカバー部材を偏光板 P L 1 の前面側に取り付けても良い。また例えば、偏光板 P L 1 及び偏光板 P L 2 に、位相差板などの光学素子を貼り付ける実施態様に適用することができる。あるいは、基板 F S 及び基板 B S のそれぞれに、光学素子を成膜する方法を適用することができる。

#### 【 0 0 3 8 】

また、図 3 に示すように、表示装置 L C D 1 は、基板 F S と基板 B S の間に配置される複数の画素電極 P E 、および共通電極 C E を有する。本実施の形態の表示装置 L C D 1 は、上記したように横電界モードの表示装置なので、複数の画素電極 P E および共通電極 C E は、それぞれ基板 B S に形成されている。

#### 【 0 0 3 9 】

図 3 に示す、基板 B S は、ガラス基板などから成る基材 B S g を有し、主として画像表示用の回路が基材 B S g に形成されている。基板 B S は、基板 F S 側に位置する前面 B S f およびその反対側に位置する背面 B S b ( 図 2 参照 ) を有する。また、基板 B S の前面 B S f 側には、TFT などの表示素子と、複数の画素電極 P E がマトリクス状に形成されている。

#### 【 0 0 4 0 】

図 3 に示す例は、横電界モード ( 詳しくは FFS モード ) の表示装置 L C D 1 を示しているので、共通電極 C E は、基板 B S が備える基材 B S g の前面側に形成され、絶縁膜 ( 絶縁層 ) O C 2 に覆われる。また、複数の画素電極 P E は、絶縁膜 O C 2 を介して共通電極 C E と対向するように絶縁膜 O C 2 の基板 F S 側に形成される。

#### 【 0 0 4 1 】

また、図 3 に示す基板 F S は、ガラス基板などから成る基材 F S g に、カラー表示の画像を形成するカラーフィルタ C F が形成された基板であって、表示面側である前面 F S f ( 図 2 参照 ) および前面 F S f の反対側に位置する背面 F S b を有する。基板 F S のように、カラーフィルタ C F が形成された基板は、上記した TFT が形成された TFT 基板と区別する際に、カラーフィルタ基板、あるいは、液晶層を介して TFT 基板と対向するため、対向基板と呼ばれる。なお、図 3 に対する変形例としては、カラーフィルタ C F を TFT 基板に設ける構成を採用しても良い。

#### 【 0 0 4 2 】

基板 F S は、例えばガラス基板などの基材 F S g の一方の面に、赤 ( R ) 、緑 ( G ) 、青 ( B ) の 3 色のカラーフィルタ画素 C F r 、 C F g 、 C F b を周期的に配列して構成されたカラーフィルタ C F が形成されている。カラー表示装置では、例えばこの赤 ( R ) 、緑 ( G ) 、青 ( B ) の 3 色のサブピクセルを 1 組として、1 画素 ( 1 ピクセルともいう ) を構成する。基板 F S の複数のカラーフィルタ画素 C F r 、 C F g 、 C F b は、基板 B S に形成されている画素電極 P E を有するそれぞれのサブピクセルと、互いに対向する位置に配置されている。

#### 【 0 0 4 3 】

また、各色のカラーフィルタ画素 C F r 、 C F g 、 C F b のそれぞれの境界には、遮光

10

20

30

40

50

膜B Mが形成されている。遮光膜B Mはブラックマトリクスと呼ばれ、例えば黒色の樹脂や、低反射性の金属から成る。遮光膜B Mは、平面視において、格子状に形成される。言い換えれば、基板F Sは、格子状に形成された遮光膜B Mの開口部に、形成された、各色のカラーフィルタ画素C F r、C F g、C F bを有する。なお、1画素を構成するものは赤(R)、緑(G)、青(B)の3色に限定されるものではない。また、ブラックマトリクスは格子状に限定されるものでなく、ストライプ状のものであっても良い。

#### 【0044】

なお、本願において、表示部D Pまたは表示領域と記載する領域は、額縁部F Lよりも内側の領域として規定される。また、額縁部F Lは、図2に示す光源L Sから照射された光を遮光する遮光膜B Mにより覆われた領域である。遮光膜B Mは表示部D P内にも形成されるが、表示部D Pには、遮光膜B Mに複数の開口部が形成されている。一般的に、遮光膜B Mに形成され、カラーフィルタC Fが埋め込まれた開口部のうち、最も周縁部側に形成された開口部の端部が、表示部D Pと額縁部F Lの境界として規定される。10

#### 【0045】

また、基板F Sは、カラーフィルタC Fを覆う樹脂層O C 1を有する。各色のカラーフィルタ画素C F r、C F g、C F bの境界には、遮光膜B Mが形成されているので、カラーフィルタC Fの内面は、凹凸面になっている。樹脂層O C 1は、カラーフィルタC Fの内面の凹凸を平坦化する、平坦化膜として機能する。あるいは、樹脂層O C 1は、カラーフィルタC Fから液晶層に対して不純物が拡散するのを防止する保護膜として機能する。樹脂層O C 1は、材料に熱硬化性樹脂成分、あるいは、光硬化性樹脂成分など、エネルギーを付与することで硬化する成分を含有させることで、樹脂材料を硬化させることができる。20

#### 【0046】

また、基板F Sと基板B Sの間には、画素電極P Eと共に共通電極C Eとの間に表示用電圧が印加されることで表示画像を形成する液晶層L C Lが設けられる。液晶層L C Lは、印加された電界の状態に応じてそこを通過する光を変調するものである。

#### 【0047】

また、基板F Sは、液晶層L C Lと接する界面である背面F S bに、樹脂層O C 1を覆う配向膜A F 1を有する。また、基板B Sは、液晶層L C Lと接する界面である前面B S fに、絶縁膜O C 2および複数の画素電極P Eを覆う配向膜A F 2を有する。この配向膜A F 1、A F 2は液晶層L C Lに含まれる液晶の初期配向を揃えるために形成された樹脂膜であって、例えばポリイミド樹脂から成る。30

#### 【0048】

図3に示す表示装置L C D 1によるカラー画像の表示方法は、例えば以下の通りである。すなわち、光源L S(図2参照)から出射された光は、偏光板P L 2(図2参照)によってフィルタリングされ、偏光板P L 2を通過する光が液晶層L C Lに入射する。液晶層L C Lに入射した光は、液晶の屈折率異方性(言い換えれば複屈折)に応じて偏光状態を変化させて液晶層L C Lの厚さ方向(言い換えれば基板B Sから基板F Sに向かう方向)に伝搬され、基板F Sから出射される。この時、画素電極P Eと共に共通電極C Eに電圧を印加して形成される電界により、液晶配向が制御され、液晶層L C Lは光学的なシャッターとして機能する。つまり、液晶層L C Lにおいて、サブピクセル毎に光の透過率を制御することができる。基板F Sに到達した光は、基板F Sに形成されたカラーフィルタにおいて、色フィルタリング処理(すなわち、所定の波長以外の光を吸収する処理)が施され、前面F S fから出射される。また、前面F S fから出射された光は、偏光板P L 1を介して観者V Wに到達する。40

#### 【0049】

また、図4に示すように、液晶層L C Lの周縁部側に設けられたシール部S Lは、シール材(封着材)S L pを備える。液晶層L C Lは、シール材S L pで囲まれた領域内に封入されている。つまり、シール材S L pは、液晶層L C Lの漏れ出しを防ぐ封着材としての機能を有している。また、シール材S L pは、基板F Sの背面F S bおよび基板B Sの50

前面 B S f のそれぞれに密着しており、基板 F S と基板 B S とは、シール材 S L p を介して接着固定されている。つまり、シール材 S L p は、基板 F S 及び基板 B S を接着固定する接着部材としての機能を有している。

#### 【 0 0 5 0 】

また、図 4 に示す例では、シール部 S L は、液晶層 L C L の周囲に配置され、液晶層 L C L の外縁に沿って延びる部材である、部材 P S を有している。部材 P S は、配向膜 A F 1 の広がりを堰き止める堰き止め用部材として機能する。また、図 3 および図 4 に示す液晶層 L C L の厚さは、基板 F S や基板 B S の厚さと比較して極端に薄い。例えば、液晶層 L C L の厚さは、基板 F S や基板 B S の厚さと比較すると、0.1% ~ 10% 程度の厚さである。図 3 および図 4 に示す例では、液晶層 L C L の厚さは、例えば 3 μm ~ 4 μm 程度である。10

#### 【 0 0 5 1 】

##### < 引出配線部の詳細 >

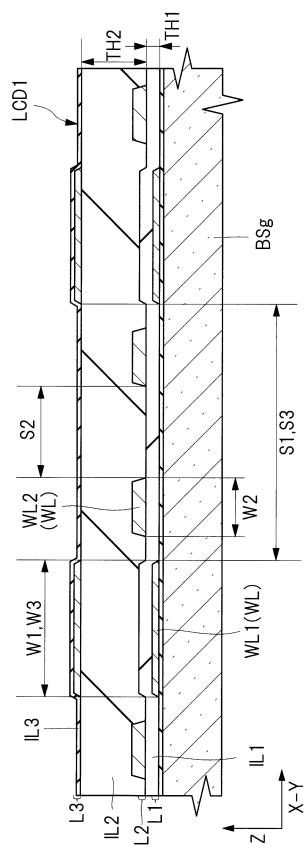

次に、図 1 に示す引出配線部 L D の詳細について説明する。図 5 は、図 1 に示す引出配線部のレイアウトを模式的に示す拡大平面図である。また、図 6 は、図 1 に示す引出配線部において、複数の配線を二層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。また、図 7 は、図 6 に対応する検討例であって、複数の配線を単層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。また、図 8 は、図 6 に対応する別の検討例であって、複数の配線を二層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。また、図 9 は、図 8 の A - A 線に沿った拡大断面図である。また、図 10 は、図 6 の A - A 線に沿った拡大断面図である。また、図 11 は、図 1 に示す表示素子部に設けられた表示素子の構造例を示す拡大断面図である。20

#### 【 0 0 5 2 】

なお、図 6 および図 8 では、異なる層に形成された配線 W L 1 と配線 W L 2 の区別をし易くするために、第 1 層目に形成された配線 W L 1 を実線で示し、第 2 層目に形成された配線 W L 2 を点線で示している。

#### 【 0 0 5 3 】

図 1 に示す引出配線部 L D には、表示素子部 D P Q に映像信号を伝送する複数の信号線、および表示素子部 D P Q にゲート信号を伝送する複数のゲート線を含む複数の配線 W L が形成されている。表示装置の画素数を増加させて、表示画像の精細度を向上させるためには、信号線およびゲート線の数を増加させる必要があるので、限られたスペースに、多数の配線 W L を配置する技術が必要になる。そこで、本願発明者は、複数の配線 W L を積層された複数の配線層に形成することで、配線 W L の数を増加させる技術において検討を行った。30

#### 【 0 0 5 4 】

まず、図 5 に示すように、X 方向における入力部 I P C の長さ P L 1 と表示素子部 D P Q の長さ P L 2 とは異なる。このため、入力部 I P C と表示素子部 D P Q とを電気的に接続する配線 W L ( 図 6 参照 ) の一部は、X 方向、および X 方向と直交する Y 方向のそれに対して交差する方向に延ばす必要がある。このため、引出配線部 L D は、表示素子部 D P Q と入力部 I P C との間において、複数の配線 W L が Y 方向に沿って延びる部分 L D 1 を有する。また、引出配線部 L D は、部分 L D 1 と入力部 I P C との間において、複数の配線 W L が Y 方向および X 方向と交差する方向に沿って延びる部分 L D 2 を有する。また、引出配線部 L D は、部分 L D 2 と入力部 I P C との間において、複数の配線 W L が Y 方向に沿って延びる部分 L D 3 を有する。40

#### 【 0 0 5 5 】

本実施の形態のように、複数の配線 W L が Y 方向および X 方向と交差する方向に沿って延びる部分 L D 2 では、チップのコスト削減のためにチップの長さを小さくすることによって入力部 I P C の長さ P L 1 が小さくなる場合や、狭額縁化のために額縁部 F L のうち、基板 B S の辺 B S s 1 と表示部 D P との間隔を狭める場合、隣り合う配線 W L 間の距離は、部分 L D 2 において狭くなる。言い換えれば、部分 L D 2 における配線密度を向上さ50

せる必要がある。

#### 【0056】

次に、図7に示す表示装置LCD2のように、単層で配線WLを引き回す場合について検討する。表示装置LCD2のように複数の配線WLを単層で引き回す場合、レイアウト可能な配線WLの数は、隣り合う配線WL間の離間距離の最小値により規定される。例えば、図7に示す複数の配線WL1のそれぞれの配線幅が4.2μm、且つ、隣り合う配線WL1の離間距離が5.1μmの設計ルールの配線層で、複数の配線WLを引き回す場合、部分LD2における隣り合う配線WL1の中心間距離は、9.3μm以上にしなければならない。言い換えれば、図7に示すレイアウトの場合、部分LD2において、9.3μm以上の配線ピッチで、配線WL1を配置する必要がある。

10

#### 【0057】

次に、図8および図9に示す表示装置LCD3のように、絶縁膜を挟んだ二層の配線層で配線WLを引き回す場合について検討する。例えば、絶縁膜を挟んだ一方の配線層はTFTのゲート電極と同層であり、他方の配線層はTFTのソース・ドレイン電極と同層である。二層の配線層で配線WLを引き回す場合、図8および図9に示すように、第一層目の配線層L1(図9参照)に設けられた配線WL1と、第二層目の配線層L2(図9参照)に設けられた配線WL2とが、互いに重ならないように設けられていることが好ましい。配線WL1と配線WL2とが互いに重ならないように設けることで、配線WL1を流れる電流と、配線WL2を流れる電流とが、互いに干渉することを抑制できる。

20

#### 【0058】

そこで、表示装置LCD3の例では、図8に示すように、平面視において、配線WL1と配線WL2とが交互に配列されている。この場合、第一層目の配線層L1(図9参照)に形成された複数の配線WL1のうち、隣り合う配線WL1の間のスペースを配線WL2の形成領域として活用できるので、第一層目の配線層L1のみで、配線WLを引き回す場合と比較して、配線密度を向上させることができる。なお、それぞれの配線は、単層の金属であっても良いし、複数の金属を積層したものであってもよい。

#### 【0059】

例えば、図9に示す例では、配線層L1では、複数の配線WL1のそれぞれの配線幅W1が4.2μm、且つ、隣り合う配線WL1の離間距離が5.1μmになっている。また、配線層L2では、複数の配線WL2のそれぞれの配線幅W2が1.8μm、且つ、隣り合う配線WL2の離間距離が7.5μmになっている。この場合、図8に示す複数の配線WLのうち、平面視において隣り合う配線WLの中心間距離は、約4.7μmになる。言い換えれば、図8に示すレイアウトの場合、部分LD2において、配線ピッチが4.7μm以上であれば良いので、図7に示す表示装置LCD2の場合と比較して、配線密度を向上させることができる。

30

#### 【0060】

ところで、表示装置LCD3のように、複数の配線層にそれぞれ配線WLを形成する場合、製造プロセス上の理由などにより、配線層ごとに、配線幅および配線間距離の設計ルール、すなわち、配線幅および配線間距離の下限値が異なる場合がある。例えば、図1に示す表示素子部DPQには複数の表示素子としてTFTを形成することを説明した。図8および図9に示す引出配線部LDの複数の配線層を効率的に形成する観点からは、TFTのゲート電極やソース電極を形成する際に、一括して形成することが好ましい。この場合、TFTの製造プロセスに起因して、配線層ごとに、配線幅および配線間距離の設計ルールが異なる場合がある。

40

#### 【0061】

例えば、上記した表示素子であるTFTが、図11に示すトランジスタQ1のように、ゲート電極GTがソース電極STおよびドレイン電極DTよりも下方に形成されるボトムゲート方式の構造を備える場合、最下層の配線層L1(図1参照)には、ゲート電極GTが形成される。また、第二層目の配線層L2には、ソース電極STおよびドレイン電極DTが形成される。図11に示す例では、ゲート電極GTは、第一層目の配線層L1に形成

50

され、ゲート絶縁膜である絶縁膜（絶縁層）IL1に覆われる。絶縁膜IL1は、例えば酸化珪素、窒化珪素、あるいはこれらの積層膜から成る無機絶縁膜である。また、ソース電極STおよびドレイン電極DTは、絶縁膜IL1上に設けられた第二層目の配線層L2に形成され、絶縁膜（絶縁層）IL2に覆われる。絶縁膜IL2は、トランジスタQ1や配線層L2の保護膜として機能する絶縁膜である。絶縁膜IL2は、トランジスタQ1を覆うので、無機膜よりの被覆性が良い有機膜で構成され、さらに窒化珪素などの無機絶縁膜から成る絶縁膜（絶縁層）IL3に覆われている。

#### 【0062】

図11に示すトランジスタQ1の製造プロセスでは、ゲート電極GTが形成された後、半導体層SCLが、ゲート電極GTを覆うゲート絶縁膜である絶縁膜IL1上に形成される。図11のトランジスタはボトムゲートであるが、基体Bsgに近い側に半導体層を形成し、半導体層を形成した後にゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を設けるトップゲートのトランジスタも存在する。トランジスタの形成時には、熱処理を行う場合があり、ゲート電極GTが形成される配線層L1に形成される配線WL1（図8および図9参照）には、熱処理に対する耐性が要求されることが多い。そのため、配線層L1を、例えば、モリブデン（Mo）などの高融点金属材料により形成する場合がある。一方、ソース電極STやドレイン電極DTは、熱処理の後で形成することができる、配線層L2に形成される配線WL1（図8および図9参照）には、例えばアルミニウムなどの低抵抗金属材料を用いることができる。この結果、配線層L2の配線WL2は、配線層L1の配線WL1と比較して、配線幅を狭くすることが可能になる。

#### 【0063】

なお、上記した配線WL1および配線WL2のそれぞれに亘りに異なる金属材料を用いる例は、配線層ごとに、配線幅および配線間距離の設計ルールが異なる理由の一例であり、配線WL1と配線WL2に例えればそれぞれアルミニウムを用いる場合もある。ただし、配線WL1と配線WL2に同じ金属材料を用いた場合でも、プロセス上の制約、あるいはステップカバレッジ等の理由により、配線層ごとに、配線の厚さ、配線幅および配線間距離の設計ルールが異なる場合がある。

#### 【0064】

図9に示す例では、配線WL2はアルミニウム配線であって、設計ルールとしては、配線間距離は、例えば2.5μm以上であれば良い。したがって、全ての配線WLを図9に示す第二層目の配線層L2に配置すれば、隣り合う配線WL2の中心間距離、すなわち、配線ピッチは、約4.3μmになる。つまり、図9に示す例の場合、平面視において、配線WL1と配線WL2とが交互に配列されているので、全ての配線WLを第二層目の配線層L2に設ける場合と比較して、配線密度が低くなっている。このように、配線層ごとに、配線幅および配線間距離の設計ルールが異なる場合において、単純に配線WL1と配線WL2とを交互に配列した場合、第二層目の配線層L2の単層で配線WLを引き回す場合と比較して、却って配線密度が低くなる場合もあることが判った。

#### 【0065】

そこで、本願発明者は、複数の配線層にそれぞれ配線WLを配置する場合に、配線密度を高くすることができる構成についてさらに検討を行い、図6および図10に示す本実施の形態の構成を見出した。すなわち、表示装置LCD1では、相対的に配線密度を向上させ易い配線層L2に形成される配線WL2の数が、相対的に配線密度を向上させ難い配線層L1に形成される配線WL1の数よりも多い。

#### 【0066】

図6および図10に示すように、本実施の形態の表示装置が備える引出配線部LD（図6参照）は、配線層L1（図10参照）および配線層L2（図10参照）から成る複数の配線層を有する。また、配線層L1には、配線幅W1の複数の配線WL1が形成され、配線層L2には、配線幅W1よりも狭い配線幅W2の複数の配線WL2が形成されている。つまり、配線層L2は、配線層L1と比較して、相対的に配線密度を向上させ易い配線層である。上記のように、複数の配線層に配線幅が異なる複数の配線WL1および複数の配

10

20

30

40

50

線WL2が形成されている点は、図8および図9に示す表示装置LCD3と同様である。

【0067】

また、図8および図9に示す表示装置LCD3の場合、配線WL1と配線WL2とが交互に配列されているので、配線WL1の数と配線WL2の数は同数である。一方、図6および図10に示す表示装置LCD1の場合、平面視において、隣り合う配線WL1の間に複数（図6では2本）の配線WL2が形成されている。したがって、図10に示す配線層L2に形成された複数の配線WL2の数は、配線層L1に形成される複数の配線WL1の数よりも多い。つまり、本実施の形態の表示装置LCD1では、相対的に配線密度を向上させ易い配線層L2に形成される配線WL2の数が、相対的に配線密度を向上させ難い配線層L1に形成される配線WL1の数よりも多いので、複数の配線WLの配線密度を向上させることができる。10

【0068】

図10に示す例では、配線WL2の配線幅W2は1.8μmであって、配線層L2の配線間距離は、例えば2.5μm以上であれば良い。一方、配線WL1の配線幅W1は、4.2μmであって、配線層L1の配線間距離は、例えば5.1μm以上であれば良い。ただし、図10に示す例では、平面視において、隣り合う配線WL1の間に二本の配線WL2を配列するために、配線層L1の配線間距離は、7.0μmとしている。この場合、平面視において、11.2μmの範囲に三本の配線WLが配置されるので、隣り合う配線WL同士の中心間距離、すなわち、配線ピッチは、約3.7μmになる。したがって、図7に示す表示装置LCD2、図8に示す表示装置LCD3、あるいは、図9に示す第二層目の配線層L2の単層で配線WLを引き回す場合の何れと比較しても、配線密度を向上させることができる。20

【0069】

また、上記説明では、配線密度の向上し易さを表す指標として、配線WLの幅を用いて表現した。しかし、配線密度の向上し易さを表す指標として、配線層L1において隣り合う配線WL1の離間距離と、配線層L2において隣り合う配線WL2の離間距離とを用いて表現することができる。

【0070】

すなわち、図10に示す配線層L1には、離間距離S1で複数の配線WL1が形成されている。また、配線層L2には、離間距離S1よりも小さい離間距離S2で複数の配線WL2が形成されている。なお、図10に示す例では、複数の配線WL2の離間距離には、離間距離S2と離間距離S4が含まれるが、離間距離S2および離間距離S4のいずれも離間距離S1よりも小さい。このように、隣り合う配線WLの離間距離が、配線層ごとに異なる場合、離間距離が小さい配線層の方が、配線密度を向上させ易い。すなわち、図10に示す例では、配線層L2の方が、配線層L1よりも配線密度を向上させ易い。30

【0071】

また、上記したように、図5に示す引出配線部LDのうち、特に、配線密度を向上させる必要がある部分は、複数の配線WL（図6参照）がX方向およびY方向に交差する方向に延びる部分LD2である。例えば図6に示すように、複数の配線WLがY方向に沿って延びる部分LD1および部分LD3では、部分LD2と比較して配線密度が低い。したがって、入力部IPCに接続される部分では、複数の配線WLのそれぞれを、例えば第一層目の配線層L1に集約して設けることができる。40

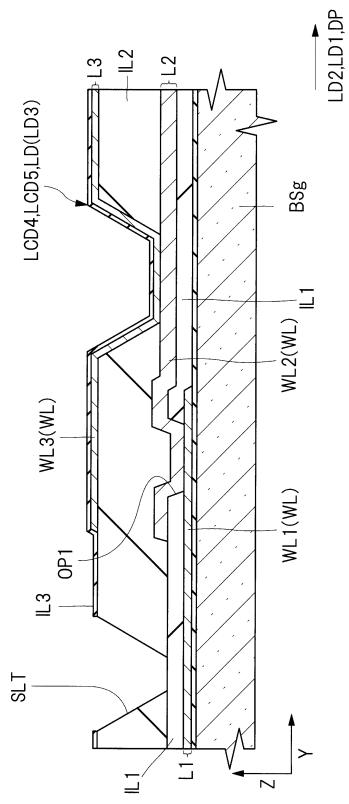

【0072】

第一層目の配線層L1と第二層目の配線層L2とを電気的に接続する方法は、例えば、図12に例示する通りである。図12は、図6および図10に示す第一層目の配線層の配線と第二層目の配線層の配線とを電気的に接続する構造例を示す拡大断面図である。

【0073】

図12に示す例では、第一層目の配線層L1を覆う絶縁膜IL1には、開口部OP1が形成され、開口部OP1において、配線WL1は絶縁膜IL1から露出している。また、第二層目の配線層L2に形成された配線WL2の一部は、絶縁膜IL1に形成された開口50

部OP1に埋め込まれており、配線WL1と電気的に接続されている。このように、配線層L1を覆う絶縁膜IL1の一部に開口部OP1を形成することにより、第二層目の配線層L2の配線WL2と第一層目の配線層L1の配線WL1とを電気的に接続することができる。なお、図12では、複数の配線層を第一層目の配線層L1に集約する例を示しているが、変形例としては、例えば第2層目の配線層L2に集約することもできる。

#### 【0074】

また、図12に示すように、異なる配線層に形成された配線WL1と配線WL2とを電気的に接続する、開口部OP1は、図6に示す部分LD3に形成されていることが好ましい。部分LD1、部分LD2、および部分LD3のうち、最も入力部IPCに近い部分LD3において、配線経路を複数の配線層に分配することで、部分LD2において配線密度向上させることができる。

10

#### 【0075】

##### <変形例>

次に、上記した実施の形態に対する変形例について、代表的な変形例を例示的に説明する。

#### 【0076】

##### <変形例1>

図6および図10では、複数の配線層のそれぞれに配線を形成する実施態様の例として、複数の配線WLを二層の配線層で引き回した場合の構造例を取り上げて説明した。本変形例1では、複数の配線WLを三層の配線層で引き回した場合の構造例を説明する。図13は、図6に対する変形例であって、複数の配線を三層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。また、図14は、図13のA-A線に沿った拡大断面図である。なお、図13では、異なる層に形成された配線WL1、配線WL2、および配線WL3の区別をしやすくするために、第一層目に形成された配線WL1を実線で示し、第二層目に形成された配線WL2を点線で示し、第三層目に形成された配線WL3を一点鎖線で示している。

20

#### 【0077】

図13および図14に示す表示装置LCD4は、第三層目の配線層L3に形成された配線WL3を有している点で、図6に示す表示装置LCD1と相違する。第三層目の配線層L3は、配線層L2を覆う絶縁膜IL2上に形成され、無機絶縁膜である絶縁膜IL3に覆われている。また、図14に示す例では、配線WL3の配線幅W3は、第二層目の配線層L2の配線WL2の配線幅W2よりも広い。つまり、本変形例1の表示装置LCD4は、配線層ごとに設計ルールが異なる。詳しくは、配線層L2は相対的に最も配線密度を向上させ易く、配線層L1および配線層L3は、それぞれ配線層L2よりも配線密度を向上させ難い。

30

#### 【0078】

本変形例1のように、複数の配線WLを配線レイアウトの設計ルールが異なる三層の配線層で引き回す場合でも、上記した表示装置LCD1と同様に考えることができる。すなわち、表示装置LCD3では、相対的に配線密度を向上させ易い配線層L2に形成される配線WL2の数が、相対的に配線密度を向上させ難い配線層L1に形成される配線WL1の数、および配線層L3に形成される配線WL3の数よりも多い。これにより、複数の配線WLの配線密度を向上させることができる。

40

#### 【0079】

図14に示す例では、配線WL1の配線幅W1は、4.2μmであって、配線層L1の配線WL1の離間距離S1は、例えば5.1μm以上であれば良い。また、配線WL2の配線幅W2は1.8μmであって、配線層L2の配線WL2の離間距離S2は、例えば2.5μm以上であれば良い。また、配線WL3の配線幅W3は、4.2μmであって、配線層L3の配線WL3の離間距離S3は、例えば5.1μm以上であれば良い。

#### 【0080】

ただし、図14に示す例では、平面視において、隣り合う配線WL同士が、互いに重な

50

らないようにするために、配線層 L 1 の配線 WL 1 の離間距離 S 1 は 9 . 7  $\mu\text{m}$  とし、配線層 L 2 の配線 WL 2 の離間距離 S 2 は 5 . 2  $\mu\text{m}$  とし、配線層 L 3 の配線 WL 3 の離間距離 S 3 は、9 . 7  $\mu\text{m}$  としている。

#### 【 0 0 8 1 】

この場合、平面視において、13 . 9  $\mu\text{m}$  の範囲に四本の配線 WL が配置されるので、隣り合う配線 WL 同士の中心間距離、すなわち、配線ピッチは、約 3 . 5  $\mu\text{m}$  になる。したがって、図 1 に示す表示装置 LCD 1 よりもさらに、配線密度を向上させることができる。

#### 【 0 0 8 2 】

また、上記説明では、配線密度の向上し易さを表す指標として、配線 WL の幅を用いて表現した。しかし、配線密度の向上し易さを表す指標として、配線層 L 1 において隣り合う配線 WL 1 の離間距離と、配線層 L 2 において隣り合う配線 WL 2 の離間距離とを用いて表現することができる。10

#### 【 0 0 8 3 】

すなわち、配線層 L 2 に形成された複数の配線 WL 2 のうち、隣り合う配線 WL 2 の離間距離 S 2 は、配線層 L 1 における配線 WL 1 の離間距離 S 1 、および配線層 L 3 における配線 WL 3 の離間距離 S 3 よりも小さい。したがって、配線層 L 2 は相対的に最も配線密度を向上させ易く、配線層 L 1 および配線層 L 3 は、それぞれ配線層 L 2 よりも配線密度を向上させ難い。20

#### 【 0 0 8 4 】

上記した相違点以外は、図 13 および図 14 に示す表示装置 LCD 4 は、図 6 および図 10 に示す表示装置 LCD 1 と同様である。したがって、重複する説明は省略する。20

#### 【 0 0 8 5 】

< 变形例 2 >

次に、上記した図 6 に示す表示装置 LCD 1 、図 7 に示す表示装置 LCD 2 、図 8 に示す表示装置 LCD 3 、および図 13 に示す表示装置 LCD 4 では、各配線層に形成された配線 WL が互いに重ならない実施態様について説明した。しかし、配線密度を向上させる点に着目すれば、異なる配線層に形成された配線 WL の一部が厚さ方向に重なっている方が配線密度を向上させることができる。一方、異なる配線層に形成された配線 WL の一部が厚さ方向に重なっている場合、各信号線が互いに干渉しノイズが生じたり、配線間の寄生容量によって信号が影響を受けたり、絶縁膜の欠陥により配線間が短絡したりする懸念が考えられる。そこで、本変形例 2 では、異なる配線層に形成された配線 WL の一部が厚さ方向に重なっており、かつ重なった部分のノイズの影響を低減する技術について説明する。30

#### 【 0 0 8 6 】

図 15 は、図 13 に対する変形例であって、複数の配線のうちの一部が、厚さ方向に重なっている場合のレイアウト例を示す拡大平面図である。また、図 16 は、図 15 の A - A 線に沿った拡大断面図である。

#### 【 0 0 8 7 】

図 15 および図 16 に示す表示装置 LCD 5 は、第三層目の配線層 L 3 に形成された配線 WL 3 と、第一層目の配線層 L 1 に形成された配線 WL とが互いに重なっている点で、図 13 に示す表示装置 LCD 4 と相違する。40

#### 【 0 0 8 8 】

また、図 16 に示すように、配線層 L 2 を覆う絶縁膜 IL 2 の厚さ TH 2 は、配線層 L 1 を覆う絶縁膜 IL 1 の厚さ TH 1 よりも厚い。絶縁膜 IL 1 は、図 11 に示すトランジスタ Q 1 のゲート絶縁膜を兼ねるので、厚さ TH 1 が極端に大きいと、トランジスタ Q 1 の駆動が難しくなる。一方、絶縁膜 IL 2 は、ソース電極 ST およびドレイン電極 DT を確実に覆う観点から、厚くなり易い。図 16 に示す例では、絶縁膜 IL 1 の厚さは 1  $\mu\text{m}$  よりも小さく、絶縁膜 IL 2 の厚さは、例えば 2  $\mu\text{m}$  程度である。

#### 【 0 0 8 9 】

10

20

30

40

50

ここで、各配線層間のノイズ等を考慮した場合、配線層間の距離が遠い程、影響は低減することができる。したがって、相対的に薄い絶縁膜 IL 1 を介して設けられた配線層 L 1 と配線層 L 2との間では配線 WL 間の相互の影響が大きくなりやすい。一方、有機絶縁膜等で形成され、相対的に厚い絶縁膜 IL 2 を介して設けられた配線層 L 2 と配線層 L 3との間では、配線 WL 間の相互の影響が低減させ易い。

#### 【0090】

上記より、各配線層間のノイズ影響、および配線密度の向上をそれぞれ考慮すると、以下の構成が好ましい。すなわち、相対的にノイズ影響が大きい配線層 L 1 の複数の配線 WL 1 と配線層 L 2 の複数の配線 WL 2 とが互いに重なっていないことが好ましい。この場合、厚さ TH 2 が厚さ TH 1 よりも厚い絶縁膜 IL 2 上に設けられている複数の配線 WL 3 は、複数の配線 WL 1 および複数の WL 1 のうちの一部と重なっていても良い。10

#### 【0091】

なお、図 16 に示す例では、配線 WL 3 と配線 WL 2 とは重なっていないが、絶縁膜 IL 2 の厚さ TH 2 が十分に厚く、ノイズや寄生容量の影響が低く、配線間の短絡の可能性が低い場合には、配線 WL 3 と配線 WL 2 とが重なっていても良い。

#### 【0092】

また、図 16 に示す例のように、配線 WL 3 と配線 WL 2 とが重なっていない場合、互いに重なる配線 WL 1 と配線 WL 3 の離間距離は、厚さ TH 1 と厚さ TH 2 の合計値になるので、特にノイズ影響を低減できる。

#### 【0093】

本変形例 2 の表示装置 LCD 5 のように、複数の配線層に形成される配線 WL の一部が互いに重なるように設けられている場合、図 13 に示す表示装置 LCD 4 よりも、さらに複数の配線 WL の配線密度を向上させることができる。20

#### 【0094】

図 16 に示す例では、配線 WL 1 の配線幅 W 1 は、4 . 2 μm であって、配線層 L 1 の配線 WL 1 の離間距離 S 1 は、例えば 5 . 1 μm 以上であれば良い。また、配線 WL 2 の配線幅 W 2 は 1 . 8 μm であって、配線層 L 2 の配線 WL 2 の離間距離 S 2 は、例えば 2 . 5 μm 以上であれば良い。また、配線 WL 3 の配線幅 W 3 は、4 . 2 μm であって、配線層 L 3 の配線 WL 3 の離間距離 S 3 は、例えば 5 . 1 μm 以上であれば良い。30

#### 【0095】

ただし、図 16 に示す例では、平面視において、複数の配線 WL 2 と複数の配線 WL 1 とが、互いに重ならないようにするために、配線層 L 1 の配線 WL 1 の離間距離 S 1 は 7 . 0 μm とし、配線層 L 2 の配線 WL 2 の離間距離 S 2 は 2 . 5 μm とし、配線層 L 3 の配線 WL 3 の離間距離 S 3 は、7 . 0 μm としている。

#### 【0096】

この場合、平面視において、9 . 2 μm の範囲に四本の配線 WL が配置されるので、隣り合う配線 WL 同士の中心間距離、すなわち、配線ピッチは、約 2 . 3 μm になる。したがって、図 13 に示す表示装置 LCD 4 よりもさらに、配線密度を向上させることができる。

#### 【0097】

上記した相違点以外は、図 15 および図 16 に示す表示装置 LCD 5 は、図 13 および図 14 に示す表示装置 LCD 4 と同様である。したがって、重複する説明は省略する。40

#### 【0098】

<変形例 3 >

また、上記変形例 1 で説明した表示装置 LCD 4 や上記変形例 2 で説明した表示装置 LCD 5 のように、絶縁膜 IL 2 上に、配線 WL 3 を形成する場合、配線 WL 3 が形成されている領域には、絶縁膜 IL 2 が形成されている必要がある。

#### 【0099】

ここで、有機絶縁膜である絶縁膜 IL 2 と無機絶縁膜である絶縁膜 IL 1 との界面には、表示装置の外部から水分が浸入し易いという特徴がある。このため、水分が表示部 DP 50

(図1参照)まで浸入することを防止する観点から、図17に示すように、絶縁膜IL2の一部を取り除き、スリットSLTを形成することが好ましい。図17は、図13および図15に示す表示装置において、複数の配線層の配線を電気的に接続する部分の構造例を示す拡大断面図である。図17に示すスリットSLTは、図1に示すX方向に沿って延びるように形成された溝であって、スリットSLTの開口部において、下地層である絶縁膜IL1が露出している。

#### 【0100】

図17に示すようにスリットSLTを形成するためには、スリットを避けた領域において第三層目の配線層L3の配線WL3と、配線層L2の配線WL2とを電気的に接続する必要がある。

10

#### 【0101】

一方、上記したように、図5に示す引出配線部LDのうち、配線密度を特に向上させる必要がある部分は、部分LD2である。したがって、図17に示すようにスリットSLTを形成する場所は、引出配線部LDの部分LD3であることが好ましい。また、第三層目の配線層L3の配線WL3と、配線層L2の配線WL2とが、部分LD3で接続されていることが好ましい。

#### 【0102】

以上、本願発明者によってなされた発明を実施の形態および代表的な変形例に基づき具体的に説明したが、例えば、上記した種々の変形例同士を組み合わせて適用することもできる。また、配線層L3は、横電界方式の表示装置であれば共通電極を低抵抗化するための金属と兼用できる。配線層L3をアルミニウムのような低抵抗金属で形成した場合、配線WL2と同程度の配線幅や配線間隔で形成することが出来る。あるいは、配線層L3の膜厚によっては配線WL2よりも少し配線幅を太くして形成することが可能である。このような場合であっても本願発明を適用することが出来る。

20

#### 【0103】

また、絶縁膜L1の特性によっては、配線WL1と配線WL2とを部分的に重畠させることも可能である。同様に、絶縁膜L2を無機膜で形成した場合に、配線WL2と配線WL3とを重畠させることも可能である。これにより、更なる高密度化が実現できる。

#### 【0104】

また、トップゲートの薄膜トランジスタでは、バックライトと半導体層との間に、バックライトの光を遮光するための遮光金属が用いられる場合がある。この遮光金属を配線層WL3に代えて使用することも可能である。また、前記遮光金属を4つ目の配線層として使用することも可能である。なお、上記で示した配線層は、表示領域のトランジスタのソース電極、あるいはドレイン電極に接続される配線を想定しているが、薄膜トランジスタのゲートに接続される配線、クロックや電源等を供給する配線、あるいは、半導体チップに信号を供給する配線等に適用することも可能である。また例えば、上述の実施の形態では、表示機能層として液晶層を用いる表示装置を開示しているがこれに限ったものではない。例えば、表示機能層として有機化合物から成る発光素子を用いる、所謂、有機ELタイプの表示装置の引出配線部に上記した技術を適用することもできる。

30

#### 【0105】

本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。例えば、前述の各実施形態に対して、当業者が適宜、構成要素の追加、削除若しくは設計変更を行ったもの、または、工程の追加、省略若しくは条件変更を行ったものも、本発明の要旨を備えている限り、本発明の範囲に含まれる。

40

#### 【産業上の利用可能性】

#### 【0106】

本発明は、表示装置や表示装置が組み込まれた電子機器に利用可能である。

#### 【符号の説明】

#### 【0107】

50

|                                         |           |    |

|-----------------------------------------|-----------|----|

| A F 1、A F 2                             | 配向膜       |    |

| B M                                     | 遮光膜       |    |

| B S、F S                                 | 基板        |    |

| B S b、F S b                             | 背面        |    |

| B S f、F S f                             | 前面        |    |

| B S g、F S g                             | 基材        |    |

| B S s 1、B S s 2、B S s 3、B S s 4         | 辺         |    |

| C C                                     | 回路部       |    |

| C E                                     | 共通電極      |    |

| C F                                     | カラーフィルタ   | 10 |

| C F r、C F g、C F b                       | カラーフィルタ画素 |    |

| C H P                                   | 半導体チップ    |    |

| C N T 1                                 | 制御回路      |    |

| D P                                     | 表示部       |    |

| D P Q                                   | 表示素子部     |    |

| D R 1                                   | 駆動回路      |    |

| D T                                     | ドレイン電極    |    |

| F L                                     | 額縁部       |    |

| G T                                     | ゲート電極     |    |

| I L 1、I L 2、I L 3                       | 絶縁膜       | 20 |

| I P C                                   | 入力部       |    |

| L 1、L 2、L 3                             | 配線層       |    |

| L C D 1、L C D 2、L C D 3、L C D 4、L C D 5 | 表示装置      |    |

| L C L                                   | 液晶層       |    |

| L D                                     | 引出配線部     |    |

| L D 1、L D 2、L D 3                       | 部分        |    |

| L S                                     | 光源        |    |

| O C 1、O C 2                             | 樹脂層       |    |

| O P 1                                   | 開口部       |    |

| P E                                     | 画素電極      | 30 |

| P L 1、P L 2                             | 偏光板       |    |

| P S                                     | 部材        |    |

| Q 1                                     | トランジスタ    |    |

| S 1、S 2、S 3、S 4                         | 離間距離      |    |

| S C L                                   | 半導体層      |    |

| S L                                     | シール部      |    |

| S L p                                   | シール材(封着材) |    |

| S L T                                   | スリット      |    |

| S T                                     | ソース電極     |    |

| V W                                     | 観者        | 40 |

| W 1、W 2、W 3                             | 配線幅       |    |

| W L、W L 1、W L 2、W L 3                   | 配線        |    |

【図1】

図1

【図2】

図2

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図14】

【図13】

図13

【図15】

図15

【図16】

図16

【図17】

図17

---

フロントページの続き

(72)発明者 石毛 信幸

東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

審査官 佐野 浩樹

(56)参考文献 特開2007-164219(JP,A)

特開2006-209089(JP,A)

特開2010-113051(JP,A)

特開2006-071861(JP,A)

米国特許出願公開第2012/0281369(US,A1)

米国特許出願公開第2015/0263043(US,A1)

特開2011-100011(JP,A)

特開2008-145461(JP,A)

特開2002-258315(JP,A)

特開2008-058928(JP,A)

特開2011-076009(JP,A)

特開2002-223051(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1343 - 1/1345、 1/135、

G09F 9/00 - 9/46