(12) 发明专利

(10) 授权公告号 CN 106531206 B

(45) 授权公告日 2022.05.27

(21) 申请号 201610704791.5

(51) Int.CI.

(22) 申请日 2016.08.22

G11C 8/08 (2006.01)

(65) 同一申请的已公布的文献号

G11C 7/10 (2006.01)

申请公布号 CN 106531206 A

(56) 对比文件

(43) 申请公布日 2017.03.22

US 8014226 B2, 2011.09.06

(30) 优先权数据

CN 1404147 A, 2003.03.19

2015-179683 2015.09.11 JP

CN 1492445 A, 2004.04.28

(73) 专利权人 瑞萨电子株式会社

US 2007268738 A1, 2007.11.22

地址 日本东京都

US 7733686 B2, 2010.06.08

(72) 发明人 石井雄一郎

US 7064981 B2, 2006.06.20

审查员 王晓春

(74) 专利代理机构 北京市金杜律师事务所

权利要求书2页 说明书8页 附图9页

(54) 发明名称

半导体器件

(57) 摘要

辅助驱动器耦合到字线驱动器未耦合到的字线的端部，并且根据字线的另一端部的电压将字线的另一端部耦合到第一电源。

1. 一种半导体器件,包括:

存储器阵列,包括以矩阵布置的多个存储器单元;

字线,被提供并且分别地对应于所述存储器阵列的行;

字线驱动器,被耦合到所述字线的端部,并且当对应的行被选择时,通过将所述字线的端部耦合到第一电源来激活所述字线;以及

辅助驱动器,被耦合到所述字线的另一端部,并且根据所述字线的所述另一端部的电压,将所述字线的所述另一端部耦合到所述第一电源,

其中所述辅助驱动器中的每个辅助驱动器包括设置在电源与对应字线的所述另一端部之间的PMOS晶体管,

其中所述辅助驱动器中的每个辅助驱动器包括NAND电路,所述NAND电路具有被耦合到所述字线的所述另一端部的一个输入、接收控制信号脉冲的另一输入和被耦合到所述PMOS晶体管的栅极的输出,

其中信号线在水平于实施所述半导体器件的衬底的方向上布置在所述存储器阵列的外部上,

其中所述控制信号脉冲通过所述信号线被传送,以及

其中所述控制信号脉冲由多个辅助驱动器共享,所述多个辅助驱动器共享耦合到所述多个辅助驱动器的对应的字线的所述另一端部。

2. 根据权利要求1所述的半导体器件,

其中所述控制信号脉冲在从所述字线的上升开始时间直到所述字线的所述另一端部的电压达到所述第一电源的电压的周期中处于高电平,并且所述脉冲在从所述字线的下降开始时间直到所述字线的所述另一端部的所述电压达到接地电压的周期中处于低电平。

3. 一种半导体器件,包括:

存储器阵列,包括以矩阵布置的多个存储器单元;

字线,被提供并且分别地对应于所述存储器阵列的行;

字线驱动器,被耦合到所述字线的端部,并且当对应的行被选择时,通过将所述字线的端部耦合到第一电源来激活所述字线;以及

辅助驱动器,被耦合到所述字线的另一端部,并且根据所述字线的所述另一端部的电压,将所述字线的所述另一端部耦合到所述第一电源,

其中所述辅助驱动器中的每个辅助驱动器包括设置在电源与对应字线的所述另一端部之间的PMOS晶体管,

其中所述辅助驱动器中的每一个包括延迟电路和NAND电路,所述延迟电路被耦合到所述字线的所述另一端部,所述NAND电路具有被耦合到所述字线的所述另一端部的一个输入、接收所述延迟电路的输出的另一输入、以及耦合到所述PMOS晶体管的栅极的输出。

4. 根据权利要求3所述的半导体器件,

其中所述延迟电路包括串联耦合的奇数个逆变器。

5. 根据权利要求1-4中任一项所述的半导体器件,

其中所述字线驱动器中的每一个包括逆变器,所述逆变器的输出被耦合到对应字线的所述端部。

6. 根据权利要求1-4中任一项所述的半导体器件,

其中所述存储器单元中的每一个是SRAM。

7. 根据权利要求6所述的半导体器件，

其中所述存储器单元中的每一个是横向地长单元。

8. 根据权利要求1-4中任一项所述的半导体器件,还包括：

位线对,被设置并且对应于所述存储器阵列的列,

其中输出单元被耦合到多个相邻列的所述位线对,并且在将数据写入到所述存储器单元的时间,将根据所写入的数据的电压输出到从所述相邻列选择的列的位线对。

9. 根据权利要求1-4中任一项所述的半导体器件,还包括

位线对,被布置并且对应于所述存储器阵列的列,以及

感测放大器,被耦合到相邻列的位线对,并且在从所述存储器单元读取数据的时间,对从所述相邻列选择的列的位线对的电压进行放大。

## 半导体器件

[0001] 相关申请的交叉引用

[0002] 包括说明书、附图和摘要的于2015年9月11日提交的日本专利申请号2015-179683的公开内容以其整体内容通过引用并入本文。

### 技术领域

[0003] 本发明涉及一种半导体器件,例如,一种具有在其中由激活字线执行数据写入和数据读取的存储器单元的半导体器件。

### 背景技术

[0004] 在相关领域中,众所周知的半导体器件包括存储器阵列、字线和字线驱动器。存储器阵列包括以矩阵布置的多个存储器单元。相应地针对存储器阵列的行提供字线。字线在自/至存储器单元的数据读取/写入的时间的所选择行的字线(参见日本未审查的专利申请公开号2014-99225)。

### 发明内容

[0005] 然而在最近,晶体管的驱动力已经被改进,并且已经提高线的微制造。因此,线的电阻部件的影响是明显的。

[0006] 在包括存储器阵列的半导体器件中,问题在于,由于在激活字线时字线的电阻部件的影响,因而远离字线驱动器的位置的电压的上升速度小于靠近字线驱动器的位置的电压的上升速度。因此,在远离字线驱动器的位置的存储器单元中,与靠近字线驱动器的位置的存储器单元相比较,在流动中延迟单元电流。这引起到存储器单元中的写入数据中的延迟和来自存储器单元的读取数据中的延迟。

[0007] 任何其他目的和新的特征将通过本说明书和附图的描述而变得明显。

[0008] 根据实施例,提供了一种半导体器件,其包括(多个)辅助驱动器,其耦合到其中未耦合字线驱动器的一侧上的(多个)字线的(多个)另一端部,并且根据字线的另一端部的电压将字线的另一端部耦合到第一电源。

[0009] 根据实施例的半导体器件,避免在激活字线的时间时远离字线驱动器的位置的电压的上升速度小于靠近字线驱动器的位置的电压的上升速度是可能的。

### 附图说明

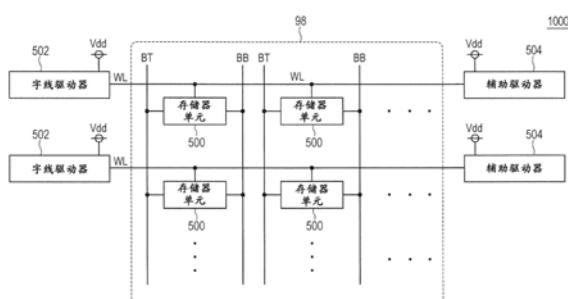

[0010] 图1是图示第一实施例的半导体器件的配置的示图。

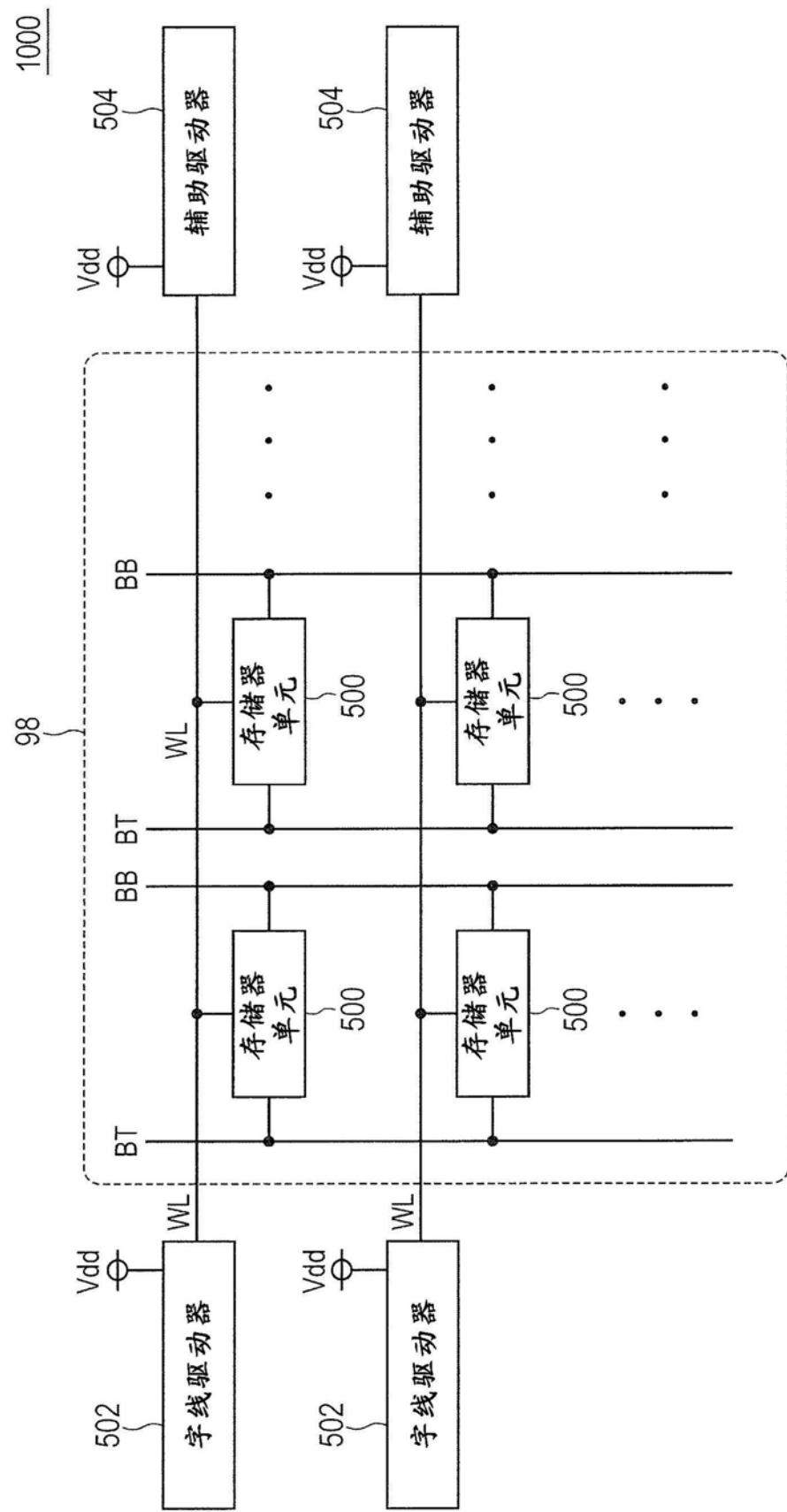

[0011] 图2是图示第二实施例的半导体器件的配置的示图。

[0012] 图3是图示第二实施例中的字线WL的前端和终端和辅助驱动器的电压改变的示图。

[0013] 图4是图示第三实施例的半导体器件的配置的示图。

[0014] 图5是图示第三实施例中的字线WL的前端和终端和辅助驱动器的电压改变的示

图。

- [0015] 图6是图示第四实施例的半导体器件的配置的示图。

- [0016] 图7是图示第四实施例中的字线WL的前端和终端和辅助驱动器的电压改变的示图。

- [0017] 图8是各自图示第五实施例的存储器单元的配置和布局的示图。

## 具体实施方式

- [0018] 现在将使用附图描述本发明的优选的实施例。

- [0019] 第一实施例

- [0020] 图1是图示第一实施例的半导体器件的配置的示图。

- [0021] 参考图1,该半导体器件1000包括存储器阵列98、多个字线WL、多个位线对BT和BB、多个字线驱动器502、第一电源Vdd和多个辅助驱动器504。

- [0022] 存储器阵列98包括以矩阵布置的多个存储器单元。

- [0023] 字线WL被提供并且分别地对应于存储器阵列98的各行。字线WL耦合到对应行的存储器单元500。

- [0024] 位线对BT和BB被提供并且分别地对应于存储器阵列98的各列。位线对BT和BB耦合到对应列的存储器单元500。

- [0025] 字线驱动器502耦合到字线WL的一个端部。当选择对应行时,字线WL的一个端部耦合到第一电源Vdd。

- [0026] 辅助驱动器504耦合到字线WL的另一端部。根据字线WL的另一端部的电压,字线WL的另一端部耦合到电源Vdd。

- [0027] 因此,在该实施例中,由辅助驱动器504使得字线WL的另一端部的电压上升。因此,在激活字线WL时,防止远离字线驱动器502的位置的电压的上升速度小于靠近字线驱动器502的位置的电压的上升速度。

- [0028] 第二实施例

- [0029] 图2是图示第二实施例的半导体器件的配置的示图。

- [0030] 半导体器件100包括存储器阵列62、多个字线WL、多个位线对BT和BB、多个字线驱动器22、多个辅助驱动器10、多个列选择器4、多个预充电路3、控制电路/地址解码器21、多个写入驱动器5和多个感测放大器6。

- [0031] 存储器阵列62包括以矩阵布置的多个存储器单元1。在图2中,以两行和两列的形式表示存储器单元1。存储器单元1是SRAM(静态随机存取存储器)单元。

- [0032] 存储器单元1中的每一个包括PMOS(金属氧化物半导体)晶体管P1和P2作为负载晶体管、NMOS晶体管N1和N2作为驱动器晶体管和NMOS晶体管N20和N21作为存取晶体管。

- [0033] 负载晶体管P1和负载晶体管P2的源极二者耦合到内部电源电压Vdd,并且其漏极相应地耦合到存储器节点A和存储器节点B,并且其栅极相应地耦合到存储器节点B和存储器节点A。

- [0034] 驱动器晶体管N1和驱动器晶体管N2的源极二者耦合到接地的电源(接地的),并且其漏极相应地耦合到存储器节点A和存储器节点B,并且其栅极相应地耦合到存储器节点B和存储器节点A。

[0035] 存取晶体管N20和N21的源极相应地耦合到存储器节点A和存储器节点B,其漏极耦合到对应的位线BT和位线BB,并且其栅极二者耦合到对应的字线WL。

[0036] PMOS晶体管P1和NMOS晶体管N1形成逆变器,并且将写入存储器节点B中的数据的反相信号输出给存储器节点A。PMOS晶体管P2和NMOS晶体管N2形成逆变器,并且将写入存储器节点A中的数据的反相信号输出给存储器节点B。因此,PMOS晶体管P1和PMOS晶体管P2和NMOS晶体管N1和NMOS晶体管N2形成锁存电路,其保持写入存储器节点A和存储器节点B中的数据。

[0037] 字线WL被提供并且分别地对应于存储器阵列62的各行。字线WL耦合到对应行的存储器单元500。

[0038] 位线对BT和BB被提供并且分别地对应于存储器阵列62的各列。位线对BT和BB耦合到对应列的存储器单元500。

[0039] 控制电路/地址解码器21包括行解码器和列解码器,以将地址指定的字线WL驱动到选择状态中。行解码器根据行地址信号生成行选择信号,同时列解码器根据列地址信号选择对应于所选择列的位线对。

[0040] 特别地,行解码器将行地址信号解码以在读取操作或写入操作时生成行选择信号。例如,在选择图2中所图示的第0行时,行解码器激活并且使选择信号XU0和XL0到高电平中。在选择图2中所图示的第1行时,其激活并且使选择信号XU1和XL1到高电平中。

[0041] 在读取操作或写入操作时,列解码器将列地址信号解码来生成列选择信号。例如,列解码器在选择图2中所图示的第0列时激活并且使选择信号Y0到高电平中,并且在选择图2中所图示的第1列时激活并且使选择信号Y1到高电平中。

[0042] 列选择器4包括逆变器IV1、逆变器IV2、PMOS晶体管P5和PMOS晶体管P6以及NMOS晶体管N5和NMOS晶体管N6。第0列的列选择器4中的逆变器IV1接收选择信号Y0。第1列的列选择器4中的逆变器IV1接收选择信号Y1。逆变器IV2接收逆变器IV1的输出。在位线BT、写入驱动器5的输出节点0与感测放大器6的输入节点I之间提供PMOS晶体管P5和NMOS晶体管N5。PMOS晶体管P5的栅极接收逆变器IV1的输出。NMOS晶体管N5的栅极接收逆变器IV2的输出。在位线BB、写入驱动器5的反相输出节点N0与感测放大器6的反相输入节点NI之间提供PMOS晶体管P6和NMOS晶体管N6。PMOS晶体管P6的栅极接收逆变器IV1的输出。NMOS晶体管N6的栅极接收逆变器IV2的输出。

[0043] 预充电路3包括PMOS晶体管P3、P4和P20。在电源Vdd与位线BT之间提供PMOS晶体管P3。PMOS晶体管P3接收逆变器IV2的输出。在电源Vdd与位线BB之间提供PMOS晶体管P4。PMOS晶体管P4接收逆变器IV2的输出。在位线BT与位线BB之间提供PMOS晶体管P20。PMOS晶体管P20的栅极接收逆变器IV2的输出。

[0044] 当用于选择第0列的选择信号Y0处于低电平时,将执行以下程序。

[0045] PMOS晶体管P3、P4、P4和P20将被导通(ON),并且利用电压Vdd对第0列的位线对BT和BB进行预充电。

[0046] 当用于选择第0列的选择信号Y0处于高电平时,将执行以下程序。

[0047] PMOS晶体管P3、P4、P4和P20将被关断(OFF),并且完成第0列的位线对BT和BB的预充电。PMOS晶体管P5和PMOS晶体管P6和NMOS晶体管N5和NMOS晶体管N6被导通(ON)。第0列的位线对BT和BB耦合到写入驱动器5和感测放大器6。

- [0048] 当用于选择第0列的选择信号Y1处于低电平时,将执行以下程序。

- [0049] PMOS晶体管P3、P4、P4和P20被导通 (ON)。利用电压Vdd对第1列的位线对BT和BB进行预充电。

- [0050] 当用于选择第0列的选择信号Y1处于高电平时,将执行以下程序。

- [0051] PMOS晶体管P3、P4、P4和P20将被关断 (OFF),并且完成第1列的位线对BT和BB的预充电。PMOS晶体管P5和PMOS晶体管P6和NMOS晶体管N5和NMOS晶体管N6被导通 (ON)。第1列的位线对BT和BB耦合到写入驱动器5和感测放大器6。

- [0052] 写入驱动器5和感测放大器6中的每一个被提供用于每个相邻两列,并且耦合到相邻两列的位线对BT和BB。写入驱动器5和感测放大器6中的每一个通常由两列共享。因此,以水平长形状形成存储器阵列62。另外,字线WL被形成长的,这展示该实施例的重大效果。

- [0053] 写入驱动器5在将数据写入存储器单元1时将对应于写入数据的电压输出到第0列和第1列中的所选择的一个的位线对BT和BB,即 (高电平、低电平) 或 (低电平、或高电平)。

- [0054] 感测放大器6在从存储器单元1读取数据时放大第0列和第1列的所选择的列的位线BT和BB的电位差。

- [0055] 字线驱动器22和辅助驱动器10被提供并且对应于存储器阵列62的字线WL。字线驱动器22中的每一个耦合到对应的字线WL的前端X。辅助驱动器10耦合到对应的字线WL的终端Y。

- [0056] 当选择对应的行时,字线驱动器22将耦合的字线WL的端部耦合到电源Vdd。

- [0057] 字线驱动器22包括逆变器,其具有NAND电路NAN1、PMOS晶体管P7和NMOS晶体管N7。该逆变器的输入耦合到NAND电路NAN1的输出,同时该逆变器的输出耦合到字线WL的前端。

- [0058] 第0行的字线驱动器22中的NAND电路NAN1接收选择信号XU0和选择信号XL0。当选择第0行时,选择信号XU0和XL0处于高电平,并且NAND电路NAN1的输出处于低电平。当未选择第0行时,选择信号XU0和选择信号XL0中的至少一个处于低电平,并且NAND电路NAN1的输出处于高电平。

- [0059] 第1行的字线驱动器22中的NAND电路NAN1接收选择信号XU1和选择信号XL1。当选择第1行时,选择信号XU1和选择信号XL1处于高电平,并且NAND电路NAN1的输出处于低电平。当未选择第1行时,选择信号XU1和选择信号XL1中的至少一个处于低电平,并且NAND电路NAN1的输出处于高电平。

- [0060] 当NAND电路NAN1的输出处于低电平时,PMOS晶体管P7被导通 (ON),并且NMOS晶体管N7被关断 (OFF)。因此,字线WL的前端X耦合到电源Vdd,并且字线WL的前端的电压上升。电压的该上升逐渐地被发送到字线WL的终端。

- [0061] 当NAND电路NAN1的输出处于高电平时,PMOS晶体管P7被导通 (OFF),并且NMOS晶体管N7被关断 (ON)。因此,字线WL的前端X接地,并且字线WL的前端的电压上升。电压的该上升逐渐地被发送到字线WL的终端。

- [0062] 根据对应的字线WL的另一端部的电压,辅助驱动器10将对应的字线WL的终端Y耦合到电源Vdd或者将对应的字线WL的终端Y与电源Vdd关断。

- [0063] 辅助驱动器10包括逆变器IV3和PMOS晶体管P8。

- [0064] 在字线WL的终端Y与电源Vdd之间提供PMOS晶体管P8。逆变器IV3的输入耦合到字线WL的终端Y,同时逆变器IV3的输出耦合到PMOS晶体管P8的栅极。

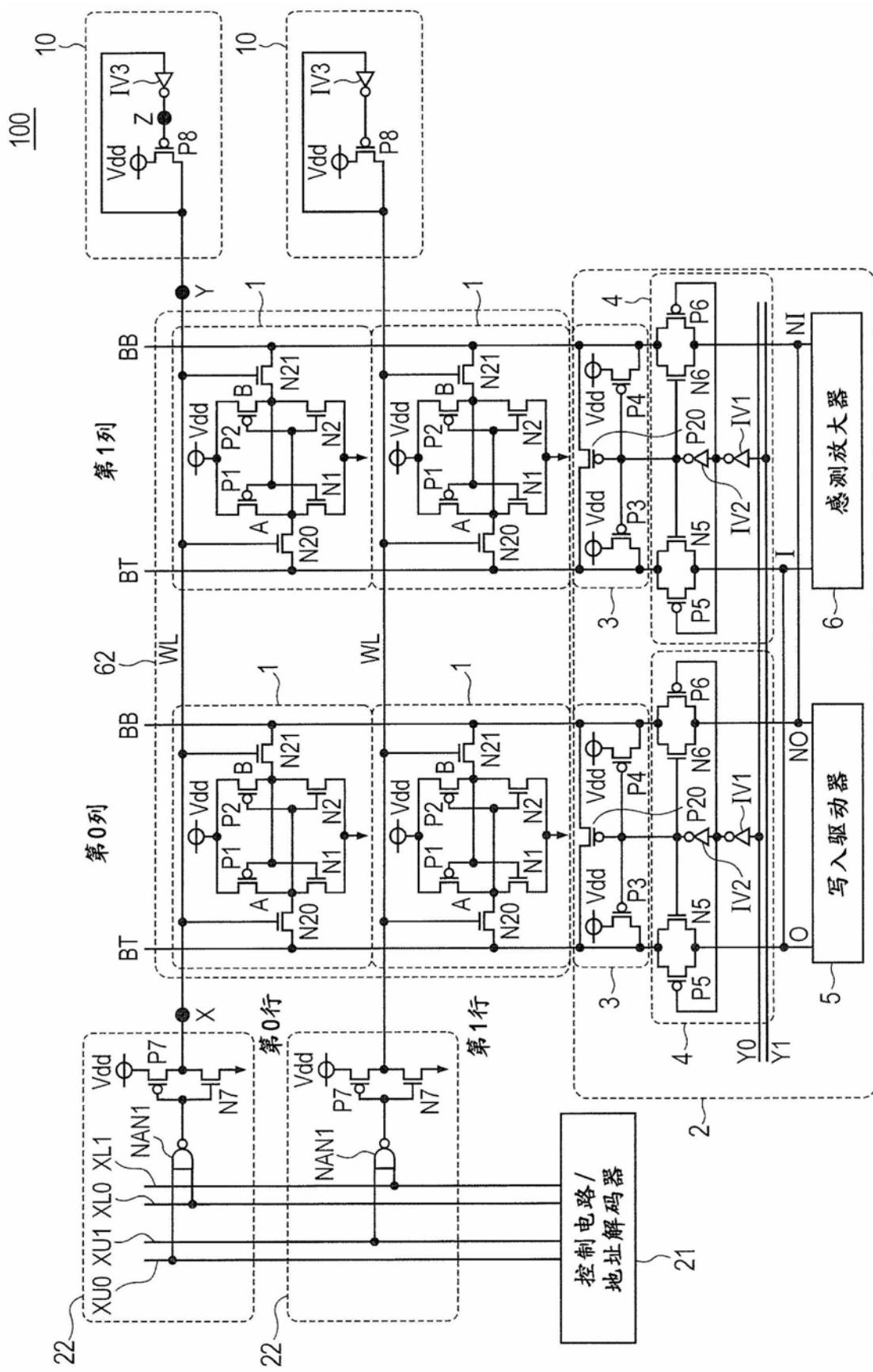

[0065] 图3是图示第二实施例中的字线WL的前端和终端和辅助驱动器10的电压改变的示图。

[0066] 在时间t1处,当字线WL的前端X通过所选择的行的字线驱动器22耦合到电源Vdd时,字线WL的前端X的电压相对地以高速度上升,如由(1)所图示的,同时字线WL的终端Y的电压相对地以低速度上升,如由(2)所图示的。

[0067] 在时间t2处,当字线WL的终端Y的电压超过辅助驱动器10中的逆变器IV3的阈值电压时,逆变器IV3的输出终端Z的电压处于低电平。然后,辅助驱动器10中的PMOS晶体管P8被导通(ON)。因此,电源Vdd耦合到字线WL的终端Y,因此加速终端Y处的电压的上升,如由(3)所图示的。

[0068] 在时间t3处,当所选择的行向非选择的行偏移时并且当字线WL的前端X由字线驱动器22接地时,字线WL的前端X的电压相对地以高速度下降,如由(4)所图示的。由于PMOS晶体管P8保持导通(ON),字线WL的终端Y的电压相对地以低速度下降,如由(5)所图示的。

[0069] 在时间T4处,当字线WL的终端Y的电压等于或小于辅助驱动器10中的逆变器IV3的阈值时,逆变器IV3的输出终端Z的电压处于高电平。然后,辅助驱动器10中的PMOS晶体管P8被关断(OFF)。因此,断开电源Vdd和字线WL的终端Y,因此加速终端Y处的电压的下降,如由(6)所图示的。

[0070] 根据该实施例,如上文所描述的,通过辅助驱动器10在激活字线WL时将字线WL的终端Y耦合到电源Vdd。另外,在激活字线WL时断开字线WL的终端Y和电源Vdd。因此,避免远离字线驱动器22的位置的电压的上升速度和下降速度小于靠近字线驱动器22的位置的电压的上升速度和下降速度是可能的。

[0071] 第三实施例

[0072] 图4是图示第三实施例的半导体器件的配置的示图。

[0073] 现在将对图4的半导体器件200与图2的半导体器件100的那些差异中的任一个进行描述。

[0074] 辅助控制电路12包括两级逆变器IV4和IV5。

[0075] 控制电路/地址解码器21通过信号线LA将控制信号脉冲PL发送给辅助控制电路12和辅助驱动器11。信号线LA被提供在与其中实现半导体器件200的衬底水平的方向上的存储器阵列62外部。

[0076] 逆变器IV4从控制电路/地址解码器21接收控制信号脉冲PL。逆变器IV5从逆变器IV4接收输出。

[0077] 辅助驱动器11包括NAND电路NAN2和PMOST晶体管P8。

[0078] 在字线WL的终端Y与电源Vdd之间提供PMOS晶体管P8。在该实施例中,当字线WL的终端Y的电压增加直到预定值时,PMOS晶体管P8在字线WL的上升时间处被导通(ON)。其响应于来自控制电路/地址解码器21的控制电路在字线WL的下降时间处被关断(OFF)。

[0079] NAND电路NAN2的输入耦合到字线WL的终端Y,同时其另一输入耦合到逆变器IV5。NAND电路NAN2的输出耦合到PMOS晶体管P8的栅极。

[0080] 控制信号脉冲PL为来自控制电路/地址解码器21的输出,并且通过逆变器IV4和IV5被输入到NAND电路NAN2。该控制信号脉冲PL在从字线WL的上升开始时间直到字线WL的终端Y的电压达到Vdd的周期中处于高电平,并且脉冲在从字线WL的下降开始时间直到字线

WL的终端Y的电压到达接地电压(0V)的周期中处于低电平。

[0081] 图5是图示第三实施例中的字线WL的前端和终端和辅助驱动器的电压改变的示图。

[0082] 在时间t0处,一旦接收到从控制电路/地址解码器21输出的控制信号脉冲PL,则NAND电路NAN2的输入终端W的电压上升。

[0083] 在时间t1处,当字线WL的前端X通过所选择的行的字线驱动器22耦合到电源Vdd时,字线WL的前端X的电压相对地以高速度上升,如由(1)所图示的,并且字线WL的终端Y的电压相对地以低速度上升,如由(2)所图示的。

[0084] 在时间t2处,如果字线WL的终端Y的电压足够高并且超过被包括在NAND电路NAN2中的逆变器的阈值,则辅助驱动器10中的NAND电路NAN2的输出终端Z的电压处于低电平。然后,辅助驱动器10中的PMOS晶体管P8将被导通。因此,电源Vdd耦合到字线WL的终端Y,因此加速终端Y处的电压的上升,如由(3)所图示的。

[0085] 在时间t3处,如果控制信号脉冲PL在NAND电路NAN2的输入终端W处下降,则NAND电路NAN2的输出终端Z的电压处于高电平。然后,PMOS晶体管P8被关断(OFF)。因此,断开电源Vdd和字线WL的终端Y。

[0086] 在时间t4处,当所选择的行向非选择的行偏移时并且当字线WL的前端X由字线驱动器22接地时,字线WL的前端X的电压相对地以高速度下降,如由(4)所图示的。由于PMOS晶体管P8已经被关断(OFF),字线WL的终端Y的电压也相对地以高速度下降,如由(5)所图示的。

[0087] 在第二实施例中,存在其中辅助驱动器10中的上拉PMOS晶体管P8和被包括在字线驱动器22中的NMOS晶体管N7二者在字线WL的失活时间处被导通(ON)的时间段。因此,如由图3的(5)所图示的,终端Y的电压变为以低速度下降。

[0088] 在该实施例中,相反,不存在其中上拉PMOS晶体管P8和被包括在字线驱动器22中的NMOS晶体管N7被导通(ON)的这样的时间段。因此,如由图5的(5)所图示的,终端Y的电压以与前端X的电压相同速度下降。因此,在字线WL的失活时间处实现高速操作和低功耗操作是可能的。

[0089] 由于字线WL被布置在正好在其中布置存储器单元1的区域上面的半导体层中,几乎没有设计形成厚字线WL。在该实施例中,从控制电路/地址解码器21输出的控制信号脉冲PL通过被布置在存储器阵列62外部的信号线LA被发送到辅助控制电路12和辅助驱动器11。因此,在没有对像字线WL的布局的限制的情况下通过具有厚宽度实现低电阻是可能的。

[0090] 第四实施例

[0091] 图6是图示第四实施例的半导体器件的示图。

[0092] 现在将对图6的半导体器件300与图2的半导体器件100的那些差异中的任一个进行描述。

[0093] 辅助驱动器13包括NAND电路NAN3、PMOS晶体管P8和延迟电路DL。延迟电路DL包括三级逆变器IV6、IV7和IV8。

[0094] 逆变器IV6的输入耦合到字线WL的终端Y,逆变器IV7的输入耦合到逆变器IV6的输出,并且逆变器IV8的输入耦合到逆变器IV7的输入。

[0095] 在字线WL的终端Y与电源Vdd之间提供PMOS晶体管P8。PMOS晶体管P8通过单脉冲被

导通 (ON) ,所述单脉冲将在字线WL的上升时间,在从字线WL的终端的电压已经上升直到预定值的预定时间段处于低电平。

[0096] NAND电路NAN3的一个输入耦合到字线WL的终端Y,同时其另一输入耦合到逆变器IN8的输出。NAND电路NAN3的输出耦合到PMOS晶体管P8的栅极。

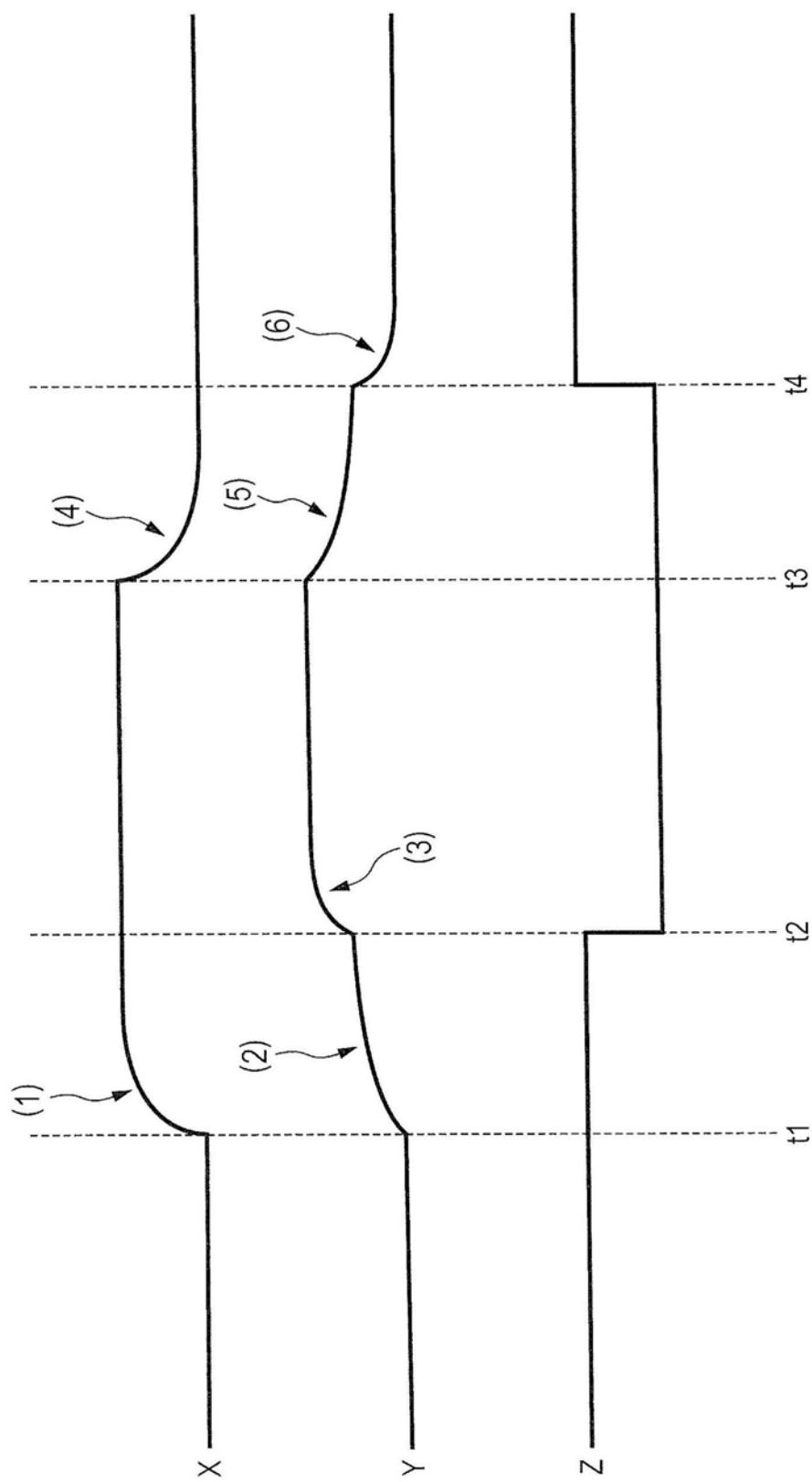

[0097] 图7是图示第四实施例中的字线WL的前端和终端和辅助驱动器13的电压改变的示图。

[0098] 在时间t1处,当字线WL的前端X通过所选择的行的字线驱动器22耦合到电源Vdd时,字线WL的前端X的电压相对地以高速度上升,如由 (1) 所图示的,同时字线WL的终端Y的电压相对地以低速度上升,如由 (2) 所图示的。

[0099] 在时间t2处,当字线WL的终端Y的电压足够高并且超过逆变器IV6的阈值时,通过延迟电路DL和NAND电路NAN3生成单脉冲。该单脉冲用于使得NAND电路NAN3的输出终端Y的电压在从时间t2直到由延迟电路DL造成的延迟时间dt的周期内处于低电平,如由 (3) 所图示的。然后,辅助驱动器10中的PMOS晶体管P8将被导通。因此,电源Vdd耦合到字线WL的终端Y,因此加速终端Y处的电压的上升,如由 (3) 所图示的。

[0100] 在时间t3处,当单脉冲结束时并且当终端Z的电压处于高电平时,辅助驱动器10中的PMOS晶体管P8将被关断 (OFF) 。因此,断开电源Vdd和字线WL的终端Y。

[0101] 在时间t4处,当所选择的行向非选择的行偏移时并且当字线WL的前端X由字线驱动器22接地时,字线WL的前端X的电压相对地以高速度下降,如由 (4) 所图示的。由于PMOS晶体管P8已经被关断 (OFF) ,字线WL的终端Y的电压也相对地以高速度下降,如由 (5) 所图示的。

[0102] 根据该实施例,如上文所描述的,像第三实施例那样,不存在辅助驱动器10中的上拉PMOS晶体管P8和被包括在字线驱动器22中的NMOS晶体管N7二者在字线WL的失活时间处被导通 (ON) 的第二实施例的这样的现象。因此,在字线WL的失活时间处实现高速操作和低功耗操作是可能的。

[0103] 根据该实施例,像第三实施例那样,不存在从控制电路/地址解码器21输出控制信号脉冲PL的需要,因此增加时序设计中的自由度。

[0104] 第五实施例

[0105] 以上实施例的存储器单元1垂直地长的存储器单元。该实施例的半导体器件包括横向地长存储器单元作为存储器单元。

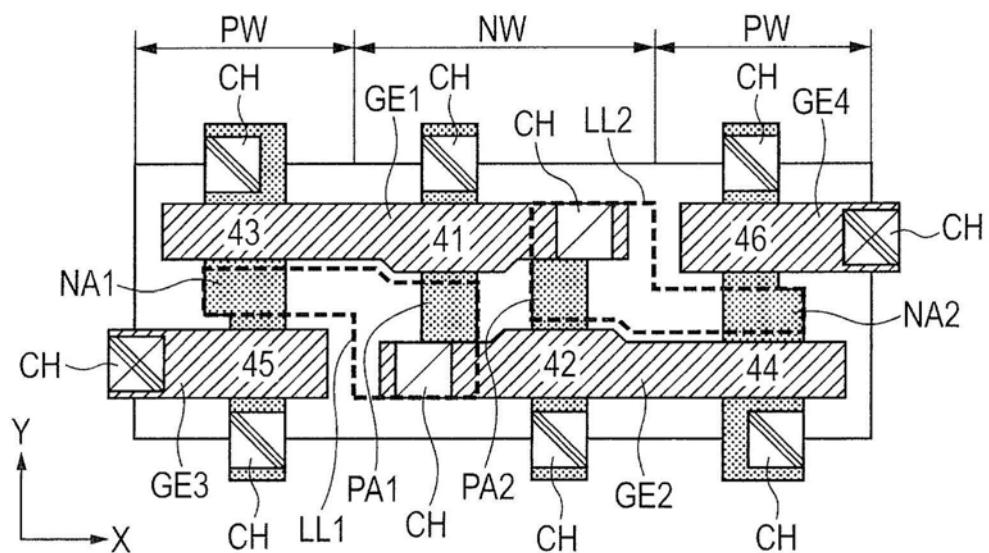

[0106] 像以上实施例的存储器单元1那样,该实施例的存储器单元MC包括负载晶体管 (P沟道MOS晶体管) 41和42、驱动器晶体管 (N沟道MOS晶体管) 43和44和存取晶体管 (N沟道MOS晶体管) 45和46,如图8A所示。该存储器单元500与晶体管41至晶体管46的布局中的存储器单元1不同。

[0107] 即,如图8B中所图示的,横向地长存储器单元MC形成在被布置在其两侧的一个N型阱NW和P型阱PW和PW的表面上。由多晶硅层形成的那些电极包括在从N型阱NW到一个P型阱PW的图示的X方向上延伸的栅极电极GE1、在从N型阱NW到另一P型阱PW的图示的X方向上延伸的栅极电极GE2、在一个P型阱PW上的图示的X方向上延伸的栅极电极GE3和在另一P型阱PW上的X方向上延伸的栅极电极GE4。

[0108] 形成了有源层,其包括跨一个P型阱PW中的栅极电极GE1和GE3的N型有源层NA1、跨

另一P型阱PW中的栅极电极GE2和GE4的N型有源层NA2和跨N型阱NW中的栅极电极GE1和GE2的P型有源层PA1和PA2。

[0109] 栅极电极GE1和P型有源层PA1形成P沟道MOS晶体管41。栅极电极GE2和P型有源层PA2形成P沟道MOS晶体管42。栅极电极GE1和N型有源层NA1形成N沟道MOS晶体管43。栅极电极GE3和N型有源层NA1形成N沟道MOS晶体管45。栅极电极GE2和N型有源层NA2形成N沟道MOS晶体管44。栅极电极GE4和N型有源层NA2形成N沟道MOS晶体管46。

[0110] 跨N型有源层NA1的中心段、P型有源层PA1的一个端部段和栅极电极GE2的一个端部段形成本本地线LL1。跨N型有源层NA2的中心段、P型有源层PA1的一个端部段和栅极电极GE1的一个端部段形成本本地线LL2。在图8B中,其中有源层NA1和PA1重叠本地线LL1的那些部分是导电的。其中有源层NA2和PA2重叠本地线LL2的那些部分是导电的。栅极电极GE2和本地线LL1通过接触孔CH耦合到彼此,并且栅极电极GE1和本地线LL2通过接触孔CH耦合到彼此。

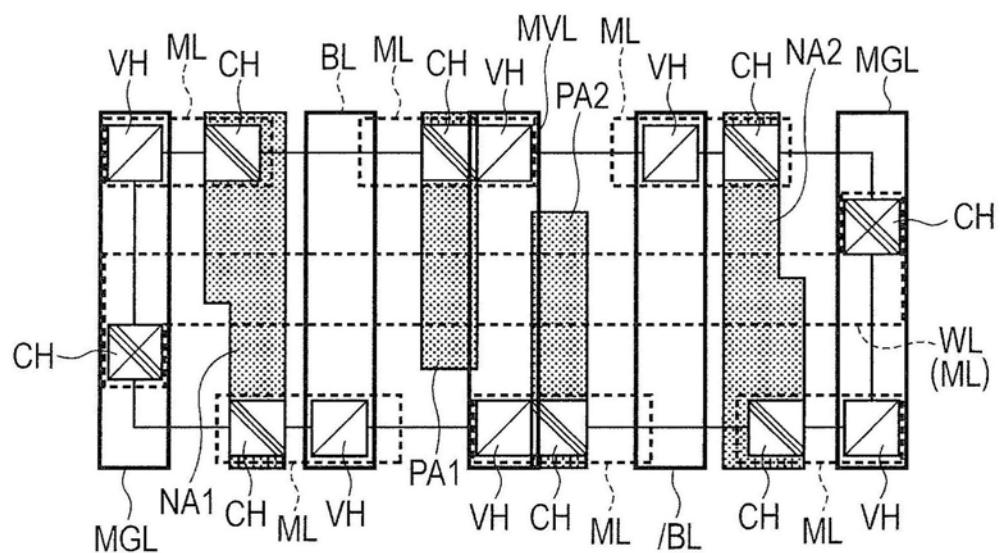

[0111] 如图8C中所图示的,在图示的X方向上延伸的多个金属线ML由第一铝线层形成。而且,在此,在图示的Y方向上延伸的存储器单元接地线MGL、位线BL、存储器单元电源线MVL、位线/BL和存储器单元接地线MGL由第二铝线层形成。关于金属线ML,跨存储器单元MC的中心段的金属线是字线WL。

[0112] P型有源层PA1的一个端部(P沟道MOS晶体管41的源极)通过接触孔CH、金属线ML并且经由孔VH耦合到存储器单元电源线MVL。P型有源层PA2的一个端部(P沟道MOS晶体管42的源极)通过接触孔CH、金属线ML并且经由孔VH耦合到存储器单元电源线MVL。

[0113] N型有源层NA1的一个端部(N沟道MOS晶体管43的源极)通过接触孔CH、金属线ML并且经由孔VH耦合到存储器单元接地线MGL。N型有源层NA2的一个端部(N沟道MOS晶体管44的源极)通过接触孔CH、存储器线ML并且经由孔VH耦合到存储器单元接地线MGL。

[0114] N型有源层NA1的另一端部(N沟道MOS晶体管45的漏极)通过接触孔CH、金属线ML并且经由孔VH耦合到位线BL。N型有源层NA2的另一端部(N沟道MOS晶体管46的漏极)通过接触孔CH、金属线ML并且经由孔VH耦合到位线/BL。栅极电极GE3和栅极电极GE4相应地通过接触孔CH耦合到字线WL。

[0115] 在该实施例中,如上文所描述的,由于存储器单元MC是横向地长的,因而该实施例的字线WL形成长的。在激活字线WL时,长字线WL引起远离字线驱动器22的位置的电压的上升速度小于靠近字线驱动器22的位置的电压的上升速度的明显的问题。

[0116] 该实施例的半导体器件包括第一实施例至第四实施例中所描述的辅助驱动器10、11和13,从而防止该问题。

[0117] 在上文实施例中,写入驱动器5和感测放大器6被提供用于每个相邻两列,并且耦合到相邻两列然而,本发明不限于此。写入驱动器5和感测放大器6可以被提供用于每个相邻三个或更多个列,并且可以耦合到相邻三个或更多个列的位线对BT和BB。

[0118] 因此,基于优选的实施例,已经特别地描述由本发明人做出的本发明。然而,本发明不限于优选的实施例。更不用说,可以在不脱离其范围的情况下做出各种改变。

图1

图2

图3

图4

图5

图6

图7

图8A

图8B

图8C