(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4253245号

(P4253245)

(45) 発行日 平成21年4月8日(2009.4.8)

(24) 登録日 平成21年1月30日(2009.1.30)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/786 (2006.01)H01L 29/78 616A

H01L 29/78 616V

請求項の数 5 (全 7 頁)

(21) 出願番号 特願2003-405622 (P2003-405622)

(22) 出願日 平成15年12月4日 (2003.12.4)

(65) 公開番号 特開2005-167057 (P2005-167057A)

(43) 公開日 平成17年6月23日 (2005.6.23)

審査請求日 平成18年2月22日 (2006.2.22)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100089266

弁理士 大島 陽一

(72) 発明者 浅野 悅子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 荒尾 達也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】薄膜トランジスタの製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に形成された非単結晶の島状の結晶性シリコン膜と、前記結晶性シリコン膜上に絶縁膜を介して配置されたゲート電極とを有し、前記結晶性シリコン膜は、ソース領域と、ドレイン領域と、チャネル領域と、前記ソース領域と前記ドレイン領域との間及び前記ドレイン領域とチャネル領域との間にそれぞれ設けられたLDD領域を含む薄膜トランジスタの製造方法であって、

前記LDD領域に対するドーピングを高加速と低加速とに前後2段階に分けて行い、当該ドーピングによって前記LDD領域の上層部にドープされた領域の不純物濃度より当該LDD領域の下層部にドープされた領域の不純物濃度を高くすることを特徴とする薄膜トランジスタの製造方法。

## 【請求項2】

基板上に形成された非単結晶の島状の結晶性シリコン膜と、前記結晶性シリコン膜上に絶縁膜を介して配置されたゲート電極とを有し、前記結晶性シリコン膜は、ソース領域と、ドレイン領域と、チャネル領域と、前記ソース領域と前記ドレイン領域との間及び前記ドレイン領域とチャネル領域との間にそれぞれ設けられたLDD領域を含む薄膜トランジスタの製造方法であって、

前記LDD領域に対するドーピングを軽重2種のイオンを用いて行い、当該ドーピングによって前記LDD領域の上層部にドープされた領域の不純物濃度より当該LDD領域の下層部にドープされた領域の不純物濃度を高くすることを特徴とする薄膜トランジスタの

製造方法。

**【請求項 3】**

前記 LDD 領域に対する軽重 2 種のイオンによるドーピングは、重いイオンによるドーピングと軽いイオンによるドーピングとに前後 2 段階に分けて行うことを特徴とする請求項 2 に記載の薄膜トランジスタの製造方法。

**【請求項 4】**

前記 LDD 領域に対する軽重 2 種のイオンによるドーピングは、重いイオンによるドーピングと軽いイオンによるドーピングとを同時に行うことを特徴とする請求項 2 に記載の薄膜トランジスタの製造方法。

**【請求項 5】**

前記 LDD 領域の上層部の不純物濃度は、 $5 \times 10^{17} \sim 5 \times 10^{18}$  atoms/cm<sup>3</sup> であることを特徴とする請求項 1 乃至 4 の何れか一項に記載の薄膜トランジスタの製造方法。

**【発明の詳細な説明】**

**【背景技術】**

**【0001】**

近年、絶縁基板上に、薄膜状の活性層（活性領域ともいう）を有する絶縁ゲート型の半導体装置、特に、薄膜状の絶縁ゲート型のトランジスタ、いわゆる薄膜トランジスタ（TFT）が、アクティブマトリックス型 LCD をはじめとして広く利用されつつある。このようなトランジスタに於いて、ホットキャリア劣化を回避し、高信頼性を確保するために、

LDD (Lightly Doped Drain) 構造や、GOLD (Gate Overlapped LDD) 構造が用いられる場合がある。

このような構造に於いては、ソース・ドレイン低濃度領域のキャリア濃度は、ドレイン端の横方向電界が最も緩和される大きさに定められる。以下の記載では、LDD (Lightly Doped Drain) 構造や、GOLD (Gate Overlapped LDD) 構造に於けるオフセット領域或いはオーバラップ領域を含むソース・ドレイン低濃度領域を、必要に応じて LDD 領域と総称するものとする。

**【0002】**

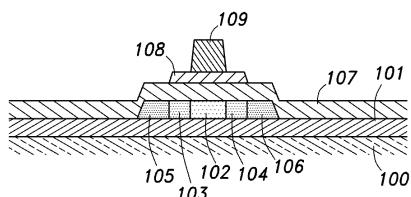

図 1 は、従来形式の GOLD 構造薄膜トランジスタを示す。これは、例えば以下のようなプロセスにより製造することができる。ガラス基板 100 上に下地酸化珪素膜 101 を設け、さらにその上にアモルファスシリコン膜をプラズマ CVD 法により連続的に成膜する。次に、アモルファスシリコン膜を、熱アニール及びレーザによる光アニールにより、結晶性シリコン膜とし、それを、エッチングにより複数の島状領域とする。さらに、プラズマ CVD 法によって酸化珪素膜 107 をゲート絶縁膜として堆積し、スパッタ法によって、TaN 膜 108 と W 膜 109 とを堆積し、更にエッチングすることにより、TaN 膜 108 を比較的広幅とし、W 膜 109 を相対的に狭幅とする。

**【0003】**

それに引き続き、ゲート電極 108, 109 をマスクとし、燐イオンを注入（ドーピング）し、ドーピングされた燐を活性化する。W 膜 109 によりマスキングされた領域は殆どドーピングされないチャネル領域 102 となり、ゲート電極 108, 109 によりマスキングされない領域は、高濃度の燐ドーピングがなされ、ソース・ドレイン領域 105, 106 を形成する。TaN 膜 108 によりマスキングされた領域は、燐による低濃度のドーピングがなされ、オーバラップ領域 103, 104 を形成する。このような GOLD 構造の詳しい製造方法については、特許文献 1 を参照されたい。

**【特許文献 1】** 特開 2001-094113 このようなオーバラップ領域、即ち LDD 構造が設けられることにより、電界緩和効果が生じ、絶縁破壊などの問題を防止することができる。特に、GOLD 構造に於いては、ゲート電極が、LDD 領域まで延伸して設けられるため、LDD 領域のキャリア濃度もゲート電極によってある程度制御される。その結果、LDD 領域の不純物濃度が低くとも、低濃度の LDD 領域の直列抵抗によって相互コンダクタンスが減少したり、LDD 領域上のゲート酸化膜に注入されるホットキャリア

10

20

30

40

50

によってトランジスタ特性が変動するというようなことは少なくなる。

#### 【0004】

特に、GOLD構造やLDD構造の濃度を所定の最適値とすることにより最も効果的にホットキャリア劣化を抑制することができる。しかしながら、そのような濃度では、抵抗値が比較的高くなり、ON特性が不良となる。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

このような従来技術の問題点に鑑み、本発明の目的は、LDD或いはGOLD構造薄膜トランジスタに於いて、オフセット領域或いはオーバラップ領域のドレイン端の横方向電界を効果的に緩和し、トランジスタの信頼性を高め、しかもON特性の低下を回避するような薄膜トランジスタの好適な製造方法を提供することにある。10

#### 【課題を解決するための手段】

#### 【0007】

このような目的は、本発明によれば、基板上に形成された非単結晶の島状の結晶性シリコン膜と、前記結晶性シリコン膜上に絶縁膜を介して配置されたゲート電極とを有し、前記結晶性シリコン膜は、ソース領域と、ドレイン領域と、チャネル領域と、前記ソース領域と前記ドレイン領域との間及び前記ドレイン領域とチャネル領域との間にそれぞれ設けられたLDD領域を含む薄膜トランジスタの製造方法であって、前記LDD領域に対するドーピングを高加速と低加速とに前後2段階に分けて行い、あるいは軽重2種のイオンを用いて行い。20

当該ドーピングによって前記LDD領域の上層部にドープされた領域の不純物濃度より当該LDD領域の下層部にドープされた領域の不純物濃度を高くすることを特徴とする薄膜トランジスタの製造方法によって達成される。このような製造方法によれば、既存の製造プロセスに対する変更を最小限とすることができます。

#### 【0008】

発明者の知見によれば、このような薄膜トランジスタに於けるホットキャリア劣化の度合は、LDD領域の上層部即ちゲート絶縁膜に隣接する部分の不純物濃度により決定される。しかるに、LDD領域のオン抵抗は、LDD領域全体の不純物濃度により決定される。従って、LDD領域の上層部の不純物濃度をホットキャリア劣化を効果的に抑制できるような低濃度とし、LDD領域の中・下層部の不純物濃度を十分低いオン抵抗を実現し得るように相対的に高濃度とすることにより、ホットキャリア劣化及びそれに起因する諸問題を回避すると同時に、オン抵抗を十分に低い値とし、所要のトランジスタ特性を確保することができる。30

#### 【発明を実施するための最良の形態】

#### 【0010】

以下に添付の図面に示された具体例に基づいて本発明の実施の形態について詳細に説明する。

#### 【0011】

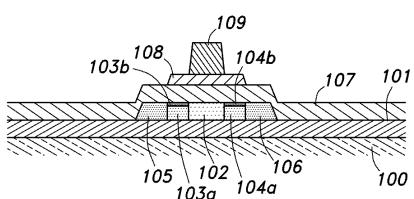

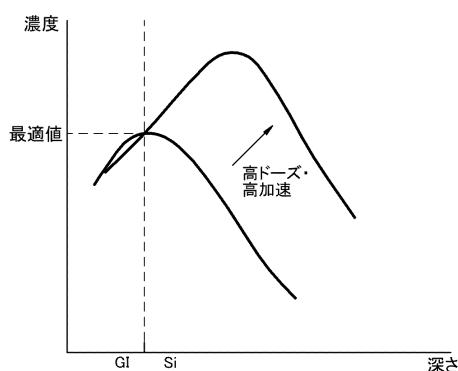

図2は、本発明に基づくGOLD構造薄膜トランジスタを示す。概ね図1に示されたトランジスタと同様であるが、オーバラップ領域103, 104に対する燐のドーピングをやや高ドーズ・高加速とし、比較的低濃度にドーピングされた上側層103b, 104bと、比較的高濃度にドーピングされた下側層103a, 104aとが形成されるようとする。下側層103a, 104aの不純物濃度は、所望の低オン抵抗が達成されるようなレベルに設定し、上側層103b, 104bの不純物濃度は、ホットキャリア劣化を回避し、高信頼性が確保されるように、ドレイン端の横方向電界を効果的に緩和し得るレベルに設定する。本実施例の場合、ホットキャリア劣化を回避するために最適な表面不純物濃度は、 $5 \times 10^{17} \sim 5 \times 10^{18}$  atoms/cm<sup>2</sup>であった。しかしながら、条件が異なる場合にあっては、本発明は、このような数値範囲に限定されない。図3は、高加速の4050

ドーピングを行うことにより、オーバラップ領域の比較的深い領域に高濃度部分を形成できる様子を示している。即ち、高加速のドーピングを行うことにより、不純物が深部に比較的集中し、所要の濃度分布を達成することができる。

#### 【0012】

図2に於いては、あたかも、オーバラップ領域の燐の不純物濃度が2段階に設定されるように示されているが、実際には、連続的な濃度分布が形成されることに留意されたい。また、上記実施例は、GOLD構造薄膜トランジスタに適用されたものであるが、LDD薄膜トランジスタにも等しく適用可能で、LDD領域に於いて、燐のドーピングをやや高ドーズ・高加速とし、比較的低濃度にドーピングされた上側層と、比較的高濃度にドーピングされた下側層とが形成されるようにすることにより、同様の効果を達成することができる。10

#### 【0013】

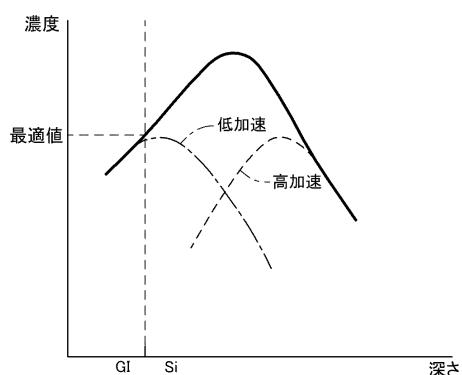

上記したようなオーバラップ領域の濃度分布を実現することは、上記したような方法以外にも可能である。図4に示されるように、比較的高加速のドーピング及び比較的低加速のドーピングを前後して、2段階に行ない、しかもそれぞれのドーズ量を制御することにより、所望の濃度分布を実現することができる。特に、浅い部分の不純物濃度は、低加速ドーピングのドーズ量により、深い部分の不純物濃度は、高加速ドーピングのドーズ量により概ね決定されることから、濃度分布の態様を自由に制御し、本発明の目的を一層好適に達成することができる。言うまでもなく、高加速のドーピング及び比較的低加速のドーピングの順序は任意に選択することができる。20

#### 【0014】

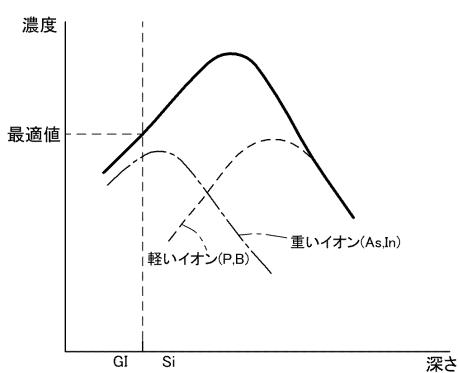

或いは、図5に示されるように、軽重2種のイオンを用いたドーピングを前後して、2段階に行ない、しかもそれぞれのドーズ量を制御することにより、所望の濃度分布を実現することができる。N型領域に対しては、例えば、比較的重いAs及び比較的軽いPを用いたドーピングを前後して、2段階に或いは同時に行ない、しかもそれぞれのドーズ量を制御することにより、所望の濃度分布を実現することができる。P型領域に対しては、例えば、比較的重いIn及び比較的軽いBを用いたドーピングを行なうと良い。これは、軽いイオンは、重いイオンよりも小さな原子半径を有することから、それだけ深く打ち込まれやすく、同程度の加速条件を選択しても、イオンの軽重により、深さ方向についての濃度分布が異なることによるものである。この場合も、軽重2種のイオンを用いたドーピングを2段階に行なう場合、その順序は任意に選択することができる。30

#### 【0015】

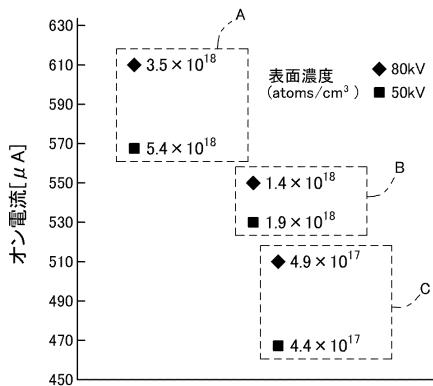

図6は、表面に於ける不純物濃度が同様である場合には、ドーピング加速電圧の低いほうが、オン特性が悪くなる様子を示したものである。ドーピング加速電圧を50kV及び80kVの高低2つの値とし、3種の表面濃度A, B, Cを達成した場合に於いて、ドーピング加速電圧の低いほうが、オン電流が小さく、それだけオン特性が悪いことが示されている。

#### 【0016】

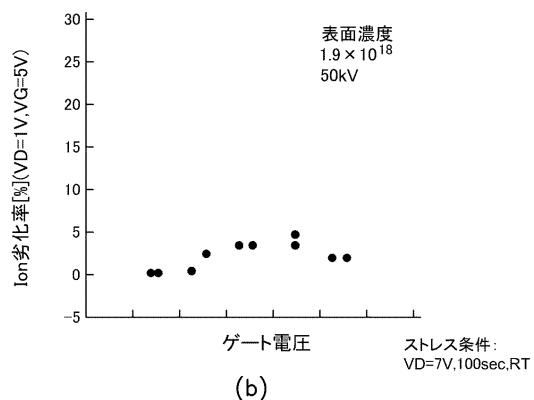

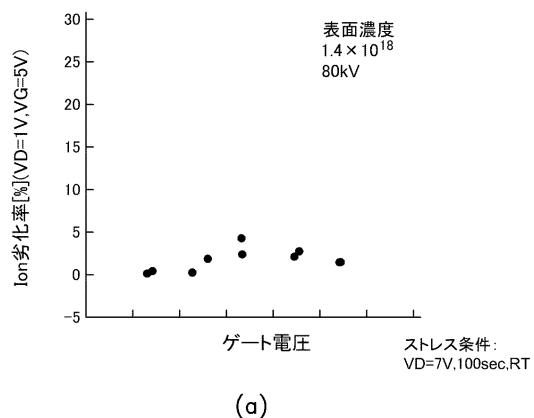

図7は、ドーピング加速電圧を50kV及び80kVの高低2つの値とし、概ね同一の表面濃度が達成された場合に於いて、ホットキャリア劣化の度合が略同程度となることを示している。前記したように、ドーピング加速電圧に応じて、深い部分の不純物濃度に差があるが、ホットキャリア劣化の度合は、深い部分の不純物濃度によらず、表面の不純物濃度により決定されることが示されている。40

#### 【図面の簡単な説明】

#### 【0017】

【図1】従来形式のGOLD構造薄膜トランジスタを示す。

【図2】本発明に基づくGOLD構造薄膜トランジスタを示す。

【図3】高ドーズ・高加速のドーピングを行なうことによりシリコン領域の深い部分に高不純物濃度部分を形成し得る様子を示すグラフ。

【図4】高加速・低加速のドーピングを行なうことによりシリコン領域の深い部分に高不50

純物濃度部分を形成し得る様子を示すグラフ。

【図5】軽重2種のイオンを用いたドーピングを行なうことによりシリコン領域の深い部分に高不純物濃度部分を形成し得る様子を示すグラフ。

【図6】表面に於ける不純物濃度が同様である場合には、ドーピング加速電圧の低いほうが、オン特性が悪くなる様子を示したグラフ。

【図7】(a)及び(b)からなり、表面に於ける不純物濃度が同様である場合には、ドーピング加速電圧に関わらず、即ち深い部分に於ける不純物濃度に関わらず、ホットキャリア劣化の度合が同程度となる様子を示したグラフ。

【符号の説明】

【0018】

100 ガラス基板

10

101 下地酸化珪素膜

102 チャネル領域

103、104 オーバラップ領域

103a, 104a 下側層

103b, 104b 上側層

105、106 ソース・ドレイン領域

107 酸化珪素膜

108 W膜

109 TaN膜

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 松尾 拓哉

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

(72)発明者 享保 昌則

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

(72)発明者 北角 英人

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

審査官 河本 充雄

(56)参考文献 特開2002-185008(JP,A)

特開2004-342936(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786