## (19) World Intellectual Property Organization International Bureau

### (43) International Publication Date 16 October 2003 (16.10.2003)

## **PCT**

## (10) International Publication Number WO 03/085725 A2

(51) International Patent Classification<sup>7</sup>: H01L 23/00

(21) International Application Number: PCT/US03/09017

(22) International Filing Date: 26 March 2003 (26.03.2003)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

10/113,502 1 April 2002 (01.04.2002) US

- (71) Applicant: INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

- (72) Inventors: ESKILDSEN, Steven; 307 Oak Canyon Way, Folsom, CA 95620 (US). MILLS, Duane; 6017 Dodson Road, Shingle Springs, CA 95682 (US).

- (74) Agents: TROP, Timothy, N.; Trop, Pruner & Hu, P.C., Suite 100, 8554 Katy Freeway, Houston, TX 77024 et al. (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NI, NO, NZ, OM, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

3/085725 A2

(54) Title: PROVIDING IN PACKAGE POWER SUPPLIES FOR INTEGRATED CIRCUITS

-1-

# Providing In Package Power Supplies For Integrated Circuits

## **Background**

5

10

15

20

25

30

This invention relates generally to techniques for providing a source of power to an integrated circuit.

All integrated circuits require a power supply. Commonly, the power supply is its own integrated circuit, which electrically couples to the powered device. For example, the powered device and the power supply may both be attached to a printed circuit board and connected to one another through electrical traces on the circuit board. As a result of the need for a separate integrated circuit to supply power, the overall size and cost of the resulting components may be increased.

Thus, it would be desirable to provide a power supply that reduces the size and/or cost of the end electrical product.

## Brief Description of the Drawings

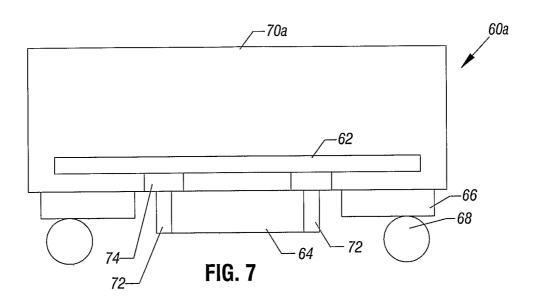

Figure 1 is a schematic depiction of one embodiment of the present invention;

Figure 2 is an enlarged, cross-sectional view of another embodiment of the present invention;

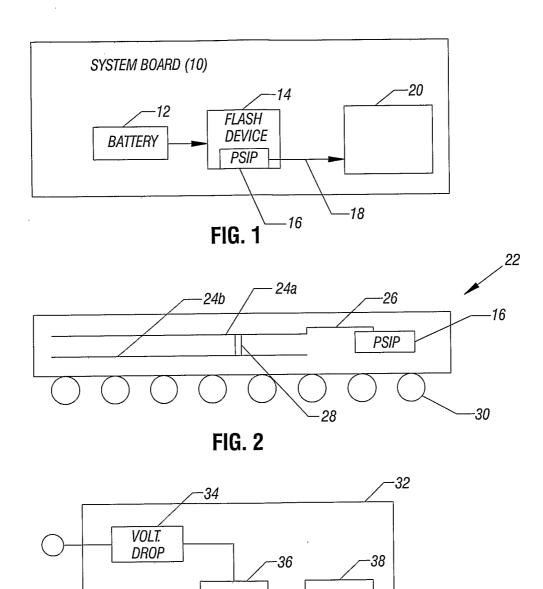

Figure 3 is a schematic depiction of still another embodiment of the present invention;

Figure 4 is an enlarged, cross-sectional view of yet another embodiment of the present invention;

Figure 5 is an enlarged, cross-sectional view of still another embodiment of the present invention;

Figure 6 is a bottom plan view of the embodiment shown in Figure 5; and

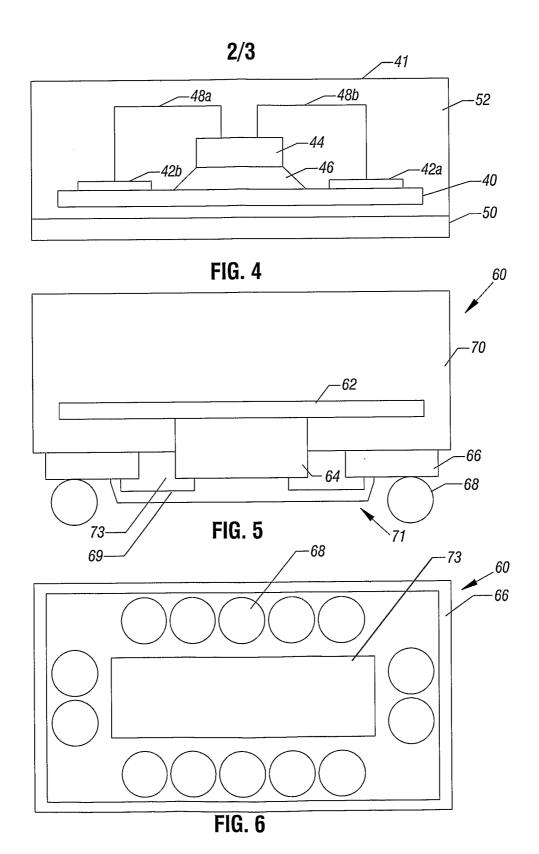

Figure 7 is an enlarged, cross-sectional view of another embodiment of the present invention.

### **Detailed Description**

Referring to Figure 1, a system board 10 may mount a battery 12 coupled to an integrated circuit device 14 that may be a flash memory, for example. The device 14 may include a power supply in package (PSIP) 16 in one embodiment of the present invention.

5

10

15

20

25

30

PCT/US03/09017

In effect, the power supply is integrated right into the same integrated circuit package that forms the device 14. This may result in considerable cost and/or size reduction of the resulting board 10.

However, other integrated circuits on the same board, such as integrated circuit 20, may then need a power supply. The integrated circuit 20 could be supplied by a separate integrated circuit power supply. However, the use of separate power supplies partially defeats the purpose of integrating the power supply into the device 14.

Many types of devices on a system board 10 of processor-based systems may not be activated at the same time. For example, different types of memory sharing the same data bus may never be activated at the same time. As one example, a flash memory device is generally not activated at the same time a static random access memory (SRAM) is accessed. Thus, whenever the device 14 is not being utilized, its PSIP 16 may be electrically coupled by a link 18 to an integrated circuit 20. For example, the link 18 may be a metal line on a printed circuit board in an embodiment where the board 10 is a printed circuit board. Thus, when the device 14 is in operation, it receives power from the PSIP 16. When the device 14 is not in operation, the power from the PSIP 16 may be supplied to another, active integrated circuit, such as the integrated circuit 20.

As a result, the size of the system board 10 may be decreased because it is not necessary to provide additional power supplies for each component. Therefore, the cost of the system board 10 may also be reduced. The cost of integrated circuit 20 may also be reduced since it may not need its own PSIP circuitry.

Referring to Figure 2, a packaged integrated circuit 22 may include a pair of spaced dice 24a and 24b, one positioned above the other, in one embodiment of the present invention. The die 24a may be coupled to a PSIP 16 via a link 26. The die 24b may be coupled to the die 24a to receive power from the PSIP 16. As long as the dice 24a and 24b are not operated at the same time, as described previously, a single in package power supply 16 may be utilized to supply both dice 24a and 24b, for example, using an electrical coupling 28 to supply power to the die 24b through the die 24a.

In one embodiment, the packaged integrated circuit 22 may include a plurality of solder balls 30 to make external contacts. However, other package architectures may be utilized as well.

Referring to Figure 3, an electronic system 32 may include a plurality of integrated circuits including the integrated circuit (IC) 38. If the regulator 36 and integrated circuit

38 combination uses a lower supply voltage than other components of the system 32, it is difficult to test all the components in the system 32 using a single power supply.

However, a single power supply may be utilized and a voltage dropping circuit element 34 may be connected to that power supply. Then the integrated circuit 38 and regulator 36 combination may receive a lower voltage even though the system 32 only generates a single test voltage. In particular, the input supply voltage supplied to the system 32 may be dropped by the voltage dropping circuit element 34 and then supplied to a voltage regulator 36. The lower voltage regulator 36 in turn provides the regulated voltage to the integrated circuit 38.

5

10

15

20

25

30

The voltage dropping circuit element 34 may simply be one or more transistors or diodes in some embodiments. Each of the transistors or diodes may drop the supply voltage by .7 volts, or any other threshold voltage, or multiples thereof.

Referring to Figure 4, an integrated circuit package 41 may include a substrate 50 in one embodiment. An encapsulant 52 may encapsulate an integrated circuit die 40. The die 40 may include its own discrete component 44 for purposes of supplying a supply voltage from within the package 41. For example, the discrete component 44 may be an integrated inductor or capacitor.

The discrete component 44 may be secured by a suitable adhesive 46, in one embodiment, to the integrated circuit die 40. The discrete component 44 may be electrically coupled to bond pads 42a and 42b on the integrated circuit die 40 through wire bonds 48a and 48b. The use of wire bonds facilitates the attachment of the discrete component 44 electrically to the integrated circuit die 40. Thus, an integrated circuit package 41 may include its own power supply, with discrete components, all packaged together.

A wire bond from the discrete component 44 may also be attached to the substrate in another embodiment. The discrete component 44 may also be adhesively attached to the substrate 50 and may be wire bonded to the substrate 50 in another embodiment.

Turning next to Figures 5 and 6, an integrated circuit package 60 may include a die 62 within an encapsulant 70 in one embodiment of the present invention. A discrete component 64 may be secured to the underside of the die 62. Again, the discrete component 64 may be an integrated capacitor or inductor, or other component to enable an in package power supply. A substrate 66 is formed on the lower surface of the

encapsulant 70. However, the substrate 66 has an open central portion 71 that allows for the passage of the discrete component 64.

-4-

As a result, the package 60 may have a lower profile because there is no interference between the substrate 66 and the discrete component 64, particularly because of the open central portion 71 of the substrate 66. The substrate 66 may provide electrical connections to the exterior environment, for example, through solder balls 68, in one embodiment. The substrate 66 may also provide wire bond connections 69 to the component 64 that may thereafter be encapsulated with encapsulant 73.

5

10

15

20

Thus, as shown in Figure 6, the discrete component 64, incorporated to provide an in package power supply, may protrude through the open central portion 71 in the substrate 66 and may be suspended, without interfering with any underlying structures, through the vertical gap created by the combination of the substrate 66 and the solder balls 68.

Referring to Figure 7, in an alternate embodiment, the package 60a may include an encapsulant 70a. The die 62 may have a pair of contact pads 72 in one embodiment. The contact pads 74 electrically contact metallic coatings 72 on the sides of the discrete component 64. Thus, the component 64 may simply be plugged into the receptacle defined by the contact pads 74.

While the present invention has been described with respect to a limited number of embodiments, those skilled in the art will appreciate numerous modifications and variations therefrom. It is intended that the appended claims cover all such modifications and variations as fall within the true spirit and scope of this present invention.

- 5 -

What is claimed is:

1. A method comprising:

providing a packaged integrated circuit with an in package power supply;

and

5

selectively coupling the in package power supply to another component when the integrated circuit is not active.

- 2. The method of claim 1 including providing a packaged integrated circuit memory with an in package power supply.

- 3. The method of claim 2 including providing a packaged integrated circuit flash memory with an in package power supply.

- The method of claim 3 including selectively coupling the in package power supply to another integrated circuit memory.

- 5. The method of claim 4 including selectively coupling the in package power supply to another component on the same system board with said packaged integrated circuit.

- 15 6. The method of claim 1 including packaging said package integrated circuit and said another component in the same integrated circuit packaging.

- 7. The method of claim 6 including electrically coupling a pair of integrated circuit dice within the same package.

- 8. The method of claim 7 including coupling said dice through a via.

- 9. The method of claim 1 including supplying power to a component that has a lower voltage supply requirement.

- 6 -

10. The method of claim 9 including dropping the voltage applied to said component.

- 11. A system comprising:

a packaged first integrated circuit including a die and an in package power

supply; and

a second die coupled to said in package power supply.

- 12. The system of claim 11 wherein both of said dice are in the same package.

- 13. The system of claim 11 wherein each of said dice is in a separate package.

- 14. The system of claim 13 wherein said dice are coupled by a via.

- 10 15. The system of claim 11 wherein only one of said dice is supplied with power at any time.

- 16. The system of claim 11 wherein one of said dice is a memory device.

- 17. The system of claim 16 wherein at least one of said dice is a flash memory and the other die is a different form of memory.

- 15 18. The system of claim 11 wherein said first integrated circuit uses a lower voltage than the second die, said first integrated circuit including a voltage dropping circuit to supply a test voltage to said circuit die.

- 19. An integrated circuit comprising:

- a die; and

- a component for an in package power supply secured to said die, said component being wire-bonded to said die.

- 20. The circuit of claim 19 wherein said component is adhesively bonded to said die.

- 7 -

- 21. The circuit of claim 19 wherein said component is one of the group consisting of a capacitor and an inductor.

- 22. A method comprising:

packaging a die and a component for an in package power supply together;

and

wire bonding said component to said die.

- 23. The method of claim 22 including adhesively bonding said component to the die.

- 24. The method of claim 22 including stacking the component on said die.

- 25. A method comprising:

coupling an in circuit power supply component and a die in a package; and

mounting said die on a substrate having a central aperture and causing said

component to extend through said central aperture.

- 26. The method of claim 25 including providing solder balls on said substrate.

- 15 27. The method of claim 26 including encapsulating said die.

20

- 28. An integrated circuit comprising:

a die;

a component for an in package power supply secured to said die; and

a substrate having a central aperture, said component extending through

said central aperture.

- 29. The integrated circuit of claim 28 wherein said substrate is coupled to solder balls.

- 8 -

30. The integrated circuit of claim 28 including a contact on said die and said component having a metallized surface to mate with said contact on said die.

1/3

FIG. 3

REG.

IC

3/3