(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-4025

(P2010-4025A)

(43) 公開日 平成22年1月7日(2010.1.7)

(51) Int.Cl.

H01L 31/10 (2006.01)

F 1

H01L 31/10

テーマコード(参考)

G 5FO49

審査請求 未請求 請求項の数 16 O L (全 31 頁)

(21) 出願番号 特願2009-118196 (P2009-118196)

(22) 出願日 平成21年5月15日 (2009.5.15)

(31) 優先権主張番号 特願2008-132835 (P2008-132835)

(32) 優先日 平成20年5月21日 (2008.5.21)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 棚田 好文

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 宍戸 英明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 天野 聖子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】光電変換装置、及び当該光電変換装置の駆動方法、並びに当該光電変換装置を具備する電子機器

## (57) 【要約】

【課題】入射光量が小さい場合であっても、容量素子への電荷の蓄積を行い、光の強度の検出ができ、構成する定電流源またはスイッチ等の素子数を増加させることなく動作させることを課題とする。

【解決手段】光電変換素子と、光電変換素子の出力電流を增幅する增幅回路と、を含む光電変換回路と、第1のスイッチを介して第1の電位が供給され、第2のスイッチを介して増幅回路で増幅された電流に応じた充電または放電がなされる容量素子と、容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、を有する。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

光電変換素子と、前記光電変換素子の出力電流を増幅する增幅回路と、を含む光電変換回路と、

第1のスイッチを介して第1の電位が供給され、第2のスイッチを介して前記増幅回路で増幅された電流に応じた充電または放電がなされる容量素子と、

前記容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、

を有することを特徴とする光電変換装置。

**【請求項 2】**

光電変換素子と、前記光電変換素子の出力電流が流れる第1のnチャネル型トランジスタと、前記出力電流が増幅された電流が流れる第2のnチャネル型トランジスタと、を含む回路と、を有する光電変換回路と、

第1のスイッチを介して第1の電位が供給されることにより充電され、第2のスイッチを介して前記第2のnチャネル型トランジスタの第1端子と電気的に接続されることで放電される容量素子と、

前記容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、

を有することを特徴とする光電変換装置。

**【請求項 3】**

請求項1または請求項2において、前記コンパレータは、前記容量素子の一方の電極の電位と第2の電位を比較した結果を出力信号として出力することを特徴とする光電変換装置

。

**【請求項 4】**

請求項3において、

前記光電変換装置は、

クロック信号を生成し、出力するクロック生成回路と、

前記クロック信号によりカウント値をカウントアップし、前記出力信号に基づいて前記カウント値を出力するカウンター回路と、

前記カウント値を保持するラッチ回路と、

を有することを特徴とする光電変換装置。

**【請求項 5】**

請求項2乃至請求項4のいずれか一において、前記光電変換回路は前記第2のnチャネル型トランジスタを複数有し、前記複数の第2のnチャネル型トランジスタにおける第1端子及び第2端子は、互いに電気的に接続されていることを特徴とする光電変換装置。

**【請求項 6】**

請求項2乃至請求項5のいずれか一において、前記第1のnチャネル型トランジスタ、前記第2のnチャネル型トランジスタ、前記第1のスイッチ及び前記第2のスイッチは、薄膜トランジスタで構成されていることを特徴とする光電変換装置。

**【請求項 7】**

光電変換素子と、前記光電変換素子の出力電流を流すための第1のpチャネル型トランジスタと、前記出力電流が増幅された電流を流すための第2のpチャネル型トランジスタと、を含むカレントミラー回路と、を有する光電変換回路と、

第1のスイッチを介して第1の電位が供給されることにより放電され、第2のスイッチを介して前記第2のpチャネル型トランジスタの第1端子と電気的に接続されることで充電される容量素子と、

前記容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、

を有することを特徴とする光電変換装置。

**【請求項 8】**

請求項7において、前記コンパレータは、前記容量素子の一方の電極の電位と前記第2の電位を比較した結果を出力信号として出力することを特徴とする光電変換装置。

**【請求項 9】**

10

20

30

40

50

請求項 8 において、

前記光電変換装置は、

クロック信号を生成し出力するクロック生成回路と、

前記クロック信号によりカウント値をカウントアップし、前記出力信号に基づいて前記カウント値を出力するカウンタ回路と、

前記カウント値を保持するラッチ回路と、を有することを特徴とする光電変換装置。

**【請求項 10】**

請求項 7 乃至請求項 9 のいずれか一において、前記光電変換回路は前記第 2 の p チャネル型トランジスタを複数有し、前記複数の第 2 の p チャネル型トランジスタにおける第 1 端子及び第 2 端子は、互いに電気的に接続されて設けられることを特徴とする光電変換装置

10

**【請求項 11】**

請求項 7 乃至請求項 10 のいずれか一において、前記第 1 の p チャネル型トランジスタ、前記第 2 の p チャネル型トランジスタ、並びに前記第 1 のスイッチ及び前記第 2 のスイッチは、薄膜トランジスタであることを特徴とする光電変換装置。

**【請求項 12】**

請求項 1 乃至請求項 11 のいずれか一において、

前記光電変換装置は、透光性基板上に設けられていることを特徴とする光電変換装置。

**【請求項 13】**

請求項 1 乃至請求項 12 に記載の光電変換装置を具備することを特徴とする電子機器。

20

**【請求項 14】**

第 1 のスイッチと、

第 2 のスイッチと、

容量素子と、

光電変換素子並びに前記光電変換素子の出力電流を流すための第 1 の n チャネル型トランジスタ及び前記出力電流が増幅された電流を流すための第 2 の n チャネル型トランジスタを含むカレントミラー回路を有する光電変換回路と、

前記容量素子の一方の電極と第 2 の電位を比較するためのコンパレータと、を有し、

前記第 1 のスイッチを導通状態、前記第 2 のスイッチを非導通状態とすることにより、前記容量素子を第 1 の電位により充電させ、

前記第 1 のスイッチを非導通状態、前記第 2 のスイッチを導通状態とし、前記容量素子を前記第 1 の n チャネル型トランジスタを流れる電流に応じて放電させ、

前記コンパレータより前記容量素子の一方の電極の電位と前記第 2 の電位を比較した結果を出力信号として出力することを特徴とする光電変換装置の駆動方法。

30

**【請求項 15】**

第 1 のスイッチと、

第 2 のスイッチと、

容量素子と、

光電変換素子並びに前記光電変換素子の出力電流を流すための第 1 の p チャネル型トランジスタ及び前記出力電流が増幅された電流を流すための第 2 の p チャネル型トランジスタを含むカレントミラー回路を有する光電変換回路と、

40

前記容量素子の一方の電極と第 2 の電位を比較するためのコンパレータと、を有し、

前記第 1 のスイッチを導通状態、前記第 2 のスイッチを非導通状態とすることにより、前記容量素子を第 1 の電位により放電させ、

前記第 1 のスイッチを非導通状態、前記第 2 のスイッチを導通状態とし、前記容量素子を前記第 1 の n チャネル型トランジスタを流れる電流に応じて充電させ、

前記コンパレータより前記容量素子の一方の電極の電位と前記第 2 の電位を比較した結果を出力信号として出力することを特徴とする光電変換装置の駆動方法。

**【請求項 16】**

請求項 14 または請求項 15 において、

50

前記光電変換装置は、ラッチ回路と、カウンター回路と、及びクロック生成回路と、を有し、

前記第1のスイッチを非導通状態、前記第2のスイッチを導通状態となつたと同時に、前記クロック生成回路はクロック信号を出力し、

前記カウンター回路は、前記クロック信号に応じてカウント値をカウントアップし、

前記ラッチ回路は、前記出力信号に基づき、前記カウント値を保持することを特徴とする光電変換装置の駆動方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、光電変換装置及びその駆動方法に関する。特に、出力される信号を、デジタル信号で出力する光電変換装置及びその駆動方法に関する。また、当該光電変換装置を具備する電子機器に関する。

10

**【背景技術】**

**【0002】**

電磁波を検知するための用途に用いられる光電変換装置は数多く知られており、例えば紫外線領域から赤外線領域にかけて感度を有するものは総括して光センサと呼ばれている。その中でも波長400nm～700nmの可視光線領域に感度を持つものは特に可視光センサと呼ばれ、人間の生活環境に応じて照度調整や、オンまたはオフの制御などが必要な機器類に数多く用いられている。

20

**【0003】**

表示装置では、表示装置の周囲の明るさを検出し、その表示輝度を調整することが行われているものもある。光センサにより、周囲の明るさを検出して適度な表示輝度を得ることによって、視認性を向上させたり、表示装置の無駄な電力を減らすことができるからである。例えば、輝度調整用の光センサを具備する表示装置としては、携帯電話、表示部付きコンピュータが挙げられる。また表示装置周囲の明るさだけではなく、表示装置、特に液晶表示装置のバックライトの輝度を光センサにより検出し、表示画面の輝度を調節することも行われている。

**【0004】**

光電変換装置である光センサは、光のセンシング部分にフォトダイオードなどの光電変換素子を用い、光電変換素子に流れる電流量に基づいて光の強度（照度ともいう）を検出することができる。特許文献1には電荷蓄積型の光センサについて、入射光量に応じてフォトダイオードから流れる電流によりコンデンサ（容量素子）に蓄積された電荷を定電流回路（定電流源）により放電することで変化する電位をコンパレータで検出し、コンパレータで検出した電位の変化に要する時間をカウンター回路及びラッチ回路によってデジタル信号として出力する構成について記載している。

30

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献1】特開平6-313840号公報**

40

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

特許文献1の光電変換装置では、入射光量に応じてフォトダイオードより流れる電流が小さい場合に、容量素子に入射光量の検出が可能な程度の電荷が蓄積されないため、入射光量が小さい場合での光の強度の検出が難しくなるといった課題がある。

**【0007】**

また特許文献1の光電変換装置では、入射光量に応じてフォトダイオードより流れる電流により容量素子に蓄積される電荷を放電するための定電流回路を設けることが必要となり、光電変換装置を駆動するための各スイッチのオン（導通、導通状態ともいう）またはオ

50

フ（非導通、非導通状態ともいう）の制御が煩雑になるといった課題がある。

【0008】

本発明の一態様は、入射光量が小さい場合であっても、容量素子への電荷の蓄積を行い、光の強度の検出が可能なデジタル信号出力型の光電変換装置を提供することを課題とする。また本発明の一態様は、構成する定電流源またはスイッチ等の素子数を増加させることなく動作することが可能なデジタル信号出力型の光電変換装置を提供することを課題とする。

【課題を解決するための手段】

【0009】

上述の課題を解決するため、容量素子に予め入射光量に依らず一定の電荷を蓄積（充電）した上で、入射光量に応じた容量素子の放電を行うことを特徴とする。本発明によれば、容量素子の放電は入射光量によって放電する量が異なるため、コンパレータで検出した放電による電位の変化に要する時間をカウンター回路でカウントし、ラッチ回路で保持した値をデジタル信号として出力できる。

10

【0010】

本発明の一態様は、光電変換素子と、光電変換素子の出力電流を增幅する增幅回路と、を含む光電変換回路と、第1のスイッチを介して第1の電位が供給され、第2のスイッチを介して増幅回路で増幅された電流に応じた充電または放電がなされる容量素子と、容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、を有する光電変換装置である。

20

【0011】

また本発明の一態様は、光電変換素子と、光電変換素子の出力電流が流れる第1のnチャネル型トランジスタと、出力電流が増幅された電流が流れる第2のnチャネル型トランジスタと、を含む回路と、を有する光電変換回路と、第1のスイッチを介して第1の電位が供給されることにより充電され、第2のスイッチを介して第2のnチャネル型トランジスタの第1端子と電気的に接続されることで放電される容量素子と、容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、を有する光電変換装置である。

【0012】

また本発明の光電変換装置の一態様において、コンパレータは、容量素子の一方の電極の電位と第2の電位を比較した結果を出力信号として出力するものであってもよい。

30

【0013】

また本発明の光電変換装置の一態様において、光電変換装置は、クロック信号を生成し、出力するクロック生成回路と、クロック信号によりカウント値をカウントアップし、出力信号に基づいてカウント値を出力するカウンター回路と、カウント値を保持するラッチ回路と、を有するものであってもよい。

【0014】

また本発明の光電変換装置の一態様において、光電変換回路は第2のnチャネル型トランジスタを複数有し、複数の第2のnチャネル型トランジスタにおける第1端子及び第2端子は、互いに電気的に接続されて設けられるものであってもよい。

【0015】

また本発明の光電変換装置の一態様において、第1のnチャネル型トランジスタ、第2のnチャネル型トランジスタ、並びに第1のスイッチ及び第2のスイッチは、薄膜トランジスタで構成されているものであってもよい。

40

【0016】

また本発明の一態様は、光電変換素子と、光電変換素子の出力電流を流すための第1のpチャネル型トランジスタと、出力電流が増幅された電流を流すための第2のpチャネル型トランジスタと、を含むカレントミラー回路と、を有する光電変換回路と、第1のスイッチを介して第1の電位が供給されることにより放電され、第2のスイッチを介して第2のpチャネル型トランジスタの第1端子と電気的に接続されることで充電される容量素子と、容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、を有する

50

光電変換装置である。

【0017】

また本発明の光電変換装置の一態様において、コンパレータは、容量素子の一方の電極の電位と第2の電位を比較した結果を出力信号として出力するものであってもよい。

【0018】

また本発明の光電変換装置の一態様において、光電変換装置は、クロック信号を生成し出力するクロック生成回路と、クロック信号によりカウント値をカウントアップし、出力信号に基づいてカウント値を出力するカウンタ回路と、カウント値を保持するラッチ回路と、を有するものであってもよい。

【0019】

また本発明の光電変換装置の一態様において、光電変換回路は第2のpチャネル型トランジスタを複数有し、複数の第2のpチャネル型トランジスタにおける第1端子及び第2端子は、互いに電気的に接続されて設けられるものであってもよい。

【0020】

また本発明の光電変換装置の一態様において、第1のpチャネル型トランジスタ、第2のpチャネル型トランジスタ、並びに第1のスイッチ及び第2のスイッチは、薄膜トランジスタであってもよい。

【0021】

また本発明の光電変換装置の一態様において、光電変換装置は、透光性基板上に設けられるものであってもよい。

【0022】

また本発明の一態様は、第1のスイッチと、第2のスイッチと、容量素子と、光電変換素子並びに光電変換素子の出力電流を流すための第1のnチャネル型トランジスタ及び出力電流が増幅された電流を流すための第2のnチャネル型トランジスタを含むカレントミラー回路を有する光電変換回路と、容量素子の一方の電極と第2の電位を比較するためのコンパレータと、を有し、第1のスイッチを導通状態、第2のスイッチを非導通状態とすることにより、容量素子を第1の電位により充電させ、第1のスイッチを非導通状態、第2のスイッチを導通状態とし、容量素子を第1のnチャネル型トランジスタを流れる電流に応じて放電させ、コンパレータより容量素子の一方の電極の電位と第2の電位を比較した結果を出力信号として出力する光電変換装置の駆動方法である。

【0023】

また本発明の一態様は、第1のスイッチと、第2のスイッチと、容量素子と、光電変換素子並びに光電変換素子の出力電流を流すための第1のpチャネル型トランジスタ及び出力電流が増幅された電流を流すための第2のpチャネル型トランジスタを含むカレントミラー回路を有する光電変換回路と、容量素子の一方の電極と第2の電位を比較するためのコンパレータと、を有し、第1のスイッチを導通状態、第2のスイッチを非導通状態とすることにより、容量素子を第1の電位により放電させ、第1のスイッチを非導通状態、第2のスイッチを導通状態とし、容量素子を第1のpチャネル型トランジスタを流れる電流に応じて充電させ、コンパレータより容量素子の一方の電極の電位と第2の電位を比較した結果を出力信号として出力する光電変換装置の駆動方法である。

【0024】

また本発明の光電変換装置の駆動方法の一態様において、光電変換装置は、ラッチ回路と、カウンタ回路と、及びクロック生成回路と、を有し、第1のスイッチを非導通状態、第2のスイッチを導通状態となったと同時に、クロック生成回路はクロック信号を出力し、カウンタ回路は、クロック信号に応じてカウント値をカウントアップし、ラッチ回路は、出力信号に基づき、カウント値を保持するものであってもよい。

【発明の効果】

【0025】

光電変換装置及び当該光電変換装置の駆動方法の一態様により、入射光量が小さい場合であっても、容量素子への電荷の蓄積を行い、光の強度の検出を可能とし、構成する定電流

10

20

30

40

50

源またはスイッチ等の素子数を増加させることなく動作させることができる。

【図面の簡単な説明】

【0026】

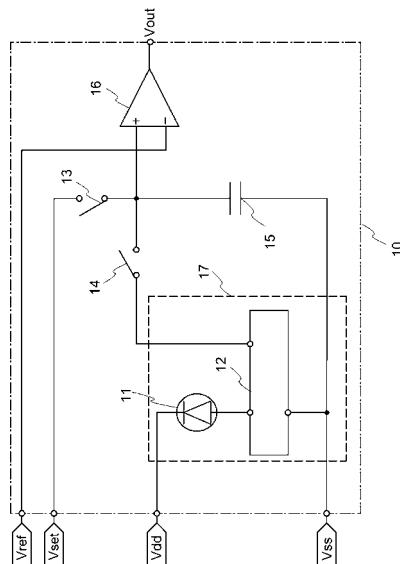

【図1】実施の形態1を説明するための回路図。

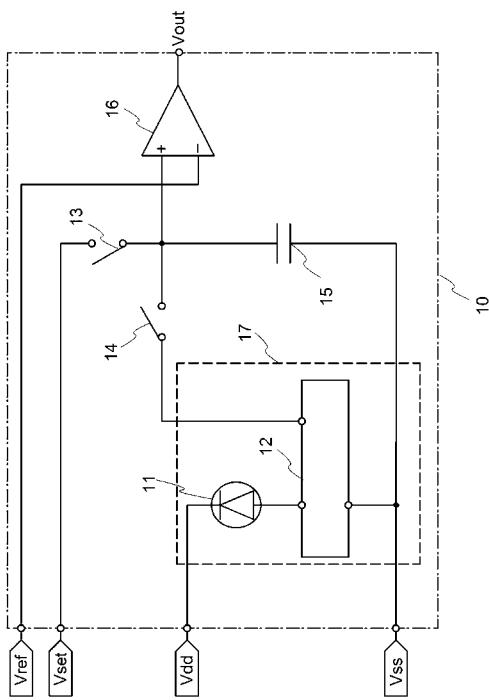

【図2】実施の形態1を説明するための回路図。

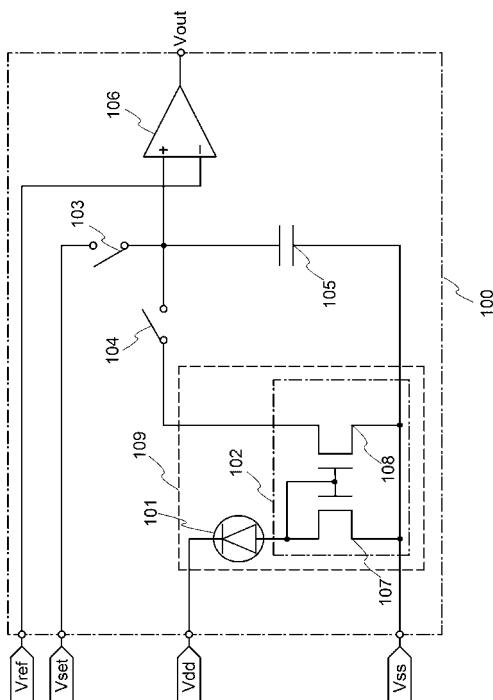

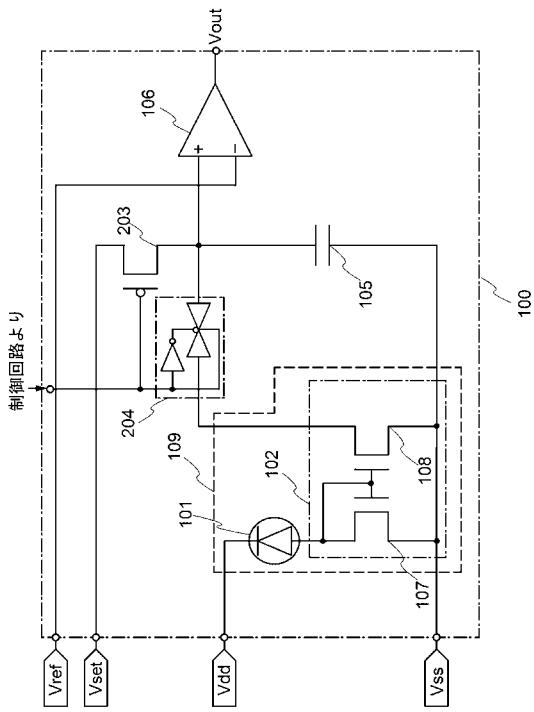

【図3】実施の形態1を説明するための回路図。

【図4】実施の形態1を説明するための回路図。

【図5】実施の形態1を説明するための回路図。

【図6】実施の形態1を説明するためのタイミングチャート図。

【図7】実施の形態1を説明するための回路図。

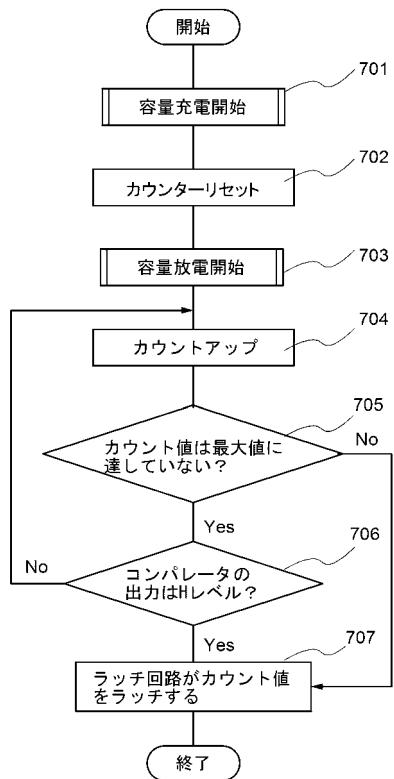

【図8】実施の形態1を説明するためのフローチャート図。

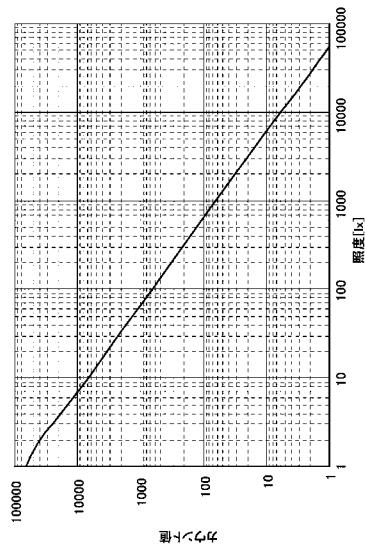

【図9】実施の形態1を説明するための図。

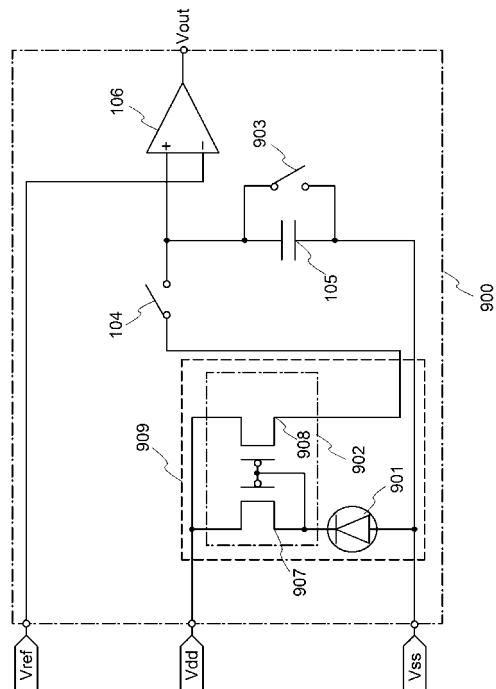

【図10】実施の形態2を説明するための回路図。

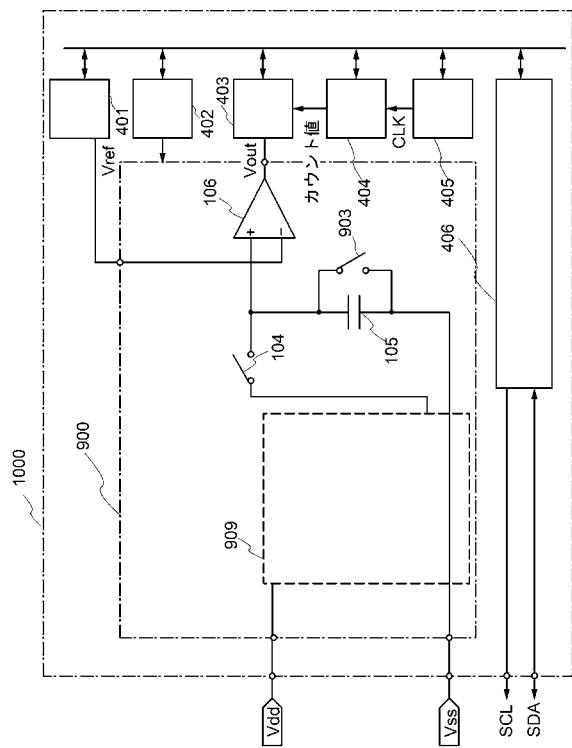

【図11】実施の形態2を説明するための回路図。

【図12】実施の形態2を説明するためのタイミングチャート図。

【図13】実施の形態2を説明するための回路図。

【図14】実施の形態2を説明するためのフローチャート図。

【図15】実施の形態3を説明するための断面図。

【図16】実施の形態3を説明するための断面図。

【図17】実施の形態4を説明するための図。

【発明を実施するための形態】

【0027】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0028】

(実施の形態1)

本実施の形態では、光電変換装置の構成及びその動作について説明する。なお本実施の形態で説明する本発明の光電変換装置は、光電変換素子により得られる入射光量に関するアナログの信号（以下、アナログ信号という）をデジタルの信号（以下、デジタル信号）に変換するための回路を含むものである。

【0029】

まず光電変換装置における回路図について説明する。図1に示す光電変換装置10は、光電変換素子11、增幅回路12、第1のスイッチ13、第2のスイッチ14、容量素子15、コンパレータ16（比較回路ともいう）を有する。光電変換素子11は、一方の端子（n型半導体側）に高電源電位（Vdd）が供給され、他方の端子（p型半導体側）が増幅回路12の入力端子に電気的に接続されている。増幅回路12は、光電変換素子11の出力電流を増幅するための回路である。増幅回路12は低電源電位（Vss）が供給されている。なお光電変換素子11及び増幅回路12を併せて、光電変換回路17ともいう。また、第1のスイッチ13の第1端子は第1の電位（充電電位、またはVsetともいう）が供給され、第2端子は容量素子15の一方の電極、第2のスイッチ14の第1端子、及びコンパレータ16の非反転入力端子に電気的に接続されている。容量素子15の他方の電極には、低電源電位が供給されている。第2のスイッチ14の第2端子は増幅回路12に電気的に接続されている。コンパレータ16の反転入力端子には第2の電位（参照電位、またはVrefともいう）が供給され、コンパレータ16の出力端子より出力信号（以下、Voutともいう）が出力される。

【0030】

10

20

30

40

50

図1に示す回路図について説明する。図1の光電変換装置10は、第1のスイッチ13を介して第1の電位が容量素子に供給されることで電荷の充電または放電を行い、一定量の電荷を容量素子15の一方の電極に保持した上で、光電変換素子11への入射光量に応じた容量素子15への電荷の充電または放電を行う。容量素子15への電荷の充電量または放電量は入射光量によって異なるため、コンパレータ16で容量素子15の一方の電極の電位と第2の電位を比較することで、コンパレータ16の出力端子より出力信号を出力し、カウンターハードウェア及びラッチ回路によって出力信号の電位の変化に要する時間を検出することによって、デジタル信号に変換することができる。

#### 【0031】

なお本明細書における增幅回路は、光電変換素子に流れる電流から増幅された電流を生成する回路のことをいう。増幅された電流は光電変換素子に流れる電流に比例している。增幅回路により増幅された電流の流れる経路に応じて、容量素子では、電荷の充電または電荷の放電が行われる。

10

#### 【0032】

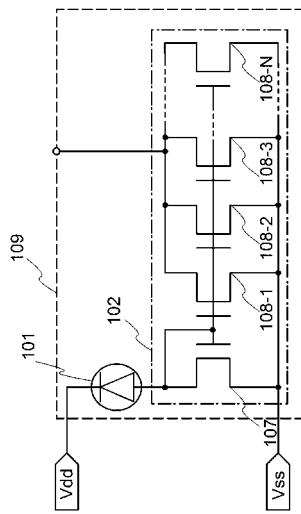

次に図2に図1で示した光電変換装置を具体化し説明する。図2に示す光電変換装置100は、光電変換素子101、増幅回路102、第1のスイッチ103、第2のスイッチ104、容量素子105、コンパレータ106を有する。光電変換素子101は、一方の端子(*n*型半導体側)に高電源電位(Vdd)が供給され、他方の端子(*p*型半導体側)が増幅回路102の入力端子に電気的に接続されている。増幅回路102は、図2に示すようにカレントミラー回路で構成されており、第1の*n*チャネル型トランジスタ107及び第2の*n*チャネル型トランジスタ108を有する。第1の*n*チャネル型トランジスタ107及び第2の*n*チャネル型トランジスタ108のゲート端子は互いに電気的に接続されており、第1の*n*チャネル型トランジスタ107の第1端子は第1の*n*チャネル型トランジスタ107及び第2の*n*チャネル型トランジスタ108のゲート端子に電気的に接続されている。第1の*n*チャネル型トランジスタ107及び第2の*n*チャネル型トランジスタ108の第2端子は低電源電位(Vss)が供給されている。なお光電変換素子101、第1の*n*チャネル型トランジスタ107及び第2の*n*チャネル型トランジスタ108を有する増幅回路102を併せて、光電変換回路109ともいう。また、第1のスイッチ103の第1端子は第1の電位が供給され、第2端子は容量素子105の一方の電極、第2のスイッチ104の第1端子、及びコンパレータ106の非反転入力端子に電気的に接続されている。容量素子105の他方の電極には、低電源電位が供給されている。第2のスイッチ104の第2端子は第2の*n*チャネル型トランジスタ108の第1端子に電気的に接続されている。コンパレータ106の反転入力端子には第2の電位が供給され、コンパレータ106の出力端子より出力信号が出力される。

20

30

30

#### 【0033】

なお本明細書にて用いる第1、第2、第3、乃至第N(Nは自然数)という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

#### 【0034】

なお本明細書において、AとBとが接続されている、とは、AとBとが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、AとBとが電気的に接続されているとは、AとBとの間に何らかの電気的作用を有する対象物が存在するとき、対象物を含むAとBとの間の部分がノードとなる場合を表すものとする。

40

#### 【0035】

具体的には、トランジスタをはじめとするスイッチング素子を介してAとBとが接続され、該スイッチング素子の導通によって、AとBとが概略同電位となる場合や、抵抗素子を介してAとBとが接続され、該抵抗素子の両端に発生する電位差が、AとBとを含む回路の動作に影響しない程度となっている場合など、回路動作を考えた場合、AとBとの間の部分をノードとして捉えて差し支えない状態である場合を表す。

#### 【0036】

50

なお本明細書において、スイッチは、一方の端子と他方の端子との導通または非導通を制御できるものであればよく、特定のものに限定されない。スイッチとしては、電気的スイッチや機械的なスイッチなどがあり、一例として薄膜トランジスタを用いて構成すればよい。

#### 【0037】

なお第1のスイッチ103及び第2のスイッチ104は、図3に示すように、pチャネル型トランジスタ203、アナログスイッチ204を用いることが好ましい。第1のスイッチ103は一方の端子が固定電位である第1の電位V<sub>set</sub>に電気的に接続されるためpチャネル型トランジスタを用いることができ、第2のスイッチ104は両端の端子の電位が共に変動するため、オンまたはオフを確実に制御するためにアナログスイッチを用いることが好ましい。また、pチャネル型トランジスタ203、アナログスイッチ204を図3に示すような電気的な接続をすることで、第1のスイッチ103及び第2のスイッチ104を交互にオンまたはオフの動作をさせることができる。その結果、第1のスイッチ103及び第2のスイッチ104を光電変換装置100の外部にある制御回路からの信号が一つで動作させることができるため、製造コストを低減することができる。なお第1のスイッチ103及び第2のスイッチ104の導通または非導通の制御については、図3に示すように一つの信号で行っても良いし、各スイッチ毎に信号を入力して制御してもよい。

10

#### 【0038】

なお、nチャネル型トランジスタまたはpチャネル型トランジスタのようなトランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことができる。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるために、いずれがソースまたはドレインであるかを限定することが困難な場合もある。そこで、本実施の形態においては、ソース及びドレインとして機能する領域のそれぞれを、第1端子、第2端子と表記するものとする。またゲートとして機能する端子については、ゲート端子と表記するものとする。

20

#### 【0039】

なお、nチャネル型トランジスタまたはpチャネル型トランジスタのようなトランジスタとして、様々な形態のトランジスタを用いることができる。例えば、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、セミアモルファスとも言う）シリコンなどに代表される非単結晶半導体膜を有する薄膜トランジスタ（TFT）などを用いることができる。TFTを用いる場合、比較的低温のプロセスで作製することができるため製造装置を大きくでき、大型基板上に製造できる。そのため、一度の製造工程で多くの取り数を得ることができ、低コストで製造することができる。さらに、比較的に低温のプロセスで作製するため、耐熱性の低い基板を用いることができる。そのため、透光性を有する基板（例えば、絶縁表面を有するガラス基板）上にトランジスタを製造でき、耐熱性が低く、透光性を有する基板上のトランジスタを光の透過を利用して装置に用いることができる。

30

#### 【0040】

なお光電変換回路109の増幅回路102における第2のnチャネル型トランジスタ108を、図4に示すように電気的に並列に複数配設する構成としてもよい。図4に示すように第2のnチャネル型トランジスタ108-1乃至108-N（Nは2以上の自然数）と複数設けることにより、光電変換素子101に光が照射されることで第1のnチャネル型トランジスタのソースとドレインの間を流れる電流を、N倍にして第2のnチャネル型トランジスタ108-1乃至108-Nの側で流すことができる。そのため、光電変換素子101に照射される入射光量が小さい場合であっても、第2のnチャネル型トランジスタ108-1乃至108-Nの側に出力信号を得るために十分な電流を流すことができる。また第2のnチャネル型トランジスタ108のチャネル幅を長くする、またはチャネル長を短くすることでも十分な電流を流すことができる。

40

#### 【0041】

なお容量素子105は、第1のスイッチ103がオンになることで第1の電位V<sub>set</sub>に

50

より充電がなされ、その後第2のスイッチ104がオンになり、光電変換回路109に流れる電流に応じて放電するものである。そのため、増幅回路102の第2のnチャネル型トランジスタの電荷の放電される際の時間を考慮して、容量素子105の静電容量は電荷を充電できる容量を備えておくことが望ましい。また、第1の電位V<sub>set</sub>としては、高電源電位V<sub>dd</sub>以下で、低電源電位V<sub>ss</sub>よりも大きい値に設定することが好ましい。なお、第1の電位V<sub>set</sub>を高電源電位V<sub>dd</sub>とする場合には、高電源電位V<sub>dd</sub>が固定電位であることが望ましい。

#### 【0042】

またコンパレータ106の反転入力端子に供給される第2の電位V<sub>ref</sub>は、第1のスイッチ103がオンになることで第1の電位V<sub>set</sub>による充電がなされ、その後増幅回路102による放電がなされた際の容量素子105の一方の電極の電位と、比較されることで出力端子より出力信号V<sub>out</sub>を出力するための電位である。第2の電位V<sub>ref</sub>としては、第1の電位V<sub>set</sub>よりも小さく、低電位電源V<sub>ss</sub>より大きい値に設定することが好ましい。出力信号V<sub>out</sub>としては、Hレベルの信号またはLレベルの信号が出力される。

10

#### 【0043】

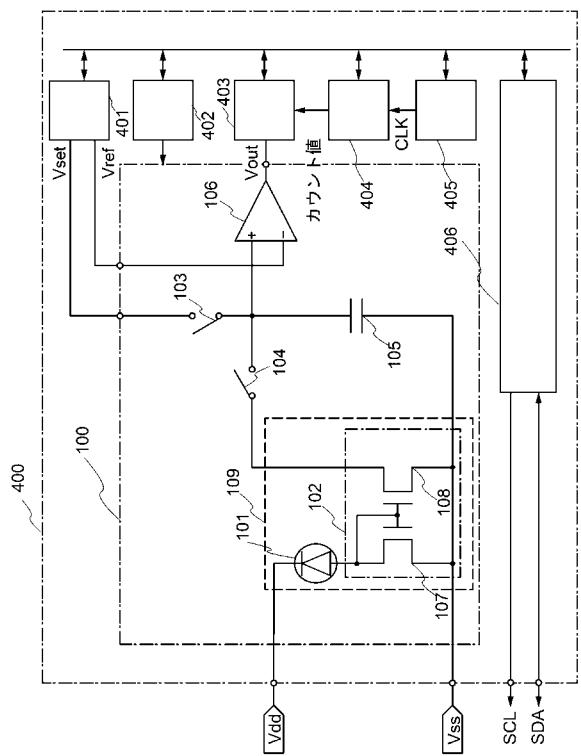

次に図2で説明した回路図に加え、アナログ信号をデジタル信号に変換するための信号を生成する構成を加えたブロック図を含む構成について図5を用いて説明する。図5に示すデジタル出力型の光電変換装置400は、図2で示した光電変換装置100に加え、定電圧回路401（レギュレータともいう）、制御回路402、ラッチ回路403、カウンターレベル回路404、クロック生成回路405、インターフェース回路406を有する。

20

#### 【0044】

定電圧回路401は、デジタル出力型の光電変換装置400に入力される高電源電位V<sub>dd</sub>及び低電源電位V<sub>ss</sub>より、第1の電位V<sub>set</sub>及び第2の電位V<sub>ref</sub>等の複数の電位を生成するための回路である。また定電圧回路401は、必要に応じて、制御回路402、ラッチ回路403、カウンターレベル回路404、クロック生成回路405、またはインターフェース回路406を駆動するための電位を供給する。

20

#### 【0045】

また制御回路402は、光電変換装置100における第1のスイッチ103及び第2のスイッチ104のオンまたはオフを切り替える回路であり、且つラッチ回路403及びカウンターレベル回路404をリセットするための信号を出力する回路である。また制御回路402はラッチ回路403、カウンターレベル回路404、クロック生成回路405、またはインターフェース回路406における各信号の同期をとるための回路である。

30

#### 【0046】

またラッチ回路403は、光電変換装置100より出力される出力信号V<sub>out</sub>に応じて、カウンターレベル回路404より出力されるカウント値を保持するための回路である。ラッチ回路403で保持されたカウント値はインターフェース回路406にデジタル信号として出力される。

#### 【0047】

またカウンターレベル回路404は、クロック生成回路405より出力されるクロック信号（CLK）に基づいてカウントするための回路である。クロック信号によりカウンターレベル回路404で得られるカウント値はラッチ回路403に出力される。なお出力するカウント値はデジタル信号として出力するため、ビット数に応じたバス数にて、ラッチ回路に出力される。

40

#### 【0048】

またクロック生成回路405は、カウンターレベル回路404でカウントするためのクロック信号CLKをカウンターレベル回路404に出力するための回路である。クロック生成回路としては、一例としては、固体振動子発振回路、またはCR発振回路等を用いて構成すればよい。

#### 【0049】

50

またインターフェース回路 406 は、一例として、デジタルシリアルインターフェースの一つである I<sub>2</sub>C ( I n t e r I n t e g r a t e d c i r c u i t ) インターフェースを用いればよい。I<sub>2</sub>C インターフェースは、他の装置とのデータ通信のためのシリアルデータライン ( S D A ) と、他の装置との間のデータ通信を制御及び同期化するためのシリアルクロックライン ( S C L ) と、からなる I<sub>2</sub>C バスによって外部装置と接続されている。I<sub>2</sub>C インターフェースに接続された回路は、固有のアドレスによって応答または非応答が選択され、回路間でデータ通信を行うことができる。なお I<sub>2</sub>C バス以外に、ユニバーサルシリアルバス ( U n i v e r s a l S e r i a l B u s ) 、シリアル周辺インターフェース ( S e r i a l P e r i p h e r a l I n t e r f a c e ) 等のバス規格を用いることが可能である。

10

#### 【 0 0 5 0 】

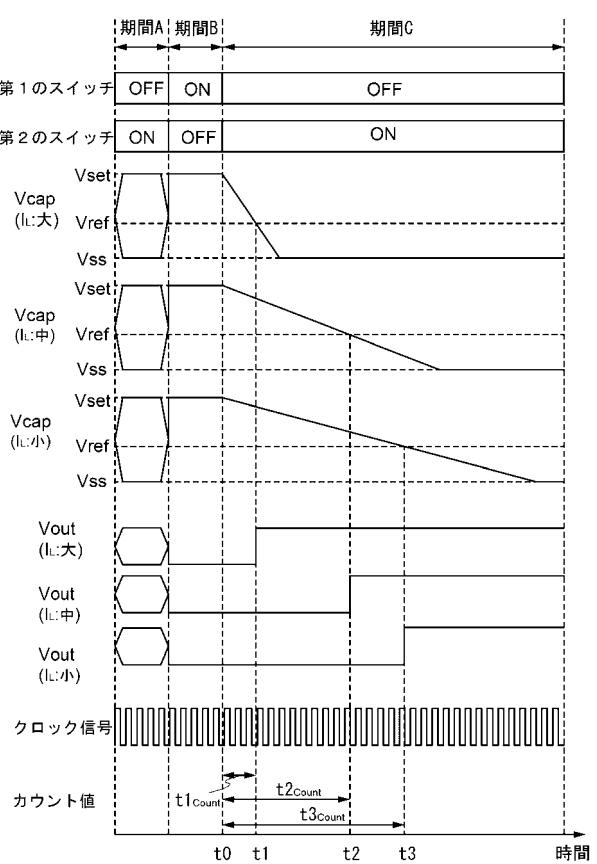

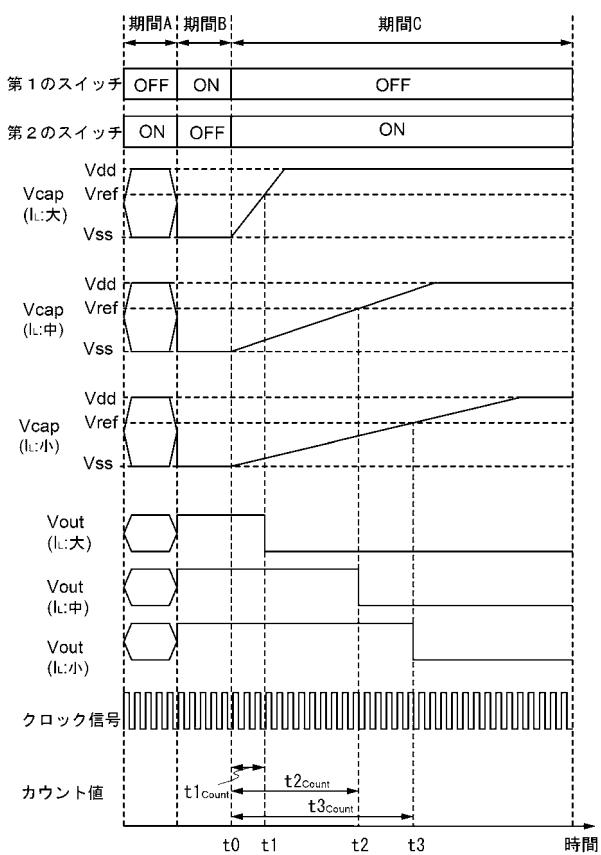

次に図 5 で示したデジタル出力型の光電変換装置 400 の具体的な動作について、図 6、図 7 ( A ) 、及び図 7 ( B ) を用いて説明する。図 6 には、第 1 のスイッチ 103 及び第 2 のスイッチ 104 のオンまたはオフを切り替えた際の容量素子 105 の一方の電極の電位 V<sub>c a p</sub> 、及びコンパレータ 106 の出力信号の電位 V<sub>o u t</sub> 、クロック信号、及びカウント値についてのタイミングチャートについて示したものである。なお、V<sub>c a p</sub> 及び V<sub>o u t</sub> については、光電変換素子 101 に光が照射された際の光電流 I<sub>L</sub> の大きさを大、中、小の 3 段階に分けて説明する。

20

#### 【 0 0 5 1 】

まず図 6 に示した、第 1 のスイッチ 103 がオフ、第 2 のスイッチ 104 がオンの状態である期間 A において説明する。期間 A において容量素子 105 の一方の電極の電位 V<sub>c a p</sub> は、光電流 I<sub>L</sub> の大きさに応じて変動し続け、電位の定まらない状態となる。また期間 A において、コンパレータ 106 の出力信号の電位 V<sub>o u t</sub> は V<sub>c a p</sub> の電位に応じて変動し続け、電位の定まらない状態となる。なおクロック信号は、期間 A でクロック生成回路 405 よりカウンター回路 404 へ出力される。そのためカウンター回路 404 では、カウント値がカウントアップされるものの、カウント値は期間 A でラッチ回路 403 に保持されない。

20

#### 【 0 0 5 2 】

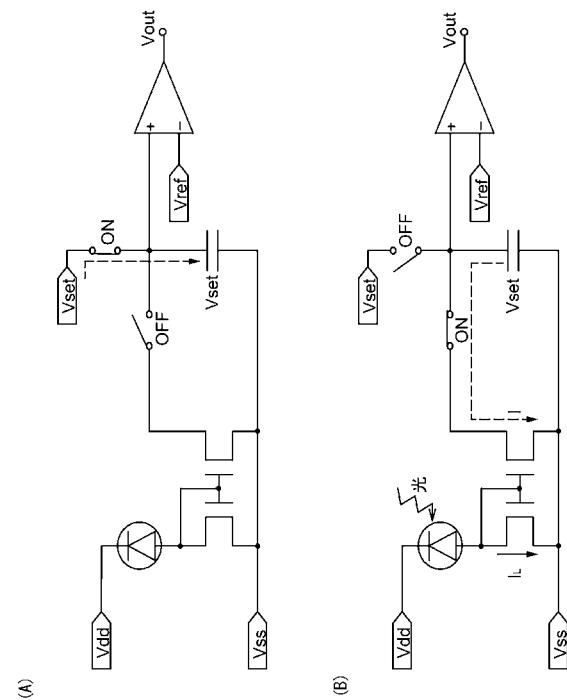

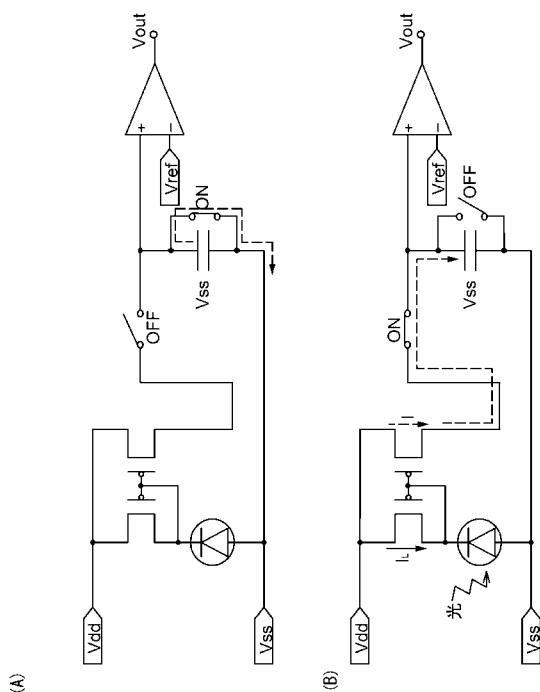

次に第 1 のスイッチ 103 がオンの状態、第 2 のスイッチ 104 がオフの状態にある期間 B について説明する。期間 B において、容量素子 105 の一方の電極の電位 V<sub>c a p</sub> は、光電流 I<sub>L</sub> の大きさに関わらず第 1 の電位 V<sub>s e t</sub> となるものである。また期間 B において、コンパレータ 106 の出力信号の電位 V<sub>o u t</sub> は光電流 I<sub>L</sub> の大きさに関わらず、第 1 の電位 V<sub>s e t</sub> が第 2 の電位 V<sub>r e f</sub> を上回るため、L レベルの信号が出力されるものである。

30

#### 【 0 0 5 3 】

期間 B における各スイッチのオンまたはオフ、電荷の流れについて、図 7 ( A ) に模式的に示す。容量素子 105 は、第 1 のスイッチ 103 がオンになるとことによって、第 1 の電位 V<sub>s e t</sub> が供給される。また、第 2 のスイッチ 104 がオフになっているため、容量素子 105 から第 2 の n チャネル型トランジスタ 108 への電荷の移動はない。

30

#### 【 0 0 5 4 】

次に第 1 のスイッチ 103 がオフの状態、第 2 のスイッチ 104 がオンの状態にある期間 C について説明する。まず期間 C において、光電変換素子 101 に光が照射され光電流 I<sub>L</sub> が大きい場合 ( 図 6 中 I<sub>L</sub> : 大 ) 、容量素子 105 の一方の電極の電位 V<sub>c a p</sub> は、光電流 I<sub>L</sub> に応じて第 2 の n チャネル型トランジスタ 108 に流れる電流 I が大きくなり、下降する。そのため、時間 t<sub>0</sub> ( 時間 t<sub>0</sub> < 時間 t<sub>1</sub> < 時間 t<sub>2</sub> < 時間 t<sub>3</sub> ) で容量素子 105 の電位 V<sub>c a p</sub> が V<sub>s e t</sub> であったのが時間 t<sub>1</sub> で電位 V<sub>r e f</sub> となり、その後容量素子 105 からの放電が完了することで電位 V<sub>s s</sub> となる。このとき、コンパレータ 106 の出力信号の電位 V<sub>o u t</sub> は、容量素子の電位 V<sub>c a p</sub> が第 1 の電位 V<sub>s e t</sub> から第 2 の電位 V<sub>r e f</sub> となつた際に、H レベルの信号を出力する。そして、当該信号でラッチ回路 403 は、入力されるカウント値を保持する。なお期間 C になる時間 t<sub>0</sub> と同時に

40

50

、カウンター回路 404 およびラッチ回路 403 がリセットされ、カウンター回路 404 でクロック信号に基づくカウントアップがなされる。そして、時間  $t_1$  にコンパレータ 106 の出力信号の電位  $V_{out}$  がラッチ回路 403 に入力されることで時間  $t_0$  から時間  $t_1$  の間の期間のクロック信号に基づいたカウント値  $t_{1\_count}$  が得られることとなる。

#### 【0055】

また第 1 のスイッチ 103 がオフの状態、第 2 のスイッチ 104 がオンの状態にある期間 C であって、光電変換素子 101 に光が照射され光電流  $I_L$  が中程度の場合（図 6 中  $I_L$  : 中）、容量素子 105 の一方の電極の電位  $V_{cap}$  は、光電流  $I_L$  が大きい場合に比べ第 2 の n チャネル型トランジスタ 108 に流れる電流  $I$  が小さいため減少の割合は小さいものの、下降していく。そのため、時間  $t_0$  で容量素子 105 の電位  $V_{cap}$  が  $V_{set}$  であったのが時間  $t_2$  で電位  $V_{ref}$  となり、その後容量素子 105 からの放電が完了することで電位  $V_{ss}$  となる。このとき、コンパレータ 106 の出力信号の電位  $V_{out}$  は、容量素子の電位  $V_{cap}$  が第 1 の電位  $V_{set}$  から第 2 の電位  $V_{ref}$  となった際に、H レベルの信号を出力する。そして、当該信号でラッチ回路 403 は、入力されるカウント値を保持する。なお期間 C になる時間  $t_0$  と同時に、カウンター回路 404 およびラッチ回路 403 がリセットされ、カウンター回路 404 でクロック信号に基づくカウントアップがなされる。そして、時間  $t_2$  にコンパレータ 106 の出力信号の電位  $V_{out}$  がラッチ回路 403 に入力されることで時間  $t_0$  から時間  $t_2$  の間の期間のクロック信号に基づいたカウント値  $t_{2\_count}$  が得られることとなる。

10

20

30

#### 【0056】

また第 1 のスイッチ 103 がオフの状態、第 2 のスイッチ 104 がオンの状態にある期間 C であって、光電変換素子 101 に光が照射され光電流  $I_L$  が小さい場合（図 6 中  $I_L$  : 小）、容量素子 105 の一方の電極の電位  $V_{cap}$  は、光電流  $I_L$  が小さいため第 2 の n チャネル型トランジスタ 108 に流れる電流  $I$  も小さく減少の割合も小さいものの、下降していく。そのため、時間  $t_0$  で容量素子 105 の電位  $V_{cap}$  が  $V_{set}$  であったのが時間  $t_3$  で電位  $V_{ref}$  となり、その後容量素子 105 からの放電が完了することで電位  $V_{ss}$  となる。このとき、コンパレータ 106 の出力信号の電位  $V_{out}$  は、容量素子の電位  $V_{cap}$  が第 1 の電位  $V_{set}$  から第 2 の電位  $V_{ref}$  となった際に、H レベルの信号を出力する。そして、当該信号でラッチ回路 403 は、入力されるカウント値を保持する。なお期間 C になる時間  $t_0$  と同時に、カウンター回路 404 およびラッチ回路 403 がリセットされ、カウンター回路 404 でクロック信号に基づくカウントアップがなされる。そして、時間  $t_3$  にコンパレータ 106 の出力信号の電位  $V_{out}$  がラッチ回路 403 に入力されることで時間  $t_0$  から時間  $t_3$  の間の期間のクロック信号に基づいたカウント値  $t_{3\_count}$  が得られることとなる。

40

#### 【0057】

期間 C における各スイッチのオンまたはオフ、電荷の流れについて、図 7 (B) に模式的に示す。容量素子 105 は、第 1 のスイッチ 103 がオフになることによって、新たに第 1 の電位  $V_{set}$  が供給されることはない。一方、第 2 のスイッチ 104 がオンになっているため、容量素子 105 から第 2 の n チャネル型トランジスタ 108 へ電流  $I$  が流れ、容量素子 105 の放電が行われる。なお、第 2 の n チャネル型トランジスタ 108 を流れる電流  $I$  は、增幅回路 102 がカレントミラー回路を形成していることにより、光電流  $I_L$  に比例した大きさとなる。

50

#### 【0058】

なお、第 1 のスイッチ 103 がオフの状態、第 2 のスイッチ 104 がオンの状態にある期間 C であって、光電変換素子 101 に光が照射されず光電流  $I_L$  が検出できない場合、容量素子 105 の一方の電極の電位  $V_{cap}$  は、第 2 の n チャネル型トランジスタ 108 に流れる電流  $I$  が生じないため、ほとんど減少しない。そのため、時間  $t_0$  で容量素子 105 の電位  $V_{cap}$  が  $V_{set}$  であるものの、時間の経過に伴う電位  $V_{ref}$  への変化がない。このとき、コンパレータ 106 の出力信号の電位  $V_{out}$  は、容量素子の電位  $V_{ca}$

50

$p$  が第 1 の電位  $V_{set}$  から第 2 の電位  $V_{ref}$  に変化しないため、L レベルの信号が出力し続けるものである。またクロック信号は、期間 C になった時間  $t_0$  より、カウンター回路 404 への出力がなされる。そのため上述のように光電流  $I_L$  に応じたカウント値を得ることが出来ずカウント値はカウンター回路の最大値に達してしまう。この場合、カウント値の最大値をラッチ回路に出力することが好ましい。

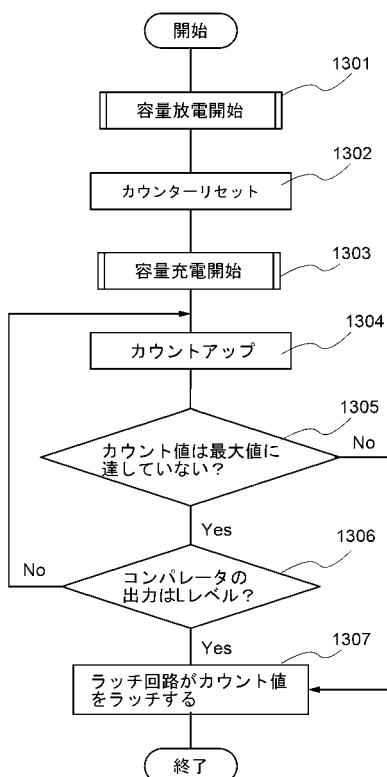

#### 【0059】

図 6、図 7 (A)、図 7 (B) で説明したデジタル出力型の光電変換装置 400 の具体的な動作について、図 8 に示すフローチャートを用いて説明する。

#### 【0060】

まず光電変換装置 400 は容量素子 105 への電荷の充電（リセット）を開始する（ステップ 701）。容量素子 105 への電荷の充電は、上述したように第 1 のスイッチ 103 をオン、第 2 のスイッチ 104 をオフにすることにより、第 1 の電位  $V_{set}$  が供給された配線と容量素子 105 とを電気的な接続をさせることによって行われる。またステップ 701 では容量素子 105 の充電と共に、クロック生成回路 405 からのクロック信号の出力が行われる。10

#### 【0061】

次に光電変換装置 400 は、容量素子 105 への電荷の充電の後、カウンター回路 404 のカウント値のリセットを行う（ステップ 702）。また、ステップ 702 ではカウンター回路 404 のカウント値のリセットと共に、ラッチ回路 403 に保持されたカウント値の初期化を行う。20

#### 【0062】

次に光電変換装置 400 は、光電変換回路 109 の第 2 の n チャネル型トランジスタ 108 により、容量素子 105 に充電された電荷の放電をおこなう（ステップ 703）。容量素子 105 からの電荷の放電は、上述したように第 1 のスイッチ 103 をオフ、第 2 のスイッチ 104 をオンにすることにより、容量素子 105 と第 2 の n チャネル型トランジスタ 108 の第 1 端子との電気的な接続をさせることによって行われる。なお容量素子 105 に充電された電荷の放電は、ステップ 702 で行われるカウンター回路 404 のリセットと共に開始されてもよい。

#### 【0063】

次に、クロック生成回路 405 からのクロック信号の出力に応じて、カウンター回路 404 ではカウント値のカウントアップが行われる（ステップ 704）。30

#### 【0064】

次に、カウントアップするカウント値が最大値に達した否かが判断される（ステップ 705）。ステップ 705 のとき、カウント値が最大値に達していないければ、ラッチ回路 403 に出力されるコンパレータ 106 からの出力信号  $V_{out}$  が H レベルであるか否かの判断がされる（ステップ 706）。ステップ 706 のとき、カウント値が最大値に達しておらず、且つコンパレータ 106 の出力が H レベルではない場合、再度ステップ 704 でのカウント値のカウントアップが行われる。ステップ 705 で、カウントアップするカウント値が最大値に達した場合、及びカウント値が最大値に達しておらず、且つコンパレータ 106 の出力が H レベルのとき、ラッチ回路 403 がカウント値を保持（ラッチ）する（ステップ 707）。以上の動作により、光電変換装置はラッチ回路でラッチしたカウント値に基づいて光の強度の検出を行う。本実施の形態では、カウント値が小さい程、光の強度が大きく、カウント値が大きいほど光の強度が小さいということになる。なお、カウント値が最大の場合には、光の検出がされなかったこととなるため、光の強度も「0」ということになる。40

#### 【0065】

図 9 は、光電変換素子への入射光の強度の変化に対するカウント値の変化を示すグラフである。ここでは、光の強度は照度で表している。図 9 に示すように本実施の形態で説明した光電変換装置は、光電流の大きさに応じてカウント値が異なることを利用し、照度の検出を行うものである。特に本実施の形態によると、光電変換素子に光が照射される光の照50

度が低く、流れる光電流が少量となる場合であっても、カウント値の光の照度に対応する値の間隔を大きくすることができます、確度の高い光の強度の検出をおこなうことができる。

#### 【0066】

以上説明したように光電変換装置の構成は、光電変換素子への入射光量に依らず、容量素子の充電を行う構成とするものである。そのため、入射光量が小さい場合であっても容量素子への電荷の蓄積を行い、光の強度の検出を行うことができる。また光電変換装置の構成は、光電変換回路によって容量素子に蓄積した電荷を放電する構成とすることができます。そのため、定電流源またはスイッチ等の素子を新たに設けることなく、光の強度の検出を行うことができる。

#### 【0067】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0068】

##### (実施の形態2)

本実施の形態では、上記実施の形態で説明した光電変換回路109の增幅回路102におけるトランジスタについて、nチャネル型トランジスタを例として挙げて説明したが、pチャネル型トランジスタを用いた構成について説明する。なお本実施の形態では、上記実施の形態1で説明した箇所については同一の符号を付し、説明を省略する。

#### 【0069】

まず本実施の形態の光電変換装置における回路図について説明する。図10に示す光電変換装置900は、光電変換素子901、増幅回路902、第1のスイッチ903、第2のスイッチ104、容量素子105、コンパレータ106を有する。光電変換素子901は、一方の端子(n型半導体側)が増幅回路902の出力端子に電気的に接続され、他方の端子(p型半導体側)が低電源電位Vssに電気的に接続されている。増幅回路902は、図10に示すようにカレントミラー回路で構成されており、第1のpチャネル型トランジスタ907及び第2のpチャネル型トランジスタ908を有する。第1のpチャネル型トランジスタ907及び第2のpチャネル型トランジスタ908のゲート端子は互いに電気的に接続されており、第1のpチャネル型トランジスタ907の第1端子は第1のpチャネル型トランジスタ907及び第2のpチャネル型トランジスタ908のゲート端子に電気的に接続されている。第1のpチャネル型トランジスタ907及び第2のpチャネル型トランジスタ908の第2端子は高電源電位Vddが供給されている。なお光電変換素子901、第1のpチャネル型トランジスタ907及び第2のpチャネル型トランジスタ908を有する増幅回路902を併せて、光電変換回路909ともいう。また、第1のスイッチ903の第1端子は容量素子105の一方の電極、第2のスイッチ104の第1端子、及びコンパレータ106の非反転入力端子に電気的に接続され、第2の端子は容量素子105の他方の電極に電気的に接続されている。容量素子105の他方の電極には、低電源電位Vssが供給されている。第2のスイッチ104の第2端子は第2のpチャネル型トランジスタ908の第1端子に電気的に接続されている。コンパレータ106の反転入力端子には参照電位Vrefが供給され、コンパレータ106の出力端子より出力信号が outputされる。

#### 【0070】

なお光電変換回路909の増幅回路902における第2のpチャネル型トランジスタ908を、電気的に並列に複数配設する構成としてもよい。第2のpチャネル型トランジスタ908を複数設けることにより、光電変換素子901に光が照射されることで第1のpチャネル型トランジスタ907のソースとドレインの間を流れる電流を増幅して流すことができる。そのため、光電変換素子901に照射される入射光量が小さい場合であっても、第2のpチャネル型トランジスタ908の側に出力信号を得るために十分な電流を流すことができる。

#### 【0071】

なお容量素子105は、第1のスイッチ903がオンになることで低電源電位Vssによ

10

20

30

40

50

り放電がなされ、その後第2のスイッチ104がオンになり、光電変換回路909に流れる電流に応じて充電するものである。そのため、増幅回路902の第2のpチャネル型トランジスタ908の電荷の充電される際の時間を考慮して、容量素子105の静電容量は電荷の充電により電位の上昇ができる程度の容量を備えておくことが望ましい。

#### 【0072】

またコンパレータ106の反転入力端子に供給される参照電位Vrefは、第1のスイッチ903がオンになることで低電源電位Vssによる放電がなされ、その後増幅回路902による充電がなされた際の容量素子105の一方の電極の電位と、比較されることで出力端子より出力信号Voutを出力するための電位である。参照電位Vrefとしては、高電源電位Vddよりも小さく、低電位電源Vssより大きい値に設定することが好ましい。出力信号Voutとしては、Hレベルの信号またはLレベルの信号が出力される。

10

#### 【0073】

次に図10で説明した回路図に加え、アナログ信号をデジタル信号に変換するための信号を生成する構成を加えたブロック図を含む構成について図11を用いて説明する。図11に示すデジタル出力型の光電変換装置1000は、図10で示した光電変換装置900に加え、定電圧回路401(レギュレータともいう)、制御回路402、ラッチ回路403、カウンタ回路404、クロック生成回路405、インターフェース回路406を有する。定電圧回路401、制御回路402、ラッチ回路403、カウンタ回路404、クロック生成回路405、インターフェース回路406に関する説明は実施の形態1と同様である。

20

#### 【0074】

次に図11で示したデジタル出力型の光電変換装置900の具体的な動作について、図12、図13(A)、及び図13(B)を用いて説明する。図12には、第1のスイッチ903及び第2のスイッチ104のオンまたはオフを切り替えた際の容量素子105の一方の電極の電位Vcap、及びコンパレータ106の出力信号の電位Vout、クロック信号、及びカウント値についてのタイミングチャートについて示したものである。なお、Vcap及びVoutについては、光電変換素子901に光が照射された際の光電流ILの大きさを大、中、小の3段階に分けて説明するものである。

#### 【0075】

まず図10に示した、第1のスイッチ903がオフの状態、及び第2のスイッチ104がオンの状態である期間Aにおいて説明する。期間Aにおいて容量素子105の一方の電極の電位Vcapは、光電流ILの大きさに応じて変動し続け、電位の定まらない状態となる。また期間Aにおいて、コンパレータ106の出力信号の電位VoutはVcapの電位に応じて変動し続け、電位の定まらない状態となる。なおクロック信号は、期間Aでクロック生成回路405よりカウンタ回路404へ出力される。そのためカウンタ回路404では、カウント値がカウントアップされるものの、カウント値は期間Aでラッチ回路403に保持されない。

30

#### 【0076】

次に第1のスイッチ903がオンの状態、第2のスイッチ104がオフの状態にある期間Bについて説明する。期間Bにおいて、容量素子105の一方の電極の電位Vcapは、光電流ILの大きさに関わらず低電源電位Vssとなるものである。また期間Bにおいて、コンパレータ106の出力信号の電位Voutは光電流ILの大きさに関わらず、低電源電位Vssが参照電位Vrefを下回るため、Hレベルの信号が出力されるものである。

40

#### 【0077】

期間Bにおける各スイッチのオンまたはオフ、電荷の流れについて、図13(A)に模式的に示す。容量素子105は、第1のスイッチ903がオンになることによって、低電源電位Vssが供給され放電する。また、第2のスイッチ104がオフになっているため、第2のpチャネル型トランジスタ908から容量素子105への電荷の移動はない。

#### 【0078】

50

次に第1のスイッチ903がオフの状態、第2のスイッチ104がオンの状態にある期間Cについて説明する。まず期間Cにおいて、光電変換素子901に光が照射され光電流 $I_L$ が大きい場合(図12中 $I_L$ :大)、容量素子105の一方の電極の電位 $V_{cap}$ は、光電流 $I_L$ に応じて第2のpチャネル型トランジスタ908より流れる電流Iが大きくなり、上昇する。そのため、時間 $t_0$ (時間 $t_0 < t_1 < t_2 < t_3$ )で容量素子105の電位 $V_{cap}$ が $V_{ss}$ であったのが時間 $t_1$ で電位 $V_{ref}$ となり、その後容量素子105への充電が完了することで電位 $V_{dd}$ となる。このとき、コンパレータ106の出力信号の電位 $V_{out}$ は、容量素子の電位 $V_{cap}$ が低電源電位 $V_{ss}$ から参照電位 $V_{ref}$ となった際に、Lレベルの信号を出力する。そして、当該信号でラッチ回路403は、入力されるカウント値を保持する。なお期間Cになる時間 $t_0$ と同時に、カウンター回路404およびラッチ回路403がリセットされ、カウンター回路404でクロック信号に基づくカウントアップがなされる。そして、時間 $t_1$ にコンパレータ106の出力信号の電位 $V_{out}$ がラッチ回路403に入力されることで時間 $t_0$ から時間 $t_1$ の間の期間のクロック信号に基づいたカウント値 $t_{1\_count}$ が得られることとなる。

## 【0079】

また第1のスイッチ903がオフの状態、第2のスイッチ104がオンの状態にある期間Cであって、光電変換素子901に光が照射され光電流 $I_L$ が中程度の場合(図12中 $I_L$ :中)、容量素子105の一方の電極の電位 $V_{cap}$ は、光電流 $I_L$ が大きい場合に比べ第2のpチャネル型トランジスタ908に流れる電流Iが小さいため上昇の割合は小さいものの、増加していく。そのため、時間 $t_0$ で容量素子105の電位 $V_{cap}$ が $V_{ss}$ であったのが時間 $t_2$ で電位 $V_{ref}$ となり、その後容量素子105への充電が完了することで電位 $V_{dd}$ となる。このとき、コンパレータ106の出力信号の電位 $V_{out}$ は、容量素子の電位 $V_{cap}$ が低電源電位 $V_{ss}$ から参照電位 $V_{ref}$ となった際に、Lレベルの信号を出力する。そして当該信号でラッチ回路403は、入力されるカウント値を保持する。なお期間Cになる時間 $t_0$ と同時に、カウンター回路404およびラッチ回路403がリセットされ、カウンター回路404でクロック信号に基づくカウントアップがなされる。そして、時間 $t_2$ にコンパレータ106の出力信号の電位 $V_{out}$ がラッチ回路403に入力されることで時間 $t_0$ から時間 $t_2$ の間の期間のクロック信号に基づいたカウント値 $t_{2\_count}$ が得られることとなる。

## 【0080】

また第1のスイッチ903がオフの状態、第2のスイッチ104がオンの状態にある期間Cであって、光電変換素子901に光が照射され光電流 $I_L$ が小さい場合(図12中 $I_L$ :小)、容量素子105の一方の電極の電位 $V_{cap}$ は、光電流 $I_L$ が小さいため第2のpチャネル型トランジスタ908に流れる電流Iも小さく上昇の割合も小さいものの、上昇していく。そのため、時間 $t_0$ で容量素子105の電位 $V_{cap}$ が $V_{ss}$ であったのが時間 $t_3$ で電位 $V_{ref}$ となり、その後容量素子105への充電が完了することで電位 $V_{dd}$ となる。このとき、コンパレータ106の出力信号の電位 $V_{out}$ は、容量素子の電位 $V_{cap}$ が低電源電位 $V_{ss}$ から参照電位 $V_{ref}$ となった際に、Lレベルの信号を出力する。そして当該信号でラッチ回路403は、入力されるカウント値を保持する。なお期間Cになる時間 $t_0$ と同時に、カウンター回路404およびラッチ回路403がリセットされ、カウンター回路404でクロック信号に基づくカウントアップがなされる。そして、時間 $t_3$ にコンパレータ106の出力信号の電位 $V_{out}$ がラッチ回路403に入力されることで時間 $t_0$ から時間 $t_3$ の間の期間のクロック信号に基づいたカウント値 $t_{3\_count}$ が得られることとなる。

## 【0081】

期間Cにおける各スイッチのオンまたはオフ、電荷の流れについて、図13(B)に模式的に示す。容量素子105は、第1のスイッチ903がオフになるとことによって、新たに低電源電位 $V_{ss}$ により放電されることはない。一方、第2のスイッチ104がオンになっているため、容量素子105へ第2のpチャネル型トランジスタ908より電流Iが流れ、容量素子105への充電が行われる。なお、第2のpチャネル型トランジスタ908

10

20

30

40

50

を流れる電流  $I_L$  は、増幅回路 902 がカレントミラー回路を形成していることにより、光電流  $I_L$  に比例した大きさとなる。

#### 【0082】

なお、第 1 のスイッチ 903 がオフの状態、第 2 のスイッチ 104 がオンの状態にある期間 C であって、光電変換素子 901 に光が照射されず光電流  $I_L$  が検出できない場合、容量素子 105 の一方の電極の電位  $V_{cap}$  は、第 2 の p チャネル型トランジスタ 908 に流れる電流  $I$  が生じないため、ほとんど増加しない。そのため、時間  $t_0$  で容量素子 105 の電位  $V_{cap}$  が  $V_{ss}$  であるものの、時間の経過に伴う電位  $V_{ref}$  への変化がない。このとき、コンパレータ 106 の出力信号の電位  $V_{out}$  は、容量素子の電位  $V_{cap}$  が低電源電位  $V_{ss}$  から参照電位  $V_{ref}$  に変化しないため、H レベルの信号が出力し続けるものである。またクロック信号は、期間 C になった時間  $t_0$  より、カウンター回路 404 への出力がなされる。そのため上述のように光電流  $I_L$  に応じたカウント値を得ることが出来ずカウント値はカウンター回路の最大値に達してしまう。この場合、カウント値の最大値をラッチ回路に出力することが好みしい。

10

#### 【0083】

図 12、図 13(A)、図 13(B) で説明したデジタル出力型の光電変換装置 1000 の具体的な動作について、図 14 に示すフローチャートを用いて説明する。

#### 【0084】

まず光電変換装置 1000 は容量素子 105 の電荷の放電（リセット）を開始する（ステップ 1301）。容量素子 105 の電荷の放電は、上述したように第 1 のスイッチ 903 をオン、第 2 のスイッチ 104 をオフにすることにより、低電源電位  $V_{ss}$  が供給された配線により容量素子 105 の両端の電極の電気的な接続をとることで行われる。またステップ 1301 では容量素子 105 の放電と共に、クロック生成回路 405 からのクロック信号の出力が行われる。

20

#### 【0085】

次に光電変換装置 1000 は、容量素子 105 の電荷の放電の後、カウンター回路 404 のカウント値のリセットを行う（ステップ 1302）。また、ステップ 1302 ではカウンター回路 404 のカウント値のリセットと共に、ラッチ回路 403 に保持されたカウント値の初期化を行う。

30

#### 【0086】

次に光電変換装置 1000 は、光電変換回路 909 の第 2 の p チャネル型トランジスタ 908 により、放電された容量素子 105 に電荷の充電をおこなう（ステップ 1303）。容量素子 105 への電荷の充電は、上述したように第 1 のスイッチ 903 をオフ、第 2 のスイッチ 104 をオンにすることにより、容量素子 105 と第 2 の p チャネル型トランジスタ 908 の第 1 端子との電気的な接続をさせることによって行われる。なお容量素子 105 への電荷の充電は、ステップ 1302 で行われるカウンター回路 404 のリセットと共に開始されてもよい。

#### 【0087】

次に、クロック生成回路 405 からのクロック信号の出力に応じて、カウンター回路 404 ではカウント値のカウントアップが行われる（ステップ 1304）。

40

#### 【0088】

次に、カウントアップするカウント値が最大値に達した否かが判断される（ステップ 1305）。ステップ 1305 のとき、カウント値が最大値に達していないければ、ラッチ回路 403 に出力されるコンパレータ 106 からの出力信号  $V_{out}$  が L レベルであるか否かの判断がされる（ステップ 1306）。ステップ 1306 のとき、カウント値が最大値に達しておらず、且つコンパレータ 106 の出力が L レベルではない場合、再度ステップ 1304 でのカウント値のカウントアップが行われる。ステップ 1305 で、カウントアップするカウント値が最大値に達した場合、及びカウント値が最大値に達しておらず、且つコンパレータ 106 の出力が L レベルのとき、ラッチ回路 403 がカウント値を保持する（ステップ 1307）。以上の動作により、光電変換装置はラッチ回路でラッチしたカウ

50

ント値に基づいて光の強度の検出を行う。本実施の形態では、カウント値が小さい程、光の強度が大きく、カウント値が大きいほど光の強度が小さいということになる。なお、カウント値が最大の場合には、光の検出がされなかったこととなるため、光の強度も「0」ということになる。

#### 【0089】

以上説明したように光電変換装置の構成では、上記実施の形態1と同様に、光電変換素子への入射光量に依らず、容量素子の充電を行う構成とするものである。そのため、入射光量が小さい場合であっても容量素子への電荷の蓄積を行い、光の強度の検出を行うことができる。また光電変換装置の構成は、容量素子のリセットした電荷を、入射光量に比例した電流を流すことのできる光電変換回路によって充電する構成とすることができる。そのため、定電流源またはスイッチ等の素子を新たに設けることなく、光の強度の検出を行うことができる。また特に本実施の形態で示した構成では、光電変換装置に対し、第1の電位V<sub>set</sub>を供給する必要がないため、配線数を少なくすることができ、光電変換装置の小型化を図ることができる。10

#### 【0090】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0091】

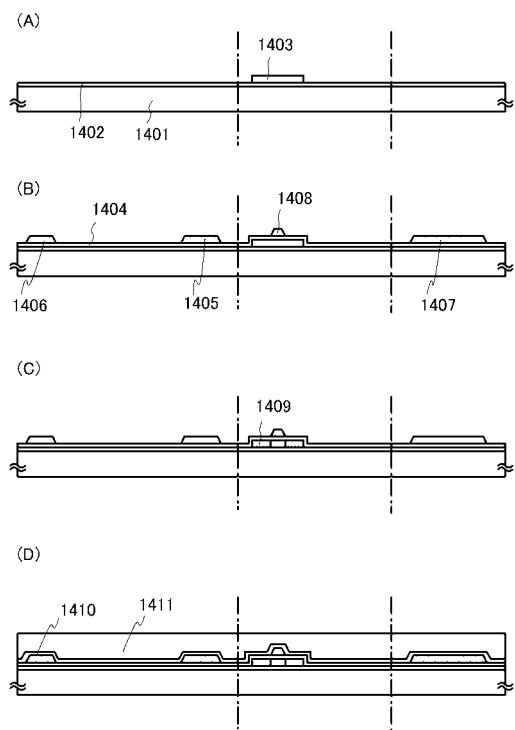

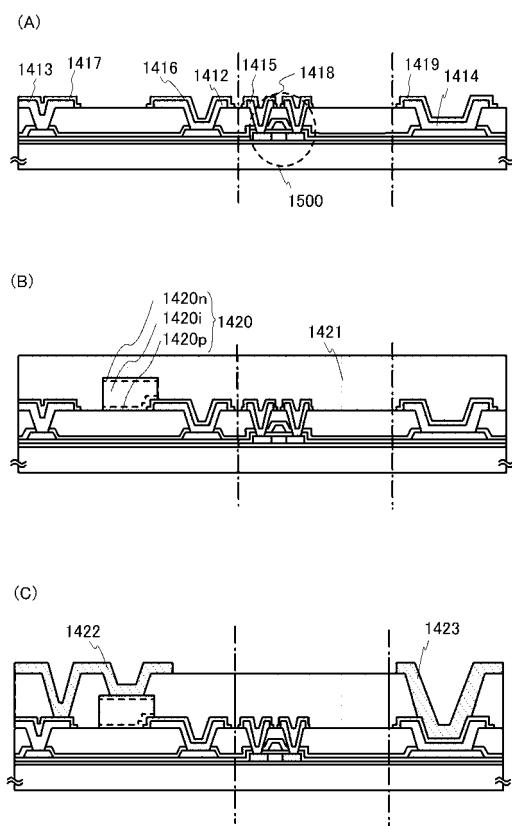

##### (実施の形態3)

本実施の形態では、光電変換装置の作製方法について図15、図16を用いて詳しく述べる。なお、本実施の形態では、光電変換装置の各回路を構成する素子である薄膜トランジスタ(TFT)と、光電変換素子である縦型接合タイプのPINフォトダイオード(以下、フォトダイオードともいう)とを具備する光電変換装置の一例を示す。なお光電変換装置は、TFT及びPINフォトダイオードの他に、記憶素子、抵抗、ダイオード、容量、インダクタなども用いることがある。また、光電変換装置は、縦型接合タイプのPINフォトダイオードの代わりに、縦型接合タイプのPNフォトダイオードを用いていても良い。20

#### 【0092】

まず、透光性を有する基板1401上にフォトダイオード及び薄膜トランジスタを形成する。ここでは基板1401として、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板等を用いることができる。基板上に形成するトランジスタとして、薄膜トランジスタを用いることにより、基板上に、フォトダイオードと薄膜トランジスタを同一工程で作製することができるため、光電変換装置の量産化がしやすいといった利点がある。30

#### 【0093】

次いで、プラズマCVD法で下地絶縁膜1402となる酸化窒化珪素膜(膜厚100nm)を形成し、さらに大気にふれることなく、半導体膜例えば水素を含む非晶質珪素膜(膜厚54nm)を積層形成する。また、下地絶縁膜1402は酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜を用いて積層形成してもよい。例えば、下地絶縁膜1402として、窒化酸化珪素膜を50nm、さらに酸化窒化珪素膜を100nm積層した膜を形成してもよい。なお、窒化酸化珪素膜や窒化珪素膜は、ガラス基板からのアルカリ金属などの不純物拡散を防止するプロッキング層として機能する。なお、石英基板など不純物の拡散がさして問題とならない基板を用いる場合は、必ずしも設ける必要はない。40

#### 【0094】

なお、酸化窒化珪素膜とは、その組成として、窒素よりも酸素の含有量が多い膜であって、ラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS: Hydrogen Forward Scattering)を用いて測定した場合に、濃度範囲として酸素が50~70原子%、窒素が0.5~15原子%、珪素が25~35原子%、水素が0.1~10原子%の範囲で含まれる膜をいう。また、窒化酸化珪素膜とは、その組成として、50

酸素よりも窒素の含有量が多い膜であって、RBS 及びHFS を用いて測定した場合に、濃度範囲として酸素が5 ~ 30 原子%、窒素が20 ~ 55 原子%、珪素が25 ~ 35 原子%、水素が10 ~ 25 原子% の範囲で含まれる膜をいう。但し、酸化窒化珪素または窒化酸化珪素を構成する原子の合計を100 原子%としたとき、窒素、酸素、珪素及び水素の含有比率が上記の範囲内に含まれるものとする。

#### 【0095】

次いで、上記非晶質珪素膜を公知の技術（固相成長法、レーザ結晶化方法、触媒金属を用いた結晶化方法など）により結晶化させて、結晶構造を有する半導体膜（結晶性半導体膜）、例えば多結晶珪素膜を形成する。ここでは、触媒元素を用いた結晶化方法を用いて多結晶珪素膜を得る。重量換算で10 ppm のニッケルを含む酢酸ニッケル溶液をスピナーで添加する。なお、溶液を添加する方法に代えてスパッタ法でニッケル元素を全面に散布する方法を用いてもよい。次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜（ここでは多結晶珪素膜）を形成する。ここでは熱処理（500 、1 時間）の後、結晶化のための熱処理（550 、4 時間）を行って多結晶珪素膜を得る。

10

#### 【0096】

次いで、多結晶珪素膜表面の酸化膜を希フッ酸等で除去する。その後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザ光（XeCl：波長308 nm）の照射を大気中、または酸素雰囲気中で行う。

#### 【0097】

レーザ光には波長400 nm 以下のエキシマレーザ光や、YAG レーザの第2高調波又は第3高調波を用いる。ここでは、繰り返し周波数10 ~ 1000 Hz 程度のパルスレーザ光を用い、当該レーザ光を光学系にて100 ~ 500 mJ / cm<sup>2</sup> に集光し、90 ~ 95 % のオーバーラップ率をもって照射し、シリコン膜表面を走査させればよい。本実施例では、繰り返し周波数30 Hz、エネルギー密度470 mJ / cm<sup>2</sup> でレーザ光の照射を大気中で行なう。

20

#### 【0098】

なお、大気中、または酸素雰囲気中で行うため、レーザ光の照射により表面に酸化膜が形成される。なお、本実施例ではパルスレーザを用いた例を示したが、連続発振のレーザを用いてもよく、半導体膜の結晶化に際し、大粒径に結晶を得るためにには、連続発振が可能な固体レーザを用い、基本波の第2高調波～第4高調波を適用するのが好ましい。代表的には、Nd : YVO<sub>4</sub> レーザ（基本波1064 nm）の第2高調波（532 nm）や第3高調波（355 nm）を適用すればよい。

30

#### 【0099】

連続発振のレーザを用いる場合には、出力10 W の連続発振のYVO<sub>4</sub> レーザから射出されたレーザ光を非線形光学素子により高調波に変換する。また、共振器の中にYVO<sub>4</sub> 結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橢円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01 ~ 100 MW / cm<sup>2</sup> 程度（好ましくは0.1 ~ 10 MW / cm<sup>2</sup>）が必要である。そして、10 ~ 2000 cm / s 程度の速度でレーザ光に對して相対的に半導体膜を移動させて照射すればよい。

40

#### 【0100】

次いで、上記レーザ光の照射により形成された酸化膜に加え、オゾン水で表面を120秒処理して合計1 ~ 5 nm の酸化膜からなるバリア層を形成する。このバリア層は、結晶化させるために添加した触媒元素、例えばニッケル（Ni）を膜中から除去するために形成する。ここではオゾン水を用いてバリア層を形成したが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する方法や酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法やプラズマCVD 法やスパッタ法や蒸着法などで1 ~ 10 nm 程度の酸化膜を堆積してバリア層を形成してもよい。また、バリア層を形成する前にレーザ光の照射により形成された酸化膜を除去してもよい。

#### 【0101】

50

次いで、バリア層上にスパッタ法にてゲッタリングサイトとなるアルゴンを含む非晶質珪素膜を10nm～400nm、ここでは膜厚100nmで成膜する。ここでは、アルゴンを含む非晶質珪素膜は、シリコンターゲットを用いてアルゴンを含む雰囲気下で形成する。プラズマCVD法を用いてアルゴンを含む非晶質珪素膜を形成する場合、成膜条件は、モノシランとアルゴンの流量比(SiH<sub>4</sub>:Ar)を1:99とし、成膜圧力を6.665Paとし、RFパワー密度を0.087W/cm<sup>2</sup>とし、成膜温度を350°とする。

#### 【0102】

その後、650°に加熱された炉に入れて3分の熱処理を行い触媒元素を除去(ゲッタリング)する。これにより結晶構造を有する半導体膜中の触媒元素濃度が低減される。炉に代えてランプアニール装置を用いてもよい。

10

#### 【0103】

次いで、バリア層をエッチングストップとして、ゲッタリングサイトであるアルゴンを含む非晶質珪素膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。

#### 【0104】

なお、触媒元素を用いて半導体膜の結晶化を行わない場合には、上述したバリア層の形成、ゲッタリングサイトの形成、ゲッタリングのための熱処理、ゲッタリングサイトの除去、バリア層の除去などの工程は不要である。

20

#### 【0105】

次いで、得られた結晶構造を有する半導体膜(例えば結晶性珪素膜)の表面にオゾン水で薄い酸化膜を形成した後、第1のフォトマスクを用いてレジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体膜(本明細書では「島状半導体領域1403」という)を形成する(図15(A)参照)。島状半導体領域を形成した後、レジストからなるマスクを除去する。

#### 【0106】

次いで、必要があればTFTのしきい値を制御するために微量な不純物元素(ホウ素またはリン)のドーピングを行う。ここでは、ジボラン(B<sub>2</sub>H<sub>6</sub>)を質量分離しないでプラズマ励起したイオンドープ法を用いる。

30

#### 【0107】

次いで、フッ酸を含むエッチャントで酸化膜を除去すると同時に島状半導体領域1403の表面を洗浄した後、ゲート絶縁膜1404となる珪素を主成分とする絶縁膜を形成する。ここでは、プラズマCVD法により115nmの厚さで窒素を含む酸化珪素膜(組成比Si=32%、O=59%、N=7%、H=2%)で形成する。

#### 【0108】

次いで、ゲート絶縁膜1404上に金属膜を形成した後、第2のフォトマスクを用いて、ゲート電極1408、配線1405及び1406、端子電極1407を形成する(図15(B)参照)。この金属膜として、例えば窒化タンタル及びタンゲステン(W)をそれぞれ30nm、370nm積層した膜を用いる。

40

#### 【0109】

また、ゲート電極1408、配線1405、配線1406、及び端子電極1407として、上記以外にもチタン(Ti)、タンゲステン(W)、タンタル(Ta)、モリブデン(Mo)、ネオジム(Nd)、コバルト(Co)、ジルコニア(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、白金(Plt)、アルミニウム(Al)、金(Au)、銀(Ag)、銅(Cu)から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。

#### 【0110】

次いで、島状半導体領域1403への一導電型を付与する不純物元素の導入を行って、T

50

F T 1 5 0 0 のソース領域またはドレイン領域 1 4 0 9 の形成を行う（図 1 5 ( C ) 参照）。本実施の形態では一例として、n チャネル型 TFT を形成するので、n 型を付与する不純物元素、例えばリン ( P ) 、砒素 ( As ) を島状半導体領域 1 4 0 3 に導入する。p チャネル型 TFT を形成する際には、p 型の不純物を島状半導体領域 1 4 0 3 に導入する。

#### 【 0 1 1 1 】

次いで、CVD 法により酸化珪素膜を含む第 1 の層間絶縁膜（図示しない）を 50 nm 形成した後、それぞれの島状半導体領域に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法 (RTA 法) 、或いは YAG レーザまたはエキシマレーザを裏面から照射する方法、或いは炉を用いた熱処理、或いはこれらの方法のうち、いずれかと組み合わせた方法によって行う。10

#### 【 0 1 1 2 】

次いで、水素及び酸素を含む窒化珪素膜を含む第 2 の層間絶縁膜 1 4 1 0 を、例えば 10 nm の膜厚で形成する。

#### 【 0 1 1 3 】

次いで、第 2 の層間絶縁膜 1 4 1 0 上に絶縁物材料から成る第 3 の層間絶縁膜 1 4 1 1 を形成する（図 1 5 ( D ) 参照）。第 3 の層間絶縁膜 1 4 1 1 は CVD 法で得られる絶縁膜を用いることができる。本実施の形態においては密着性を向上させるため、第 3 の層間絶縁膜 1 4 1 1 として、900 nm の膜厚で形成した窒素を含む酸化珪素膜を形成する。20

#### 【 0 1 1 4 】

次に、熱処理 (300 ~ 550 °C で 1 ~ 12 時間の熱処理、例えば窒素雰囲気中 410 °C で 1 時間) を行い、島状半導体領域 1 4 0 3 を水素化する。この工程は第 2 の層間絶縁膜 1 4 1 0 に含まれる水素により島状半導体膜のダングリングボンドを終端させるために行うものである。ゲート絶縁膜 1 4 0 4 の存在に関係なく島状半導体膜を水素化することができる。

#### 【 0 1 1 5 】

また第 3 の層間絶縁膜 1 4 1 1 として、シロキサンを用いた絶縁膜、及びそれらの積層構造を用いることも可能である。シロキサンは、シリコン (Si) と酸素 (O) との結合で骨格構造で構成される。置換基として、少なくとも水素を含む化合物（例えばアルキル基、芳香族炭化水素）が用いられる。置換基として、フッ素を用いてもよい。または置換基として、少なくとも水素を含む化合物と、フッ素とを用いてもよい。30

#### 【 0 1 1 6 】

第 3 の層間絶縁膜 1 4 1 1 としてシロキサンを用いた絶縁膜、及びそれらの積層構造を用いた場合は、第 2 の層間絶縁膜 1 4 1 0 を形成後、島状半導体膜を水素化するための熱処理を行い、次に第 3 の層間絶縁膜 1 4 1 1 を形成することもできる。

#### 【 0 1 1 7 】

次いで、第 3 のフォトマスクを用いてレジストからなるマスクを形成し、第 1 の層間絶縁膜、第 2 の層間絶縁膜 1 4 1 0 及び第 3 の層間絶縁膜 1 4 1 1 またはゲート絶縁膜 1 4 0 4 を選択的にエッチングしてコンタクトホールを形成する。そして、レジストからなるマスクを除去する。40

#### 【 0 1 1 8 】

なお、第 3 の層間絶縁膜 1 4 1 1 は必要に応じて形成すればよく、第 3 の層間絶縁膜 1 4 1 1 を形成しない場合は、第 2 の層間絶縁膜 1 4 1 0 を形成後に第 1 の層間絶縁膜、第 2 の層間絶縁膜 1 4 1 0 及びゲート絶縁膜 1 4 0 4 を選択的にエッチングしてコンタクトホールを形成する。

#### 【 0 1 1 9 】

次いで、スパッタ法で金属積層膜を成膜した後、第 4 のフォトマスクを用いてレジストからなるマスクを形成し、選択的に金属積層膜をエッチングして、配線 1 4 1 2 、接続電極 1 4 1 3 、端子電極 1 4 1 4 、TFT 1 5 0 0 のソース電極またはドレイン電極 1 4 1 5 を形成する。そして、レジストからなるマスクを除去する。なお、本実施の形態の金属膜

10

20

30

40

50

は、膜厚 100 nm の Ti 膜と、膜厚 350 nm の Si を微量に含む Al 膜と、膜厚 100 nm の Ti 膜との 3 層を積層したものとする。

#### 【0120】

また配線 1412、接続電極 1413、端子電極 1414、及び TFT1500 のソース電極又はドレイン電極 1415 を単層の導電膜により形成する場合は、耐熱性及び導電率等の点からチタン膜 (Ti 膜) が好ましい。またチタン膜に変えて、タングステン (W)、タンタル (Ta)、モリブデン (Mo)、ネオジム (Nd)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスミウム (Os)、イリジウム (Ir)、白金 (Pt) から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タングステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。配線 1412、接続電極 1413、端子電極 1414、及び TFT1500 のソース電極又はドレイン電極 1415 を単層膜にすることにより、作製工程において成膜回数を減少させることが可能となる。

10

#### 【0121】

以上の工程で、多結晶珪素膜を用いたトップゲート型 TFT1500 を作製することができる。

#### 【0122】

次いで、後に形成される光電変換素子（代表的にはアモルファスシリコン）と反応して合金になりにくい導電性の金属膜（チタン (Ti) またはモリブデン (Mo) など）を成膜した後、第 5 のフォトマスクを用いてレジストからなるマスクを形成し、選択的に導電性の金属膜をエッチングして配線 1412 を覆う保護電極 1416、保護電極 1417、保護電極 1418、及び保護電極 1419 を形成する（図 16 (A)）。ここではスパッタ法で得られる膜厚 200 nm の Ti 膜を用いる。なお、同様に接続電極 1413、端子電極 1414、TFT1500 のソース電極またはドレイン電極 1415 も導電性の金属膜で覆われる。従って、導電性の金属膜は、これらの電極における 2 層目の Al 膜が露呈されている側面も覆い、導電性の金属膜は光電変換素子へのアルミニウム原子の拡散も防止できる。

20

#### 【0123】

ただし、配線 1412、接続電極 1413、端子電極 1414、及び TFT1500 のソース電極またはドレイン電極 1415 を、単層の導電膜で形成する場合、保護電極 1416、保護電極 1417、保護電極 1418、及び保護電極 1419 は形成しなくてよい。

30

#### 【0124】

次に第 3 の層間絶縁膜 1411 上に、p 型半導体層 1420p、i 型半導体層 1420i 及び n 型半導体層 1420n を含む光電変換素子 1420 を形成する。

#### 【0125】

p 型半導体層 1420p は、周期表第 13 属の不純物元素、例えばホウ素 (B) を含んだセミアモルファスシリコン膜をプラズマ CVD 法にて成膜して形成すればよい。

40

#### 【0126】

また配線 1412 及び保護電極 1416 は光電変換素子 1420 の最下層、本実施例では p 型半導体層 1420p と接している。

#### 【0127】

p 型半導体層 1420p を形成したら、さらに i 型半導体層 1420i 及び n 型半導体層 1420n を順に形成する。これにより p 型半導体層 1420p、i 型半導体層 1420i 及び n 型半導体層 1420n を有する光電変換素子 1420 が形成される。

#### 【0128】

i 型半導体層 1420i としては、例えばプラズマ CVD 法でセミアモルファスシリコン膜を形成すればよい。また n 型半導体層 1420n としては、周期表第 15 属の不純物元素、例えばリン (P) を含むセミアモルファスシリコン膜を形成してもよいし、セミアモ

50

ルファスシリコン膜を形成後、周期表第15属の不純物元素を導入してもよい。

【0129】

またp型半導体層1420p、i型半導体層1420i、n型半導体層1420nとして、セミアモルファス半導体膜だけではなく、アモルファス半導体膜を用いてもよい。

【0130】

次いで、全面に絶縁物材料（例えば珪素を含む無機絶縁膜）からなる封止層1421を厚さ $1\text{ }\mu\text{m} \sim 30\text{ }\mu\text{m}$ で形成して図16(B)の状態を得る。ここでは絶縁物材料膜としてCVD法により、膜厚 $1\text{ }\mu\text{m}$ の窒素を含む酸化珪素膜を形成する。CVD法による絶縁膜を用いることによって密着性の向上を図っている。

【0131】

次いで、封止層1421をエッティングして開口部を設けた後、スパッタ法により端子電極1422及び端子電極1423を形成する。端子電極1422及び1423は、チタン膜(Ti膜)(100nm)と、ニッケル膜(Ni膜)(300nm)と、金膜(Au膜)(50nm)との積層膜とする。こうして得られる端子電極1422及び端子電極1423の固着強度は5Nを超え、端子電極として十分な固着強度を有している。

10

【0132】

以上の工程で、半田接続が可能な端子電極1422及び端子電極1423が形成され、図16(C)に示す構造が得られる。

【0133】

なお上記工程で得られる光電変換装置は、基板より個々に切断して複数の光電変換装置を切り出すことで大量生産が可能である。1枚の大面積基板（例えば $600\text{ cm} \times 720\text{ cm}$ ）からは大量の光電変換装置（例えば $2\text{ mm} \times 1.5\text{ mm}$ ）を製造することができる。

20

【0134】

なお、本実施の形態で示す島状半導体領域1403の作製方法としては、上記作製方法に限らず他の作製方法を用いて形成することもできる。一例としては、SOI（シリコン・オン・インシュレータ）基板を用いて島状半導体領域1403を形成してもよい。SOI基板としては、公知のSOI基板を用いればよく、その作製方法や構造は特に限定されない。SOI基板としては、代表的にはSIMOX基板や貼り合わせ基板が挙げられる。また、貼り合わせ基板の例として、ELTRAN（登録商標）、UNIBOND（登録商標）、スマートカット（登録商標）等が挙げられる。

30

【0135】

SIMOX基板は、単結晶シリコン基板に酸素イオンを注入し、1300以上で熱処理して埋め込み酸化膜層(Box; Buried Oxide)を形成することにより、表面に薄膜シリコン層を形成し、SOI構造を得ることができる。薄膜シリコン層は、埋め込み酸化膜層により、単結晶シリコン基板と絶縁分離されている。また、埋め込み酸化膜層形成後に、さらに熱酸化するITOX(Internal Thermal Oxidation-SIMOX)と呼ばれる技術を用いることもできる。

【0136】

貼り合わせ基板は、酸化膜層を介して2枚の単結晶シリコン基板（第1単結晶シリコン基板、第2単結晶シリコン基板）を貼り合わせ、一方の単結晶シリコン基板を貼り合わせた面ではない方の面から薄膜化することにより、表面に薄膜シリコン層を形成したSOI基板のことをいう。酸化膜層は、一方の基板（ここでは第1単結晶シリコン基板）を熱酸化して形成することができる。また、2枚の単結晶シリコン基板は、接着剤なしで直接貼り合わせることができる。

40

【0137】

なお、貼り合わせ基板としては、2枚の単結晶基板を貼り合わせることに限らず、ガラス基板等の絶縁表面を有する基板と、単結晶基板とを貼り合わせてSOI基板を作製してもよい。

【0138】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に

50

対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【0139】

(実施の形態4)

光電変換装置は、入射光量が小さい場合であっても、容量素子への電荷の蓄積を行い、光の強度の検出を可能とし、構成する定電流源またはスイッチ等の素子数を増加させることなく動作させることができるといった特徴を有している。よって、光電変換装置を具備する電子機器は、光電変換装置をその構成要素に追加することに伴って、電子機器の生産コストの上昇を抑制し、暗所での光の検出を行うことができる。光電変換装置は、表示装置、ノート型パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、光電変換装置を用いることができる電子機器として、携帯電話、携帯型ゲーム機または電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、などが挙げられる。これら電子機器の具体例を図17に示す。

10

【0140】

図17(A)は表示装置であり、筐体5001、表示部5002、センサ部5003等を有する。光電変換装置は、センサ部5003に用いることができる。センサ部5003は外光の強度を検知する。表示装置は、検知した外光の強度に合わせて、表示部5002の輝度のコントロールを行うことができる。外光の強度に合わせて表示部5002の輝度のコントロールすることで、表示装置の消費電力を抑えることができる。なお、表示装置には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

20

【0141】

図17(B)は携帯電話であり、本体5101、表示部5102、音声入力部5103、音声出力部5104、操作キー5105、センサ部5106等を有する。センサ部5106は外光の強度を検知する。携帯電話は、検知した外光の強度に合わせて、表示部5102または操作キー5105の輝度のコントロールを行うことができる。外光の強度に合わせて表示部5102または操作キー5105の輝度のコントロールすることで、携帯電話の消費電力を抑えることができる。

30

【0142】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【符号の説明】

【0143】

10 光電変換装置

11 光電変換素子

12 増幅回路

13 スイッチ

14 スイッチ

15 容量素子

16 コンパレータ

17 光電変換回路

40

100 光電変換装置

101 光電変換素子

102 増幅回路

103 スイッチ

104 スイッチ

105 容量素子

106 コンパレータ

50

|         |               |    |

|---------|---------------|----|

| 1 0 7   | n チャネル型トランジスタ |    |

| 1 0 8   | n チャネル型トランジスタ |    |

| 1 0 9   | 光電変換回路        |    |

| 2 0 3   | p チャネル型トランジスタ |    |

| 2 0 4   | アナログスイッチ      |    |

| 4 0 0   | 光電変換装置        |    |

| 4 0 1   | 定電圧回路         |    |

| 4 0 2   | 制御回路          |    |

| 4 0 3   | ラッチ回路         |    |

| 4 0 4   | カウンター回路       | 10 |

| 4 0 5   | クロック生成回路      |    |

| 4 0 6   | インターフェース回路    |    |

| 7 0 1   | ステップ          |    |

| 7 0 2   | ステップ          |    |

| 7 0 3   | ステップ          |    |

| 7 0 4   | ステップ          |    |

| 7 0 5   | ステップ          |    |

| 7 0 6   | ステップ          |    |

| 7 0 7   | ステップ          |    |

| 9 0 0   | 光電変換装置        | 20 |

| 9 0 1   | 光電変換素子        |    |

| 9 0 2   | 增幅回路          |    |

| 9 0 3   | スイッチ          |    |

| 9 0 7   | p チャネル型トランジスタ |    |

| 9 0 8   | p チャネル型トランジスタ |    |

| 9 0 9   | 光電変換回路        |    |

| 1 0 0 0 | 光電変換装置        |    |

| 1 1 0 0 | 光電変換装置        |    |

| 1 3 0 1 | ステップ          |    |

| 1 3 0 2 | ステップ          | 30 |

| 1 3 0 3 | ステップ          |    |

| 1 3 0 4 | ステップ          |    |

| 1 3 0 5 | ステップ          |    |

| 1 3 0 6 | ステップ          |    |

| 1 3 0 7 | ステップ          |    |

| 1 4 0 1 | 基板            |    |

| 1 4 0 2 | 下地絶縁膜         |    |

| 1 4 0 3 | 島状半導体領域       |    |

| 1 4 0 4 | ゲート絶縁膜        |    |

| 1 4 0 5 | 配線            | 40 |

| 1 4 0 6 | 配線            |    |

| 1 4 0 7 | 端子電極          |    |

| 1 4 0 8 | ゲート電極         |    |

| 1 4 0 9 | ドレイン領域        |    |

| 1 4 1 0 | 層間絶縁膜         |    |

| 1 4 1 1 | 層間絶縁膜         |    |

| 1 4 1 2 | 配線            |    |

| 1 4 1 3 | 接続電極          |    |

| 1 4 1 4 | 端子電極          |    |

| 1 4 1 5 | ドレイン電極        | 50 |

|           |        |

|-----------|--------|

| 1 4 1 6   | 保護電極   |

| 1 4 1 7   | 保護電極   |

| 1 4 1 8   | 保護電極   |

| 1 4 1 9   | 保護電極   |

| 1 4 2 0   | 光電変換素子 |

| 1 4 2 1   | 封止層    |

| 1 4 2 2   | 端子電極   |

| 1 4 2 3   | 端子電極   |

| 1 5 0 0   | TFT    |

| 5 0 0 1   | 筐体     |

| 5 0 0 2   | 表示部    |

| 5 0 0 3   | センサ部   |

| 5 1 0 1   | 本体     |

| 5 1 0 2   | 表示部    |

| 5 1 0 3   | 音声入力部  |

| 5 1 0 4   | 音声出力部  |

| 5 1 0 5   | 操作キー   |

| 5 1 0 6   | センサ部   |

| 1 4 2 0 i | i型半導体層 |

| 1 4 2 0 n | n型半導体層 |

| 1 4 2 0 p | p型半導体層 |

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【図12】

【図 1 3】

【 図 1 4 】

【図15】

【図16】

【図17】

---

フロントページの続き

(72)発明者 柳澤 真

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

Fターム(参考) 5F049 MA04 NA04 NA18 NA19 SS01 UA05 UA13 UA14 UA17