#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

### (43) International Publication Date 16 September 2010 (16.09.2010)

### (10) International Publication Number WO 2010/104918 A1

- (51) International Patent Classification:

- H01L 27/102 (2006.01) H01L 27/24 (2006.01) H01L 27/105 (2006.01) H01L 29/78 (2006.01)

- H01L 27/112 (2006.01) G11C 11/56 (2006.01)

- H01L 29/87 (2006.01) G11C 17/14 (2006.01) H01L 27/06 (2006.01) G11C 16/02 (2006.01)

- (21) International Application Number:

PCT/US2010/026775

(22) International Filing Date:

10 March 2010 (10.03.2010)

- (25) Filing Language: English

- (26) Publication Language: English

- (30) Priority Data:

| 61/209,725 | 10 March 2009 (10.03.2009)    | US |

|------------|-------------------------------|----|

| 61/273,163 | 31 July 2009 (31.07.2009)     | US |

| 61/275,169 | 26 August 2009 (26.08.2009)   | US |

| 61/281,388 | 17 November 2009 (17.11.2009) | US |

- (71) Applicant (for all designated States except US): CON-TOUR SEMICONDUCTOR, INC. [US/US]; 101 Billerica Avenue, Building 5, N. Billerica, MA 01862 (US).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): SHEPARD, Daniel, R. [US/US]; 186 Atlantic Avenue, North Hampton, NH (US).

- (74) Agents: FRANK, Steven, J. et al.; Goodwin Procter LLP, Exchange Place, Boston, MA 02109 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD,  $SE,\,SG,\,SK,\,SL,\,SM,\,ST,\,SV,\,SY,\,TH,\,TJ,\,TM,\,TN,\,TR,$ TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

[Continued on next page]

(54) Title: THREE-DIMENSIONAL MEMORY ARRAY COMPRISING VERTICAL SWITCHES HAVING THREE TERMI-**NALS**

FIG. 27A

(57) Abstract: A memory device includes a substrate, and, disposed thereover, an array of vertical memory switches. The switches are for example transistors or four-layer diodes (e.g. thyristors). The switches are connected to an overlying memory material, e.g. phase-change material, resistance-change material or one-time-programmable material.

#

(84) Designated States (unless otherwise indicated, for every Published: kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

# THREE-DIMENSIONAL MEMORY ARRAY COMPRISING VERTICAL SWITCHES HAVING THREE TERINALS

#### Cross-Reference to Related Applications

[001] This application claims priority to and the benefit of U.S. Provisional Patent

Application No. 61/209,725, filed on March 10, 2009; U.S. Provisional Patent Application No. 61/273,163, filed on July 31, 2009; U.S. Provisional Patent Application No. 61/275,169, filed on August 26, 2009; and U.S. Provisional Patent Application No. 61/281,388, filed on November 17, 2009. The entire disclosure of each of these applications is incorporated by reference herein.

10 <u>Technical Field</u>

[002] In various embodiments, the present invention relates to arrays of switches utilized in memory devices, and more particularly to arrays of transistors that have a high packing density for use in memory devices.

15 <u>Background</u>

20

25

30

[003] As advances continue to be made in the area of semiconductor memory devices, high capacity and low cost are increasingly important. In particular, memory cell designs having small footprints are increasingly desired to provide high density. For this reason, diode arrays are increasingly finding utility in memory designs. However, because of leakage currents in diode arrays, increasingly large arrays often result in non-negligible total leakage currents. These leakage currents may grow geometrically with the size of the array, resulting in higher power consumption. U.S. Patent No. 7,376,008 ("the '008 patent") describes this cumulative leakage problem in detail, and the entire disclosure thereof is incorporated by reference herein. To deal with this leakage problem, diode array memories can be broken down into multiple tiles or sub-arrays such that only a portion of the entire array is energized at a given point in time. However, each sub-array or tile typically requires some peripheral support circuitry and, as a result, will contribute to a reduction in array efficiency. The '008 patent addresses this problem through the use of current-level switching devices (CLSDs) and describes that when only a single row and a single column are energized, with the remaining (i.e., non-selected) rows and columns floating, the total current leakage grows only linearly with the size of the array. However, CLSDs switch when a voltage level is exceeded and, as such, have analog characteristics — i.e., they are not purely digital devices. Many memory-design engineers are skilled in digital logic design, but fewer engineers are trained in analog design. Thus, the increasing use of CLSDs leads to increased design complexity, time, and expense.

- 2 -

**[004]** Thus, a device more digital than CLSDs that facilitates low power consumption by minimizing leakage currents is highly desirable. Furthermore, such a memory device should be inexpensive to manufacture and should utilize existing manufacturing tools and techniques while avoiding the use of materials that might contaminate manufacturing equipment.

5

10

15

20

25

30

#### **Summary**

[005] Embodiments of the present invention include memory arrays having substantially the same packing density as a diode array, and techniques for their manufacture. Some embodiments utilize vertical switches, such as MOS transistors, that may be tightly packed into an array for information-storage applications. Embodiments of the present invention are useful for many information-storage technologies that require a memory cell having a switchable current path and high packing density. Specifically, embodiments of the invention yield a terabit memory array on a single die. Furthermore, some embodiments of the present invention include conductive strapping features that help to compensate for the series resistance of bit lines and/or word lines in order to provide greater current to a given memory cell while requiring lower supply voltages.

[006] Embodiments of the invention may include peripheral and/or support logic. This logic may include transistors built with a vertical orientation and/or built at the same time as the transistors in the high-density storage array. The logic circuitry may utilize transistors wired in series to withstand higher voltages or transistors wired in parallel to accommodate higher currents. It may comprise transistors that are drawn on a mask or reticule to provide for larger features for greater channel widths and, thereby, higher currents. Embodiments of the invention may include self-aligned features, and may include implantation or other doping techniques to form source layers, channel layers, and/or drain layers.

[007] Memory arrays fabricated in accordance with the present invention may be programmed with data including or consisting essentially of music, video, computer software, a computer application, reference data, text, and/or a diagram. The memory array may be disposed within a removable memory storage device. The memory array may include or consist essentially of a plurality of storage cells, at least one of which may include or consist essentially of a phase-change material. The data typically includes error-correcting bits, but might not in some cases.

[008] Embodiments of the invention are implemented with silicon or silicon-based materials; however, other semiconducting materials may also be utilized, including III-V semiconductors, organic semiconductors, field-emitting devices, and the like. Embodiments of the invention may

- 3 -

be implemented in conjunction with various information storage materials and techniques including resistive change materials, phase-change materials, magnetic materials (for MRAM), one-time programmable (OTP) materials such as a fuse or anti-fuse material, charged oxide materials, trapped charge devices, and many other programmable materials.

5

10

15

20

25

30

[009] Embodiments of the present invention also relates to the manufacture and processing of semiconductor devices, and more particularly to methods for fabricating three-dimensional memory devices having a programmable element that is self-aligned. Representative types of programmable elements for memory cells include phase-change materials, such as chalcogenide alloys, and resistive-change materials. These and other materials are switched from one stored data state to another by heating the material, which is accomplished by passing a current through the material. To effectively heat the material without passing excessive current (and thereby consuming considerable power), the current may be forced through a constricted area in order to increase the current density through that area and the concomitant heating. In addition, memory cells in accordance with embodiments of the invention may be one-time programmable (OTP) or multiply programmable or rewritable, and may alternatively include fusible or antifusible materials.

**[0010]** Embodiments of the present invention also include methods of processing a semiconductor device such that a constricted area is formed at the junction of a contacting material and a programmable-element material or at the junction of two portions of the programmable-element material. Embodiments include memory cells having multiple storage bits per cell, including cells having one to eight bits per cell or even more.

[0011] Embodiments of the present invention also include methods for forming features (such as conductive posts) between other features separated by the minimum dimension of the lithographic techniques utilized to form the device. Embodiments include methods for processing a programmable-element portion of a memory cell such that the programmable material is not exposed to high temperatures that might damage it, even that programmable material utilized in stacked or three-dimensional memory variants. Embodiments also include methods for forming memory cells having one or more layers of programmable elements, where at least of the layers has one or more programmable elements, and where one or more of the elements has two or more programmable states. Thus, the number of bits of information per memory cell is a function of the number of layers, the number of programmable elements per layer, and the number of programmable states per element. For example, a memory cell having eight layers per cell, two elements per layer, and four states per element (two bits per element)

has 32 bits per cell.

5

10

15

20

25

30

**[0012]** Embodiments of the present invention include methods for constructing a memory cell having an active device in the substrate (e.g., a transistor, a thristor, a nonlinear current-steering device such as a diode, a field emitter, or the like) that is shared by multiple programmable elements. The cell may have one or more layers of such programmable elements.

**[0013]** In an aspect, embodiments of the invention feature a memory device that includes a substrate, and, disposed thereover, an array of vertical memory switches each having at least three terminals and a cross-sectional area less than  $6F^2$ . Each memory switch may have a cross-sectional area less than approximately  $4F^2$ . At least one of the memory switches includes or consists essentially of a MOS transistor or a four-layer diode. At least two memory switches may share a common gate for operating the channel of each of the memory switches.

**[0014]** The device may include two interleaved pluralities of bit lines for selecting a memory switch, one plurality of bit lines being connected to a first selection circuit on a first side of the array of memory switches and the other plurality of bit lines being connected to a second selection circuit on a second side of the array opposing the first side. The device may include a first array of programmable memory elements disposed over the array of memory switches. Each memory element in the first array may be electrically connected to at least one of the memory switches through a conductive post. A second array of programmable memory elements may be disposed over the first array. Each memory element in the second array may be electrically connected to at least one of the memory switches through a conductive post. At least one, or even each, of the memory elements in the first array may include or consist essentially of a phase-change material, a resistive-change material, and/or a one-time-programmable element. Peripheral circuitry including or consisting essentially of a plurality of vertical MOS transistors may be electrically connected to the array of memory switches. F may be less than approximately 25 nm. Each vertical memory switch may correspond to a single bit or to a plurality of bits.

[0015] In another aspect, embodiments of the invention feature a method of forming a memory device. A substrate is provided, and a source layer is formed on the substrate. A channel layer having a doping type different from the doping type of the source layer is formed over the source layer. A drain layer having a doping type different from the doping type of the channel layer is formed over the channel layer. The source, channel, and drain layers are patterned into an array of memory switches each having a cross-sectional area less than 6F<sup>2</sup>. Patterning the source, channel, and drain layers may include forming a plurality of generally parallel isolation trenches

intersecting the source, channel, and drain layers, depositing a dielectric material into the plurality of isolation trenches, and planarizing the dielectric material such that the top surface of the dielectric material is substantially coplanar with the top surface of the drain layer. Patterning the source, channel, and drain layers may include forming a plurality of generally parallel gate trenches intersecting the isolation trenches, each of the memory switches being bounded by intersecting isolation trenches and gate trenches. The isolation trenches and the gate trenches may be substantially perpendicular to each other. The cross-sectional area of each memory switch may be less than approximately  $4F^2$ .

5

10

15

20

25

30

[0016] A gate dielectric contacting the channel layer may be formed within the gate trenches, and a gate contact material may be deposited in the gate trenches. The gate contact material may be planarized such that the top surface of the gate contact material is substantially coplanar with the top surface of the dielectric material in the isolation trenches. A conductive post may be formed over a memory switch. A programmable material may be formed in contact with the conductive post, thereby forming a programmable memory cell. The programmable material may include or consist essentially of a phase-change material, a resistive-change material, and/or a one-time-programmable material.

[0017] Forming the programmable material may include or consist essentially of etching at least a portion of a dielectric material disposed around the conductive post to form a recess, at least substantially filling the recess with the programmable material, and planarizing the programmable material such that the top surface of the programmable material is substantially coplanar with the top surface of the conductive post. The conductive post may have a substantially quadrilateral (e.g., rectangular or square) cross-sectional area. The programmable may be disposed in contact with only one corner or with only two corners of the conductive post. Forming the source, channel, and drain layers each may include or consist essentially of ion implantation of dopants into the substrate and/or deposition of a semiconductor material over the substrate. The source, channel, and drain layers may be patterned into a plurality of peripheral devices disposed proximate the array of memory switches substantially simultaneously with their patterning into the array of memory switches. The peripheral devices may be electrically connected to the array of memory switches.

[0018] In yet another aspect, embodiments of the invention feature a memory device including a substrate defining a die, and, disposed over the substrate within the die, an array of vertical memory switches. Each of the vertical memory switches may have at least three terminals. The array of vertical memory switches may define a memory array of at least one terabit. Each

WO 2010/104918

5

10

15

20

25

vertical memory switch may correspond to a single bit or to a plurality of bits. The die may have an area of approximately 1 cm<sup>2</sup>, and the memory array may have at least 5 terabits of storage capacity. At least one memory switch may include or consist essentially of a MOS transistor and/or a four-layer diode. At least two memory switches may share a common gate for operating a channel of each of the memory switches.

**[0019]** In a further aspect, embodiments of the invention feature a memory device including a vertical conductor disposed over a substrate, a switch for selecting the vertical conductor, and a plurality of layers, each layer comprising a plurality of programmable memory elements and being disposed over and electrically connected to the vertical conductor. The layers may be stacked vertically, and/or the vertical conductor may extend through each of the layers. The switch may include or consist essentially of a vertical memory switch having at least three terminals and a cross-sectional area less than  $6F^2$ . At least one of the programmable memory elements may include or consist essentially of a phase-change material, a resistive-change material, and/or a one-time-programmable element.

[0020] In still another aspect, embodiments of the invention include memory devices comprising a first set of parallel rows of memory cells connected together; a second set of parallel rows of memory cells connected together; and a control conductor selectable to activate at least one of the rows of the first set and at least one of the rows of the second set. Selection of (i) one of the sets, and (ii) at least one of the rows by the control conductor, causes activation of at least one row of memory cells.

#### Brief Description of the Drawings

[0021] In the drawings, like reference characters generally refer to the same parts throughout the different views. Also, the drawings are not necessarily to scale, emphasis instead generally being placed upon illustrating the principles of the invention. In the following description, various embodiments of the present invention are described with reference to the following drawing, in which:

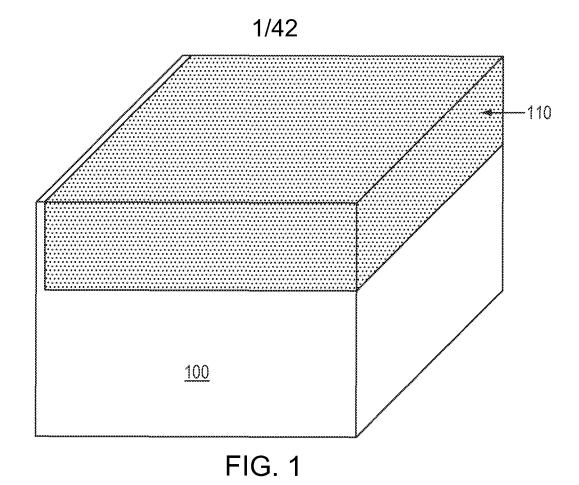

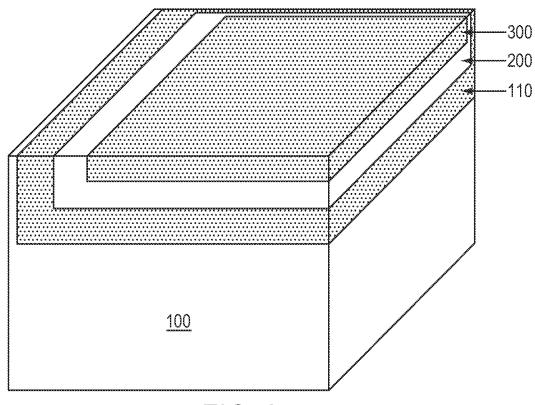

- [0022] FIG. 1 is a schematic perspective view of a substrate following a first dopant implant in accordance with various embodiments of the invention;

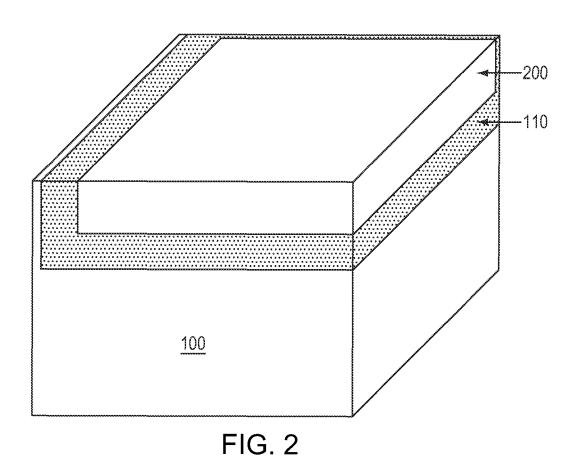

- 30 **[0023]** FIG. 2 is a schematic perspective view of the substrate of FIG. 1 following a second dopant implant in accordance with various embodiments of the invention;

- [0024] FIG. 3 is a schematic perspective view of the substrate of FIGS. 1 and 2 following a third dopant implant in accordance with various embodiments of the invention;

5

10

15

20

25

30

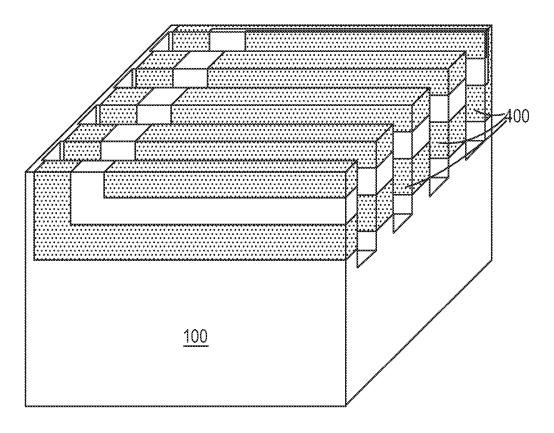

[0025] FIG. 4 is a schematic perspective view of the substrate of FIGS. 1-3 following the etching of isolation trenches in accordance with various embodiments of the invention;

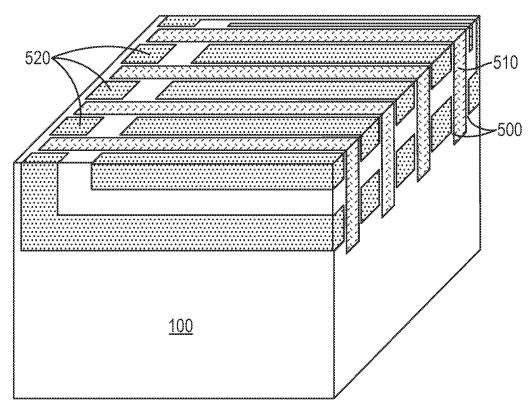

**[0026]** FIG. 5 is a schematic perspective view of the substrate of FIGS. 1-4 following (a) filling of the isolation trenches with a body contact liner and oxide and (b) planarization in accordance with various embodiments of the invention;

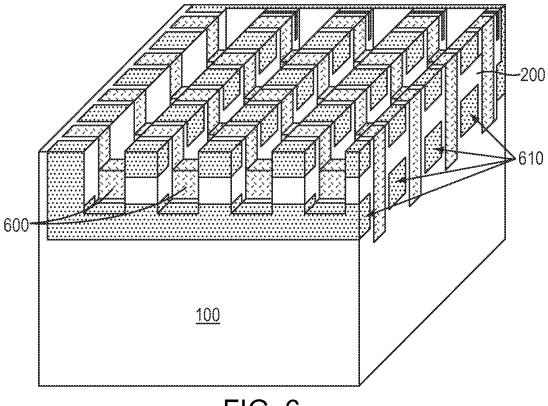

[0027] FIG. 6 is a schematic perspective view of the substrate of FIGS. 1-5 following the etching of gate trenches in accordance with various embodiments of the invention;

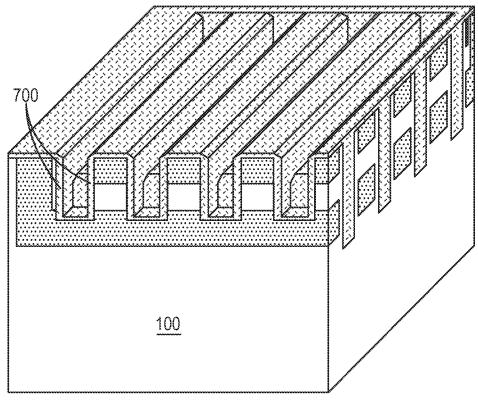

[0028] FIG. 7 is a schematic perspective view of the substrate of FIGS. 1-6 following the growing of gate oxide in the gate trenches in accordance with various embodiments of the invention;

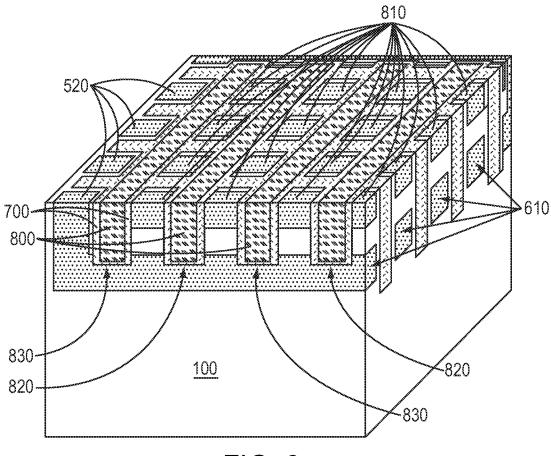

[0029] FIG. 8 is a schematic perspective view of the substrate of FIGS. 1-7 following filling of the gate trenches with polysilicon and planarization in accordance with various embodiments of the invention;

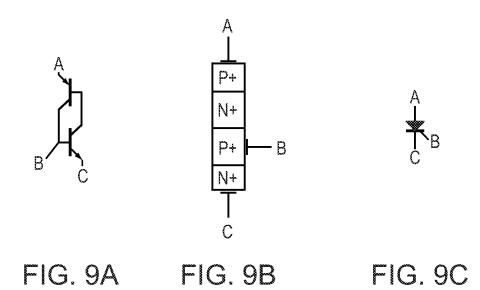

[0030] FIGS. 9A, 9B, and 9C are three symbolic representations of a four layer diode, also known as a thrystor, shockley diode, PNPN diode, or SCR;

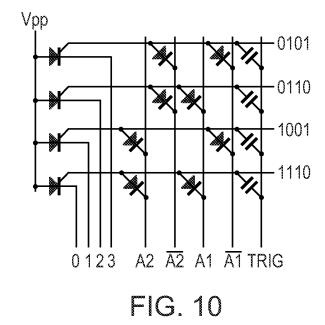

[0031] FIG. 10 is a schematic diagram of a diode decoder for disabling all but one four layer diode device in accordance with various embodiments of the invention;

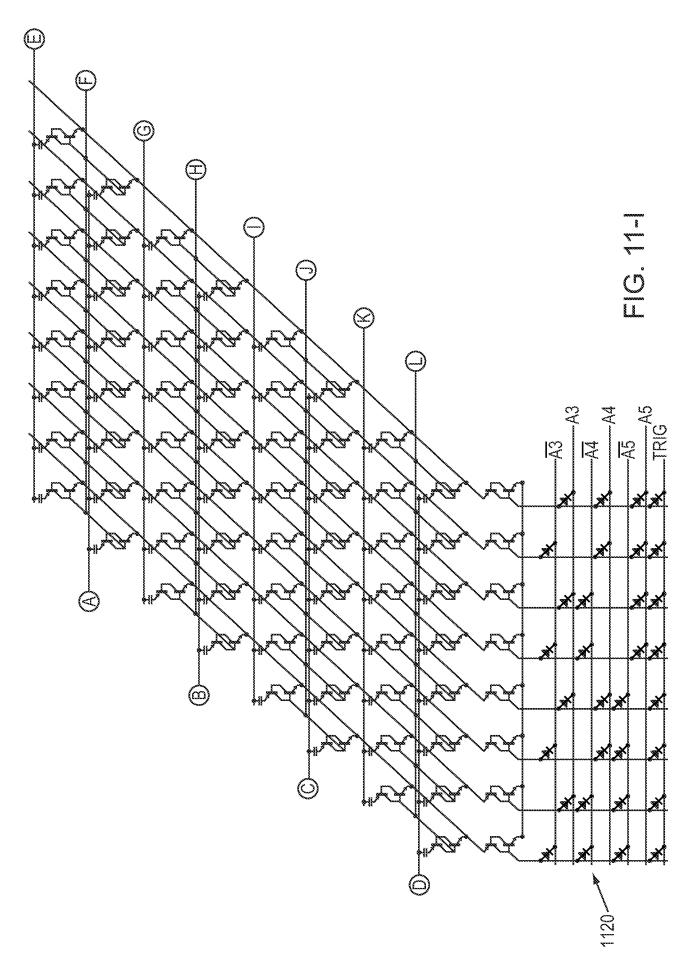

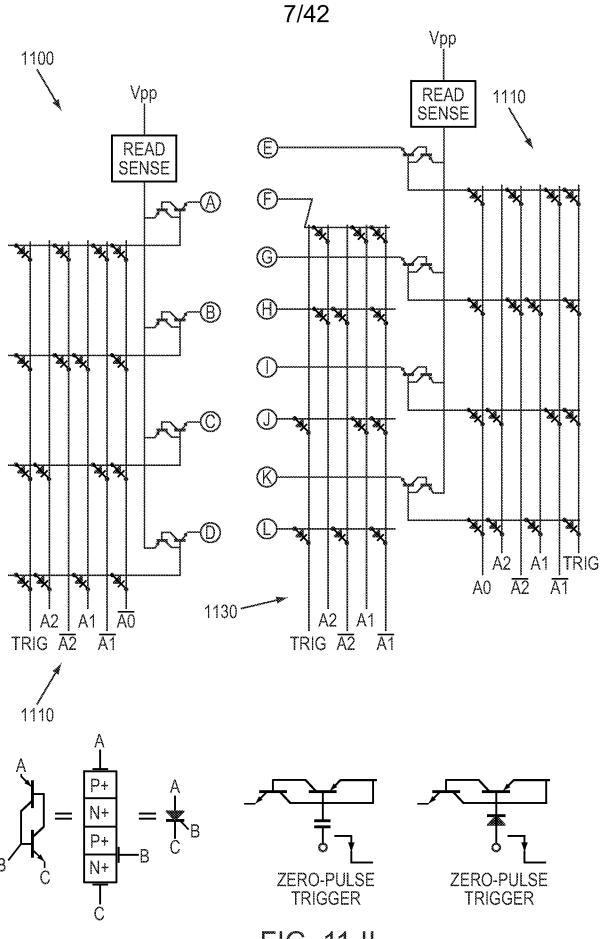

[0032] FIGS. 11-I, 11-II are schematic diagram of an 8 bit × 8 bit memory array in which row line and column line selection and memory cell enabling is performed by a diode decoder in accordance with various embodiments of the invention;

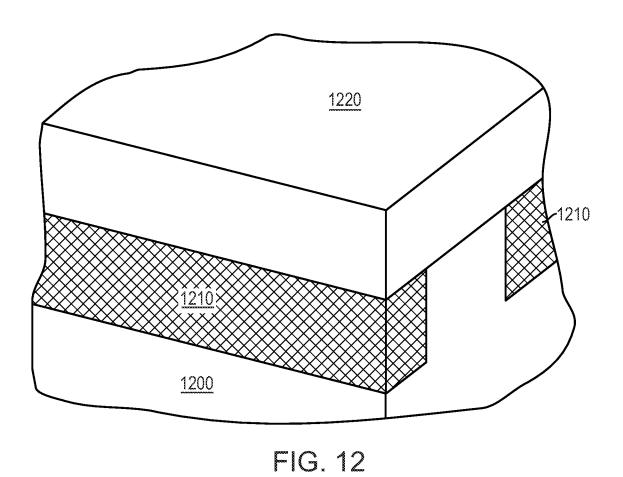

[0033] FIG. 12 is a perspective view of a portion of a memory device during fabrication following damascene formation of column lines and encapsulation with dielectric material in accordance with various embodiments of the invention;

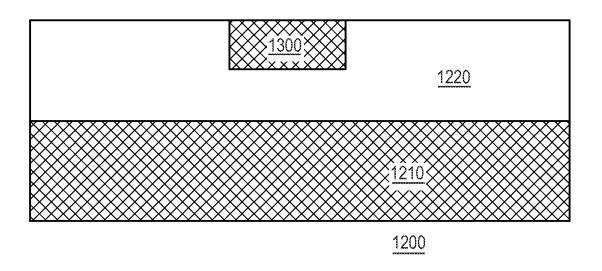

[0034] FIG. 13 is a side view of a portion of the memory device of FIG. 12 following damascene formation of an orthogonal column gate control line in accordance with various embodiments of the invention;

[0035] FIG. 14 is a side view of a portion of the memory device of FIGS. 12 and 13 following etching of two memory cell locations in accordance with various embodiments of the invention;

[0036] FIG. 15 is a side view of a portion of the memory device of FIGS. 12-14 following N+ silicon deposition in accordance with various embodiments of the invention;

[0037] FIG. 16 is a side view of a portion of the memory device of FIGS. 12-15 following planarization in accordance with various embodiments of the invention;

[0038] FIG. 17 is a side view of a portion of the memory device of FIGS. 12-16 following P+

20

30

silicon implant in accordance with various embodiments of the invention;

- **[0039]** FIG. 18 is a side view of a portion of the memory device of FIGS. 12-17 following deposition of P+ silicon, N+ silicon, P+ silicon, and a top contact in accordance with various embodiments of the invention;

- 5 **[0040]** FIG. 19 is a side view of a portion of the memory device of FIGS. 12-18 following pillar etch formation of active memory elements in accordance with various embodiments of the invention:

- [0041] FIG. 20 is a side view of a portion of the memory device of FIGS. 12-19 following a dielectric fill in accordance with various embodiments of the invention;

- 10 **[0042]** FIG. 21 is a side view of a portion of the memory device of FIGS. 12-20 following dielectric planarization in accordance with various embodiments of the invention;

- [0043] FIG. 22 is a side view of a portion of the memory device of FIGS. 12-21 following deposition and patterning of the top metal into row lines in accordance with various embodiments of the invention;

- 15 **[0044]** FIG. 23 is a side view of a portion of the memory device of FIGS. 12-22 following deposition and alternate patterning of the top metal into row lines in accordance with various embodiments of the invention;

- **[0045]** FIG. 24 is a side view of a portion of the memory device of FIGS. 12-23 following via connection formation for a top-metal-to-bottom-metal contact and formation of P-N junction devices for decoder diodes in accordance with various embodiments of the invention;

- **[0046]** FIG. 25 is a side view of a portion of the memory device of FIGS. 12-24 following formation of exemplary programmable resistive-change cells in accordance with various embodiments of the invention;

- [0047] FIG. 26 is a side view of a portion of the memory device of FIGS. 12-24 following formation of exemplary one-time programmable (OTP) antifuse cells in accordance with various embodiments of the invention;

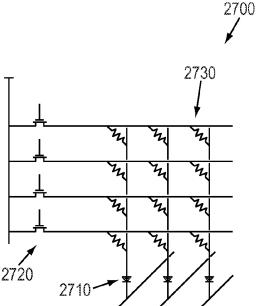

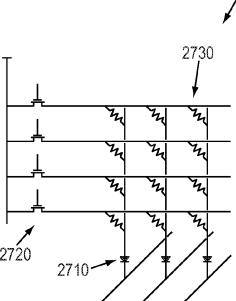

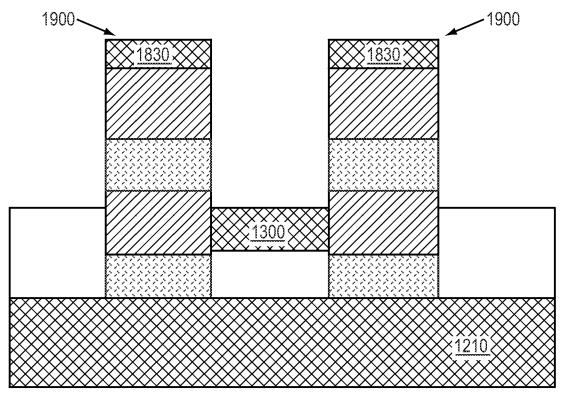

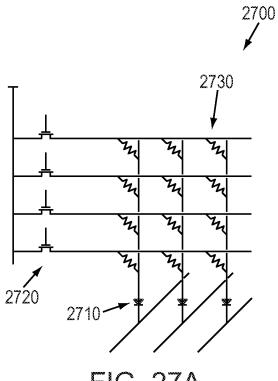

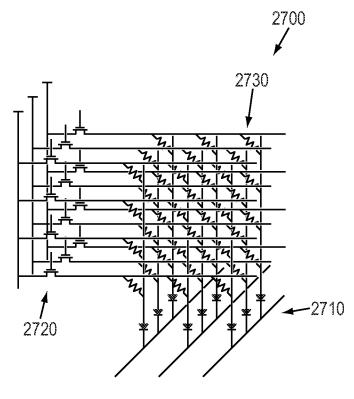

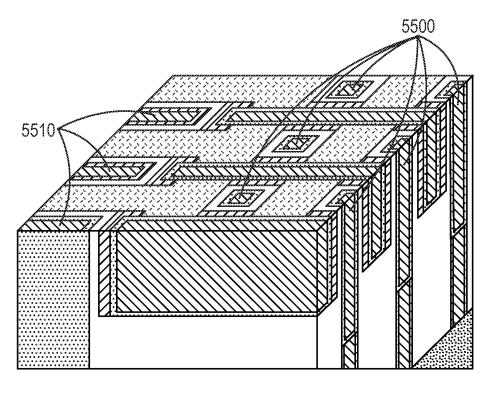

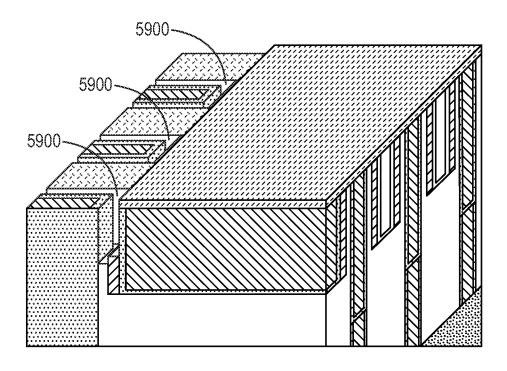

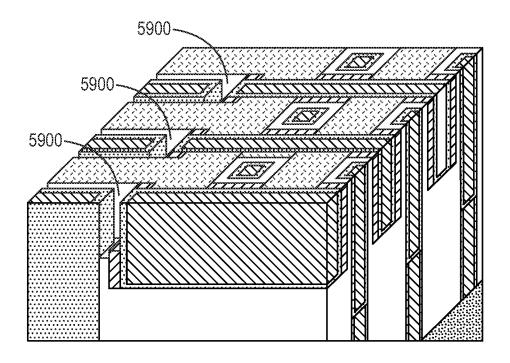

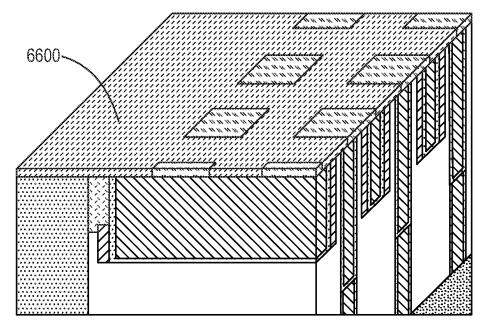

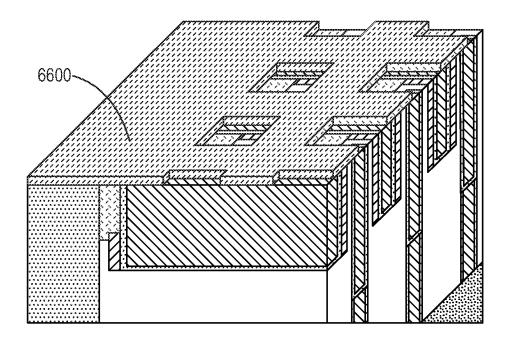

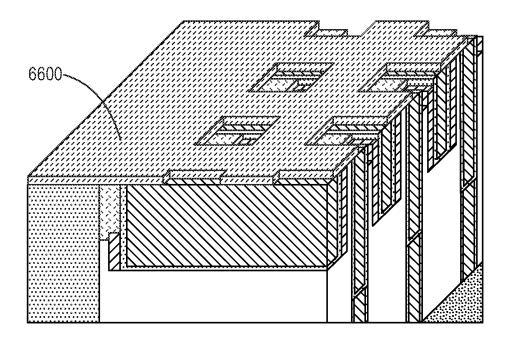

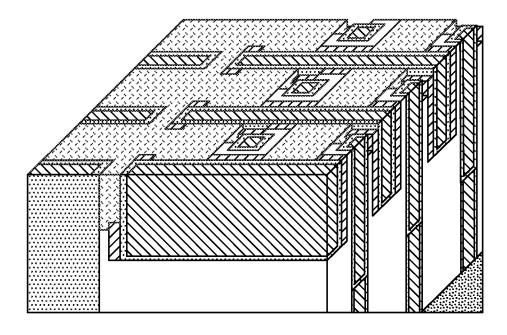

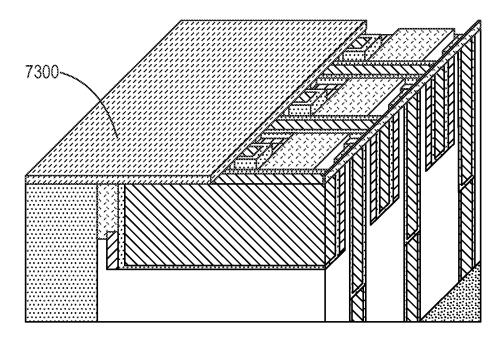

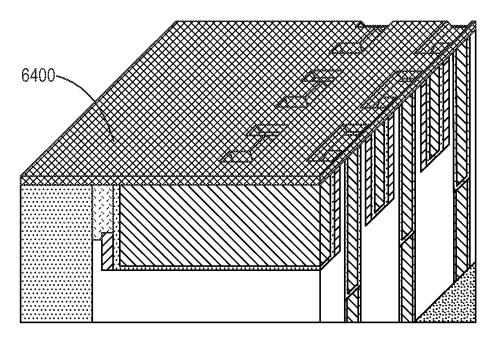

- [0048] FIGS. 27A and 27B depict partial circuit schematics for memory elements in a vertical third dimension according to various embodiments of the present invention;

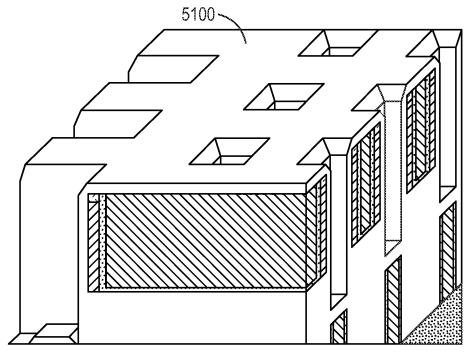

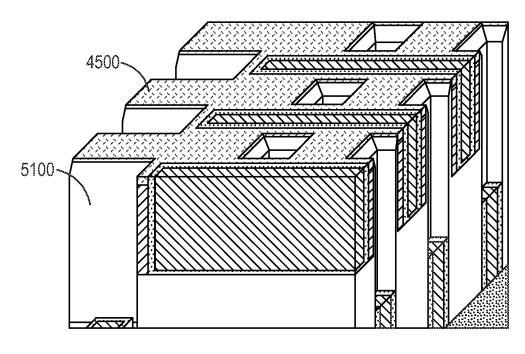

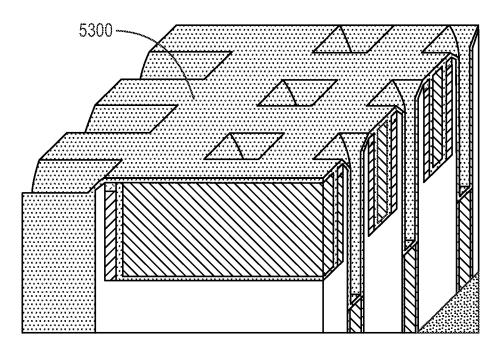

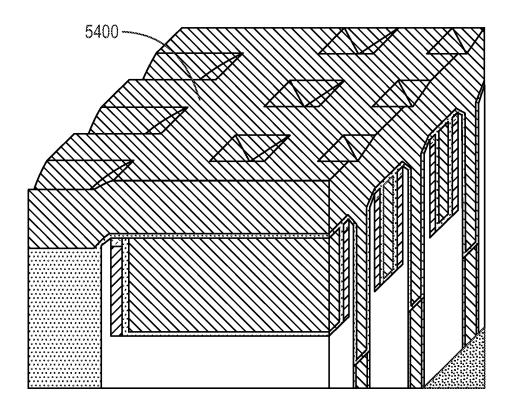

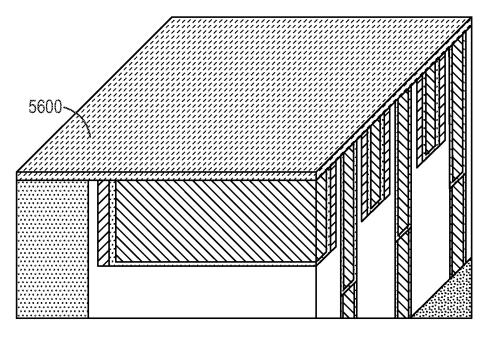

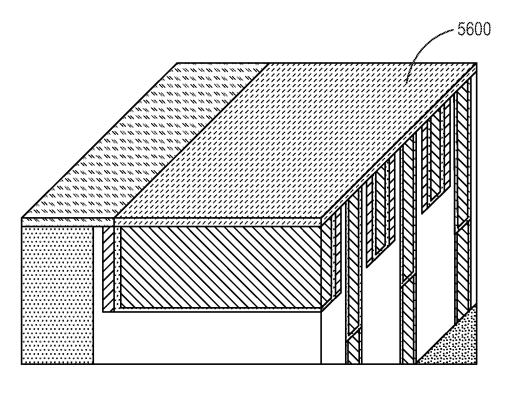

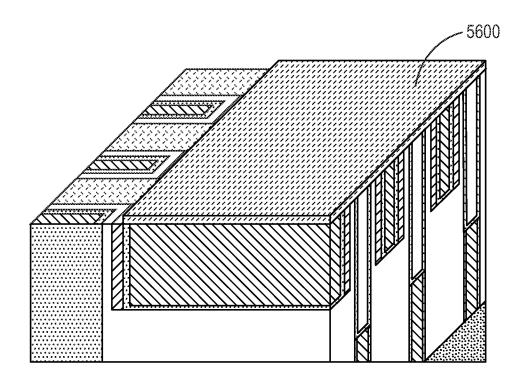

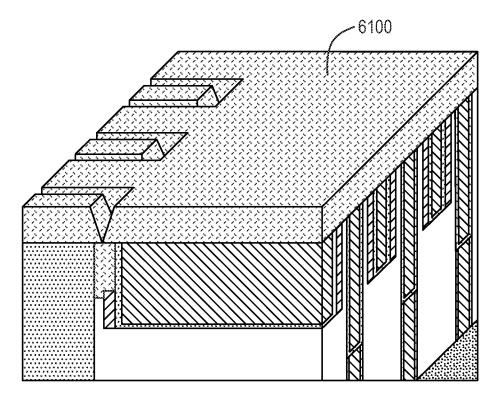

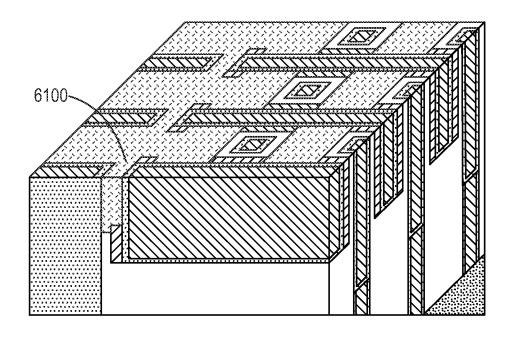

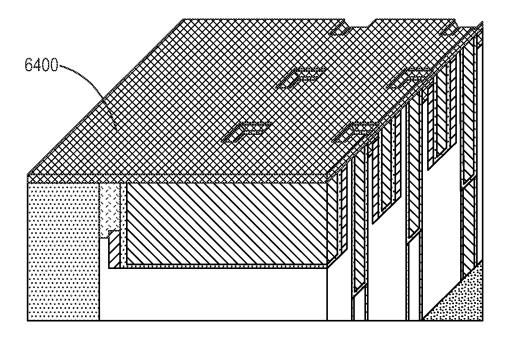

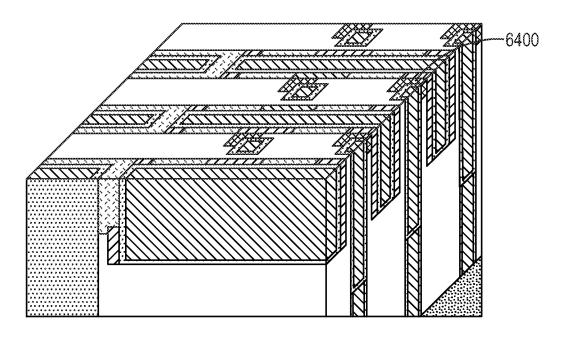

- [0049] FIGS. 28-65 are perspective views of memory elements being fabricated according to various embodiments of the present invention at various stages during the fabrication process;

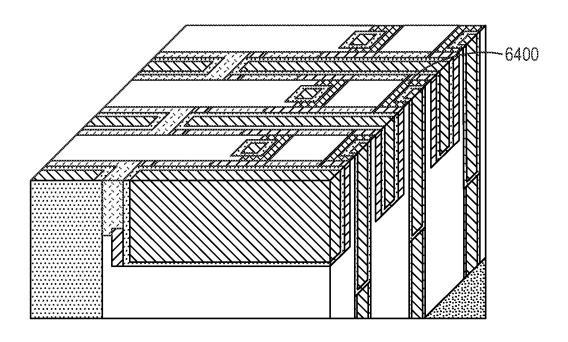

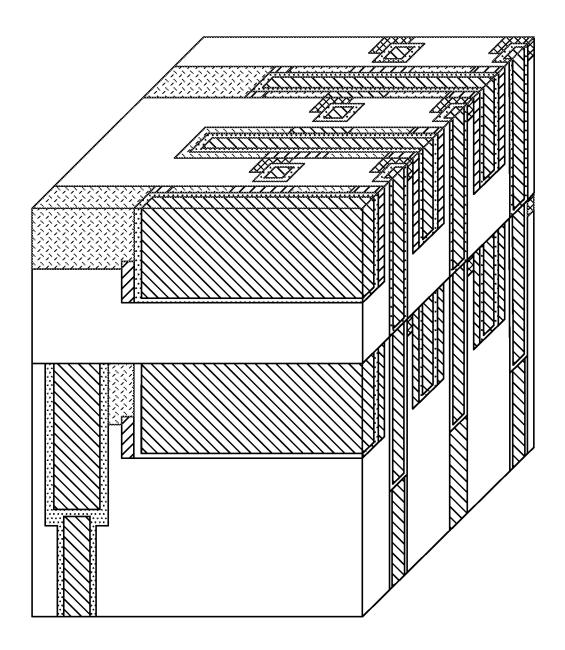

- [0050] FIGS. 66-72 are perspective views of memory elements being fabricated according to various embodiments of the present invention at various stages during the fabrication process;

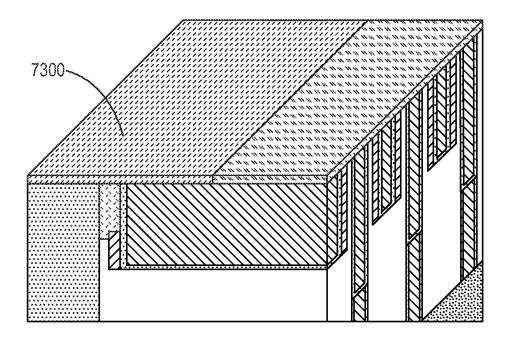

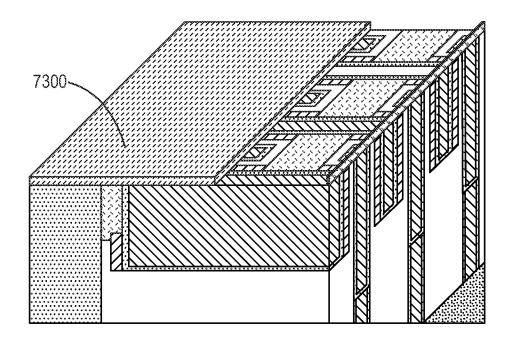

- [0051] FIGS. 73-78 are perspective views of memory elements being fabricated according to

- 9 -

various alternative embodiments of the present invention at various stages during the fabrication process; and

[0052] FIG. 79 is a perspective view of a memory device including stacked layers of memory elements fabricated in accordance with various embodiments of the invention.

5

10

15

20

25

30

#### **Detailed Description**

[0053] Embodiments of the present invention may be fabricated using standard techniques and equipment, and include arrays of memory switches each having a "footprint" (i.e., cross-sectional area) no larger than 4F<sup>2</sup> (where F represents the minimum feature size of a particular technology generation). In a preferred embodiment, MOS transistors are fabricated in a vertical orientation and have a center channel layer vertically surrounded by a source and drain layer. The gate (that turns on the channel) is positioned to the side of the vertically stacked device. To facilitate a higher packing density, the gate is preferably shared by two adjacent MOS devices, resulting in transistors being enabled in pairs. Final resolution of a selected memory storage element is preferably accomplished by uniquely selecting a bit line to one of the two activated transistors. Various embodiments of the present invention do not require the highest packing density or fabrication of shared-gate transistors, which may be desirable for formation of peripheral circuits to support the operation of a high-density memory array.

**[0054]** Figure 1 depicts a portion of a substrate 100, which may include or consist essentially of a semiconductor material such as silicon. One or more dopant species are introduced into substrate 100, e.g., by ion implantation, forming a first implanted layer 110. As depicted, an area is masked prior to introducing the dopant species by, e.g., photolithographic techniques. For fabrication of an array of memory cells, a single large-geometry mask may be used to outline the memory cells as well as the connections to the ends of the word lines (as described below). First implanted layer 110 will also be referred to herein as the "source layer."

[0055] Referring to Figures 2 and 3, second and third implanted layers 200, 300 are formed in portions of substrate 100 by, e.g., photolithographic masking and ion implantation of one or more dopant species as described above with reference to first implanted layer 110. Second implanted layer 200 will also be referred to herein as the "channel layer," and third implanted layer 300 will also be referred to herein as the "drain layer."

[0056] As an alternative embodiment to that depicted in Figures 1-3, the dopants defining first, second, and third implanted layers 110, 200, 300 may be blanket-implanted in sequence. In such an approach, extra steps (as will be clear to those skilled in the art) will generally be required to

make the appropriate connections to the end of the word line connections. For example, one may implement an etch that is timed to land within the desired (e.g., source) layer along with insulating layer to prevent that connection from also contacting the middle (e.g., channel) and topmost (e.g., drain) doped layers. A suitable insulating layer may be formed by conformal dielectric deposition and etch-back as is done with a spacer formation. Additional alternatives for the formation of first, second, and third implanted layers 110, 200, 300 include epitaxial growth of the layers with in-situ doping of the layers, thin-film deposition of doped layers, or any other combination of growth, deposition, and/or implantation.

5

10

15

20

25

[0057] Trenches 400 are then etched into substrate 100 as depicted in Figure 4. These trenches are for isolation, e.g., shallow trench isolation (STI), of the transistors formed along the word lines. Trenches 400 are typically etched such that they extend through the drain layer 300, the channel layer 200, and the source layer 110, and into the bulk of substrate 100. Trenches 400 are typically formed at the finest or critical geometry of the lithography used to maximize the packing density of the device being fabricated.

**[0058]** In a traditional lateral MOS fabrication, the channel area is generally connected to the semiconductor bulk of the substrate. To provide such a connection in embodiments of the present invention, as depicted in Figure 5, a thin liner layer 500 (which may be doped similarly to the bulk of the substrate 100 and/or to the channel layer 200) is deposited by, for example, chemical vapor deposition (CVD) or another generally conformal process, and is typically in-situ doped. However, this connection to the substrate bulk (liner layer 500) is optional; if omitted, fabricated transistors may have characteristics similar to planar thin-film transistors (TFT) or silicon-on-insulator (SOI) transistors. Following the deposition of optional liner layer 500, the trenches 400 are filled with a dielectric material 510 (which may include or consist essentially of, e.g., SiO<sub>2</sub>), and the result is polished by, e.g., chemical-mechanical polishing (CMP), to isolate trenches 400 and to expose the drain 300 and the ends of the word lines 520. (Omission of the liner layer 500 is more preferable as devices are scaled to smaller dimensions, as the number of atoms of thickness of such a liner layer relative to the number of dopant atoms necessary to achieve a particular doping profile may become an issue. Nonetheless, the figures depict an embodiment including liner layer 500.)

30 **[0059]** Finally, as depicted in Figure 6, gate trenches 600 are formed by, e.g., etching. Gate trenches 600 preferably reach the bottom of the channel layer 102 and may be over-etched slightly into the source layer 110. However, the word lines 610 in the source layer 110 should not be severed by the etch of gate trenches 600, and excessive over-etching is generally avoided

- 11 -

in order to maintain low resistivity in word lines 610.

5

10

15

20

25

30

[0060] A variation to either connecting the channel layer to the substrate or omitting that connection in a TFT approach is to form the gate trenches in two steps. Specifically, in this variation, the STI trenches are filled with dielectric (without a liner to connect to the substrate) and the gate trenches are patterned and etched and filled in two separate sequences of steps. The first sequence of steps in forming the gate trenches is to pattern and etch out the trenches corresponding to the alternate gate-like lines 830 and filling them with silicon (doped generally to match the substrate), and thereupon connecting these silicon-filled, gate-like lines to the substrate. The second sequence of steps in forming the gate trenches is to form the gate lines as described above. In this variation, during operation, the gate-like lines have no other connection. [0061] Referring to Figures 7 and 8, following the etch of gate trenches 600, a gate oxide 700 is grown on the exposed silicon surfaces, and the remainder of each gate trench 600 is substantially filled with gate polysilicon 800. The substrate 100 is planarized, e.g., by CMP, to remove any gate polysilicon and any gate oxide remaining on the surface above the gate trenches 600. As shown in Figure 8, each transistor 810 in the depicted array of transistors occupies an area equal to  $2F \times 2F$  (i.e.,  $4F^2$ ) or less. Since laterally constructed MOS transistors typically require a footprint of at least  $3F \times 2F$  (i.e.,  $6F^2$ ), this is a significant area savings.

[0062] Alternatively, again referring to Figures 7 and 8, following the etch of gate trenches 600, other gate dielectric materials may be deposited or grown, in addition to or in the place of gate oxide 700, e.g., materials derived from hafnium, aluminum, tantalum, silicon, and the like. These alternative gate dielectric materials may include or consist essentially of (but are not limited to) HfO<sub>2</sub>, HfN, Al<sub>2</sub>O<sub>3</sub>, AlN, TaN, Ta<sub>2</sub>O<sub>5</sub>, other high-κ dielectrics, and the like. Furthermore, the remainder of each gate trench 600 may be substantially filled with metal gate material or other gate material in place of or in addition to gate polysilicon 800. Such alternative gate materials may be deposited or grown by sputtering, thermal or e-beam evaporation, CVD (in its various forms), ALD, or the like.

[0063] In an embodiment, the transistors 810 are NMOS devices (and thus, the substrate 100 is doped P-, the source and drain layers 110, 300 are doped N+ and the channel layer 200 is doped P-) and (as pictured) the bottom N+ region is the source and the top N+ region is the drain. In operation, substrate 100 is generally at the lowest voltage (typically ground or a small negative voltage) and all of the word lines 610 and all of the gate lines 820 are biased to a voltage v. To select a memory cell, the voltage on the word line on which the memory cell is connected is lowered (e.g., to  $v - V_{th}$  where  $V_{th}$  is the turn-on threshold voltage of the transistor 810), and the

gate line 820 passing next to the memory cell is raised (e.g., to  $v + V_{th}$ ). This will result in a gate-to-source voltage greater than  $V_{th}$  (e.g., a voltage of about  $2V_{th}$ ) being placed on the device and the two transistors on the selected word line that are also on either side of the asserted gate line may be switched on. In a preferred embodiment, the bit lines (not depicted in Figure 8) will exit the array on two sides; the even-numbered bit lines will exit to one side and the odd-numbered bit lines will exit to the other. In this way, only one of the two above-referenced transistors will be active; which transistor is active is determined by which side of the array the active bit line comes from. The gate lines 820 include every other gate line, as the gates are shared by pairs of memory devices. Thus, the alternate gate-like lines 830 may act as additional isolation between device pairs and may be left floating or may be connected to a bias voltage (e.g., equal to the substrate bias voltage).

5

10

15

20

25

30

[0064] In one embodiment, drain 300 of the memory cell NMOS transistor 810 is connected to a word line 610. In this way, all of the unselected word lines (as well as the substrate 100) may be kept at ground potential. To select a word line 610, the voltage on that word line 610 is raised. This approach minimizes current leakage, as only one word line 610 is biased to a voltage different from the substrate, resulting in the word-line-to-substrate junction being reverse biased (with a concomitant low leakage current). All of the unselected word lines 610 are biased to the same potential as the substrate and exhibit no current leakage. The corresponding bit line selection has the unselected bit lines biased to a small positive voltage such that the selected bit line is pulled to a lower potential (e.g., ground potential or the potential of the substrate). If transistors 810 are PMOS transistors, the above voltage polarities may simply be reversed to achieve the same result.

[0065] Embodiments of the present invention include conductive strapping features that help to compensate for the series resistance of bit lines and/or word lines in order to provide greater current at a given memory cell while requiring lower supply voltages. To add strapping to reduce the resistance of the word lines, word line contacts 520 may be intermittently placed along the length of the word lines 610 (e.g., every 16 or 32 or 64 memory cells or the like) and then connected to a metal word line conductor running above and parallel to each word line 610. In this manner, the resistivity of the doped silicon word line 610 is offset by a parallel, more conductive metal word line and only a short resistive segment (from the closest strapping connection between the doped word line 610 and the parallel metal word line to the targeted memory cell) is on the conduction path. Similarly, strapping may be added to the gate lines. The strapping preferably does not interfere with the positioning of the storage elements and the

- 13 -

bit lines. Since the bit lines run parallel with the gate lines, the gate line strapping may be placed below the bit lines; however, the word line strapping is still preferably located above the memory elements and the bit lines (to avoid colliding with the storage elements that connect between the bit lines and the tops of the transistors 810). The spacing on either side of the word line strapping contact vias may optionally be sized larger than the critical geometry along the direction of the word line 610 without a significant loss of array density. The gate line strapping may optionally be formed directly on the gate line poly, thus eliminating the need for the drop-down connections, and the gate-line material may include or consist essentially of a higher conductive material such as metal and/or be made taller.

5

10

15

20

25

30

[0066] Peripheral circuits including vertical MOS transistors may be fabricated simultaneously with the vertical transistors of the storage cells. By fabricating these peripheral transistors at substantially the same time as the storage cell transistors 810, a lower manufacturing cost may be achieved. These peripheral transistors may also be wired together to achieve additional electrical properties such as higher current passing ability, greater capacitance, or the like. The peripheral transistors may also be laid-out with a larger area for wider transistor channels for higher current carrying capacity. Two or more transistors in series may equate the performance of a higher voltage transistor by acting as a voltage divider and sharing the voltage drop across them. The channel length of such transistors is determined by the thickness of the channel layer 200.

[0067] An alternate embodiment of the present invention, as suggested above, excludes the sequence of masking and implanting in favor of creating an initial substrate having the requisite layers of doped materials (that define layers 110, 200, 300) through blanket techniques. For example, these layers may be formed by epitaxial deposition. Once the layers are deposited, the STI trenching and other subsequent etches may be performed with the inclusion of additional steps for creating contacts 520 to the layer 110. This may be accomplished by etching openings to a depth where layer 110 is exposed at those locations where contacts 520 are desired; these openings may then be filled with conductive material, such as heavily doped semiconductor material (doped to the same type, N or P, as the layer to be contacted) or metal (optionally with appropriate surface doping to make the contact ohmic). In a further variation, areas of the substrate 100 may be etched and then refilled utilizing epitaxial deposition. In this case, the deposited layers may be doped differently in certain areas in order to enable the fabrication of different device types on a single substrate (e.g., vertical NMOS plus vertical P-i-N diodes or vertical PMOS and vertical NMOS). The layers may be formed by implantation and/or epitaxy.

Once the areas of layered doping are created, if the bottom conductive layers 110 are at the same

- 14 -

depth for two or more areas, those areas may be processed in parallel (i.e., the orthogonal trenches etched and filled with STI and/or gate poly). If a combination of vertical MOS and diodes is created, the "gate" material on both sides of the diodes may be biased to a set voltage that enables normal diode operation.

5

10

15

20

25

30

#### Alternative Switching Devices

[0068] Various embodiments of the present invention utilize switching devices different from the vertical MOS transistors described above. One example is the threshold triggered device, such as the four-layer diodes described in U.S. Patent No. 7,376,008, the entire disclosure of which is incorporated herein by reference. Figure 9 illustrates three symbolic representations of a four-layer diode, also known as a thrystor, shockley diode, PNPN diode, or SCR. Figure 9A illustrates the twin-bipolar-transistor model that may be utilized to describe characteristics of the devices utilized in embodiments of the present invention. In this model, a positive voltage (such as Vpp) is applied to the PNP transistor's emitter A and a lower voltage is applied to the NPN transistor's emitter C. In a two-terminal device (i.e., if terminal B is ignored for a moment), by raising the positive voltage, leakage current through the PNP transistor's collector to the base of the NPN transistor causes the NPN to begin to turn on. This starts to turn on the PNP transistor, forming a positive feedback loop that eventually causes the full device to avalanche and switch on. If a negative voltage (or a voltage lower than that which would occur at point B in a twoterminal version of the device) is applied to terminal B, the leakage current that causes avalanche is drawn away from the NPN transistor's base and makes avalanche more difficult (a greater positive voltage may be required at terminal A). However, if the voltage at point B is raised, this helps to turn on the NPN transistor and makes avalanche easier (a lesser positive voltage may be required at terminal A). Figure 9B illustrates a generalized silicon device structure, and figure 9C illustrates the schematic symbol of the device. Other switching type devices may also be utilized in embodiments of the present invention.

[0069] Figure 10 depicts a simplified diode-decoded, four-layer-diode switch selector. A fully decoded diode decoder has as inputs N complementary address pairs to decode one out of 2N lines. In a fully decoded diode decoder, every line to be decoded is typically connected to every address pair (either to the address line or the address complement line, but not both) by a diode. All of the decoding diodes generally face in the same direction, i.e., every address line will be connected to either the anodes or the cathodes. The complementary address pair lines are used to disable a given line in the collection of lines to be decoded and thus, a diode is present in the

5

10

15

20

25

30

- 15 -

decoder between every complementary address pair line and every line in the collection of lines to which that address line does not correspond. That is, if each of the collection of lines is uniquely numbered with one of the decoded addresses between 0 and (2N-1) inclusive, and if that unique number is written as a binary number showing both the address bit and its complement, the binary address pattern corresponding to that line will reveal the pattern of diodes to be connected between it and the complementary address lines. If the cathodes of the diodes are connected to the address lines, each one bit represents a diode. For example, if the first line in Figure 10 is line 0, the bits corresponding to this address, showing both the address and complement bits in the same order as the address lines are ordered, are 0101 (corresponding to A2,  $\overline{A2}$ , A1, and  $\overline{A1}$ ), and the diode pattern is no-diode, diode, no-diode, diode as shown in Figure 10. The diode decoder illustrated in Figure 10 pulls all lines to a low voltage except for the one being addressed. By reversing the direction of the diodes in the decoding array, one may alternatively pull all but one line to a high voltage for connecting to the base of the NPN transistor (i.e., the other internal layer of the four-layer diode) to achieve a similar effect. With either approach, the four-layer diodes may be used as the line drivers to an array. One line driver may be made to be more easily switched (while the rest are less easily switched) by applying a control voltage to the middle layer of the other four-layer diodes, making them less easily switched. Switching may also be controlled by adding a capacitively coupled trigger input. Such an input may be held low with the addresses being applied and then brought high to impose a pulse of current to each control gate line to the line drivers. Then, since all but one line is being held low through the diode-decoder array, only one control gate experiences a pulse of current and is triggered to its on state. As described below, embodiments of the present invention include a method for fabricating both the diodes of the decoders and the four-layer diodes in a unified process.

[0070] Various embodiments of the invention include programmable materials such as phase-change materials or resistive-change materials that change their programmed state by applying a voltage across that material (or, correspondingly, by causing a current of a given magnitude and duration to pass therethrough). In embodiments in which threshold devices such as four-layer diodes are utilized in a memory array including such materials, care is taken to ensure that the voltages across the four-layer diodes is not placed across the programmable material when those devices switch (thereby causing the voltage across those devices to drop). Figure 10 includes an additional input TRIG for triggering the switching of the device. The TRIG input is used to capacitively couple (as depicted, through capacitors, but reverse biased diodes may be utilized) a

- 16 -

positive pulse of current to the B terminal of the four-layer device to cause it to avalanche without placing a large voltage across the outer terminals of the device (that might be momentarily placed across the programmable material at the time of avalanche). Only one fourlayer device is switched on as a function of the complementary address inputs and the layout of the diode decoder, because the diode decoder ensures that every line but one will have a path through a diode in the decoder to a low voltage address input. This path will dissipate the capacitively coupled trigger pulse to all but the one device without a diode path to a low voltage through the diode decoder. In this manner, the desired voltage to be placed across the memory cell may be applied to Vpp (taking into account any circuit voltage drops) without having to elevate that voltage to cause triggering. Furthermore, since memory-cell reading is typically done with a low voltage and writing is done with a higher voltage, a targeted memory cell should be avalanched by a lower voltage when reading and a non-targeted memory cell should not be inadvertently avalanched by the higher voltages used during writing. In embodiments of the present invention, the desired voltage for reading or writing (or, in the case of some programmable materials, a third voltage for erasing) is applied to Vpp (taking into account any circuit voltage drops) and then the separate triggering input TRIG switches on the selected fourlayer device.

5

10

15

20

25

30

[0071] Figure 11 illustrates a schematic diagram of a simplified memory array 1100 in accordance with various embodiments of the invention for ease of explanation (in practice, arrays of much greater capacity are anticipated). In Figure 11, the four-layer devices have been drawn using the bipolar equivalent circuit of Figure 9A, but the devices are generally constructed as illustrated in Figure 9B. Figure 11 is drawn with the row decoders 1110 split with the even rows being driven from the left side of array 1100 and the odd rows driven from the right side. The columns are drawn as being all driven from the bottom of array 1100 in order to illustrate that both divided and non-divided decoders may be utilized for the rows and/or the columns. The row diode decoders 1110 are duplicated on both sides of array 1100 (except for  $\overline{A0}$  on the left and A0 on the right), and the column diode decoder 1120 is drawn below the column drivers at the bottom of the figure. Unlike previous designs, the switching control inputs for every pair of lines are tied together. The decoder 1130 for the memory cell gate control signal is drawn between the array 1100 and the right-side row drivers 1110 (the rows are decoded and driven in pairs of rows). A single row is selected by activating the gates of the memory cells in a given pair of rows, and resolving to a single memory cell as the intersection of the pair of rows triggered (by the gate pulse to the pair of rows), with the driven row (driven from either the left

5

10

15

20

25

30

- 17 -

or right side), and the driven column. In operation, the complementary address pairs are asserted (where an address bit is either pulled low for a 0 input or floating for a 1 bit) along with the TRIG input being held low. The Vpp level is applied, and the TRIG input is transitioned from low to high in order to induce a capacitively coupled voltage spike to the decoder line connected to each corresponding gate terminal of the four-layer devices (e.g., their B inputs). The TRIG inputs are typically designed to be on the far side of the diode decoder from the four-layer device, but this is only a consideration for tight geometries where the transmission of the trigger signal may propagate to the B terminal input before being fully dissipated by the low address inputs. Only the capacitively coupled spike on the single line without a diode connected to a low address input will reach and trigger its respective four-layer device. This will turn on the row driver, column driver, and memory cell at generally the same time. During a read operation, the low Vpp voltage results in a current through the array 1100 that will be sensed with a Read Sense circuit in the current path (depicted at the top of array 1100 on the row driving circuits 1110, but may be at the bottom of array 1100 at the column driving circuits 1120). During an erase or program operation, the read sense is generally ignored or switched off, and writing or erasing is controlled by the level, duration, and waveform of the Vpp voltage. Threedimenstional stacking of arrays 1100 may be accomplished as described in U.S. Patent No. 6,956,757 (the entire disclosure of which is incorporated by reference herein), where a relatively small number of signals (typically complementary address signals, Vpp, TRIG and Read Sense) are connected vertically, layer to layer.

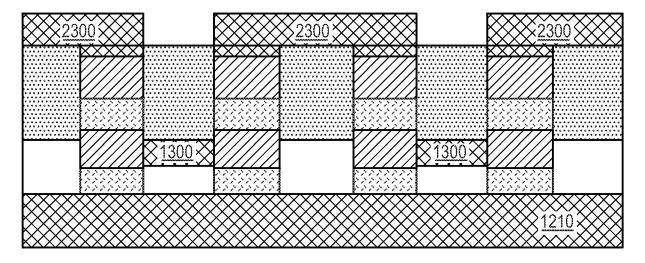

**[0072]** Manufacture of the array 1100 may be accomplished with standard semiconductor-processing techniques. Referring to Figure 12, a substrate 1200 has within it bottom metal conductors 1210. Bottom metal conductors 1210 may be fabricated by, e.g., a metal damascene process, although pattern-and-etch techniques may also be utilized. These conductor lines 1210 will typically correspond to the column lines (sometimes called bit lines) and connect to the cathode ends of the active memory cell devices. Typically, for a high-density memory device, bottom metal conductors 1210 are fabricated at the critical dimension F (also referred to as the memory half-pitch). The center-to-center distance from one such line to the next is  $2 \times F$ , or 2F. Typically, for a single bit per cell memory cell, the highest density is  $2F \times 2F$ , or  $4F^2$ . Following the formation of bottom metal conductors 1210, a layer 1220 of dielectric or non-conductive material is deposited. In accordance with various embodiments of the invention, F may be approximately 250 nm or less, approximately 180 nm or less, approximately 45 nm or less, or even

- 18 -

approximately 25 nm or less.

5

10

15

30

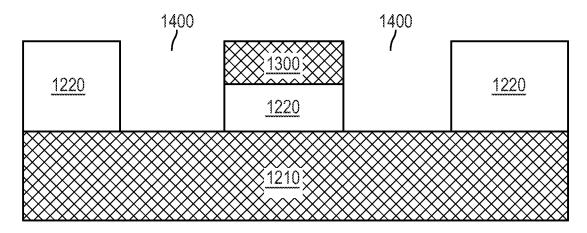

**[0073]** Referring to Figure 13, middle electrode conductor line 1300 is formed within layer 1220 by, e.g., a damascene process. In the depicted embodiment, middle electrode conductor line 1300 is orthogonal to bottom metal conductor line 1210. As discussed below, other designs and layouts may also be utilized.

**[0074]** As shown in Figure 14, holes 1400 corresponding to the active element of the individual memory cells to be fabricated (two are depicted here) are patterned and etched. The pattern may be made with two features that are each  $1F^2$  or with a single feature centered about metal line 1300 that is  $3F \times 1F$  (in which case the middle electrode conductor line 1300 metal protects the area between holes 1400 from being etched).

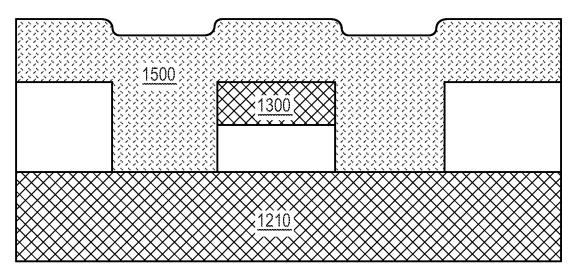

[0075] Referring to Figure 15, N+ silicon 1500 is blanket-deposited to at least substantially fill the etched holes 1400. Silicon 1500 may be polycrystalline if deposited on a bottom conductor 1300 including or consisting essentially of metal. However, bottom conductor 1300 may alternatively be made of doped silicon and substantially all of silicon 1500 may be single crystalline. In an embodiment, silicon 1500 is deposited in a selective epitaxial process in which silicon 1500 grows from the silicon surfaces exposed in the bottoms of the holes 1400. Silicon 1500 is planarized (e.g., by CMP) as shown in Figure 16. A small amount of overpolishing of silicon 1500, conductive line 1300, and layer 1220 (where exposed to the surface) is performed in some embodiments to ensure a substantially planar surface.

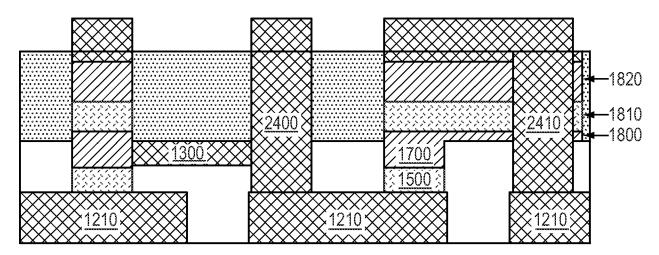

20 [0076] As shown in Figure 17, a P+ implant is used to change the doping of the upper portion of deposited silicon 1500, thus forming P+ silicon 1700. The lower boundary of P+ silicon 1700 is below the bottom edge of middle electrode conductor line 1300 such that middle electrode conductor line 1300 contacts P+ silicon 1700 but not N+ silicon 1500 (or the junction between P+ silicon 1700 and N+ silicon 1500). In another embodiment, silicon 1500 and silicon 1700 are epitaxially deposited using in-situ doping of the appropriate type.

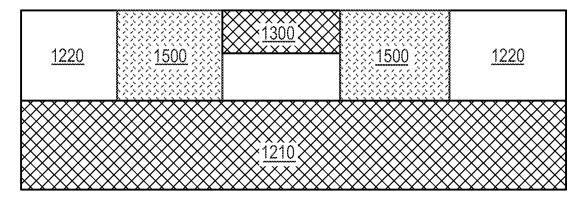

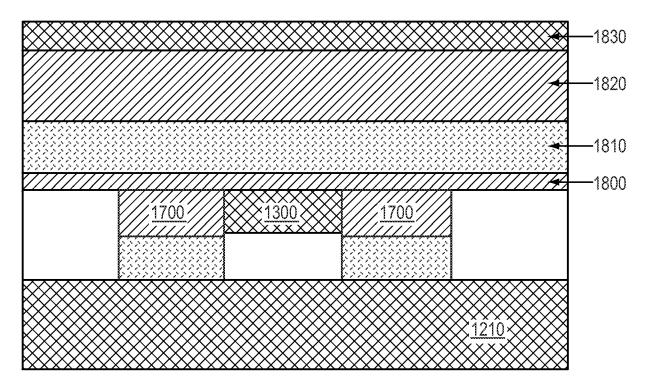

[0077] Referring now to Figure 18, layers of doped silicon and a top contact are formed. First a P+ silicon layer 1800 is deposited, followed by deposition of an N+ silicon layer 1810. The P+ layer 1800 extends the thickness of P+ silicon layer 1700 such that middle electrode conductor line 1300 contacts P+ silicon 1700 but not N+ silicon 1810 (or the junction between P+ silicon 1700 and N+ silicon 1810). A P+ silicon layer 1820 and a top contact 1830 are formed above N+ silicon 1810. The above-described layer formations may be more complex and may further comprise intervening layers of intrinsic silicon as is understood to those skilled in the art. Such layers may be deposited with a selective epitaxial growth process, particularly if silicon 1500 is

5

10

15

20

25

30

deposited with a selective epitaxial growth process. Epitaxial growth will limit leakage currents that could result in the false triggering of, or a lowered switching threshold for, the pillar device 1900 when it is an avalanching device such as an SCR, a four-layer diode, a gated four-layer diode, or the like. In various embodiments, the above-described layers include or consist essentially of materials other than silicon, e.g., other type-IV semiconductor materials, III-V semiconductor materials, or even polymeric or organic semiconductors.

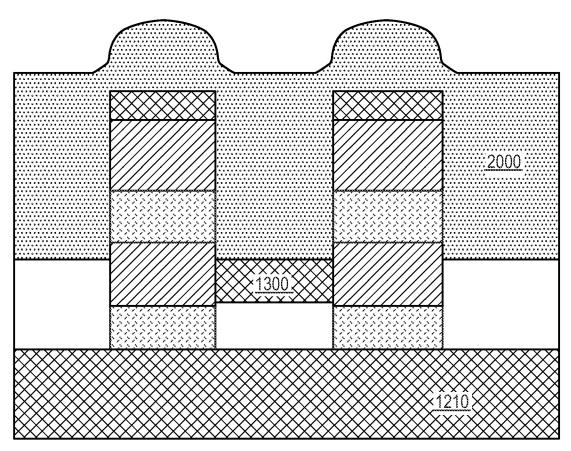

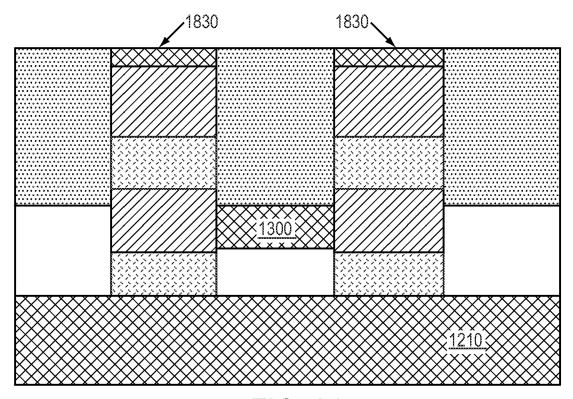

[0078] As illustrated in Figure 19, the layers are patterned and etched into individual pillars 1900, each pillar 1900 forming the active switch of a memory cell. Each pillar 1900 is generally of the size 1F<sup>2</sup>. With a spacing to the left and right of each pillar 1900 being approximately 1F, and with a spacing (not shown) in front and in back of each pillar 1900 also being approximately 1F, the memory cell has a footprint of approximately 4F<sup>2</sup>. It should be noted that the top contacts 1830 may include or consist essentially of materials and/or structures to implement programmable capability as will be described below, but for simplicity, are shown only as a simple conductive material here. As shown in Figure 20, pillars 1900 are then surrounded with a dielectric or non-conductive material 2000 that is subsequently planarized to expose contacts 1830 to the top of each memory cell (as shown in Figure 21).

[0079] The process described above produces multiple twin columns of memory cells where each pair of memory cells shares a single conductor line connecting to bottom conductor 1300 (i.e., the middle electrode of each memory cell). When this conductor line is energized, all memory devices on either side of that conductor line may be activated together, and a single cell is identified by the signals selecting (i.e., asserting with a low voltage) a single row passing below the cells (thereby reducing the number of potentially activated cells to two at the intersection of the one active row with the twin columns of memory cells) and selecting (i.e., asserting with a high voltage) a single column passing above the cells.

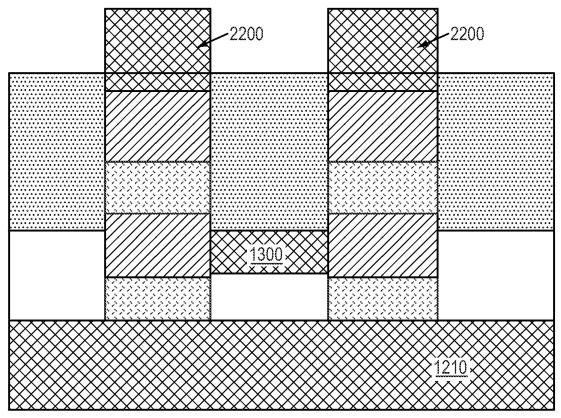

[0080] Referring to Figure 22, top column conductor lines 2200 that run in parallel with middle electrode conductor line 1300 and orthogonal to bottom metal conductor line 1210 are fabricated. One of these two top column conductor lines 2200 is energized (with a high voltage) to uniquely select a single memory cell. All other top column conductor lines (not shown) have little or no impact on circuit operation as the memory cells associated with those other top conductors are disabled by a low voltage on their middle electrode conductor lines.

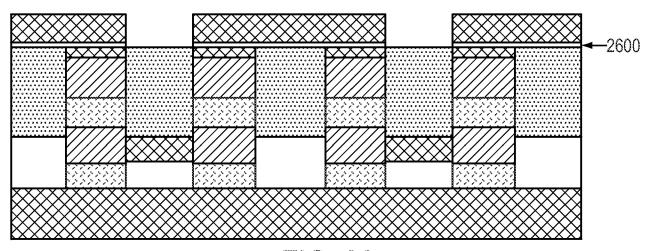

[0081] For this reason, as shown in Figure 23, as an alternative to top conductor lines 2200, top conductors 2300 may be fabricated. Top conductors 2300 each contact the tops of two columns of memory cells. As long as the two contacted columns include cells from two different twin-

cell columns (i.e., two columns not both contacted by the same conductor 1300 therebetween), a column of memory cells may be uniquely identified as being the intersection of two rows of memory cells having a common middle electrode conductor line 1300 and two rows of memory cells having a common top conductor 2300. A memory cell from this uniquely selected column of memory cells is identified by the selection of a single orthogonal row 1210 passing below it. An additional benefit of this structure is that the resistance along the length of "triple-wide" top conductor 2300 is approximately one-third that of "single-width" top conductors 2200. As a result, the voltage drop thereacross is also reduced by approximately one third, enabling use of smaller supply voltages. An embodiment of the invention implements a similar triple-wide conductor as the bottom conductor (i.e., the two conductors to the same side of a gate line) and a column of memory cells may be uniquely identified as being the intersection of two rows of memory cells having a common middle electrode conductor line 1300 and two rows of memory cells having a common bottom conductor. This may be implemented in the conductive line in the substrate or in the parallel conductive strapping lines described above.

5

10

15

20

25

30

[0082] As an alternative to triple-wide top conductors 2300, single-width top conductors 2200 may be implemented so that all of the even-numbered top conductors are wired together an exit to one side of the array, and all of the odd-numbered top conductors are wired together and exit the array to the opposite side. In this implementation, each control conductor (i.e., gate line) turns on one row of even-numbered transistors and one row of odd-numbered transistors.

Selecting either all of the even-numbered top conductors or all of the odd-numbered top conductors results in the selection of a single row of memory cells (i.e., the intersection of one even-numbered row and one odd-numbered row selected by the gate conductor with either the even-numbered top conductors or the odd-numbered top conductors). A similar alternative implementation can be achieved by tying together all the even-numbered gate conductors and all of the odd-numbered gate conductors and selecting a single triple-wide top conductor 2300, which also results in a single row selection. Other smaller groupings comprising fewer than half of all the conductors (e.g., fewer than all the even-numbered or odd-numbered conductors) as well as other groupings of gate conductors and top conductors can be employed. The bottom conductors can be brought into such groupings as well. In some implementations, such as when multiple memory cells are accessed at once, the resulting intersection can involve selection of more than one row.

[0083] As shown in Figure 24, vertical via connections 2400, 2410 are formed. These via connections are formed by patterning holes and then filling the holes with conductive material

- 21 -

(e.g., a metal). The via formation is generally performed just before the top metal conductors 2200 or 2300 are formed. It should be noted that via 2410 passes through layers of silicon 1800, 1810, 1820 (patterned, in this instance, to the side of lower silicon layers 1500, 1700) and will typically short circuit those layers together. This structure enables via conductor 2410 to make an electrical connection to layer 1800, in particular, and through it a connection to layer 1700. Layer 1700 forms a P-N junction with layer 1500 before contacting the bottom conductor 1210. Thus, via 2410 enables the fabrication of P-N junction devices simultaneously with the formation of three-terminal P-N-P-N devices. Alternatively, the device shown on the left side of Figure 24 may be used as a P-N junction device if its top connection is unused. As shown, the P-N junction device on the right side of Figure 24 is connected to a three-terminal P-N-P-N device on the left side, thus corresponding to a portion of the circuit shown in Figure 11. These techniques may also be used to wire peripheral circuits that include or consist essentially of vertical MOS transistors.

5

10

15

20

25

30

[0084] Many variants of the present invention will be apparent to one skilled in the art in light of the present teaching, such as implementation on the column lines (rather than, or in addition to on the row lines), decoders other than diode decoders, use with fuses instead of antifuses, and use with other reprogrammable devices (such as phase-change material devices, resistive material devices, one-time programmable (OTP) devices, and Flash-like floating gate devices, etc.) instead of antifuses. Furthermore, for three-dimensional memory array variants, the disabled line may be in the third dimension (i.e., in the direction orthogonal to the rows and columns) or may disable the selection of one out of many subtiles. The switching device in the memory cell may be a gated P-N-P-N device, or as one skilled in the art will readily recognize by omitting the top P+ deposition step, may be an N-P-N bipolar transistor device. Using the techniques described herein to fabricate other devices such as P-N junction devices, N-P-N-P devices, P-N-P devices, FET devices, J-FET devices and unijunction transistors will all be apparent in light of the present teaching. Note that in the case of an FET-type device, middle conductor layer 1300 is constructed as a pair of layers where the first (lower) layer is a conductive layer and the second (upper) layer is a dielectric layer. Before depositing the silicon in the hole, a thin dielectric layer is either conformally deposited or grown and then etched back (as is often done for a side-wall spacer structure) to form the gate oxide; these extra features wrap the middle conductor with an insulating layer. The switching devices may be constructed with one middle contact in addition to the top and bottom contacts, or with two or more middle contacts. Devices may be constructed as a part of an array or may be designed and manufactured

- 22 -

to stand alone or as portions of peripheral circuits.

5

10

15

20

25

30

[0085] Referring back to Figure 22, an embodiment of the present invention features top column conductor lines 2200 running in parallel with middle electrode conductor line 1300 and orthogonal to bottom metal conductor line 1210. One of the two top column conductor lines 2200 is energized (with a high voltage) to uniquely select a single memory cell. In an alternative embodiment, top column conductor lines 2200 run in parallel with bottom metal conductor line 1210 and orthogonal to middle electrode conductor line 1300. In such a variant, one of the two bottom metal conductor lines 1210 is energized (with a low voltage) to uniquely select a single memory cell.

**[0086]** Embodiments of the present invention may feature memory cell devices having multiple middle connections. For example, from the point in the process shown in Figure 17, a layer of dielectric or non-conductive material may be deposited and then patterned. Into such a layer, an additional middle conductor may be formed with a damascene process (resulting in a layer on top of that shown in Figure 17 looking like the upper half of Figure 13). This second, upper middle electrode conductor line may be parallel to or orthogonal to the first, lower middle electrode conductor line 1300. The ends of the two middle conductor lines may be staggered to enable via connections to be made to both. The process continues by etching holes at each memory cell and filling with P+ silicon (to merge with the P+ shown in Figure 17) and planarizing. An implant may be made to change the doping of the P+ silicon to N-type (driving it deep enough to reach just below the bottom edge of the second, upper middle conductor line, but not so deep as to reach the top of first, lower middle electrode conductor line 1300). Finally, N+ silicon is deposited to extend the N-type silicon above the second, upper middle conductor line, followed by a layer of P+ silicon 1820 and top contact material 1830. The middle contacts and the junctions between N+ and P+ silicon layers are preferably not in contact with each other.

Processing then resumes at the point shown in Figure 18, now allowing for via connections to more than one middle conductor. One skilled in the art will recognize this technique may be repeated for more middle conductors than the two described here. Another variation includes formation of the circuit of Figure 11 with gated field emitters replacing the three-terminal, four-layer devices and simple two-terminal (ungated) field emitters replacing the decoder diodes.

#### Programmable elements

[0087] Following the formation of memory cells having vertically constructed switching elements (e.g., the MOS transistors in Figure 8 or the voltage threshold switching devices in

- 23 -

Figure 21), each of the array of memory has an exposed top contact. This facilitates the formation of any of several types of programmable elements on top of one or more cells prior to the formation of the top conductors.

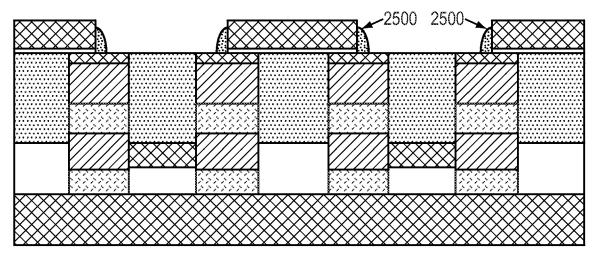

[0088] Figure 25 depicts an embodiment of the present invention incorporating a programmable material 2500. Such a structure is described in U.S. Patent Application Serial No. 12/643,278, filed on December 21, 2009, the entire disclosure of which is incorporated by reference herein. Programmable material 2500 (e.g., a resistive-change or phase-change material) may be formed by a sidewall spacer technique, and may be disposed between the top contact of the memory cell and the top conductor (an insulating dielectric layer disposed below the top conductor prevents current from bypassing material 2500).

**[0089]** Figure 26 shows an embodiment of the present invention that incorporates an OTP material 2600. This programmable structure includes a thin dielectric antifuse layer 2600 between the top contact of the memory cell and the top conductor. Antifuse layer-based memory cells are well understood by those skilled in the art.

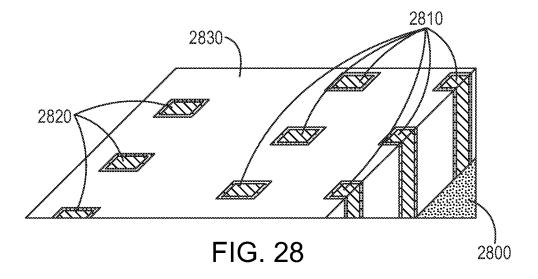

15 **[0090]** Regardless of the type of memory cell switching device utilized and the method of its formation, a surface substantially similar to that depicted in Figure 28 may be achieved above the switches (as described below).

#### Self-aligned programmable element contacts

5

10

20 [0091] Embodiments of the present invention include memory-cell arrays having active devices disposed below the memory cells (e.g., in the underlying substrate or in another layer of circuitry). The active devices (e.g., diodes, transistors, and/or thyristors) are each shared by multiple programmable elements. The memory-cell array may have multiple stacked layers of memory cells. In various embodiments, the memory-cell layer includes a portion of the active device. For example, it may include base and emitter portions of transistors that cooperate with 25 previously fabricated collector portions therebelow. Figure 27A shows a partial schematic in which the columns of an array 2700 are drawn as three column lines to each of which a vertical connection is made through a memory cell switch 2710 (each depicted as a diode). Above each switch 2710, a post connects to multiple layers of row lines (here four are depicted) each 30 controlled by a FET 2720. At each intersection of a row line with a post is a programmable memory element 2730. Each programmable memory element 2730 may be a phase-change element (e.g., one including or consisting essentially of a chalcogenide material such as a germanium-antimony-tellurium alloy (GST)), a resistive-change element, an organic

- 24 -

programmable element, a nano-material element, an OTP element (such as a fuse or an antifuse), a factory programmed link, or some other information storing element. FETs 2720 are typically be formed in a substrate with higher-temperature processing, but this is not a requirement, and these row-selection switching devices may be put in each layer of memory cells. Memory cell switches 2710 may be any of a number of devices formed in a base (e.g., substrate) layer, e.g., diodes, transistors, thristors, and the like. The control gate of each FET 2720 is selected by address circuitry that determines which row line or lines in which layer or layers is selected at any particular time.

5

10

15

20

25

30

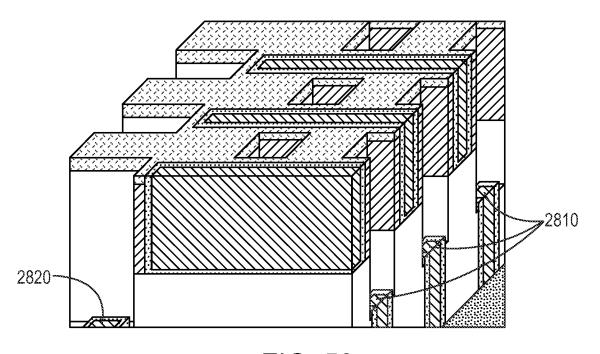

[0092] Figure 27B shows array 2700 in three dimensions; three rows in each of four layers are shown above three columns of a diode array. Selection of an individual memory storage element is accomplished by selection of a column (by way of column address decode circuitry, not shown but well understood by those skilled in the art) and one or more row FETs 2720 (by way of row address decode circuitry, not shown in the figure but well understood by those skilled in the art). As mentioned above, devices other than diodes 2710 may be utilized at the base of the posts, e.g., switching devices such as transistors (an individual post may be selected through address decode circuitry such that a single post is activated as opposed to a column of devices). Furthermore, circuitry to detect current flowing through an addressed or selected path from one or more rows to a column may be implemented in embodiments of the present invention. For example, each set of row-selection FETs 2720 in a given layer may pass through a sense amplifier that senses the amount of current flowing into the FETs 2720 of a given layer and thereby determine the information stored in the selected bit within that layer. In various embodiments, one or more layers (or even all layers) may be active simulaneously and sensed to read a bit therefrom. The layer(s) may be active simultaneously and programmed to write a bit into the layer(s) simultaneously. The programmable elements 2730 may exhibit more than two bit states and therefore each store more than one bit of information.

[0093] Figure 28 depicts a perspective view of a portion of a starting surface 2800. Surface 2800 may be a base layer above an array of memory cells including vertical switches (or of other orientations) or may be a portion of one or more layers of programmable memory elements according to embodiments of the present invention. Contacts 2810 to individual memory cells are disposed on surface 2800, as are contacts 2820 connecting the substrate and individual row lines. Contacts 2810, 2820 may include or consist essentially of one or more conductive materials (e.g., a metal). As depicted in Figure 28, contacts 2810, 2820 are metal surrounded by a thin layer of material that promotes adhesion of the metal to surrounding non-conductive

substrate material 2830.

5

10

15

20

25

30

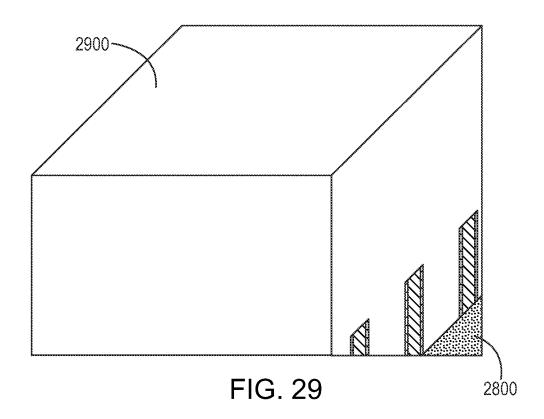

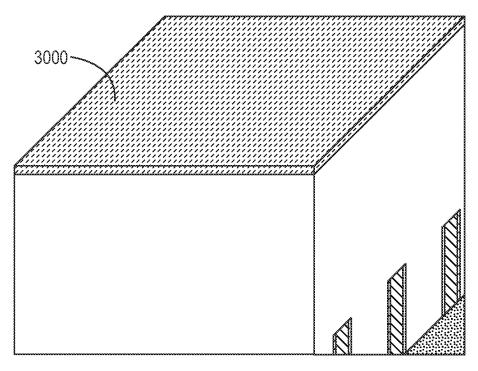

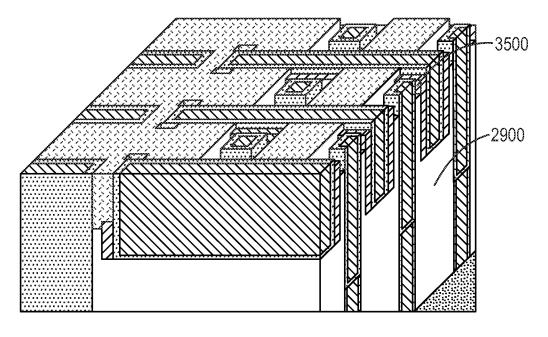

**[0094]** In Figure 29, a layer of non-conductive material 2900 (e.g., a dielectric such as silicon dioxide) has been deposited over surface 2800. As described below, one or more layers of programmable memory elements are formed in layer 2900 in accordance with various embodiments of the invention.

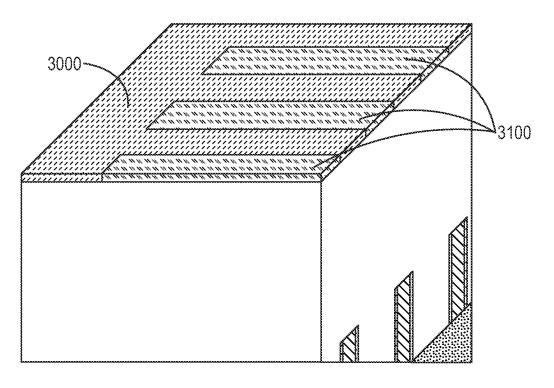

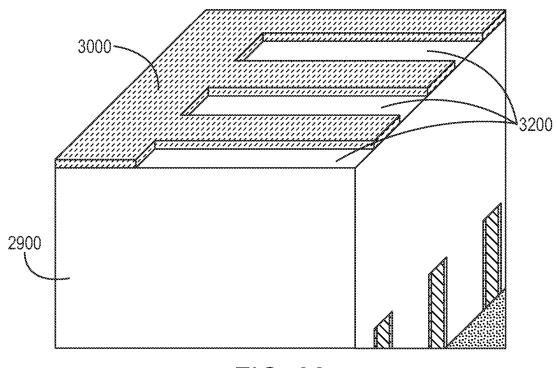

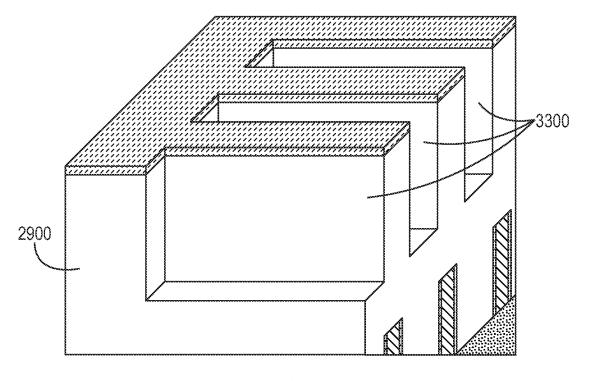

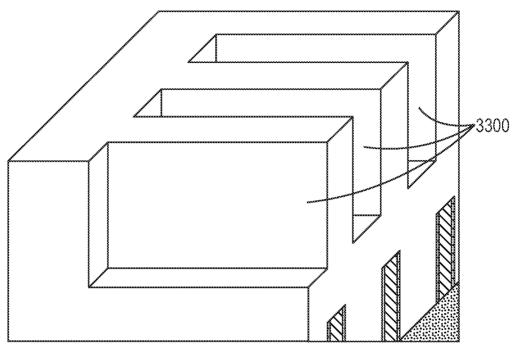

**[0095]** Referring to Figures 30-33, photoresist 3000 is deposited over layer 2900. A pattern of row lines 3100 is exposed in photoresist 3000 and then developed to form openings 3200 corresponding to row lines to be fabricated as described below. Material 2900 is exposed by openings 3200 and is subsequently etched to form row trenches 3300.

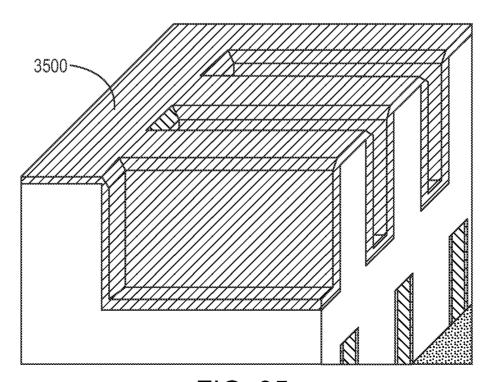

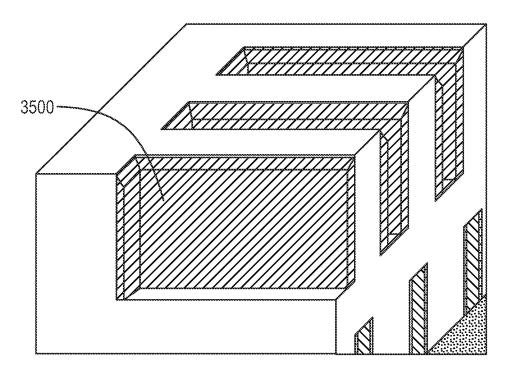

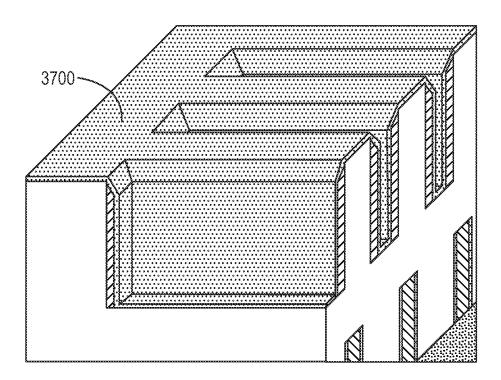

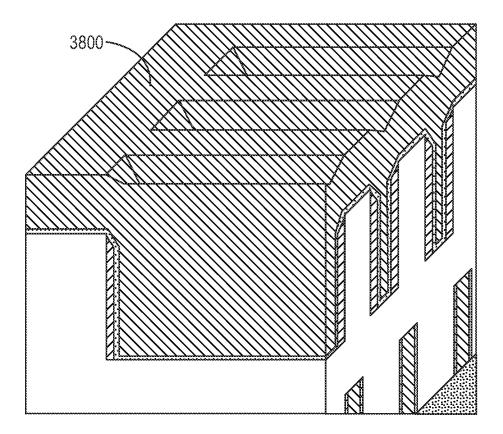

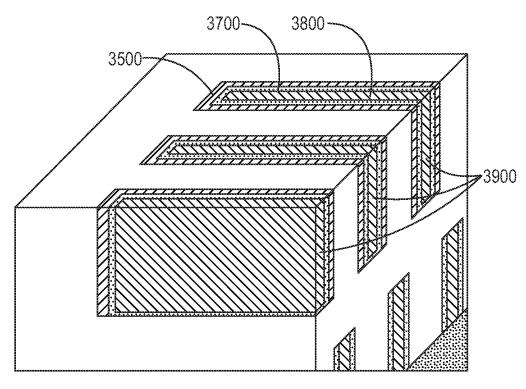

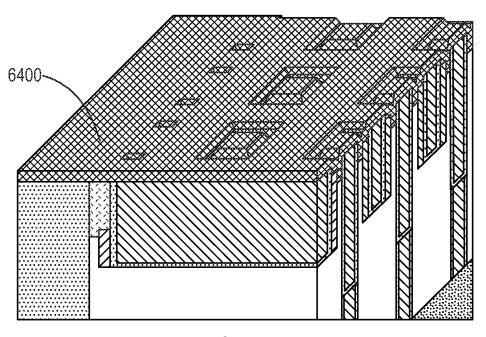

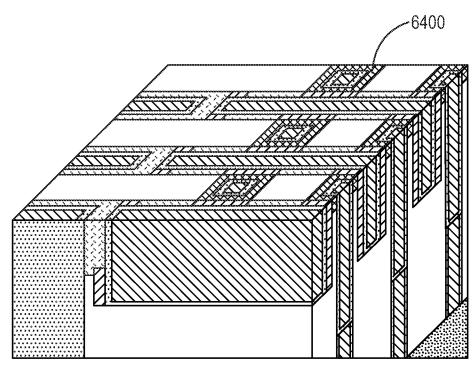

[0096] As shown in Figure 34, after formation of row trenches 3300, the remaining photoresist 3000 is removed. With reference to Figures 35 and 36, a spacer layer 3500 including or consisting essentially of a non-conductive material (e.g., a dielectric such as silicon nitride) is conformally deposited and then directionally etched back (e.g., by reactive-ion etching (RIE)), thus removing spacer layer 3500 on the top surface and in the bottom of the trenches 3300 while leaving spacer layer 3500 on the sidewalls of the row trenches 3300. As shown in Figure 37, a thin barrier layer 3700 is conformally deposited in row trenches 3300. Barrier layer 3700 promotes adhesion to and may substantially prevent interdiffusion between spacer layer 3500 and subsequently deposited layers. As shown in Figure 38, conductive material 3800 is then deposited within row trenches 3300. Conductive material 3800 may include or consist essentially of, e.g., a metal such as copper, tungsten, molybdenum, aluminum, and/or a noble metal. Afterwards, as shown in Figure 39, a planarization step is performed (e.g., by chemical-mechanical polishing), forming the conductive row lines 3900. Row lines 3900 may include regions of conductive material 3800 surrounded by barrier layer 3700 spacer layer 3500.

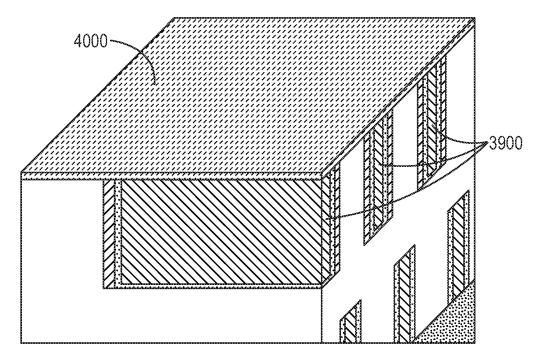

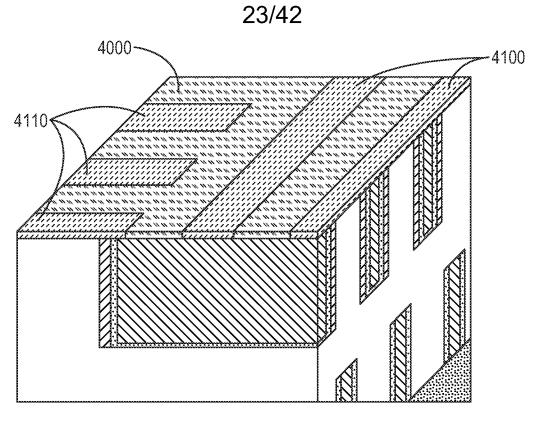

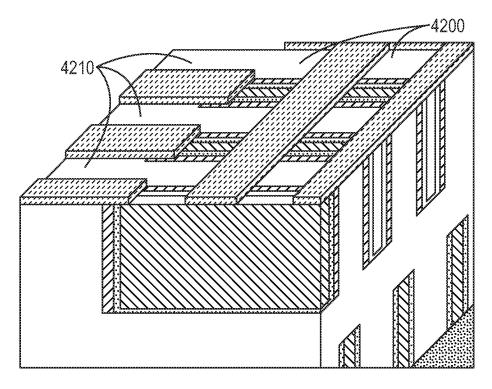

[0097] Referring now to Figures 40-42, a layer of photoresist 4000 is deposited over row lines 3900. Photoresist 4000 is exposed, defining a pattern of column lines 4100 and end-of-row connectors 4110. Photoresist 4000 is then developed, forming openings 4200 corresponding to the spaces between column lines 4100 and opening 4210 between end-of-row connectors 4110. Through these openings, the materials underlying photoresist 4000 are revealed.

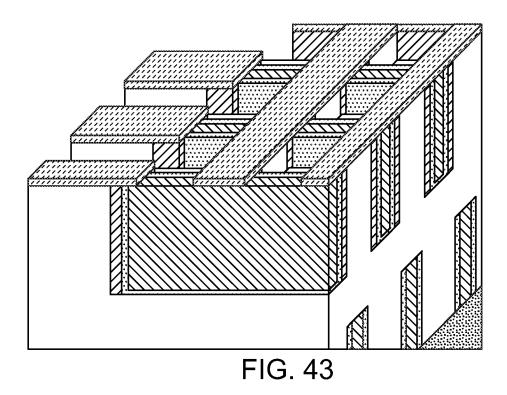

[0098] As shown in Figure 43, a selective dielectric etch is performed by, for example, reactive ion etching (RIE). This etch removes exposed portions of layer 2900 and spacer layer 3500 but does not significantly remove any of the exposed conductive (e.g., metal) materials. The etch selectivity is preferably such that the spacer layer 3500 is etched deeper than the non-conductive bulk material (i.e., layer 2900). For example, an etch tailored for nitride materials may remove

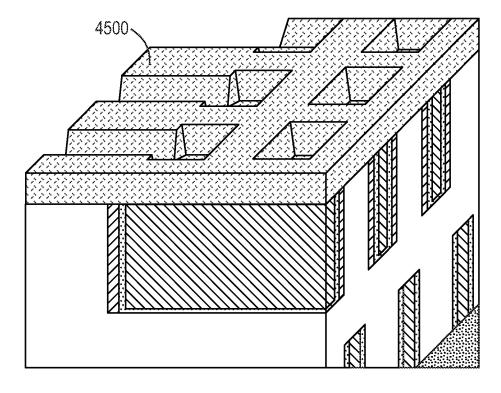

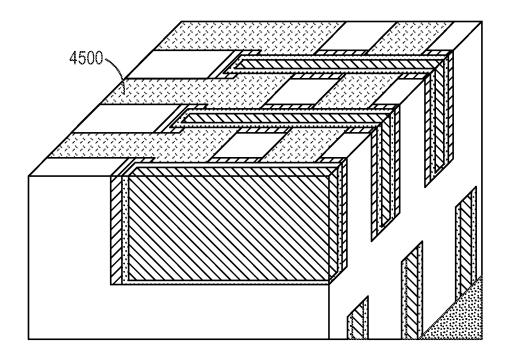

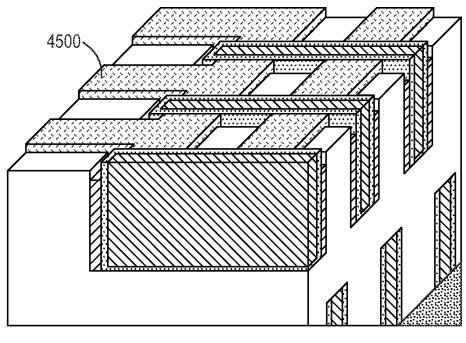

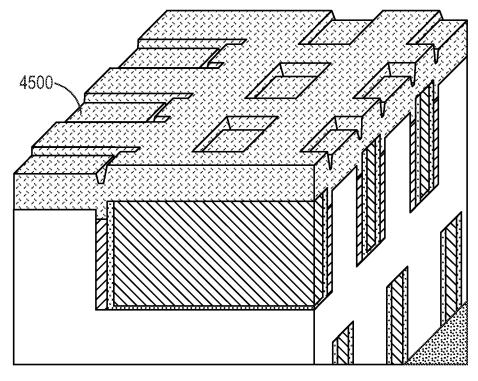

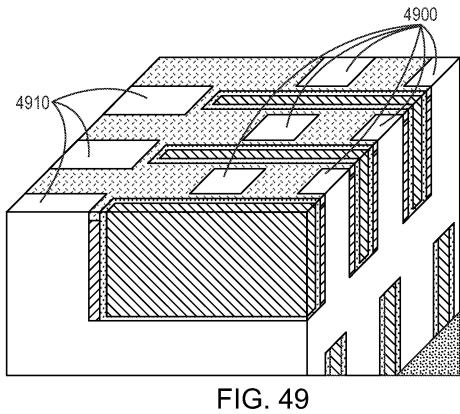

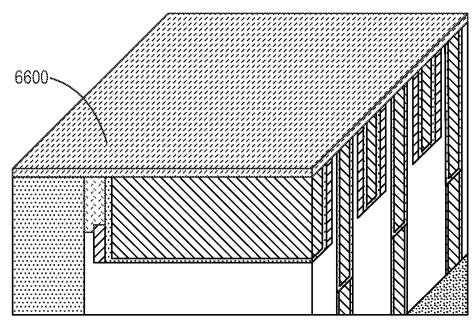

silicon nitride faster than silicon oxide (at a ratio of 2:1 to 3:1). Following this etch, remaining portions of photoresist 4000 are stripped away (Figure 44) and a conductive masking material 4500 (e.g., a metal such as tungsten) is deposited (Figure 45). As shown in Figure 46, conductive mask 4500 is planarized and remains only in the etched areas shown in Figure 44, thus forming an etch-resistant pattern for protection of the spaces between the column lines 4100 and between the end-of-row connectors 4110 (the rows are also made of an etch-resistant material such as metal).

5

10

15

20

25