(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6131369号

(P6131369)

(45) 発行日 平成29年5月17日(2017.5.17)

(24) 登録日 平成29年4月21日(2017.4.21)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 617K |

| HO1L 21/768  | (2006.01) | HO1L 21/88 | F    |

| HO1L 21/3205 | (2006.01) | HO1L 29/78 | 612C |

| HO1L 29/41   | (2006.01) | HO1L 29/44 | S    |

| HO1L 29/49   | (2006.01) | HO1L 29/58 | G    |

請求項の数 4 (全 44 頁) 最終頁に続く

|              |                                                                   |

|--------------|-------------------------------------------------------------------|

| (21) 出願番号    | 特願2016-114255 (P2016-114255)                                      |

| (22) 出願日     | 平成28年6月8日(2016.6.8)                                               |

| (62) 分割の表示   | 特願2015-14978 (P2015-14978)<br>の分割<br>原出願日 平成20年11月28日(2008.11.28) |

| (65) 公開番号    | 特開2016-187040 (P2016-187040A)                                     |

| (43) 公開日     | 平成28年10月27日(2016.10.27)                                           |

| 審査請求日        | 平成28年6月22日(2016.6.22)                                             |

| (31) 優先権主張番号 | 特願2007-312818 (P2007-312818)                                      |

| (32) 優先日     | 平成19年12月3日(2007.12.3)                                             |

| (33) 優先権主張国  | 日本国(JP)                                                           |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 桑原 秀明<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 竹口 泰裕                                          |

最終頁に続く

(54) 【発明の名称】半導体装置と半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上方の第1の配線層と、

前記基板上方の第2の配線層と、

前記第1の配線層上方及び前記第2の配線層上方の第1の絶縁層と、

前記第1の絶縁層上方の半導体層と、

前記第1の絶縁層上方の第3の配線層と、

前記半導体層に電気的に接続された第4の配線層と、

前記半導体層に電気的に接続された第5の配線層と、

前記第1の絶縁層上方、前記半導体層上方、前記第3の配線層上方、前記第4の配線層上方、及び前記第5の配線層上方の第2の絶縁層と、

前記第2の絶縁層上方の画素電極と、を有し、

前記半導体層は、前記第1の配線層と重なる領域を有し、

前記第3の配線層は、前記第2の配線層と重なる領域を有し、

前記第5の配線層は、前記第1の配線層と重なる第1の領域と、前記第1の配線層と重ならない第2の領域と、を有し、

前記第1の領域における前記第5の配線層の側面は、前記第2の領域における前記第5の配線層の側面よりもテーパ角が小さく、

前記半導体層は、金属酸化物を主成分とする特徴とする半導体装置。

## 【請求項 2】

10

20

請求項 1において、

前記半導体層は、インジウムと、ガリウムと、亜鉛と、を有することを特徴とする半導体装置。

**【請求項 3】**請求項 1または請求項 2において、

前記画素電極は、前記第 3 の配線層と重なる領域を有することを特徴とする半導体装置

。

**【請求項 4】**

請求項 1乃至請求項 3 のいずれか一に記載の半導体装置の作製方法であって、

前記第 3 の配線層と、前記第 4 の配線層と、前記第 5 の配線層とは、同一の導電層を加工する工程を経て形成されたものであることを特徴とする半導体装置の作製方法。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は薄膜トランジスタ（以下、TFTという）で構成された回路を有する半導体装置およびその作製方法に関する。例えば、液晶表示パネルに代表される電気光学装置や有機発光素子を有する発光表示装置を部品として搭載した電子機器に関する。

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

20

**【背景技術】****【0003】**

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。

**【0004】**

特に、マトリクス状に配置された表示画素毎に TFT からなるスイッチング素子を設けたアクティブマトリクス型の表示装置（液晶表示装置や発光表示装置）が盛んに開発されている。

30

**【0005】**

この画像表示装置のスイッチング素子は、高精細な画像表示を得るために、面積効率よく配置することができる高精細なフォトリソグラフィ技術が要求される。

**【0006】**

また、これまで、一枚のマザーガラス基板から複数のパネルを切り出して、大量生産を効率良く行う生産技術が採用してきた。マザーガラス基板のサイズは、1990年初頭における第1世代の300×400mmから、2000年には第4世代となり680×880mm若しくは730×920mmへと大型化して、一枚の基板から多数の表示パネルが取れるように生産技術が進歩してきた。今後、さらにマザーガラス基板のサイズは、大型化するため、例えば第10世代の3mを超えるサイズの基板にも対応する必要がある。

40

**【0007】**

高精細な画像表示を得る表示装置を得るために、マザーガラス基板上に成膜された金属薄膜に対してフォトリソグラフィ技術により得られるレジストマスクを用いてエッチングして配線を形成する。

**【0008】**

エッチング方法には、様々な方法があるが、大きく分けてドライエッチング方法とウェットエッチング方法とが挙げられる。ウェットエッチング方法は等方性エッチングのため、レジストマスクで保護された配線層の側面がある程度削り取られてしまい、微細化には向きとされている。

**【0009】**

50

また、一般に知られているドライエッティング方法は、R I E ドライエッティング方法であり、異方性エッティングである。異方性エッティングであるため、微細化には等方性エッティングであるウェットエッティング方法と比べて有利とされている。

【0010】

また、I C P エッティング装置を用いて断面形状がテーパー形状を有するタングステン配線が特許文献1に開示されている。

【0011】

また、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスク或いはレチクルをゲート電極形成用フォトリソグラフィ工程に適用したT F T 作製工程が特許文献2に開示されている。

10

【0012】

また、レジストマスク幅およびエッティング条件を調節することで配線の断面形状を部分的に異ならせる技術が特許文献3で開示されている。

【0013】

また、半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクを用いてソース電極またはドレイン電極を形成する技術が特許文献4に開示されている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2001-35808

20

【特許文献2】特開2002-151523

【特許文献3】特開2006-13461

【特許文献4】特開2007-133371

【発明の概要】

【発明が解決しようとする課題】

【0015】

1枚のマザーガラス基板上に配線を形成する場合、従来の方法では、同じ断面形状の配線となってしまう。例えば、R I E ドライエッティング方法を用いる場合、現像したレジストを加熱して溶かしてレジスト形状を変形させた後、エッティングを行うことでレジスト形状を反映させて配線の側面をテーパー形状としている。この場合、レジストを加熱するプロセスが増加することとなる。また、溶かしてレジスト面積を拡大させるため、隣り合う配線の間隔を狭くすることが困難である。また、多層配線を形成する場合、配線を形成しようとする領域の下方に配線がある場合には、レジストを溶かす際に下方の配線も加熱されるため、レジスト加熱温度が不均一となり場所によってレジストが溶けて広がる割合が変化してしまい、所望の配線形状を得ることが困難である。

30

【0016】

また、I C P エッティング装置を用いる場合、コイル状アンテナを用いるため、長方形である1枚のマザーガラス基板全面に渡って一様な放電を得ることが困難である。

【0017】

例えば、透過型の液晶表示装置の画素部において、ゲート配線をテーパ形状とすることで薄い半導体層をその上に形成する一方、テーパー形状とすると配線幅が広がるため、開口率の低下を招く恐れがある。また、テーパー形状とすると配線幅が広がるため、その配線と絶縁膜を介して重なる他の配線が存在すると、不要な寄生容量が形成される。この寄生容量を小さくするために、異なる層に配置する配線同士が重ならないように各層の配線のレイアウトを行うと、開口率の低下を招くこととなってしまう。

40

【0018】

また、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクを用いる場合、選択的に配線の断面形状を異ならせることができる。この場合、配線の側面が2段の階段状の部分と、そうでない部分との2種類の断面形状の配線となってしまう。

50

**【0019】**

半導体装置の作製方法において、工程を増やすことなく、1枚のマザーガラス基板上に所望の部分にそれぞれ精密に配線の側面の角度を異ならせた配線を提供することを課題とする。

**【課題を解決するための手段】****【0020】**

露光光を透過可能な透光性基板と、透光性基板に形成されたクロム等からなる遮光部と、所定の線幅で遮光材料からなるラインおよびスペースが繰り返し形成された光強度低減機能を有する半透過部とを備えた露光マスクを用いる。ラインおよびスペースで形成された半透過部を備えた露光マスクをグレートーン露光用マスクともいい、この露光マスクを用いた露光をグレートーン露光ともいう。10

**【0021】**

グレートーン露光用マスクは、スリット、ドット等のパターンが少なくとも1つ以上、周期的あるいは非周期的に配置された開口パターンを有している。なお、露光装置の解像限界以下のラインおよびスペースから成るマスクの開口のスペースで構成される光強度低減機能を有する補助パターンの光強度は、10～70%の範囲で調整可能となっている。

**【0022】**

また、露光光の光強度を低減する機能を有する半透過膜からなる半透過部を備えた露光マスクは、ハーフトーン露光用マスクともいい、この露光マスクを用いた露光をハーフトーン露光ともいう。半透過膜としては、MoSiNの他に、MoSi、MoSiO、MoSiON、CrSiなどを用いることができる。20

**【0023】**

なお、本明細書において、グレートーン露光用マスクや、ハーフトーン露光用マスクを総称して、便宜上、多階調マスクと呼ぶ。

**【0024】**

多階調マスクを用いることで1つのフォトレジスト層を1枚のマザーガラス基板から遠ざかる方向に向かって断面積が連続的に減少するテーパ形状を有するフォトレジスト層を形成する。本発明は、グレートーン露光用マスクまたはハーフトーン露光用マスクを用いることで1つのフォトレジスト層を2つの異なる膜厚に現像し、フォトレジスト層の両端にそれぞれ1つの段差を形成するのではない。30

**【0025】**

本発明は、1本の配線を形成する際、1枚のフォトマスクを用い、第1の領域の部分にはグレートーン露光（またはハーフトーン露光）が行われ、同時に第2の領域の部分には通常の露光が行われる。その後、現像を行い、金属膜を選択的にエッチングすることで、場所によって側面形状（具体的には基板主平面に対する角度）が異なる1本の配線を得る。この方法により、意図的に配線の側面形状を異ならせることができ、実施者にとって、所望の配線を得ることができる。

**【0026】**

結果的に第1の領域の配線における側面の幅（テーパー部分の幅とも呼ぶ）は、第2の領域の配線における側面の幅よりも広くなる。また、第1の領域は、基板主平面に対する側面の角度が第2の領域よりも小さくなる。40

**【0027】**

1本の配線において、少なくとも第1の領域の部分と第2の領域の部分とは、基板主平面に対する側面の角度の差が10°より大きくなるようにするのが好ましい。

**【0028】**

例えば、透過型の液晶表示装置において、半導体層と重なるゲート電極となる領域を第1の領域として電気特性の優れた薄膜トランジスタを形成し、画素電極の間に延材するゲート配線となる領域を第2の領域としてテーパー部の幅を狭くすることで開口率を向上させる。また、ゲート配線は配線抵抗を低減させ、且つ、開口率を向上させるために、テーパー部の幅を狭くすることが好ましい。なお、トータルのゲート配線幅は、ゲート電極のト50

ータルの電極幅よりも広くすることで、配線抵抗を低減できる。

【0029】

本明細書で開示する発明の構成は、基板上に半導体層と、半導体層と一部重なる配線とを有し、配線は、配線側部の幅の広い領域と配線側部の幅の狭い領域とを有し、配線側部の幅が広い領域は、半導体層と少なくとも一部重なり、且つ、配線側部の幅が狭い領域の配線幅方向断面の側面角度と比べて配線幅方向断面の側面角度が10°以上小さいことを特徴とする半導体装置である。

【0030】

具体的には、配線側部の幅の広い領域の配線幅方向断面の側面角度は、10°から50°の範囲とし、配線側部の幅が狭い領域の配線幅方向断面の側面角度は、60°から90°の範囲とする。なお、配線幅方向断面の側面角度が、90°であれば配線の断面形状は長方形または正方形であり、90°未満であれば配線の断面形状は、上辺が底辺より短い台形である。

10

【0031】

逆スタガ型の薄膜トランジスタにおいては、ゲート配線上に形成される半導体層は約50nmと薄いため、ゲート配線側部の幅の広い領域の配線幅方向断面の側面角度は、10°から50°の範囲として、ゲート配線の端部または側面と重なる半導体層の一部が薄膜化しないようにすることが好ましい。

【0032】

本発明は、上記課題の少なくとも一つを解決する。

20

【0033】

また、ゲート配線に限定されず、層間絶縁膜上にソース配線やドレイン配線や接続配線などの他の配線を形成する場合にも本発明を用いることができる。

【0034】

また、断面において配線の端部の両端に同じ角度の側面を有する配線を形成するだけではなく、一方の側面と他方の側面の基板主平面に対する角度を異ならせることもできる。この場合、配線の断面形状は、底辺に接する2つの内角が異なる台形と言える。

【0035】

また、他の発明の構成は、基板上に第1の配線と、第1の配線を覆う絶縁膜と、絶縁膜を介して第1の配線と電気的に接続する第2の配線とを有し、第2の配線の断面形状における2つの端部のうち、一方の側面と他方の側面との基板主平面に対する角度が異なる半導体装置である。

30

【0036】

さらに、上記構成に加え、第2の配線と一部重なる透明導電膜を有し、透明導電膜は、第2の配線の断面形状における2つの端部のうち、基板主平面に対する角度が小さい一方の側面と接する。このような構成とすることによって第2の配線の一方の側面と重なる透明導電膜との電気的な接続を確実に行い、透明導電膜の断線を低減する。

【0037】

また、他の発明の構成は、グレートーン露光用マスクまたはハーフトーン露光用マスクを用いることで1つのフォトレジスト層を3つ以上の異なる膜厚に現像し、フォトレジスト層の両端にそれぞれ2つ以上の段差を形成する。このフォトレジスト層をマスクとして導電層をエッチングすると、得られる配線の断面形状は、一方の側面に段差を2つ以上有する階段状となる。勿論、この断面形状を有する配線は、選択的に形成するため、同一絶縁膜表面上に第1の配線と、第1の配線と断面形状の異なる第2の配線とを有し、第1の配線の断面形状は、長方形または台形であり、第2の配線の断面形状は、一方の側面に段差を2つ以上有する階段状であり、第1の配線と第2の配線は、同じ材料である半導体装置とすることができる。配線の断面形状をテーパー形状とする場合、テーパーの端部の位置がエッチング時間によって左右され、特にテーパー角60°未満とするとトータルの配線幅にバラツキが生じる恐れや、側面が湾曲した曲面となって裾状となり、断面積が減少して配線抵抗が増大する恐れがあるが、階段状とすることで、エッチング時間

40

50

が多少違っても一定の配線幅を得ることができる。即ち、第2の配線の断面形状を階段状の配線層とすることでエッチング条件のマージンを十分にとることができ。さらに、第2の配線の断面形状において2つの段差を有する端部とすることで、テーパー角50°未満のテーパー形状を有する配線と同程度の段差被覆性を確保することができる。

#### 【0038】

なお、一本の配線において、第1の領域の断面形状を長方形または台形とし、第2の領域の断面形状を一方の側面に段差を2つ以上有する階段状とすることもできる。

#### 【0039】

また、上記構造を実現するための作製方法に関する発明の構成は、基板上に導電層を形成し、多階調マスクを用いて、1回の露光を行い、断面における側面と基板主平面とがなす角が異なる第1のレジストマスクと第2のレジストマスクを現像し、第1のレジストマスクと第2のレジストマスクをマスクとして導電層をエッチングしてそれぞれ配線を形成し、現像後の第1のレジストマスクの側断面の角度と、第2のレジストマスクの側断面の角度との差は10°よりも大きい半導体装置の作製方法である。10

#### 【0040】

また、他の作製方法に関する発明の構成は、基板上に導電層を形成し、多階調マスクを用いて、1回の露光を行い、断面における側面と基板主平面とがなす角が異なる第1のレジストマスクと第2のレジストマスクを現像し、第1のレジストマスクと第2のレジストマスクをマスクとして導電層をエッチングして1本の配線を形成し、現像後の第1のレジストマスクの側断面の角度と、第2のレジストマスクの側断面の角度との差は10°よりも大きい半導体装置の作製方法である。20

#### 【0041】

上記各作製方法において、第1のレジストマスクの断面形状は、長方形または台形であり、第2のレジストマスクの断面形状は、台形である。或いは、上記作製方法において、第1のレジストマスクの断面形状は、長方形または台形であり、第2のレジストマスクの断面形状は、一方の側面に段差を2つ以上有する階段状である。

#### 【0042】

上述したこれらの手段は単なる設計事項ではなく、多階調マスクを用いて実際に配線を形成し、発明者らの深い検討の後、発明された事項である。

#### 【0043】

特許文献1に開示の技術は、ICPエッチング装置のエッチング条件によって、配線の側面における角度が決定されるため、同一基板上に、同じエッチング工程で形成される配線の側面形状は、全ての配線において一定とすることを意図している。従って、意図的に配線の側面形状を場所によって異ならせる本発明とは大きく異なっている。30

#### 【0044】

また、特許文献2及び特許文献4に開示の技術は、レジストマスクの側部を階段状とし、そのレジストマスクの形状を反映させて配線の側面も階段状としている。特許文献2及び特許文献4に開示されている配線の段差は一つであり、両端のそれぞれ設けられている。

#### 【0045】

また、特許文献3に開示の技術は、配線の断面形状を部分的に異ならせる技術であるが、同じエッチング工程で形成される配線の側面と基板主平面とがなす角度は同じである。40

#### 【0046】

なお、本明細書において、上、下、側、水平、垂直等の方向を表す文言は、基板表面の上にデバイスを配置した場合の基板面を基準とする方向を指す。

#### 【0047】

また、本明細書において、ゲート電極とは、半導体層とゲート絶縁膜を介して重なり、薄膜トランジスタのチャネルを形成する部分を指し、ゲート配線とは、それ以外の部分を指す。なお、同じ導電材料からなる一つのパターンの一部がゲート電極であり、その他の部分がゲート配線となる。

#### 【0048】

10

20

30

40

50

また、本発明において、半導体層は、珪素を主成分とする半導体膜、或いは金属酸化物を主成分とする半導体膜を用いることができる。珪素を主成分とする半導体膜としては、非晶質半導体膜、結晶構造を含む半導体膜、非晶質構造を含む化合物半導体膜などを用いることができ、具体的にはアモルファスシリコン、微結晶シリコン、多結晶シリコン、単結晶シリコンなどを用いることができる。また、金属酸化物を主成分とする半導体膜としては、酸化亜鉛（ZnO）や亜鉛とガリウムとインジウムの酸化物（In-Ga-Zn-O）等を用いることができる。

#### 【0049】

また、TFT構造やトランジスタ構造に関係なく本発明を適用することが可能であり、例えば、トップゲート型TFTや、ボトムゲート型（逆スタガ型）TFTや、順スタガ型TFTを用いることが可能である。また、シングルゲート構造のトランジスタに限定されず、複数のチャネル形成領域を有するマルチゲート型トランジスタ、例えばダブルゲート型トランジスタとしてもよい。

10

#### 【発明の効果】

#### 【0050】

1枚のマスクを用いて、工程を増やすことなく、1枚のマザーガラス基板上に所望の部分にそれぞれ精密に配線の側面の角度を異ならせた配線を作製することができる。

#### 【図面の簡単な説明】

#### 【0051】

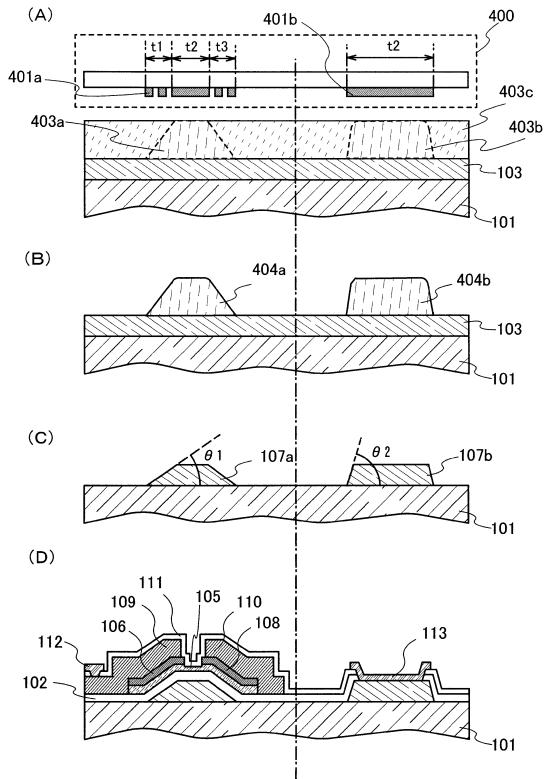

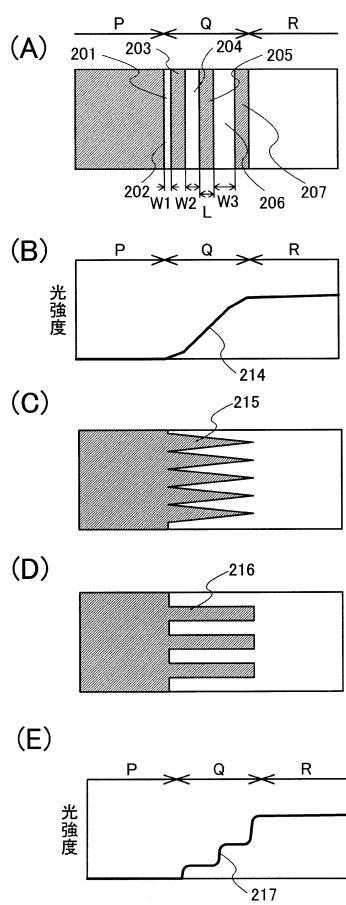

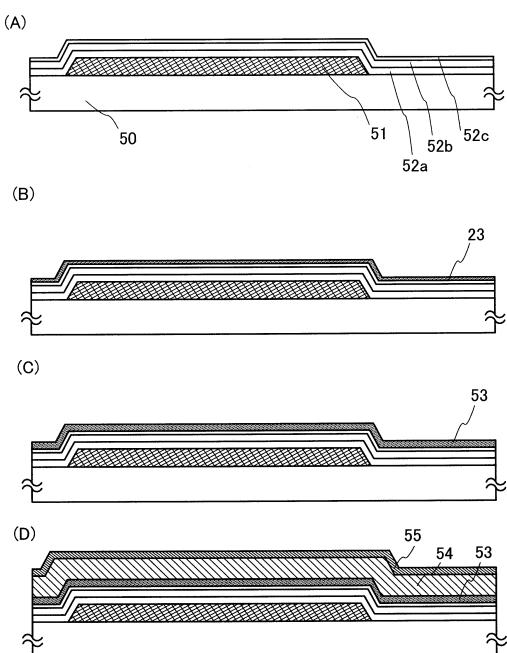

【図1】半導体装置の作製工程を示す断面図。

20

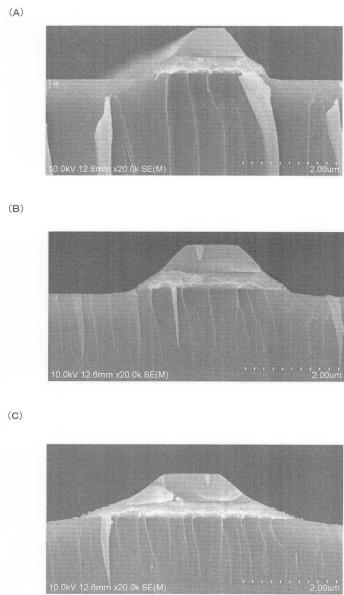

【図2】配線の断面の一例を示す写真図。

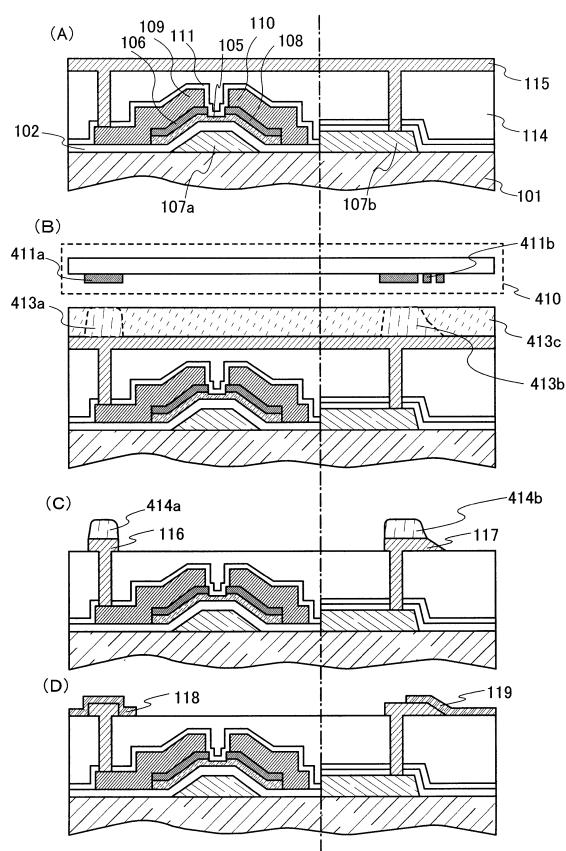

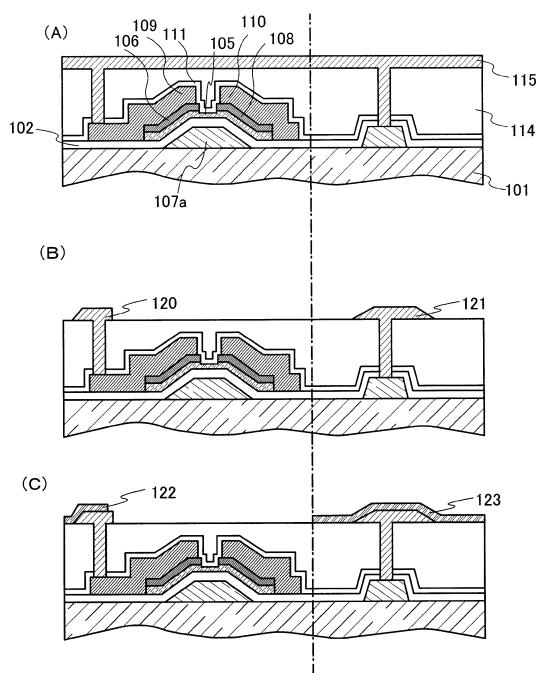

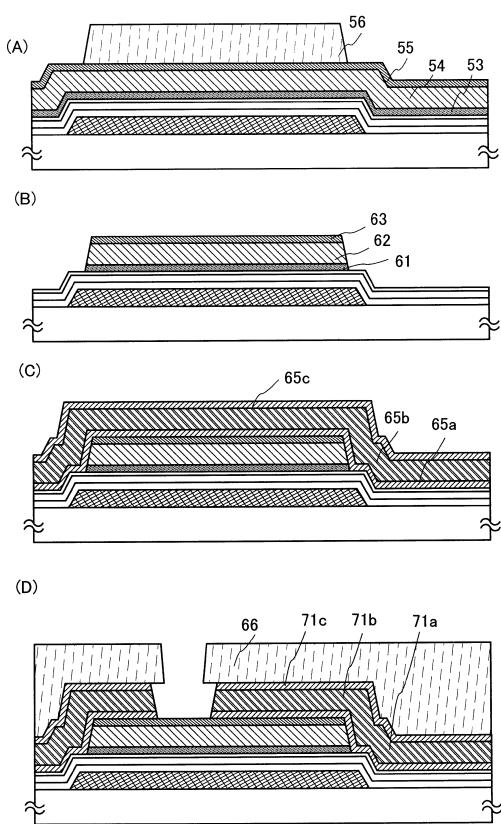

【図3】半導体装置の作製工程を示す断面図。

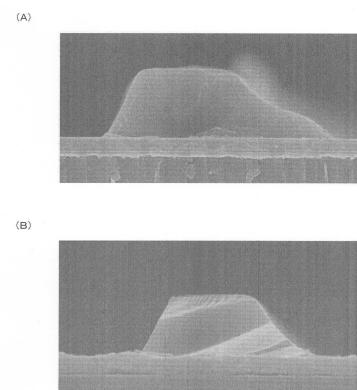

【図4】配線の断面の一例を示す写真図。

【図5】(A)、(C)、(D)はマスクの一部上面図を示す図であり、(B)、(E)は光強度の関係の一例を示す模式図。

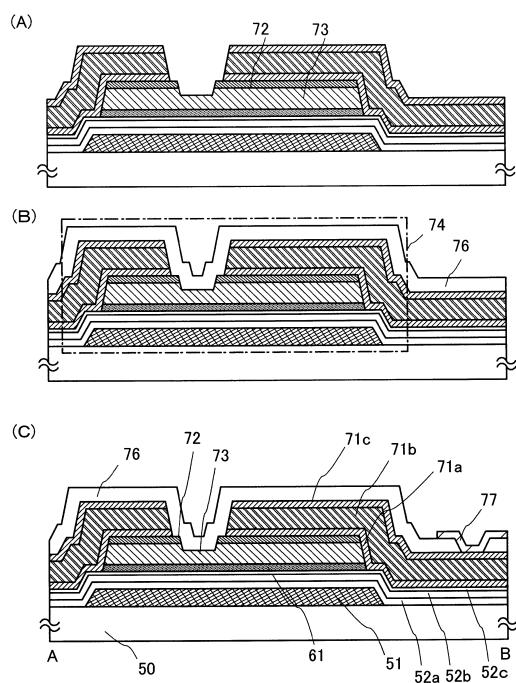

【図6】半導体装置の作製工程を示す断面図。

【図7】半導体装置の作製工程を示す断面図。

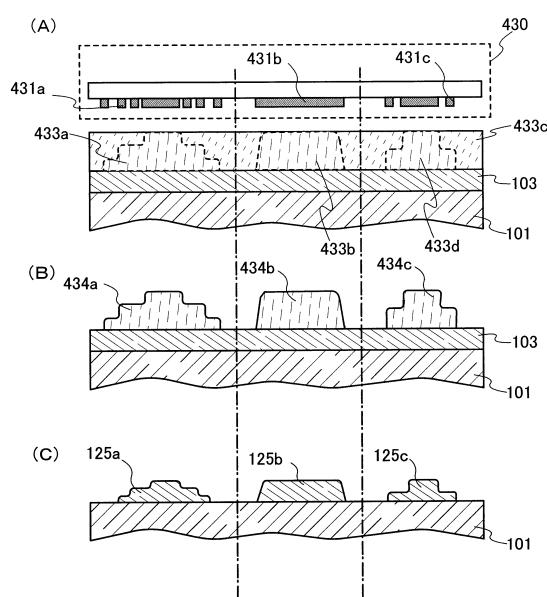

【図8】半導体装置の作製工程を示す断面図。

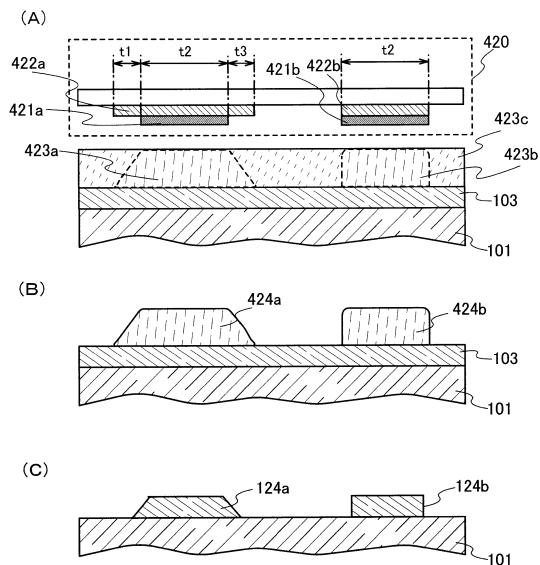

【図9】本発明の作製方法を説明する断面図である。

【図10】本発明の作製方法を説明する断面図である。

30

【図11】本発明の作製方法を説明する断面図である。

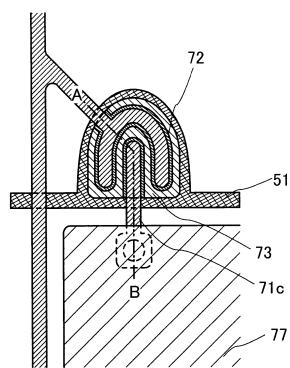

【図12】本発明の作製方法を説明する上面図である。

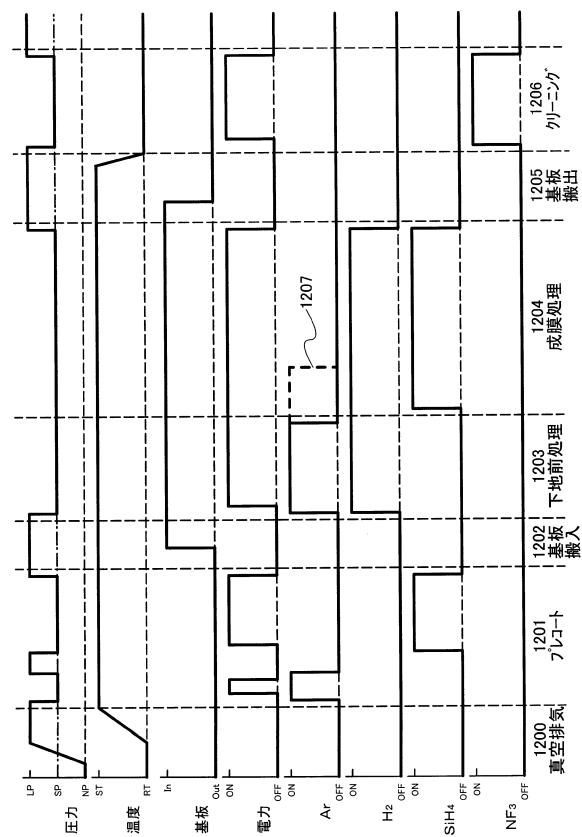

【図13】微結晶シリコン膜を形成する工程を説明するタイムチャートの一例を示す図である。

【図14】エッティング装置を示す断面図。

【図15】半導体装置の作製工程を示す断面図。

【図16】半導体装置の作製工程を示す断面図。

【図17】半導体装置の作製工程を示す断面図。

【図18】半導体装置の作製工程を示す断面図。

【図19】半導体装置の作製工程を示す断面図。

40

【図20】液晶表示装置の一例を説明する断面図である。

【図21】液晶表示装置の一例を説明する上面図である。

【図22】液晶表示装置の一例を説明する上面図である。

【図23】液晶表示装置の画素の等価回路図である。

【図24】液晶表示装置の一例を説明する図である。

【図25】液晶表示装置の一例を説明する図である。

【図26】表示パネルを説明する斜視図である。

【図27】表示パネルを説明する上面図及び断面図である。

【図28】電子機器を説明する斜視図である。

【発明を実施するための形態】

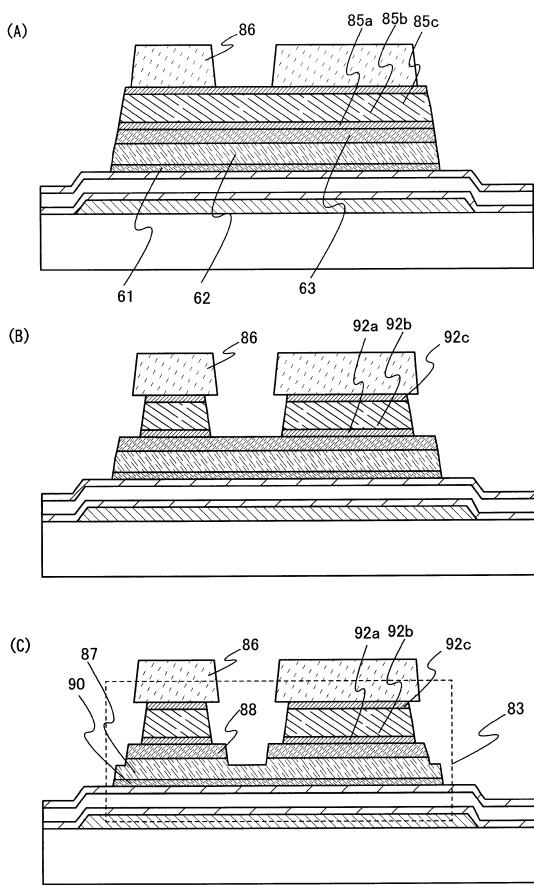

50

**【0052】**

本発明の実施形態について、以下に説明する。

**【0053】****(実施の形態1)**

本実施の形態は、薄膜トランジスタを有する画素部と、FPCなどを用いて外部装置と接続するための接続配線を有する端子部とを同一基板上に形成する作製工程を図1に示す。

**【0054】**

まず、絶縁表面を有する基板101を用意する。絶縁表面を有する基板101としては、透光性を有する基板、例えばガラス基板、結晶化ガラス基板、もしくはプラスチック基板を用いることができる。基板101がマザーガラスの場合、基板の大きさは、第1世代(320mm×400mm)、第2世代(400mm×500mm)、第3世代(550mm×650mm)、第4世代(680mm×880mm、または730mm×920mm)、第5世代(1000mm×1200mmまたは1100mm×1250mm)、第6世代(1500mm×1800mm)、第7世代(1900mm×2200mm)、第8世代(2160mm×2460mm)、第9世代(2400mm×2800mm、2450mm×3050mm)、第10世代(2950mm×3400mm)等を用いることができる。

**【0055】**

また、絶縁表面を有する基板101は、最表面となる層または膜が絶縁表面を有していれば、絶縁体からなる下地膜や半導体層、または導電膜を既に形成していてもよい。

**【0056】**

次に、絶縁表面を有する基板101上に、第1の導電層103を形成する。第1の導電層103はタンゲステン、チタン、クロム、タンタル、またはモリブデンなどの高融点金属、又は窒化タンタルなどの高融点金属を主成分とする合金もしくは化合物を200nm～600nmの厚さで形成する。また、配線の低抵抗化を図るために、アルミニウム、金、銅などの金属膜と上記高融点金属の積層としてもよい。

**【0057】**

次いで、第1の導電層103上にレジスト膜403を全面に塗布した後、図1(A)に示すマスク400を用いて露光を行う。ここでは、膜厚1.5μmのレジスト膜を塗布し、露光は、解像度が1.5μmの露光機を用いる。露光に用いる光は、i線(波長365nm)であり、露光エネルギーは、70～140mJ/cm<sup>2</sup>の範囲から選択する。また、i線に限定されず、i線とg線(波長436nm)とh線(波長405nm)とを混合させた光を露光に用いてもよい。

**【0058】**

本実施の形態では、第1のフォトマスクとして露光マスクの一部に光強度低減機能を有する補助パターン(グレートーン)を設置したものを用いて画素部の薄膜トランジスタのゲート電極のテーパ角を10°から50°の範囲とする。

**【0059】**

図1(A)において、露光マスク400は、Crなどの金属膜からなる遮光部401bと、光強度低減機能を有する補助パターンとして、スリットが設けられた半透過部401aとが設置されている。露光マスク400の断面図において、遮光部401bの幅をt2と示し、半透過部401aの幅をt1とt3と示す。ここでは露光マスクの一部としてグレートーンを用いた例を示したが、半透膜を用いるハーフトーンを用いてもよい。

**【0060】**

図1(A)に示す露光マスク400を用いてレジスト膜403の露光を行うと、レジスト膜403に非露光領域403a、403bと露光領域403cが形成される。露光時には、光が遮光部401bの回り込みや半透過部401aを通過することによって図1(A)に示す露光領域403cが形成される。

**【0061】**

そして、現像を行うと、露光領域403cが除去されて、図1(B)に示すように、画

10

20

30

40

50

素部に第1のレジストマスク404aと、端子部に第2のレジストマスク404bとがそれぞれ第1の導電層103上に得られる。露光エネルギーなどの露光条件を調節することで段差を一つ有する端部ではなく、テーパー形状の第1のレジストマスク404aを得ることができる。グレートーンが設けられていない領域のフォトマスクで露光された端子部においては、第1のレジストマスク404aよりも断面の側面角度が大きい第2のレジストマスク404bが形成される。

#### 【0062】

次に、レジストマスク404a、404bをマスクとして用い、ドライエッチングにより第1の導電層103のエッチングを行う。なお、エッチング条件によっては、絶縁表面を有する基板101もエッチングされて、部分的に膜厚が薄くなる。そのため予め、基板101の最表面の層、または基板101上に、エッチングされてもよい絶縁膜を有しているとよい。エッチングガスには、四弗化炭素( $\text{CF}_4$ )、弗化硫黄( $\text{SF}_6$ )、塩素( $\text{Cl}_2$ )、酸素( $\text{O}_2$ )を用いる。また、ICPエッチング装置と比べて広い面積に渡って一様な放電が得られやすいドライエッチング装置を用いる。そのようなドライエッチング装置としては、上部電極を接地させ、下部電極に13.56MHzの高周波電源を接続し、さらに下部電極に3.2MHzの低周波電源を接続したECCP(Enhanced Capacitively Coupled Plasma)モードのエッチング装置が最適である。このエッチング装置であれば、例えば基板101として、第10世代の3mを超えるサイズの基板を用いる場合にも対応することができる。

#### 【0063】

上記エッチング工程の終了後、アッシング処理などを行って残っているレジストマスクを除去する。こうして図1(C)で示すように、基板101上に第1の配線層107aと第2の配線層107bがそれぞれ形成される。ここでは、画素部に形成される第1の配線層107aのテーパ角<sub>1</sub>を約50°とし、端子部に形成される第2の配線層107bのテーパ角<sub>2</sub>を約70°とする。後の工程で、第1の配線層107a上には半導体膜や配線を形成するので、段切れ防止のため両側面のテーパ角を小さく加工することは効果的である。また、第2の配線層107bは隣接して複数配置され、FPCなどと接続されるため、隣り合う第2の配線層107b間で短絡が生じないように両側面のテーパ角を大きく加工することは効果的である。また、複数の第2の配線層107bを狭い範囲に並べたい場合、隣接する第2の配線層107bの間隔を狭くすることができるため、両側面のテーパ角を大きく加工することは効果的である。

#### 【0064】

尚、この第1導電層103のエッチング工程で使用されるレジスト膜はネガ型レジストが適用困難である為、当該ゲート電極形成用フォトマスクまたはレチクルのパターン構成は、ポジ型レジストを前提にしている。

#### 【0065】

次いで、第1の配線層107a上に窒化珪素(誘電率7.0、厚さ300nm)のゲート絶縁膜102を積層する。ゲート絶縁膜102はCVD法やスピッタリング法等を用いて、窒化珪素膜、または窒化酸化珪素膜で形成することができる。なお、ここでは、窒化酸化珪素膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が15~30原子%、窒素が20~35原子%、Siが25~35原子%、水素が15~25原子%の範囲で含まれるものという。

#### 【0066】

次いで、ゲート絶縁膜102の成膜後、大気に触れさせることなく基板を搬送し、ゲート絶縁膜を成膜する真空チャンバーとは異なる真空チャンバーで非晶質半導体膜105を成膜する。

#### 【0067】

次いで、非晶質半導体膜105の成膜後、大気に触れさせることなく基板を搬送し、非晶質半導体膜105を成膜する真空チャンバーとは異なる真空チャンバーで一導電型を付与する不純物が添加された半導体膜を成膜する。

10

20

30

40

50

**【 0 0 6 8 】**

一導電型を付与する不純物が添加された半導体膜は、代表的な不純物元素としてリンを添加すれば良く、水素化珪素にフオスフィンガスなどの不純物気体を加えれば良い。一導電型を付与する不純物が添加された半導体膜は 2 nm 以上 50 nm 以下の厚さで形成する。一導電型を付与する不純物が添加された半導体膜の膜厚を、薄くすることでスループットを向上させることができる。

**【 0 0 6 9 】**

次いで、一導電型を付与する不純物が添加された半導体膜上にレジストマスクを形成する。レジストマスクは、フォトリソグラフィ技術またはインクジェット法により形成する。ここでは、第 2 のフォトマスクを用いて、一導電型を付与する不純物が添加された半導体膜上に塗布されたレジストを露光現像して、レジストマスクを形成する。10

**【 0 0 7 0 】**

次いで、レジストマスクを用いて一導電型を付与する不純物が添加された半導体膜及び非晶質半導体膜 105 をエッチングして、島状の半導体層を形成する。この後、レジストマスクを除去する。

**【 0 0 7 1 】**

次に、一導電型を付与する不純物が添加された半導体膜及びゲート絶縁膜 102 を覆うように第 2 の導電層を形成する。第 2 の導電層は、アルミニウム、若しくは銅、シリコン、チタン、ネオジム、スカンジウム、モリブデンなどの耐熱性向上元素若しくはヒロック防止元素が添加されたアルミニウム合金の単層または積層で形成することが好ましい。ここでは、第 2 の導電層としては、図示しないが、3 層が積層した構造の導電膜を示し、第 2 の導電層の 1 層目と 3 層目にモリブデン膜、第 2 の導電層の 2 層目にアルミニウム膜を用いる。第 2 の導電層は、スパッタリング法や真空蒸着法で形成する。20

**【 0 0 7 2 】**

次に、図 1 (D) に示すように、第 2 の導電層上に第 3 のフォトマスクを用いてレジストマスクを形成し、第 2 の導電層の一部をエッチングして一対のソース電極又はドレイン電極 109、110 を形成する。第 2 の導電層をウエットエッチングすると、第 2 の導電層の端部が選択的にエッチングされる。この結果、レジストマスクより面積の小さいソース電極及びドレイン電極 109、110 を形成することができる。

**【 0 0 7 3 】**

次に、そのままレジストマスクを用いて一導電型を付与する不純物が添加された半導体膜をエッチングして、一対のソース領域又はドレイン領域 106、108 を形成する。さらに、当該エッチング工程において、非晶質半導体膜 105 の一部もエッチングする。ソース領域及びドレイン領域の形成工程と、非晶質半導体膜 105 の窪み（溝）とを同一工程で形成することができる。非晶質半導体膜 105 の窪み（溝）の深さを非晶質半導体膜 105 の一番膜厚の厚い領域の 1/2 ~ 1/3 とすることで、ソース領域及びドレイン領域の距離を離すことが可能であるため、ソース領域及びドレイン領域の間でのリーク電流を低減することができる。この後、レジストマスクを除去する。30

**【 0 0 7 4 】**

次に、ソース電極またはドレイン電極 109、110、ソース領域またはドレイン領域 106、108、非晶質半導体膜 105、及びゲート絶縁膜 102 を覆う絶縁膜 111 を形成する。絶縁膜 111 は、ゲート絶縁膜 102 と同じ成膜方法を用いて形成することができる。なお、ゲート絶縁膜 102 は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい。40

**【 0 0 7 5 】**

以上の工程により、画素部に薄膜トランジスタを形成することができる。

**【 0 0 7 6 】**

次いで、第 4 のフォトマスクを用いて形成したレジストマスクを用いて絶縁膜 111 を選択的にエッチングして画素部にソース電極またはドレイン電極 109 を露呈する第 1 のコントラクトホールと、絶縁膜 111 及びゲート絶縁膜 102 を選択的にエッチングして端子50

部に第2の配線層107bを露呈させる第2のコンタクトホールを形成する。コンタクトホールの形成後にレジストマスクは除去する。

#### 【0077】

次いで、透明導電膜を形成した後、第5のフォトマスクを用いて形成したレジストマスクを用いて透明導電膜の一部をエッチングして画素部にソース電極またはドレイン電極109に電気的に接続する画素電極112と、端子部に第2の配線層107bと電気的に接続する接続電極113を形成する。画素電極112及び接続電極113の形成後にレジストマスクは除去する。ここまででの工程を終えた断面図が図1(D)に相当する。

#### 【0078】

透明導電膜は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。また、透明導電膜は、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極112は、シート抵抗が10000 /以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

#### 【0079】

導電性高分子としては、いわゆる電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。

#### 【0080】

以上により透過型の液晶表示装置に用いることが可能な素子基板を形成することができる。

#### 【0081】

また、実験を行い、グレートーンマスクを用いてエッチングして得られた配線の断面SEM写真を図2に示す。

#### 【0082】

試料は、ガラス基板上に膜厚100nmの酸化窒化珪素膜を成膜し、その上に400nmのチタン膜を成膜した。そして、チタン膜上にレジスト膜を形成した。

#### 【0083】

露光装置の解像度1.5μmの露光装置を用いてレジスト膜を露光し、現像した。その後、第1のエッチング条件としてBCl<sub>3</sub>ガスの流量を40sccmとし、Cl<sub>2</sub>ガスの流量を40sccmとし、65秒のエッチングを行った後、第2のエッチング条件としてBCl<sub>3</sub>ガスの流量を70sccmとし、Cl<sub>2</sub>ガスの流量を10sccmとしてエッチングを行った。

#### 【0084】

グレートーンが無い領域の配線の断面が図2(A)に相当する。遮光部の幅は3μmである。図2(A)の配線のテーパー角は、約50°である。

#### 【0085】

また、ライン幅0.5μm、スペース幅0.5μmのグレートーンマスクを用いて露光した領域の配線の断面が図2(B)に相当する。遮光部の幅は3μmである。図2(B)の配線のテーパー角は約40°である。

#### 【0086】

また、ライン幅0.5μm、スペース幅0.5μmを2回繰り返して配置したグレートーンマスクを用いて露光した領域の配線の断面が図2(C)に相当する。遮光部の幅は3μmである。図2(C)の配線のテーパー角は約30°である。

#### 【0087】

このように遮光部の幅は同一であっても、グレートーンのライン幅やスペース幅によって得られる配線幅とテーパー角を異ならせることができる。なお、グレートーンのライン幅

10

20

30

40

50

やスペース幅を変えて実験を行ったところ、側面に一つの段差を有する配線形状や、突出した部分を有する配線形状となることもある。

**【0088】**

ここでは、上記エッチング条件で実験したが、特に限定されず、露光現像によってテーパー角の異なるレジストが得られ、そのレジスト形状を反映した配線が得られるように、実施者が適宜、マスクの設計や、エッチング条件を調節することが望ましい。

**【0089】**

(実施の形態2)

本実施の形態では、薄膜トランジスタを覆う層間絶縁膜上に配線を形成する際、画素部と端子部とで断面形状を異ならせる例を図3を用いて説明する。

10

**【0090】**

なお、途中の工程までは、実施の形態1と同一であるため、ここでは詳細な説明は省略する。また、図3において、図1と共通の部分には同じ符号を用いて説明する。

**【0091】**

本実施の形態は、実施の形態1で形成した薄膜トランジスタを覆う絶縁膜111上に平坦化膜を形成する例である。

**【0092】**

まず、実施の形態1に従って、絶縁膜111の形成工程まで行う。

**【0093】**

次いで、平坦化膜114を形成する。平坦化膜114は有機樹脂膜で形成する。次いで、第4のフォトマスクを用いて形成したレジストマスクを用いて絶縁膜111及び平坦化膜114を選択的にエッチングして画素部にソース電極またはドレイン電極109を露呈する第1のコンタクトホールを形成し、ゲート絶縁膜102、絶縁膜111、及び平坦化膜114を選択的にエッチングして端子部に第2の配線層107bを露呈する第2のコンタクトホールを形成する。

20

**【0094】**

次いで、平坦化膜114上に第3の導電層115を成膜する。この段階までの工程断面図が図3(A)に相当する。

**【0095】**

次いで、第3の導電層115上にレジスト膜を全面に塗布した後、図3(B)に示すマスク410を用いて露光を行う。

30

**【0096】**

本実施の形態では、第4のフォトマスクとして露光マスクの一部に光強度低減機能を有する補助パターン(グレートーン)を設置したものを用いて端子部の接続電極の一方の側面のテーパ角を10°から50°の範囲とする。

**【0097】**

図3(B)において、露光マスク410は、Crなどの金属膜からなる遮光部411aと、光強度低減機能を有する補助パターンとして、スリットが設けられた半透過部411bとが設置されている。ここでは露光マスクの一部としてグレートーンを用いた例を示したが、半透膜を用いるハーフトーンを用いてもよい。

40

**【0098】**

図3(B)に示す露光マスク410を用いてレジスト膜の露光を行うと、レジスト膜に非露光領域413a、413bと露光領域413cが形成される。露光時には、光が遮光部411aの回り込みや半透過部411bを通過することによって図3(B)に示す露光領域413cが形成される。

**【0099】**

そして、現像を行うと、露光領域413cが除去されて、画素部に第3のレジストマスクと、端子部に第4のレジストマスクとがそれぞれ第3の導電層115上に得られる。露光エネルギーなどの露光条件を調節することで段差を一つ有する端部ではなく、一方の側面がテーパー形状である第4のレジストマスクを得ることができる。

50

## 【0100】

次に、第3のレジストマスク、及び第4のレジストマスクをマスクとして用い、ドライエッティングにより第3の導電層115のエッティングを行う。また、ICPエッティング装置と比べて広い面積に渡って一様な放電が得られやすいドライエッティング装置を用いる。そのようなドライエッティング装置としては、上部電極を接地させ、下部電極に13.56MHzの高周波電源を接続し、さらに下部電極に3.2MHzの低周波電源を接続したECCP(Enhanced Capacitively Coupled Plasma)モードのエッティング装置が最適である。このエッティング装置であれば、例えば基板101として、第10世代の3mを超えるサイズの基板を用いる場合にも対応することができる。

## 【0101】

この段階までの工程断面図が図3(C)に相当する。第3のレジストマスク、及び第4のレジストマスクも第3の導電層115のエッティングの際にエッティングされて第1の接続電極116上に第3のレジストマスク414a、第2の接続電極117上に第4のレジストマスク414bが残存する。第2の接続電極117は、第4のレジストマスクの形状を反映して一方の側面のみがテーパー形状となっている。また、グレートーンが設けられていない領域のフォトマスクで露光された画素部においては、第1の接続電極116の面積が小さくなるようにエッティングされ、開口率の向上に寄与することができる。

## 【0102】

上記エッティング工程の終了後、アッシング処理などを行って残っているレジストマスクを除去する。

## 【0103】

次いで、透明導電膜を形成した後、第5のフォトマスクを用いて形成したレジストマスクを用いて透明導電膜の一部をエッティングして画素部に第1の接続電極116を覆って電気的に接続する画素電極118と、端子部に第2の接続電極117と電気的に接続する第3の接続電極119を形成する。画素電極118及び第3の接続電極119の形成後にレジストマスクは除去する。ここまで工程を終えた断面図が図3(D)に相当する。第3の接続電極119は、第2の接続電極117のテーパ形状となっている部分と重なるように設けることで、第3の接続電極119の段切れ防止を図っている。

## 【0104】

以上により透過型の液晶表示装置に用いることが可能な素子基板を形成することができる。

## 【0105】

また、実験を行い、グレートーンマスクを用いてエッティングして得られた配線の断面SEM写真を図4に示す。

## 【0106】

試料は、ガラス基板上に膜厚100nmの酸化窒化珪素膜を成膜し、その上に400nmのチタン膜を成膜した。そして、チタン膜上にレジスト膜を形成した。

## 【0107】

露光装置の解像度1.5μmの露光装置を用いてレジスト膜を露光し、現像した。その後、第1のエッティング条件としてBC1<sub>3</sub>ガスの流量を40sccmとし、C1<sub>2</sub>ガスの流量を40sccmとし、65秒のエッティングを行った後、第2のエッティング条件としてBC1<sub>3</sub>ガスの流量を70sccmとし、C1<sub>2</sub>ガスの流量を10sccmとしてエッティングを行った。

## 【0108】

図3(B)のフォトマスクに示すように、一方の側のみにライン幅0.5μm、スペース幅0.5μmを2回繰り返して配置したグレートーンマスクを用いて露光した領域の配線の断面が図4(A)に相当する。一方のテーパ角は約70°であり、もう一方のテーパ角は約35°である。

## 【0109】

また、一方の側のみにライン幅0.5μm、スペース幅0.75μmを配置したグレート

10

20

30

40

50

ーンマスクを用いて露光した領域の配線の断面が図4(B)に相当する。一方のテーパ角は約70°であり、もう一方の側面は一方よりもなだらかになっており、異なるテーパ角を有している。もう一方の側面は、基板から近い側のテーパ角は約30°であり、基板から遠い側のテーパ角は約60°である。

#### 【0110】

なお、一方の側のみにライン幅0.5μm、スペース幅0.5μmを3回繰り返して配置したグレートーンマスクを用いて露光した場合、側面に一つの段差を有する配線形状が得られた。このようにライン幅とスペース幅が変われば、得られる配線形状が大きく変わってしまう。従って、実施者は最適なライン幅とスペース幅を選定し、エッチング条件の最適化を図ることが重要である。

10

#### 【0111】

また、ラインおよびスペース、または矩形パターンおよびスペースで形成された半透過部を備えた露光マスクの一例について図5を用いて説明する。

#### 【0112】

露光マスクの上面図の具体例を図5(A)に示す。また、その露光マスクを用いたときの光強度分布214の一例を図5(B)に示す。図5(A)に示す露光マスクは、遮光部P、半透過部Q、透過部Rを備えている。図5(A)に示す露光マスクの半透過部Qは、縞状(ストライプ状、スリット状)にライン203、205、207およびスペース201、204、206が繰り返し設けられ、ラインおよびスペースが遮光部Pの端部202に平行な方向に配置されている。この半透過部において、遮光材料からなるライン205の幅がL、遮光材料間のスペース204の幅がW2である。ライン203は遮光材料からなり、遮光部Pと同じ遮光材料を用いて設けることができる。ライン203は矩形状に形成されているが、これに限定されない。一定の幅を有していればよい。例えば、角が丸みを帯びた形状でもよい。

20

#### 【0113】

図5(A)の露光マスクにおいては、スペース201の幅W1よりスペース204の幅W2が広くなっている、スペース204の幅W2よりスペース206の幅W3が広くなっている。また、図5(A)の露光マスクにおいては、ラインの幅は同じとしている。

#### 【0114】

なお、図5(A)の露光マスクは一例であって、図5(B)に示す光強度分布が得られるのであれば、特に限定されない。例えば、図5(C)に示すように、ラインではなく、先端が鋭角である遮光部215を有する露光マスクを用いて、露光を行い、図5(B)に示す光強度分布とする。また、図5(D)に示すような複数の枝部を備えた遮光部216を有する露光マスクを用いて図5(B)に示す光強度分布とする。

30

#### 【0115】

本実施の形態は、実施の形態1と自由に組み合わせができる。

#### 【0116】

##### (実施の形態3)

本実施の形態は実施の形態2と一部異なる例であり、図6を用いて説明する。図6(A)は図3(A)と同一であるため、ここでは詳細な説明を省略し、同じ部分には同じ符号を用いて説明する。

40

#### 【0117】

実施の形態2に従って、第3の導電層115を形成するまでの工程を行い、図6(A)と同じ段階とする。

#### 【0118】

次いで、実施の形態2とは異なるフォトマスクを用いて第3の導電層115を選択的にエッチングする。本実施の形態においては、画素部において一方のみにテーパ角を有する第1の接続電極120を形成し、端子部において、両端に同じテーパ角を有する第2の接続電極121を形成する例である。

#### 【0119】

50

上記エッティング工程の終了後、アッシング処理などを行って残っているレジストマスクを除去する。

**【0120】**

次いで、透明導電膜を形成した後、第5のフォトマスクを用いて形成したレジストマスクを用いて透明導電膜の一部をエッティングして画素部に第1の接続電極120の一部と重なり、電気的に接続する画素電極122と、端子部に第2の接続電極121と電気的に接続する第3の接続電極123を形成する。

**【0121】**

本実施の形態においては、画素電極122は、第1の接続電極120のテーパ形状となっている部分と重なるように設けることで、画素電極122の段切れ防止を図っている。

10

**【0122】**

以上により透過型の液晶表示装置に用いることが可能な素子基板を形成することができる。

**【0123】**

本実施の形態は、実施の形態1または実施の形態2と自由に組み合わせることができる。

**【0124】**

(実施の形態4)

本実施の形態は、露光マスクに半透過膜からなる光強度低減機能を有する補助パターン(ハーフトーン膜)を設置したものを用いる例である。

**【0125】**

まず、実施の形態1と同様に、基板101上に第1の導電層103を形成し、その上にレジスト膜を形成する。

20

**【0126】**

図7(A)において、露光マスク420は、Crなどの金属膜からなる遮光部421a、421bと、光強度低減機能を有する補助パターンとして、半透膜(ハーフトーン膜ともいう)が設けられた部分(半透過部422a、422bとも呼ぶ)とが設置されている。露光マスク420の断面図において、遮光部421bと半透過部422b、において遮光部421bと半透過部422bとが重なった領域の幅をt2と示し、半透過部422aにおいて一層の領域の幅をt1とt3と示す。つまり、半透過部422aにおいて遮光部421aと重ならない領域の幅をt1、t3と示す。

30

**【0127】**

図7(A)に示す露光マスク420を用いてレジスト膜の露光を行うと、レジスト膜に非露光領域423a、423bと露光領域423cが形成される。露光時には、光が遮光部421a、421bの回り込みや半透過部422a、422bを通過することによって図7(A)に示す露光領域423cが形成される。

**【0128】**

そして、現像を行うと、露光領域423cが除去されて、図7(B)に示すように、テーパー形状を両側側部に有するレジストマスク424aと、断面がほぼ長方形のレジストマスク424bとが第1の導電層103上に得られる。

**【0129】**

40

次に、レジストマスク424a、424bをマスクとして用い、ドライエッティングにより第1の導電層103のエッティングを行う。

**【0130】**

上記エッティング工程の終了後、アッシング処理などを行って残っているレジストマスクを除去する。こうして図7(C)で示すように、基板101上に第1の配線層124aと第2の配線層124bがそれぞれ形成される。ここでは、画素部に形成される第1の配線層124aのテーパ角を約60°とし、端子部に形成される第2の配線層124bの側面の角度を約90°とする。

**【0131】**

以降の工程は、実施の形態1に従って薄膜トランジスタを形成し、透過型の液晶表示装置

50

に用いることが可能な素子基板を形成する。

**【0132】**

本実施の形態は、実施の形態1、実施の形態2、または実施の形態3と自由に組み合わせることができる。

**【0133】**

(実施の形態5)

本実施の形態は、配線として、2つの段差を有する断面形状と、台形の断面形状と、1つの段差を有する断面形状の3種類と同じマスクで形成する例である。

**【0134】**

まず、実施の形態1と同様に、基板101上に第1の導電層103を形成し、その上にレジスト膜を形成する。 10

**【0135】**

次いで、図8(A)に示す露光マスク430を用いてレジスト膜の露光を行う。レジスト膜の露光を行うと、レジスト膜に非露光領域433a、433b、433dと露光領域433cが形成される。露光時には、光が遮光部431bの回り込みや半透過部431a、431cを通過することによって図8(A)に示す露光領域433cが形成される。

**【0136】**

本実施の形態では、第1のフォトマスクとして露光マスクの一部に光強度低減機能を有する補助パターン(グレートーン)を設置したものを用いて画素部の薄膜トランジスタのゲート電極の両端に2つの段差を形成する。第1のフォトマスクとしては、図5(A)に示すパターンを遮光部の両側に配置したものを用いる。ラインの幅やスペースの幅や露光条件を変えることで、図5(B)に示す光強度分布と異なる分布、例えば図5(E)に示す2つの段差を持たせる光強度分布217とする。また、図5(A)に示す露光マスクは一例であり、例えば、図5(C)に示すように、ラインではなく、先端が鋭角である遮光部215を有する露光マスクを用いて、露光を行い、図5(E)に示す光強度分布としてもよい。また、図5(D)に示すような複数の枝部を備えた遮光部216を有する露光マスクを用いて図5(E)に示す光強度分布としてもよい。 20

**【0137】**

また、端子部の接続電極の両端に1つの段差を形成する。画素部の薄膜トランジスタのゲート電極とは異なる半透過部431cを用いることによって形成する。 30

**【0138】**

そして、現像を行うと、露光領域433cが除去されて、図8(B)に示すように、画素部に第1のレジストマスク434aと、画素部のゲート配線部に第2のレジストマスク434bと、端子部に第3のレジストマスク434cとがそれぞれ第1の導電層103上に得られる。露光エネルギーなどの露光条件を調節することで端部に段差を2つ有する第1のレジストマスク434aを得ることができる。グレートーンが設けられていない領域のフォトマスクで露光された画素部のゲート配線部においては、台形状の第2のレジストマスク434bが形成される。また、端子部には、端部に段差を1つ有する第3のレジストマスク434cを得ることができる。

**【0139】**

次に、レジストマスク434a、434b、434cをマスクとして用い、ドライエッチングにより第1の導電層103のエッチングを行う。 40

**【0140】**

上記エッチング工程の終了後、アッシング処理などを行って残っているレジストマスクを除去する。こうして図8(C)で示すように、基板101上に第1の配線層125aと第2の配線層125bと第3の配線層125cがそれぞれ形成される。ここでは、画素部に形成される第1の配線層125aを2つの段差を有する端部とし、画素部のゲート配線部に形成される第2の配線層125bの側面を台形状とし、端子部に形成される第3の配線層125cを1つの段差を有する端部とする。テーパー形状とする場合、テーパーの端部の位置がエッチング時間によって左右され、特にテーパー角60°未満とするとトータル

ルの配線幅にバラツキが生じる恐れがあるが、階段状の配線層とすることで、エッティング時間が多少違っても一定の配線幅を得ることができる。即ち、階段状の配線層とすることでエッティング条件のマージンを十分にとることができ。さらに、第1の配線層125aを2つの段差を有する端部とすることで、テーパー角50°未満のテーパー形状を有する配線層と同程度の段差被覆性を確保することができる。なお、画素部のゲート配線部に形成される第2の配線層125bの側面角度は、60°から90°の範囲である。

#### 【0141】

このように実施者が露光マスク430を適宜設計することで、所望の配線層の形状を選択的に形成することができる。

#### 【0142】

以降の工程は、実施の形態1に従って薄膜トランジスタを形成し、透過型の液晶表示装置に用いることが可能な素子基板を形成する。

#### 【0143】

本実施の形態は、実施の形態1、実施の形態2、実施の形態3、または実施の形態4と自由に組み合わせることができる。

#### 【0144】

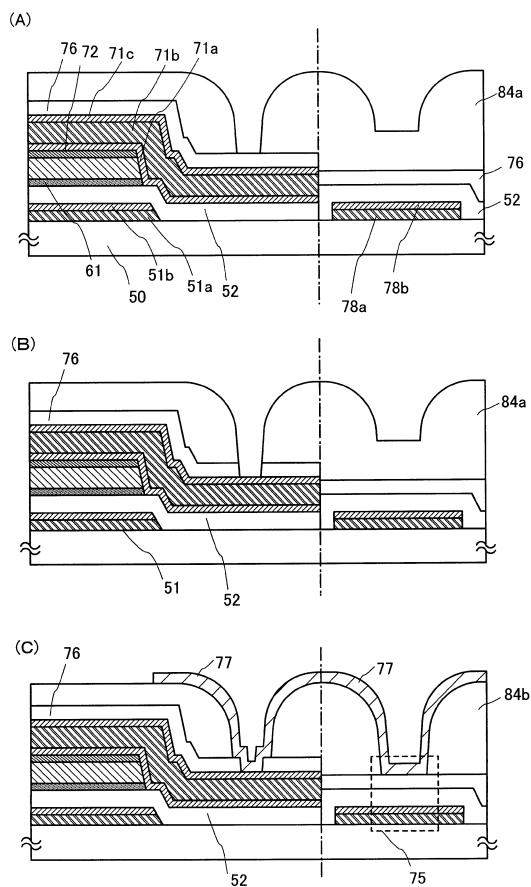

##### (実施の形態6)

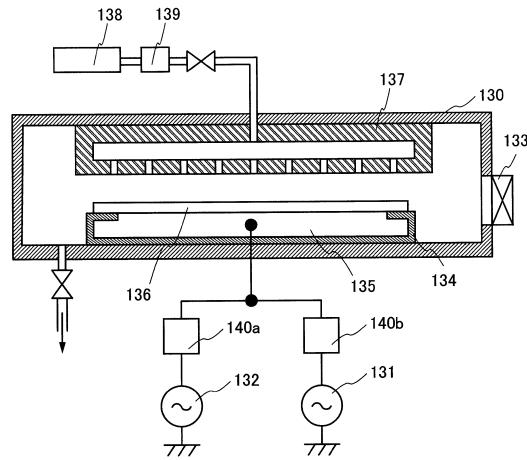

本実施の形態では、液晶表示装置に用いられる薄膜トランジスタの作製工程について、図9乃至図14を用いて説明する。図9乃至図11は、薄膜トランジスタの作製工程を示す断面図であり、図12は、一画素における薄膜トランジスタ及び画素電極の接続領域の上面図である。また、図13は、微結晶シリコン膜の成膜方法を示すタイミングチャートである。また、図14は、電極または配線を形成する際に用いるエッティング装置の断面図である。

#### 【0145】

微結晶半導体膜を有する薄膜トランジスタはp型よりもn型の方が、移動度が高いので駆動回路に用いるのにより適している。同一の基板上に形成する薄膜トランジスタを全て同じ極性にそろえておくことが、工程数を抑えるためにも望ましい。ここでは、nチャネル型の薄膜トランジスタを用いて説明する。

#### 【0146】

図9(A)に示すように、基板50上にゲート電極51を形成する。基板50は、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、若しくはアルミニノシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板等を用いることができる。基板50がマザーガラスの場合、基板の大きさは、第1世代(320mm×400mm)、第2世代(400mm×500mm)、第3世代(550mm×650mm)、第4世代(680mm×880mm、または730mm×920mm)、第5世代(1000mm×1200mmまたは1100mm×1250mm)、第6世代(1500mm×1800mm)、第7世代(1900mm×2200mm)、第8世代(2160mm×2460mm)、第9世代(2400mm×2800mm、2450mm×3050mm)、第10世代(2950mm×3400mm)等を用いることができる。

#### 【0147】

ゲート電極51は、チタン、モリブデン、クロム、タンタル、タングステン、アルミニウムなどの金属材料またはその合金材料を用いて形成する。ゲート電極51は、スパッタリング法や真空蒸着法で基板50上に導電膜を形成し、当該導電膜上に実施の形態1に示す多階調マスクによりレジストマスクを形成し、当該マスクを用いて導電膜をエッティングすることで、形成する。なお、ゲート電極51の密着性向上と下地への拡散を防ぐバリアメタルとして、上記金属材料の窒化物膜を、基板50及びゲート電極51の間に設けてよい。ここでは、多階調マスクであるフォトマスクを用いて形成したレジストマスクを用いて基板50上に形成された導電膜をエッティングしてゲート電極51を形成し、ゲート電極と側面の角度が異なる配線(ゲート配線、引き回し配線、容量配線など)も同時に形成する。

10

20

30

40

50

**【0148】**

また、ここでは図14に示すエッティング装置を用いてエッティングを行う。

**【0149】**

図14に示すエッティング装置は、上部電極137を接地させ、下部電極135に13.56MHzの高周波電源132を接続し、さらに下部電極135に3.2MHzの低周波電源131を接続したECCP(Enhanced Capacitively Coupled Plasma)モードのエッティング装置である。このエッティング装置であれば、例えば基板50として、第10世代の3mを超えるサイズの基板を用いる場合にも対応することができる。

**【0150】**

チャンバー130は、被処理基板を導入するため、チャンバー外壁に設けられている開口にゲートバルブ133が設けられており、ゲートバルブ133は基板のロード室またはアンロード室、或いは搬送室と連結している。また、チャンバー130内部はターボ分子ポンプなどの真空排気手段により減圧可能となっている。また、チャンバー130内には、上部電極137と下部電極135とからなる一対の平行平板電極を有している。

10

**【0151】**

上部電極137は、シャワーヘッドとなっており、チャンバー130内にエッティングガスを導入する開口が複数設けられている。また、上部電極137の中空部分に供給するエッティングガスはガス供給管及びバルブを介して連結しているガス供給機構139から供給される。また、ガス供給機構139は、ガス供給源138と連結されている。

20

**【0152】**

下部電極135の外周および上面周縁には絶縁部材134が設けられている。また、図示しないが、下部電極135には、被処理基板136を保持するための静電チャックなどの基板保持手段と、温度調節するための加熱手段または冷却手段とを有している。また、上部電極137に温度調節するための加熱手段または冷却手段を設けてもよい。

**【0153】**

下部電極135には給電線が電気的に接続されており、この給電線には、第1の整合器140aと高周波電源132とが接続されている。高周波電源132は、13.56MHzのプラズマ形成用の高周波電力を下部電極に供給する。また、この給電線には、第2の整合器140bと低周波電源131とが接続されている。低周波電源131は、例えば、3.2MHzの高周波電力を下部電極に供給し、プラズマ形成用の高周波電力に重畠されるようになっている。

30

**【0154】**

また、図14に示すエッティング装置の各構成部は、プロセスコントローラに制御される。このエッティング装置を用いることで、第10世代の3mを超えるサイズの基板を用いても面内均一性を確保することができる。

**【0155】**

次に、ゲート電極51上に、ゲート絶縁膜52a、52b、52cを順に形成する。ここまで工程を終えた断面図が図9(A)に相当する。

**【0156】**

ゲート絶縁膜52a、52b、52cはそれぞれ、CVD法やスピッタリング法等を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、または窒化酸化珪素膜で形成することができる。ゲート絶縁膜に形成されるピンホール等による層間ショートを防ぐため、異なる絶縁層を用いて多層とすることが好ましい。ここでは、ゲート絶縁膜52a、52b、52cとして、窒化珪素膜、酸化窒化珪素膜、窒化珪素膜の順に積層して形成する形態を示す。

40

**【0157】**

ここでは、酸化窒化珪素膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、濃度範囲として酸素が55~65原子%、窒素が1~20原子%、Siが25~35原子%、水素が0.1~10原子%の範囲で含まれるものという。

50

## 【0158】

ゲート絶縁膜の1層目及び2層目の膜厚はともに50nmよりも厚くする。ゲート絶縁膜の1層目は、基板からの不純物（例えばアルカリ金属など）の拡散を防ぐために、窒化珪素膜または窒化酸化珪素膜が好ましい。また、ゲート絶縁膜の1層目は、ゲート電極の酸化防止の他、ゲート電極にアルミニウムを用いる場合にヒロック防止ができる。また、微結晶半導体膜と接するゲート絶縁膜の3層目は、0nmより厚く5nm以下、望ましくは約1nmとする。ゲート絶縁膜の3層目は、微結晶半導体膜との密着性を向上させるために設けるものである。また、ゲート絶縁膜の3層目を窒化珪素膜とすることで後に行われる熱処理による微結晶半導体膜の酸化防止を図ることができる。例えば、酸素の含有量が多い絶縁膜と微結晶半導体膜とを接した状態で熱処理を行うと、微結晶半導体膜が酸化する恐れがある。

10

## 【0159】

更には、周波数が1GHzのマイクロ波プラズマCVD装置を用いてゲート絶縁膜を形成することが好ましい。マイクロ波プラズマCVD装置で形成した酸化窒化珪素膜、窒化酸化珪素膜は、耐圧が高く、薄膜トランジスタの信頼性を高めることができる。

## 【0160】

ここでは、ゲート絶縁膜を3層構造としたが、液晶表示装置のスイッチング素子に用いる場合、交流駆動させるため、窒化珪素膜の単層のみでもよい。

## 【0161】

次いで、ゲート絶縁膜の成膜後、大気に触れさせることなく基板を搬送し、ゲート絶縁膜を成膜する真空チャンバーとは異なる真空チャンバーで微結晶半導体膜53を成膜することが好ましい。

20

## 【0162】

以下に、図13も参照しながら微結晶半導体膜53を形成する手順について説明する。図13の説明は真空チャンバーを大気圧から真空排気200する段階から示されており、その後に行われるプレコート1201、基板搬入1202、下地前処理1203、成膜処理1204、基板搬出1205、クリーニング1206の各処理が時系列的に示されている。ただし、大気圧から真空排気することに限定されず、常時ある程度の真空度に真空チャンバーを保っておくことが、量産を行う上好ましい、または短時間で到達真空度を下げる上で好ましい。

30

## 【0163】

本実施の形態では、基板搬入前の真空チャンバー内の真空度を $10^{-5}$ Paよりも低くする超高真空排気を行う。この段階が図13の真空排気1200に対応する。このような超高真空排気を行う場合、クライオポンプを併用し、ターボ分子ポンプによる排気を行い、さらにクライオポンプを使って真空排気することが好ましい。ターボ分子ポンプを2台直列に連結して真空排気することも有効である。また、真空チャンバーにベーキング用のヒータを設けて加熱処理して真空チャンバー内壁からの脱ガス処理を行うことが好ましい。また、基板を加熱するヒータも動作させて温度を安定化させる。基板の加熱温度は100～300、好ましくは120～220で行う。

40

## 【0164】

次いで、基板搬入前にプレコート1201を行い、内壁被覆膜としてシリコン膜を形成する。プレコート1201として、水素または希ガスを導入してプラズマを発生させて真空チャンバーの内壁に付着した気体（酸素及び窒素などの大気成分、若しくは真空チャンバーのクリーニングに使用したエッティングガス）を除去した後、シランガスを導入して、プラズマを生成する。シランガスは酸素、水分等と反応するので、シランガスを流し、さらにシランプラズマを生成することで真空チャンバー内の酸素、水分を除去することができる。また、プレコート1201の処理をしておくことで、微結晶シリコン膜中に真空チャンバーを構成する部材の金属元素を不純物として取り込んでしまうのを防ぐことができる。すなわち、真空チャンバー内をシリコンで被覆しておくことで、真空チャンバー内がプラズマにより食刻されるのを防ぐことができ、後に成膜する微結晶シリコン膜中に含まれ

50

る不純物濃度を低減することができる。プレコート 1201 は、真空チャンバーの内壁を基板上に堆積されるべき膜と同種の膜で被覆する処理が含まれている。

#### 【0165】

プレコート 1201 の後、基板搬入 1202 が行われる。微結晶シリコン膜が堆積されるべき基板は、真空排気されたロード室に保管されているので、基板を搬入したとしても真空チャンバー内の真空度が著しく悪化することはない。

#### 【0166】

次いで、下地前処理 1203 を行う。下地前処理 1203 は、微結晶シリコン膜を形成する場合において、特に有効な処理であり行うことが好ましい。すなわち、ガラス基板表面、絶縁膜の表面若しくは非晶質シリコンの表面上に微結晶シリコン膜をプラズマ CVD 法で成膜する場合には、不純物や格子不整合などの要因により堆積初期段階において非晶質層が形成されてしまう恐れがある。この非晶質層の厚さを極力低減し、可能であれば無くすために下地前処理 1203 を行うことが好ましい。下地前処理としては希ガスプラズマ処理、水素プラズマ処理若しくはこの両者の併用により行うことが好ましい。希ガスプラズマ処理としては、アルゴン、クリプトン、キセノンなど質量数の大きい希ガス元素を用いることが好ましい。表面に付着した酸素、水分、有機物、金属元素などの不純物をスペッタリングの効果で除去するためである。水素プラズマ処理は、水素ラジカルにより、表面に吸着した上記不純物の除去と、絶縁膜若しくは非晶質シリコン膜に対するエッティング作用により清浄な被成膜表面を形成するのに有効である。また、希ガスプラズマ処理と水素プラズマ処理を併用することにより微結晶核生成の促進を助長する。

10

#### 【0167】

微結晶核の生成を促進させるという意味においては、図 13 中の破線 1207 で示すように、微結晶シリコン膜の成膜初期においてアルゴンなどの希ガスを供給し続けることは有効である。

#### 【0168】

次いで、下地前処理 1203 に続いて微結晶シリコン膜を形成する成膜処理 1204 を行う。本実施の形態では、成膜速度は低いが品質のよい第 1 の成膜条件でゲート絶縁膜界面付近の膜を形成し、その後、高い成膜速度の第 2 の成膜条件に変えて膜を堆積する。

#### 【0169】

第 1 の成膜条件での成膜速度よりも第 2 の成膜条件の成膜速度が速ければ特に限定されない。従って、周波数が数十 MHz ~ 数百 MHz の高周波プラズマ CVD 法、または周波数が 1 GHz 以上のマイクロ波プラズマ CVD 装置により形成し、代表的には、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$  などの水素化珪素を水素で希釈してプラズマ生成することで成膜することができる。また、水素化珪素及び水素に加え、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。これらのときの水素化珪素に対して水素の流量比を 12 倍以上 1000 倍以下、好ましくは 50 倍以上 200 倍以下、更に好ましくは 100 倍とする。なお、水素化珪素の代わりに、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$  等を用いることができる。

30

#### 【0170】

また、材料ガスにヘリウムを加えた場合、ヘリウムは 24.5 eV とすべての気体中で最も高いイオン化エネルギーを持ち、そのイオン化エネルギーよりも少し低い、約 20 eV の準位に準安定状態があるので、放電持続中においては、イオン化にはその差約 4 eV しか必要としない。そのため放電開始電圧も全ての気体中最も低い値を示す。このような特性から、ヘリウムはプラズマを安定的に維持することができる。また、均一なプラズマを形成することができるので、微結晶シリコン膜を堆積する基板の面積が大きくなてもプラズマ密度の均一化を図る効果を奏する。

40

#### 【0171】

また、シラン等のガス中に  $\text{CH}_4$ 、 $\text{C}_2\text{H}_6$  などの炭素の水素化物、 $\text{GeH}_4$ 、 $\text{GeF}_4$  などの水素化ゲルマニウム、フッ化ゲルマニウムを混合して、エネルギー・バンド幅を 1.

50

5 ~ 2 . 4 e V、若しくは 0 . 9 ~ 1 . 1 e V に調節しても良い。シリコンに炭素又はゲルマニウムを加えると TFT の温度特性を変えることができる。

#### 【 0 1 7 2 】

ここでは、第 1 の成膜条件は、シランは水素及び / 又は希ガスで 100 倍を超える 2000 倍以下に希釈し、基板の加熱温度は 100 ~ 300 、好ましくは 120 ~ 220 とする。微結晶シリコン膜の成長表面を水素で不活性化し、微結晶シリコンの成長を促進するためには 120 ~ 220 で成膜を行うことが好ましい。

#### 【 0 1 7 3 】

第 1 の成膜条件を終えた段階での断面図を図 9 ( B ) に示す。ゲート絶縁膜 52c 上には成膜速度は低いが品質のよい微結晶半導体膜 23 が成膜されている。この第 1 の成膜条件で得られる微結晶半導体膜 23 の品質が、後に形成される TFT のオン電流増大および電界効果移動度の向上に寄与するため、膜中の酸素濃度が  $1 \times 10^{-7} / \text{cm}$  以下となるように十分酸素濃度を低減させることが重要である。また、上記手順により、酸素だけではなく、窒素、及び炭素が微結晶半導体膜の膜中に混入する濃度を低減することができるため、微結晶半導体膜が n 型化になることを防止することができる。10

#### 【 0 1 7 4 】

次いで、第 2 の成膜条件に変えて成膜速度を上げて微結晶半導体膜 53 を成膜する。この段階での断面図が図 9 ( C ) に相当する。微結晶半導体膜 53 の膜厚は、50 nm ~ 500 nm ( 好ましくは 100 nm ~ 250 nm ) の厚さとすれば良い。なお、本実施の形態では、微結晶半導体膜 53 の成膜時間は、第 1 の成膜条件で成膜が行われる第 1 の成膜時間と第 2 の成膜条件で成膜が行われる第 2 の成膜時間とを有する。20

#### 【 0 1 7 5 】

ここでは、第 2 の成膜条件は、シランは水素及び / 又は希ガスで 12 倍以上 100 倍以下に希釈し、基板の加熱温度は 100 ~ 300 、好ましくは 120 ~ 220 とする。なお、容量結合型 ( 平行平板型 ) の CVD 装置を用い、ギャップ ( 電極面と基板表面の間隔 ) を 20 mm とし、真空チャンバー内の真空中度 100 Pa とし、基板温度 300 とし、60 MHz の高周波電力を 20 W 加え、シランガス ( 流量 8 sccm ) を水素 ( 流量 400 sccm ) で 50 倍に希釈して微結晶シリコン膜を成膜する。また、上記成膜条件でシランガスの流量のみを 4 sccm に変更して 100 倍に希釈して微結晶シリコン膜を成膜すると成膜速度が遅くなる。水素流量を固定し、シラン流量を増やすことで成膜速度が増大する。成膜速度を低下させることで、結晶性が向上する。30

#### 【 0 1 7 6 】

本実施の形態では、容量結合型 ( 平行平板型 ) の CVD 装置を用い、ギャップ ( 電極面と基板表面の間隔 ) を 20 mm とし、第 1 の成膜条件を真空チャンバー内の真空中度 100 Pa とし、基板温度 100 とし、60 MHz の高周波電力を 30 W 加え、シランガス ( 流量 2 sccm ) を水素 ( 流量 400 sccm ) で 200 倍に希釈する条件とし、ガス流量を変えて成膜速度を速める第 2 の成膜条件として 4 sccm のシランガスを水素 ( 流量 400 sccm ) で 100 倍に希釈する条件で成膜を行う。

#### 【 0 1 7 7 】

次いで、第 2 の成膜条件での微結晶シリコンの成膜が終了した後、シラン、水素などの材料ガス及び高周波電力の供給を止めて基板搬出 1205 を行う。引き続き次の基板に対して成膜処理を行う場合には、基板搬入 1202 の段階に戻り同じ処理が行われる。真空チャンバー内に付着した被膜や粉末を除去するには、クリーニング 1206 を行う。40

#### 【 0 1 7 8 】

クリーニング 1206 は NF<sub>3</sub> 、 SF<sub>6</sub> に代表されるエッティングガスを導入してプラズマエッティングを行う。また、 ClF<sub>3</sub> のようにプラズマを利用しなくてもエッティングが可能なガスを導入して行う。クリーニング 1206 においては基板加熱用のヒータを切って、温度を下げるが好ましい。エッティングによる反応副生成物の生成を抑えるためである。クリーニング 1206 の終了後はプレコート 1201 に戻り、次の基板に対して上述した同様の処理を行えば良い。 NF<sub>3</sub> は窒素を組成に含んでいるため、成膜室中の窒素50

濃度を低減するためにはプレコートを行って十分に窒素濃度を下げることが望ましい。

#### 【0179】

次いで、微結晶半導体膜53の成膜後、大気に触れさせることなく基板を搬送し、微結晶半導体膜53を成膜する真空チャンバーとは異なる真空チャンバーでバッファ層54を成膜することが好ましい。バッファ層54の真空チャンバーと別にすることで、微結晶半導体膜53を成膜する真空チャンバーは基板導入前に超高真空にする専用チャンバーとすることができ、不純物汚染を極力抑え、且つ、超高真空に到達する時間を短縮することができる。超高真空に到達するためにベークを行う場合、チャンバー内壁温度が下がって安定になるまで時間がかかるため、特に有効である。また、真空チャンバーを別々とすることで、得ようとする膜質に合わせてそれぞれ高周波電力の周波数を異ならせることができる。10

#### 【0180】

バッファ層54は、水素、若しくはハロゲンを含む非晶質半導体膜を用いて形成する。水素化珪素の流量の1倍以上10倍以下、更に好ましくは1倍以上5倍以下の流量の水素を用いて、水素を含む非晶質半導体膜を形成することができる。また、上記水素化珪素と、フッ素、塩素、臭素、またはヨウ素を含む気体( $F_2$ 、 $Cl_2$ 、 $Br_2$ 、 $I_2$ 、 $HF$ 、 $HCl$ 、 $HBr$ 、 $HI$ 等)を用いることで、フッ素、塩素、臭素、またはヨウ素を含む非晶質半導体膜を形成することができる。なお、水素化珪素の代わりに、 $SiH_2Cl_2$ 、 $SiHCl_3$ 、 $SiCl_4$ 、 $SiF_4$ 等を用いることができる。

#### 【0181】

また、バッファ層54は、ターゲットに非晶質半導体を用いて水素、または希ガスでスパッタリングして非晶質半導体膜を形成することができる。また、雰囲気中にフッ素、塩素、臭素、またはヨウ素を含む気体( $F_2$ 、 $Cl_2$ 、 $Br_2$ 、 $I_2$ 、 $HF$ 、 $HCl$ 、 $HBr$ 、 $HI$ 等)を含ませることにより、フッ素、塩素、臭素、またはヨウ素を含む非晶質半導体膜を形成することができる。

#### 【0182】

バッファ層54は、結晶粒を含まない非晶質半導体膜で形成することが好ましい。このため、周波数が数十MHz～数百MHzの高周波プラズマCVD法、またはマイクロ波プラズマCVD法で形成する場合は、結晶粒を含まない非晶質半導体膜となるように、成膜条件を制御することが好ましい。30

#### 【0183】

バッファ層54は、後のソース領域及びドレイン領域の形成プロセスにおいて、一部エッチングする。そのときに、微結晶半導体膜53が露呈しないようにバッファ層54の一部が残存する厚さで形成することが好ましい。代表的には、100nm以上400nm以下、好ましくは200nm以上300nm以下の厚さで形成することが好ましい。薄膜トランジスタの印加電圧の高い(例えば15V程度)表示装置、代表的には液晶表示装置において、バッファ層54の膜厚を上記範囲に示すように厚く形成すると、耐圧が高くなり、薄膜トランジスタに高い電圧が印加されても、薄膜トランジスタが劣化することを回避することができる。

#### 【0184】

なお、バッファ層54には、リンやボロン等の一導電型を付与する不純物が添加されていない。一導電型を付与する不純物が添加された半導体膜55から一導電型を付与する不純物が微結晶半導体膜53へ拡散しないように、バッファ層54がバリア層として機能している。バッファ層を設けない場合、微結晶半導体膜53と一導電型を付与する不純物が添加された半導体膜55とが接してしまうと、後のエッチング工程や加熱処理により不純物が移動し、しきい値制御が困難になる恐れがある。

#### 【0185】

さらにバッファ層54を微結晶半導体膜53の表面上に形成することで、微結晶半導体膜53に含まれる結晶粒の表面の自然酸化を防止することが可能である。特に、非晶質半導体と微結晶粒が接する領域では、局部応力により亀裂が入りやすい。この亀裂が酸素に触

10

20

30

40

50

れると結晶粒は酸化され、酸化珪素が形成されてしまう。

**【0186】**

非晶質半導体膜であるバッファ層54のエネルギーギャップが微結晶半導体膜53に比べて大きく(非晶質半導体膜のエネルギーギャップは1.6eV以上1.8eV以下、微結晶半導体膜53のエネルギーギャップは1.1eV以上1.5eV以下)、また抵抗が高く、移動度が低く、微結晶半導体膜53の1/5~1/10である。このため、後に形成される薄膜トランジスタにおいて、ソース領域及びドレイン領域と、微結晶半導体膜53との間に形成されるバッファ層は高抵抗領域として機能し、微結晶半導体膜53がチャネル形成領域として機能する。このため、薄膜トランジスタのオフ電流を低減することができる。当該薄膜トランジスタを表示装置のスイッチング素子として用いた場合、表示装置のコントラストを向上させることができる。10

**【0187】**

なお、微結晶半導体膜53上に、プラズマCVD法によりバッファ層54を300~400の温度にて成膜することが好ましい。この成膜処理により水素が微結晶半導体膜53に供給され、微結晶半導体膜53を水素化したのと同等の効果が得られる。すなわち、微結晶半導体膜53上にバッファ層54を堆積することにより、微結晶半導体膜53に水素を拡散させて、ダンギリングボンドの終端を行うことができる。

**【0188】**

次いで、バッファ層54の成膜後、大気に触れさせることなく基板を搬送し、バッファ層54を成膜する真空チャンバーとは異なる真空チャンバーで一導電型を付与する不純物が添加された半導体膜55を成膜することが好ましい。この段階での断面図が図9(D)に相当する。バッファ層54を成膜する真空チャンバーとは異なる真空チャンバーで一導電型を付与する不純物が添加された半導体膜55を成膜することでバッファ層の成膜時に一導電型を付与する不純物が混入しないようにすることができる。20

**【0189】**

一導電型を付与する不純物が添加された半導体膜55は、nチャネル型の薄膜トランジスタを形成する場合には、代表的な不純物元素としてリンを添加すれば良く、水素化珪素にPH<sub>3</sub>などの不純物気体を加えれば良い。また、pチャネル型の薄膜トランジスタを形成する場合には、代表的な不純物元素としてボロンを添加すれば良く、水素化珪素にB<sub>2</sub>H<sub>6</sub>などの不純物気体を加えれば良い。一導電型を付与する不純物が添加された半導体膜55は、微結晶半導体、または非晶質半導体で形成することができる。一導電型を付与する不純物が添加された半導体膜55は2nm以上50nm以下の厚さで形成する。一導電型を付与する不純物が添加された半導体膜の膜厚を、薄くすることでスループットを向上させることができる。30

**【0190】**

次いで、図10(A)に示すように、一導電型を付与する不純物が添加された半導体膜55上にレジストマスク56を形成する。レジストマスク56は、フォトリソグラフィ技術またはインクジェット法により形成する。ここでは、第2のフォトマスクを用いて、一導電型を付与する不純物が添加された半導体膜55上に塗布されたレジストを露光現像して、レジストマスク56を形成する。40

**【0191】**

次いで、レジストマスク56を用いて微結晶半導体膜53、バッファ層54、及び導電型を付与する不純物が添加された半導体膜55をエッチングし分離して、図10(B)に示すように、微結晶半導体膜61、バッファ層62、及び一導電型を付与する不純物が添加された半導体膜63を形成する。この後、レジストマスク56を除去する。

**【0192】**

微結晶半導体膜61、バッファ層62の端部側面が傾斜していることにより、バッファ層62上に形成されるソース領域及びドレイン領域と微結晶半導体膜61との間にリーク電流が生じること防止することが可能である。また、ソース電極及びドレイン電極と、微結晶半導体膜61との間にリーク電流が生じるのを防止することが可能である。微結晶半導50

体膜 6 1 及びバッファ層 6 2 の端部側面の傾斜角度は、30°～90°、好ましくは45°～80°である。このような角度とすることで、段差形状によるソース電極またはドレイン電極の段切れを防ぐことができる。

#### 【0193】

次に、図10(C)に示すように、一導電型を付与する不純物が添加された半導体膜63及びゲート絶縁膜52cを覆うように導電膜65a～65cを形成する。導電膜65a～65cは、アルミニウム、若しくは銅、シリコン、チタン、ネオジム、スカンジウム、モリブデンなどの耐熱性向上元素若しくはヒロック防止元素が添加されたアルミニウム合金の単層または積層で形成することが好ましい。また、一導電型を付与する不純物が添加された半導体膜と接する側の膜を、チタン、タンタル、モリブデン、タングステン、またはこれらの元素の窒化物で形成し、その上にアルミニウムまたはアルミニウム合金を形成した積層構造としても良い。更には、アルミニウムまたはアルミニウム合金の上面及び下面を、チタン、タンタル、モリブデン、タングステン、またはこれらの元素の窒化物で挟んだ積層構造としてもよい。ここでは、導電膜としては、導電膜65a～65c 3層が積層した構造の導電膜を示し、導電膜65a、65cにモリブデン膜、導電膜65bにアルミニウム膜を用いた積層導電膜や、導電膜65a、65cにチタン膜、導電膜65bにアルミニウム膜を用いた積層導電膜を示す。導電膜65a～65cは、スパッタリング法や真空蒸着法で形成する。10

#### 【0194】

次に、図10(D)に示すように、導電膜65a～65c上に第3のフォトマスクを用いてレジストマスク66を形成し、導電膜65a～65cの一部をエッチングして一対のソース電極及びドレイン電極71a～71cを形成する。導電膜65a～65cをウェットエッチングすると、選択的にエッチングされる。この結果、導電膜65a～65cを等方的にエッチングするため、レジストマスク66より面積の小さいソース電極及びドレイン電極71a～71cを形成することができる。20

#### 【0195】

次に、図11(A)に示すように、レジストマスク66を用いて一導電型を付与する不純物が添加された半導体膜63をエッチングして、一対のソース領域及びドレイン領域72を形成する。さらに、当該エッチング工程において、バッファ層62の一部もエッチングする。一部エッチングされた、窪み(溝)が形成されたバッファ層をバッファ層73と示す。ソース領域及びドレイン領域の形成工程と、バッファ層の窪み(溝)とを同一工程で形成することができる。バッファ層の窪み(溝)の深さをバッファ層73の一番膜厚の厚い領域の1/2～1/3とすることで、ソース領域及びドレイン領域の距離を離すことが可能であるため、ソース領域及びドレイン領域の間でのリーク電流を低減することができる。この後、レジストマスク66を除去する。30

#### 【0196】

特にドライエッチングなどで用いるプラズマに曝されるとレジストマスクは変質し、レジスト除去工程で完全には除去されず、残渣が残ることを防ぐためにバッファ層73を50nm程度エッチングする。レジストマスク66は、導電膜65a～65cの一部のエッチング処理と、ソース領域及びドレイン領域72の形成時のエッチング処理の2回に用いられており、どちらもドライエッチングを用いる場合には、残渣が残りやすいため、残渣を完全に除去する際にエッチングされてもよいバッファ層73の膜厚を厚く形成することは有効である。また、バッファ層73は、ドライエッチングの際にプラズマダメージが微結晶半導体膜61に与えられることを防止することもできる。40

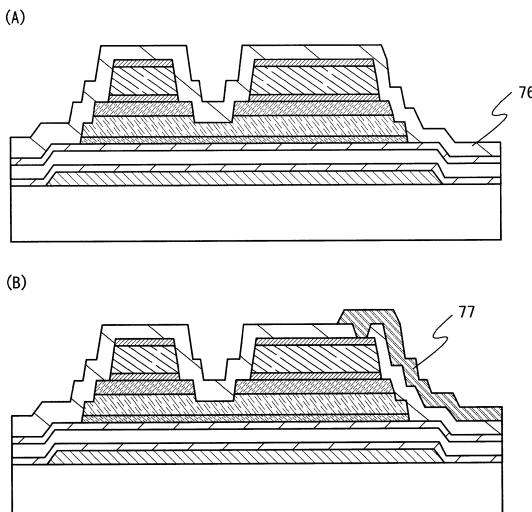

#### 【0197】

次に、図11(B)に示すように、ソース電極及びドレイン電極71a～71c、ソース領域及びドレイン領域72、バッファ層73、微結晶半導体膜61、及びゲート絶縁膜52cを覆う絶縁膜76を形成する。絶縁膜76は、ゲート絶縁膜52a、52b、52cと同じ成膜方法を用いて形成することができる。なお、絶縁膜76は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好50

ましい。また、絶縁膜 7 6 に窒化珪素膜を用いることで、バッファ層 7 3 中の酸素濃度を  $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下とすることができます。

#### 【0198】

図 11 (B) に示すように、ソース電極及びドレイン電極 7 1 a ~ 7 1 c の端部と、ソース領域及びドレイン領域 7 2 の端部は一致せずずれた形状となることで、ソース電極及びドレイン電極 7 1 a ~ 7 1 c の端部の距離が離れるため、ソース電極及びドレイン電極間のリーク電流やショートを防止することができる。また、ソース電極及びドレイン電極 7 1 a ~ 7 1 c の端部と、ソース領域及びドレイン領域 7 2 の端部は一致せずずれた形状であるため、ソース電極及びドレイン電極 7 1 a ~ 7 1 c 及びソース領域及びドレイン領域 7 2 の端部に電界が集中せず、ゲート電極 5 1 と、ソース電極及びドレイン電極 7 1 a ~ 7 1 c との間でのリーク電流を防止することができる。このため、信頼性が高く、且つ耐圧の高い薄膜トランジスタを作製することができる。10

#### 【0199】

以上の工程により、薄膜トランジスタ 7 4 を形成することができる。

#### 【0200】

本実施の形態で示す薄膜トランジスタは、ゲート電極上にゲート絶縁膜、微結晶半導体膜、バッファ層、ソース領域及びドレイン領域、ソース電極及びドレイン電極が積層され、チャネル形成領域として機能する微結晶半導体膜の表面をバッファ層が覆う。また、バッファ層の一部には窪み（溝）が形成されており、当該窪み以外の領域がソース領域及びドレイン領域で覆われる。即ち、バッファ層に形成される窪みにより、ソース領域及びドレイン領域の距離が離れているため、ソース領域及びドレイン領域の間でのリーク電流を低減することができる。また、バッファ層の一部をエッチングすることにより窪みを形成するため、ソース領域及びドレイン領域の形成工程において発生するエッチング残渣を除去することができるため、残渣を介してソース領域及びドレイン領域にリーク電流（寄生チャネル）が発生することを回避することができる。20

#### 【0201】

また、チャネル形成領域として機能する微結晶半導体膜とソース領域及びドレイン領域との間に、バッファ層が形成されている。また、微結晶半導体膜の表面がバッファ層で覆われている。高抵抗のバッファ層は、微結晶半導体膜と、ソース領域及びドレイン領域との間にまで延在しているため、薄膜トランジスタにリーク電流が発生することを低減することができると共に、高い電圧の印加による劣化を低減することができる。また、バッファ層と、微結晶半導体膜と、ソース領域及びドレイン領域は、全てゲート電極と重なる領域上に形成される。従って、ゲート電極の端部形状に影響されない構造と言える。ゲート電極を積層構造とした場合、下層としてアルミニウムを用いると、ゲート電極側面にアルミニウムが露出し、ヒロックが発生する恐れがあるが、さらにソース領域及びドレイン領域をゲート電極端部とも重ならない構成とすることで、ゲート電極側面と重なる領域でショートが発生することを防ぐことができる。また、微結晶半導体膜の表面に水素で表面が終端された非晶質半導体膜がバッファ層として形成されているため、微結晶半導体膜の酸化を防止することができると共に、ソース領域及びドレイン領域の形成工程に発生するエッチング残渣が微結晶半導体膜に混入することを防ぐことができる。このため、電気特性が優れ、且つ耐圧に優れた薄膜トランジスタである。3040

#### 【0202】

また、薄膜トランジスタのチャネル長を短くすることができ、薄膜トランジスタの平面面積を縮小することができる。

#### 【0203】

次に、絶縁膜 7 6 に第 4 のフォトマスクを用いて形成したレジストマスクを用いて絶縁膜 7 6 の一部をエッチングしてコンタクトホールを形成し、当該コンタクトホールにおいてソース電極またはドレイン電極 7 1 c に接する画素電極 7 7 を形成する。なお、図 11 (C) は、図 12 の鎖線 A - B の断面図に相当する。50

**【0204】**

図12に示すように、ソース領域及びドレイン領域72の端部は、ソース電極及びドレイン電極71cの端部の外側に位置することが分かる。また、バッファ層73の端部はソース電極及びドレイン電極71c及びソース領域及びドレイン領域72の端部の外側に位置する。また、ソース電極及びドレイン電極の一方はソース領域及びドレイン領域の他方を囲む形状（具体的には、U字型、C字型）である。このため、キャリアが移動する領域の面積を増加させることができるのであるため、電流量を増やすことが可能であり、薄膜トランジスタの面積を縮小することができる。また、ゲート電極上において、微結晶半導体膜、ソース電極及びドレイン電極が重畠されているため、ゲート電極の凹凸の影響が少なく、被覆率の低減及びリーク電流の発生を抑制することができる。なお、ソース電極またはドレイン電極の一方は、ソース配線またはドレイン配線としても機能する。10

**【0205】**

また、微結晶半導体膜と重なっていないゲート配線側部の幅は、微結晶半導体膜と重なっているゲート電極側部の幅よりも狭い。こうすることで画素部の開口率の向上を図っている。また、微結晶半導体膜と重なっているゲート電極の側面の角度（テーパー角）は、微結晶半導体膜と重なっていないゲート配線側面よりも小さい。こうすることで、上方に形成される膜の被覆性を良好なものとしている。

**【0206】**

また、画素電極77は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。20

**【0207】**

また、画素電極77として、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極77は、シート抵抗が10000 /以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

**【0208】**

導電性高分子としては、いわゆる電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。30

**【0209】**

ここでは、画素電極77としては、スパッタリング法によりインジウム錫酸化物膜を成膜した後、インジウム錫酸化物膜上にレジストを塗布する。次に、第5のフォトマスクを用いてレジストを露光及び現像し、レジストマスクを形成する。次に、レジストマスクを用いてインジウム錫酸化物膜をエッチングして画素電極77を形成する。

**【0210】**

以上により表示装置に用いることが可能な素子基板を形成することができる。

**【0211】**

本実施の形態は、実施の形態1、実施の形態2、実施の形態3、実施の形態4または実施の形態5と自由に組み合わせることができる。40

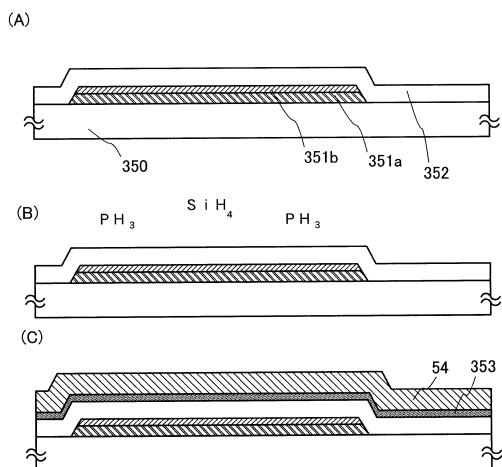

**【0212】****(実施の形態7)**

本形態は基板を真空チャンバーに搬入する前に、水素または希ガスを導入してプラズマを発生させて真空チャンバーの内壁に付着した気体（酸素及び窒素などの大気成分、若しくは真空チャンバーのクリーニングに使用したエッティングガス）を除去した後、水素とシランガスと微量のフォスフィン（PH<sub>3</sub>）ガスを導入する例を示す。実施の形態2とは一部工程が違うのみであるので、異なる工程のみを以下に詳細に図15を用いて説明する。図15において、実施の形態2と同じ部分には同じ符号を用いる。50

**【0213】**

まず、実施の形態6と同様に多階調マスクを用いて基板350上にゲート電極を形成する。ここでは、600mm×720mmのサイズの無アルカリガラス基板を用いる。また、ここでは、大面積の基板を用いて表示画面が大きい表示装置を作製する例であるので、電気抵抗の低いアルミニウムからなる第1の導電層351aと、第1の導電層351aよりも耐熱性の高いモリブデンからなる第2の導電層351bとを積層させたゲート電極とする。エッチング装置は、図14に示すECCPモードのエッチング装置を用いる。

**【0214】**

次に、ゲート電極の上層である第2の導電層351b上に、ゲート絶縁膜352を形成する。液晶表示装置のスイッチング素子に用いる場合、交流駆動させるため、ゲート絶縁膜352は、窒化珪素膜の単層のみとすることが望ましい。ここでは、ゲート絶縁膜352として、単層の窒化珪素膜（誘電率7.0、厚さ300nm）をプラズマCVD法により形成する。ここまで工程を終えた断面図が図15(A)に相当する。

10

**【0215】**

次いで、ゲート絶縁膜の成膜後、大気に触れさせることなく基板を搬送し、ゲート絶縁膜を成膜する真空チャンバーとは異なる真空チャンバーで微結晶半導体膜を成膜する。

**【0216】**

基板を成膜装置の真空チャンバーに搬入する前に、水素または希ガスを導入してプラズマを発生させて真空チャンバーの内壁に付着した気体（酸素及び窒素などの大気成分、若しくは真空チャンバーのクリーニングに使用したエッチングガス）を除去した後、水素とシランガスと微量のフォスフィン（PH<sub>3</sub>）ガスを導入する。シランガスは、真空チャンバー内の酸素、水分等と反応させることができる。微量のフォスフィンガスは、後に成膜される微結晶半導体膜中にリンを含ませることができる。

20

**【0217】**

次いで、基板を真空チャンバーに搬入して、図15(B)に示すように、シランガス及び微量のフォスフィンガスに曝した後、微結晶半導体膜を成膜する。微結晶半導体膜は、代表的には、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>などの水素化珪素を水素で希釈してプラズマ生成することで成膜することができる。シランガスの流量の100倍を超える2000倍以下の流量の水素を用いて、リン及び水素を含む微結晶半導体膜353を形成することができる。微量のフォスフィンガスに曝すことにより、結晶核発生を助長して微結晶半導体膜353を成膜する。この微結晶半導体膜353は、リンの濃度がゲート絶縁膜界面から離れる距離の増大に従って減少する濃度プロファイルを示す。

30

**【0218】**

次いで、同じチャンバーで成膜条件を変更し、水素化珪素の流量の1倍以上10倍以下、更に好ましくは1倍以上5倍以下の流量の水素を用いて、水素を含む非晶質シリコンからなるバッファ層54を積層する。ここまで工程を終えた断面図が図15(C)に相当する。

**【0219】**

次いで、バッファ層54の成膜後、大気に触れさせることなく基板を搬送し、微結晶半導体膜353及びバッファ層54を成膜する真空チャンバーとは異なる真空チャンバーで一導電型を付与する不純物が添加された半導体膜55を成膜する。半導体膜55の成膜以降の工程は、実施の形態6と同一であるため、ここでは詳細な説明は省略する。

40

**【0220】**

本実施の形態は、実施の形態1、実施の形態2、実施の形態3、実施の形態4、実施の形態5または実施の形態6と自由に組み合わせることができる。

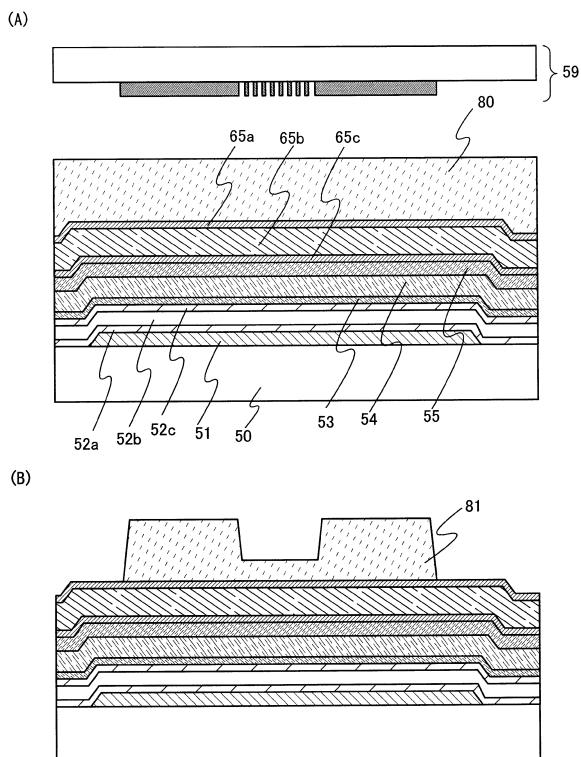

**【0221】****(実施の形態8)**

実施の形態2とは異なる薄膜トランジスタの作製方法について、図16乃至図18を用いて説明する。ここでは、上記実施の形態6と比べフォトマスク数を削減することが可能なプロセスを用いて薄膜トランジスタを作製する工程について示す。

50

**【0222】**

実施の形態6に示した図9(A)と同様に、基板50上に導電膜を形成し、導電膜上にレジストを塗布し、多階調マスクを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて導電膜の一部をエッチングして、ゲート電極51を形成する。ここでは図示しないが、適宜、テーパー角が異なる側面を有するゲート電極またはゲート配線を形成する。次に、ゲート電極51上に、ゲート絶縁膜52a、52b、52cを順に形成する。

**【0223】**

次に、第1の成膜条件で微結晶半導体膜53を形成する。引き続き、同じチャンバーで第2の成膜条件で成膜を行って、実施の形態6に示した図9(C)と同様に、微結晶半導体膜53を形成する。次に、実施の形態6に示した図9(D)と同様に、微結晶半導体膜53上に、バッファ層54、一導電型を付与する不純物が添加された半導体膜55を順に形成する。

10

**【0224】**

次に、一導電型を付与する不純物が添加された半導体膜55上に導電膜65a～65cを形成する。次に、図16(A)に示すように、導電膜65a上にレジスト80を塗布する。

**【0225】**

レジスト80は、ポジ型レジストまたはネガ型レジストを用いることができる。ここでは、ポジ型レジストを用いて示す。

20

**【0226】**

次に、第2のフォトマスクとして多階調マスク59を用いて、レジスト80に光を照射して、レジスト80を露光する。

**【0227】**

多階調マスクを用いて露光した後、現像することで、図16(B)に示すように、膜厚の異なる領域を有するレジストマスク81を形成することができる。

**【0228】**

次に、レジストマスク81をマスクとして、微結晶半導体膜53、バッファ層54、一導電型を付与する不純物が添加された半導体膜55、及び導電膜65a～65cをエッチングし分離する。この結果、図17(A)に示すような、微結晶半導体膜61、バッファ層62、一導電型を付与する不純物が添加された半導体膜63、及び導電膜85a～85cを形成することができる。

30

**【0229】**

次に、レジストマスク81をアッシングする。この結果、レジストの面積が縮小し、厚さが薄くなる。このとき、膜厚の薄い領域のレジスト(ゲート電極51の一部と重畠する領域)は除去され、図17(A)に示すように、分離されたレジストマスク86を形成することができる。

**【0230】**

次に、レジストマスク86を用いて、導電膜85a～85cをエッチングし分離する。この結果、図17(B)に示すような、一対のソース電極及びドレイン電極92a～92cを形成することができる。レジストマスク86を用いて導電膜85a～85cをウエットエッチングすると、導電膜85a～85cの端部が選択的にエッチングされる。この結果、レジストマスク86より面積の小さいソース電極及びドレイン電極92a～92cを形成することができる。

40

**【0231】**

次に、レジストマスク86を用いて、一導電型を付与する不純物が添加された半導体膜63をエッチングして、一対のソース領域及びドレイン領域88を形成する。なお、当該エッチング工程において、バッファ層62の一部もエッチングする。一部エッチングされたバッファ層をバッファ層87と示す。なお、バッファ層87には凹部が形成される。ソース領域及びドレイン領域の形成工程と、バッファ層の窪み(溝)とを同一工程で形成す

50

ることができる。ここでは、バッファ層 8 7 の一部が、レジストマスク 8 1 と比較して面積が縮小したレジストマスク 8 6 で一部エッチングされたため、ソース領域及びドレイン領域 8 8 の外側にバッファ層 8 7 が突出した形状となる。この後、レジストマスク 8 6 を除去する。また、ソース電極及びドレイン電極 9 2 a ~ 9 2 c の端部と、ソース領域及びドレイン領域 8 8 の端部は一致せずずれており、ソース電極及びドレイン電極 9 2 a ~ 9 2 c の端部の外側に、ソース領域及びドレイン領域 8 8 の端部が形成される。

#### 【0232】

図 17 (C) に示すように、ソース電極及びドレイン電極 9 2 a ~ 9 2 c の端部と、ソース領域及びドレイン領域 8 8 の端部は一致せずずれた形状となることで、ソース電極及びドレイン電極 9 2 a ~ 9 2 c の端部の距離が離れるため、ソース電極及びドレイン電極間のリーク電流やショートを防止することができる。また、ソース電極及びドレイン電極 9 2 a ~ 9 2 c の端部と、ソース領域及びドレイン領域 8 8 の端部は一致せずずれた形状であるため、ソース電極及びドレイン電極 9 2 a ~ 9 2 c 及びソース領域及びドレイン領域 8 8 の端部に電界が集中せず、ゲート電極 5 1 と、ソース電極及びドレイン電極 9 2 a ~ 9 2 c との間でのリーク電流を防止することができる。

#### 【0233】

以上の工程により、薄膜トランジスタ 8 3 を形成することができる。また、2枚のフォトマスクを用いて薄膜トランジスタを形成することができる。

#### 【0234】

次に、図 18 (A) に示すように、ソース電極及びドレイン電極 9 2 a ~ 9 2 c 、ソース領域及びドレイン領域 8 8 、バッファ層 8 7 、微結晶半導体膜 9 0 、及びゲート絶縁膜 5 2 c 上に絶縁膜 7 6 を形成する。

#### 【0235】

次に、第3のフォトマスクを用いて形成したレジストマスクを用いて絶縁膜 7 6 の一部をエッチングしてコンタクトホールを形成する。次に、当該コンタクトホールにおいてソース電極またはドレイン電極 7 1 c に接する画素電極 7 7 を形成する。ここでは、画素電極 7 7 としては、スパッタリング法によりインジウム錫酸化物膜を成膜した後、インジウム錫酸化物膜上にレジストを塗布する。次に、第4のフォトマスクを用いてレジストを露光及び現像し、レジストマスクを形成する。次に、レジストマスクを用いてインジウム錫酸化物膜をエッチングして画素電極 7 7 を形成する。

#### 【0236】

以上により、多階調マスクを用いてマスク数を減らし、表示装置に用いることが可能な素子基板を形成することができる。

#### 【0237】

本実施の形態は、実施の形態 1 、実施の形態 2 、実施の形態 3 、実施の形態 4 、実施の形態 5 、実施の形態 6 、または実施の形態 7 と自由に組み合わせることができる。

#### 【0238】

##### (実施の形態 9 )

本実施の形態では、多階調マスクを用いて保持容量を形成する工程と薄膜トランジスタと画素電極のコンタクトを形成する工程について示す。なお、図 19 において、実施の形態 6 と同一の箇所は、実施の形態 6 と同じ符号を用いる。

#### 【0239】

実施の形態 6 に従って、絶縁膜 7 6 を形成する工程まで終えた後、多階調マスクを用いて深さの異なる開口を有する第 1 の層間絶縁膜 8 4 a を形成する。ここでは容量部となる容量配線の側面の角度は、図 19 (A) に示すように、ゲート電極の側面の角度よりも大きい。多階調マスクにより配線側面の角度を異ならせて配線幅を場所毎に制御することで画素部の開口率を向上させている。この段階の断面図が図 19 (A) に相当する。

#### 【0240】

図 19 (A) に示すように、ソース電極またはドレイン電極 7 1 c の上方に絶縁膜 7 6 の表面を露呈する第 1 の開口と、第 1 の導電層 7 8 a と第 2 の導電層 7 8 b との積層からな

10

20

30

40

50

る容量配線上に第1の開口よりも浅い深さの第2の開口が設けられる。なお、容量配線の第1の導電層78aと第2の導電層78bは、それぞれゲート電極の第1の導電層51aと第2の導電層51bと同じ工程で形成される。

#### 【0241】

次いで、第1の層間絶縁膜84aをマスクとして絶縁膜76の一部を選択的にエッティングしてソース電極またはドレイン電極71cの一部を露呈させる。

#### 【0242】

次いで、第2の開口が拡大して絶縁膜76の表面を露呈するまで第1の層間絶縁膜84aをアッシングする。同時に第1の開口も拡大するが、絶縁膜76に形成した開口のサイズは変わらないため、段差が形成される。

10

#### 【0243】

次いで、画素電極77を形成する。この段階の断面図が図19(C)に相当する。アッシングにより第1の層間絶縁膜は第2の層間絶縁膜84bに縮小される。また、保持容量75は、誘電体として絶縁膜76とゲート絶縁膜52を用い、一対の電極として容量配線と画素電極77とを用いる。

#### 【0244】

こうして、多階調マスクを用いて少ない工程数で保持容量を形成することができる。

#### 【0245】

本実施の形態は、実施の形態1、実施の形態2、実施の形態3、実施の形態4、実施の形態5、実施の形態6、実施の形態7、または実施の形態8と自由に組み合わせることができる。

20

#### 【0246】

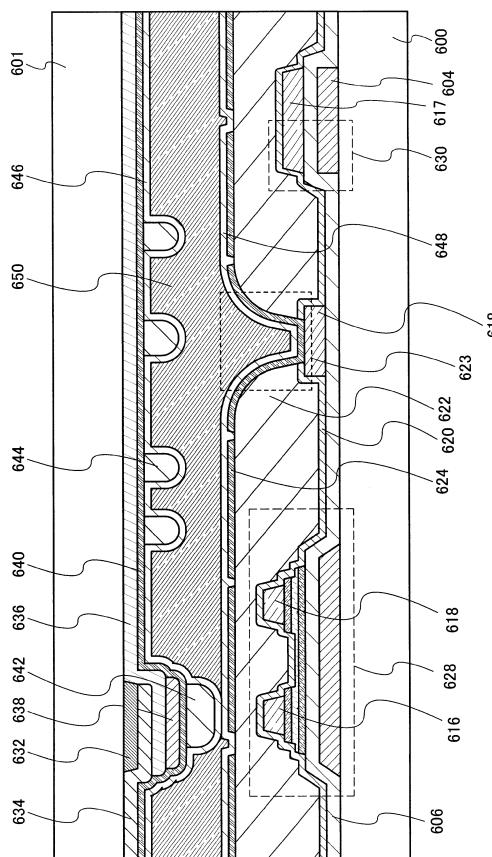

##### (実施の形態10)

本実施の形態では、表示装置の一形態として、実施の形態6で示す薄膜トランジスタを有する液晶表示装置について、以下に示す。

#### 【0247】

はじめにVA(Vertical Alignment)型の液晶表示装置について示す。VA型の液晶表示装置とは、液晶パネルの液晶分子の配列を制御する方式の一種である。VA型の液晶表示装置は、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く方式である。本実施の形態では、特に画素(ピクセル)をいくつかの領域(サブピクセル)に分け、それぞれ別の方向に分子を倒すよう工夫されている。これをマルチドメイン化あるいはマルチドメイン設計という。以下の説明では、マルチドメイン設計が考慮された液晶表示装置について説明する。

30

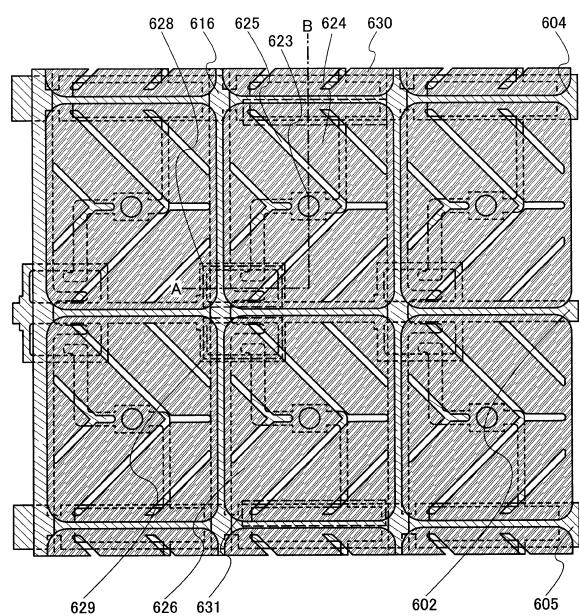

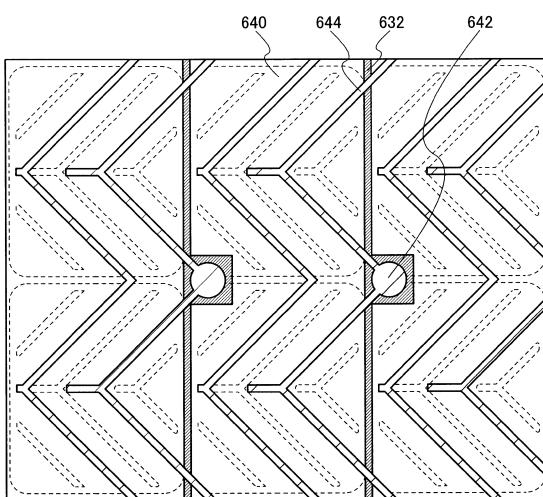

#### 【0248】

図21及び図22は、それぞれ画素電極及び対向電極を示している。なお、図21は画素電極が形成される基板側の平面図であり、図中に示す切断線A-Bに対応する断面構造を図20に表している。また、図22は対向電極が形成される基板側の平面図である。以下の説明ではこれらの図を参照して説明する。

#### 【0249】

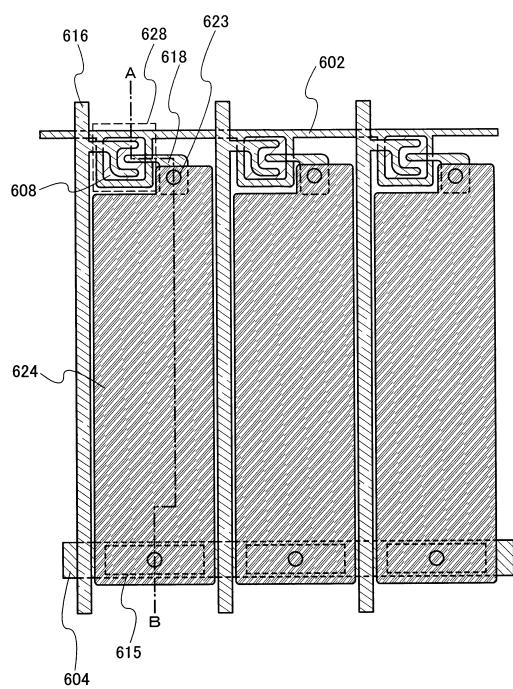

図20は、TFT628とそれに接続する画素電極624、及び保持容量部630が形成された基板600と、対向電極640等が形成される対向基板601とが重ね合わせられ、液晶が注入された状態を示している。

40

#### 【0250】

対向基板601においてスペーサ642が形成される位置には、遮光膜632、第1の着色膜634、第2の着色膜636、第3着色膜638、対向電極640が形成されている。この構造により、液晶の配向を制御するための突起644とスペーサ642の高さを異ならせている。画素電極624上には配向膜648が形成され、同様に対向電極640上にも配向膜646が形成されている。この間に液晶層650が形成されている。

#### 【0251】

スペーサ642はここでは柱状スペーサを用いて示したがビーズスペーサを散布してもよ

50

い。さらには、スペーサ 642 を基板 600 上に形成される画素電極 624 上に形成してもよい。

#### 【0252】

基板 600 上には、TFT628 とそれに接続する画素電極 624、及び保持容量部 630 が形成される。画素電極 624 は、TFT628、配線、及び保持容量部 630 を覆う絶縁膜 620、絶縁膜を覆う第 3 絶縁膜 622 をそれぞれ貫通するコンタクトホール 623 で、配線 618 と接続する。また、多階調マスクを用いて、配線 618 と TFT628 のソース電極またはドレイン電極を選択的にエッチングし、配線 618 の側面角度は、TFT628 のソース電極またはドレイン電極の側面角度よりも大きくして開口率向上に寄与している。TFT628 は実施の形態 6 で示す薄膜トランジスタを適宜用いることができる。また、保持容量部 630 は、実施の形態 2 に従って TFT628 のゲート配線 602 と同じ多階調マスクで形成した第 1 の容量配線 604 と、ゲート絶縁膜 606 と、配線 616、618 と同様に形成した第 2 の容量配線 617 で構成される。また、第 1 の容量配線 604 の側面角度は、TFT628 の配線 616、618 の側面角度よりも大きくして開口率向上に寄与している。10

#### 【0253】

画素電極 624 と液晶層 650 と対向電極 640 が重なり合うことで、液晶素子が形成されている。

#### 【0254】

図 21 に基板 600 上の構造を示す。画素電極 624 は実施の形態 6 で示した材料を用いて形成する。画素電極 624 にはスリット 625 を設ける。スリット 625 は液晶の配向を制御するためのものである。20

#### 【0255】

図 21 に示す TFT629 とそれに接続する画素電極 626 及び保持容量部 631 は、それぞれ TFT628、画素電極 624 及び保持容量部 630 と同様に形成することができる。TFT628 と TFT629 は共に配線 616 と接続している。この液晶パネルの画素（ピクセル）は、画素電極 624 と画素電極 626 により構成されている。画素電極 624 と画素電極 626 はサブピクセルである。

#### 【0256】

図 22 に対向基板側の構造を示す。遮光膜 632 上に対向電極 640 が形成されている。対向電極 640 は、画素電極 624 と同様の材料を用いて形成することが好ましい。対向電極 640 上には液晶の配向を制御する突起 644 が形成されている。また、遮光膜 632 の位置に合わせてスペーサ 642 が形成されている。30

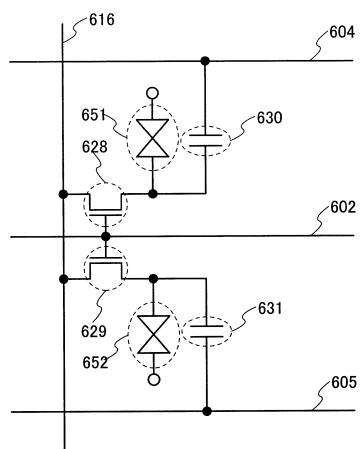

#### 【0257】

この画素構造の等価回路を図 23 に示す。TFT628 と TFT629 は、共にゲート配線 602、配線 616 と接続している。この場合、第 1 の容量配線 604 と第 3 の容量配線 605 の電位を異ならせることで、液層素子 651 と液層素子 652 の動作を異ならせることができる。すなわち、第 1 の容量配線 604 と第 3 の容量配線 605 の電位を個別に制御することにより液晶の配向を精密に制御して視野角を広げている。40

#### 【0258】

スリット 625 を設けた画素電極 624 に電圧を印加すると、スリット 625 の近傍には電界の歪み（斜め電界）が発生する。このスリット 625 と、対向基板 601 側の突起 644 とを交互に咬み合うように配置することで、斜め電界が効果的に発生させて液晶の配向を制御することで、液晶が配向する方向を場所によって異ならせている。すなわち、マルチドメイン化して液晶パネルの視野角を広げている。

#### 【0259】

上述では、VA 型の液晶表示装置の一例を示したが図 21 に示す画素電極構造に特に限定されない。

#### 【0260】

次に、TN 型の液晶表示装置の形態について示す。50

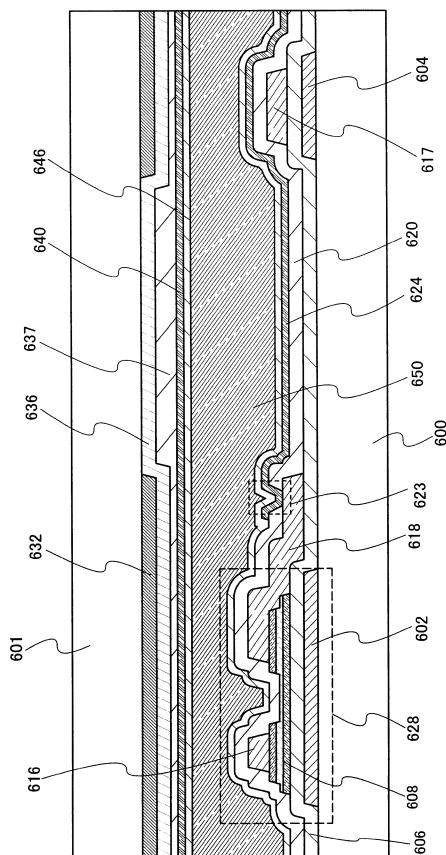

**【0261】**

図24と図25は、TN型の液晶表示装置の画素構造を示している。図25は平面図であり、図中に示す切断線A-Bに対応する断面構造を図24に表している。以下の説明ではこの両図を参照して説明する。なお、図24及び図25において、図20と同じ部位には同じ符号を用いる。

**【0262】**

画素電極624はコンタクトホール623により、配線618でTFT628と接続している。データ線として機能する配線616は、TFT628と接続している。TFT628は実施の形態2に示すTFTのいずれかを適用することができる。

**【0263】**

画素電極624は、実施の形態2で示す画素電極77を用いて形成されている。

10

**【0264】**

対向基板601には、遮光膜632、第2の着色膜636、対向電極640が形成されている。また、第2の着色膜636と対向電極640の間には平坦化膜637が形成され、液晶の配向乱れを防いでいる。液晶層650は画素電極624と対向電極640の間に形成されている。

**【0265】**

画素電極624と液晶層650と対向電極640が重なり合うことで、液晶素子が形成されている。

**【0266】**

また、基板600または対向基板601にカラーフィルタや、ディスクリネーションを防ぐための遮蔽膜（ブラックマトリクス）などが形成されていても良い。また、基板600の薄膜トランジスタが形成されている面とは逆の面に偏光板を貼り合わせ、また対向基板601の対向電極640が形成されている面とは逆の面に、偏光板を貼り合わせておく。

20

**【0267】**

以上の工程により、液晶表示装置を作製することができる。本実施の形態の液晶表示装置は、オフ電流が少なく、電気特性が優れ、信頼性の高い薄膜トランジスタを用いているため、コントラストが高く、視認性の高い液晶表示装置である。また、多階調マスクを用いて、配線の側面角度を場所毎に調節することで、開口率の高い液晶表示装置を実現している。また、多階調マスクを用いて、配線の側面角度を場所毎に調節することで、配線端部の上方での断線や、短絡不良を低減している。

30

**【0268】**

また、本発明は横電界方式の液晶表示装置に応用することもできる。横電界方式は、セル内の液晶分子に対して水平方向に電界を加えることで液晶を駆動して階調表現する方式である。この方式によれば、視野角を約180度にまで広げることができる。

**【0269】**

本実施の形態は、実施の形態1、実施の形態2、実施の形態3、実施の形態4、実施の形態5、実施の形態6、実施の形態7、実施の形態8、または実施の形態9と自由に組み合わせることができる。

40

**【0270】****(実施の形態11)**

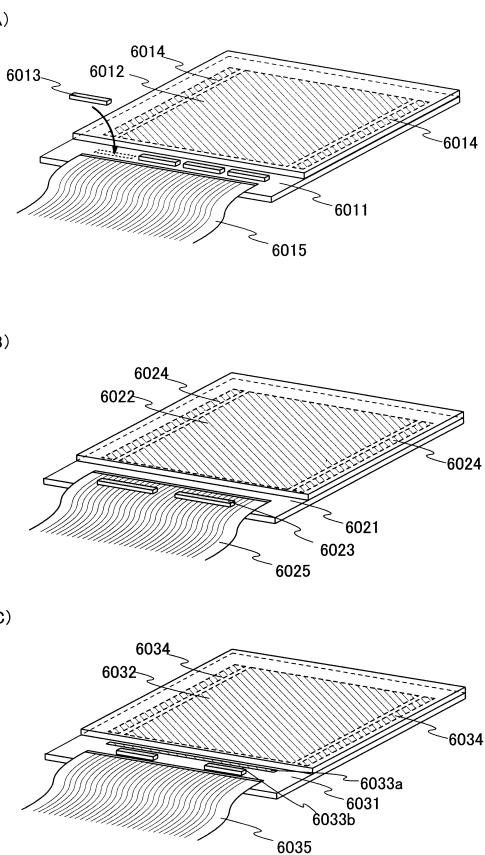

本発明の液晶表示装置の一形態である表示パネルの構成について、以下に示す。

**【0271】**

図26(A)に、信号線駆動回路6013のみを別途形成し、基板6011上に形成された画素部6012と接続している表示パネルの形態を示す。画素部6012及び走査線駆動回路6014は、微結晶半導体膜を用いた薄膜トランジスタを用いて形成する。微結晶半導体膜を用いた薄膜トランジスタよりも高い移動度が得られるトランジスタで信号線駆動回路を形成することで、走査線駆動回路よりも高い駆動周波数が要求される信号線駆動回路の動作を安定させることができる。なお、信号線駆動回路6013は、単結晶の半

50

導体を用いたトランジスタ、多結晶の半導体を用いた薄膜トランジスタ、またはS O I を用いたトランジスタであっても良い。画素部 6 0 1 2 と、信号線駆動回路 6 0 1 3 と、走査線駆動回路 6 0 1 4 とに、それぞれ電源の電位、各種信号等が、F P C 6 0 1 5 を介して供給される。

#### 【 0 2 7 2 】

なお、信号線駆動回路及び走査線駆動回路を、共に画素部と同じ基板上に形成しても良い。

#### 【 0 2 7 3 】

また、駆動回路を別途形成する場合、必ずしも駆動回路が形成された基板を、画素部が形成された基板上に貼り合わせる必要はなく、例えばF P C 上に貼り合わせるようにしても良い。図 2 6 ( B ) に、信号線駆動回路 6 0 2 3 のみを別途形成し、基板 6 0 2 1 上に形成された画素部 6 0 2 2 及び走査線駆動回路 6 0 2 4 と接続している液晶表示装置パネルの形態を示す。画素部 6 0 2 2 及び走査線駆動回路 6 0 2 4 は、微結晶半導体膜を用いた薄膜トランジスタを用いて形成する。信号線駆動回路 6 0 2 3 は、F P C 6 0 2 5 を介して画素部 6 0 2 2 と接続されている。画素部 6 0 2 2 と、信号線駆動回路 6 0 2 3 と、走査線駆動回路 6 0 2 4 とに、それぞれ電源の電位、各種信号等が、F P C 6 0 2 5 を介して供給される。

#### 【 0 2 7 4 】

また、信号線駆動回路の一部または走査線駆動回路の一部のみを、微結晶半導体膜を用いた薄膜トランジスタを用いて画素部と同じ基板上に形成し、残りを別途形成して画素部と電気的に接続するようにしても良い。図 2 6 ( C ) に、信号線駆動回路が有するアナログスイッチ 6 0 3 3 a を、画素部 6 0 3 2 、走査線駆動回路 6 0 3 4 と同じ基板 6 0 3 1 上に形成し、信号線駆動回路が有するシフトレジスタ 6 0 3 3 b を別途異なる基板に形成して貼り合わせる液晶表示装置パネルの形態を示す。画素部 6 0 3 2 及び走査線駆動回路 6 0 3 4 は、微結晶半導体膜を用いた薄膜トランジスタを用いて形成する。信号線駆動回路が有するシフトレジスタ 6 0 3 3 b は、F P C 6 0 3 5 を介して画素部 6 0 3 2 と接続されている。画素部 6 0 3 2 と、信号線駆動回路と、走査線駆動回路 6 0 3 4 とに、それぞれ電源の電位、各種信号等が、F P C 6 0 3 5 を介して供給される。

#### 【 0 2 7 5 】

図 2 6 に示すように、液晶表示装置は、駆動回路の一部または全部を、画素部と同じ基板上に、微結晶半導体膜を用いた薄膜トランジスタを用いて形成することができる。

#### 【 0 2 7 6 】

なお、別途形成した基板の接続方法は、特に限定されるものではなく、公知のC O G 方法、ワイヤボンディング方法、或いはT A B 方法などを用いることができる。また接続する位置は、電気的な接続が可能であるならば、図 2 6 に示した位置に限定されない。また、コントローラ、C P U 、メモリ等を別途形成し、接続するようにしても良い。

#### 【 0 2 7 7 】

なお本実施の形態で用いる信号線駆動回路は、シフトレジスタとアナログスイッチのみを有する形態に限定されない。シフトレジスタとアナログスイッチに加え、バッファ、レベルシフタ、ソースフォロワ等、他の回路を有していても良い。また、シフトレジスタとアナログスイッチは必ずしも設ける必要はなく、例えばシフトレジスタの代わりにデコード回路のような信号線の選択ができる別の回路を用いても良いし、アナログスイッチの代わりにラッチ等を用いても良い。

#### 【 0 2 7 8 】

本実施の形態は、実施の形態 1 、実施の形態 2 、実施の形態 3 、実施の形態 4 、実施の形態 5 、実施の形態 6 、実施の形態 7 、実施の形態 8 、実施の形態 9 または実施の形態 1 0 と自由に組み合わせることができる。

#### 【 0 2 7 9 】

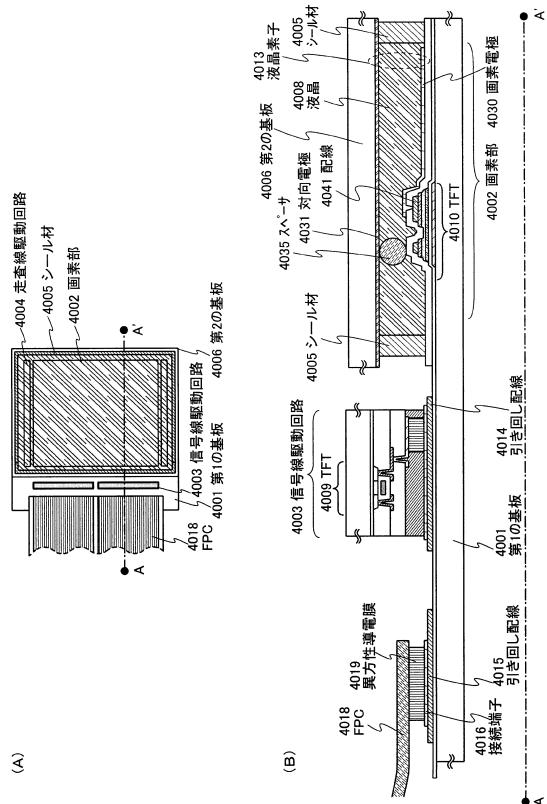

( 実施の形態 1 2 )

本発明の表示装置の一形態に相当する液晶表示パネルの外観及び断面について、図 2 7 を

10

20

30

40

50

用いて説明する。図27(A)は、第1の基板4001上に形成された微結晶半導体膜を有する薄膜トランジスタ4010及び液晶素子4013を、第2の基板4006との間にシール材4005によって封止した、パネルの上面図であり、図27(B)は、図27(A)のA-A'における断面図相当する。

#### 【0280】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられている。よって画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、液晶4008と共に封止されている。また第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に多結晶半導体膜で形成された信号線駆動回路4003が実装されている。なお本実施の形態では、多結晶半導体膜を用いた薄膜トランジスタを有する信号線駆動回路を、第1の基板4001に貼り合わせる例について説明するが、単結晶半導体を用いた薄膜トランジスタで信号線駆動回路を形成し、貼り合わせるようにしても良い。図27では、信号線駆動回路4003に含まれる、多結晶半導体膜で形成された薄膜トランジスタ4009を例示する。

#### 【0281】

また第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、薄膜トランジスタを複数有しており、図27(B)では、画素部4002に含まれる薄膜トランジスタ4010とを例示している。薄膜トランジスタ4010は微結晶半導体膜を用いた薄膜トランジスタに相当する。

#### 【0282】

また4011は液晶素子に相当し、液晶素子4013が有する画素電極4030は、薄膜トランジスタ4010と配線4041を介して電気的に接続されている。そして液晶素子4013の対向電極4031は第2の基板4006上に形成されている。画素電極4030と対向電極4031と液晶4008とが重なっている部分が、液晶素子4013に相当する。

#### 【0283】

なお、第1の基板4001、第2の基板4006としては、ガラス、金属（代表的にはステンレス）、セラミックス、プラスチックを用いることができる。プラスチックとしては、F R P (F i b e r g l a s s - R e i n f o r c e d P l a s t i c s ) 板、P V F (ポリビニルフルオライド) フィルム、ポリエステルフィルム、またはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをP V F フィルムやポリエスチルフィルムで挟んだ構造のシートを用いることもできる。

#### 【0284】

また4035は球状のスペーサであり、画素電極4030と対向電極4031との間の距離（セルギャップ）を制御するために設けられている。なお絶縁膜を選択的にエッティングすることで得られるスペーサを用いていても良い。

#### 【0285】

また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、引き回し配線4014、4015を介して、F P C 4018から供給されている。

#### 【0286】

本実施の形態では、接続端子4016が、液晶素子4013が有する画素電極4030と同じ導電膜から形成されている。また、引き回し配線4014、4015は、配線4041と同じ導電膜で形成されている。実施の形態1に示すように、多階調マスクを用いることによって、引き回し配線4014、4015の側面の角度は、配線4041よりも大きい。隣り合う引き回し配線間で短絡が生じないように両側面の垂直に加工することは効果的である。

#### 【0287】

10

20

30

40

50

接続端子 4016 は、FPC 4018 が有する端子と、異方性導電膜 4019 を介して電気的に接続されている。

#### 【0288】

なお図示していないが、本実施の形態に示した液晶表示装置は配向膜、偏光板を有し、更にカラーフィルタや遮蔽膜を有していても良い。

#### 【0289】

また図27では、信号線駆動回路 4003 を別途形成し、第1の基板 4001 に実装している例を示しているが、本実施の形態はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

10

#### 【0290】

本実施の形態は、他の実施の形態に記載した構成と組み合わせて実施することが可能である。

#### 【0291】

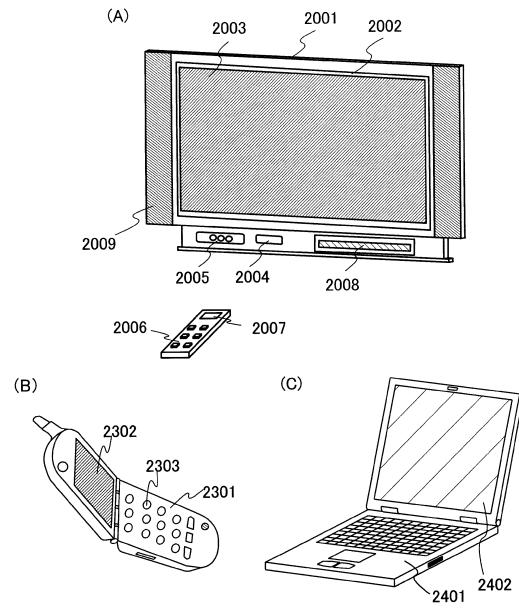

##### (実施の形態 13)

本発明により得られる表示装置等によって、アクティブマトリクス型表示装置モジュールに用いることができる。即ち、それらを表示部に組み込んだ電子機器全てに本発明を実施できる。

#### 【0292】

その様な電子機器としては、ビデオカメラ、デジタルカメラ等のカメラ、ヘッドマウントディスプレイ（ゴーグル型ディスプレイ）、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話または電子書籍等）などが挙げられる。それらの一例を図28に示す。

20

#### 【0293】

図28(A)はテレビジョン装置である。表示モジュールを、図28(A)に示すように、筐体に組みこんで、テレビジョン装置を完成させることができる。FPCまで取り付けられた表示パネルのことを表示モジュールとも呼ぶ。表示モジュールにより主画面2003が形成され、その他付属設備としてスピーカー部2009、操作スイッチなどが備えられている。このように、テレビジョン装置を完成させることができる。

#### 【0294】

30

図28(A)に示すように、筐体2001に表示素子を利用した表示用パネル2002が組みこまれ、受信機2005により一般的のテレビ放送の受信をはじめ、モデム2004を介して有線又は無線による通信ネットワークに接続することにより一方向（送信者から受信者）又は双方向（送信者と受信者間、又は受信者間同士）の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操作機2006により行うことが可能であり、このリモコン装置にも出力する情報を表示する表示部2007が設けられていても良い。

#### 【0295】

また、テレビジョン装置にも、主画面2003の他にサブ画面2008を第2の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成において、主画面2003を視野角の優れた液晶表示パネルで形成し、サブ画面2008を低消費電力で表示可能な発光表示パネルで形成しても良い。また、低消費電力化を優先させるためには、主画面2003を発光表示パネルで形成し、サブ画面を発光表示パネルで形成し、サブ画面は点滅可能とする構成としても良い。

40

#### 【0296】

勿論、本発明はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表示媒体としても様々な用途に適用することができる。

#### 【0297】

図28(B)は携帯電話機2301の一例を示している。この携帯電話機2301は、表

50

示部 2302、操作部 2303などを含んで構成されている。表示部 2302においては、上記実施の形態で説明した表示装置を適用することで、量産性を高めることができる。

### 【0298】

また、図 28 (C) に示す携帯型のコンピュータは、本体 2401、表示部 2402 等を含んでいる。表示部 2402 に、上記実施の形態に示す表示装置を適用することにより、量産性を高めることができる。

### 【符号の説明】

#### 【0299】

|                      |    |

|----------------------|----|

| 101 : 基板             | 10 |

| 102 : ゲート絶縁膜         |    |

| 103 : 第 1 の導電層       |    |

| 106 : ソース領域及びドレイン領域  |    |

| 107a : 第 1 の配線層      |    |

| 107b : 第 2 の配線層      |    |

| 108 : ソース領域及びドレイン領域  |    |

| 109 : ソース電極またはドレイン電極 |    |

| 110 : ソース電極またはドレイン電極 |    |

| 111 : 絶縁膜            |    |

| 112 : 画素電極           | 20 |

| 113 : 接続電極           |    |

| 116 : 第 1 の接続電極      |    |

| 117 : 第 2 の接続電極      |    |

| 118 : 画素電極           |    |

| 119 : 第 3 の接続電極      |    |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

---

フロントページの続き

(51)Int.Cl. F I

|                         |               |         |

|-------------------------|---------------|---------|

| H 01 L 29/423 (2006.01) | H 01 L 29/50  | M       |

| H 01 L 29/417 (2006.01) | G 02 F 1/1368 |         |

| G 02 F 1/1368 (2006.01) | H 01 L 29/78  | 6 2 7 C |

| H 01 L 21/336 (2006.01) |               |         |

(56)参考文献 特開2004-199074 (JP, A)

特開2001-053283 (JP, A)

特開2007-293071 (JP, A)

特開2007-299833 (JP, A)

特開2003-223119 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 336、29 / 786