## **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

#### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification <sup>3</sup>:

A1

(11) International Publication Number: WO 80/00633

(43) International Publication Date: 3 April 1980 (03.04.80)

(21) International Application Number: PCT/US79/00660

(22) International Filing Date: 23 August 1979 (23.08.79)

(31) Priority Application Number:

939,021

(32) Priority Date:

1 September 1978 (01.09.78)

(33) Priority Country:

US

(71) Applicant: NCR CORPORATION [US/US]; World Headquarters, Dayton, OH 45479 (US).

(72) Inventor: WARD, William, Pearson; 9330 Sea Turtle Manor, Plantation, FL 33324 (US).

(74) Agents: DUGAS, Edward et al.; Patent Division, NCR Corporation, World Headquarters, Dayton, OH 45479 (US). (81) Designated States: DE (European patent), FR (European patent), GB (European patent), JP, NL (European patent).

#### **Published**

With international search report

(54) Title: DATA STORAGE SYSTEM FOR STORING MULTILEVEL SIGNALS

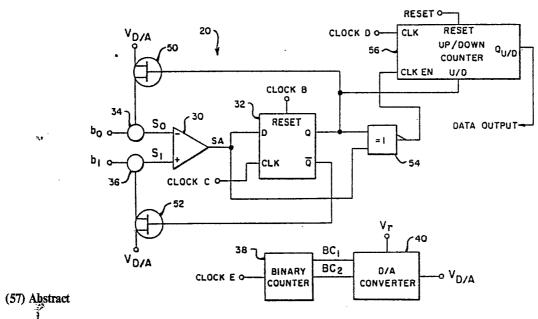

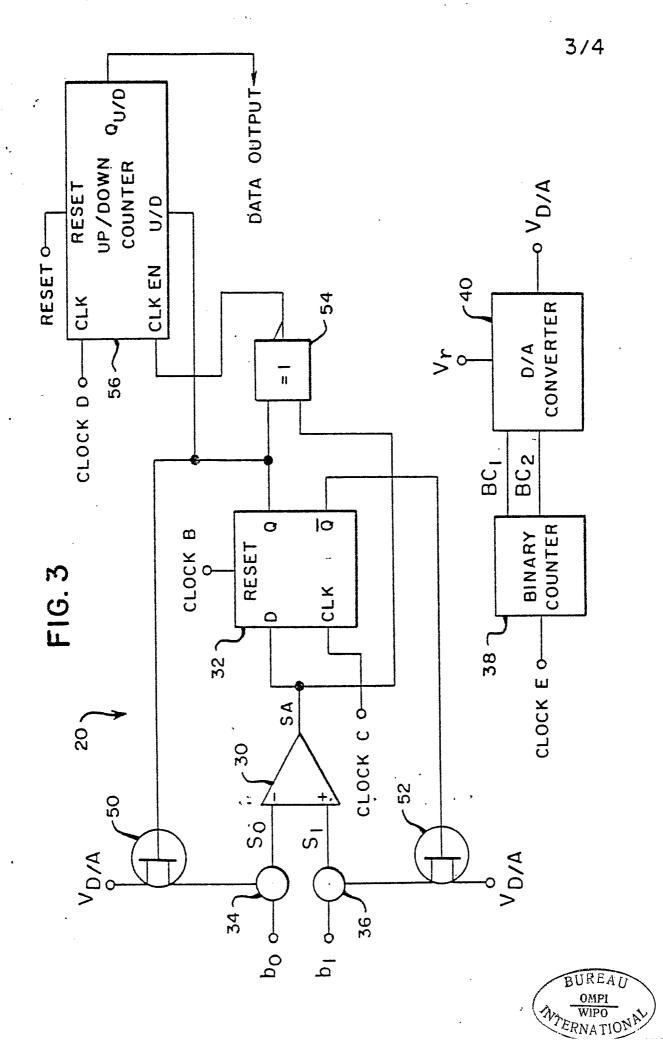

A data storage system (10) for storing multilevel, non-binary data includes a charge coupled device shift register (12) and a detection circuit (20) for detecting the data level represented by the charge or signal within each cell location of the shift register (12). The detection circuit (20) includes a sense amplifier (30) for comparing the signals from two adjacent cell locations (b0, b1), with one signal representing a known data level. The comparison of adjacent cell locations compensates for signal losses during shifting, since the losses experienced by adjacent cell locations are nearly identical. Switching transistors (50, 52) cause the output of an incrementing digital-to-analog converter (40) to be added to one of the signals prior to comparison. The output of the sense amplifier (30) is provided to a flip-flop (32), which controls the switching transistors (50, 52). The outputs of the sense amplifier (30) and flip-flop (32) are connected to an EXCLUSIVE NOR gate (54), whose output enables an up/down counter (56), which in turn provides a detected data level.

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT

| ΑT | Austria                      | LU | Luxembourg               |

|----|------------------------------|----|--------------------------|

| BR | Brazil                       | MC | Monaco                   |

| CF | Central African Republic     | MG | Madagascar               |

| CG | Congo                        | MW | Malaŵi                   |

| CH | Switzerland                  | NL | Netherlands              |

| CM | Cameroon                     | RO | Romania                  |

| DE | Germany, Federal Republic of | SE | Sweden                   |

| DK | Denmark                      | SN | Senegal                  |

| FR | France                       | SU | Soviet Union             |

| GA | Gabon                        | TD | Chad                     |

| GB | United Kingdom               | TG | Togo                     |

| JP | Japan                        | US | United States of America |

|    |                              |    |                          |

15

20

25

30

# DATA STORAGE SYSTEM FOR STORING MULTILEVEL SIGNALS

#### Technical Field

This invention relates to data storage systems of the kind including a charge transfer device shift register having a plurality of storage cells, each storage cell adapted to store multilevel data in the form of a charge having one of at least three data levels, and a detection circuit adapted to detect the data stored in a first one of said storage cells.

One example of a charge transfer device shift register is a charge coupled device (CCD) shift register.

#### Background Art

One problem associated with charge transfer shift registers is the difficulty of accurately and reliably detecting the data stored in the shift register, since charge losses tend to occur during shifting. Charge losses can vary from device to device and may be affected by variations in temperature, clocking frequency and the physical dimensions within the device.

A data storage system of the kind specified is known from U.S. Patent Specification No. 3,929,171. According to this known system a recirculating charge transfer device shift register is used to store analog data and a variable gain amplifier is included in a recirculation path between the shift register output and input. The gain of this amplifier is periodically adjusted so as to maintain the overall loop gain of the system at unity, gain adjustment being effected under the control of a comparator which compares the amplitudes of a reference signal pulse before and after propagation through the shift register.

#### Disclosure of the Invention

The known system has the disadvantage of

10

15

20

25

30

35

being complex and expensive in view of the need to provide and control a variable gain amplifier.

It is an object of the present invention to provide a data storage system of the kind specified wherein the aforementioned disadvantage is alleviated.

Therefore, according to the present invention there is provided a data storage system of the kind specified characterized by means adapted to provide signals respectively representing the data stored in a first storage cell, and known data stored in a second one of said storage cells, which is adjacent to said first storage cell, said detection circuit including: summing means adapted to add an adjustment signal including an incrementally changing component to one of the data-representing signals thereby providing first and second signals; comparison means adapted to compare said first and second signals thereby providing a comparison signal; and incrementable means adapted to initially provide an output signal having a value representing said known data and capable of changing said output signal incrementally in correspondence with changes in said adjustment signal and in dependence on said comparison signal until said output has a value representing the data stored in said first storage cell.

A further advantage of a data storage system according to the immediately preceding paragraph is that a high bit density system is provided in view of the multi-level data storage capacity of each storage cell. A further advantage is that a reliable detection of stored data is achieved despite cell-to-cell losses which occur during shifting.

One embodiment of the invention will now be described by way of example with reference to the accompanying drawings.

#### Brief Description of the Drawings

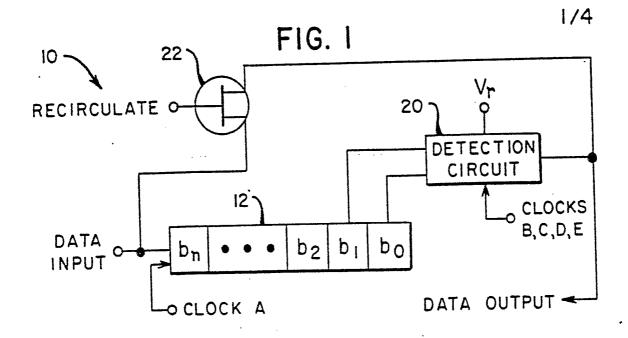

Fig. 1 illustrates a data storage system,

15

25

30

35

including a shift register and detection circuit, in accordance with the present invention.

Fig. 2 is a table comparing the amount of data stored in a single cell of a shift register in accordance with the present invention, with the same amount of data requiring two cells in a binary shift register.

Fig. 3 is a block diagram illustrating the detection circuit of Fig. 1.

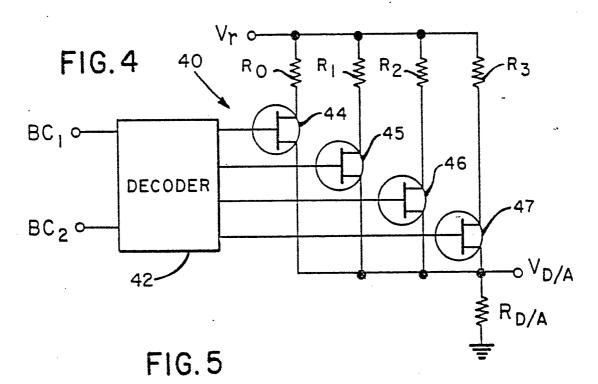

Fig. 4 is a circuit diagram illustrating the D/A converter of Fig. 3.

Fig. 5 is a table illustrating the operation of the D/A converter shown in Fig. 4.

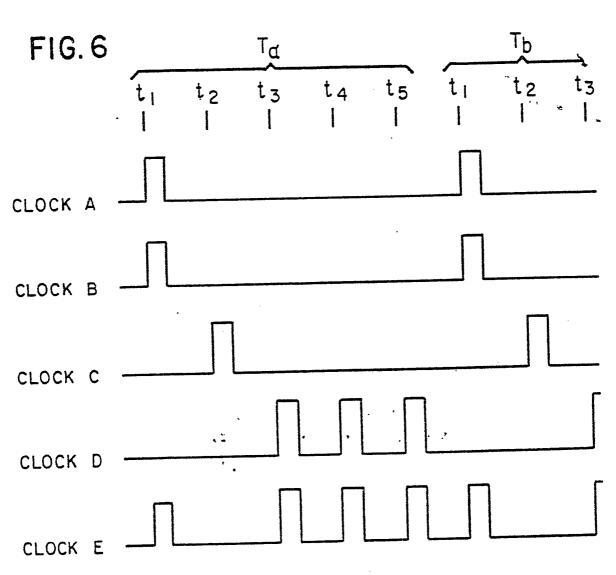

Fig. 6 is a timing diagram illustrating the clock pulses applied to the data storage system, including the detection circuit, of Fig. 1.

Fig. 7 is a table illustrating, in three exemplary cases, the operation of the detection circuit of Fig. 3.

#### 20 Best Mode for Carrying Out the Invention

Referring now to Fig. 1, a data storage system 10 is illustrated. The data storage system 10 includes a charge transfer device, such as a charge coupled device (CCD) shift register 12. A CCD, as is well known, stores charge packets in potential wells, and moves or transfers the charge packets along a series of storage or cell locations from one cell to the next, in order to function as a serial shift register. For purposes of illustration, the shifting of data within shift register 12 is shown in Fig. 1 and the timing diagram of Fig. 6 as occurring upon application of each clock pulse in a CLOCK A signal. However, it will be appreciated by those skilled in the art that in a typical CCD, plural, multiphase clock pulses are applied in a well known manner to accomplish each shift or transfer of data from one cell to the next.

20

30

The individual cells within the shift register 12 are labelled  $b_0$  through  $b_n$ . The storage system 10 stores multilevel, non-binary data and, in the disclosed embodiment, each of the cells b, through b, stores one of four possible data levels, "0", "1", "2", or "3", and each data level is represented by a different signal or voltage value. It should be apparent that, under this arrangement, the shift register 12 can store approximately twice as much data as a similar shift register storing binary data where each cell can store only one of two possible data levels. illustrated by the table of Fig. 2 wherein the four possible data levels capable of being stored in each cell of the shift register 12 are compared to the same amount of data requiring two cells of a binary shift register.

Although in the described embodiment only four data levels are stored in each cell of the shift register 12, it will be appreciated that almost any number of data levels could be stored in a single cell and be detected in accordance with the present invention. There are, of course, practical constraints in selecting the number of data levels, such as the need to limit the highest data level to the maximum voltage which the CCD can store without breakdown, and keeping a significant difference in the voltage values between successive data levels.

The two most rightward cell locations as viewed in Fig. 1,  $b_0$  and  $b_1$ , are connected to the two data inputs of a detection circuit 20. The output of the detection circuit 20 provides, in a manner which will be discussed in greater detail later, the data level of the signal within cell location  $b_1$  and regenerates that data level to its full signal or voltage value. The cell location  $b_0$  is initially loaded with a reference or marker signal, and thus the shift register 12 can store a total of n-1 data digits plus a

20

25

30

single marker digit. The marker digit is provided because data level detection is accomplished in the system 10 by sensing the difference between the voltages or signals within the two adjacent cell locations  $b_0$  and  $b_1$ , with the data level within cell location  $b_0$  always known, either because initially it is the marker digit or because it was previously determined when in the cell location  $b_1$ . The marker digit value can be any one of the four possible data levels.

The actual manner in which the register 12 is constructed in order to permit the voltages or signals in the adjacent cell locations  $b_0$  and  $b_1$  to be sensed is unimportant for purposes of the present description. However, if shift register 12 is a CCD, a conventional gate, such as a "floating gate", could be physically located at each of the two cell locations  $b_0$  and  $b_1$  in order to provide the signals at the cell locations to the detection circuit 20.

The output of the detection circuit is provided to the input of the shift register 12 by way of a field-effect transistor (FET) 22. When data is to be recirculated through the shift register, an enabling signal, designated "RECIRCULATE", is applied to the gate of FET 22. FET 22 becomes conductive and the data bit then at the  $b_0$  cell, after having been regenerated by the detection circuit 20 to its full value, is passed through the FET 22 to the  $b_0$  cell.

The detection circuit 20, in addition to receiving the data inputs from the cell locations  $\mathbf{b}_0$  and  $\mathbf{b}_1$ , also receives clocking signals CLOCK B, CLOCK C, CLOCK D and CLOCK E, which will be described in greater detail later, and a reference voltage, designated  $\mathbf{V}_r$ . The detection circuit 20 is illustrated in greater detail in Fig. 3.

In Fig. 3, the detection circuit 20 is seen to include a sense amplifier 30 and a flip-flop 32.

The amplifier 30 has a first, positive (+) input ter-

20

25

30

35

minal and a second, negative (-) input terminal. The negative input terminal of the amplifier 30 is connected to the  $b_0$  cell by a summing node 34 and the positive input terminal of the amplifier 30 is connected to the  $b_1$  cell by a summing node 36. The signals from the summing nodes 34 and 36 are designated  $S_0$  and  $S_1$ , respectively. The amplifier 30 can be a differential amplifier of conventional design that compares the signals  $S_0$  and  $S_1$ , and at its output SA provides a "0" logic level signal if  $S_0$  is larger and a "1" logic level signal if  $S_1$  is larger.

The detection circuit 20 also includes a binary counter 38 and a digital-to-analog (D/A) converter 40. The D/A converter 40 receives the two outputs BC and BC of the binary counter 38 and also the reference voltage  $V_r$ . The binary counter 38 receives the clocking signal CLOCK E, and in response to each clock pulse in the CLOCK E signal, advances by one the binary number represented at its outputs BC and BC. The D/A converter 40 converts the signals from the outputs BC and BC of the counter 38 into an incrementing adjustment signal at its output  $V_{D/A}$  having values corresponding to each of the four possible data levels "0", "1", "2" and "3". The D/A converter 40 also adds a small, constant adjustment voltage  $V_a$  to each of the data levels at its output  $V_{D/A}$ .

Fig. 4 illustrates in greater detail the D/A converter 40. The D/A converter includes a decoder 42 of conventional design that receives the signals BC<sub>1</sub> and BC<sub>2</sub> and has four outputs, each connected to the gate of one of four field-effect transistors (FET's) 44, 45, 46 and 47. Each of the FET's connects one of four resistors  $R_0$ ,  $R_1$ ,  $R_2$  and  $R_3$  to ground by way of a resistor  $R_{D/A}$ . The four resistors  $R_0$ ,  $R_1$ ,  $R_2$  and  $R_3$  are also connected, as shown, to the reference voltage  $V_r$ .

The operation of the D/A converter 40 will now be described with reference to Fig. 4 and the table

in Fig. 5, which illustrates the values of the outputs  ${\rm BC}_1$  and  ${\rm BC}_2$  of counter 38 and the output  ${\rm V}_{\rm D/A}$  of  ${\rm D/A}$ converter 40 at times  $t_1$ ,  $t_2$ ,  $t_3$ ,  $t_4$  and  $t_5$ . The decoder 42 enables one of its outputs, and thus one of the FET's 44, 45, 46 and 47, in response to each of the four possible combinations of the signals at the outputs  $BC_1$  and  $BC_2$  of counter 38. The resistors  $R_0$ ,  $R_1$ ,  $R_2$  and  $R_3$  each form a voltage divider with the resistor  $R_{\mathrm{D/A}}$ , and have values chosen to provide each of the four data levels (plus the adjustment voltage  $V_a$ ) across the resistor  $R_{D/A}$ . Thus, at times  $t_1$  and  $t_2$ , when BC<sub>1</sub> and BC<sub>2</sub> are both at "0" and FET 44 is conductive, the voltage  ${\rm V}_{\rm D/A}$  across resistor  ${\rm R}_{\rm D/A}$  is at  $v_a$ . At time  $t_3$ , FET 45 is conductive and  $v_{D/A}$  is at the data level "1" plus Va; at time t4, FET 46 is con-15 ductive and  $V_{D/A}$  is at the data level "2" plus  $V_a$ ; and at time  $t_3$ , FET 47 is conductive and  $V_{D/A}$  is at the data level "3" plus  $V_a$ . It can be seen from Figs. 4 and 5 and the timing diagram of Fig. 6, that the CLOCK E signal includes a clock pulse at times  $t_3$ ,  $t_4$ 20 and  $t_5$  to advance the counter 38 and D/A converter 40, and at time t<sub>1</sub> to return the counter 38 to zero and the output of the D/A converter 40 to  $V_a$ .

Referring again to Fig. 3, the summing nodes 34 and 36 are connected to the output  $V_{\mathrm{D/A}}$  of the D/A 25 converter by field effect transistors (FET's) 50 and 52, respectively. The gate of the FET 50 is connected to the output Q of the flip-flop 32 and the gate of the FET 52 is connected to the inverted output  $\overline{\mathbb{Q}}$  of the flip-flop 32. The reason for the connection of 30 the FET's 50 and 52 to the flip-flop 32 and the reason for the adjustment voltage  $\mathbf{V}_{\mathbf{a}}$  will become apparent later when the operation of the detection circuit 20 is described. Briefly, however, the flip-flop 32 causes the incrementing output  $V_{\mathrm{D/A}}$  of the D/A converter 40 to be summed to the signal from the cell  $\mathbf{b}_0$ or  $b_1$  which is at the lower data level. The adjustment

10

15

20

25

30

voltage  $V_a$  compensates for any cell-to-cell losses between  $b_0$  and  $b_1$ . If  $b_0$  and  $b_1$  are at the same data level, or if  $S_0$  and  $S_1$  are at the same data level after the summing of  $V_{D/A}$  to one of the cells  $b_0$  and  $b_1$ , the adjustment voltage  $V_a$  causes the signal to which it is summed to be the larger of the signals sensed by amplifier 30.

Although the signal losses experienced by the signals in two adjacent cells are nearly identical, there will normally be a very small loss from cell-to-cell and V must have a value at least slightly greater than the worst case cell-to-cell loss that could be present between b and b. For a typical CCD, assuming the difference in voltage or signal value between each of the four data levels is the same, a satisfactory value for V would be one-half the difference between each of the full voltage values. It should be noted, however, that V should not exceed the difference between each of the full voltage values of the four data levels. Otherwise, an erroneous comparison could be made by amplifier 30.

The flip-flop 32 receives the CLOCK B signal at its reset input, which resets the flip-flop to a "0" when the reading of the cell b<sub>1</sub> is initiated. The flip-flop 32 also receives the CLOCK C signal at its clock (CLK) input which clocks into the flip-flop the data level (either a "0" or a "1") from the output SA of amplifier 30.

The output SA of the amplifier 30 and the output Q of the flip-flop 32 are connected to the inputs of an EXCLUSIVE NOR control gate 54. The output of gate 54 provides an enable control signal and is connected to the clock enable (CLK EN) input of an up/down counter 56. The counter 56 receives the CLOCK D signal at its clock (CLK) input, a reset signal at its reset input, and the signal from the output Q of flip-flop 32 at its up/down (U/D) input. The up/down count-

15

20

ter 56 will count, in response to the clock pulses of CLOCK D, through the four data levels "0", "1", "2" and "3", which will appear at its output  $Q_{\rm U/D}$  at their full signal or voltage values. The signal at  $Q_{\rm U/D}$  at the end of each read cycle will be the data level of the signal in the b<sub>1</sub> cell. The clock enable input enables the counter when it receives a "1" from the output of gate 54. When a "0" is received from output of gate 54, the counter 56 is disabled and does not count in response to the clock pulses of CLOCK D.

The reset input of counter 56 is used to reset the counter to the same data level as the marker signal or digit when the marker digit reaches the cell The reset signal can be generated by a source external to the detection circuit 20, such as a memory controller, or the detection circuit can include an additional counter circuit (not shown) responsive to each cell-to-cell shift within the shift register 12 so that each time the marker digit reaches  $b_0$  the additional counter circuit generates a signal to reset the counter 56. While the shift register 12 is mentioned as only having one marker digit, it should be appreciated that more than one marker digit could be located at spaced apart cells along the shift register, and that the up/down counter 56 could be reset each time one of the marker digits reaches the  $\mathbf{b}_0$  cell.

The operation of detection circuit 20 will now be described with reference to Figs. 3 and 6. The detection circuit is initialized when the marker digit is in the  $b_0$  cell. If the marker digit has been given, for example, a data level of "0", the up/down counter 56 is reset so that a "0" data level signal appears at the output  $Q_{\mathrm{U/D}}$  of counter 56.

In Fig. 6 there is illustrated the signals CLOCK A, B, C, D and E and their occurrence during a first read cycle  $T_a$  and a portion of a second read cycle  $T_b$ . Each read cycle is marked at five moments,

20

designated times  $t_1$  through  $t_5$ . At time  $t_1$ , the clock pulse in the CLOCK A signal shifts the data in the shift register so that the signal formerly in the  $b_1$  cell is now in the  $b_0$  cell. The data level of the signal in  $b_0$  is now known, either because it is a marker digit or because its level was previously determined when it was in  $b_1$ . Also at time  $t_1$ , the clock pulse in the CLOCK B signal resets flip-flop 32 (Fig. 3) so that a "0" and "1" appear at its outputs Q and  $\overline{Q}$ , respectively, and the clock pulse in the CLOCK E signal returns binary counter 38 to zero.

During the interval between times  $t_1$  and  $t_2$  the amplifier 30 compares the signals  $s_0$  and  $s_1$ . Since Q is at "0" and FET 50 is not conductive,  $s_0$  will have the same value as  $b_0$ . On the other hand,  $\overline{Q}$  is at "1" and FET 52 is conductive and causes the voltage  $V_{D/A}$ , then at its initial value of  $V_a$ , to be added to the value of  $b_1$  at summing node 36. The output SA of amplifier 30 will be either a "0" or "1", depending upon whether  $s_0$  or  $s_1$  is larger. At time  $t_2$  the output SA of amplifier 30 is clocked into the flip-flop by the clock pulse in the CLOCK C signal.

In the interval between times  $t_2$  and  $t_3$  the amplifier 30 again compares  $s_0$  and  $s_1$ , with the output  $V_{D/A}$  (still having a value of  $V_A$ ) being added to either  $b_0$  or  $b_1$ , depending on the signals at the outputs Q and  $\overline{Q}$  of flip-flop 32. Still in the same interval, the output SA of amplifier 30 and the output Q of flip-flop 32 are received by the EXCLUSIVE NOR gate 54. If  $b_0$  and  $b_1$  are at the same data level, then output SA will be at a "0" and output Q will be at a "1" and the output of gate 54 goes to a "0". The "0" at the output of gate 54 is applied to the CLK EN input to disable the up/down counter 56. On the other hand, if  $b_0$  is greater than  $b_1$ , outputs SA and Q will both be at "0", and if  $b_0$  is less than  $b_1$ , outputs SA and Q will both be at "1", with either condition causing the output of

10

15

20

25

30

35

gate 54 to go to a "l". The "l" at the output of gate 54 is applied to the CLK EN input to enable the up/down counter 56.

Still in the same interval between  $t_2$  and  $t_3$ , the output Q of flip-flop 32 is also applied to the U/D input of counter 56 and determines whether counter 56 will count up or count down from the data level then present at its output  $Q_{\rm U/D}$ . The data level at its output will be the same as the data level in the cell  $b_0$ . If Q is at a "1", the counter 56 will count up; and if Q is at a "0", the counter 56 will count down.

At times  $t_3$ ,  $t_4$  and  $t_5$ , clock pulses in the CLOCK D signal are applied to the CLK input of counter 56, and clock pulses in the CLOCK E signal are applied to the binary counter 38 to advance the D/A converter. 40. The output  $V_{\rm D/A}$  of the D/A converter 40 is applied during each of these times to the same one of either summing node 34 or summing node 36, depending on the signals at outputs Q and  $\overline{\rm Q}$  of flip-flop 32. The outputs Q and  $\overline{\rm Q}$  control FET's 50 and 52 so that FET 50 is conductive at times  $t_3$ ,  $t_4$  and  $t_5$  if the data level in  $b_1$  is greater than the data level in  $b_0$ , and FET 52 is conductive if the data level in  $b_0$  is greater than the data level in  $b_0$  is greater than the data level in  $b_0$  is greater than the

The output  $Q_{\rm U/D}$  of up/down counter 56 can either increment or decrement upon each of the clock pulses in the CLOCK D signal. However, when the output  $V_{\rm D/A}$  of the D/A converter increments to such a value that, when added to the smaller of  $b_0$  and  $b_1$ , the resulting signal exceeds the larger of  $b_0$  and  $b_1$ , the output SA of amplifier 30 changes, and the output of gate 54 goes to a "0". Up/down counter 56 is then disabled by the "0" at its CLK EN input before the next clock pulse in the CLOCK D signal is applied, and the output  $Q_{\rm U/D}$  is then at the same data level as the signal in  $b_1$  and remains at that data level until the next read cycle,  $T_{\rm b}$  (Fig. 6).

10

15

20

- 25

30

At the first time  $t_1$  of the next read cycle  $T_b$ , data is shifted in the shift register 12 by the CLOCK A signal and the flip-flop 32 is again reset by the CLOCK B signal. At the same time, the binary counter 38 receives a clock pulse in the CLOCK E signal so that its outputs  $BC_1$  and  $BC_2$  return to a binary zero.

The remainder of the operation of the detection circuit 20 in the read cycle  $\mathbf{T}_{b}$  proceeds in the same fashion as the operation in the first read cycle  $\mathbf{T}_{a}$ .

To illustrate the operation of the detection circuit 20 by way of example, the table of Fig. 7 shows, for three different cases, the values of  $b_0$ ,  $b_1$ , Q,  $\overline{Q}$ ,  $S_0$ ,  $S_1$ , SA, the output of gate 54, and the Data Output of the detection circuit.

Referring now to Fig. 7, in connection with the circuit of Fig. 3 and the timing diagram of Fig. 6, in Case No. 1 the signals in both bo and b, are at a "0". At time  $t_1$ , Q is reset to a "0" by the CLOCK B signal and the output  $V_{\rm D/A}$  of the D/A converter 40 (then at a value of  $V_a$ ) is added to  $b_1$  at summing node The output SA of amplifier 30 goes to a "1" since  $S_1$  is greater than  $S_0$ . At time  $t_2$ , the "1" from SA is clocked into flip-flop 32, and thus Q is at a "1". Va is then added to  $\mathbf{b}_0$  at summing node 34 and the output SA goes to a "0", since  $S_0$  is now greater than  $S_1$ . The output of gate 54 goes to a "0" and disables the up/ down counter 56. Thus, while the D/A converter 40 increments, increasing the value of  $S_0$ , the output  $Q_{U/D}$ of up/down counter 56 (also the Data Output) remains at its original  $b_0$  data level of "0", indicating that b<sub>1</sub> is also at a "0":

In Case No. 2 of Fig. 7,  $b_0$  is at a "0" and  $b_1$  is at a "2". At time  $t_1$ , Q is reset to "0",  $s_0$  is thus at a "0", and the output  $v_{D/A}$  of the D/A converter 40 (then at a value of  $v_a$ ) is summed with  $b_1$  to give

15

20

25

30

35

$s_1$  a value of 2 +  $v_a$ . Since  $s_1$  is greater than  $s_0$ , the output SA of amplifier 30 goes to a "1", which is clocked into flip-flop 32 and appears at Q at time  $t_2$ . The  $V_a$  at the output of the D/A converter 40 is then added to  $b_0$ , so that  $S_0$  is at  $V_a$  and  $S_1$  is at "2". The output SA goes to a "1" and in turn the output of gate 54 goes to a "1" which enables the up/down counter 56. With Q at a "1", the counter 56 will increment. The D/A converter increments at time  $t_3$  to "1 +  $V_a$ " and then at time  $t_4$  to "2 +  $V_a$ ", which causes the value of  $s_0$  to finally exceed the value of  $s_1$ . SA will then go to "0", and the output of gate 54 goes to a "0", disabling the counter 56 so that the final value of the Data Output is "2". The one further increment of the D/A converter at time  $t_5$  causing  $s_0$  to go to 3 +  $V_a$ has no effect on the up/down counter 56.

In Case No. 3,  $b_0$  is at a "3" and  $b_1$  is at a "0". Since  $S_1$  is less than  $S_0$  at time  $t_1$ , Q will remain at "0" at time  $t_2$  and thereafter, causing the counter 56 to count down. The output of gate 54 is at a "1" at times  $t_2$ ,  $t_3$  and  $t_4$ , enabling the counter 56 to decrement until after the Data Output goes to "0" at time  $t_5$ .

It can thus be seen that the value of the signal in the  $b_1$  cell is determined by comparing the signals from the  $b_0$  and  $b_1$  cells, with the value of  $b_0$  being known, either because it has the value of a marker digit and the up/down counter 56 has been reset to such value, or it has the value of the signal just shifted from the  $b_1$  cell, and the value of such signal is at the Data Output of the counter 56 from the previous read cycle. In either case, the determination of what data level is represented by the signal from the  $b_1$  cell is made by comparison with the known signal from the  $b_0$  cell, rather than with an external reference voltage, as is commonly done in the prior art. A reliable determination is made even if large or unknown

signal losses are experienced during shifting, as long as the signals representing the four data levels are not completely dissipated before they reach the  $\mathbf{b}_1$  cell.

#### WHAT IS CLAIMED IS:

- A data storage system including a charge transfer device shift register (12) having a plurality of storage cells each adapted to store multilevel data in the form of a charge having one of at least three data levels, and a detection circuit (20) adapted to detect the data stored in a first one of said storage cells (b<sub>1</sub>), characterized by means adapted to provide signals respectively representing the data stored in said first storage cell (b<sub>1</sub>) and known data stored in a second one of said storage cells  $(b_0)$ , which is ad-10 jacent to said first storage cell  $(b_1)$ , said detection circuit (20) including: summing means (34, 36, 40, 50, 52) adapted to add an adjustment signal including an incrementally changing component to one of the datarepresenting signals thereby providing first and 15 second signals ( $S_1$ ,  $S_0$ ); comparison means (30) adapted to compare said first and second signals  $(S_1, S_0)$  thereby providing a comparison signal (SA); and incrementable means (56) adapted to initially provide an output signal having a value representing said known data and 20 capable of changing said output signal incrementally in correspondence with changes in said adjustment signal and in dependence on said comparison signal (SA) until said output signal has a value representing the data stored in said first storage cell (b<sub>1</sub>). 25

- 2. A data storage system according to claim 1, characterized in that said adjustment signal further includes a constant component ( $V_a$ ).

- 3. A data storage system according to claim 2, characterized in that said constant component ( $V_a$ ) has a value greater than the worst case cell-to-cell signal loss between said first and second storage cells ( $b_1$ ,  $b_0$ ) and less than the difference between each of

data.

5

5

5

3. (concluded) the full values of the data levels in said multilevel

- 4. A data storage system according to claim 3, characterized in that said comparison means includes a differential amplifier (30), said comparison signal (SA) having a first or second comparison value dependent on the relative value of said first and second signals  $(S_1, S_0)$ , said comparison signal (SA) being applied in operation to control means (54) adapted to provide an enabling control signal to said incrementable means (56).

- 5. A data storage system according to claim 4, characterized in that one of said storage cells is arranged to store reference data, said incrementable means (56) being arranged to be reset such that said output signal corresponds to said reference data when said reference data is stored in said control cell  $(b_0)$ .

- 5. A data storage system according to claim 5, characterized in that said detection circuit (20) includes flip-flop means (32) arranged to store the initial output of said comparison means (30), said summing means (34, 36, 50, 52) including: a digital-to-analog converter (40) adapted to provide said adjustment signal; first and second summing node means (36, 34) arranged to receive the data-representing signals from said first and second storage cells (b<sub>1</sub>, b<sub>0</sub>) respectively, and being coupled to switching means (50, 52) arranged to selectively provide said adjustment signal to said first and second summing node means (36, 34) under the control of said flip-flop means (32).

- 7. A data storage system according to claim 6, characterized in that said comparison means includes

5

### 7. (concluded)

a differential amplifier (30) having first and second inputs arranged to receive outputs of said first and second summing node means (36, 34) respectively and arranged to provide said comparison signal (SA) in the form of a logic "1" or a logic "0" level output signal according to whether the signal at said first or second input is the greater.

- 8. A data storage system according to claim 7, characterized in that said incrementable means includes an up/down counter (56) adapted to be enabled for counting in accordance with said control signal, the direction of counting being controlled by an output of said flip-flop means (32).

- 9. A data storage system according to any one of the preceding claims characterized in that said charge transfer device shift register is a charge coupled device (CCD) shift register (12).

FIG. 2

| 7                                                       |                                                        |

|---------------------------------------------------------|--------------------------------------------------------|

| FOUR DATA LEVELS<br>IN ONE CELL OF<br>SHIFT REGISTER 12 | SAME DATA REQUIRING TWO CELLS OF BINARY SHIFT REGISTER |

| 0.                                                      | 00                                                     |

|                                                         | 01                                                     |

| 2                                                       | 10                                                     |

| 3.                                                      | 11                                                     |

| TIME           | BC <sub>1</sub> | BC <sub>2</sub> | V <sub>D/A</sub> |  |  |

|----------------|-----------------|-----------------|------------------|--|--|

| t <sub>1</sub> | 0               | 0.              | Уa               |  |  |

| t <sub>2</sub> | ·. 0            | 0               | Vα               |  |  |

| t <sub>3</sub> | 0               | 1               | I + Va           |  |  |

| t <sub>4</sub> | ı               | 0               | 2 + Va           |  |  |

| t 5            | 1               | ı               | 3+√a             |  |  |

| FIG. | 7    |                |   |                |         |          |                    |                  |    |       | 17 PUT      |   |

|------|------|----------------|---|----------------|---------|----------|--------------------|------------------|----|-------|-------------|---|

|      |      | 7/1/7          |   | 0/4            |         | ,/10     | So                 | Sr               | /5 | UTPUT | DATA OUTPUT |   |

|      |      |                |   |                |         |          |                    |                  |    | 00    |             |   |

| CASE | NO.1 | tı             | 0 | 0              | 0       | 1        | 0                  | Vα               | 1  |       |             |   |

|      |      | t <sub>2</sub> |   |                | ı       | 0        | ٧α                 | 0                | 0  | 0     | 0           |   |

|      |      | t <sub>3</sub> |   |                | 1       | 0        | 1 + V <sub>a</sub> | 0                | 0  | 0     | 0           |   |

|      |      | t <sub>4</sub> | - |                | 1       | 0        | 2 + Va             | 0                | 0  | 0     | 0           |   |

|      |      | t <sub>5</sub> |   |                | 1       | 0        | 3+ Va              | 0                | 0  | 0     | Ò           | · |

|      |      |                |   |                |         |          |                    |                  |    |       | •           |   |

| CASE | NO.2 | tı             | 0 | 2              | 0       | 1        | 0                  | 2+V <sub>a</sub> | I  |       |             |   |

|      |      | t <sub>2</sub> |   |                | I       | 0        | Vα                 | 2                |    | 1     |             |   |

|      |      | tз             |   |                | 1       | 0        | I + Vα             | 2                | I  | ı     | l           |   |

|      |      | t4             |   |                | l       | 0        | $2 + V_{\alpha}$   | - 2              | 0  | 0     | 2           |   |

|      |      | t <sub>5</sub> |   |                | 1       | 0        | 3 + Vq             | 2                | 0  | 0     | 2           |   |

|      |      |                | · | . <del> </del> | <b></b> | <u> </u> |                    |                  |    |       |             |   |

| CASE | NO.3 | tı             | 3 | 0              | 0       | 1        | 3                  | να               | 0  |       |             |   |

|      |      | t <sub>2</sub> |   |                | 0       | 1        | 3                  | να               | 0  | 1     | 3           |   |

|      |      | t <sub>3</sub> |   |                | 0       | 1        | 3                  | 1 + Va           | 0  | I     | 2           |   |

|      |      | t <sub>4</sub> |   | :              | 0       | 1.       | 3                  | 2+Va             | 0  | I     | 1           |   |

|      |      | t <sub>5</sub> |   | · •            | 0       | 1        | 3                  | $3 + V_{\alpha}$ | 1  | 0     | 0           |   |

# INTERNATIONAL SEARCH REPORT

International Application No

PCT/US79/00660

| I. CLASSIFICATION OF SUBJECT MATTER (if several classification symbols apply, indicate all) 3                                                                                            |                  |         |                                                                           |                              |                |                               |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|---------------------------------------------------------------------------|------------------------------|----------------|-------------------------------|--|--|--|--|

| According to International Patent Classification (IPC) or to both National Classification and IPC Int. C1. G11C 19/28; G11C 7/06;                                                        |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| Tht. C1. G11C 19/28; G11C 7/06;<br>U.S. C1. 365/222,75,183; 307/221C                                                                                                                     |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| II. FIELDS SEARCHED                                                                                                                                                                      |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| Minimum Documentation Searched 4                                                                                                                                                         |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| Classification System Classification Symbols                                                                                                                                             |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| U.S. 365/73,75,183,222; 307/221C, 221D                                                                                                                                                   |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| Documentation Searched other than Minimum Documentation<br>to the Extent that such Documents are Included in the Fields Searched <sup>5</sup>                                            |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| III. DOCUMENTS CONSIDERED TO BE RELEVANT 14                                                                                                                                              |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| Category *                                                                                                                                                                               |                  |         | f Document, 16 with indication, where appro                               | priate, of the relevant pass | ages 17        | Relevant to Claim No. 18      |  |  |  |  |

| Х                                                                                                                                                                                        | US,              | Α,      | 3,999,171, Published Robert Parsons.                                      | l 21 December                | 1976           | 1-9                           |  |  |  |  |

| X                                                                                                                                                                                        | υs,              | Α,      | 3,946,368, Published Sunlin Chou.                                         | l 23 March 19                | 76,            | 1-9                           |  |  |  |  |

| X,P                                                                                                                                                                                      | υs,              | Α,      | 4,156,152, Published Walter J. Butler et                                  |                              | ,              | 1-9 -                         |  |  |  |  |

| A                                                                                                                                                                                        | us,              | Α,      | 4,072,939, Published 07 February 1978,<br>Lawrence Griffith Heller et al. |                              |                |                               |  |  |  |  |

| x                                                                                                                                                                                        | US,              | Α,      | 4,085,459, Published 18 April 1978, Kanji Hirabayashì.                    |                              |                |                               |  |  |  |  |

| х                                                                                                                                                                                        | DE,              | Α,      | 2,509,567, Published Siemens.                                             | 1 09 Septembe                | er 197         | 6, 6                          |  |  |  |  |

|                                                                                                                                                                                          |                  |         | _                                                                         |                              |                |                               |  |  |  |  |

|                                                                                                                                                                                          |                  |         |                                                                           |                              |                |                               |  |  |  |  |

|                                                                                                                                                                                          |                  |         |                                                                           |                              | ·              | •                             |  |  |  |  |

| • Snaain                                                                                                                                                                                 | l categori       | as of a | ited documents:15                                                         |                              |                |                               |  |  |  |  |

| 1                                                                                                                                                                                        |                  |         | he general state of the art                                               | "P" document published       | I prior to the | International filing date but |  |  |  |  |

| "E" earlier document but published on or after the international on or after the priority date claimed                                                                                   |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| "L" document cited for special reason other than those referred date or priority date and not in conflict with the application,                                                          |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| to in the other categories but cited to understand the principle of theory underlying the invention                                                                                      |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| other means "X" document of particular relevance                                                                                                                                         |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| IV. CERTIFICATION  Date of the Actual Completion of the International Search  Date of Mailing of this International Search Report  Date of Mailing of this International Search Report 2 |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| 13 December 1979 21 DEC 1979                                                                                                                                                             |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| International Searching Authority 1  Signature of Authorized Officer 30  Stuart h. Hecker                                                                                                |                  |         |                                                                           |                              |                |                               |  |  |  |  |

| ISA/                                                                                                                                                                                     | ISA/US Swan 7. 7 |         |                                                                           |                              |                |                               |  |  |  |  |