(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6057568号

(P6057568)

(45) 発行日 平成29年1月11日(2017.1.11)

(24) 登録日 平成28年12月16日(2016.12.16)

(51) Int.Cl.

F 1

H04N 5/365 (2011.01)

H04N 5/335 650

H04N 5/369 (2011.01)

H04N 5/335 690

H04N 5/3745 (2011.01)

H04N 5/335 745

請求項の数 11 (全 20 頁)

(21) 出願番号

特願2012-150839 (P2012-150839)

(22) 出願日

平成24年7月4日(2012.7.4)

(65) 公開番号

特開2014-14021 (P2014-14021A)

(43) 公開日

平成26年1月23日(2014.1.23)

審査請求日

平成27年4月22日(2015.4.22)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 衣笠 友壽

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 鈴木 肇

最終頁に続く

(54) 【発明の名称】光電変換装置

(57) 【特許請求の範囲】

## 【請求項 1】

光電変換部と前記光電変換部に接続されるセンサセル部書き込みスイッチとを含むセンサセル部と、

メモリ容量と前記メモリ容量に接続されるメモリセル部書き込みスイッチとを含むメモリセル部と、

前記センサセル部及び前記メモリセル部に接続される共通信号線とを有し、

前記メモリセル部は、前記光電変換部の信号を前記メモリ容量に保持する前に、前記センサセル部書き込みスイッチのオフ動作に伴う前記光電変換部の電位変動と、前記センサセル部の固定パターンノイズと、前記メモリセル部の固定パターンノイズとを含む信号を前記メモリ容量に保持することを特徴とする光電変換装置。

10

## 【請求項 2】

前記センサセル部は、前記光電変換部の光電変換信号と、前記センサセル部書き込みスイッチのオフ動作に伴う前記光電変換部の電位変動とを含む信号を前記共通信号線に出力し、

前記メモリセル部は、前記メモリ容量に保持されている信号を前記共通信号線に出力し、

さらに、前記センサセル部の出力信号と、前記メモリセル部の出力信号との差分信号を生成する転送部を有することを特徴とする請求項1記載の光電変換装置。

## 【請求項 3】

20

さらに、前記転送部により生成される差分信号を基にオートゲインコントロールを行うゲイン可変増幅部を有することを特徴とする請求項2記載の光電変換装置。

【請求項4】

前記メモリセル部は、前記差分信号を前記メモリ容量に保持することを特徴とする請求項2又は3記載の光電変換装置。

【請求項5】

前記転送部は、前記メモリ容量に保持されている前記差分信号と、前記転送部の固定パターンノイズとの差分信号を生成する請求項4記載の光電変換装置。

【請求項6】

前記メモリセル部は、

メモリセル部アンプと、

前記メモリセル部アンプの出力信号を前記共通信号線に出力するためのメモリセル部選択スイッチとを有し、

前記メモリセル部選択スイッチをオンすることにより、前記メモリ容量に記憶されている前記センサセル部書き込みスイッチのオフ動作に伴う前記光電変換部の電位変動と、前記センサセル部の固定パターンノイズと、前記メモリセル部の固定パターンノイズとを含む信号を前記共通信号線に出力し、

前記メモリセル部書き込みスイッチをオンすることにより、前記メモリ容量に保持されている前記差分信号を前記共通信号線に出力することを特徴とする請求項4又は5記載の光電変換装置。

10

20

【請求項7】

さらに、読み出し線を有し、

前記メモリセル部は、

メモリセル部アンプと、

前記メモリセル部アンプの出力信号を前記共通信号線に出力するためのメモリセル部選択スイッチと、

前記メモリ容量と前記読み出し線との間に設けられる読み出しスイッチとを有し、

前記メモリセル部選択スイッチをオンすることにより、前記メモリ容量に記憶されている前記センサセル部書き込みスイッチのオフ動作に伴う前記光電変換部の電位変動と、前記センサセル部の固定パターンノイズと、前記メモリセル部の固定パターンノイズとを含む信号を前記共通信号線に出力し、

前記読み出しスイッチをオンすることにより、前記メモリ容量に保持されている前記差分信号を前記読み出し線に出力することを特徴とする請求項4又は5記載の光電変換装置。

30

【請求項8】

前記センサセル部は、前記光電変換部の信号に基づく信号を出力するセンサセル部反転アンプを有し、

前記メモリセル部は、前記メモリ容量に保持されている信号に基づく信号を出力するメモリセル部反転アンプを有することを特徴とする請求項1～5のいずれか1項に記載の光電変換装置。

40

【請求項9】

前記センサセル部は、前記光電変換部の信号に基づく信号を出力するセンサセル部正転アンプを有し、

前記メモリセル部は、前記メモリ容量に保持されている信号に基づく信号を出力するメモリセル部正転アンプを有することを特徴とする請求項1～5のいずれか1項に記載の光電変換装置。

【請求項10】

請求項1～9のいずれか1項に記載の光電変換装置を有する焦点検出装置。

【請求項11】

請求項10記載の焦点検出装置と、

50

撮像装置と、

光学像を結像するレンズと

を有することを特徴とする撮像システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光電変換装置、焦点検出装置及び撮像システムに関する。

【背景技術】

【0002】

撮像システムにおいては、焦点を検出するAF(Auto Focusing)センサを備えることが一般的である。近年のAFセンサは測距点数の多点化のみならず焦点検出の高精度化が求められている。測距点数を増やす手段として、測距点を構成するリニアセンサを複数本並列に配置して列方向に共通配線で接続するエリアタイプが採用されている。エリアタイプAFの回路構成として、特許文献1には、センサセル部から出力された信号をメモリセル部に転送する転送系を備えた固体撮像装置が記載されている。センサ信号のSN比を上げてAFの測距精度を高めるために、特許文献1では、センサセル部及びメモリセル部に信号の反転出力機能を持たせてセンサセル部とメモリセル部自身の固定パターンノイズを除去している。

【0003】

また、AFセンサは、広いダイナミックレンジを実現するために、蓄積信号の最大値と最小値を検出して蓄積信号の振幅値を適切に制御する動作(AGC:Auto Gain Control)を行うことが知られている。蓄積制御の精度はAF精度に関係するので、AGCに用いる蓄積信号もセンサの固定パターンノイズを除去することにより、AFの精度を高めることができる。特許文献1では、センサセル部と転送部の固定パターンノイズをセンサセル部に保持することで、蓄積信号から固定パターンノイズを除去している。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平9-200614号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1のようにセンサセル部に固定パターンノイズを保持すると、光電荷の検出容量を小さくしたときに不具合が生じるおそれがある。なぜなら、特許文献1におけるセンサセル部のスイッチ手段が新たなノイズ発生要因になるからである。スイッチ手段がMOSトランジスタで構成される場合、スイッチオフ時にゲート電位の変動がMOSトランジスタのソース、ドレインに伝搬する(クロックフィールドスルーリー)。また、スイッチオン時にゲート下に保持されたキャリアが、スイッチオフ時にソース又はドレインに移動する(チャージインジェクション)。これらのスイッチオフ時のソース、ドレインの電位変動量は、スイッチオフ直前のソース、ドレインの電位に依存する。すなわち、特許文献1のように、固定パターンノイズをスイッチ手段を介してセンサセル部のフォトダイオードに保持する場合、固体パターンノイズに相当するばらつきが画素間のソース、ドレイン電位に現れる。すると、前述したスイッチオフ時に生じる電位変動量も画素間で異なるため、フォトダイオードに保持される固定パターンノイズは本来除去すべき固定パターンノイズと異なる。その結果、AGC時に蓄積信号から固定パターンノイズを十分に除去できないのでAGC精度及びAF精度が低下する。

【0006】

近年、撮像素子の高感度化に伴いAFセンサも高感度化が求められている。センサの高感度化には検出容量を小さくすることであるが、上記した理由から、検出容量を小さくするとスイッチオフ時の電位変動が大きくなり、AGC精度が低下するという問題が生じて

10

20

30

40

50

いる。

【0007】

本発明の目的は、固定パターンノイズを除去することができる光電変換装置、焦点検出装置及び撮像システムを提供することである。

【課題を解決するための手段】

【0008】

光電変換装置は、光電変換部と前記光電変換部に接続されるセンサセル部書き込みスイッチとを含むセンサセル部と、メモリ容量と前記メモリ容量に接続されるメモリセル部書き込みスイッチとを含むメモリセル部と、前記センサセル部及び前記メモリセル部に接続される共通信号線とを有し、前記メモリセル部は、前記光電変換部の信号を前記メモリ容量に保持する前に、前記センサセル部書き込みスイッチのオフ動作に伴う前記光電変換部の電位変動と、前記センサセル部の固定パターンノイズと、前記メモリセル部の固定パターンノイズとを含む信号を前記メモリ容量に保持することを特徴とする。

10

【発明の効果】

【0009】

本発明によれば、固定パターンノイズを除去することができる。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態に係る光電変換装置の構成例を示す図である。

20

【図2】第1の実施形態に係るラインセンサ部のブロック図である。

【図3】第1の実施形態に係る光電変換装置の回路図である。

【図4】第2の実施形態に係る光電変換装置の回路図である。

【図5】第4の実施形態に係る光電変換装置の回路図である。

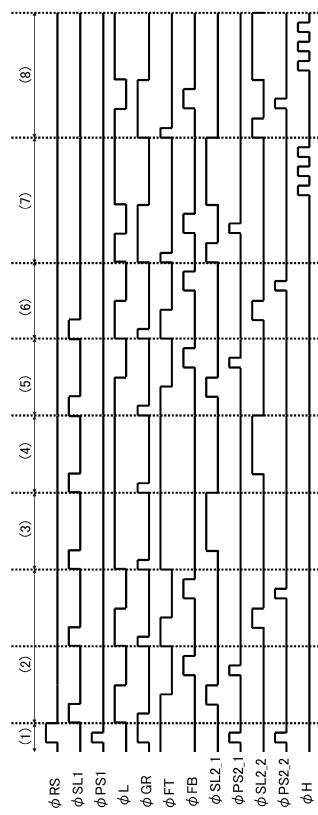

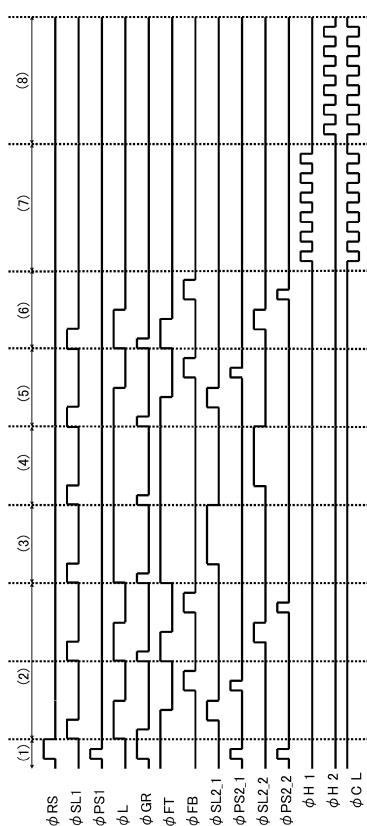

【図6】第1の実施形態に係るタイミング図である。

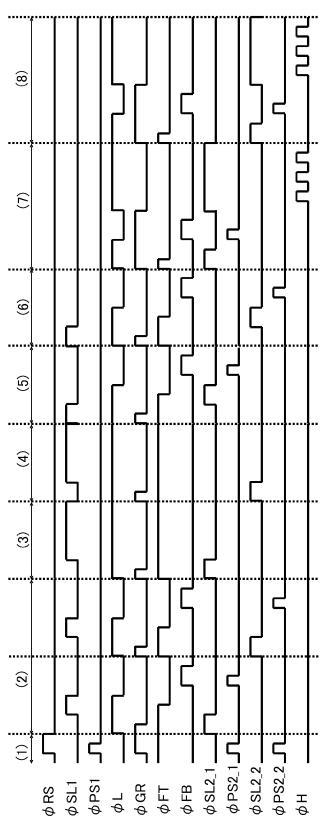

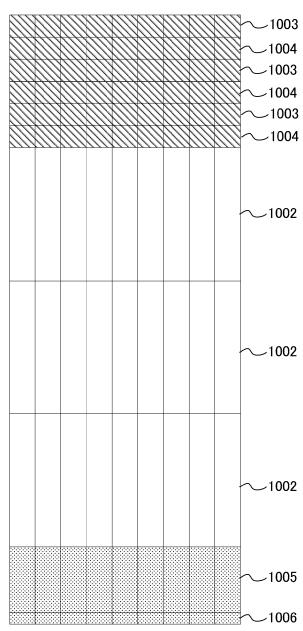

【図7】第2の実施形態に係るタイミング図である。

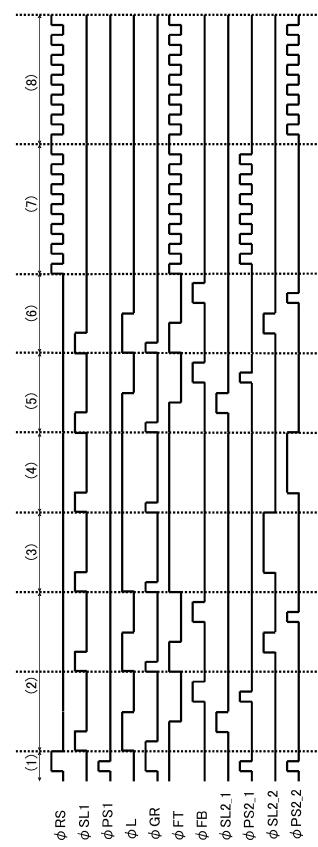

【図8】第3の実施形態に係るタイミング図である。

【図9】第4の実施形態に係るタイミング図である。

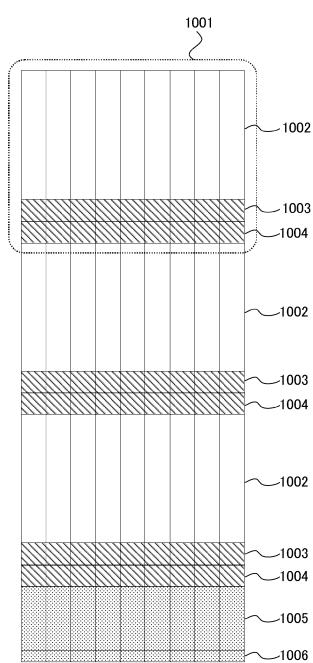

【図10】第1の実施形態に係る第1のレイアウト図である。

【図11】第1の実施形態に係る第2のレイアウト図である。

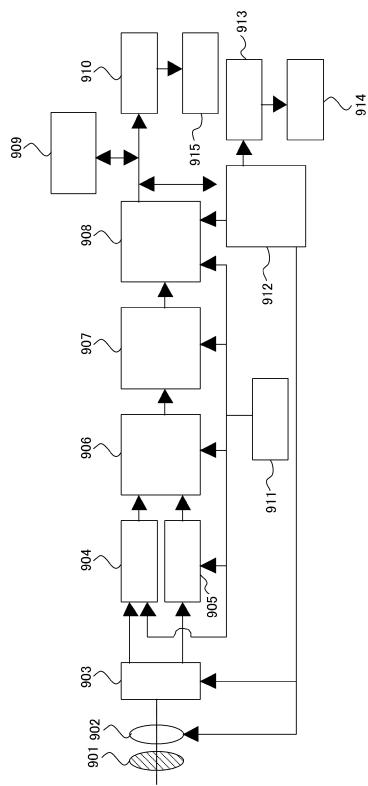

【図12】第5の実施形態に係るAFセンサのブロック図である。

30

【図13】第6の実施形態に係る撮像システムの構成例図である。

【発明を実施するための形態】

【0011】

(第1の実施形態)

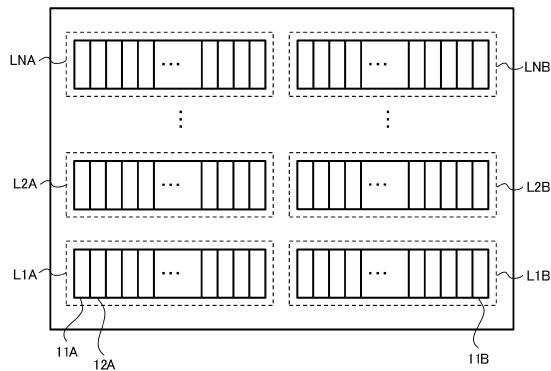

図1は、本発明の第1の実施形態に係る位相差焦点検出(Auto Focusing; AF)用の光電変換装置における撮像面を模式的に示した図である。撮像面には、対となるラインセンサ部L1AとL1B、L2AとL2B、・・・、LN<sub>A</sub>とLN<sub>B</sub>が存在する。一対のラインセンサ部は、撮像面のある領域における被写体のデフォーカス量を測定するために用いられ、このラインセンサ部の対を複数配列することで測距点を複数設け、AFの精度を向上させることができる。ラインセンサ部L1A～LN<sub>A</sub>、L1B～LN<sub>B</sub>の画素開口部の配置間隔を狭めて、二次元アレイ状に配置した構成をエリアタイプAFセンサと呼んでいる。各ラインセンサ部L1A～LN<sub>A</sub>は、複数の単位画素11A、12A、・・・を有し、各ラインセンサ部L1B～LN<sub>B</sub>も、複数の単位画素11B、・・・を有する。

40

【0012】

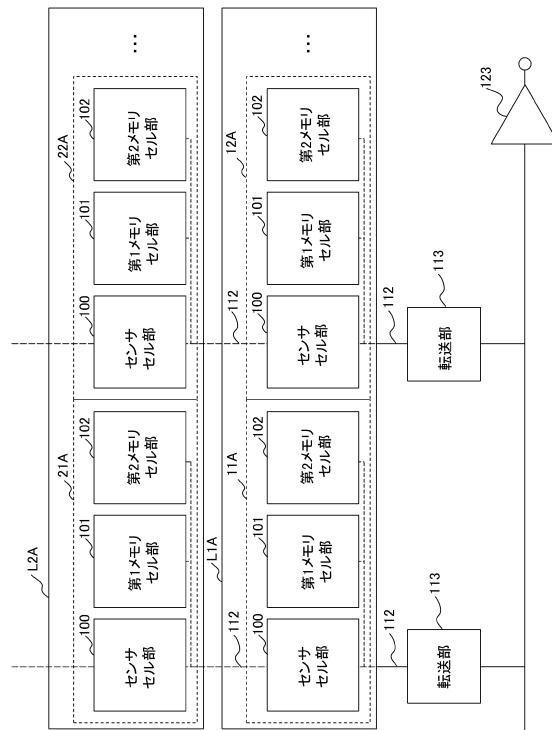

図2は、ラインセンサ部L1A及びL2Aをより詳細に示したブロック図である。ラインセンサ部L1Aは、単位画素11A、12A、・・・を有する。ラインセンサ部L2Aは、単位画素21A、22A、・・・を有する。各単位画素11A、12A、21A、22Aは、センサセル部100、第1メモリ部101、及び第2メモリ部102を有し、共通信号線112に接続されている。また、異なるラインセンサ部L1A及びL2Aの同様

50

の位置に存在する単位画素（例えば画素 11A、21A、・・・）は、共通信号線 112 を介して、共通の転送部 113 に接続される。各転送部 113 は、共通のバッファアンプ 123 に接続される。ラインセンサ部 L1B、L2B、・・・も、図 2 と同様の構成を有する。

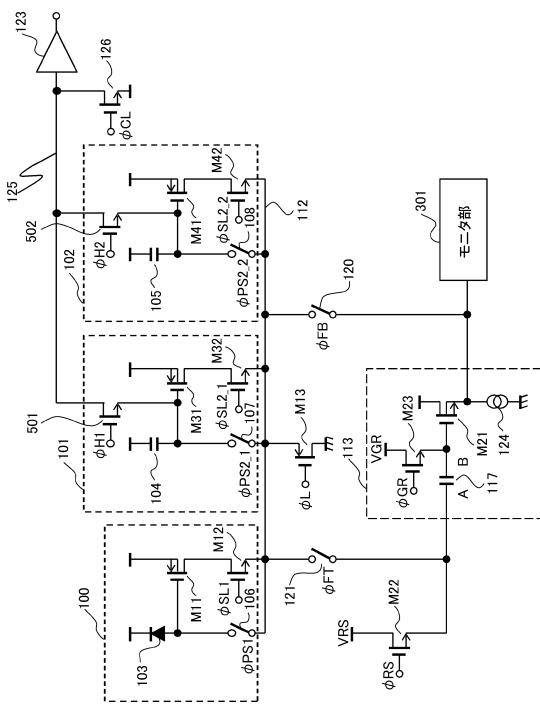

#### 【0013】

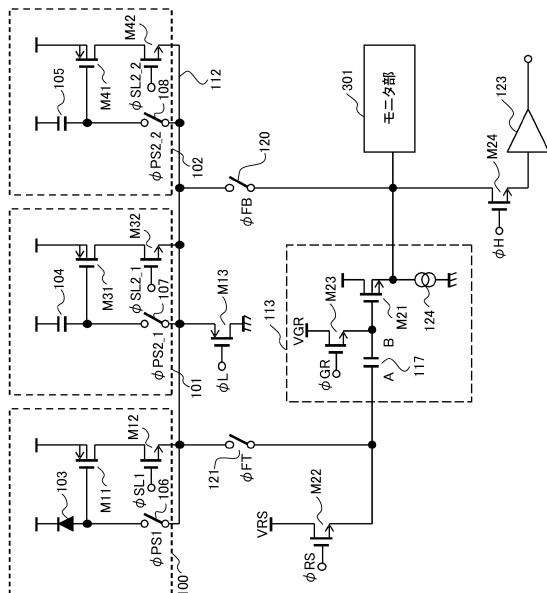

図 3 は、図 2 の一部を抜き出した光電変換装置の構成例を示す図であり、特に単位画素 11A と、これに接続された転送部 113 とに着目して説明を行う。単位画素 11A は、センサセル部 100、第 1 メモリセル部 101、及び第 2 メモリセル部 102 を有する。図 3 において、MOS トランジスタの制御電極並びにスイッチに付された PS1、S L1 等は、不図示の制御部から供給される信号を意味している。

10

#### 【0014】

単位画素 11A に着目すると、センサセル部 100 は、光電変換部であるフォトダイオード 103、センサセル部書き込みスイッチ 106、及びトランジスタ M11、M12 を有する。フォトダイオード 103 のアノードはセンサセル部書き込みスイッチ 106 の一方の端子とトランジスタ M11 の制御電極に接続され、カソードは電源電圧ノードに接続される。トランジスタ M11 は、負荷 MOS トランジスタ M13 とともに、ゲインが -1 のソース接地反転アンプを構成する。センサセル部 100 は、トランジスタ M11 のセンサセル部反転アンプを介して、フォトダイオード 103 で光電変換された電荷量に基づく蓄積信号を共通信号線 112 に出力する。トランジスタ M11 の反転アンプは、フォトダイオード 103 の信号に基づく信号を出力する。MOS トランジスタ M12 は、センサセル部 100 を選択するための選択スイッチとして機能する。センサセル部書き込みスイッチ 106 は、フォトダイオード 103 のアノードと共に共通信号線 112 との導通又は非導通を切り換えるもので、PMOS トランジスタ、NMOS トランジスタ、又は CMOS トランジスタなどで構成することができる。メモリセル部 101 及び 102 は、センサセル部 100 に対して、フォトダイオード 103 をメモリ容量 104 及び 105 に置き換えた構成となっている。第 1 メモリセル部 101 は、メモリ容量 104 と、メモリ容量 104 に接続されるメモリセル部書き込みスイッチ 107 と、メモリセル部ソース接地反転アンプを構成するトランジスタ M31 と、メモリセル部選択スイッチ M32 とを有する。メモリセル部選択スイッチ M32 は、トランジスタ M31 の出力信号を共通信号線 112 に出力するためのスイッチである。トランジスタ M31 のメモリセル部アンプは、メモリセル部反転アンプであり、メモリ容量 104 に保持されている信号に基づく信号を出力する。第 2 メモリセル部 102 は、メモリ容量 105 と、メモリ容量 105 に接続されるメモリセル部書き込みスイッチ 108 と、メモリセル部ソース接地反転アンプを構成するトランジスタ M41 と、メモリセル部選択スイッチ M42 とを有する。メモリセル部選択スイッチ M42 は、トランジスタ M41 の出力信号を共通信号線 112 に出力するためのスイッチである。トランジスタ M41 のメモリセル部アンプは、メモリセル部反転アンプであり、メモリ容量 105 に保持されている信号に基づく信号を出力する。共通信号線 112 は、センサセル部 100、第 1 メモリセル部 101 及び第 2 メモリセル部 102 に接続される。

20

#### 【0015】

次に、転送部 113 について説明する。転送部 113 は、MOS トランジスタ M21、M23、転送容量 117 及び定電流源 124 を有し、スイッチ 120 及び 121 を介して共通信号線 112 に接続可能である。MOS トランジスタ M21 と定電流源 124 とでソースフォロワを形成している。共通信号線 112 は、トランスファースイッチ 121 とフィードバックスイッチ 120 に接続される。トランスファースイッチ 121 の他方の端子は、転送容量 117 の一方の端子 A 及び MOS トランジスタ M22 の一方の主電極に接続される。MOS トランジスタ M22 の他方の主電極は、基準電圧 VRS のノードに接続される。光信号読み出しスイッチである MOS トランジスタ M24 の一方の主電極は、バッファアンプ 123 に接続される。転送容量 117 の他方の端子 B は、MOS トランジスタ M21 の制御電極及び MOS トランジスタ M23 の一方の主電極に接続される。MOS ト

40

50

ランジスタM23の他方の主電極は、クランプ電圧VGRのノードに接続される。MOSトランジスタM21の一方の主電極は、電源電圧VDDのノードに接続される。MOSトランジスタM21の他方の主電極は、定電流源124、フィードバックスイッチ120の他方の端子、センサアレイ外部に配置されたモニタ部301及び光信号読み出しスイッチであるMOSトランジスタM24の他方の主電極に接続される。転送部113は、後述する動作により、センサセル部100から出力された信号とメモリセル部104, 105から出力された信号との差分処理を行う。

#### 【0016】

図6は、図3に示すスイッチやMOSトランジスタの制御電極に与えられる信号を示している。以下では、図3及び6を参照しながら本実施形態に係る光電変換装置の駆動方法を説明する。各スイッチ及びMOSトランジスタは、図6に示す信号がハイレベルで導通し、ローレベルで非導通になる。信号Lは、ハイレベルのとき、トランジスタM11に電位VRSが入力された時、トランジスタM11と負荷MOSトランジスタM13で構成される反転アンプが電位VRSを出力するように一定の電流を駆動するゲート電位に設定される。

#### 【0017】

図6において、期間(1)では、フォトダイオード103及びメモリ容量104, 105をリセットする動作が行われる。具体的な動作として、信号RS、FT、PS1、PS2\_1、PS2\_2及びGRがハイレベルになる。すると、センサセル部書き込みスイッチ106、メモリセル部書き込みスイッチ107, 108、トランスファースイッチ121、MOSトランジスタM22及びMOSトランジスタM23が導通する。これにより、フォトダイオード103及びメモリ容量104, 105が基準電圧VRSにリセットされるとともに、転送容量117の端子Aが基準電圧VRS、端子Bがクランプ電圧VGRにリセットされる。ここで、クランプ電圧VGRは、基準電位VRSに、センサセル部100、メモリセル部104, 105又は転送部113のセルフバイアスソースフォロワの閾値Vthを加えた、 $VGR = VRS + Vth$ に設定される。次に、信号PS1、PS2\_1、PS2\_2及びRSがローレベルになり、初期化動作が終了する。このとき、書き込みスイッチ106、107、108がオフする直前の両端の電位は、リセット電位にそろっているので、前述した書き込みスイッチオフ動作に伴う電位変動は各ビットで共通である。したがって、フォトダイオード103及びメモリ容量104, 105には、容量値に依存するkTCノイズのみ発生する。ここで、メモリ容量104及び105の容量値は、フォトダイオード103の検出容量に比べて十分大きい。例えば、フォトダイオード103の検出容量6fFに対して、メモリ容量104及び105の容量値は320fFである。メモリ容量104及び105の容量値は、メモリセル部101及び102の書き込みスイッチ107及び108がオフする際の電位変動、及びkTCノイズを十分無視できる程度に設計している。以下では、kTCノイズを含む書き込みスイッチ106のオフ時のフォトダイオード103の電位変動をNrstとする。信号PS1がローレベルになったタイミングから、センサセル部100の蓄積動作期間が開始する。

#### 【0018】

その後、期間(2)でセンサセル部100の電位変動Nrst及びトランジスタM11のアンプの固定パターンノイズNsを転送部113を介してメモリセル部101、102に書き込む動作を行う。信号PS1、PS2\_1、PS2\_2及びRSがローレベルになった後に、信号SL1及びLがハイレベルになる。すると、リセット電位VRSにセンサセル部100の電位変動Nrst及びセンサセル部100の固定パターンノイズNsが加わったVRS - Nrst + Nsが転送容量117の端子Aに書き込まれる。ここで、Nrstの符号が反転しているのは、反転アンプで-1のゲインが印加されているためである。そして、信号GRがローレベルになることにより、転送容量117の端子Bがフローティングになる。さらに、信号SL2\_1がハイレベルになることにより、メモリセル部101からトランジスタM31の固定パターンノイズNm1を含んだ信号VRS + Nm1が出力される。転送容量117の端子AがVRS + Nm1に変化するので

10

20

30

40

50

、端子 B の電位は  $V_{GR} + N_{rst} - N_s + N_{m1} = V_{RS} + V_{th} + N_{rst} - N_s + N_{m1}$  になる。次に、信号  $F_B$  がハイレベルになる。すると、転送容量 117 の端子 B に保持された  $V_{RS} + V_{th} + N_{rst} - N_s + N_{m1}$  に転送部 113 のソースフォロワの  $V_{th}$  と固定パターンノイズ  $N_t$  が重畠された  $V_{RS} + N_{rst} - N_s + N_{m1} + N_t$  が共通信号線 112 に出力される。この間に信号  $PS2\_1$  が一時的にハイレベルとなることで、電圧  $V_{RS} + N_{rst} - N_s + N_{m1} + N_t$  がメモリセル部 101 のメモリ容量 104 に書き込まれる。メモリセル部 101 は、フォトダイオード 103 の信号をメモリ容量 104 に保持する前に、電位変動  $N_{rst}$  と、センサセル部 100 の固定パターンノイズ  $N_s$  と、メモリセル部 101 の固定パターンノイズ  $N_{m1}$  とを含む信号をメモリ容量 104 に保持する。電位変動  $N_{rst}$  は、センサセル部書き込みスイッチ 106 のオフ動作に伴うフォトダイオード 103 の電位変動である。

10

#### 【0019】

メモリセル部 102 に対しても同様の動作を行い、電圧  $V_{RS} + N_{rst} - N_s + N_{m2} + N_t$  がメモリセル部 102 のメモリ容量 105 に書き込まれる。ここで、 $N_{m2}$  は、メモリセル部 102 のトランジスタ M41 の固定パターンノイズである。メモリセル部 102 は、フォトダイオード 103 の信号をメモリ容量 105 に保持する前に、電位変動  $N_{rst}$  と、センサセル部 100 の固定パターンノイズ  $N_s$  と、メモリセル部 102 の固定パターンノイズ  $N_{m2}$  とを含む信号をメモリ容量 105 に保持する。

#### 【0020】

期間 (3) では、オートゲインコントロール (AGC) 動作が行われる。信号  $SL1$  20 及び  $FT$  がハイレベルになるので、センサセル部 100 から共通信号線 112 にセンサセル部 100 で光電変換された信号  $S1$  に応じた信号  $V_{RS} - S1 + N_s - N_{rst}$  が現れる。すなわち、センサセル部 100 は、フォトダイオード 103 の光電変換信号  $S1$  と、センサセル部書き込みスイッチ 106 のオフ動作に伴うフォトダイオード 103 の電位変動  $N_{rst}$  とを含む信号を共通信号線 112 に出力する。さらに、信号  $GR$  をハイレベルにするので、端子 B が  $V_{GR}$  ( $= V_{RS} + V_{th}$ ) にリセットされる。その後、信号  $GR$  をローレベルにして、転送容量 117 の端子 B をフローティングにする。

#### 【0021】

次に、信号  $SL1$  をローレベルにした後、信号  $SL2\_1$  がハイレベルになり、メモリセル部選択スイッチ M32 がオンする。期間 (2) では、メモリセル部 101 のメモリ容量 104 に保持された  $V_{RS} + N_{rst} - N_s + N_{m1} + N_t$  にメモリセル部 101 の固定パターンノイズ  $N_{m1}$  が加わる。これにより、メモリセル部 101 のメモリ容量 104 から共通信号線 112 を通して電圧  $V_{RS} - N_{rst} + N_s - N_t$  が転送容量 117 の端子 A に出力される。このとき、転送容量 117 の端子 B は電圧  $V_{GR} + S1 - N_t$  となり、転送部 113 から電圧  $V_{RS} + S1$  が出力される。すなわち、転送部 113 は、上記のセンサセル部 100 の出力信号と、メモリセル部 101 の出力信号との差分信号を生成する。転送部 113 から電圧  $V_{RS} + S1$  の出力がモニタ部 301 に入力されるので、モニタ部 301 ではノイズの影響のない光信号  $S1$  だけをモニタすることができる。期間 (3) におけるセンサセル部 100 の出力は、モニタ部 301 にてリアルタイムで観測される。モニタ部 301 にはゲイン可変増幅部が含まれており、光信号波形の最大値及び最小値の検出結果に応じてゲインが可変され、所定の蓄積レベルに達すると蓄積終了のフラグを立てる。この動作をオートゲインコントロール (AGC) と呼ぶ。光信号蓄積中に期間 (3) の動作を行うことにより、モニタ部 301 でフォトダイオード 103 の蓄積状況をリアルタイムにモニタできる。モニタ部 301 によるモニタ動作の結果、期間 (3) で蓄積動作が終了した時点での、センサセル部 100 に保持される光信号を  $S2$  とする。メモリセル部 102 についても、期間 (4) にて同様の動作を行う。モニタ部 301 によるモニタ動作の結果、期間 (4) で蓄積動作が終了した時点での、センサセル部 100 に保持される光信号を  $S3$  とする。

30

40

#### 【0022】

期間 (5) では、蓄積終了後に、蓄積信号  $S2$  をメモリセル部 101 に保持する動作を 50

行う。信号  $S_{L1}$ 、 $L$  及び  $FT$  がハイレベルになるので、センサセル部 100 から共通信号線 112 にセンサセル部 100 で光電変換された信号  $S_2$  に応じた信号  $VRS - S_2 + Ns - Nrst$  が現れる。すなわち、センサセル部 100 は、フォトダイオード 103 の光電変換信号  $S_2$  と、センサセル部書き込みスイッチ 106 のオフ動作に伴うフォトダイオード 103 の電位変動  $Nrst$  とを含む信号を共通信号線 112 に出力する。さらに、信号  $GR$  をハイレベルにするので、転送容量 117 の端子 B が電圧  $VGR$  ( $= VRS + Vth$ ) にリセットされる。その後、信号  $GR$  をローレベルにして、転送容量 117 の端子 A と端子 B をフローティングにする。次に、信号  $S_{L1}$  をローレベルにした後、信号  $S_{L2\_1}$  がハイレベルになり、メモリセル部選択スイッチ  $M_{32}$  がオンする。すると、期間 (2) でメモリセル部 101 のメモリ容量 104 に保持された  $VRS + Nrst - Ns + Nm1 + Nt$  にメモリセル部 101 の固定パターンノイズ  $Nm1$  が加わる。これにより、メモリセル部 101 から共通信号線 112 を通して電圧  $VRS - Nrst + Ns - Nt$  が転送容量 117 の端子 A に出力される。このとき、転送容量 117 の端子 B は電圧  $VGR + S2 - Nt$  となり、信号  $PS2\_1$  が一時的にハイレベルになることで、転送部 113 から出力された電圧  $VRS + S2$  がメモリセル部 101 のメモリ容量 104 に保持される。すなわち、転送部 113 は、上記のセンサセル部 100 の出力信号と、メモリセル部 101 の出力信号との差分信号を生成する。メモリセル部 101 は、その差分信号をメモリ容量 104 に保持する。

10

#### 【0023】

期間 (6) では、期間 (2) の後半と同様にして、異なる蓄積時間の蓄積信号  $S_3$  がメモリセル部 102 に保持される。信号  $S_{L1}$ 、 $L$  及び  $FT$  がハイレベルになるので、センサセル部 100 から共通信号線 112 にセンサセル部 100 で光電変換された信号  $S_3$  に応じた信号  $VRS - S_3 + Ns - Nrst$  が現れる。すなわち、センサセル部 100 は、フォトダイオード 103 の光電変換信号  $S_3$  と、センサセル部書き込みスイッチ 106 のオフ動作に伴うフォトダイオード 103 の電位変動  $Nrst$  とを含む信号を共通信号線 112 に出力する。さらに、信号  $GR$  をハイレベルにするので、転送容量 117 の端子 B が電圧  $VGR$  ( $= VRS + Vth$ ) にリセットされる。その後、信号  $GR$  をローレベルにして、転送容量 117 の端子 A と端子 B をフローティングにする。次に、信号  $S_{L1}$  をローレベルにした後、信号  $S_{L2\_2}$  がハイレベルになり、メモリセル部選択スイッチ  $M_{42}$  がオンする。すると、期間 (2) でメモリセル部 102 のメモリ容量 105 に保持された  $VRS + Nrst - Ns + Nm2 + Nt$  にメモリセル部 102 の固定パターンノイズ  $Nm2$  が加わる。これにより、メモリセル部 102 から共通信号線 112 を通して電圧  $VRS - Nrst + Ns - Nt$  が転送容量 117 の端子 A に出力される。このとき、転送容量 117 の端子 B は電圧  $VGR + S3 - Nt$  となり、信号  $PS2\_2$  が一時的にハイレベルになることで、転送部 113 から出力された電圧  $VRS + S3$  がメモリセル部 102 のメモリ容量 105 に保持される。すなわち、転送部 113 は、上記のセンサセル部 100 の出力信号と、メモリセル部 102 の出力信号との差分信号を生成する。メモリセル部 102 は、その差分信号をメモリ容量 105 に保持する。こうすることで、1 回の蓄積シーケンスでセンサセル部 100 から、異なる蓄積時間に基づく信号を取得することができる。これにより、1 回の蓄積シーケンスに同一ラインで複数の測距点を設けることができる。測距点の多点化又は高速な焦点検出動作が実現できる。

20

30

40

#### 【0024】

期間 (7) では、メモリセル部 101 のメモリ容量 104 に保持した光信号をビット毎に読み出す動作を行う。信号  $S_{L2\_1}$ 、 $L$ 、 $GR$ 、 $FT$  がハイレベルになる。すると、第 1 メモリセル部 101 のメモリ容量 104 に保持されていた光信号  $S_2$  に、第 1 メモリセル部 101 のノイズ  $Nm1$  が加わって、電圧  $VRS - S2 + Nm1$  が転送容量 117 の端子 A に与えられ、端子 B の電位は  $VGR$  ( $= VRS + Vth$ ) になる。その後、信号  $FT$  がローレベルになることで、転送容量 117 の端子 A がフローティングになる。

#### 【0025】

次に、信号 F B と P S 2 \_ 1 がハイレベルになり、固定パターンノイズ N t を含んだ転送部 1 1 3 の出力 V R S + N t がメモリセル部 1 0 1 に入力される。その後、信号 P S 2 \_ 1 がローレベルになって、電圧 V R S + N t がメモリセル部 1 0 1 のメモリ容量 1 0 4 に保持される。

【 0 0 2 6 】

次に、信号 G R をローレベルにして、転送容量 1 1 7 の端子 B をフローティングにする。さらに、信号 S L 2 \_ 1 、 L 、 F T がハイレベルになる。すると、第 1 メモリセル部 1 0 1 のメモリ容量 1 0 4 に保持されていた電圧 V R S + N t に、第 1 メモリセル部 1 0 1 のノイズ N m 1 が加わる。これにより、電圧 V R S - N t + N m 1 が転送容量 1 1 7 の端子 A に与えられ、端子 B の電位は  $V G R + S 2 - N t = V R S + V t h + S 2 - N t$  10 になる。転送部 1 1 3 から出力される信号は、転送部 1 1 3 の固定パターンノイズ N t が加わって V R S + S 2 となる。すなわち、転送部 1 1 3 は、メモリ容量 1 0 4 に保持されている信号と、転送部 1 1 3 の固定パターンノイズ N t との差分信号を生成する。結果的に、ノイズの影響が低減された信号が出力される。この期間に、シフトレジスタ 1 0 0 6 ( 図 1 0 ) から信号 H が供給されると、信号 S 2 がバッファアンプ 1 2 3 に伝達されて、後段の信号処理装置 9 0 6 ( 図 1 3 ) に出力される。

【 0 0 2 7 】

期間 ( 8 ) では、メモリセル部 1 0 2 について異なる蓄積時間の蓄積信号 S 3 を読み出す動作を行う。信号 S L 2 \_ 2 、 L 、 G R 、 F T がハイレベルになる。すると、第 2 メモリセル部 1 0 2 のメモリ容量 1 0 5 に保持されていた光信号 S 3 に、第 2 メモリセル部 1 0 2 のノイズ N m 2 が加わって、電圧 V R S - S 3 + N m 2 が転送容量 1 1 7 の端子 A に与えられ、端子 B の電位は  $V G R (= V R S + V t h)$  20 になる。その後、信号 F T がローレベルになることで、転送容量 1 1 7 の端子 A がフローティングになる。

【 0 0 2 8 】

次に、信号 F B と P S 2 \_ 2 がハイレベルになり、固定パターンノイズ N t を含んだ転送部 1 1 3 の出力 V R S + N t がメモリセル部 1 0 2 に入力される。その後、信号 P S 2 \_ 2 がローレベルになって、電圧 V R S + N t がメモリセル部 1 0 2 のメモリ容量 1 0 5 に保持される。

【 0 0 2 9 】

次に、信号 G R をローレベルにして、転送容量 1 1 7 の端子 B をフローティングにする。さらに、信号 S L 2 \_ 2 、 L 、 F T がハイレベルになる。すると、第 2 メモリセル部 1 0 2 のメモリ容量 1 0 5 に保持されていた電圧 V R S + N t に、第 2 メモリセル部 1 0 2 のノイズ N m 2 が加わる。これにより、電圧 V R S - N t + N m 2 が転送容量 1 1 7 の端子 A に与えられ、端子 B の電位は  $V G R + S 3 - N t = V R S + V t h + S 3 - N t$  30 になる。転送部 1 1 3 から出力される信号は、転送部 1 1 3 の固定パターンノイズ N t が加わって V R S + S 3 となる。すなわち、転送部 1 1 3 は、メモリ容量 1 0 5 に保持されている信号と、転送部 1 1 3 の固定パターンノイズ N t との差分信号を生成する。結果的に、ノイズの影響が低減された信号が出力される。この期間に、シフトレジスタ 1 0 0 6 ( 図 1 0 ) から信号 H が供給されると、信号 S 3 がバッファアンプ 1 2 3 に伝達されて、後段の信号処理装置 9 0 6 ( 図 1 3 ) に出力される。40

【 0 0 3 0 】

以上、説明したように、本実施形態では、センサセル部 1 0 0 の書き込みスイッチ 1 0 6 のオフ動作に伴うフォトダイオード 1 0 3 の電位変動 N r s t をメモリセル部 1 0 1 又は 1 0 2 に保持する。さらに、センサセル部 1 0 0 の固定パターンノイズ N s と、メモリセル部 1 0 1 又は 1 0 2 の固定パターンノイズ N m 、転送部 1 1 3 の固定パターンノイズ N t をメモリセル部 1 0 1 又は 1 0 2 に保持する。

【 0 0 3 1 】

また、蓄積モニタ及び蓄積信号保持動作において、以下の ( a ) 及び ( b ) の動作を行う。 ( a ) 蓄積電圧 S 1 とセンサセル部 1 0 0 の書き込みスイッチ 1 0 6 のオフ動作に伴うフォトダイオード 1 0 3 の電位変動 N r s t と、センサセル部 1 0 0 の固定パターンノ 50

イズN<sub>s</sub>を含むセンサセル部100の出力を得る。(b)センサセル部100の書き込みスイッチ106のオフ動作に伴うフォトダイオード103の電位変動N<sub>r s t</sub>と、センサセル部100の固定パターンノイズN<sub>s</sub>と、転送部113の固定パターンノイズN<sub>t</sub>を含むメモリセル部101又は102の出力を得る。そして、(a)と(b)の差分を演算して、転送部113から出力する。

#### 【0032】

また、信号読み出し動作において、以下の(c)及び(d)の動作を行う。(c)光信号S2を保持したメモリセル部101の出力又は光信号S3を保持したメモリセル部102の出力と、(d)転送部113の固定パターンノイズN<sub>t</sub>を保持したメモリセル部101又は102の出力を得る。そして、(c)と(d)の差分を演算して、転送部113から出力する。

10

#### 【0033】

仮に、センサセル部100にセンサセル部100と転送部113の固定パターンノイズを保持すると、書き込みスイッチ106がオフする際にフォトダイオード103の電位変動が発生する。書き込みスイッチ106がMOSトランジスタで構成される場合、スイッチオフ時にゲート電位の変動がMOSトランジスタのソース、ドレインに伝搬する(クロックフィールドスルーリー)。また、スイッチオン時にゲート下に保持されたキャリアが、スイッチオフ時にソース又はドレインに移動する(チャージインジェクション)。これらのスイッチオフ時のソース、ドレインの電位変動は、スイッチオフ直前のソース、ドレインの電位に依存する。すなわち、固定パターンノイズをスイッチ手段を介してセンサセル部100のフォトダイオード103に保持する場合、固体パターンノイズに相当するばらつきが画素間のソース、ドレイン電位に生じる。すると、前述したスイッチオフ時に生じる電位変動量もビット間で異なるため、フォトダイオード103に保持される固定パターンノイズは本来除去すべき固定パターンノイズと異なる。その結果、AGC時に蓄積信号から固定パターンノイズを十分に除去できないのでAF精度が低下する。

20

#### 【0034】

本実施形態では、センサセル部100にセンサセル部100及び転送部113の固定パターンノイズを保持することなく、AGCと信号読み出しでノイズを除去した信号を読み出すことができる。センサセル部100の検出容量を小さくしても、書き込みスイッチ106のオフ動作に伴う電位変動の画素間バラツキが発生しない。よって、ノイズの少ない信号で精度よくAGCを行えるので、高精度なAFを実現することができる。その結果、エリアタイプAFにおいて、フォトダイオード103の検出容量を下げて、センサ感度を高めても、高精度なAFを実現することができる。

30

#### 【0035】

本実施形態では、2つのメモリセル部101及び102を設けた例を説明したが、メモリセル部の数は1又は3以上であってもよい。3つ以上の場合には、期間(2)、(4)、(6)、(8)の動作に対応する操作を、追加したメモリセル部に対しても行う。

#### 【0036】

図10及び図11は、図3に示した光電変換装置のレイアウト例を示す図である。図10では、ラインセンサ部1001は、図2のラインセンサ部L1A, L2A等に対応する。センサセル部1002は、図2の複数のセンサセル部100を有する。第1メモリセル部1003は、図2の複数の第1メモリセル部101を有する。第2メモリセル部1004は、図2の複数の第2メモリセル部102を有する。転送部1005は、図2の複数の転送部113を有する。シフトレジスタ10006は、信号Hを図3の回路に出力する。センサセル部1002と2つのメモリセル部1003, 1004を一つの組として、その組を行列状に配列したものである。転送部1005及びシフトレジスタ1006は、各列に設けられた複数のセンサセル部1002とメモリセル部1003, 1004に対して共通に設けられている。

40

#### 【0037】

図11は、センサセル部1002のみが配列された領域と、メモリセル部1003及び

50

1004のみが配列された領域とに分けてレイアウトした場合の図である。このレイアウトにおいても、転送部1005及びシフトレジスタ1006は、各列に設けられた複数のセンサセル部1002とメモリセル部1003, 1004に対して共通に設けられている。

【0038】

また、転送部113は、複数列のラインセンサ部L1A, L2Aに対して1つ配置すればよいので、センサセル部100、メモリセル部101及び102と比較してレイアウト面積に余裕がある。一例として、転送部113にソースフォロワのオフセットを除去する機能を備えてもよい。その場合、本実施形態の信号伝搬の記述から転送部113の固定パターンノイズNtrを無視できる。

10

【0039】

(第2の実施形態)

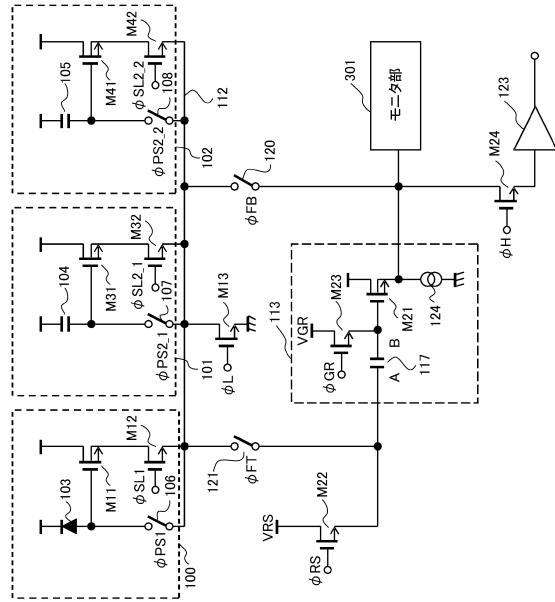

図4は、本発明の第2の実施形態に係る光電変換装置の構成例を説明する図である。図3と共に用いられる箇所は説明を省略する。図3と異なるのは、図3のゲイン-1の反転アンプが図4のゲイン1のソースフォロワの正転アンプに変更されている点である。セルフバイアストランジスタM11、M31、M41が負荷MOSトランジスタM13とともにゲインが1のソースフォロワ正転アンプを構成する。センサセル部100は、トランジスタM11のセンサセル部正転アンプを介して、フォトダイオード103で光電変換された電荷量に基づく蓄積信号を共通信号線112に出力する。メモリセル部101は、トランジスタM31のメモリセル部正転アンプを介して、メモリ容量104に保持されている信号に基づく信号を共通信号線112に出力する。メモリセル部102は、トランジスタM41のメモリセル部正転アンプを介して、メモリ容量105に保持されている信号に基づく信号を共通信号線112に出力する。

20

【0040】

図7を用いて、本発明の第2の実施形態の動作を説明する。期間(1)の動作は第1の実施形態と同じなので説明を省略する。第1の実施形態と異なるのは、リセット電圧VRSとVGRである。前述のソースフォロワアンプによる入出力電圧オフセット量をVthとすると、それぞれVRSがVRSからVRS+Vthに変更され、VGRがVRS+VthからVRS+2Vthに変更されている。ここで、Vthは各画素に共通のオフセット量で、センサ内の代表的なソースフォロワ回路から決定される。

30

【0041】

期間(2)では、センサセル部100の電位変動Nrst及び固定パターンノイズNsを転送部113を介してメモリセル部101、102に書き込む動作を行う。信号PS1、PS2\_1、PS2\_2及びRSがローレベルになった後に、信号SL2\_1及びLがハイレベルになる。すると、メモリセル部101から固定パターンノイズNm1を含んだ信号VRS+Nm1が出力され、転送容量117の端子Aに書き込まれる。そして、信号GRがローレベルになることで、転送容量117の端子Bがフローティングになる。次に、信号SL2\_1がローレベルになって、信号SL1がハイレベルになることで、リセット電圧VRSにセンサセル部100の電位変動Nrst及びセンサセル部100の固定パターンノイズNsが加わったVRS+Nrst+Nsが出力される。転送容量117の端子AがVRS+Nrst+Nsに変化するので、転送容量117の端子Bの電位はVGR+Nrst+Ns-Nm1=VRS+2Vth+Nrst+Ns-Nm1になる。次に、信号FBがハイレベルになる。すると、転送容量117の端子Bに保持された電圧VRS+2Vth+Nrst+Ns-Nm1に転送部113のソースフォロワのVthと固定パターンノイズNtが重畠された電圧VRS+Vth+Nrst+Ns-Nm1+Ntが共通信号線112に出力される。この期間に、信号PS2\_1が一時的にハイレベルとなることで、電圧VRS+Vth+Nrst+Ns-Nm1+Ntがメモリセル部101のメモリ容量104に書き込まれる。メモリセル部102に対しても同様の動作を行い、電圧VRS+Vth+Nrst+Ns-Nm2+Ntがメモリセル部102のメモリ容量105に書き込まれる。ここで、Nm2はメモリセル部102の固定

40

50

パターンノイズである。

【0042】

期間(3)では、AGC動作が行われる。信号SL2\_1及びL、FTがハイレベルになるので、期間(2)においてメモリセル部101のメモリ容量104に保持された電圧VRS+Vth+Nrst+Ns-Nm1+Ntにメモリセル部101の固定パターンノイズNm1が加わる。これにより、メモリセル部101から共通信号線を通してVRS+Nrst+Ns+Ntが転送容量117の端子Aに出力される。さらに、信号GRをハイレベルにすることで、転送容量117の端子Bが電圧VGR(=VRS+2Vth)にリセットされる。その後、信号GRをローレベルにして、転送容量117の端子Bをフローティングにする。

10

【0043】

次に、信号SL2\_1がローレベルになって、信号SL1がハイレベルになるので、センサセル部100で光電変換された信号S1に応じた信号VRS+S1+Ns+Nrstがセンサセル部100から転送容量117の端子Aに出力される。このとき、転送容量117の端子Bは電圧VGR+S1-Ntとなり、転送部113から電圧VRS+Vth+S1が出力される。モニタ部301におけるAGC動作は、第1の実施形態と同様である。Vthは各画素で共通のオフセット量なので、画素バラツキの要因にはならない。メモリセル部102についても、期間(4)にて同様の動作を行う。

【0044】

期間(5)では、蓄積終了後に蓄積信号S2をメモリセル部101に保持する動作を行う。信号SL1、L及びFTがハイレベルになるので、センサセル部100から共通信号線112にセンサセル部100で光電変換された信号S2に応じた信号VRS+S2+Ns+Nrstが現れる。さらに、信号GRをハイレベルにすることで、転送容量117の端子Bが電圧VGR(=VRS+2Vth)にリセットされる。その後、信号GRをローレベルにして、転送容量117の端子Aと端子Bをフローティングにする。次に、信号SL1をローレベルにした後、信号SL2\_1がハイレベルになる。すると、期間(2)でメモリセル部101のメモリ容量104に保持された電圧VRS+Vth+Nrst+Ns-Nm1+Ntにメモリセル部101の固定パターンノイズNm1が加わる。これにより、メモリセル部101のメモリ容量104から共通信号線112を通して電圧VRS+Nrst+Ns+Ntが転送容量117の端子Aに出力される。このとき、転送容量117の端子Bは電圧VGR-S2+Ntとなり、信号PS2\_1がハイレベルになることで、転送部113から出力された電圧VRS+Vth-S2+2Ntがメモリセル部101のメモリ容量104に保持される。

20

30

【0045】

期間(6)では、期間(5)と同様にして、異なる蓄積時間の蓄積信号S3がメモリセル部102のメモリ容量105に保持される。こうすることで、1回の蓄積シーケンスでセンサセル部100から、異なる蓄積時間に基づく信号を取得することができる。これにより、1回の蓄積シーケンスに同一ラインで複数の測距点を設けることができるので、測距点の多点化又は高速な焦点検出動作が実現できる。

【0046】

40

期間(7)では、メモリセル部101に保持した光信号をビット毎に読み出す動作である。信号SL2\_1、L、GR、FTがハイレベルになる。すると、第1メモリセル部101のメモリ容量104に保持されていた電圧VRS+Vth-S2+2Ntに、第1メモリセル部101のノイズNm1が加わる。これにより、電圧VRS-S2+Nm1+2Ntが転送容量117の端子Aに与えられ、転送容量117の端子Bの電位は電圧VGR(=VRS+2Vth)になる。その後、信号FTがローレベルになることで、転送容量117の端子Aがフローティングになる。

【0047】

次に、信号FBとPS2\_1がハイレベルになり、固定パターンノイズNtを含んだ転送部113の出力VRS+Vth+Ntがメモリセル部101に入力される。その後

50

、信号 P S 2 \_ 1 がローレベルになって、電圧 V R S + V t h + N t がメモリセル部 101 のメモリ容量 104 に保持される。

#### 【 0 0 4 8 】

次に、信号 G R をローレベルにして、転送容量 117 の端子 B をフローディングにする。さらに、信号 S L 2 \_ 1 、 L 、 F T がハイレベルになると、第 1 メモリセル部 101 のメモリ容量 104 に保持されていた固定パターンノイズ N t に、第 1 メモリセル部 101 のノイズ N m 1 が加わる。これにより、電圧 V R S + N t + N m 1 が転送容量 117 の端子 A に与えられ、転送容量 117 の端子 B の電位は V G R + S 2 - N t = V R S + 2 V t h + S 2 - N t になる。転送部 113 から出力される信号は、転送部 113 の固定パターンノイズ N t が加わって、電圧 V R S + V t h + S 2 となる。結果的に、ノイズの影響が低減された信号が出力される。この期間に、シフトレジスタ 1006 ( 図 10 ) から信号 H が供給されると、信号 S 2 がバッファアンプ 123 に伝達されて、後段の信号処理装置 906 ( 図 13 ) に出力される。

#### 【 0 0 4 9 】

期間 ( 8 ) では、期間 ( 7 ) と同様にして、メモリセル部 102 について異なる蓄積時間の蓄積信号 S 3 を読み出す動作を行う。

#### 【 0 0 5 0 】

以上、説明したように、本実施形態では、センサセル部 100 とメモリセル部 101 , 102 の出力を第 1 の実施形態の反転出力から、セルフバイアスソースフォロワの正転出力に変更している。センサセル部 100 とメモリセル部 101 , 102 が正転出力であっても、センサセル部 100 、メモリセル部 101 , 102 、転送部 113 で発生する固定パターンノイズを除去できるように、駆動パターンを変更する。

#### 【 0 0 5 1 】

第 1 の実施形態で用いている反転アンプは、省レイアウトと出力特性を両立させることが困難である。なぜなら、差動アンプと帰還容量で構成されるスイッチトキャパシタを用いると、レイアウト面積が大きくなる。A F センサは、光学系によりファインダー上の測距点配置によりセンサ上の画素開口位置が限定されるので、反転アンプのレイアウトが大きくなると、測距点を密に配置できず、A F 特性を悪化させる要因になる。

#### 【 0 0 5 2 】

また、第 1 の実施形態で用いているソース接地反転アンプは、基板バイアス効果で出力の線形性が悪化する。また、反転アンプの入力に応じて駆動電流が大きく変化するので、センサの省電力と回路応答性を両立させることが難しい。さらに、反転アンプのトランジスタの相対バラツキによって、出力のゲインが変化して P R N U を悪化しやすい。

#### 【 0 0 5 3 】

一方、本実施形態のように、セルフバイアスソースフォロワの正転出力を用いることで、ソース接地の反転アンプに対して、良好な線形性、安定した駆動電流、相対バラツキが P R N U に影響しにくいといった利点を得られる。

#### 【 0 0 5 4 】

##### ( 第 3 の実施形態 )

図 8 を用いて、本発明の第 3 の実施形態の光電変換装置の動作を説明する。期間 ( 1 ) ~ ( 6 ) の動作は第 1 の実施形態と同じなので説明を省略する。

#### 【 0 0 5 5 】

期間 ( 7 ) において、信号 P S 2 \_ 1 をシフトレジスタで各画素について順次ハイレベルにすると、メモリセル部書き込みスイッチ 107 がオンする。信号 P S 2 \_ 1 に対して、相補的に、信号 R S と F T をハイレベルにする。その結果、前期間までにメモリ容量 104 に保持されていた光信号 S 2 が共通信号線 112 を介してバッファアンプ 123 の入力に伝搬するので、画素信号を順次読み出すことができる。バッファアンプ 123 に入力される電圧は、共通信号線 112 とバッファアンプ 123 の寄生容量とメモリ容量 104 の容量比で決定される。

#### 【 0 0 5 6 】

期間(8)では、期間(7)と同様にして、メモリセル部102について異なる蓄積時間の蓄積信号S3を読み出す動作を行う。信号PS2\_2をシフトレジスタで各画素について順次ハイレベルにする。信号PS2\_2に対して、相補的に、信号RSとFTをハイレベルにする。その結果、前期間までにメモリ容量105に保持されていた光信号S3が共通信号線112を介してバッファアンプ123の入力に伝搬するので、画素信号を順次読み出すことができる。バッファアンプ123に入力される電圧は、共通信号線112とバッファアンプ123の寄生容量とメモリ容量105の容量比で決定される。

#### 【0057】

以上、説明したように、本実施形態では、メモリセル部101及び102に保持されていた蓄積信号を、メモリ容量104及び105に直接接続したスイッチ107及び108を介して共通信号線112へ電荷転送で読み出すことができる。

10

#### 【0058】

これにより、第1及び第2の実施形態の期間(7)、(8)で行っていた、メモリセル部101、102の固定パターンノイズNm除去のため、メモリセル部101、102と転送部113間の信号伝搬動作を省くことができる。また、電荷転送は、スイッチ107及び108のオン抵抗と共通信号線112の寄生容量で時定数が決定されるため、転送部113の反転アンプの出力に比べて、高速な読み出し速度を実現することができる。本実施形態は、第2の実施形態の図4の回路にも適用することができる。

#### 【0059】

##### (第4の実施形態)

20

図5は、本発明の第4の実施形態に係る光電変換装置の構成例を説明する図である。図3と共に用いられる箇所は説明を省略する。本実施形態は、図3に対して、図3の信号HのスイッチM24とバッファアンプ123で構成される読み出し経路が、図5の信号H1及びH2の読み出しスイッチ501及び502と、信号CLの初期化スイッチ126に変更されている。読み出しスイッチ501及び502は、シフトレジスタで駆動される信号H1及びH2により制御される。初期化スイッチ126は、読み出しスイッチ501及び502に接続される読み出し線125を所定の電位に初期化するためのスイッチである。メモリセル部101は、メモリ容量104と読み出し線125との間に設けられる読み出しスイッチ501を有する。メモリセル部102は、メモリ容量105と読み出し線125との間に設けられる読み出しスイッチ502を有する。

30

#### 【0060】

図9を用いて、本発明の第4の実施形態の光電変換装置の動作を説明する。期間(1)～(6)の動作は、第1及び第3の実施形態と同じなので説明を省略する。

#### 【0061】

期間(7)において、シフトレジスタで各画素順次オンされる信号H1の読み出しスイッチ501と、信号CLの初期化スイッチ126とが交互にオンさせる。その結果、前期間までにメモリ容量104に保持されていた光信号S2が読み出し線125を介してバッファアンプ123の入力に伝搬するので、画素信号を順次読み出すことができる。バッファアンプ123に入力される電圧は、読み出し線125とバッファアンプ123の寄生容量とメモリ容量104の容量比で決定される。

40

#### 【0062】

期間(8)はメモリセル部102について異なる蓄積時間の蓄積信号S3を読み出す動作である。シフトレジスタで各画素順次オンされる信号H2の読み出しスイッチ502と、信号CLの初期化スイッチ126とが交互にオンさせる。その結果、前期間までにメモリ容量105に保持されていた光信号S3が読み出し線125を介してバッファアンプ123の入力に伝搬するので、画素信号を順次読み出すことができる。バッファアンプ123に入力される電圧は、読み出し線125とバッファアンプ123の寄生容量とメモリ容量105の容量比で決定される。

#### 【0063】

以上、説明したように、本実施形態では、メモリセル部101及び102に保持されて

50

いた蓄積信号を、メモリ容量 104 及び 105 に直接接続した読み出しスイッチ 501 及び 502 を介して読み出し線 125 へ電荷転送で読み出すことができる。第 3 の実施形態では、メモリ容量 104 及び 105 から共通信号線 112 へ電荷転送を行っていた。信号読み出し用の読み出し線 125 を用いることで、信号読み出し時には動作しない素子の接続数を最小限に抑えられる。その結果、第 3 の実施形態の共通信号線 112 の寄生容量に比べて、読み出し線 125 の寄生容量を小さくできるので、読み出し速度の高速化と S/N 向上を実現できる。本実施形態は、第 2 の実施形態の図 4 の回路にも適用することができる。

#### 【0064】

##### (第 5 の実施形態)

図 12 は、本発明の第 5 の実施形態に係る位相差検出方式の焦点検出装置（以下 AF センサと称す）811 の構成例を示す図である。AF センサ 811 は、第 1 ~ 第 4 の実施形態の光電変換装置を有する。AF センサ 811 は、ラインセンサ部 L1A、L2A、…・及び L1B、L2B、…が配列されたセンサブロックと、外部インターフェースと AF センサのタイミング信号を生成する機能を持つロジックブロック 801、アナログ回路ブロック 810 とを有する。アナログ回路ブロック 810 は、AGC 回路 802 ~ 805 を有し、ラインセンサ部 L1A ~ LNA, L1B ~ LNB からの信号のモニタリングや、蓄積時間の制御を行う。アナログ回路ブロック 810 は、さらに、光電変換装置で用いられる参照電圧や参照電流を生成する参照電圧電流生成回路 806、温度計回路 807 等を有する。端子 813 及び 814 は、外部通信端子である。ロジックブロック 801 は、シリアル通信端子 812 を介して外部とのシリアル通信によって AF センサ 811 の駆動タイミングを制御する。本実施形態においても、第 1 ~ 第 4 の実施形態で説明した光電変換装置を用いることで、高速かつ高精度な焦点検出動作が実現できる。

#### 【0065】

##### (第 6 の実施形態)

図 13 は、本発明の第 6 の実施形態に係る撮像システムの構成例を示すブロック図である。901 は後述するレンズ 902 のプロテクトを行うバリア、902 は被写体の光学像を固体撮像装置 904 に結像するレンズ、903 はレンズ 902 を通過した光量を調整するための絞りである。904 はレンズ 902 で結像された被写体の光学像を画像信号として取得する固体撮像装置である。905 は先述の各実施形態で説明した光電変換装置を有する AF センサである。906 は固体撮像装置 904 や AF センサ 905 から出力される信号を処理するアナログ信号処理装置、907 は信号処理装置 906 から出力された信号をアナログデジタル変換する A/D 変換器である。908 は A/D 変換器 907 より出力された画像データに対して各種の補正や、データを圧縮するデジタル信号処理部である。909 は画像データを一時記憶するためのメモリ部、910 は外部コンピュータなどと通信するための外部 I/F 回路、911 はデジタル信号処理部 908 などに各種タイミング信号を出力するタイミング発生部である。912 は各種演算とカメラ全体を制御する全体制御・演算部、913 は記録媒体制御 I/F 部、914 は取得した画像データを記録、又は読み出しを行うための半導体メモリなどの着脱可能な記録媒体、915 は外部コンピュータである。

#### 【0066】

次に、上記の撮像システムの撮影時の動作について説明する。バリア 901 がオープンされ、AF センサ 905 から出力された信号を基に、全体制御・演算部 912 は位相差検出により被写体までの距離を演算する。その後、演算結果に基づいてレンズ 902 を駆動し、再び合焦しているか否かを判断し、合焦していないと判断したときには、再びレンズ 902 を駆動するオートフォーカス制御を行う。次いで、合焦が確認された後に固体撮像装置 904 による蓄積動作が始まる。固体撮像装置 904 の蓄積動作が終了すると、固体撮像装置 904 から出力された画像信号は A/D 変換器 907 でアナログデジタル変換され、デジタル信号処理部 908 を通り全体制御・演算部 912 によりメモリ部 909 に書き込まれる。その後、メモリ部 909 に蓄積されたデータは、全体制御・演算部 912 の

10

20

30

40

50

制御により、記録媒体制御 I / F 部 910 を介して記録媒体 914 に記録される。また、外部 I / F 部 910 を通り直接コンピュータなどに入力してもよい。

### 【0067】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

### 【符号の説明】

### 【0068】

100 センサセル部、101 第1メモリセル部、102 第2メモリセル部、103 10

フォトダイオード、104, 105 メモリ容量、106 センサセル部書き込みスイ

ッチ、107, 108 メモリセル部書き込みスイッチ、112 共通信号線、113

転送部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 义 8 】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

---

フロントページの続き

(56)参考文献 特開2011-120175(JP,A)

特開平09-200614(JP,A)

特開2003-259223(JP,A)

特開2012-124439(JP,A)

特開2010-200276(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762