(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4372115号

(P4372115)

(45) 発行日 平成21年11月25日(2009.11.25)

(24) 登録日 平成21年9月11日(2009.9.11)

(51) Int.Cl.

F 1

|             |           |            |     |

|-------------|-----------|------------|-----|

| H01L 21/301 | (2006.01) | H01L 21/78 | L   |

| B81B 3/00   | (2006.01) | H01L 21/78 | B   |

| B23K 26/38  | (2006.01) | B81B 3/00  |     |

| B23K 26/40  | (2006.01) | B23K 26/38 | 320 |

| B23K 26/00  | (2006.01) | B23K 26/40 |     |

請求項の数 11 (全 12 頁) 最終頁に続く

(21) 出願番号

特願2006-133160 (P2006-133160)

(22) 出願日

平成18年5月12日 (2006.5.12)

(65) 公開番号

特開2007-305810 (P2007-305810A)

(43) 公開日

平成19年11月22日 (2007.11.22)

審査請求日

平成21年3月18日 (2009.3.18)

早期審査対象出願

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100068087

弁理士 森本 義弘

(74) 代理人 100096437

弁理士 笹原 敏司

(74) 代理人 100100000

弁理士 原田 洋平

(72) 発明者

隈川 隆博

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

審査官 横山 幸弘

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法、および半導体モジュールの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板に形成された、複数の半導体素子を個々に分割して半導体装置を製造する方法であつて、

前記複数の半導体素子を個々に分割するための、互いに交差する第一の方向および第二の方向の分割ラインを設定し、前記半導体素子を囲む、前記第一の方向および第二の方向の分割ラインのうち、第一の方向の分割ライン上にエッチングにより溝を形成する工程と、

前記第一の方向の分割ラインに形成された前記溝のライン上、および第二の方向の分割ラインに沿って、レーザ光を照射して、半導体基板の内部に改質領域を形成する工程と、

前記第一の方向および第二の方向の分割ラインに沿って半導体基板を分割して個々の半導体装置を形成する工程と

を有し、

前記溝は交差するパターンをもたないように形成されること

を特徴とする半導体装置の製造方法。

## 【請求項 2】

前記半導体素子に、ダイアフラム構造を形成する工程をさらに有すること

を特徴とする請求項1記載の半導体装置の製造方法。

## 【請求項 3】

前記第一の方向の分割ライン上の溝は連続的に形成されること

10

20

を特徴とする請求項 1 または請求項 2 に記載の半導体装置の製造方法。

**【請求項 4】**

前記第一の方向の分割ラインに形成される溝は、V溝に形成されることを特徴とする請求項 1 ~ 請求項 3 のいずれか 1 項に記載の半導体装置の製造方法。

**【請求項 5】**

前記第一の方向の分割ラインに形成される溝は、U溝に形成されることを特徴とする請求項 1 ~ 請求項 3 のいずれか 1 項に記載の半導体装置の製造方法。

**【請求項 6】**

前記第一の方向の分割ライン上に溝を形成する工程と、前記半導体装置にダイアフラム構造を形成する工程とが、異方性エッチングにより行われることを特徴とする請求項 1 ~ 請求項 5 のいずれか 1 項に記載の半導体装置の製造方法。 10

**【請求項 7】**

前記半導体基板の内部に改質領域を形成する工程において、前記溝が形成された第一の方向の分割ラインに沿ってレーザ光を走査する回数が、前記溝が形成されない第二の方向の分割ラインに沿ってレーザ光を走査する回数よりも少ないことを特徴とする請求項 1 ~ 請求項 6 のいずれか 1 項に記載の半導体装置の製造方法。

**【請求項 8】**

前記第一および第二の方向の分割ラインに沿って半導体基板を分割して個々の半導体装置を形成する工程は、前記半導体基板に外力を加えることにより行われることを特徴とする請求項 1 ~ 請求項 7 のいずれか 1 項に記載の半導体装置の製造方法。 20

**【請求項 9】**

前記請求項 1 ~ 請求項 8 のいずれかの半導体装置の製造方法において形成された半導体装置を、実装基板に固着する工程を有することを特徴とする半導体モジュールの製造方法。

**【請求項 10】**

前記半導体装置を実装基板に固着する工程において、前記半導体装置の裏面が、ダイボンド材によって前記実装基板の上面に接着されることを特徴とする請求項 9 記載の半導体モジュールの製造方法。

**【請求項 11】**

半導体基板に形成された、複数の半導体素子を個々に分割して半導体装置を製造する方法であって、

前記複数の半導体素子を個々に分割するための、互いに交差する第一の方向および第二の方向の分割ラインを設定し、前記半導体素子を囲む、前記第一の方向および第二の方向の分割ラインのうち、一方向の分割ライン上にエッチングにより溝を形成する工程と、

前記第一の方向および第二の方向の分割ラインに沿って、レーザ光を照射して、半導体基板の内部に改質領域を形成する工程と、

前記第一の方向および第二の方向の分割ラインに沿って半導体基板を分割して個々の半導体装置を形成する工程と

を有し、

前記溝は交差するパターンをもたないように形成され、

前記半導体基板の内部に改質領域を形成する工程において、前記溝が形成された分割ラインに沿ってレーザ光を走査する回数が、前記溝が形成されない分割ラインに沿ってレーザ光を走査する回数よりも少ないことを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、MEMS (Micro Electro Mechanical System) に代表される、半導体基板の一部を薄厚化したダイアフラム構造や梁構造を有する

50

半導体基板を分割して製造される半導体装置の製造方法、およびこの製造方法により形成された半導体装置を実装する半導体モジュールの製造方法に関するものである。

【背景技術】

【0002】

上記MEMSにより製造される、一部を薄厚化したダイアフラム構造や梁構造を有する半導体装置に、MEMS圧力センサやMEMS加速度センサがあり、このようなセンサ類は、一般的に半導体ウェハプロセスにおいて複数の上記ダイアフラム構造や梁構造が同時に形成された後に、個々に分割されて製造される。この分割は、ダイヤモンドやCBNの粒子をボンド材で保持させた環状のダイシングソーを高速回転させて破碎加工する手法が最も一般的に用いられる。このダイシングソーによる加工は、破碎屑の洗浄および摩擦熱の冷却のために切削水を流しながら行われるため、またダイアフラム構造や梁構造は脆弱な構造であるため、ダイシングソーによる加工時の切削水圧力によりダイアフラム構造や梁構造が破壊されてしまうという課題があった。10

【0003】

近年、このような課題を解決する方法として、レーザ光による加工が注目されており、その一例が、例えば特許文献1に開示されている。

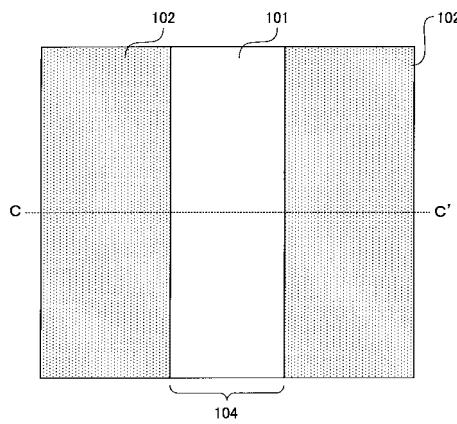

この特許文献1に開示されているレーザ光による製造方法は、半導体ウェハ内に多光子吸収による改質領域を形成し、この改質領域を起点とした劈開にて分割している。多光子吸収とは、光子のエネルギーが材料の吸収のバンドギャップよりも小さい場合、つまり光学的に透過となる場合でも、光の強度を非常に大きくすると材料に吸収が生じる現象であり、半導体ウェハの内部にレーザ光の集光点をあわせることで多光子吸収の現象を引き起こし、半導体ウェハの内部に改質領域を形成する。そして、形成した改質領域を起点として、ダイシングレーンに沿って、基板を容易に割ることで、切削水を必要としない分割を可能としている。20

【0004】

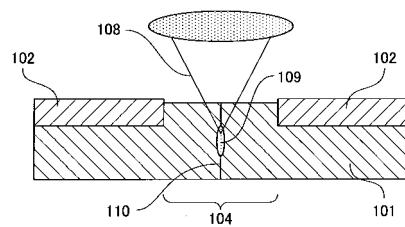

このレーザ加工方法について、図面に基づいて説明する。図9は被レーザ加工物である半導体基板の分割ラインおよびその周辺を示す平面図、図10はレーザ加工中の図9に示すC-C'断面図である。図9および図10において、101は半導体基板、102は半導体基板101に形成された半導体装置を構成する半導体デバイス(半導体素子)、104は半導体デバイス102の分割ライン、108はレーザ光、109は改質領域、110は改質領域109を起点として生じた切断部(クラック)を示している。30

【0005】

以下、レーザ加工方法の工程を説明する。

まず、レーザ光108を半導体基板101の内部に集光点をあわせ、所定の厚み方向に多光子吸収を生じさせる。

【0006】

次に、多光子吸収を連続的、または断続的に生じさせながら、レーザ光108を分割ライン104の中心に沿って走査されることにより、半導体基板101の内部に、分割ライン104に沿った改質領域109を形成し、切断部110を形成する。

【0007】

次に、半導体基板101の両端に同時に外力をかけて、改質領域109を起点として半導体基板101を割り、半導体装置を形成する。このとき、改質領域109を起点として、切断部110が形成されているため、比較的小さな外力で、半導体基板101を容易に割ることができる。なお、特に半導体基板101が薄い場合は、特に外力を与えないでも、自然に厚み方向に割れる。40

【0008】

また上記レーザ加工による方法以外に、切削水圧力によりダイアフラム構造や梁構造が破壊されてしまうという課題を解決する他の方法として、分割ライン上に予め異方性エッチングなどで溝を形成しておき、加工部分の厚みを抑える方法がある。この方法は、例えば特許文献2に開示されている。50

**【0009】**

特許文献2に開示されている製造方法では、まず方位面(100)面の半導体基板に、縦方向および横方向に分割ラインを開口するようにエッチング保護膜を形成し、その後、異方性エッチング処理を行う。このエッチング処理では、方位面(111)面でエッチングが止まるため、傾斜確度54.7度のV溝が形成される。次に、V溝が拡張するように半導体基板に外力を加えて、V溝に沿って半導体基板を分割し、個々の半導体装置を形成する。

【特許文献1】特許第3408805号公報

【特許文献2】特開2001-127008号公報

【発明の開示】

10

【発明が解決しようとする課題】

【0010】

しかしながら、特許文献1に開示されているレーザ加工方法では、半導体基板101が厚い場合においては、一回の走査による改質領域109では分割できないため、複数回レーザ加工を実施して、複数の改質領域109を厚み方向に平行に形成する必要があり、加工にかかるタクトの増加につながるという課題がある。

【0011】

20

また、特許文献2に開示されているV溝を形成する製造方法では、以下の課題がある。

分割ラインの縦方向および横方向にV溝が交差する部分においては、異方性エッチングの侵食が他の部分と異なるため、過剰にエッチングを行うと、方位面(111)面でエッチングが止まらず、例えば方位面(211)面にエッチングが進行する。すなわち、例えばV溝よりも深いエッチングを要するダイアフラム構造を形成する工程と同時にV溝を形成しようとした場合、V溝の交差部分が過剰にエッチングされ、半導体基板を貫通してしまうため、半導体基板の強度が極端に劣化し、ハンドリング時に半導体基板が破損してしまう。

【0012】

そこで、本発明は、半導体基板の一部を薄厚化したダイアフラム構造や梁構造を有する半導体基板を個々の半導体装置に分割する際ににおいて、分割の品質を低下させることなく、加工タクトの向上を可能とする、すなわち、レーザ加工の走査回数を抑えることができ、且つ強度劣化による破損のない半導体装置の製造方法、およびこの製造方法により形成された半導体装置を実装する半導体モジュールの製造方法を提供することを目的とするものである。

30

【課題を解決するための手段】

【0015】

上記課題を解決するために、本発明のうち請求項1に記載の半導体装置の製造方法は、半導体基板に形成された、複数の半導体素子を個々に分割して半導体装置を製造する方法であって、前記複数の半導体素子を個々に分割するための、互いに交差する第一の方向および第二の方向の分割ラインを設定し、前記半導体素子を囲む、前記第一の方向および第二の方向の分割ラインのうち、第一の方向の分割ライン上にエッチングにより溝を形成する工程と、前記第一の方向の分割ラインに形成された前記溝のライン上、および第二の方向の分割ラインに沿って、レーザ光を照射して、半導体基板の内部に改質領域を形成する工程と、前記第一の方向および第二の方向の分割ラインに沿って半導体基板を分割して個々の半導体装置を形成する工程とを有し、前記溝は交差するパターンをもたないように形成されることを特徴とするものである。

40

【0016】

また請求項2記載の半導体装置の製造方法は、請求項1に記載の半導体装置の製造方法であって、前記半導体素子に、ダイアフラム構造を形成する工程をさらに有することを特徴とする。

また請求項3記載の半導体装置の製造方法は、請求項1または請求項2に記載の半導体装置の製造方法であって、前記第一の方向の分割ライン上の溝は連続的に形成されること

50

を特徴とする。

また請求項4記載の半導体装置の製造方法は、請求項1～請求項3のいずれか1項に記載の半導体装置の製造方法であって、前記第一の方向の分割ラインに形成される溝は、V溝に形成されることを特徴とする。

また請求項5記載の半導体装置の製造方法は、請求項1～請求項3のいずれか1項に記載の半導体装置の製造方法であって、前記第一の方向の分割ラインに形成される溝は、U溝に形成されることを特徴とする。

#### 【0017】

また請求項6に記載の半導体装置の製造方法は、請求項1～請求項5のいずれか1項に記載の半導体装置の製造方法であって、前記第一の方向の分割ライン上に溝を形成する工程と、前記半導体装置にダイアフラム構造を形成する工程とが、異方性エッチングにより行われることを特徴とするものである。10

また請求項7に記載の半導体装置の製造方法は、請求項1～請求項6のいずれか1項に記載の半導体装置の製造方法であって、前記半導体基板の内部に改質領域を形成する工程において、前記溝が形成された第一の方向の分割ラインに沿ってレーザ光を走査する回数が、前記溝が形成されない第二の方向の分割ラインに沿ってレーザ光を走査する回数よりも少ないことを特徴とする。

また請求項8に記載の半導体装置の製造方法は、請求項1～請求項7のいずれか1項に記載の半導体装置の製造方法であって、前記第一および第二の方向の分割ラインに沿って半導体基板を分割して個々の半導体装置を形成する工程は、前記半導体基板に外力を加えることにより行われることを特徴とする。20

#### 【0018】

また請求項9に記載の半導体モジュールの製造方法は、前記請求項1～請求項8のいずれかの半導体装置の製造方法において形成された半導体装置を、実装基板に固着する工程を有することを特徴とする。

また請求項10に記載の半導体モジュールの製造方法は、請求項9に記載の半導体モジュールの製造方法であって、前記半導体装置を実装基板に固着する工程において、前記半導体装置の裏面が、ダイボンド材によって前記実装基板の上面に接着されることを特徴とするものである。

#### 【0019】

また請求項11に記載の半導体装置の製造方法は、半導体基板に形成された、複数の半導体素子を個々に分割して半導体装置を製造する方法であって、前記複数の半導体素子を個々に分割するための、互いに交差する第一の方向および第二の方向の分割ラインを設定し、前記半導体素子を囲む、前記第一の方向および第二の方向の分割ラインのうち、一方の分割ライン上にエッチングにより溝を形成する工程と、前記第一の方向および第二の方向の分割ラインに沿って、レーザ光を照射して、半導体基板の内部に改質領域を形成する工程と、前記第一の方向および第二の方向の分割ラインに沿って半導体基板を分割して個々の半導体装置を形成する工程とを有し、前記溝は交差するパターンをもたないように形成され、前記半導体基板の内部に改質領域を形成する工程において、前記溝が形成された分割ラインに沿ってレーザ光を走査する回数が、前記溝が形成されない分割ラインに沿ってレーザ光を走査する回数よりも少ないことを特徴とするものである。3040

#### 【発明の効果】

#### 【0021】

本発明の半導体装置の製造方法は、交差する第一の方向および第二の方向の分割ラインのうち第一の方向の分割ライン上のみに、溝をエッチングで形成するため、エッチングの制御が極めて難しい溝の交差部分ができないので、極めて容易に安定した溝を形成でき、また溝の形成された第一の方向の分割ラインに沿って個々の半導体装置に分割するため、溝を形成しない場合に比較して、容易に直進性に優れた分割を行うことができる、という効果を有している。

#### 【0022】

50

また本発明の半導体装置の製造方法は、半導体基板を個々の半導体装置に分割する工程において、半導体基板を個々の半導体装置に分割するための起点となる半導体基板内部に改質領域を形成する際、溝が形成された分割ラインに沿ってレーザ光を走査する回数が、溝が形成されない分割ラインに沿ってレーザ光を走査する回数よりも少なくても、直進性のよい安定した分割が可能であり、分割ラインに溝が形成されていない場合と比較して加工タクトを短縮することができる、という効果を有している。

#### 【発明を実施するための最良の形態】

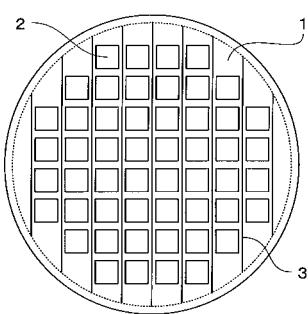

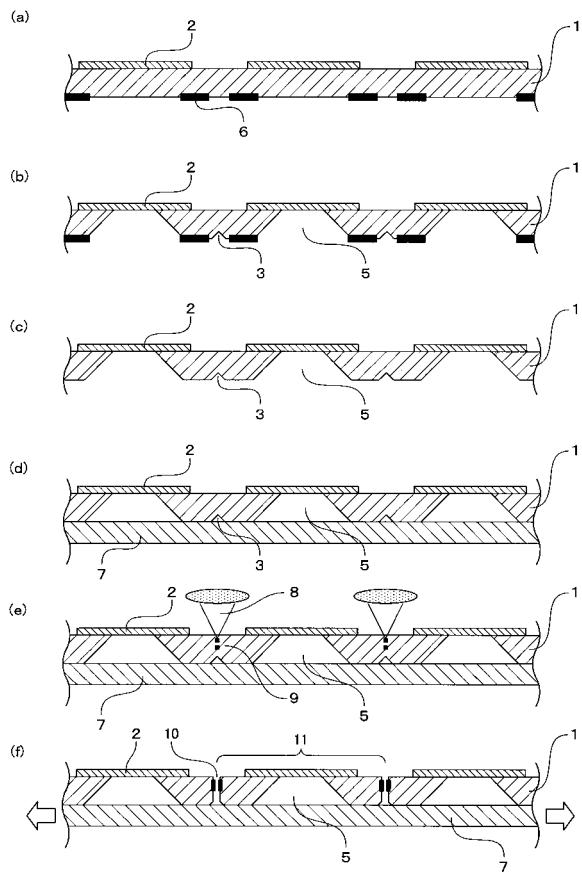

##### 【0026】

以下、本発明の実施の形態を、図面を参照しながら説明する。

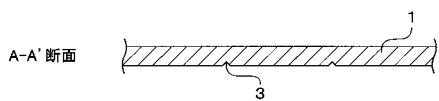

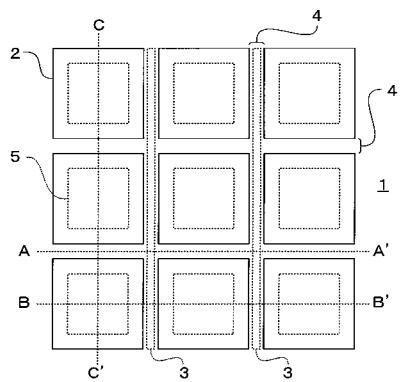

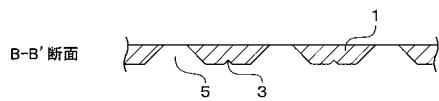

図1は、本発明の実施形態における複数の半導体素子が形成された半導体基板の平面図、図2は図1の拡大図、図3および図4はそれぞれ図2におけるA-A'断面図、B-B'断面図である。

##### 【0027】

図1～図4において、1はSi単結晶からなる半導体基板、2は半導体装置を構成する半導体デバイス(半導体素子)、3はV溝(溝の一例)、4は分割ライン、5はダイアフラムを示しており、図3のA-A'断面図は、横方向の分割ライン4に沿った半導体基板1の断面図、図4のB-B'断面図は、ダイアフラム5が形成された半導体デバイス2に沿った横方向の半導体基板1の断面図である。

##### 【0028】

図1および図2に示すように、半導体基板1には、縦方向および横方向に格子状に複数の半導体デバイス2が形成されており、半導体デバイス2には、それぞれダイアフラム5が形成されている。

##### 【0029】

また複数の半導体デバイス2は、分割ライン4で区切られている。ここで分割ライン4は、半導体基板1から、半導体デバイス2を個々に分割する際に設定される分割領域である。そして、分割ライン4は、縦方向および横方向に直交する(交差する)ように形成されており、これら直交する分割ラインのうち、縦方向または横方向の一方の平行する分割ライン(図では縦方向の分割ライン)上のみにV溝3が形成されている。これらV溝3は、例えば傾斜角度が54.7度となる方位面(111)面で形成されている。

##### 【0030】

次に、図5を参照して、本発明の半導体装置の製造方法を説明する。図5は、図4に示すB-B'断面図を用いた本発明の半導体装置の製造方法の工程を順に示す断面図である。図5において、6はエッティングマスク、7はエキスピンドテープ、8はレーザ光、9は改質領域、10は改質領域を起点としたクラック(切断部)、11は半導体基板1から個々の半導体デバイス2を切り出した後の半導体装置を示している。

##### 【0031】

まず、「縦方向の平行する分割ライン上のみに連続して、異方性エッティングによりV溝を形成する工程」を実行する。

すなわち、まず図5(a)に示すように、複数の半導体デバイス2が形成され、個々の半導体デバイス2を分割するための分割ライン(図示せず)が設定された半導体基板1に、エッティングマスク6を形成する。エッティングマスク6は、ダイアフラム5およびV溝3を形成したい領域が開口するように形成する。このとき、V溝3を形成するためのエッティングマスク6の開口は、一方の平行する分割ライン4上のみに形成する。

##### 【0032】

ここで、例えばエッティングマスク6は、シリコン酸化膜などの材料をCVD法を用いて形成した後、リソグラフィ技術でパターニングして形成する。なお、図示していないが、このとき半導体デバイス2が形成された面には全面にエッティングマスクを残しておく。

##### 【0033】

次に、図5(b)に示すように、ダイアフラム5およびV溝3を異方性エッティングにより形成する。ここで、異方性エッティング液としては、例えばKOH溶液や、TMAH(水

10

20

30

40

50

酸化テトラメチルアンモニウム) 溶液が使用される。このとき、V溝3は一方の平行する分割ライン4上のみに形成されるので、交差するパターンをもたない。よって、Si単結晶基板からなる半導体基板1のエッチングは、交差パターン部分の異常侵食がなく、方位面(111)面で確実に進行が止まるため、エッチング深さの異なるダイアフラム5と、V溝3を同時に形成しても、傾斜角54.7度となる深さでストップさせることができる。つまりV溝3の深さと幅は、エッチングマスク6の開口幅で決定できる。

#### 【0034】

次に図5(c)に示すように、エッチングマスク6を除去する。エッチングマスク6の除去には、例えばBHF溶液を用いる。ここで、エッチングマスク6を除去しているが、特に必要なければ、エッチングマスク6は残しておいても構わない。

10

#### 【0035】

続いて、「直交する分割ラインに沿ってそれぞれ、レーザ光を半導体基板の内部に焦点をあわせて照射して、半導体基板の内部に改質領域を形成する工程」を実行する。

すなわち、まず図5(d)に示すように、エキスピンドテープ7に半導体基板1をマウントする。

#### 【0036】

次に、図5(e)に示すように、直交する分割ライン4に沿ってそれぞれ、レーザ光8を半導体基板1の内部に焦点をあわせて照射して、半導体基板1の内部に改質領域9を形成する。このとき、縦方向のレーザ光8の走査は、V溝3のライン上に沿って実施し、改質領域9から発生するマイクロクラックがV溝3に進展するように実施する。

20

#### 【0037】

最後に、「半導体基板に外力を加えることにより、直交する分割ラインに沿って半導体基板を個々の半導体装置に分割する工程」を実行する。

すなわち、図5(f)に示すように、エキスピンドテープ7に外力を加えて、直交する分割ライン4に沿ってそれぞれ形成された改質領域9からクラック10を進展させて半導体基板1を分割し、個々の半導体装置11を形成する。

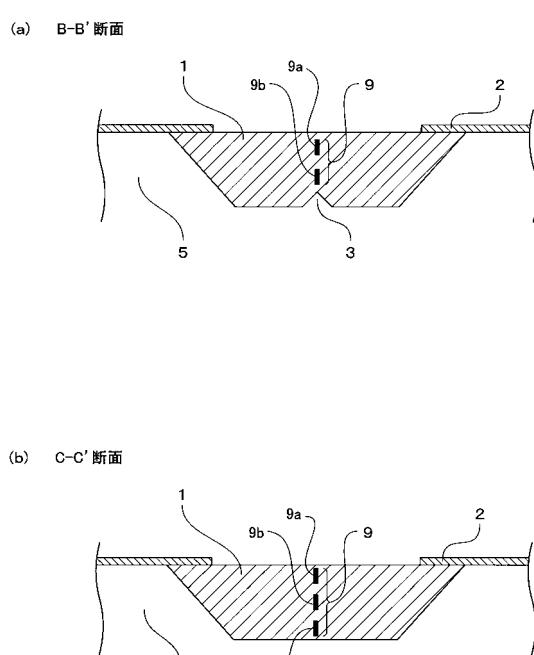

#### 【0038】

ここで、半導体基板1が厚い場合、レーザ光8の走査を複数回行って改質領域9を複数形成することにより、分割を容易にすることができますが、図6(a),(b)に示すように、V溝3が形成されている分割ライン4に沿ってレーザ光8を走査する回数は、V溝3が形成されていない分割ライン4に沿ってレーザ光8を走査する回数より少なくとも、分割が可能である。

30

#### 【0039】

図6(a)は、上記半導体基板1のB-B'断面の拡大図であり、V溝3が形成された分割ライン4に沿って形成された、レーザ光8の走査回数を2回としたときの深さ方向の改質領域9a,9bを示し、また図6(b)は、ダイアフラム5が形成された半導体デバイス2に沿った縦方向の半導体基板1のC-C'断面の拡大図であり、V溝3が形成されていない分割ライン4に沿って形成された、レーザ光8の走査回数を3回としたときの深さ方向の改質領域9a,9b,9cを示している。

#### 【0040】

40

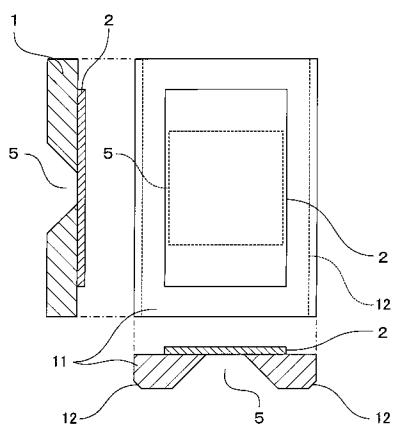

このようにして、個々に分割された半導体装置11は、図7に示すように、ダイアフラム構造を有する半導体装置となる。

以上のように、半導体基板1の構成および半導体装置11の製造方法によれば、半導体基板1を個々の半導体装置11に分割するための起点となる改質領域9を形成する際、V溝3が形成された分割ライン4に沿ってレーザ光8を走査する回数を、V溝3の無い分割ライン4に沿ってレーザ光8を走査する回数よりも少なくすることができ、加工タクトを短くすることができ、また直進性の良い安定した分割を可能にできる。

#### 【0041】

また直交する分割ライン4のうち一方の平行する分割ライン上のみに、V溝3を連続するようにエッチングで形成するため、エッチングの制御が極めて難しいV溝3の交差部分

50

ができないことにより、極めて容易に安定したV溝3を形成でき、また連続したV溝3が形成された分割ライン4に沿って個々の半導体装置11に分割するため、V溝3を形成しない場合と比較して、容易に直進性に優れた分割を行うことができる。

#### 【0042】

またV溝3の形成は、ダイアフラム構造を形成する異方性エッチング工程と同時に行われるため、特に工程の増加がなく、コストアップや、リードタイムが増加することを回避できる。

#### 【0043】

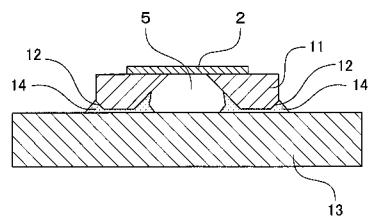

図7に、分割された後の半導体装置の平面図、横断面図、縦断面図を示す。図7において、11は個々に分割された後の半導体装置、12はV溝の頂点を起点に分割された際にできる面取りであり、個々の半導体装置11の裏面側において対向する2辺のみに、面取り12が形成されている。10

#### 【0044】

図7に示すように、V溝3が形成された部分に相当する面取り12の部分は、半導体装置11の長辺側に配置している。すなわち、V溝3を形成する分割ライン4として、半導体装置11の長辺側に沿った分割ラインを選択し、V溝3を形成している。

#### 【0045】

一般的に半導体装置は長細いと折れやすいが、折れる際の起点は、長辺側にできたクラックであり、長辺側を面取りすることで、起点となるクラックが無くなるため半導体装置の抗折強度は、飛躍的に向上する。すなわち、半導体装置11の抗折強度の低下につながる長辺のチッピングが抑制され、機械的強度の優れた半導体装置11を得ることができる。20

#### 【0046】

図8に本発明の半導体装置が基板に実装されている状態の断面図を示す。図8において、13は実装基板、14は実装基板13と半導体装置11を接着するためのダイボンド材である。

#### 【0047】

通常、半導体装置11と実装基板13との接着はダイボンド材14で行われるが、接着の際には半導体装置11の側面への這い上がりを制御するために、ダイボンド材14の塗布量を厳しく制御する必要がある。図8に示すように、半導体装置11に面取り12が施されている場合、ダイボンド材の半導体装置11の側面への這い上がりは、面取り12の表面張力によって抑制されるため、従来よりも極めて容易に管理が可能である。また残りの二辺側(短辺側)には面取りを行わないことで、短辺側の半導体装置11の裏面の面積を減少させることなく、ダイボンド時の接着面積を確保できる。30

#### 【0048】

なお、本実施の形態では、半導体基板1および半導体装置11にダイアフラム構造を形成しているが、特にダイアフラム構造でなくても勿論構わない。

また本実施の形態では、直交する分割ラインのうち、縦方向または横方向の一方の平行する分割ライン上のみに形成されている溝を、V溝としているが、V溝に限ることはなく、U溝とすることも可能である。また溝を異方性エッチングにより形成しているが、ドライエッチングにより形成することも可能である。40

#### 【産業上の利用可能性】

#### 【0049】

本発明の半導体基板、および半導体装置ならびにその半導体装置の製造方法は、シリコン基板や、化合物半導体基板の分割において、加工コストの増加や、加工の品質を低下させることなく、半導体装置を製造するのに適し、特にダイアフラム構造を有するMEMSセンサ等を製造する際の分割として有用である。

#### 【図面の簡単な説明】

#### 【0050】

【図1】本発明の実施の形態における半導体基板の平面図である。

50

【図2】同半導体基板の分割ライン周辺を示す平面図である。

【図3】図2におけるA-A'断面図である。

【図4】図2におけるB-B'断面図である。

【図5】本発明の実施の形態における半導体装置の製造方法の工程を順に示す半導体基板の断面図である。

【図6】同半導体装置の製造方法を示す断面図である。

【図7】本発明の実施の形態における半導体装置の平面図および縦・横断面図である。

【図8】同半導体装置が実装された半導体基板の断面図である。

【図9】従来の半導体基板の平面図である。

【図10】従来の半導体装置の製造方法を示す断面図である。

10

【符号の説明】

【0051】

1 半導体基板

2 半導体デバイス

3 V溝

4 分割ライン

5 ダイアフラム

6 エッチングマスク

7 エキスピンドテープ

8 レーザ光

20

9, 9a, 9b, 9c 改質領域

10 クラック

11 半導体装置

12 面取り

13 実装基板

14 ダイボンド材

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

---

フロントページの続き

(51)Int.Cl. F I

H 01L 29/84 (2006.01) B 23K 26/00 H

B 23K 101/40 (2006.01) H 01L 29/84 Z

B 23K 101:40

(56)参考文献 特開2004-363517(JP,A)

特開2006-173428(JP,A)

特開2005-268752(JP,A)

特開平05-285935(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01L 21/301

B 81B 3/00

B 23K 26/00-26/42